# ADVANCED INFORMATION MX26L3220

#### 32M-BIT [2M x 16] CMOS MULTIPLE-TIME-PROGRAMMABLE EPROM

#### FEATURES

- 2,097,152 x 16 byte structure

- Single Power Supply Operation

- 2.7 to 3.6 volt for read, erase, and program operations

- Low Vcc write inhibit is equal to or less than 2.5V

- Compatible with JEDEC standard

- High Performance

- Fast access time: 90/120ns (typ.)

- Fast program time: 70s/chip (typ.)

- Fast erase time: 90s/chip (typ.)

- Low Power Consumption

- Low active read current: 17mA (typ.) at 5MHz

- Low standby current: 30uA (typ.)

- Minimum 100 erase/program cycle

Status Reply

- Data polling & Toggle bits provide detection of program and erase operation completion

- 12V ACC input pin provides accelerated program capability

- Output voltages and input voltages on the device is deterined by the voltage on the VI/O pin.

- VI/O voltage range:1.65V~3.6V

- 10 years data retention

- Package

- 44-Pin SOP

- 48-Pin TSOP

- 48-Ball CSP

#### GENERAL DESCRIPTION

The MX26L3220 is a 32M bit MTP EPROM<sup>™</sup> organized as 2M bytes of 16 bits. MXIC's MTP EPROM<sup>™</sup> offer the most cost-effective and reliable read/write non-volatile random access memory. The MX26L3220 is packaged in 44-pin SOP, 48-pin TSOP and 48-ball CSP. It is designed to be reprogrammed and erased in system or in standard EPROM programmers.

The standard MX26L3220 offers access time as fast as 90ns, allowing operation of high-speed microprocessors without wait states. To eliminate bus contention, the MX26L3220 has separate chip enable ( $\overline{CE}$ ) and output enable  $\overline{OE}$  controls. MXIC's MTP EPROM<sup>TM</sup> augment EPROM functionality with in-circuit electrical erasure and programming. The MX26L3220 uses a command register to manage this functionality.

MXIC's MTP EPROM<sup>™</sup> technology reliably stores memory contents even after 100 erase and program cycles. The MXIC cell is designed to optimize the erase and program mechanisms. In addition, the combination of advanced tunnel oxide processing and low internal electric fields for erase and programming operations produces reliable cycling.

The MX26L3220 uses a 2.7V to 3.6V VCC supply to perform the High Reliability Erase and auto Program/ Erase algorithms.

The highest degree of latch-up protection is achieved with MXIC's proprietary non-epiprocess. Latch-up protection is proved for stresses up to 100 milliamps on address and data pin from -1V to VCC +1V.

#### **PIN CONFIGURATION**

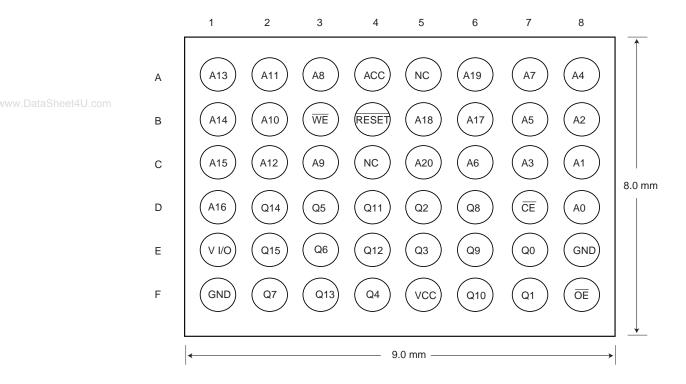

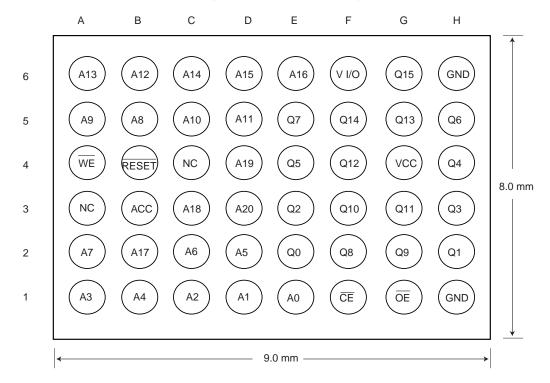

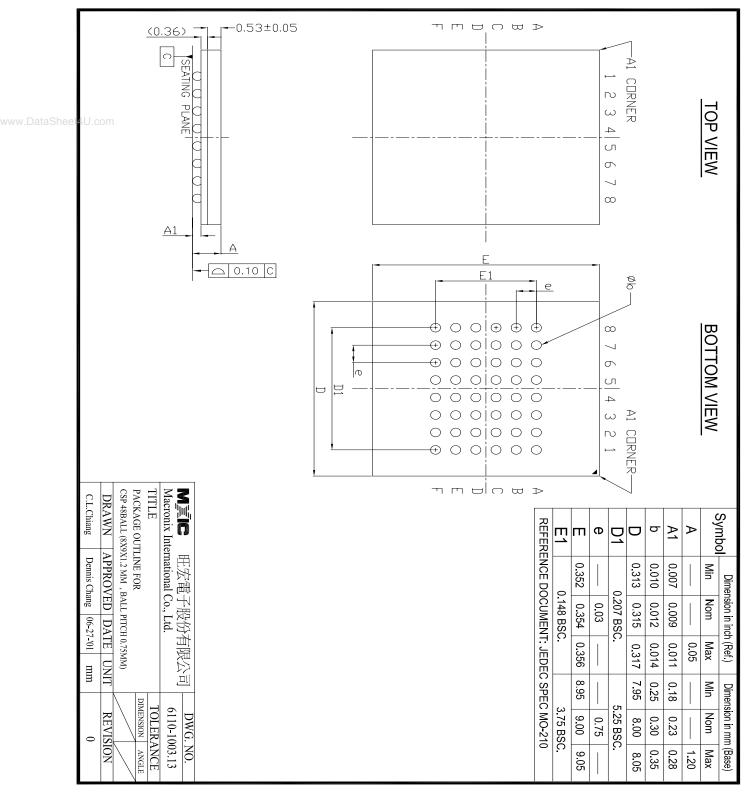

#### 48 CSP

#### 1. Ball pitch=0.75mm for MX26L3220XA (TOP view, Ball down)

#### 2. Ball pitch=0.8mm for MX26L3220XB(TOP view, Ball down)

## MX26L3220

#### **44 SOP**

|                  | _          |    |           |    | _   |     |

|------------------|------------|----|-----------|----|-----|-----|

| NC [             | <b>_</b> [ | 0  |           | 44 |     | A20 |

| A18 [            |            | 2  |           | 43 |     | A19 |

| A17 [            |            | 3  |           | 42 |     | A8  |

| A7 [             |            | 4  |           | 41 |     | A9  |

| A6 [             |            | 5  |           | 40 | F   | A10 |

| A5 [             |            | 6  |           | 39 | IF. | A11 |

| A3 5             |            | 7  |           | 38 | F   | A12 |

| A3 [             |            | 8  |           | 37 | F   | A13 |

| A3 -             |            | 9  |           | 36 | F   | A14 |

| A2 5             |            | 10 | 0         | 35 | F   | A15 |

| AT C             |            | 11 | 53        | 34 | F   | A16 |

|                  |            | 12 | Ľ         | 33 | E   | WE  |

|                  |            | 13 | MX26L3220 | 32 | E   | GND |

|                  |            | 14 | ×         | 31 | E   | Q15 |

| OE [             |            | 15 | $\geq$    | 30 | E   | Q7  |

| Q0 [             |            | 16 |           |    | E   |     |

| Q8 L             |            |    |           | 29 | Ľ   | Q14 |

| Q1 [             |            | 17 |           | 28 | E   | Q6  |

| Q9 [             |            | 18 |           | 27 | E.  | Q13 |

| Q2               |            | 19 |           | 26 |     | Q5  |

| Q10              |            | 20 |           | 25 |     | Q12 |

| Q3 [             |            | 21 |           | 24 |     | Q4  |

| Q11 <sup>[</sup> | =1         | 22 |           | 23 |     | VCC |

|                  | _          |    |           |    | -   |     |

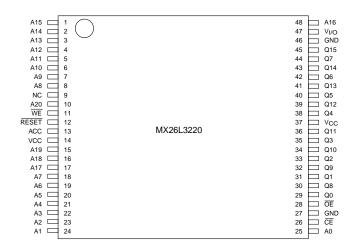

#### 48 TSOP

#### **PIN DESCRIPTION**

| SYMBOL | PINNAME                           |

|--------|-----------------------------------|

| A0~A20 | Address Input                     |

| Q0~Q15 | Data Inputs/Outputs               |

| CE     | Chip Enable Input                 |

| WE     | Write Enable Input                |

| OE     | Output Enable Input               |

| RESET  | Hardware Reset Pin, Active Low    |

| VCC    | +3.0V single power supply         |

| ACC    | Hardware Acceleration Pin         |

| V I/O  | I/O power supply (for 48 TSOP and |

|        | 48 CSP package only)              |

| GND    | Device Ground                     |

| NC     | Pin Not Connected Internally      |

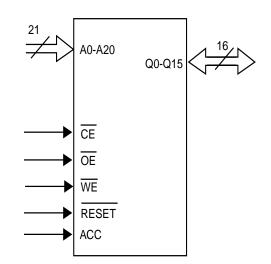

#### LOGIC SYMBOL

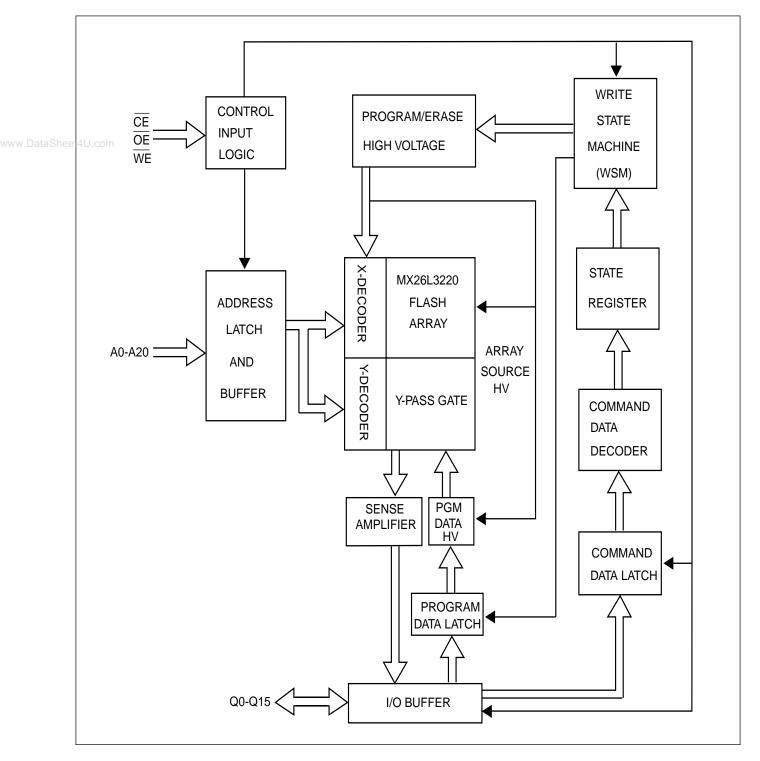

#### **BLOCK DIAGRAM**

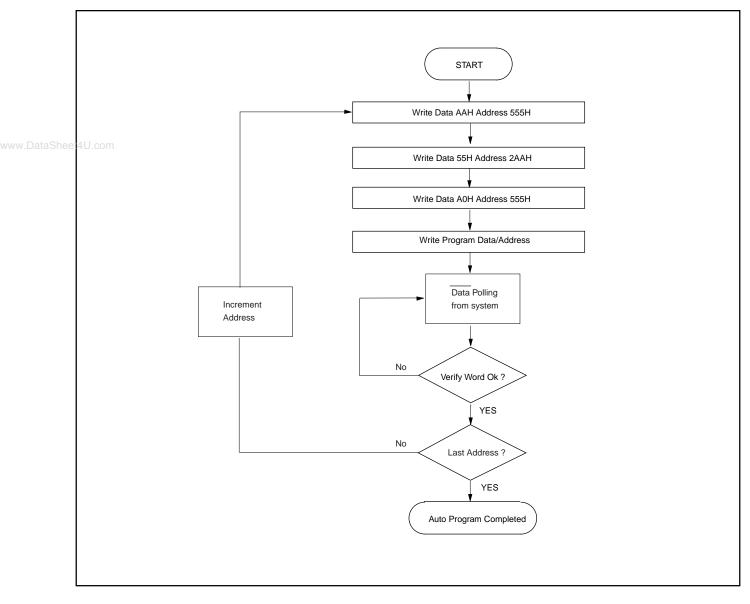

#### AUTOMATIC PROGRAMMING

The MX26L3220 is word programmable using the Automatic Programming algorithm. The Automatic Programming algorithm makes the external system do not need to have time out sequence nor to verify the data programmed. The typical chip programming time at room temperature of the MX26L3220 is less than 90 seconds.

#### AUTOMATIC PROGRAMMING ALGORITHM

MXIC's Automatic Programming algorithm require the user to only write program set-up commands (including 2 unlock write cycle and A0H) and a program command (program data and address). The device automatically times the programming pulse width, provides the program verification, and counts the number of sequences. A status bit similar to DATA polling and a status bit toggling between consecutive read cycles, provide feedback to the user as to the status of the programming operation.

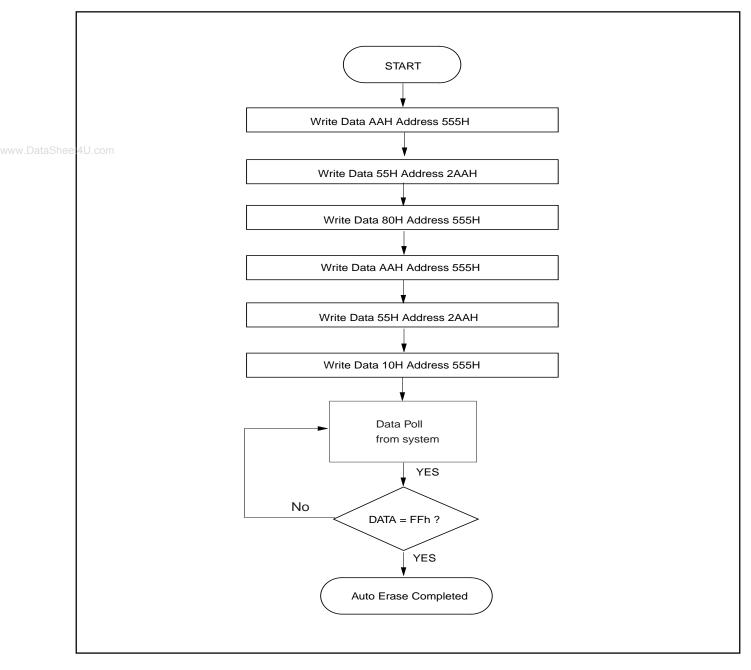

#### AUTOMATIC CHIP ERASE

The entire chip is bulk erased using 50 ms erase pulses according to MXIC's Automatic Chip Erase algorithm. Typical erasure at room temperature is accomplished in less than 45 seconds. The Automatic Erase algorithm automatically programs the entire array prior to electrical erase. The timing and verification of electrical erase are controlled internally within the device.

#### AUTOMATIC ERASE ALGORITHM

MXIC's Automatic Erase algorithm requires the user to write commands to the command register using standard microprocessor write timings. The device will automatically pre-program and verify the entire array. Then the device automatically times the erase pulse width, provides the erase verification, and counts the number of sequences. A status bit toggling between consecutive read cycles provides feedback to the user as to the status of the programming operation.

Register contents serve as inputs to an internal statemachine which controls the erase and programming circuitry. During write cycles, the command register internally latches address and data needed for the programming and erase operations. All address are latched on the falling edge of WE or CE, whichever happens later. All data are latched on the rising edge of  $\overline{WE}$  or  $\overline{CE}$ , whichever happens later.

MXIC's Flash technology combines years of EPROM experience to produce the highest levels of quality, reliability, and cost effectiveness. The MX26L3220 electrically erases all bits simultaneously using Fowler-Nordheim tunneling. The bytes are programmed by using the EPROM programming mechanism of hot electron injection.

During a program cycle, the state-machine will control the program sequences and command register will not respond to any command set. After the state machine has completed its task, it will allow the command register to respond to its full command set.

#### Table 1. BUS OPERATION(1)

| Operation      | CE       | OE | WE | RESET    | Address         | Q15~Q0           |

|----------------|----------|----|----|----------|-----------------|------------------|

| Read           | L        | L  | Н  | н        | A <sub>IN</sub> | D <sub>OUT</sub> |

| Write(Note 1)  | L        | Н  | L  | н        | A <sub>IN</sub> | D <sub>IN</sub>  |

| Standby        | VCC±0.3V | Х  | Х  | VCC±0.3V | Х               | High-Z           |

| Output Disable | L        | Н  | Н  | н        | Х               | High-Z           |

| Reset          | Х        | Х  | X  | L        | Х               | High-Z           |

Legend:

L=Logic LOW=V<sub>IL</sub>,H=Logic High=V<sub>IH</sub>,V<sub>ID</sub>=12.0±0.5V,X=Don't Care, A<sub>IN</sub>=Address IN, D<sub>IN</sub>=Data IN, D<sub>OUT</sub>=Data OUT

Notes:

1. When the ACC pin is at  $V_{HH}$ , the device enters the accelerated program mode. See "Accelerated Program Operations" for more information.

|                   |    |    |    |           |    | A5 |            | <b>A</b> 8 |                 | A14 |         |                      |

|-------------------|----|----|----|-----------|----|----|------------|------------|-----------------|-----|---------|----------------------|

| Operation         | CE | OE | WE | <b>A0</b> | A1 | to | <b>A</b> 6 | to         | A9              | to  | A15~A21 | Q15~Q0               |

|                   |    |    |    |           |    | A2 |            | A7         |                 | A10 |         |                      |

| Read Silicon ID   | L  | L  | Н  | L         | L  | Х  | L          | Х          | V <sub>ID</sub> | Х   | X00     | C2H                  |

| Manufactures Code |    |    |    |           |    |    |            |            |                 |     |         |                      |

| Read Silicon ID   | L  | L  | Н  | Н         | L  | Х  | L          | Х          | V <sub>ID</sub> | Х   | Х       | 22FDH                |

| Device Code       |    |    |    |           |    |    |            |            |                 |     |         |                      |

| Secured Silscon   |    |    |    |           |    |    |            |            |                 |     |         | xx88h                |

| Sector Indicator  | L  | L  | н  | Н         | н  | X  | L          | Х          | $V_{ID}$        | Х   | Х       | (factory locked)     |

| Bit(Q7)           |    |    |    |           |    |    |            |            |                 |     |         | xx08h                |

|                   |    |    |    |           |    |    |            |            |                 |     |         | (non-factory locked) |

#### Table 2. AUTOSELECT CODES (High Voltage Method)

## REQUIREMENTS FOR READING ARRAY DATA

To read array data from the outputs, the system must drive the  $\overline{CE}$  and  $\overline{OE}$  pins to VIL.  $\overline{CE}$  is the power control and selects the device.  $\overline{OE}$  is the output control and gates array data to the output pins. WE should remain at VIH.

The internal state machine is set for reading array data upon device power-up, or after a hardware reset. This ensures that no spurious alteration of the memory contect occurs during the power transition. No command is necessary in this mode to obtain array data. Standard microprocessor read cycles that assert valid address on the device address inputs produce valid data on the device data outputs. The device remains enabled for read access until the command register contents are altered.

#### WRITE COMMANDS/COMMAND SEQUENCES

To program data to the device the system must drive  $\overline{\text{WE}}$  and  $\overline{\text{CE}}$  to VIL, and  $\overline{\text{OE}}$  to VIH.

An erase operation can erase the entire device. The "Writing specific address and data commands or sequences into the command register initiates device operations. Table 1 defines the valid register command sequences. Writing incorrect address and data values or writing them in the improper sequence resets the device to reading array data."section has details on erasing the entire chip.

After the system writes the autoselect command sequence, the device enters the autoselect mode. The system can then read autoselect codes from the internal register (which is separate from the memory array) on Q15-Q0. Standard read cycle timings apply in this mode. Refer to the Autoselect Mode and Autoselect Command Sequence section for more information.

ICC2 in the DC Characteristics table represents the active current specification for the write mode. The "AC Characteristics" section contains timing specification table and timing diagrams for write operations.

#### STANDBY MODE

MX26L3220 can be set into Standby mode with two different approaches. One is using both  $\overline{CE}$  and  $\overline{RESET}$ pins and the other one is using  $\overline{RESET}$  pin only.

When using both pins of  $\overline{CE}$  and  $\overline{RESET}$ , a CMOS Standby mode is achieved with both pins held at Vcc ± 0.3V. Under this condition, the current consumed is less than 50uA (typ.). If both of the  $\overline{CE}$  and  $\overline{RESET}$  are held at VIH, but not within the range of VCC ± 0.3V, the device will still be in the standby mode, but the standby currect will be larger. During Auto Algorithm operation, Vcc active current (lcc2) is required even  $\overline{CE} = "H"$  until the operation is complated. The device can be read with standard access time (tCE) from either of these standby modes.

When using only RESET, a CMOS standby mode is achieved with RESET input held at Vss  $\pm$  0.3V, Under this condition the current is consumed less than 50uA (typ.). Once the RESET pin is taken high,the device is back to active without recovery delay.

In the standby mode the outputs are in the high impedance state, independent of the  $\overline{OE}$  input.

MX26L3220 is capable to provide the Automatic Standby Mode to restrain power consumption during read-out of data. This mode can be used effectively with an application requested low power consumption such as handy terminals.

To active this mode, MX26L3220 automatically switch themselves to low power mode when MX26L3220 addresses remain stable during access time of tACC+30ns. It is not necessary to control CE, WE, and OE on the mode. Under the mode, the current consumed is typically 50uA (CMOS level).

#### OUTPUT DISABLE

With the  $\overline{OE}$  input at a logic high level (VIH), output from the devices are disabled. This will cause the output pins to be in a high impedance state.

#### **RESET OPERATION**

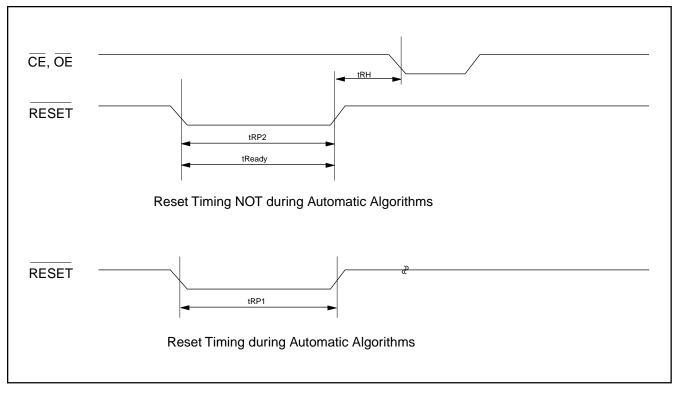

The RESET pin provides a hardware method of resetting the device to reading array data. When the RESET pin is driven low for at least a period of tRP, the device immediately terminates any operation in progress, tristates all output pins, and ignores all read/write commands for the duration of the RESET pluse. The device also resets the internal state machine to reading array data. The operation that was interrupted should be reinitated once the device is ready to accept another command sequence, to ensure data integrity

Current is reduced for the duration of the RESET pulse. When RESET is held at VSS±0.3V, the device draws CMOS standby current (ICC4). If RESET is held at VIL but not within VSS±0.3V, the standby current will be greater.

The RESET pin may be tied to system reset circuitry. A system reset would that also reset the MTP EPROM.

Refer to the AC Characteristics tables for RESET parameters and to Figure 14 for the timing diagram.

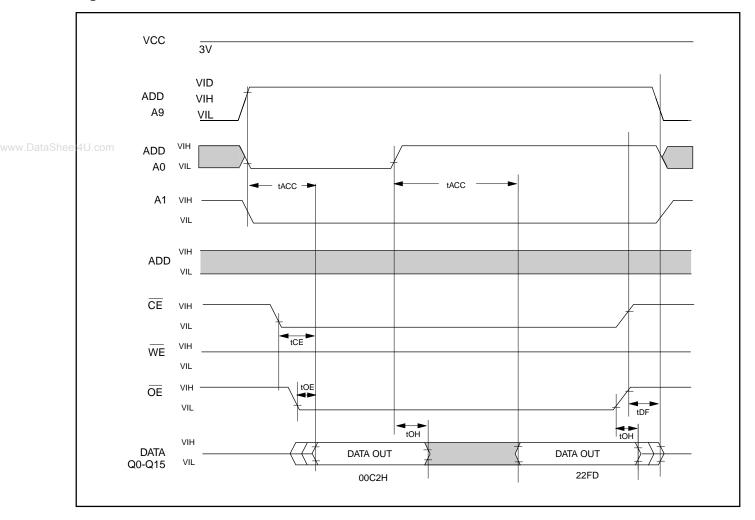

#### SILICON ID READ OPERATION

MTP EPROM are intended for use in applications where the local CPU alters memory contents. As such, manufacturer and device codes must be accessible while the device resides in the target system. EPROM programmers typically access signature codes by raising A9 to a high voltage. However, multiplexing high voltage onto address lines is not generally desired system design practice.

MX26L3220 provides hardware method to access the silicon ID read operation. Which method requires VID on A9 pin, VIL on  $\overline{CE}$ ,  $\overline{OE}$ , A6, and A1 pins. Which apply VIL on A0 pin, the device will output MXIC's manufacture code of C2H. Which apply VIH on A0 pin, the device will output MX26L3220 device code of 22FDH.

#### **VI/O PIN OPERATION**

MX26L3220 is capable to provide the I/O prower supply (VI/O) pin to control Input/Output voltage levels of the device. The data outputs and voltage tolerated at its data input is determined by the voltage on the VI/O pin. This device is allows to operate in 1.8V or 3V system as required.

#### Table 3

|              | VCC / VI/O Voltage Range |                    |  |  |  |  |  |  |  |  |

|--------------|--------------------------|--------------------|--|--|--|--|--|--|--|--|

| Part No.     | VCC=2.7V to 3.6V         | VCC=2.7V to 3.6V   |  |  |  |  |  |  |  |  |

|              | VI/O=2.7V to 3.6V        | VI/O=1.65V to 2.6V |  |  |  |  |  |  |  |  |

| MX26L3220-90 | 90ns                     | 100ns              |  |  |  |  |  |  |  |  |

| MX26L3220-12 | 120ns                    | 130ns              |  |  |  |  |  |  |  |  |

Notes: Typical values measured at VCC=2.7V to 3.6V, VI/O=2.7V to 3.6V

#### DATA PROTECTION

The MX26L3220 is designed to offer protection against accidental erasure or programming caused by spurious system level signals that may exist during power transition. During power up the device automatically resets the state machine in the Read mode. In addition, with its control register architecture, alteration of the memory contents only occurs after successful completion of specific command sequences. The device also incorporates several features to prevent inadvertent write cycles resulting from VCC power-up and power-down transition or system noise.

#### SECURED SILICON SECTOR

The MX26L3220 features a Flash memory region where the system may access through a command sequence to create a permant part identification as so called Electronic Serial Number (ESN) in the device. Once this region is programmed, any further modification on the region is impossible. The secured silicon sector is a 512 words in length, and uses a Secured Silicon Sector Indicator Bit (Q7) to indicate whether or not the Secured Silicon Sector is locked when shipped from the factory. This bit is permanently set at the factory and cannot be changed, which prevent duplication of a factory locked part. This ensures the security of the ESN once the product is shipped to the field.

The MX26L3220 offers the device with Secured Silicon Sector either factory locked or custor lockable. The factory-locked version is always protected when shipped from the factory , and has the Secured Silicon Sector Indicator Bit permanently set to a "1". The customerlockable version is shipped with the Secured Silicon Sector unprotected, allowing customer to utilize that sector in any form they prefer. The customer-lockable ver-

sion has the secured sector Indicator Bit permanently set to a "0". Therefore, the Secured Silicon Sector Indicator Bit permanently set to a "0". Therefore, the Second Silicon Sector Indicator Bit prevents customer, lockable device from being used to replace devices that are factory locked.

The system access the Secured Silicon Sector through a command sequence (refer to "Enter Secured Silicon/ Exit Secured Silicon Sector command Sequence). After the system has written the Enter Secured Silicon Sector command sequence, it may read the Secured Silicon Sector by using the address normally occupied by the address 00000h-0001FFh. This mode of operation continues until the system issues the Exit Secured Silicon Sector command sequence, or until power is removed from the device. On power-up, or following a hardware reset, the device reverts to sending command to address 00000h-0001FFFh.

#### LOW VCC WRITE INHIBIT

When VCC is less than VLKO the device does not accept any write cycles. This protects dataduring VCC power-up and power-down. The command register and all internal program/erase circuits are disabled, and the device resets. Subsequent writes are ignored until VCC is greater thanVLKO. The system must provide the proper signals to the control pins to prevent unintentional write when VCC is greater than VLKO.

#### WRITE PULSE "GLITCH" PROTECTION

Noise pulses of less than 5ns(typical) on  $\overline{CE}$  or  $\overline{WE}$  will not initiate a write cycle.

#### LOGICAL INHIBIT

Writing is inhibited by holding any one of  $\overline{OE} = VIL$ ,  $\overline{CE} = VIH$  or  $\overline{WE} = VIH$ . To initiate a write cycle  $\overline{CE}$  and  $\overline{WE}$  must be a logical zero while  $\overline{OE}$  is a logical one.

#### POWER-UP SEQUENCE

The MX26L3220 powers up in the Read only mode. In addition, the memory contents may only be altered after successful completion of the predefined command sequences.

#### FACTORY LOCKED:Secured Silicon Sector Programmed and Protected At the Factory

In device with an ESN, the Secured Silicon Sector is protected when the device is shipped from the factory. The Secured Silicon Sector cannot be modified in any way. A factory locked device has an 8-word random ESN at address 000000h-000007h.

#### CUSTOMER LOCKABLE:Secured Silicon Sector NOT Programmed or Protected At the Factory

As an alternative to the factory-locked version, the device may be ordered such that the customer may program and protect the 512-word Secured Silicon Sector. Programming and protecting the Secured Silicon Sector must be used with caution since, once protected, there is no procedure available for unprotecting the Secured Silicon Sector area and none of the bits in the Secured Silicon Sector memory space can be modified in any way.

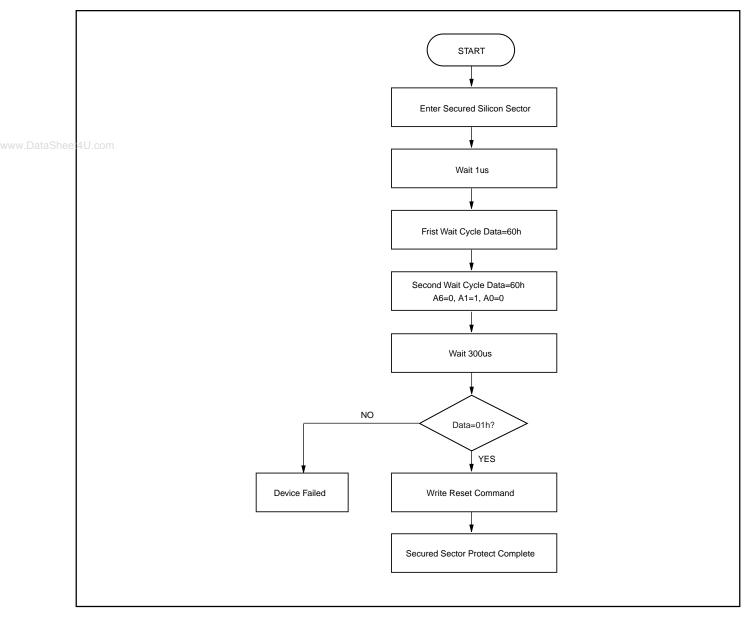

The Secured Silicon Sector area can be protected using the following procedures:

Write the three-cycle Enter Secured Silicon Sector Region command sequence. This allows in-system protection of the Secured Silicon Sector without raising any device pin to a high voltage. Note that method is only applicable to the Secured Silicon Sector.

Once the Secured Silicon Sector is programmed, locked and verified, the system must write the Exit Secured Silicon Sector Region command sequence to return to reading and writing the remainder of the array.

#### SOFTWARE COMMAND DEFINITONS

Device operations are selected by writing specific address and data sequences into the command register. Writing incorrect address and data values or writing them in the improper sequence will reset the device to the read mode. Table 4 defines the valid register command sequences. Either of the two reset command sequences will reset the device(when applicable). All addresses are latched on the falling edge of WE or  $\overline{CE}$ , whichever happens later. All data are latched on rising edge of WE or  $\overline{CE}$ , whichever happens first.

#### aSheet4U.com

|                       | First Bus |       | Second Bus Third Bus F |       |      | Fourth Bus |      | Fifth Bus |       | Sixth Bus |      |       |      |

|-----------------------|-----------|-------|------------------------|-------|------|------------|------|-----------|-------|-----------|------|-------|------|

| Command               | Bus       | Cycle |                        | Cycle |      | Cycle      |      | Cycle     |       | Cycle     |      | Cycle |      |

|                       | Cycle     | Addr  | Data                   | Addr  | Data | Addr       | Data | Addr      | Data  | Addr      | Data | Addr  | Data |

| Read(Note 5)          | 1         | RA    | RD                     |       |      |            |      |           |       |           |      |       |      |

| Reset(Note 6)         | 1         | XXX   | F0                     |       |      |            |      |           |       |           |      |       |      |

| Autoselect(Note 7)    |           |       |                        |       |      |            |      |           |       |           |      |       |      |

| Manufacturer ID       | 4         | 555   | AA                     | 2AA   | 55   | 555        | 90   | X00       | C2    |           |      |       |      |

| Device ID             | 4         | 555   | AA                     | 2AA   | 55   | 555        | 90   | X01       | 22FD  |           |      |       |      |

| Secured Sector        | 4         | 555   | AA                     | 2AA   | 55   | 555        | 90   | x03       | see   |           |      |       |      |

| Factory Protect       |           |       |                        |       |      |            |      |           | Note9 |           |      |       |      |

| Enter Secured Silicon | 3         | 555   | AA                     | 2AA   | 55   | 555        | 88   |           |       |           |      |       |      |

| Sector                |           |       |                        |       |      |            |      |           |       |           |      |       |      |

| Exit Secured Silicon  | 4         | 555   | AA                     | 2AA   | 55   | 555        | 90   | ххх       | 00    |           |      |       |      |

| Sector                |           |       |                        |       |      |            |      |           |       |           |      |       |      |

| Porgram               | 4         | 555   | AA                     | 2AA   | 55   | 555        | A0   | PA        | PD    |           |      |       |      |

| Chip Erase            | 6         | 555   | AA                     | 2AA   | 55   | 555        | 80   | 555       | AA    | 2AA       | 55   | 555   | 10   |

#### TABLE4. MX26L3220 COMMAND DEFINITIONS

Legend:

X=Don't care

RA=Address of the memory location to be read.

RD=Data read from location RA during read operation.

PA=Address of the memory location to be programmed.

Addresses are latched on the falling edge of the  $\overline{WE}$  or  $\overline{CE}$  pulse.

PD=Data to be programmed at location PA. Data is latched on the rising edge of  $\overline{WE}$  or  $\overline{CE}$  pulse.

#### Notes:

- 1.See Table 1 for descriptions of bus operations.

- 2.All values are in hexadecimal.

- 3.Except when reading array or autoselect data, all bus cycles are write operation.

- 4.Address bits are don't care for unlock and command cycles, except when PA is required.

- 5.No unlock or command cycles required when device is in read mode.

- 6. The Reset command is required to return to the read mode when the device is in the autoselect mode or if Q5 goes high.

- 7. The fourth cycle of the autoselect command sequence is a read cycle.

- 8.Command is valid when device is ready to read array data or when device is in autoselect mode.

- 9. The data is 88h for factory locked and 48h for non-factory locked.

#### **READING ARRAY DATA**

The device is automatically set to reading array data after device power-up. No commands are required to retrieve data. The device is also ready to read array data after completing an Automatic Program or Automatic Erase algorithm.

The system must issue the reset command to re-enable the device for reading array data if Q5 goes high, or while in the autoselect mode. See the "Reset Command" section, next.

#### **RESET COMMAND**

Writing the reset command to the device resets the device to reading array data. Address bits are don't care for this command.

The reset command may be written between the sequence cycles in an erase command sequence before erasing begins. This resets the device to reading array data. Once erasure begins, however, the device ignores reset commands until the operation is complete.

The reset command may be written between the sequence cycles in a program command sequence before programming begins. This resets the device to reading array data. Once programming begins, however, the device ignores reset commands until the operation is complete.

The reset command may be written between the sequence cycles in an SILICON ID READ command sequence. Once in the SILICON ID READ mode, the reset command must be written to return to reading array data.

If Q5 goes high during a program or erase operation, writing the reset command returns the device to reading array data.

#### SILICON ID READ COMMAND SEQUENCE

The SILICON ID READ command sequence allows the host system to access the manufacturer and devices codes, and determine whether or not. Table 4 shows the address and data requirements. This method is an alternative to that shown in Table 1, which is intended for EPROM programmers and requires V<sub>ID</sub> on address bit A9.

The SILICON ID READ command sequence is initiated by writing two unlock cycles, followed by the SILICON ID READ command. The device then enters the SILICON ID READ mode, and the system may read at any address any number of times, without init iating another command sequence. A read cycle at address XX00h retrieves the manufacturer code. A read cycle at address XX01h returns the device code.

The system must write the reset command to exit the autoselect mode and return to reading array data.

#### WORD PROGRAM COMMAND SEQUENCE

The command sequence requires four bus cycles, and is initiated by writing two unlock write cycles, followed by the program set-up command. The program address and data are written next, which in turn initiate the Embedded Program algorithm. The system is not required to provide further controls or timings. The device automatically generates the program pulses and verifies the programmed cell margin. Table 4 shows the address and data requirements for the byte program command sequence.

When the Embedded Program algorithm is complete, the device then returns to reading array data and addresses are no longer latched. The system can determine the status of the program operation by using Q7, Q6. See "Write Operation Status" for information on these status bits.

Any commands written to the device during the Embedded Program Algorithm are ignored. Note that a hardware reset immediately terminates the programming operation. The Word Program command sequence should be reinitiated once the device has reset to reading array data, to ensure data integrity.

Programming is allowed in any sequence. A bit cannot be programmed from a "0" back to a "1". Cause the Data Polling algorithm to indicate the operation was successful. However, a succeeding read will show that the data is still "0". Only erase operations can convert a "0" to a "1".

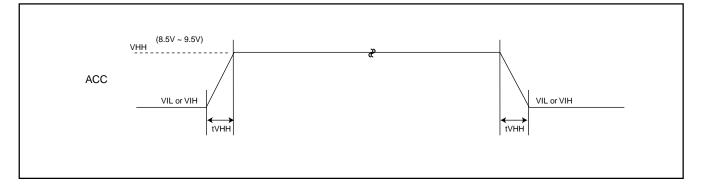

#### ACCELERATED PROGRAM OPERATIONS

The device offers accelerated program operations through the ACC pin. When the system asserts V<sub>HH</sub> on the ACC pin, the device automatically bypass the two "Unlock" write cycle. The device uses the higher voltage on the ACC pin to accelerate the operation. Note that the ACC pin must not be at V<sub>HH</sub> any operation other than accelerated programming, or device damage may result.

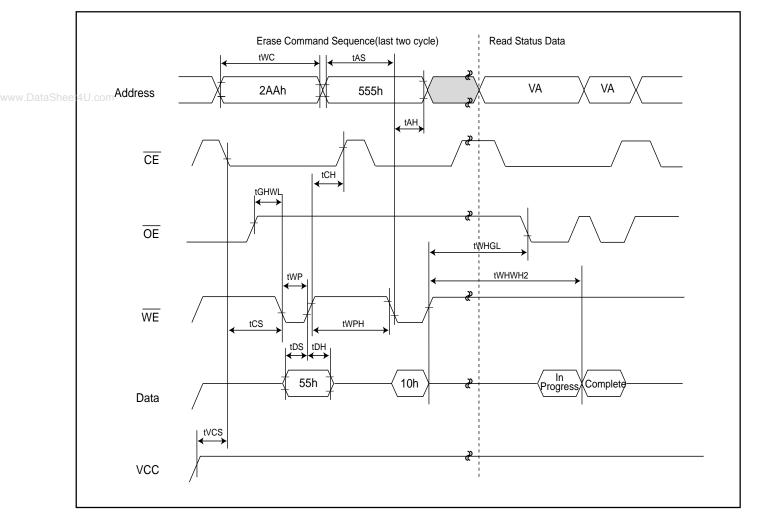

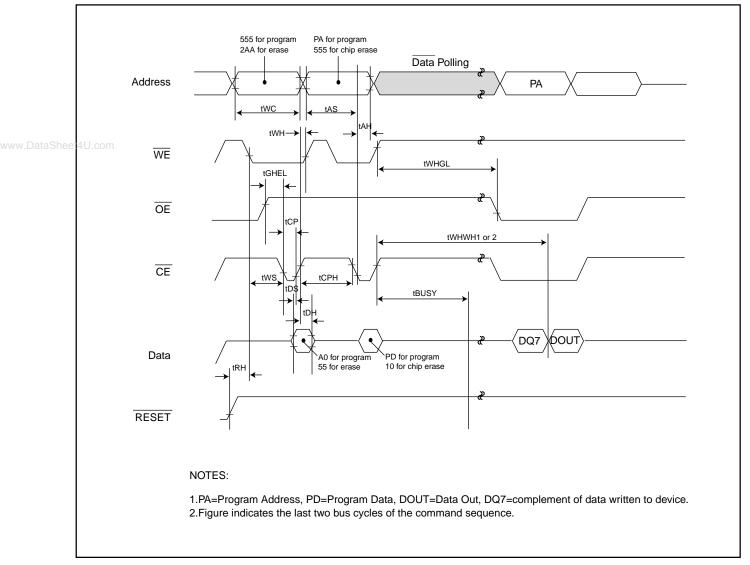

#### SETUP AUTOMATIC CHIP ERASE

Chip erase is a six-bus cycle operation. There are two "unlock" write cycles. These are followed by writing the "set-up" command 80H. Two more "unlock" write cycles are then followed by the chip erase command 10H.

The MX26L3220 contains a Silicon-ID-Read operation to supplement traditional PROM programming methodology. The operation is initiated by writing the read silicon ID command sequence into the command register. Following the command write, a read cycle with A6=VIL, A1=VIL, A0=VIL retrieves the manufacturer code of C2H. A read cycle with A6=VIL, A1=VIL, A0=VIH returns the device code of 22FDH for MX26L3220.

#### AUTOMATIC CHIP ERASE COMMAND

The device does not require the system to preprogram prior to erase. The Automatic Erase algorithm automatically preprograms and verifies the entire memory for an all zero data pattern prior to electrical erase. The system is not required to provide any controls or timings during these operations. Table 4 shows the address and data requirements for the chip erase command sequence.

Any commands written to the chip during the Automatic Erase algorithm are ignored. Note that a hardware reset during the chip erase operation immediately terminates the operation. The Chip Erase command sequence should be reinitiated once the device has returned to reading array data, to ensure data integrity.

The system can determine the status of the erase operation by using Q7, Q6. See "Write Operation Status" for information on these status bits. When the Automatic Erase algorithm is complete, the device returns to reading array data and addresses are no longer latched.

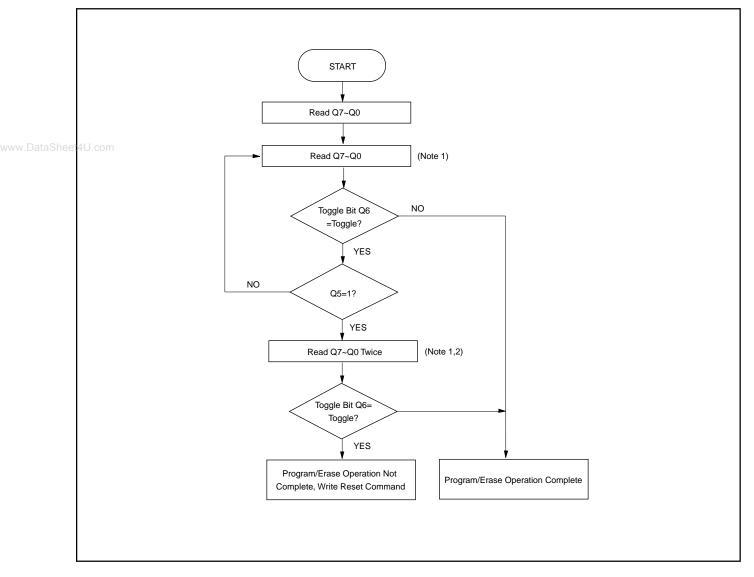

Figure 5 illustrates the algorithm for the erase operation.See the Erase/Program Operations tables in "AC Characteristics" for parameters, and to Figure 4 for timing diagrams.

#### TABLE 5. SILICON ID CODE

| Pins                      | A0  | <b>A</b> 1 | <b>A6</b> | Q15<br> | Q7 | Q6 | Q5 | Q4 | Q3 | Q2 | Q1 | Q0 | Code(Hex) |

|---------------------------|-----|------------|-----------|---------|----|----|----|----|----|----|----|----|-----------|

|                           |     |            |           | Q8      |    |    |    |    |    |    |    |    |           |

| Manufacture code          | VIL | VIL        | VIL       | 00H     | 1  | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 00C2H     |

| Device code for MX26L3220 | VIH | VIL        | VIL       | 22H     | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 22FDH     |

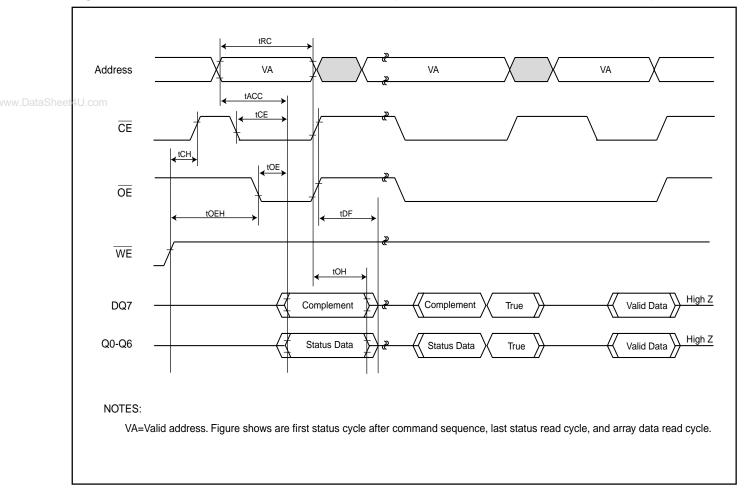

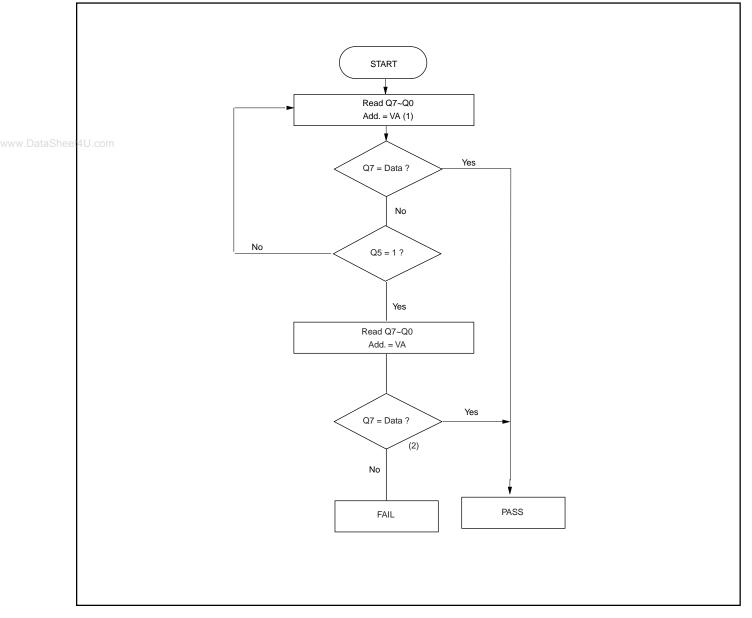

#### WRITE OPERSTION STATUS

The device provides several bits to determine the status of a write operation: Q5, Q6, Q7. The following sub-

sections describe the functions of these bits. Q7, and Q6 each offer a method for determining whether a program or erase operation is complete or in progress. These three bits are discussed first.

#### Table 6. Write Operation Status

|             | Status                                 | Q7         | Q6     | Q5 |

|-------------|----------------------------------------|------------|--------|----|

|             |                                        |            | Note1  |    |

| In Progress | Word Program in Auto Program Algorithm | <b>Q</b> 7 | Toggle | 0  |

|             | Auto Erase Algorithm                   | 0          | Toggle | 0  |

| Exceeded    | Word Program in Auto Program Algorithm | <u>Q7</u>  | Toggle | 1  |

| Time Limits | Auto Erase Algorithm                   | 0          | Toggle | 1  |

Notes:

1.Performing successive read operations from any address will cause Q6 to toggle.

#### Q7: Data Polling

The Data Polling bit, Q7, indicates to the host system whether an Automatic Algorithm is in progress or completed. Data Polling is valid after the rising edge of the final WE pulse in the program or erase command sequence.

During the Automatic Program algorithm, the device outputs on Q7 the complement of the datum programmed to Q7. This Q7 status also applies to programming during Er ase Suspend. When the Automatic Program algorithm is complete, the device outputs the datum programmed to Q7. The system must provide the program address to read valid status information on Q7.

During the Automatic Erase algorithm, Data Polling produces a "0" on Q7. When the Automatic Erase algorithm is complete. Data Polling produces a "1" on Q7. This is analogous to the complement/true datum out-put described for the Automatic Program algorithm: the erase function changes all the bits to "1" prior to this, the device outputs the "complement," or "0"."

#### Q6:Toggle BIT I

Toggle Bit I on Q6 indicates whether an Automatic Program or Erase algorithm is in progress or complete. Toggle Bit I may be read at any address, and is valid after the rising edge of the final WE or CE, whichever happens first pulse in the command sequence(prior to the program or erase operation).

During an Automatic Program or Erase algorithm operation, successive read cycles to any address cause Q6 to toggle. The system may use either  $\overline{OE}$  or  $\overline{CE}$  to control the read cycles. When the operation is complete, Q6 stops toggling.

#### Q5:Program/Erase Timing

Q5 will indicate if the program or erase time has exceeded the specified limits(internal pulse count). Under these conditions Q5 will produce a "1". This time-out condition indicates that the program or erase cycle was not successfully completed. Data Polling and Toggle Bit are the only operating functions of the device under this condition. If this time-out condition occurs during chip erase operation, it specifies that Device is bad and it may not be reused. Write the Reset command sequence to the device, and then execute program or erase command sequence. This allows the system to continue to use the other active sectors in the device.

If this time-out condition occurs during the chip erase operation, it specifies that the entire chip is bad.

If this time-out condition occurs during the word programming operation, the word is bad and maynot be reused, (other word are still functional and can be reused).

#### ABSOLUTE MAXIMUM RATINGS

| Storage Temperature |

|---------------------|

|---------------------|

| Plastic Packages65°C to +150°C               |

|----------------------------------------------|

| Ambient Temperature                          |

| with Power Applied65°C to +125°C             |

| Voltage with Respect to Ground               |

| VCC (Note 1)                                 |

| A9, $\overline{OE}$ , and                    |

| RESET (Note 2)0.5 V to +12.5 V               |

| All other pins (Note 1)0.5 V to VCC +0.5 V   |

| Output Short Circuit Current (Note 3) 200 mA |

#### Notes:

- Minimum DC voltage on input or I/O pins is -0.5 V. During voltage transitions, input or I/O pins may overshoot VSS to -2.0 V for periods of up to 20 ns. See Figure 6. Maximum DC voltage on input or I/O pins is VCC +0.5 V. During voltage transitions, input or I/O pins may overshoot to VCC +2.0 V for periods up to 20 ns. See Figure 7.

- 2. <u>Minimum DC input voltage on pins A9, OE</u>, and <u>RESET is -0.5 V. During voltage transitions</u>, A9, OE, and <u>RESET may overshoot VSS to -2.0 V for periods</u> of up to 20 ns. See Figure 6. Maximum DC input voltage on pin A9 is +12.5 V which may overshoot to 14.0 V for periods up to 20 ns.

- 3. No more than one output may be shorted to ground at a time. Duration of the short circuit should not be greater than one second.

Stresses above those listed under "Absolute Maximum Rat-ings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this data sheet is not implied. Exposure of the device to absolute maximum rating conditions for extended periods may affect device reliability.

#### **OPERATING RATINGS**

| Commercial (C) Devices                                                  |

|-------------------------------------------------------------------------|

| Ambient Temperature (T <sub>A</sub> )0 $^{\circ}$ C to +70 $^{\circ}$ C |

| Industrial (I) Devices                                                  |

| Ambient Temperature (T <sub>A</sub> )40℃ to +85℃                        |

| Vcc Supply Voltages                                                     |

| Vcc for full voltage range +2.7 V to 3.6 V                              |

Operating ranges define those limits between which the functionality of the device is guaranteed.

#### DC CHARACTERISTICS TA=0°C to 70°C, VCC=2.7V~3.6V

| Para-    |                             |                                                 |          | VI/O     | =2.7V | ~3.6V   | VI/O     |     |      |      |

|----------|-----------------------------|-------------------------------------------------|----------|----------|-------|---------|----------|-----|------|------|

| meter    | Description                 | Test Conditions                                 |          | Min      | Тур   | Max     | Min      | Тур | Max  | Unit |

| I LI     | Input Load Current (Note 1) | VIN = VSS to VCC                                | ,        |          |       | ±1.0    |          |     | ±1.0 | uA   |

|          |                             | VCC = VCC max                                   |          |          |       |         |          |     |      |      |

| I LIT    | A9 Input Load Current       | VCC=VCC max; As                                 |          |          | 35    |         |          | 35  | uA   |      |

| ILO      | Output Leakage Current      | VOUT = VSS to VCC ,                             |          |          |       | ±1.0    |          |     | ±1.0 | uA   |

| et4U.com |                             | VCC= VCC max                                    |          |          |       |         |          |     |      |      |

| ICC1     | VCC Active Read Current     | $\overline{CE}$ = VIL, $\overline{OE}$ = VIH    | 5 MHz    |          | 17    | 25      |          | 17  | 25   | mA   |

|          | (Notes1, 2)                 |                                                 | 1 MHz    |          | 4     | 7       |          | 4   | 7    | mA   |

| ICC2     | VCC Active Write Current    | $\overline{CE} = V IL$ , $\overline{OE} = V II$ |          | 26       | 30    |         | 26       | 30  | mA   |      |

|          | (Notes 1, 3, 4)             |                                                 |          |          |       |         |          |     |      |      |

| ICC3     | VCC Standby Current(CMOS)   | CE, RESET,                                      |          |          | 30    | 100     |          | 30  | 100  | uA   |

|          | (Note 1)                    | ACC=VCC ± 0.3V                                  |          |          |       |         |          |     |      |      |

| ICC4     | VCC Standby Current (TTL)   | CE=VIH                                          |          |          | 0.5   | 1       |          | 0.5 | 1    | mA   |

|          | (Note 1)                    |                                                 |          |          |       |         |          |     |      |      |

| ICC5     | VCC Reset Current (Note 1)  | $\overline{RESET} = V SS \pm 0.$                | .3 V,    |          | 0.2   | 5       |          | 0.2 | 5    | uA   |

|          |                             | ACC = VCC ± 0.3 \                               | /        |          |       |         |          |     |      |      |

| IACC     | ACC Accelerated Program     | CE=VIL, OE=VIH                                  | Acc pin  |          | 5     | 10      |          | 5   | 10   | mA   |

|          | Current, Word               |                                                 | Vcc pin  |          | 15    | 30      |          | 15  | 30   | mA   |

| VIL      | Input Low Voltage           |                                                 |          | -0.5     |       | 0.8     |          |     | 0.4  | V    |

| VIH      | Input High Voltage          |                                                 |          | 0.7xVcc  |       | Vcc+0.3 | VI/O-0.4 |     |      | V    |

| VHH      | Voltage for ACC             | VCC = 3.0 V ± 10%                               | ,<br>D   | 11.5     |       | 12.5    | 11.5     |     | 12.5 | V    |

|          | Program Acceleration        |                                                 |          |          |       |         |          |     |      |      |

| VID      | Voltage for Autoselect      | VCC = 3.0 V ± 10%                               | ,<br>D   | 11.5     |       | 12.5    | 11.5     |     | 12.5 | V    |

| VOL      | Output Low Voltage          | IOL= 4.0mA,VCC=                                 | VCC min  |          |       | 0.45    |          |     | 0.45 | V    |

| VOH1     | Output High Voltage         | IOH=-2.0mA,VCC=                                 | ⊧VCC min | 0.85VI/O |       |         | 0.85VI/O |     |      | V    |

| VOH2     |                             | IOH=-100uA,VCC=                                 | =VCC min | VI/O-0.4 |       |         | VI/O-0.4 |     |      | V    |

| VLKO     | Low V CC Lock-Out Voltage   |                                                 |          | 2.3      |       | 2.5     | 2.3      |     | 2.5  | V    |

|          | (Note 4)                    |                                                 |          |          |       |         |          |     |      |      |

Notes:

1. Maximum ICC specifications are tested with VCC = VCC max.

2. The ICC current listed is typically is less than 2 mA/MHz, with  $\overline{OE}$  at V IH. Typical specifications are for VCC = 3.0 V.

3. ICC active while Embedded Erase or Embedded Program is in progress.

4. Not 100% tested.

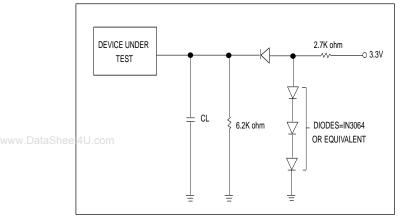

#### SWITCHING TEST CIRCUITS

**KEY TO SWITCHING WAVEFORMS**

#### **TEST SPECIFICATIONS**

| Test Condition              | 90      | Unit    |    |

|-----------------------------|---------|---------|----|

| Output Load                 | 1 T     | FL gate |    |

| Output Load Capacitance, CL | 30      | 100     | pF |

| (including jig capacitance) |         |         |    |

| Input Rise and Fall Times   | 5       |         | ns |

| Input Pulse Levels          | 0.0-3.0 |         | V  |

| Input timing measurement    | 1.5     |         | V  |

| reference levels            |         |         |    |

| Output timing measurement   | 1.5     |         | V  |

| reference levels            |         |         |    |

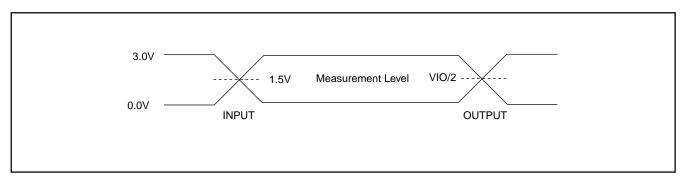

| WAVEFROM | INPUTS                           | OUTPUTS                                     |

|----------|----------------------------------|---------------------------------------------|

|          | Steady                           |                                             |

|          | Changing from H to               | L                                           |

|          | Changing from L to H             | I                                           |

| XXXXX    | Don't Care, Any Change Permitted | Changing, State Unknown                     |

|          | Does Not Apply                   | Center Line is High Impedance State(High Z) |

#### SWITCHING TEST WAVEFORMS

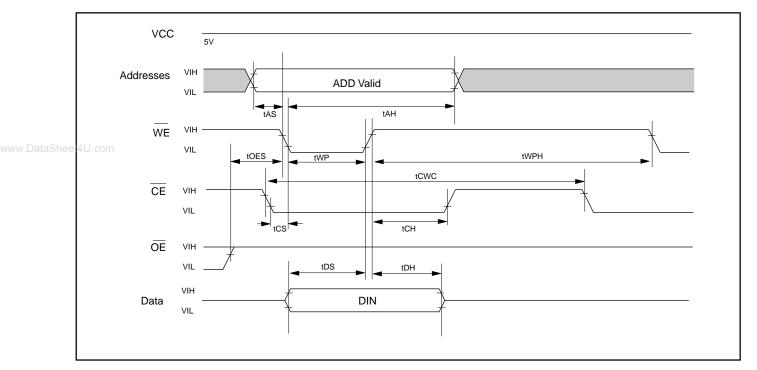

#### AC CHARACTERISTICS TA=0°C to 70°C, VCC=2.7V~3.6V

| Symbol           | DESCRIPTION                                                   |              | CONDIT | ION | 90 | 120 | Unit |

|------------------|---------------------------------------------------------------|--------------|--------|-----|----|-----|------|

| tACC             | Address to output delay                                       |              | CE=VIL | MAX | 90 | 120 | ns   |

|                  | <del>OE</del> =VIL                                            |              |        |     |    |     |      |

| tCE              | Chip enable to output delay                                   |              | OE=VIL | MAX | 90 | 120 | ns   |

| tOE              | Output enable to output delay                                 |              |        | MAX | 34 | 44  | ns   |

| tDF              | OE High to output float(Note1)                                |              |        | MAX | 25 | 35  | ns   |

| e:4U. <b>tOH</b> | Output hold time of from the rising e                         | edge of      |        | MIN | 0  | 0   | ns   |

|                  | Address, $\overline{CE}$ , or $\overline{OE}$ , whichever hap | opens first  |        |     |    |     |      |

| tRC              | Read cycle time (Note 1)                                      |              |        | MIN | 90 | 120 | ns   |

| tWC              | Write cycle time (Note 1)                                     |              |        | MIN | 90 | 120 | ns   |

| tCWC             | Command write cycle time(Note 1)                              |              |        | MIN | 90 | 120 | ns   |

| tAS              | Address setup time                                            |              |        | MIN | 0  | 0   | ns   |

| tAH              | Address hold time                                             |              |        | MIN | 45 | 50  | ns   |

| tDS              | Data setup time                                               |              |        | MIN | 45 | 50  | ns   |

| tDH              | Data hold time                                                |              |        | MIN | 0  | 0   | ns   |

| tVCS             | Vcc setup time(Note 1)                                        |              |        | MIN | 50 | 50  | us   |

| tCS              | Chip enable setup time                                        |              |        | MIN | 0  | 0   | ns   |

| tCH              | Chip enable hold time                                         |              |        | MIN | 0  | 0   | ns   |

| tOES             | Output enable setup time (Note 1)                             |              |        | MIN | 0  | 0   | ns   |

| tOEH             | Output enable hold time (Note 1)                              | Read         |        | MIN | 0  | 0   | ns   |

|                  |                                                               | Toggle &     |        | MIN | 10 | 10  | ns   |

|                  |                                                               | Data Polling |        |     |    |     |      |

| tWES             | WE setup time                                                 |              |        | MIN | 0  | 0   | ns   |

| tWEH             | WE hold time                                                  |              |        | MIN | 0  | 0   | ns   |

| tCEP             | CE pulse width                                                |              |        | MIN | 45 | 50  | ns   |

| tCEPH            | CE pulse width high                                           |              |        | MIN | 30 | 30  | ns   |

| tWP              | WE pulse width                                                |              |        | MIN | 35 | 50  | ns   |

| tWPH             | WE pulse width high                                           |              |        | MIN | 30 | 30  | ns   |

| tOLZ             | Output enable to output low Z                                 |              |        | MAX | 30 | 40  | ns   |

| tWHGL            | $\overline{WE}$ high to $\overline{OE}$ going low             |              |        | MIN | 30 | 30  | ns   |

Note: 1.Not 100% Tested

2.tr = tf = 5ns

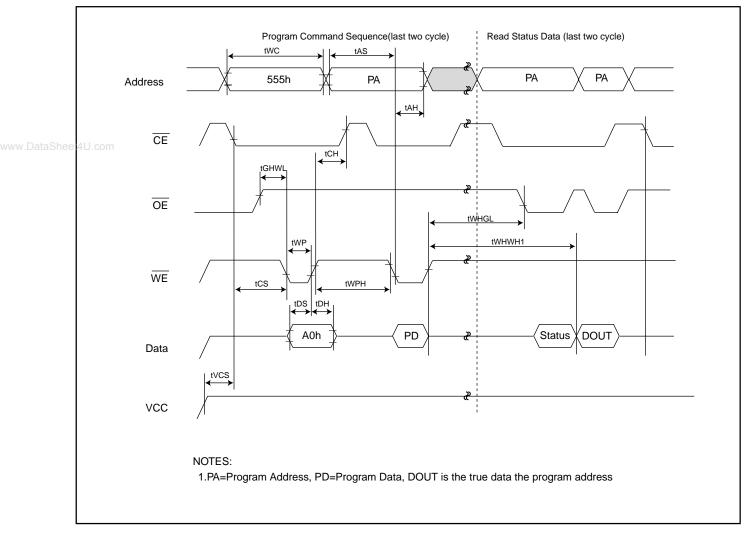

#### Fig 1. COMMAND WRITE OPERATION

#### **READ/RESET OPERATION**

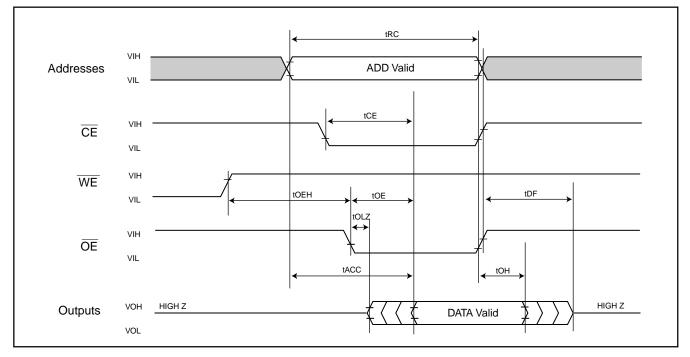

#### Fig 2. READ TIMING WAVEFORMS

#### AC CHARACTERISTICS

| Parameter | Description                                        | Test Setup | Setup All Speed Optio |    |

|-----------|----------------------------------------------------|------------|-----------------------|----|

| tREADY    | RESET PIN Low (NOT During Automatic                | MAX        | 500                   | ns |

|           | Algorithms) to Read or Write (See Note)            |            |                       |    |

| tRP1      | RESET Pulse Width (During Automatic Algorithms)    | MIN        | 10                    | us |

| tRP2      | RESET Pulse Width (NOT During Automatic Algorithms | s) MIN     | 500                   | ns |

| tRH       | RESET High Time Before Read(See Note)              | MIN        | 50                    | ns |

Note:Not 100% tested

#### Fig 3. RESET TIMING WAVFORM

#### **ERASE/PROGRAM OPERATION**

#### Fig 4. AUTOMATIC CHIP ERASE TIMING WAVEFORM

#### Fig 5. AUTOMATIC CHIP ERASE ALGORITHM FLOWCHART

#### Fig 6. AUTOMATIC PROGRAM TIMING WAVEFORMS

Fig 7. Accelerated Program Timing Diagram

#### Fig 9. AUTOMATIC PROGRAMMING ALGORITHM FLOWCHART

#### Fig 10. SECURED SILICON SECTOR PROTECTED ALOGORITHMS FLOWCHART

#### Fig 11. SILICON ID READ TIMING WAVEFORM

#### WRITE OPERATION STATUS

#### Fig 12. DATA POLLING TIMING WAVEFORMS (DURING AUTOMATIC ALGORITHMS)

#### Fig 13. Data Polling Algorithm

Notes:

1.VA=valid address for programming.

2.Q7 should be rechecked even Q5="1"because Q7 may change simultaneously with Q5.

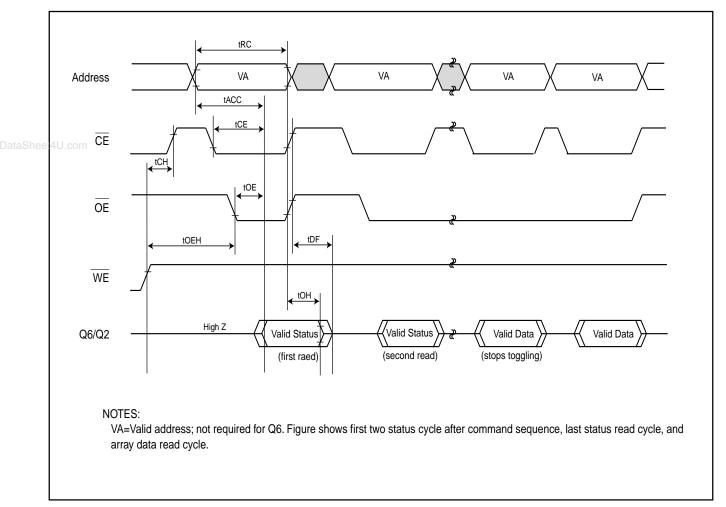

#### Fig 14. TOGGLE BIT TIMING WAVEFORMS (DURING AUTOMATIC ALOGRITHMS)

#### Fig 15. Toggle Bit Algorithm

Note:

1.Read toggle bit twice to determine whether or not it is toggling.

2.Recheck toggle bit because it may stop toggling as Q5 changes to "1".

#### ERASE AND PROGRAMMING PERFORMANCE(1)

|                               |      | LIMITS  |      |        |  |

|-------------------------------|------|---------|------|--------|--|

| PARAMETER                     | MIN. | TYP.(2) | MAX. | UNITS  |  |

| Chip Erase Time               |      | 90      | 180  | sec    |  |

| Word Programming Time         |      | 30      | 350  | us     |  |

| Chip Programming Time         |      | 70      | 125  | sec    |  |

| Accelerated Word Program Time |      | 7       | 210  | us     |  |

| Erase/Program Cycles          | 100  |         |      | Cycles |  |

Note: 1.Not 100% Tested, Excludes external system level over head. 2.Typical values measured at 25°C,3.3V. Additionally programming typicals assume checkerboard pattern.

#### LATCHUP CHARACTERISTICS

|                                                                               | MIN.   | MAX.       |

|-------------------------------------------------------------------------------|--------|------------|

| Input Voltage with respect to GND on all pins except I/O pins                 | -1.0V  | 13.5V      |

| Input Voltage with respect to GND on all I/O pins                             | -1.0V  | Vcc + 1.0V |

| Current                                                                       | -100mA | +100mA     |

| Includes all pins except Vcc. Test conditions: Vcc = 5.0V, one pin at a time. |        |            |

#### CAPACITANCE TA=0℃ to 70℃, VCC=2.7V~3.6V

| Parameter Symbol | Parameter Description   | Test Set | TYP | MAX | UNIT |

|------------------|-------------------------|----------|-----|-----|------|

| CIN              | Input Capacitance       | VIN=0    | 6   | 7.5 | pF   |

| COUT             | Output Capacitance      | VOUT=0   | 8.5 | 12  | pF   |

| CIN2             | Control Pin Capacitance | VIN=0    | 7.5 | 9   | pF   |

#### Notes:

1. Sampled, not 100% tested.

2. Test conditions TA=25 °C, f=1.0MHz

#### DATA RETENTION

| Parameter                           | Test Conditions | Min | Unit  |

|-------------------------------------|-----------------|-----|-------|

| Minimum Pattern Data Retention Time | 150             | 10  | Years |

|                                     | 125             | 20  | Years |

#### **ORDERING INFORMATION**

#### PLASTIC PACKAGE

| PARTNO.         | ACCESS TIME | Temperature | Package type  | Ball Pitch |

|-----------------|-------------|-------------|---------------|------------|

|                 | (ns)        | Range       |               |            |

| MX26L3220MC-90  | 90          | Commerical  | 44 pin SOP    | -          |

| MX26L3220MC-12  | 120         | Commerical  | 44 pin SOP    | -          |

| MX26L3220TC-90  | 90          | Commerical  | 48 pin TSOP   | -          |

|                 |             |             | (Normal Type) |            |

| MX26L3220TC-12  | 120         | Commerical  | 48 pin TSOP   | -          |

|                 |             |             | (Normal Type) |            |

| MX26L3220XAC-90 | 90          | Commerical  | 48 ball CSP   | 0.75 mm    |

| MX26L3220XAC-12 | 120         | Commerical  | 48 ball CSP   | 0.75 mm    |

| MX26L3220XBC-90 | 90          | Commerical  | 48 ball CSP   | 0.8 mm     |

| MX26L3220XBC-12 | 120         | Commerical  | 48 ball CSP   | 0.8 mm     |

| MX26L3220MI-90  | 90          | Industrial  | 44 pin SOP    | -          |

| MX26L3220MI-12  | 120         | Industrial  | 44 pin SOP    | -          |

| MX26L3220TI-90  | 90          | Industrial  | 48 pin TSOP   | -          |

|                 |             |             | (Normal Type) |            |

| MX26L3220TI-12  | 120         | Industrial  | 48 pin TSOP   | -          |

|                 |             |             | (Normal Type) |            |

| MX26L3220XAI-90 | 90          | Industrial  | 48 ball CSP   | 0.75 mm    |

| MX26L3220XAI-12 | 120         | Industrial  | 48 ball CSP   | 0.75 mm    |

| MX26L3220XBI-90 | 90          | Industrial  | 48 ball CSP   | 0.8 mm     |

| MX26L3220XBI-12 | 120         | Industrial  | 48 ball CSP   | 0.8 mm     |

#### PACKAGE INFORMATION

#### 48-Ball CSP(Ball Pitch=0.75mm)

MX26L3220

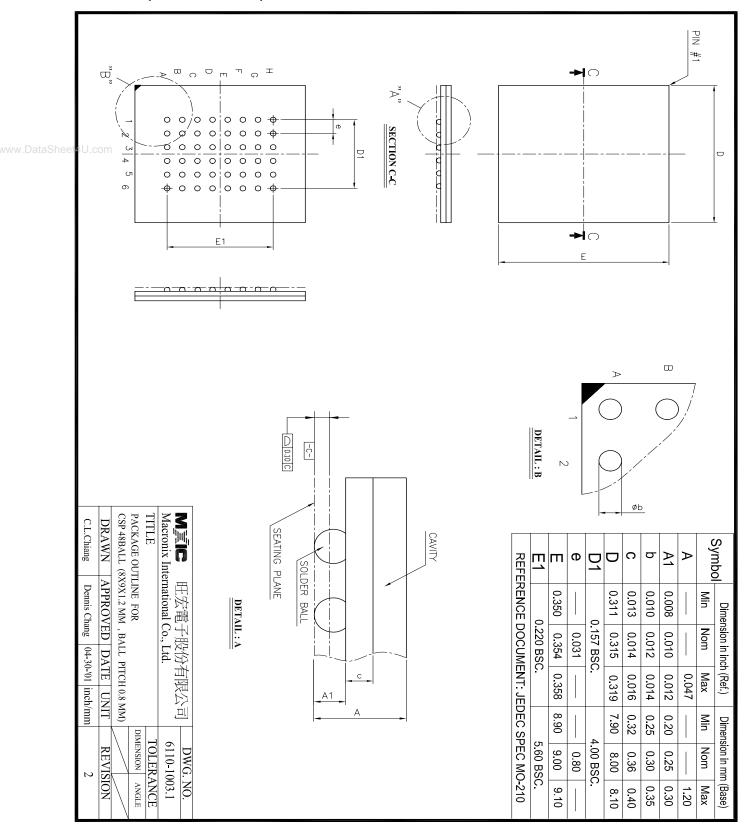

#### 48-Ball CSP(Ball Pitch=0.8mm)

Reww.DataSheetdU.com

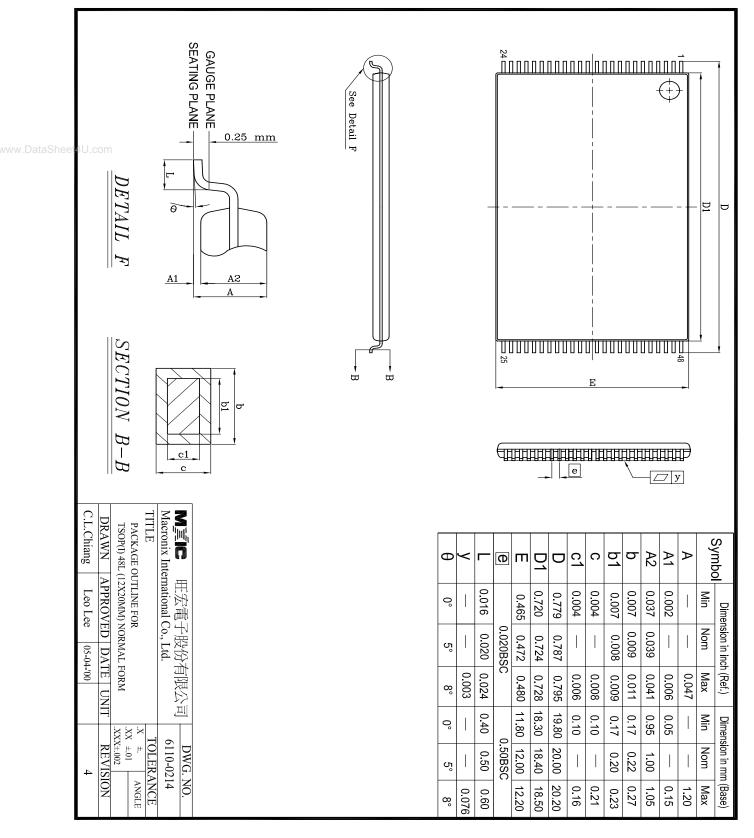

#### **48-PIN PLASTIC TSOP**

Reww.DataSheetdU.com

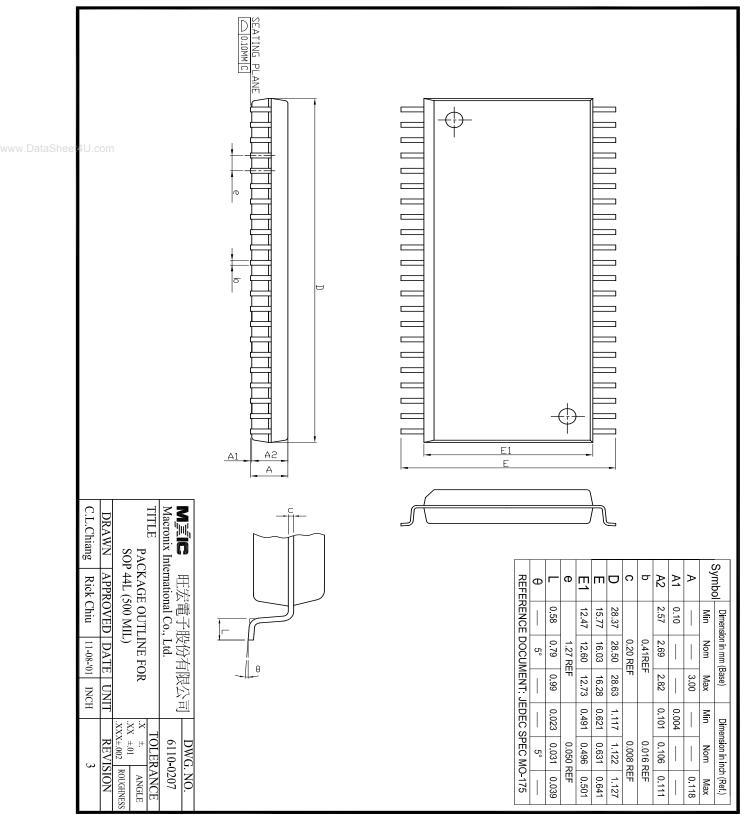

#### 44-Pin SOP

#### **REVISION HISTORY**

|         | <b>Revision No.</b> | Description                                                                        | Page    | Date        |

|---------|---------------------|------------------------------------------------------------------------------------|---------|-------------|

|         | 0.1                 | 1.To added the VI/O voltage range and performance                                  | P1,7    | JUL/23/2001 |

|         |                     | 2.To modify Autoselect code table                                                  | P5      |             |

|         |                     | 3.To added Deep power-down mode                                                    | P9,10   |             |

|         |                     | 4.To added chip erase algorithm flowchart                                          | P23     |             |

|         |                     | 5.To added secured silicon sector protect Algorithm flowchart                      | P24     |             |

|         |                     | 6.To modify the 14-pin of 48 TSOP package from NC to VCC                           | P2      |             |

|         | 0.2                 | 1.To added 44 SOP package                                                          | P1,2,35 | JUL/31/2001 |

| aSheet4 |                     | 2.To modify the VI/O range from 1.8V~5V to 1.8V~3.6V                               | P1      |             |

|         |                     | 3.Cancel th regulated voltage range                                                | 14      |             |

|         |                     | 4.Modify DC Characteristics table for VIL/VIH voltage when VI/O range is 1.8V~2.6V | P15     |             |

|         | 0.3                 | 1.To Added 0.8mm ball pitch 48 ball CSP package                                    | P2,34   | SEP/26/2001 |

|         |                     | 2.To modify VI/O voltage range from 1.8V to 1.65V                                  | P1,8,15 |             |

|         |                     | 3.To modify ICC4/tCS/tCH/tOLZ/tWHGL spec                                           | P15,17  |             |

|         |                     | 4.To modify VCC standby current from 50uA to 30uA                                  | P1,16   |             |

|         |                     | 5.Cancel the deep power-down mode                                                  | P11,16  |             |

|         |                     | 6.To modify the programming time                                                   | P1,31   |             |

|         | 0.4                 | 1.To modify chip erase time from 45ns(typ.) to 90ns                                | P1,31   | NOV/27/2001 |

|         |                     | 2.To modify the CSP size from 8mm x 9mm to 9mm x 8mm                               | P2      |             |

|         |                     | 3.To modify the ICC1 @5MHz:9/16mA>17/25mA<br>ICC1 @1MHz:2/4mA>4/7mA                | P15     |             |

|         |                     | 4. To correct the VHH to 12V±0.5V                                                  | P15     |             |

|         | 0.5                 | 1.To modify the content error                                                      | P1,7,11 | JAN/29/2002 |

ww.DataSheet4U.com

### MACRONIX INTERNATIONAL CO., LTD.

HEADQUARTERS: TEL:+886-3-578-6688 FAX:+886-3-563-2888

EUROPE OFFICE: TEL:+32-2-456-8020 FAX:+32-2-456-8021

JAPAN OFFICE: TEL:+81-44-246-9100 FAX:+81-44-246-9105

SINGAPORE OFFICE: TEL:+65-348-8385 FAX:+65-348-8096

TAIPEI OFFICE: TEL:+886-2-2509-3300 FAX:+886-2-2509-2200

MACRONIX AMERICA, INC. TEL:+1-408-453-8088 FAX:+1-408-453-8488

CHICAGO OFFICE: TEL:+1-847-963-1900 FAX:+1-847-963-1909

http://www.macronix.com