# ADVANCED INFORMATION MX26L6419

# 64M [x16] SINGLE 3V PAGE MODE MTP MEMORY

#### **FEATURES**

- 3.0V to 3.6V operation voltage

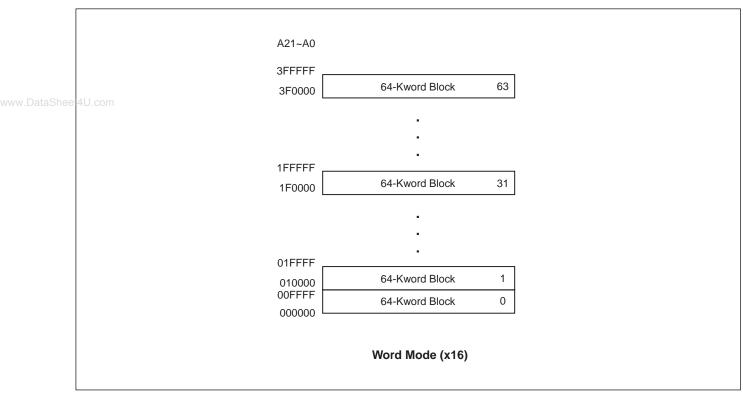

- Block Structure

- 64 x 64Kword Erase Blocks

- Fast random / page mode access time

- 100/25 ns Read Access Time (page depth:8-word)

- 128-bit Protection Register

- 64-bit Unique Device Identifier

- 64-bit User Programmable OTP Cells

- 16-Word Write Buffer

- 14 us/word Effective Programming Time

- Enhanced Data Protection Features Absolute Protection with VPEN = GND

- Flexible Block Locking

- Block Erase/Program Lockout during Power Transitions

#### **Performance**

- · Low power dissipation

- typical 15mA active current for page mode read

- 80uA/(max.) standby current

- High Performance

- Block erase time: 2s typ.

- Word programming time: 210us typ.

- Block programming time: 0.8s typ. (using Write to

- **Buffer Command)**

- Program/Erase Endurance cycles: 100 cycles

#### **Software Feature**

- Support Common Flash Interface (CFI)

- MTP device parameters stored on the device and provide the host system to access.

#### **Hardware Feature**

- ACC pin

- 12V VPP for fast program/erase mode.

- VPEN pin

- For Erase /Program/ Block Lock enable.

- VCCQ Pin

- The output buffer power supply, control the device 's output voltage.

- RESET pin

- Hardware reset

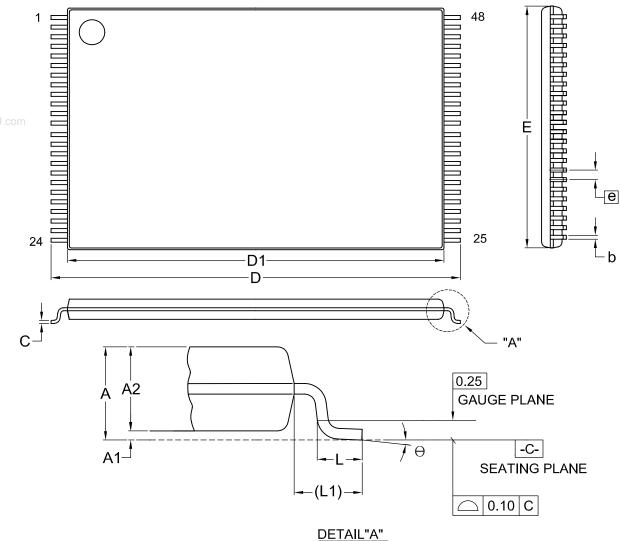

## **Packaging**

- 48-Lead TSOP

## **Technology**

- Two bits per cell Nbit (0.25u) MTP Technology

#### **GENERAL DESCRIPTION**

The MXIC's MX26L6419 series MTP use the most advance 2 bits/cell Nbit technology, double the storage capacity of memory cell. The device provide the high density MTP memory solution with reliable performance and most cost-effective.

The device organized as by 16 bits of output bus. The device is packaged in 48-Lead TSOP. It is designed to be reprogrammed and erased in system or in standard EPROM programmers.

The device offers fast access time and allowing operation of high-speed microprocessors without wait states. The device augment EPROM functionality with in-circuit

electrical erasure and programming. The device uses a command register to manage this functionality.

The MXIC's Nbit technology reliably stores memory contents even after the specific erase and program cycles. The MXIC cell is designed to optimize the erase and program mechanisms by utilizing the dielectric's character to trap or release charges from ONO layer.

The device uses a 3.0V to 3.6V VCC supply to perform the High Reliability Erase and auto Program/Erase algorithms.

The highest degree of latch-up protection is achieved with MXIC's proprietary non-epi process. Latch-up protection is proved for stresses up to 100 milliamps on address and data pin from -1V to VCC + 1V.

## **PIN CONFIGURATION**

# 48-TSOP (12mm x 20mm)

A15 🗆 □ A16 A14 □ 2 47 \_\_ vccq A13 🖂 3 46 □ GND A12 🗀 45 \_\_\_\_ Q15 A11 🖂 44 \_\_\_\_ Q7 A10 🗀 43 \_\_\_ Q14 \_\_\_\_ Q6 Α9 41 □ Q13 A8 □ 8 40 A21 □ \_\_\_\_ Q5 39 38 A20 | | | 10 \_\_\_\_ Q12 \_\_\_ Q4 RESET  $\square$ 37 36 ─ vcc 12 MX26L6419 (x16 only) ACC □ \_\_\_ Q11 Normal Type VPEN \_\_ □ Q3 Q10 Q2 A19 🗀 34 15 A18 🗀 33 16 32 31 Q9 Q1 17 18 Q8 Q0 30 19 20 29 □ Œ GND CE 22 27 26 23 25 □ A0

#### PIN DESCRIPTION

| SYMBOL | PIN NAME                       |

|--------|--------------------------------|

| A0~A21 | Address Input                  |

| Q0~Q15 | Data Inputs/Outputs            |

| CE     | Chip Enable Input              |

| WE     | Write Enable Input             |

| ŌĒ     | Output Enable Input            |

| RESET  | Reset Power Down mode          |

| VPEN   | ERASE/PROGRAM/BLOCK Lock       |

|        | Enable                         |

| ACC    | Program/erase acceleration pin |

| VCCQ   | Output Buffer Power Supply     |

| VCC    | Device Power Supply            |

| GND    | Device Ground                  |

Note: ACC pin and VPEN pin are not allowed to be operation at the same time.

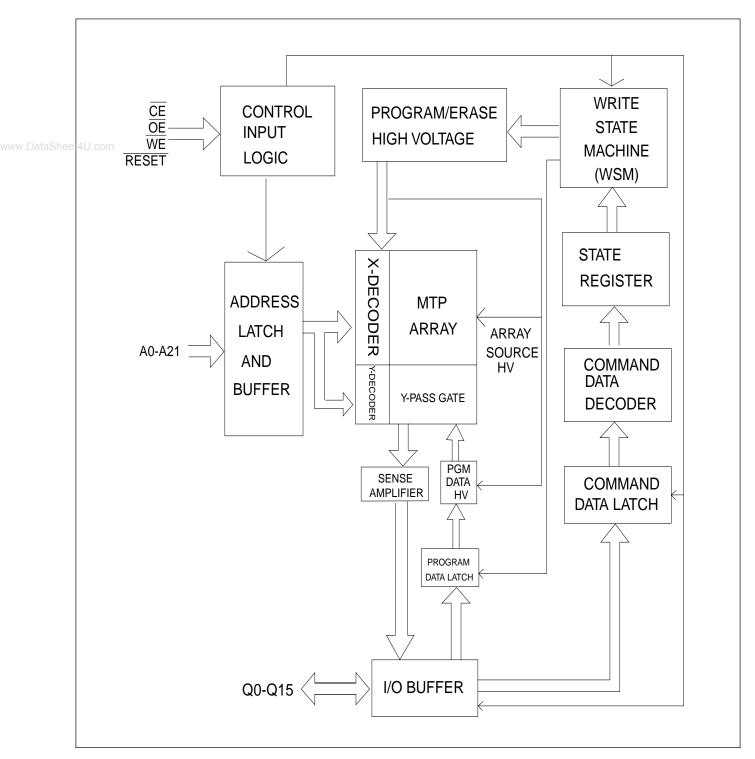

## **BLOCK DIAGRAM**

# Figure 1. Block Architecture

MTP memory reads erases and writes in-system via the local CPU. All bus cycles to or from the MTP memory conform to standard microprocessor bus cycles.

# **Table 1. Bus Operations**

|       | Command         | Read     | Output  | Standby  | RESET  | Read ID  | Read    | Read      | Read         | Write                                 |

|-------|-----------------|----------|---------|----------|--------|----------|---------|-----------|--------------|---------------------------------------|

|       | Sequence        | Array    | Disable |          | Mode/  |          | Query   | Status    | Status       |                                       |

|       |                 |          |         |          | Power  |          |         | (WSM off) | (WSM on)     |                                       |

|       |                 |          |         |          | Down   |          |         |           |              |                                       |

|       |                 |          |         |          | Mode   |          |         |           |              |                                       |

| 201   | d-l-rem         |          |         |          |        |          |         |           |              |                                       |

| , ( ) | Notes           | 3,4      |         |          |        |          |         |           |              | 8,9                                   |

|       |                 |          |         |          |        |          |         |           |              |                                       |

|       | RESET           | VIH      | VIH     | VIH      | VIL    | VIH      | VIH     | VIH       | VIH          | VIH                                   |

|       |                 |          |         |          |        |          |         |           |              |                                       |

|       | CE              | Enabled  | Enabled | Disabled | X      | Enabled  | Enabled | Enabled   | Enabled      | Enabled                               |

|       | <del></del> (1) |          |         |          | .,     |          |         |           |              |                                       |

|       | OE (1)          | VIL      | VIH     | X        | Χ      | VIL      | VIL     | VIL       | VIL          | VIH                                   |

|       | 10/E (4)        | \        | \ /II I |          |        | \ /!! !  | \ //L   | \ /II I   | \ //L        | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

|       | WE (1)          | VIH      | VIH     | X        | X      | VIH      | VIH     | VIH       | VIH          | VIL                                   |

|       | A ddroop        | Χ        | X       | X        | X      | See      | See     | X         | Χ            | X                                     |

|       | Address         | ^        | ^       | ^        | ^      |          |         | ^         | ^            | ^                                     |

| -     | VDEN            | V        | V       | V        | V      | Figure 2 | Table 5 | V         | V            | \/DENIII                              |

|       | VPEN            | Χ        | X       | X        | X      | X        | X       | X         | X            | VPENH                                 |

|       | O (2)           | Data out | High 7  | High Z   | High Z | Note 6   | Note 7  | Data out  | Q7=Data out  | Data in                               |

|       | Q (2)           | Data out | nigii Z | nign Z   | ⊓ign ∠ | Note 6   | Note /  | Dala out  | · ·          | Data in                               |

|       |                 |          |         |          |        |          |         |           | Q15-8=High Z |                                       |

|       |                 |          |         |          |        |          |         |           | Q6-0=High Z  |                                       |

## NOTES:

- 1.  $\overline{OE}$  and  $\overline{WE}$  should never be enabled simultaneously.

- 2. Q refers to Q0~Q15.

- 3. Refer to DC Characteristics. When VPEN ≤ VPENLK, memory contents can be read, but not altered.

- 4. X can be VIL or VIH for control and address pins, and VPENLK or VPENH for VPEN . See DC Characteristics for VPENLK and VPENH voltages.

- 5. High Z will be VOH with an external pull-up resistor.

- 6. See Section, "Read Identifier Codes" for read identifier code data.

- 7. See Section, "Read Query Mode Command" for read query data.

- 8. Command writes involving block erase, program, or lock-bit configuration are reliably executed when VPEN= VPENH and VCC is within specification.

- 9. Refer to Table 2 on page 7 for valid DIN during a write operation.

#### **FUNCTION**

The device includes on-chip program/erase control circuitry. The Write State Machine (WSM) controls block erase and word/page program operations. Operational modes are selected by the commands written to the Command User Interface (CUI). The Status Register indicates the status of the WSM and when the WSM successfully completes the desired program or block erase operation.

leet40.com

A Powerdown mode is enabled when the RESET pin is at GND minimizing power consumption.

#### **READ**

The device has three read modes, which accesses to the memory array, the Device Identifier or the Status Register independent of the VPEN voltage. The appropriate read command are required to be written to the CUI. Upon initial device powerup or after exit from powerdown, the device automatically resets to read array mode. In the read array mode, low level input to  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$ , high level input to  $\overline{\text{WE}}$  and  $\overline{\text{RESET}}$  or low level input to  $\overline{\text{RESET}}$ , and address signals to the address inputs (A21-A0) output the data of the addressed location to the data input/output (Q15~Q0).

When reading information in read array mode, the device defaults to asynchronous page mode. In this state, data is internally read and stored in a high-speed page buffer. A2:0 addresses data in the page buffer. The page size is 8 words. Asynchronous word mode is supported with no additional commands required.

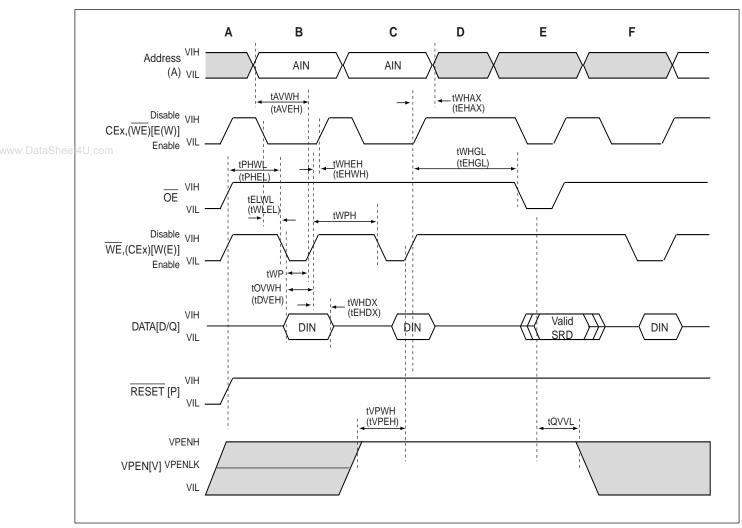

#### WRITE

Writes to the CUI enables reading of memory array data, device identifiers and reading and clearing of the Status Register and when VPEN=VPENH block erasure program and lock-bit configuration. The CUI is written when the device is enable,  $\overline{\text{WE}}$  is active and  $\overline{\text{OE}}$  is at high level. Address and data are latched on the earlier rising edge of  $\overline{\text{WE}}$  and  $\overline{\text{CE}}$ . Standard micro-processor write timings are used.

#### **OUTPUT DISABLE**

When  $\overline{OE}$  is at VIH, output from the devices is disabled. Data input/output are in a high-impedance(High-Z) state.

#### **STANDBY**

When  $\overline{\text{CE}}$  disable the device (see table1) and place it in standby mode. The power consumption of this device is reduced. Data input/output are in a high-impedance(High-Z) state. If the memory is deselected during block erase, program or lock-bit configuration, the internal control circuits remain active and the device consume normal active power until the operation completes.

#### **POWER-DOWN**

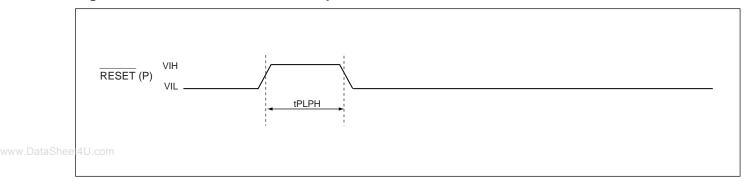

When RESET pin is at VIL, the device is in the power-down mode and its power consumption is substantially low around 25uA. During read modes, the memory is deselected and the data input/output are in a high-impedance(High-Z) state. To return from power down mode requires RESET pin at VIH. After return from powerdown, the CUI is reset to Read Array , and the Status Register is set to value 80H.

During block erase program or lock-bit configuration modes, RESET pin at VIL will abort either operation. Memory array data of the block being altered become invalid.

Time tPHWL is required after RESET goes to logic-high (VIH) before another command can be written.

#### **READ QUERY**

The read query operation outputs block status information, CFI (Common Flash Interface) ID string, system interface information, device geometry information and MXIC extended query information.

## **COMMAND DEFINITIONS**

Device operations are selected by writing specific address and data sequences into the CUI. Table 3 defines the valid register command sequences.

When VPEN\_VPENLK only read operations from the status register, query, indentifier code or blocks are enabled. When VPEN=VPENH enables block erase program and lock-bit configuration operations.

**Table 2. Command Definitions**

| Command                 |              | Read  | Read       | Read          | Read     | Clear    | Write to | Word    | Sector |

|-------------------------|--------------|-------|------------|---------------|----------|----------|----------|---------|--------|

| Sequence                |              | Array | ID         | Query         | Status   | Status   | Buffer   | Program | Erase  |

|                         |              |       |            |               | Register | Register |          |         |        |

| Notes                   |              |       | 5          |               | 6        |          | 7,8,9    | 10,11   | 9,10   |

|                         |              |       |            |               |          |          |          |         |        |

| Bus Write Cyc           | cles Req'd   | 1     | <u>≥</u> 2 | <u>&gt;</u> 2 | 2        | 1        | > 2      | 2       | 2      |

| First Bus               | Operation(2) | Write | Write      | Write         | Write    | Write    | Write    | Write   | Write  |

| Write Cycles            | Address(3)   | Χ     | X          | X             | Χ        | Χ        | ВА       | Χ       | ВА     |

|                         | Data(4,5)    | FFH   | 90H        | 98H           | 70H      | 50H      | E8H      | 40H/10H | 20H    |

| Second Bus Operation(2) |              |       | Read       | Read          | Read     |          | Write    | Write   | Write  |

| Read Query              | Address(3)   |       | IA         | QA            | Х        |          | ВА       | PA      | ВА     |

|                         | Data(4,5)    |       | ID         | QD            | SRD      |          | N        | PD      | D0H    |

| Command<br>Sequence |              | Configur-<br>ation | Set Sector<br>Lock-Bit | Clear<br>Sector | Protection<br>Program<br>Lock-Bit |

|---------------------|--------------|--------------------|------------------------|-----------------|-----------------------------------|

| Notes               |              |                    |                        | 12              |                                   |

| Bus Write Cy        | cles Req'd   | 2                  | 2                      | 2               | 2                                 |

| First Bus           | Operation(2) | Write              | Write                  | Write           | Write                             |

| Write Cycle         | Address(3)   | X                  | Х                      | Χ               | Х                                 |

|                     | Data(4,5)    | B8H                | 60H                    | 60H             | C0H                               |

| Second Bus          | Operation(2) | Write              | Write                  | Write           | Write                             |

| Write Cycle         | Address(3)   | Х                  | BA                     | X               | PA                                |

|                     | Data(4,5)    | CC                 | 01H                    | D0H             | PD                                |

#### NOTES:

- 1. Bus operations are defined in Table 1.

- 2. X = Any valid address within the device.

- BA = Address within the block.

- IA = Identifier Code Address: see Figure 2 and Table 13.

- QA = Query database Address.

- PA = Address of memory location to be programmed.

- RCD = Data to be written to the read configuration register. This data is presented to the device on A15~A0; all other address inputs are ignored.

- 3. ID = Data read from Identifier Codes.

- QD = Data read from Query database.

- SRD = Data read from status register. See Table 14 for a description of the status register bits.

- PD = Data to be programmed at location PA. Data is latched on the rising edge of WE.

- CC = Configuration Code.

- 4. The upper byte of the data bus (Q8-Q15) during command writes is a "Don't Care" in x16 operation.

- 5. Following the Read Identifier Codes command, read operations access manufacturer, device and block lock codes. See Section 4.3 for read identifier code data.

- 6. If the WSM is running, only Q7 is valid; Q15-Q8 and Q6-Q0 float, which places them in a high impedance state.

- 7. After the Write to Buffer command is issued check the XSR to make sure a buffer is available for writing.

- 8. The number of words to be written to the Write Buffer = N + 1, where N = word count argument.

Count ranges on this device for word mode are N = 0000H to N = 000FH. The third and consecutive bus cycles, as determined by N, are for writing data into the Write Buffer.

- The Confirm command (D0H) is expected after exactly N + 1 write cycles; any other command at that point in the sequence aborts the write to buffer operation. Please see Figure 4. "Write to Buffer Flowchart" for additional information.

- 9. The write to buffer or erase operation does not begin until a Confirm command (D0h) is issued.

- 10. Attempts to issue a block erase or program to a locked block.

- 11. Either 40H or 10H are recognized by the WSM as the word program setup.

- 12. The clear block lock-bits operation simultaneously clears all block lock-bits.

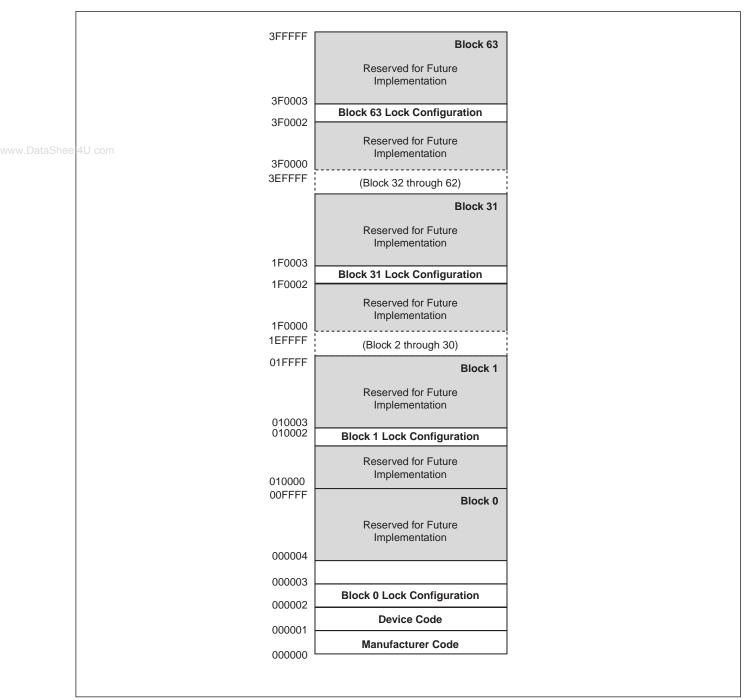

Figure 2. Device Identifier Code Memory Map

NOTE: Data is always given on the low byte in x16 mode (upper byte contains 00h).

# **Read Array Command**

The device is in Read Array mode on initial device power up and after exit from power down, or by writing FFH to the Command User Interface. The read configuration register defaults to asynchronous read page mode. The device remains enabled for reads until another command is written. The Read Array command functions independently of the VPEN voltage.

w.DataSheet4U.com

# **Read Query Mode Command**

This section defines the data structure or "Database" returned by the Common Flash Interface (CFI) Query command. System software should parse this structure to gain critical information such as block size, density, x8/x16, and electrical specifications. Once this information has been obtained, the software will know which command sets to use to enable MTP writes, block erases, and otherwise control the MTP component.

# **Query Structure Output**

The Query Database allows system software to gain information for controlling the MTP component. This section describes the device CFI-compliant interface that allows the host system to access Query data.

Query data are always presented on the lowest-order data outputs (DQ 0-7) only. The numerical offset value is the address relative to the maximum bus width supported by the device. On this family of devices, the Query table device starting address is a 10h, which is a word address for x16 devices.

For a word-wide (x16) device, the first two bytes of the Query structure, "Q" and "R" in ASCII, appear on the low byte at word addresses 10h and 11h. This CFI-compliant device outputs 00H data on upper bytes. Thus, the device outputs ASCII "Q" in the low byte (DQ 0-7) and 00h in the high byte (DQ 8-15).

At Query addresses containing two or more bytes of information, the least significant data byte is presented at the lower address, and the most significant data byte is presented at the higher address.

In all of the following tables, addresses and data are represented in hexadecimal notation, so the "h" suffix has been dropped. In addition, since the upper byte of word-wide devices is always "00h"," the leading "00" has been dropped from the table notation and only the lower byte value is shown. Any x16 device outputs can be assumed to have 00h on the upper byte in this mode.

Table 3. Summary of Query Structure Output as a Function of Device and Mode

| Device Query start location |                    | Quer   | Query data with maximum     |       |        | Query data with byte |        |  |  |

|-----------------------------|--------------------|--------|-----------------------------|-------|--------|----------------------|--------|--|--|

| Type/Mode                   | maximum device bus | devic  | device bus width addressing |       |        | addressing           |        |  |  |

|                             | width addresses    |        |                             |       |        |                      |        |  |  |

| t4U.com                     |                    | Hex    | Hex                         | ASCII | Hex    | Hex                  | ASCII  |  |  |

|                             |                    | Offset | Code                        | Value | Offset | Code                 | Value  |  |  |

| x16 device                  |                    | 10:    | 0051                        | "Q"   | 20:    | 51                   | "Q"    |  |  |

| x16 mode                    | 10h                | 11:    | 0052                        | "R"   | 21:    | 00                   | "Null" |  |  |

|                             |                    | 12:    | 0059                        | "Y"   | 22:    | 52                   | "R"    |  |  |

| x16 device                  |                    |        | •                           |       | 20:    | 51                   | "Q"    |  |  |

| x8 mode                     | N/A (1)            |        | N/A (1)                     |       | 21:    | 51                   | "Q"    |  |  |

|                             |                    |        |                             |       | 22:    | 52                   | "R"    |  |  |

#### NOTE:

Table 4. Example of Query Structure Output of a x16- and x8-Capable Device

|        | Word Addressing    |           |        | Byte Addressing    |          |

|--------|--------------------|-----------|--------|--------------------|----------|

| Offset | Hex Code           | Value     | Offset | Hex Code           | Value    |

| A15-A0 | D15                | - D0      | A7-A0  | D7 -               | D0       |

| 0010h  | 0051               | "Q"       | 20h    | 51                 | "Q"      |

| 0011h  | 0052               | "R"       | 21h    | 51                 | "Q"      |

| 0012h  | 0059               | "Y"       | 22h    | 52                 | "R"      |

| 0013h  | P_ID <sub>LO</sub> | PrVendor  | 23h    | 52                 | "R"      |

| 0014h  | P_ID <sub>HI</sub> | ID#       | 24h    | 59                 | "Y"      |

| 0015h  | PLO                | PrVendor  | 25h    | 59                 | "Y"      |

| 0016h  | PHI                | TblAdr    | 26h    | P_ID <sub>LO</sub> | PrVendor |

| 0017h  | A_ID <sub>LO</sub> | AltVendor | 27h    | P_ID <sub>LO</sub> | ID#      |

| 0018h  | A_ID <sub>HI</sub> | ID#       | 28h    | P_ID <sub>HI</sub> | ID#      |

|        |                    |           |        |                    |          |

<sup>1.</sup> The system must drive the lowest order addresses to access all the device's array data when the device is configured in x8 mode. Therefore, word addressing, where these lower addresses are not toggled by the system, is "Not Applicable" for x8-configured devices.

# **Query Structure Overview**

The Query command causes the MTP component to display the Common Flash Interface (CFI) Query structure or "database". The structure sub-sections and address locations are summarized below.

**Table 5. Query Structure (1)**

| Offset          | Sub-Section                     | Name Description                                      |

|-----------------|---------------------------------|-------------------------------------------------------|

| 00h             |                                 | Manufacturer Code                                     |

| 4 <b>.01h</b> m |                                 | Device Code                                           |

| (BA+2)h (2)     | Block Status Register           | Block-Specific Information                            |

| 04-0Fh          | Reserved                        | Reserved for Vendor-Specific Information              |

| 10h             | CFI Query Identification String | Reserved for Vendor-Specific Information              |

| 1Bh             | System Interface Information    | Command Set ID and Vendor Data Offset                 |

| 27h             | Device Geometry Definition      | MTP Device Layout                                     |

| P(3)            | Primary MXIC-Specific Extended  | Vendor-Defined Additional Information Specific to the |

|                 | Query Table                     | Primary Vendor Algorithm                              |

#### NOTES:

- 1. Refer to the Query Structure Output section and offset 28h for the detailed definition of offset address as a function of device bus width and mode.

- 2. BA = Block Address beginning location (i.e., 02000h is block 2s beginning location when the block size is 128 Kbyte).

- 3. Offset 15 defines "P" which points to the *Primary MXIC-Specific Extended Query* Table.

# **Block Status Register**

The block status register indicates whether an erase operation completed successfully or whether a given block is locked or can be accessed for MTP program/erase operations.

**Table 6. Block Status Register**

| Offset      | Length | Description                      | Address | Value           |

|-------------|--------|----------------------------------|---------|-----------------|

| (BA+2)h (1) | 1      | Block Lock Status Register       | BA+2:   | 00 or01         |

|             |        | BSR.0 Block Lock Status          |         |                 |

|             |        | 0 = Unlocked                     | BA+2:   | (bit 0): 0 or 1 |

|             |        | 1 = Locked                       |         |                 |

|             |        | BSR 1-7: Reserved for Future Use | BA+2:   | (bit 1-7): 0    |

#### NOTE:

1. BA = The beginning location of a Block Address (i.e., 008000h is block 1s (64-KB block) beginning location in word mode).

# **CFI Query Identification String**

The CFI Query Identification String provides verification that the component supports the Common Flash Interface specification. It also indicates the specification version and supported vendor-specified command set(s).

**Table 7. CFI Identification**

| Offset   | Length | Description                                                 | Add. | Hex  | Value |

|----------|--------|-------------------------------------------------------------|------|------|-------|

|          |        |                                                             |      | Code |       |

| 10h      | 3      | Query-unique ASCII string "QRY"                             | 10   | 51   | "Q"   |

| ±411 00m |        |                                                             | 11:  | 52   | "R"   |

| et4U.com |        |                                                             | 12:  | 59   | "Y"   |

| 13h      | 2      | Primary vendor command set and control interface ID code.   | 13:  | 01   |       |

|          |        | 16-bit ID code for vendor-specified algorithms              | 14:  | 00   |       |

| 15h      | 2      | Extended Query Table primary algorithm address              | 15:  | 31   |       |

|          |        |                                                             | 16:  | 00   |       |

| 17h      | 2      | Alternate vendor command set and control interface ID code. | 17:  | 00   |       |

|          |        | 0000h means no second vendor-specified algorithm exists     | 18:  | 00   |       |

| 19h      | 2      | Secondary algorithm Extended Query Table address.           | 19:  | 00   |       |

|          |        | 0000h means none exists                                     | 1A:  | 00   |       |

# **System Interface Information**

The following device information can optimize system interface software.

**Table 8. System Interface Information**

| Offset | Length | Description                                                                | Add. | Hex<br>Code | Value |

|--------|--------|----------------------------------------------------------------------------|------|-------------|-------|

| 1Bh    | 1      | VCC logic supply minimum program/erase voltage                             |      |             |       |

|        |        | bits 0-3 BCD 100 mV                                                        | 1B:  | 30          | 3.0V  |

|        |        | bits 4-7 BCD volts                                                         |      |             |       |

| 1Ch    | 1      | VCC logic supply maximum program/erase voltage                             |      |             |       |

|        |        | bits 0-3 BCD 100 mV                                                        | 1C:  | 36          | 3.6 V |

|        |        | bits 4-7 BCD volts                                                         |      |             |       |

| 1Dh    | 1      | VPP [programming] supply minimum program/erase voltage                     |      |             |       |

|        |        | bits 0-3 BCD 100 mV                                                        | 1D:  | 00          | 0.0V  |

|        |        | bits 4-7 HEX volts                                                         |      |             |       |

| 1Eh    | 1      | VPP [programming] supply maximum program/erase voltage                     |      |             |       |

|        |        | bits 0-3 BCD 100 mV                                                        | 1E:  | 00          | 0.0V  |

|        |        | bits 4-7 HEX volts                                                         |      |             |       |

| 1Fh    | 1      | "n" such that typical single word program time-out = 2 <sup>n</sup> us     | 1F:  | 07          | 128us |

| 20h    | 1      | "n" such that typical max. buffer write time-out = 2 <sup>n</sup> us       | 20:  | 07          | 128us |

| 21h    | 1      | "n" such that typical block erase time-out = 2 <sup>n</sup> ms             | 21:  | 0A          | 1s    |

| 22h    | 1      | "n" such that typical full chip erase time-out = 2 <sup>n</sup> ms         | 22:  | 00          | NA    |

| 23h    | 1      | "n" such that maximum word program time-out = 2 <sup>n</sup> times typical | 23:  | 04          | 2ms   |

| 24h    | 1      | "n" such that maximum buffer write time-out = 2 <sup>n</sup> times typical | 24:  | 04          | 2ms   |

| 25h    | 1      | "n" such that maximum block erase time-out = 2 <sup>n</sup> times typical  | 25:  | 04          | 16s   |

| 26h    | 1      | "n" such that maximum chip erase time-out = 2 <sup>n</sup> times typical   | 26:  | 00          | NA    |

# **Device Geometry Definition**

This field provides critical details of the MTP device geometry.

# **Table 9. Device Geometry Definition**

| Offset          | Length | Description                                                            | Code | e See Ta | ble |

|-----------------|--------|------------------------------------------------------------------------|------|----------|-----|

|                 |        |                                                                        |      | Below    |     |

| 27h             | 1      | "n" such that device size = 2 <sup>n</sup> in number of bytes          | 27:  | 17       |     |

| 4U <b>28h</b> 1 | 2      | MTP device interface: x8 async(28:00,29:00),                           | 28:  | 01       | x16 |

|                 |        | x16 async(28:01,29:00), x8/x16 async(28:02,29:00)                      | 29:  | 00       |     |

| 2Ah             | 2      | "n" such that maximum number of bytes in write buffer = 2 <sup>n</sup> | 2A:  | 05       | 32  |

|                 |        |                                                                        | 2B:  | 00       |     |

|                 |        | Number of erase block regions within device:                           |      |          |     |

|                 |        | 1. x = 0 means no erase blocking; the device erases in "bulk"          |      |          |     |

|                 |        | 2. x specifies the number of device or partition regions with one or   |      |          |     |

| 2Ch             | 1      | more contiguous same-size erase blocks                                 | 2C:  | 01       | 1   |

|                 |        | 3. Symmetrically blocked partitions have one blocking region           |      |          |     |

|                 |        | 4. Partition size = (total blocks) x (individual block size)           |      |          |     |

| 2Dh             | 4      | Erase Block Region 1 Information                                       | 2D:  | 3F       |     |

|                 |        | bits 0-15 = y, y+1 = number of identical-size erase blocks             | 2E:  | 00       |     |

|                 |        | bits 16-31 = z, region erase block(s) size are z x 256 bytes           | 2F:  | 00       |     |

|                 |        |                                                                        | 30:  | 02       |     |

P/N:PM0946

# **Primary-Vendor Specific Extended Query Table**

Certain MTP features and commands are optional. The *Primary Vendor-Specific Extended Query* table specifies this and other similar information.

**Table 10. Primary Vendor-Specific Extended Query**

| Offset(1) | Length | Description                                                   | Add.  | Hex       | Value  |

|-----------|--------|---------------------------------------------------------------|-------|-----------|--------|

| P=31h     |        | (Optional MTP Features and Commands)                          |       | Code      |        |

| (P+0)h    | 3      | Primary extended query table                                  | 31:   | 50        | "P"    |

| (P+1)h    |        | Unique ASCII string "PRI"                                     | 32:   | 52        | "R"    |

| (P+2)h    |        |                                                               | 33:   | 49        | " "    |

| (P+3)h    | 1      | Major version number, ASCII                                   | 34:   | 31        | "1"    |

| (P+4)h    | 1      | Minor version number, ASCII                                   | 35:   | 31        | "1"    |

| (P+5)h    |        | Optional feature and command support (1=yes, 0=no)            | 36:   | C8        |        |

| (P+6)h    |        | bits 9-31 are reserved; undefined bits are "0". If bit 31 is  | 37:   | 00        |        |

| (P+7)h    |        | "1" then another 31 bit field of optional features follows at | 38:   | 00        |        |

| (P+8)h    |        | the end of the bit-30 field.                                  | 39:   | 00        |        |

|           |        | bit 0 Chip erase supported                                    | bit   | 0 = 0     | No     |

|           | 4      | bit 1 Suspend erase not supported                             | bit   | 1 = 0     | No     |

|           |        | bit 2 Suspend program not supported                           | bit   | 2 = 0     | No     |

|           |        | bit 3 Legacy lock/unlock supported                            | bit 3 | = 1(1)    | Yes(1) |

|           |        | bit 4 Queued erase supported                                  | bit   | 4 = 0     | No     |

|           |        | bit 5 Instant Individual block locking supported              | bit   | 5 = 0     | No     |

|           |        | bit 6 Protection bits supported                               | bit   | 6 = 1     | Yes    |

|           |        | bit 7 Page-mode read supported                                | bit   | 7 = 1     | Yes    |

|           |        | bit 8 Synchronous read supported                              | bit   | 8 = 0     | No     |

| (P+9)h    | 1      | Reserved for future use                                       | 3A:   | 00        |        |

| (P+A)h    |        | Block status register mask                                    | 3B:   | 01        |        |

| (P+B)h    | 2      | bits 2-15 are Reserved; undefined bits are "0"                | 3C:   | 00        |        |

|           |        | bit 0 Block Lock-Bit Status register active                   | b     | it 0 = 1  | Yes    |

|           |        | bit 1 Block Lock-Down Bit Status active                       | b     | oit 1 = 0 | No     |

| (P+C)h    | 1      | VCC logic supply highest performance program/erase voltage    |       |           |        |

|           |        | bits 0-3 BCD value in 100 mV                                  | 3D:   | 33        | 3.3V   |

|           |        | bits 4-7 BCD value in volts                                   |       |           |        |

| (P+D)h    | 1      | VPP optimum program/erase supply voltage                      |       |           |        |

|           |        | bits 0-3 BCD value in 100 mV                                  | 3E:   | 00        | 0.0V   |

|           |        | bits 4-7 HEX value in volts                                   |       |           |        |

# NOTE:

<sup>1.</sup> Future devices may not support the described "Legacy Lock/Unlock" function. Thus bit 3 would have a value of "0".

**Table 11. Protection Register Information**

| Offset(1) Length Description |   | Description                                                      | Add. | Hex  | Value |

|------------------------------|---|------------------------------------------------------------------|------|------|-------|

| P=31h                        |   | (Optional MTP Features and Commands)                             |      | Code |       |

| (P+E)h                       | 1 | Number of Protection register fields in JEDEC ID space.          | 3F:  | 01   | 01    |

|                              |   | "00h," indicates that 256 protection bytes are available         |      |      |       |

|                              |   | Protection Field 1: Protection Description                       |      |      |       |

|                              |   | This field describes user-available One Time Programmable        |      |      |       |

|                              |   | (OTP) protection register bytes. Some are pre-programmed         |      |      |       |

| (P+F)h                       |   | with device-unique serial numbers. Others are user-programmable. |      |      |       |

| (P+10)h                      |   | Bits 0-15 point to the protection register lock                  | 40:  | 00   | 00h   |

| (P+11)h                      |   | byte, the section's first byte. The following bytes are factory  |      |      |       |

| (P+12)h                      |   | pre-programmed and user-programmable.                            |      |      |       |

|                              |   | bits 0-7 = Lock/bytes JEDEC-plane physical low address           |      |      |       |

|                              |   | bits 8-15 = Lock/bytes JEDEC-plane physical high address         |      |      |       |

|                              |   | bits 16-23 = "n" such that 2 " = factory pre-programmed bytes    |      |      |       |

|                              |   | bits 24-31 = "n" such that 2 n = user-programmable bytes         |      |      |       |

# NOTE:

**Table 12. Page Read Information**

| Offset(1) Length<br>P=31h |   | Description                                                             | Add. | Hex  | Value   |

|---------------------------|---|-------------------------------------------------------------------------|------|------|---------|

|                           |   | (Optional MTP Features and Commands)                                    |      | Code |         |

|                           |   | Page Mode Read capability                                               |      |      |         |

|                           |   | bits 0-7 = "n" such that 2 <sup>n</sup> HEX value represents the number |      |      |         |

| (P+13)h                   | 1 | of read-page bytes. See offset 28h for device word width to             | 44:  | 04   | 16 byte |

|                           |   | determine page-mode data output width. 00h indicates no                 |      |      |         |

|                           |   | read page buffer.                                                       |      |      |         |

| (P+14)h                   | 1 | Number of synchronous mode read configuration fields that               | 45:  | 00   | 0       |

|                           |   | follow. 00h indicates no burst capability.                              |      |      |         |

| (P+15)h                   |   | Reserved for future use                                                 | 46:  |      |         |

## NOTE:

<sup>1.</sup> The variable P is a pointer which is defined at CFI offset 15h.

<sup>1.</sup> The variable P is a pointer which is defined at CFI offset 15h.

# **DEVICE OPERATION**

#### SILICON ID READ

The Silicon ID Read mode allows the reading out of a binary code from the device and will identify its manufacturer and type. This mode is intended for use by programming equipment for the purpose of automatically matching the device to be programmed with its corresponding programming algorithm. This mode is functional over the entire temperature range of the device.

To activate this mode, the two cycle "Silicon ID Read" command is requested. (The ID code value is illustrated in Table 13.)

During the "Silicon ID Read" Mode, manufacturer's code (MXIC=C2H) can be read out by setting A0=VIL and device identifier can be read out by setting A0=VIH.

To terminate the operation, it is necessary to write the read command. The "Silicon ID Read" command functions independently of the VPEN voltage. This command is valid only when the WSM is off.

Table 13. MX26L6419 Silicon ID Codes

| Туре                      | Address (1) | Code (HEX) | Q7 | Q6 | Q5 | Q4 | Q3 | Q2 | Q1 | Q0 |

|---------------------------|-------------|------------|----|----|----|----|----|----|----|----|

| Manufacture Code          | 00000       | C2H        | 1  | 1  | 0  | 0  | 0  | 0  | 1  | 0  |

| Device Code               | 00001       | 00AEH      | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 0  |

| Block Lock Configuration  | X0002 (2)   |            |    |    |    |    |    |    |    |    |

| - Block is Unlocked       |             | DQ0=0      |    |    |    |    |    |    |    |    |

| - Block is Locked         |             | DQ0=1      |    |    |    |    |    |    |    |    |

| - Reserved for Future Use |             | DQ1-7      |    |    |    |    |    |    |    |    |

#### Notes:

- 1. The lowest order address line is A0.

- 2. X selects the specific blocks lock configuration code.

# **Table 14. Status Register Definitions**

|         | High Z     |                            | Definiti                  | on                   |       |

|---------|------------|----------------------------|---------------------------|----------------------|-------|

| Symbol  | When Busy? | Status                     | "1"                       | "0"                  | Notes |

| SR.7    | No         | WRITE STATE MACHINE STATUS | Ready                     | Busy                 | 1     |

| SR.6    | Yes        | RESERVED                   |                           |                      |       |

| SR.5    | Yes        | ERASE AND CLEAR LOCK-BITS  | Error in Block Erasure or | Successful Block     | 2     |

| 14U.com |            | STATUS                     | Clear Lock-Bits           | Erase or Clear       |       |

|         |            |                            |                           | Lock-Bits            |       |

| SR.4    | Yes        | PROGRAM AND SET LOCK-BIT   | Error in Setting Lock-Bit | Successful Set Block |       |

|         |            | STATUS                     |                           | Lock Bit             |       |

| SR.3    | Yes        | PROGRAMMING VOLTAGE        | Low Programming Voltage   | Programming Voltage  | 3     |

|         |            | STATUS                     | Detected, Operation       | OK                   |       |

|         |            |                            | Aborted                   |                      |       |

| SR.2    | Yes        | RESERVED                   |                           |                      |       |

| SR.1    | Yes        | DEVICE PROTECT STATUS      | Block Lock-Bit Detected,  | Unlock               | 4     |

|         |            |                            | Operation Abort           |                      |       |

| SR.0    | Yes        | RESERVED                   |                           |                      | 5     |

#### Notes

- 1. Check SR.7 to determine block erase, program, or lock-bit configuration completion. SR.6-SR.0 are not driven while SR.7 = 0

- 2. If both SR.5 and SR.4 are "1" after a block erase or lock-bit configuration attempt, an improper command sequence was entered.

- 3. SR.3 does not provide a continuous programming voltage level indication. The WSM interrogates and indicates the programming voltage level only after Block Erase, Program, Set Block Lock-Bit, or Clear Block Lock-Bits command sequences.

- 4. SR.1 does not provide a continuous indication of block lock-bit values. The WSM interrogates the block lock-bits only after Block Erase, Program, or Lock-Bit configuration command sequences. It informs the system, depending on the attempted operation, if the block lock-bit is set. Read the block lock configuration codes using the Read Identifier Codes command to determine block lock-bit status.

- 5. SR.0 is reserved for future use and should be masked when polling the status register.

## **Table 15. Extended Status Register Definitions**

| Symbol | High Z<br>When | Status              | Definition             |                            |   |  |  |  |

|--------|----------------|---------------------|------------------------|----------------------------|---|--|--|--|

|        | Busy?          |                     | "1"                    | "0"                        |   |  |  |  |

| XSR.7  | No             | WRITE BUFFER STATUS | Write buffer available | Write buffer not available | 1 |  |  |  |

| XSR.6- | Yes            | RESERVED            |                        |                            | 2 |  |  |  |

| XSR.0  |                |                     |                        |                            |   |  |  |  |

#### Notes:

- 1. After a Buffer-Write command, XSR.7 = 1 indicates that a Write Buffer is available.

- 2. XSR.6-XSR.0 are reserved for future use and should be masked when polling the status register.

#### READ STATUS REGISTER COMMAND

The Status Register is read after writing the Read Status Register command of 70H to the Command User Interface. Also, after starting the internal operation the device is set to the Read Status Register mode automatically.

The contents of Status Register are latched on the later falling edge of  $\overline{OE}$  or the first edge of  $\overline{CE}$  that enables the device  $\overline{OE}$  must be toggle to VIH or the device must be disable before further reads to update the status register latch. The Read Status Register command functions independently of the VPEN voltage.

#### **CLEAR STATUS REGISTER COMMAND**

The Erase Status, Program Status, Block Status bits and protect status are set to "1" by the Write State Machine and can only be reset by the Clear Status Register command of 50H. These bits indicates various failure conditions.

#### **BLOCK ERASE COMMAND**

Automated block erase is initiated by writing the Block Erase command of 20H followed by the Confirm command of D0H. An address within the block to be erased is required (erase changes all block data to FFH).

Block preconditioning, erase, and verify are handled internally by the WSM (invisible to the system). The CPU can detect block erase completion by analyzing the status register bit SR.7. Toggle  $\overline{OE}$ ,  $\overline{CE}$  to update the status register. The CUI remains in read status register mode until a new command is issued. Also, reliable block erasure can only occur when VCC is valid and VPEN = VPENH .

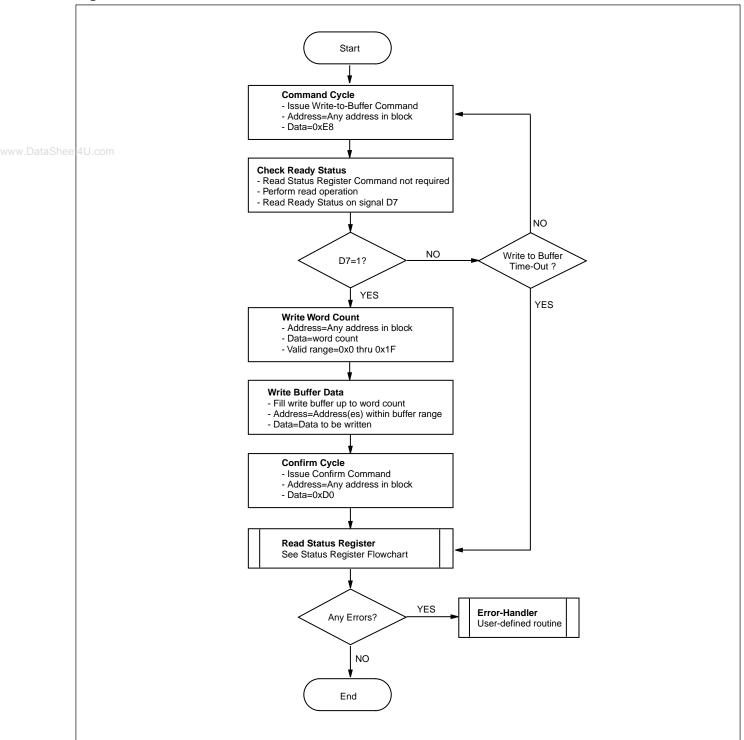

## WRITE TO BUFFER COMMAND

To program the device, a Write to Buffer command is issue first. A variable number of bytes, up to the buffer size, can be loaded into the buffer and written to the MTP device. First, the Write to Buffer Setup command is issued along with the Block Address (see Figure 4, Write to Buffer Flowchart on page 25). After the command is issued, the extended Status Register (XSR) can

be read when  $\overline{\text{CE}}$  is VIL. XSR.7 indicates if the Write Buffer is available.

If the buffer is available, the number of words to be program is written to the device. Next, the start address is given along with the write buffer data. Subsequent writes provide additional device addresses and data, depending on the count. After the last buffer data is given, a Write Confirm command must be issued. The WSM beginning copy the buffer data to the MTP array.

If an error occurs while writing, the device will stop writing, and status register bit SR.4 will be set to a "1" to indicate a program failure. The internal WSM verify only detects errors for "1" that do not successfully program to "0". If a program error is detected, the status register should be cleared. Any time SR.4 and/or SR.5 is set, the device will not accept any more Write to Buffer commands. Reliable buffered writes can only occur when VCC is valid and VPEN = VPENH. Also, successful programming requires that the corresponding block lock-bit be reset.

#### WORD PROGRAM COMMANDS

Word program is executed by a two-command sequence. The Word Program Setup command of 40H is written to the Command Interface, followed by a second write specifying the address and data to be written. The WSM controls the program pulse application and verify operation. The CPU can detect the completion of the program event by analyzing the status register bit SR.7.

If a word program is attempted while VPEN\_V PENLK, status register bits SR.4 and SR.3 will be set to "1". Successful word programs require that the corresponding block lock-bit be cleared. If a word program is attempted when the corresponding block lock-bit is set, SR.1 and SR.4 will be set to "1".

## ACC FAST PROGRAM/ERASE FUNCTIONS

When VPP is between 3.0V and 3.6V, all program and erase current is drawn through the VCC pin. When ACC pin is connected to a 12V power supply, the device draws program and erase current directly from the ACC pin. This eliminates the need for an external switching transistor control the voltage VPP.

The 12V ACC mode enhances programming performance during the short period of time typically found in manufacturing processes; however, it is not intended for extended use. ACC pin may be connected to 12V for a total of 80 hours maximum. Stressing the device beyond these limits may cause permanent damage.

www.DataSheet4II.com

# **Read Configuration**

The device will support both asynchronous page mode and standard word reads. No configuration is required. Status register and identifier only support standard word single read operations.

**Table 16. Read Configuration Register Definition**

|                   | RM                            | R           | R                | R                                                 | R                                                    | R  | R | R |  |  |

|-------------------|-------------------------------|-------------|------------------|---------------------------------------------------|------------------------------------------------------|----|---|---|--|--|

| eet <del>4U</del> | 15(A15)                       | 14          | 13               | 12                                                | 11                                                   | 10 | 9 | 8 |  |  |

|                   | R                             | R           | R                | R                                                 | R                                                    | R  | R | R |  |  |

|                   | 7                             | 6           | 5                | 4                                                 | 3                                                    | 2  | 1 | 0 |  |  |

|                   |                               |             |                  |                                                   | Notes                                                |    |   |   |  |  |

|                   | RCR.15 =                      | READ MOI    | DE (RM)          |                                                   | Read mode configuration effects reads from the MTP   |    |   |   |  |  |

|                   | 0 = Standa                    | ard Word Re | eads Enabled (De | efault)                                           | array.                                               |    |   |   |  |  |

|                   | 1 = Page-N                    | Mode Read   | s Enabled        |                                                   | Status register, query, and identifier reads support |    |   |   |  |  |

|                   |                               |             |                  |                                                   | standard word read cycles.                           |    |   |   |  |  |

|                   | RCR.14-0= RESERVED FOR FUTURE |             |                  | These bits are reserved for future use. Set these |                                                      |    |   |   |  |  |

|                   | ENHANCEMENTS (R)              |             |                  | bits to "0".                                      |                                                      |    |   |   |  |  |

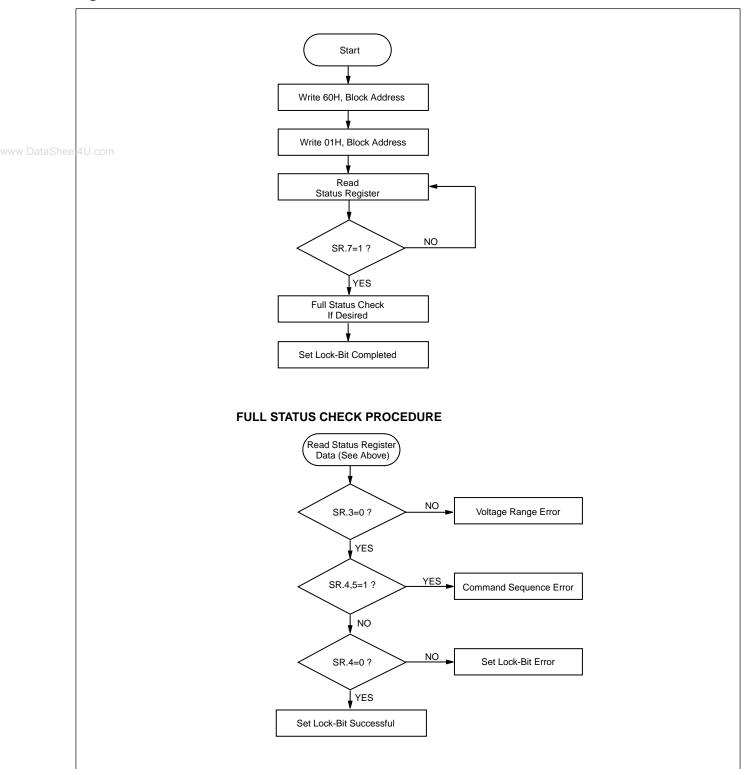

#### Set Block Lock-Bit Commands

This device provided the block lock-bits, to lock and unlock the individual block. To set the block lock-bit, the two cycle Set Block Lock-Bit command is requested. This command is invalid while the WSM is running. Writing the set block lock-bit command of 60H followed by confirm command and an appropriate block address. After the command is written, the device automatically outputs status register data when read. The CPU can detect the completion of the set lock-bit event by analyzing the status register bit SR.7. Also, reliable operations occur only when VCC and VPEN are valid. With VPEN\_VPENLK, lock-bit contents are protected against alteration.

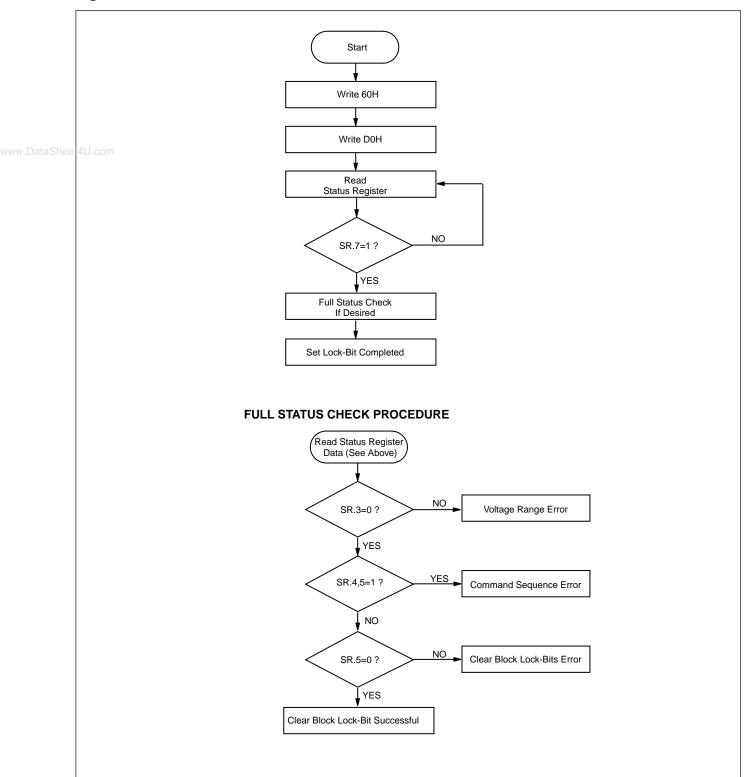

#### Clear Block Lock-Bits Command

All set block lock-bits can clear by the Clear Block Lock-Bits command. This command is invalid while the WSM is running. To Clear the block lock-bits, two cycle command is requested . The device automatically outputs status register data when read. The CPU can detect completion of the clear block lock-bits event by analyzing the status register bit SR.7. If a clear block lock-bits operation is aborted due to V PEN or V CC transitioning out of valid range, block lock-bit values are left in an undetermined state. A repeat of clear block lock-bits is required to initialize block lock-bit contents to known values.

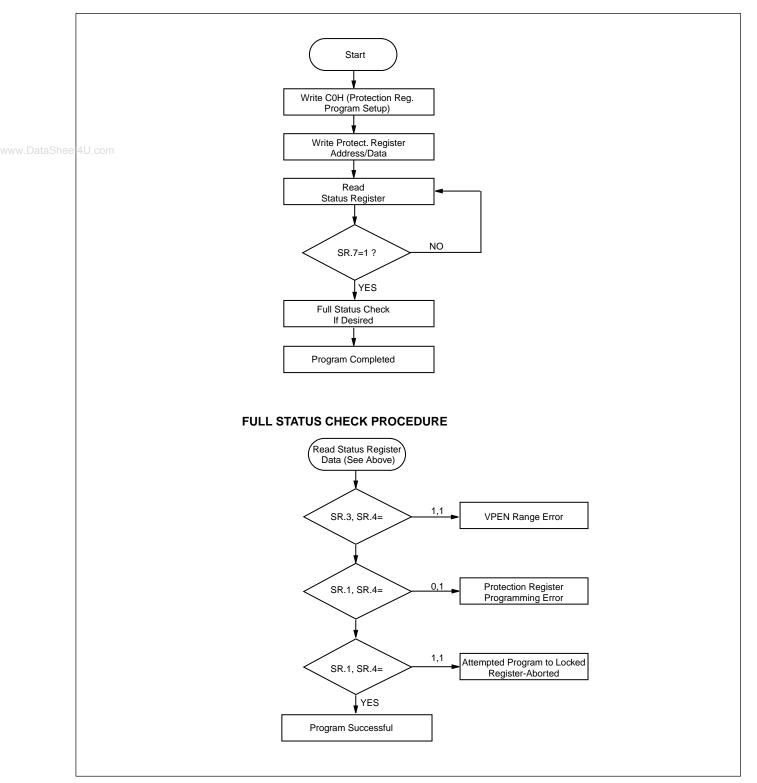

#### **Protection Register Program Command**

The device offer a 128-bit protection register to increase the security of a system design. The 128-bits protection register are divided into two 64-bit segments. One is programmed in the factory with a unique 64-bit number, which is unchangeable. The other one is left blank for customer designers to program as desired. Once the customer segment is programmed, it can be locked to prevent reprogramming.

# **Reading the Protection Register**

The protection register is read in the identification read mode. The device is switched to this mode by writing the Read Identifier command 90H. Once in this mode, read cycles from addresses retrieve the specified information. To return to read array mode, write the Read Array command (FFH).

# **Programming the Protection Register**

The protection register bits are programmed using the two-cycle Protection Program command. The 64-bit number is programmed 16 bits at a time for word-wide parts. First write the Protection Program Setup command, C0H. The next write to the device will latch in address and data and program the specified location.

Any attempt to address Protection Program commands outside the defined protection register address space will result in a status register error. Attempting to program a locked protection register segment will result in a status register error.

# **Locking the Protection Register**

The user-programmable segment of the protection register is lockable by programming Bit 1 of the PR-LOCK location to 0. Bit 0 of this location is programmed to 0 at the MXIC factory to protect the unique device number. Bit 1 is set using the Protection Program command to program "FFFD" to the PR-LOCK location. After these bits have been programmed, no further changes can be made to the values stored in the protection register. Protection Program commands to a locked section will result in a status register error. Protection register lockout state is not reversible.

## VCC, VPEN, RESET--TRANSITIONS

Block erase, program, and lock-bit configuration are not guaranteed if VPEN or VCC falls outside of the specified operating ranges, or RESET = VIH. If RESET transitions to VIL during block erase, program, or lock-bit configuration will remain low for a maximum time of tPLPH+tPHRH until the reset operation is complete. Then, the operation will abort and the device will enter reset/power-down mode. The aborted operation may leave data partially corrupted after programming, or partially altered after an erase or lock-bit configuration. Therefore, block erase and lock-bit configuration commands must be repeated after normal operation is restored. Device power-off or RESET=VIL clears the Status Register.

The CUI latches commands <u>issued</u> by system software and is not altered by VPEN, CE transitions, or WSM actions. Its state is read array mode upon power-up, after exit from reset/power-down mode, or after VCC transitions below VLKO. VCC must be kept at or above VPEN during VCC transitions.

After block erase, program, or lock-bit configuration, even after VPEN transitions down to VPENLK, the CUI must be placed in read array mode via the Read Array command if subsequent access to the memory array is desired. VPEN must be kept at or below VCC during VPEN transitions.

Word Address A[21 - 0]: 64 Mbit

88H

4 Words

User Programmed

4 Words

Factory Programmed

1 Word Lock

**Figure 3. Protection Register Memory Map**

**NOTE:** The lowest order address line is A0.

P/N:PM0946

# **Table 17. Word-Wide Protection Register Addressing**

| Word             | Use     | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |  |

|------------------|---------|----|----|----|----|----|----|----|----|--|

| LOCK             | Both    | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |  |

| 0                | Factory | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |  |

| 1                | Factory | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 0  |  |

| 2                | Factory | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 1  |  |

| 3                | Factory | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |  |

| t4U. <b>4</b> pm | User    | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 1  |  |

| 5                | User    | 1  | 0  | 0  | 0  | 0  | 1  | 1  | 0  |  |

| 6                | User    | 1  | 0  | 0  | 0  | 0  | 1  | 1  | 1  |  |

| 7                | User    | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 0  |  |

**NOTE:** 1. All address lines not specified in the above table must be 0 when accessing the Protection Register, i.e., A21-A8 = 0.

P/N:PM0946

Figure 4. Write to Buffer Flowchart

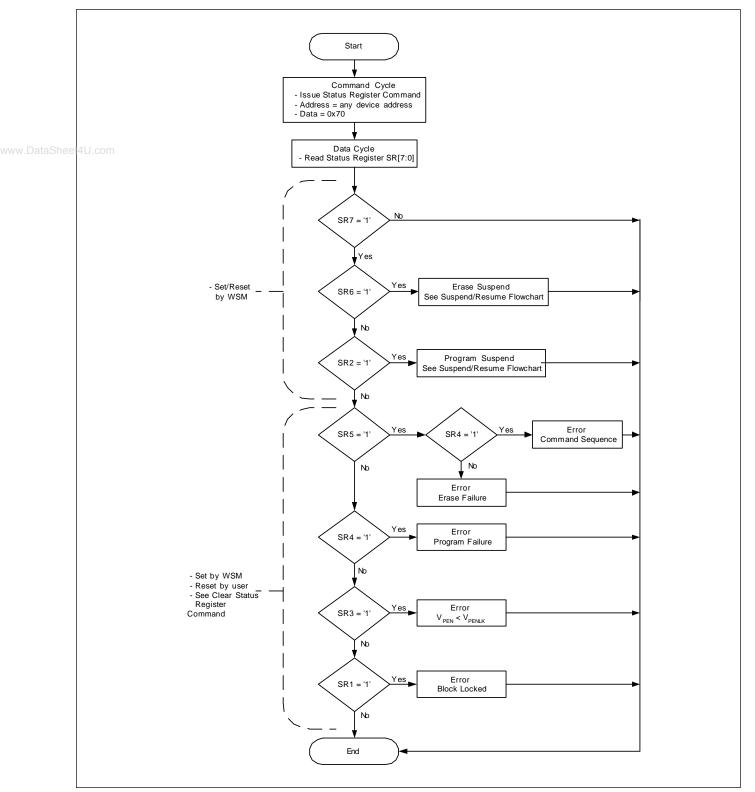

Figure 5. Status Register Flowchart

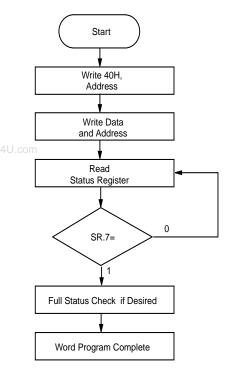

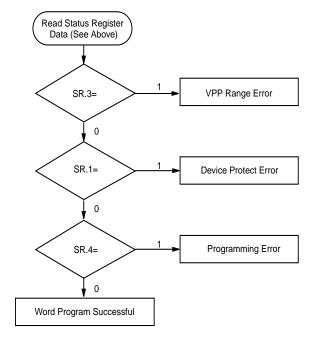

Figure 6. Word Programming Flowchart

#### **FULL STATUS CHECK PROCEDURE**

| Bus       | Command      | Comments             |

|-----------|--------------|----------------------|

| Operation |              |                      |

| Write     | Setup        | Data=40H             |

|           | Word Program | Addr=Location to Be  |

|           |              | Programmed           |

| Write     | Word         | Data=Data to Be      |

|           | Program      | Programmed           |

|           |              | Addr=Location to Be  |

|           |              | Programmed           |

| Read      |              | Status Register Data |

| (Note 1)  |              |                      |

| Standby   |              | Check SR.7           |

|           |              | 1=WSM Ready          |

|           |              | 0=WSM Busy           |

1. Toggling OE (low to high to low) updates the status register. This can be done in place of issuing the Read Status Register command. Repeat for subsequent programming operations.

SR full status check can be done after each program operation, or after a sequence of programming operations.

Write FFH after the last program operation to place device in read array mode.

| Bus       | Command                 | Comments                    |

|-----------|-------------------------|-----------------------------|

| Operation |                         |                             |

| Standby   |                         | Check SR.3                  |

|           |                         | 1=Programming to Voltage    |

|           |                         | Error Detect                |

| Standby   |                         | Check SR.1                  |

|           |                         | 1=Device Protect Detect     |

|           |                         | RP=VIH, Block Lock-Bit is   |

|           |                         | Set Only required for       |

|           |                         | systems                     |

| Standby   |                         | Check SR.4                  |

|           |                         | 1=Programming Error         |

| T         | <del>-</del> // / / / / | tala Variation that at at a |

Toggling  $\overline{OE}$  (low to high to low) updates the status register. This can be done in place of issuing the Read Status Register command. Repeat for subsequent programming operations.

SR.4, SR.3, and SR.1 are only cleared by the Clear Status Register Command in cases where multiple location are programmed before full status is checked. If an error is detected, clear the status register before attempting retry or other error recovery.

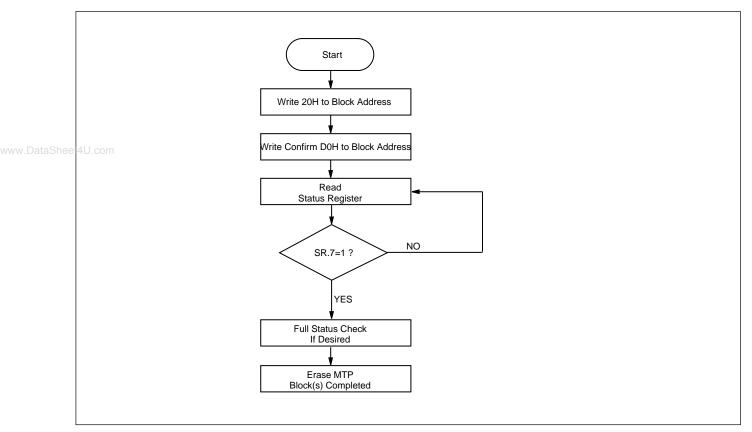

# Figure 7. Block Erase Flowchart

Figure 8. Set Block Lock-Bit Flowchart

Figure 9. Clear Lock-Bit Flowchart

Figure 10. Protection Register Programming Flowchart

## ABSOLUTE MAXIMUM RATINGS

Storage Temperature

Plastic Packages ...... -65°C to +150°C

Ambient Temperature

with Power Applied ..... -65°C to +125°C

Voltage with Respect to Ground

VCC (Note 1) ..... -0.5 V to +4.0 V

RESET (Note 2) ..... -0.5 V to +12.5 V

All other pins (Note 1) ..... -0.5 V to VCC +0.5 V

ACC pin (Note 1, Note 4) ..... -0.5 V to +13.5 V

Output Short Circuit Current (Note 3) ..... 200 mA

#### Notes:

- 1. Minimum DC voltage on input or I/O pins is -0.5 V. During voltage transitions, input or I/O pins may overshoot VSS to -2.0 V for periods of up to 20 ns. See Figure 6. Maximum DC voltage on input or I/O pins is VCC +0.5 V. During voltage transitions, input or I/O pins may overshoot to VCC +2.0 V for periods up to 20 ns. See Figure 7.

- 2. Minimum DC input voltage on pins RESET is -0.5 V. During voltage transitions, RESET may overshoot VSS to -2.0 V for periods of up to 20 ns. See Figure 6.

- 3. No more than one output may be shorted to ground at a time. Duration of the short circuit should not be greater than one second.

- 4. ACC pin may be connected to 12V for a total of 80 hours maximum.

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this data sheet is not implied. Exposure of the device to absolute maximum rating conditions for extended periods may affect device reliability.

#### **OPERATING RATINGS**

| 0℃ to +70℃      |

|-----------------|

|                 |

| +3.0 V to 3.6 V |

|                 |

Operating ranges define those limits between which the functionality of the device is guaranteed.

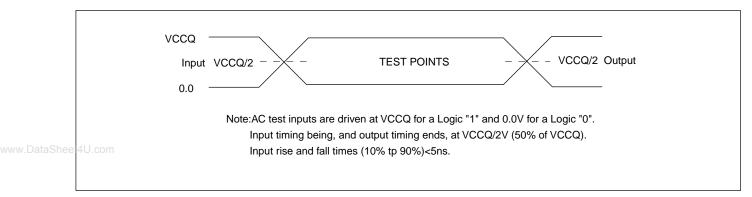

# **DC Characteristics**

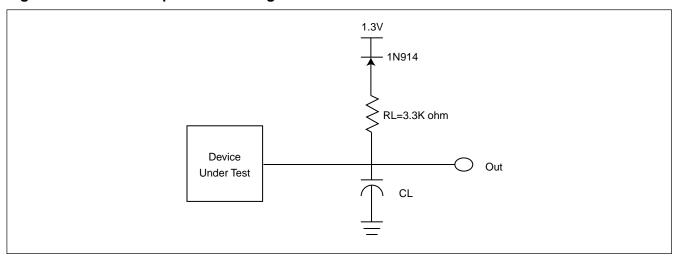

| Parameter                   | Notes                                                                                                                                                                                       | Тур                                                                                                                                                                                                 | Max                         | Unit                        | Test Conditions                  |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|----------------------------------|

| Input and VPEN Load Current |                                                                                                                                                                                             |                                                                                                                                                                                                     | ±1                          | uA                          | VCC = VCC Max; VCCQ = VCCQ Max   |

|                             |                                                                                                                                                                                             |                                                                                                                                                                                                     |                             |                             | VIN = VCCQ or GND                |

| Output Leakage Current      |                                                                                                                                                                                             |                                                                                                                                                                                                     | ±10                         | uA                          | VCC = VCC Max; VCCQ = VCCQ Max   |

|                             |                                                                                                                                                                                             |                                                                                                                                                                                                     |                             |                             | VIN = VCCQ or GND                |

|                             |                                                                                                                                                                                             |                                                                                                                                                                                                     |                             |                             | CMOS Inputs, VCC = VCC Max,      |

| VCC Standby Current         | 1,2                                                                                                                                                                                         | 25                                                                                                                                                                                                  | 80                          | uA                          | Device is disabled (see table 1) |

|                             |                                                                                                                                                                                             |                                                                                                                                                                                                     |                             |                             | RESET=VCCQ±0.2V                  |

|                             |                                                                                                                                                                                             | 0.71                                                                                                                                                                                                | 2                           | mA                          | TTL Inputs, VCC=VCC max,         |

|                             |                                                                                                                                                                                             |                                                                                                                                                                                                     |                             |                             | Device is disable (see table 1), |

|                             |                                                                                                                                                                                             |                                                                                                                                                                                                     |                             |                             | RESET=VIH                        |

| VCC Power-Down Current      |                                                                                                                                                                                             | 25                                                                                                                                                                                                  | 80                          | uA                          | RESET=GND±0.2V,                  |

|                             |                                                                                                                                                                                             |                                                                                                                                                                                                     |                             |                             |                                  |

|                             |                                                                                                                                                                                             |                                                                                                                                                                                                     |                             |                             | CMOS Inputs, VCC=VCC Max,        |

|                             |                                                                                                                                                                                             |                                                                                                                                                                                                     |                             |                             | VCCQ=VCCQ Max                    |

|                             |                                                                                                                                                                                             | 15                                                                                                                                                                                                  | 20                          | mA                          | Device is enabled (see Table 1)  |

| VCC Page Mode Read Current  | 2                                                                                                                                                                                           |                                                                                                                                                                                                     |                             |                             | f=5MHz, IOUT=0mA                 |

|                             |                                                                                                                                                                                             |                                                                                                                                                                                                     |                             |                             | CMOS Inputs, VCC=VCC Max,        |

|                             |                                                                                                                                                                                             |                                                                                                                                                                                                     |                             |                             | VCCQ=VCCQ Max                    |

|                             |                                                                                                                                                                                             | 24                                                                                                                                                                                                  | 29                          | mA                          | Device is enabled (see Table 1)  |

|                             |                                                                                                                                                                                             |                                                                                                                                                                                                     |                             |                             | f=33MHz, IOUT=0mA                |

| VCC Program or Set Lock-Bit |                                                                                                                                                                                             | 35                                                                                                                                                                                                  | 60                          | mA                          | CMOS Inputs, VPEN=VCC            |