## MULTIPLEXED, Burst Mode, Flash Memory MX29NS320E/640E/128E

# Contents

| 1. | . FEATURES                   |                                                                                       |        |

|----|------------------------------|---------------------------------------------------------------------------------------|--------|

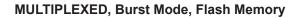

| 2. | GENE<br>2-1.<br>2-2.<br>2-3. | ERAL INFORMATION<br>Operating Speeds<br>Ordering Information<br>Part Name Description | 8<br>8 |

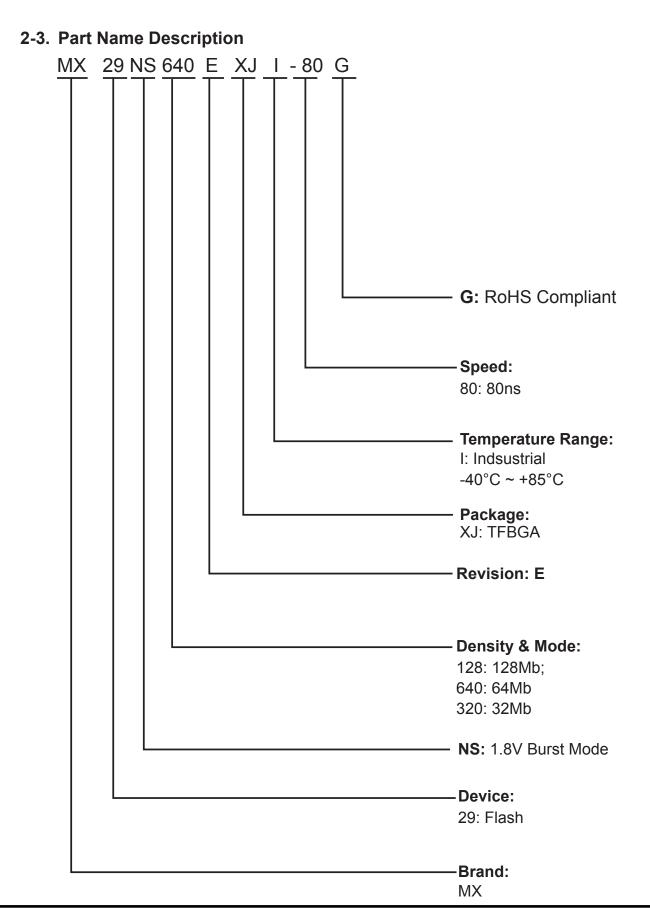

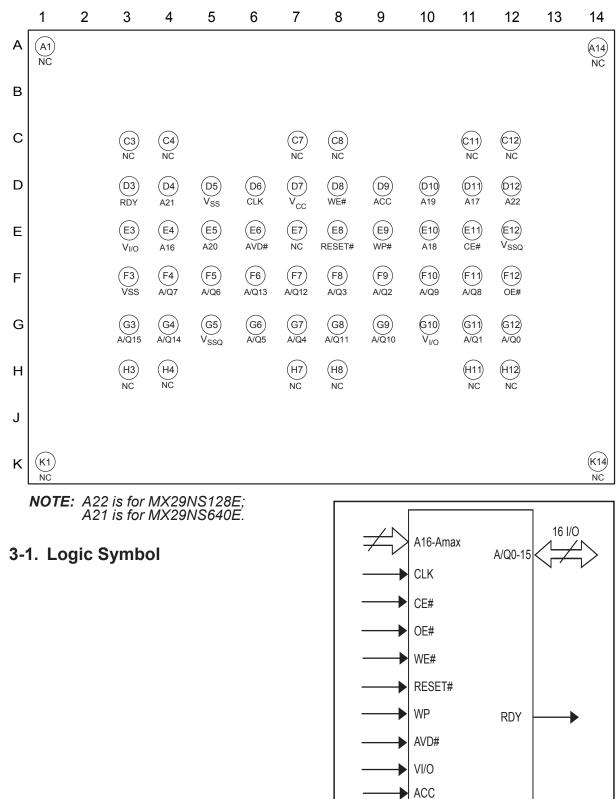

| 3. | PIN C                        | ONFIGURATION / SYMBOL DESCRIPTION                                                     | 10     |

|    | 3-1.<br>3-2.                 | Logic Symbol<br>Pin Descriptions                                                      |        |

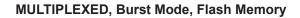

| 4. | BLOO                         | CK DIAGRAM                                                                            | 12     |

|    | 4-1.                         | Block Structure                                                                       | 13     |

|    |                              | Table 1-1. Sector Address Table (MX29NS320E)                                          | 13     |

|    |                              | Table 1-2. Sector Address Table (MX29NS640E)                                          | 14     |

|    |                              | Table 1-3. Sector Address Table (MX29NS128E)                                          | 16     |

| 5. | BUS                          | OPERATIONS                                                                            | 17     |

|    |                              | Table 2. Bus Operations                                                               | 17     |

|    | 5-1.                         | Non-Burst (Asynchronous) Read Operation                                               |        |

|    | 5-2.                         | Burst (Synchronous) Read Operation                                                    |        |

|    |                              | 5-2-1. Continuous Burst Read.                                                         |        |

|    |                              | Table 3-1. Address Latency for 10, 9 and 8 Dummy Cycles                               | 19     |

|    |                              | Table 3-2. Address Latency for 7, 6, and 5 Dummy Cycles                               | 19     |

|    |                              | Table 3-3. Address Latency for 4 Dummy Cycles                                         | 19     |

|    |                              | Table 3-4. Address Latency for 3 Dummy Cycles                                         | 19     |

|    |                              | Table 3-5. Address/8-word Boundary Crossing Latency for 10, 9 and 8 Dummy Cycles      | 19     |

|    |                              | Table 3-6. Address/128-word Boundary Crossing Latency for 7, 6, and 5 Dummy Cycles    | 20     |

|    |                              | Table 3-7. Address/128-word Boundary Crossing Latency for 4 Dummy Cycles              | 20     |

|    |                              | Table 3-8. Address/128-word Boundary Crossing Latency for 3 Dummy Cycles              | 20     |

|    |                              | 5-2-2. 8-, 16-Word Modes Linear Burst with Wrap Around                                | 20     |

|    |                              | Table 4. Burst Address Groups                                                         | 20     |

|    |                              | 5-2-3. Reading Memory Array                                                           | 21     |

|    | 5-3.                         | Set Configuration Register Command Sequence                                           | 21     |

|    |                              | 5-3-1. Programmable Dummy Cycle                                                       | 22     |

|    |                              | 5-3-2. Configurable Dummy Cycle                                                       |        |

|    |                              | 5-3-3. Burst Length Configuration                                                     | 22     |

|    |                              | Table 5. Configurable Dummy Cycles vs. Frequency                                      |        |

|    |                              | 5-3-4. Burst Wrap Around                                                              |        |

|    |                              | 5-3-5. Output Drive Strength                                                          | 23     |

| 5-4.  | Program Operation                                                     | 24 |

|-------|-----------------------------------------------------------------------|----|

|       | 5-4-1. Programming Commands/Command Sequences                         | 25 |

|       | 5-4-2. Accelerated Program and Erase Operations                       | 25 |

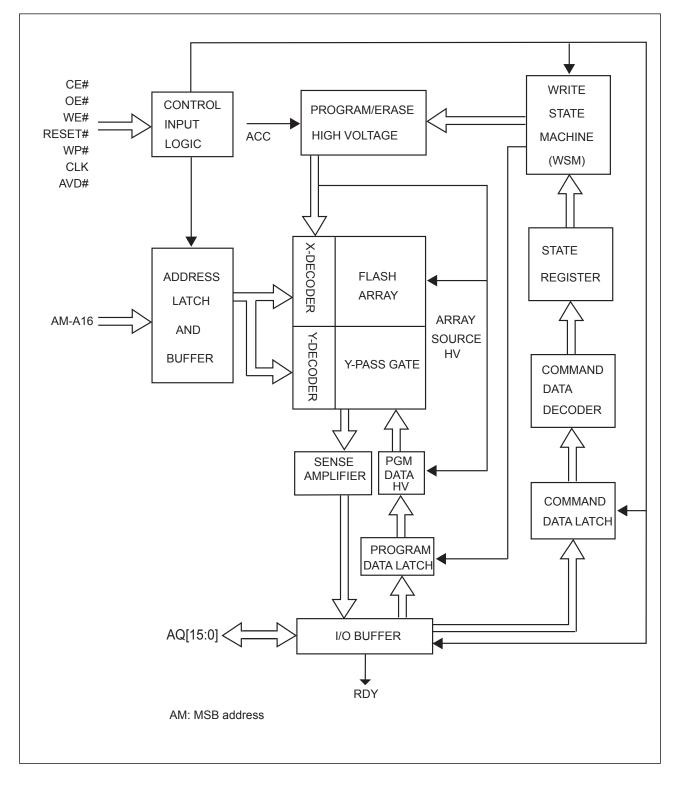

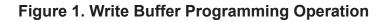

|       | 5-4-3. Write Buffer Programming Operation                             | 25 |

|       | 5-4-4. Write Buffer Programming Command Sequence                      | 26 |

|       | 5-4-5. Buffer Write Abort                                             | 26 |

|       | Table 6. Write Buffer Command Sequence                                | 26 |

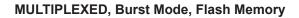

|       | Figure 1. Write Buffer Programming Operation                          | 27 |

|       | Figure 2. Status Polling For Write Buffer Program                     | 28 |

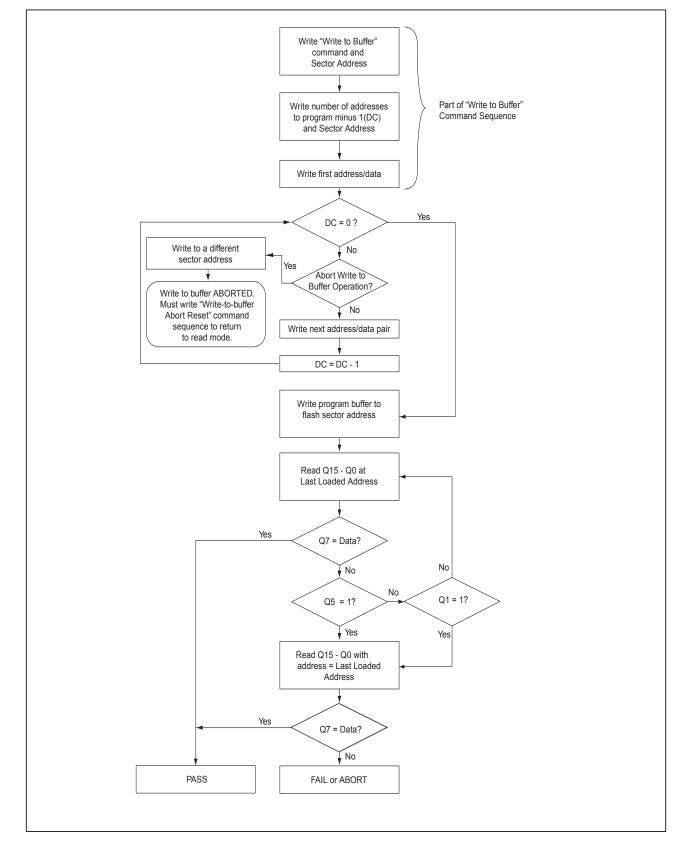

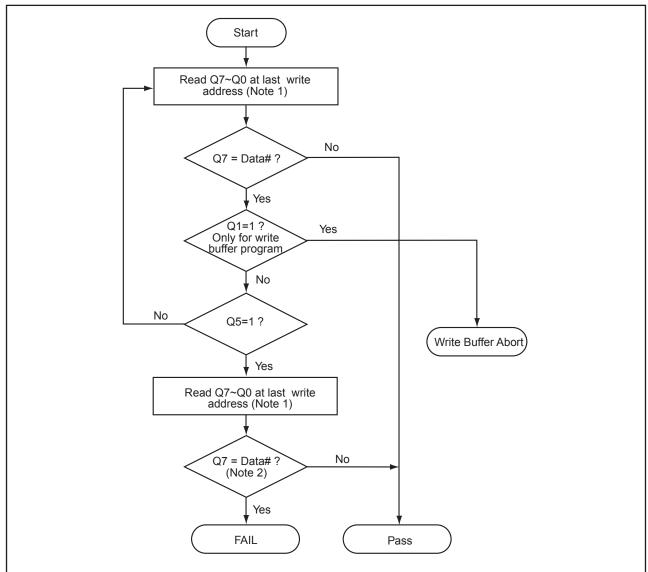

| 5-5.  | Erase Operation                                                       | 29 |

|       | 5-5-1. Sector Erase                                                   | 29 |

|       | 5-5-2. Chip Erase                                                     | 29 |

|       | 5-5-3. Sector Erase Command Sequence                                  |    |

|       | 5-5-4. Accelerated Sector Erase                                       |    |

|       | Figure 3. Erase Operation                                             | 31 |

| 5-6.  | Program/Erase Operation Status                                        | 32 |

|       | Table 7. Program Operation Status                                     | 32 |

| 5-7.  | Program/Erase Suspend/Resume                                          | 33 |

|       | 5-7-1. Program Suspend                                                | 33 |

|       | 5-7-2. Program Resume                                                 |    |

|       | 5-7-3. Program Suspend/Program Resume Commands                        |    |

|       | 5-7-4. Erase Suspend                                                  |    |

|       | 5-7-5. Sector Erase Resume                                            |    |

|       | Figure 4. Data# Polling Timing Waveforms (During Embedded Algorithms) |    |

|       | Figure 5. Data# Polling For Word Program/Erase                        |    |

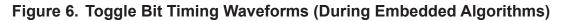

|       | Figure 6. Toggle Bit Timing Waveforms (During Embedded Algorithms)    |    |

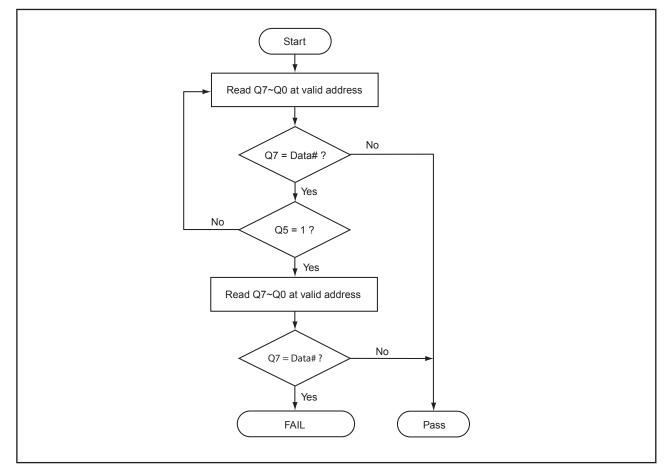

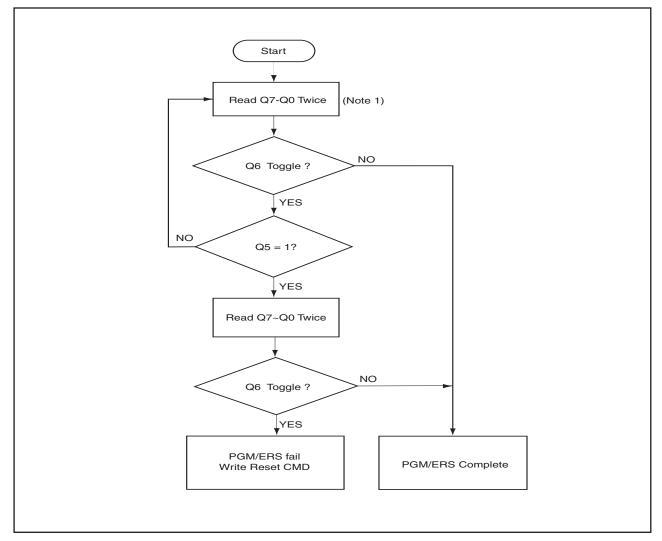

|       | Figure 7. Toggle Bit Algorithm                                        | 37 |

| 5-8.  | Configuration Register                                                | 38 |

|       | Table 8. Configuration Register                                       |    |

| 5-9.  | Enter/Exit Secured Silicon Sector Command Sequence                    |    |

|       | 5-9-1. Program Secured Silicon Sector Command Sequence                |    |

| 5-10. | Auto Select Operations                                                |    |

|       | 5-10-1. Auto Select Command Sequence                                  | 40 |

| 5-11. | Handshaking Feature                                                   |    |

|       | Table 9. Dummy Cycles for Handshaking                                 | 41 |

| 6. | SECURITY FEATURES |                                                                                      |    |  |

|----|-------------------|--------------------------------------------------------------------------------------|----|--|

|    | 6-1.              | Lock Register                                                                        | 42 |  |

|    |                   | 6-1-1. Lock Register Bits                                                            | 42 |  |

|    |                   | Table 10. Lock Register bits                                                         | 42 |  |

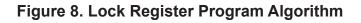

|    |                   | Figure 8. Lock Register Program Algorithm                                            | 43 |  |

|    |                   | 6-1-2. Dynamic Write Protection Bits (DPBS)                                          | 44 |  |

|    | 6-2.              | Hardware Data Protection Mode                                                        | 44 |  |

|    |                   | 6-2-1. Write Protect (WP#)                                                           |    |  |

|    |                   | 6-2-2. WP# Boot Sector Protection                                                    |    |  |

|    | 6-3.              | Security Sector Flash Memory Region                                                  |    |  |

|    |                   | 6-3-1. Factory Locked: Security Sector Programmed and Protected at the Factory       |    |  |

|    |                   | 6-3-2. Customer Lockable: Security Sector NOT Programmed or Protected at the Factory | 45 |  |

| 7. | СОМ               | MAND DEFINITIONS                                                                     | 46 |  |

| 8. | ENE               | RGY SAVING MODE                                                                      | 48 |  |

|    | 8-1.              | Standby Mode                                                                         | 48 |  |

|    | 8-2.              | Automatic Sleep Mode                                                                 |    |  |

|    |                   | Table 11. DC Characteristics                                                         | 49 |  |

|    | 8-3.              | Reset Commands                                                                       | 50 |  |

|    |                   | 8-3-1. Hardware Reset                                                                | 50 |  |

|    |                   | Table 12. Hardware Reset                                                             | 50 |  |

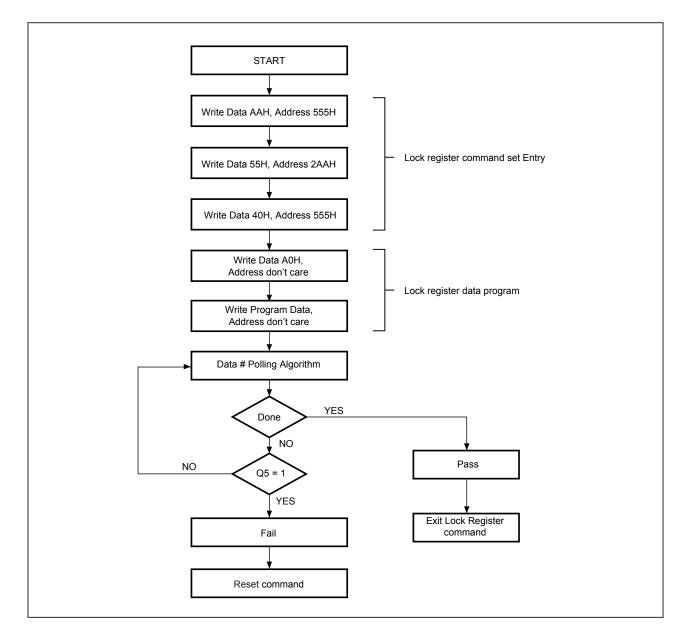

|    |                   | Figure 9. Reset Timings                                                              | 51 |  |

|    |                   | 8-3-2. Software Reset                                                                | 51 |  |

| 9. | СОМ               | MON FLASH MEMORY INTERFACE (CFI) MODE                                                | 52 |  |

|    |                   | Table 13-1. CFI Mode: Identification Data Values                                     |    |  |

|    |                   | Table 13-2. CFI Mode: System Interface Data Values                                   |    |  |

|    |                   | Table 13-3. CFI Mode: Device Geometry Data Values                                    | 53 |  |

|    |                   | Table 13-4. CFI Mode: Primary Vendor-Specific Extended Query Data Values             | 54 |  |

| 10 |                   | TRICAL CHARACTERISTICS                                                               |    |  |

|    |                   | Absolute Maximum Stress Ratings                                                      |    |  |

|    |                   | Operating Temperatures and Voltages                                                  |    |  |

|    | 10-3.             | Test Conditions                                                                      |    |  |

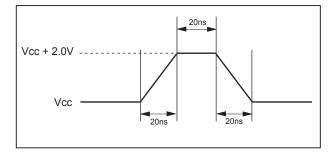

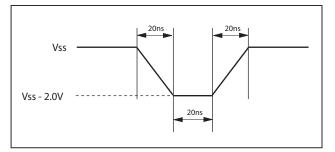

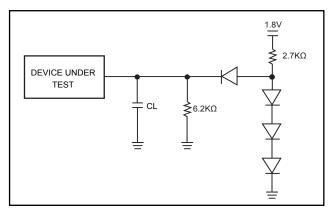

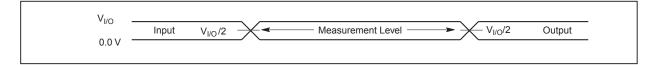

|    |                   | Figure 10. Test Setup                                                                |    |  |

|    |                   | Figure 11. Input Waveforms and Measurement Levels                                    |    |  |

| 10-4.    | AC Characteristics                                           | 57 |

|----------|--------------------------------------------------------------|----|

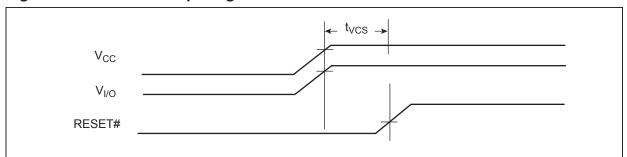

|          | Figure 12. VCC Power-up Diagram CLK Characterization         | 57 |

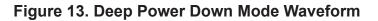

|          | Figure 13. Deep Power Down Mode Waveform                     | 58 |

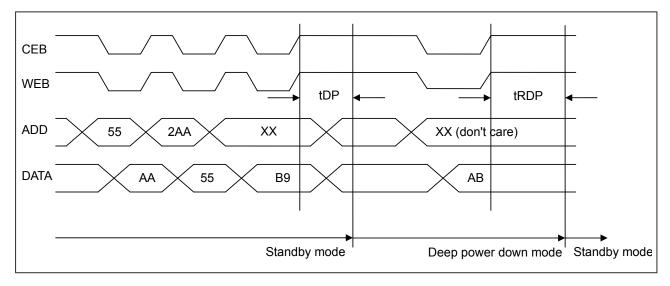

|          | Figure 14. CLK Characterization                              | 58 |

|          | Table 15. Synchronous / Burst Read                           | 59 |

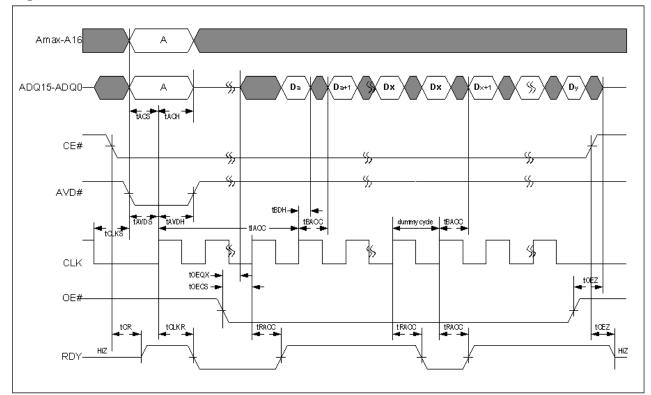

|          | Figure 15. Burst Mode Read                                   | 59 |

|          | Table 16. Asynchronous Read                                  | 60 |

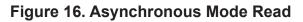

|          | Figure 16. Asynchronous Mode Read                            | 60 |

|          | Table 17. Erase/Program Operations                           | 61 |

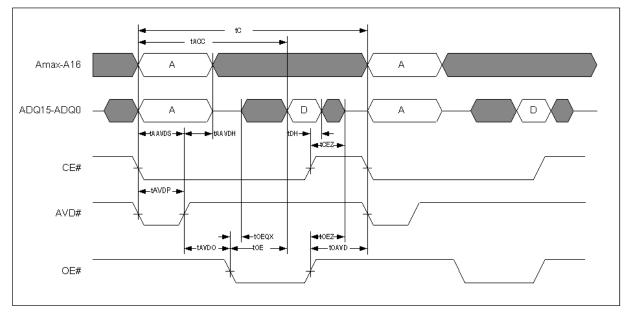

|          | Figure 17. Program Operation Timings                         | 62 |

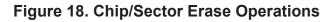

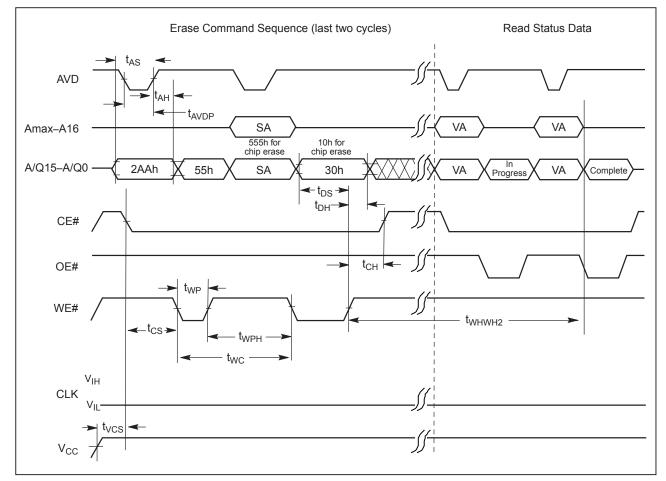

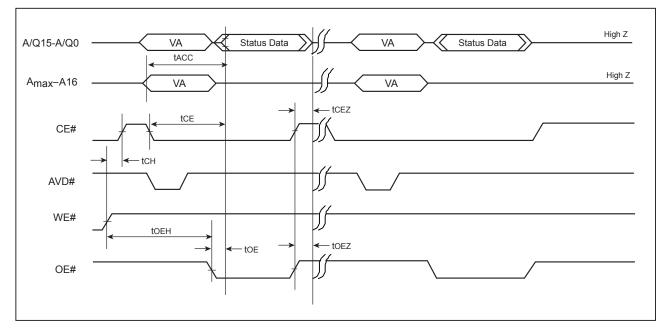

|          | Figure 18. Chip/Sector Erase Operations                      | 63 |

|          | Figure 19. Data# Polling Timings (During Embedded Algorithm) | 64 |

|          | Figure 20. Toggle Bit Timings (During Embedded Algorithm)    | 64 |

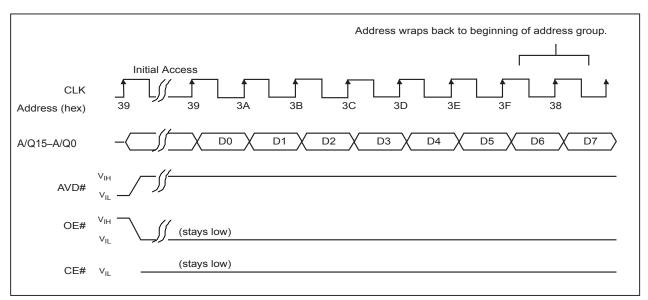

|          | Figure 21. 8-, 16-Word Linear Burst Address Wrap Around      | 65 |

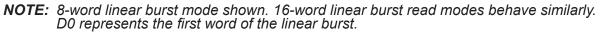

|          | Figure 22. Latency with Boundary Crossing                    | 65 |

| 10-5.    | Erase and Programming Performance                            | 66 |

|          | 10-5-1. BGA Ball Capacitance                                 | 67 |

| 10-6.    | Low VCC Write Prohibit                                       | 67 |

|          | 10-6-1. Write Pulse "Glitch" Protection                      | 67 |

|          | 10-6-2. Logical Prohibit                                     | 67 |

|          | 10-6-3. Power-up Sequence                                    | 67 |

|          | 10-6-4. Power-up Write Prohibit                              | 67 |

|          | 10-6-5. Power Supply Decoupling                              | 67 |

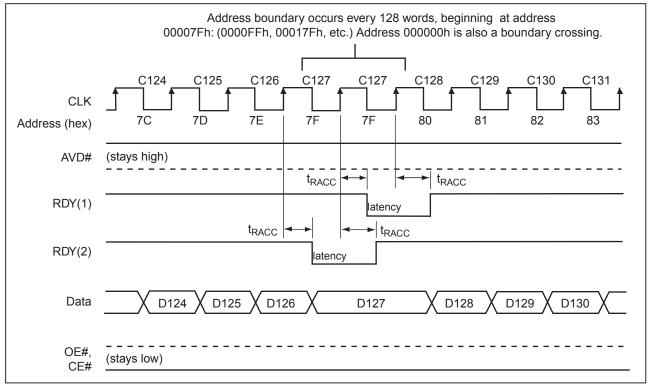

| 11. PAC  |                                                              | 68 |

| 12 DE\/I | SION HISTORY                                                 | 60 |

|          |                                                              |    |

## 128/64/32M-BIT [8/4/2M x16-bit] CMOS 1.8 Volt-only, Multiplexed Flash Memory

## 1. FEATURES

## **Characteristics**

#### **Burst Length**

- Continuous linear burst

- 8/16 word linear burst length with wrap around

#### **Sector Architecture**

- Single bank Architecture.

- Four 8 Kword sectors in upper-most address range (MX29NS320E/640E)

- Four 16Kword sectors in upper-most address range (MX29NS128E)

- MX29NS320E: Sixty-three 32 KWord

- MX29NS640E: One hundred twentyseven 32 Kword sectors

- MX29NS128E: One hundred twenty seven 64 Kword sectors

#### **Power Supply Operations**

- 1.8V for read, program and erase operations (1.70V to 1.95V)

- Deep power down mode

## Performance

#### **High Performance**

- 40 µs Word programming time

- 9.4 µs Effective word programming time utilizing a 32 word Write Buffer at VCC level

- 4.8 µs Effective word programming time of utilizing a 32 word Write Buffer at ACC level

#### Sector Erase Time

- 600 ms for 32 Kword sectors

- 800 ms for 64 Kword sectors

#### VI/O Feature

- Generates data output voltages and tolerates data input voltages as determined by the voltage on the VI/O pin

- 1.8V compatible I/O signals

#### **Read Access Time**

- Burst access times: 7 ns (at industrial temperature range)

- 80 ns of Asynchronous random access times

- 80 ns of Synchronous random access times

#### **Secured Silicon Sector Region**

- 256 words accessible through a command sequence

- 128 words for the factory secured silicon sector

- 128 words for the customer secured silicon sector

#### **Power Dissipation**

• Typical values: 8 bits switching,

CL = 10 pF at 108 MHz, CIN excluded

- 32 mA for Continuous burst read mode

- 20 mA for Program/Erase Operations

- 40 uA for Standby mode

#### **Program/Erase Cycles**

• 100,000 cycles typical

#### **Data Retention**

20 years

## Hardware Features

- Supports multiplexing data and address for reduced I/O count.

- A15–A0 multiplexed as Q15–Q0 Sector Architecture

#### Hardware Sector Protection

- WP# protects two highest sectors

- All sectors locked when ACC = VIL

#### Package

- 56-Ball Thin FBGA (Fine-Pitch Ball Grid Array)

- REACH SVHC Free and RoHS Compliant

#### Handshaking Feature

Allows system to determine the read operation of burst data with minimum possible latency by monitoring RDY.

#### Data# Polling and Toggle Bits

• Provides a software method of detecting and sending signals to indicate the completion of program and erase operations.

#### Erase Suspend/Erase Resume

• Erase operation will be halted when the device receives an Erase Suspend command. And will be restarted when the device receives the Erase Resume command.

#### Program Suspend/Program Resume

• Program operation will be halted when the device receives a Program Suspend command. It will be restarted when the device receives the Program Resume command.

#### **Electronic Identification**

- Software command set compatible with JEDEC 42.4 standards

- Common Flash Interface (CFI) supported

## Software Features

#### Advanced Security Features

- Volatile Sector Protection

- A command sector protection method that protects individual sectors from being programmed or erased.

- Sectors can be locked or unlocked insystem at VCC level.

## 2. GENERAL INFORMATION

## 2-1. Operating Speeds

| Clock Speed | Burst Access | Synch. Initial | Asynch. Initial | Output  |

|-------------|--------------|----------------|-----------------|---------|

|             | (ns)         | Access (ns)    | Access (ns)     | Loading |

| 108 MHz     | 7            | 80             | 80              | 10 pF   |

The operating temperature range is -40°C to +85°C.

## 2-2. Ordering Information

| Part Number                                                   | Access Time (ns) | Package  | Remark   |

|---------------------------------------------------------------|------------------|----------|----------|

| MX29NS320E XJI-80G<br>MX29NS640E XJI-80G<br>MX29NS128EXJI-80G | 80               | 56 TFBGA | VI/O=VCC |

#### NOTES:

- 1. MX29NS320/640/128E have been pre-released and in mass production.

- 2. MX29NS128E is for the validation of MCP products. Please contact Macronix local sales for discrete product support.

## 3. PIN CONFIGURATION / SYMBOL DESCRIPTION

56-Ball Thin FBGA

VSSQ

## 3-2. Pin Descriptions

| SYMBOL  | DESCRIPTIONS                                                                                                                                                                    |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| A22-A16 | Address Inputs for MX29NS128E                                                                                                                                                   |  |  |

| A21-A16 | Address Inputs for MX29NS640E                                                                                                                                                   |  |  |

| A20-A16 | Address Inputs for MX29NS320E                                                                                                                                                   |  |  |

| A/Q15~  | Multiplexed Data Inputs/Outputs                                                                                                                                                 |  |  |

| A/Q0    | Chin Enchla Innut                                                                                                                                                               |  |  |

| CE#     | Chip Enable Input                                                                                                                                                               |  |  |

| OE#     | Output Enable Input                                                                                                                                                             |  |  |

| WE#     | Write Enable Input                                                                                                                                                              |  |  |

| VCC     | Device Power Supply (1.70V~1.95V)                                                                                                                                               |  |  |

| VI/O    | Input/Output Power Supply (1.70V~1.95V)                                                                                                                                         |  |  |

| VSS     | Device Ground                                                                                                                                                                   |  |  |

| VSSQ    | Input/Output Ground                                                                                                                                                             |  |  |

| NC      | No Connection                                                                                                                                                                   |  |  |

| RDY     | Ready output, the status of the Burst Read                                                                                                                                      |  |  |

|         | Refer to configuration register table                                                                                                                                           |  |  |

| CLK     | The first rising edge of CLK in conjunction with AVD# low latches address input<br>and activates burst mode operation.                                                          |  |  |

| AVD#    | Address Valid input. Indicates to device that the valid address is present on the address inputs (Address bits A15–A0 are multiplexed, address bits Amax–A16 are address only). |  |  |

| AVD#    | VIL= For asynchronous mode, indicates valid address; for burst mode, causes starting address to be latched on rising edge of CLK.                                               |  |  |

|         | VIH = Device ignores address inputs                                                                                                                                             |  |  |

| RESET#  | Hardware Reset Pin, Active Low                                                                                                                                                  |  |  |

| WP#     | Hardware Write Protect                                                                                                                                                          |  |  |

| ACC     | Programming Acceleration Input                                                                                                                                                  |  |  |

#### NOTES:

- 1. WP# and ACC have internal pull up. WP# VIL protects the upper most two sectors from write; ACC=Vhv enters into the ACC programming mode. ACC=VIL, erase/program function disabled.

- 2. VI/O Voltage must tight up with VCC.

*VI/O* = *VCC* = 1.70V~1.95V

## 4. BLOCK DIAGRAM

## 4-1. Block Structure

The main flash memory array is organized as Word mode (x16). The details of the address ranges and the corresponding sector addresses are shown in Table 1.

| Sector Size |              |                                    |

|-------------|--------------|------------------------------------|

| Kwords      | Sector       | Address Range                      |

| 32          | SA0          | 000000h-007FFFh                    |

| 32          | SA1          | 008000h-00FFFFh                    |

| 32          | SA2          | 010000h-017FFFh                    |

| 32          | SA3          | 018000h-01FFFFh                    |

| 32          | SA4          | 020000h-027FFFh                    |

| 32          | SA5          | 028000h-02FFFFh                    |

| 32          | SA6          | 030000h-037FFFh                    |

| 32          | SA7          | 038000h-03FFFFh                    |

| 32          | SA8          | 040000h-047FFFh                    |

| 32          | SA9          | 048000h-04FFFFh                    |

| 32          | SA10         | 050000h-057FFFh                    |

| 32          | SA11         | 058000h-05FFFFh                    |

| 32          | SA12         | 060000h-067FFFh                    |

| 32          | SA13         | 068000h-06FFFFh                    |

| 32          | SA14         | 070000h-077FFFh                    |

| 32          | SA14<br>SA15 | 078000h-07FFFFh                    |

| -           |              | 080000h-087FFFh                    |

| 32          | SA16         | 088000h-08FFFFh                    |

| 32          | SA17         |                                    |

| 32          | SA18         | 090000h-097FFFh                    |

| 32          | SA19         | 098000h-09FFFFh                    |

| 32          | SA20         | 0A0000h-0A7FFFh                    |

| 32          | SA21         | 0A8000h-0AFFFFh                    |

| 32          | SA22         | 0B0000h-0B7FFFh                    |

| 32          | SA23         | 0B8000h-0BFFFFh                    |

| 32          | SA24         | 0C0000h-0C7FFFh                    |

| 32          | SA25         | 0C8000h-0CFFFFh                    |

| 32          | SA26         | 0D0000h-0D7FFFh                    |

| 32          | SA27         | 0D8000h-0DFFFFh                    |

| 32          | SA28         | 0E0000h-0E7FFh                     |

| 32<br>32    | SA29         | 0E8000h-0EFFFFh                    |

| 32          | SA30<br>SA31 | 0F0000h-0F7FFFh<br>0F8000h-0FFFFFh |

| 32          | SA32         | 100000h-107FFFh                    |

| 32          | SA33         | 108000h-10FFFFh                    |

| 32          | SA34         | 110000h-117FFFh                    |

| 32          | SA35         | 118000h-11FFFFh                    |

| 32          | SA36         | 120000h-127FFFh                    |

| 32          | SA37         | 128000h-12FFFFh                    |

| 32          | SA38         | 130000h-137FFFh                    |

| 32          | SA39         | 138000h-13FFFFh                    |

| 32          | SA40         | 140000h-147FFFh                    |

### Table 1-1. Sector Address Table (MX29NS320E)

| Sector Size | Sector | Addross Panac   |  |

|-------------|--------|-----------------|--|

| Kwords      | Sector | Address Range   |  |

| 32          | SA41   | 148000h-14FFFFh |  |

| 32          | SA42   | 150000h-157FFFh |  |

| 32          | SA43   | 158000h-15FFFFh |  |

| 32          | SA44   | 160000h-167FFFh |  |

| 32          | SA45   | 168000h-16FFFFh |  |

| 32          | SA46   | 170000h-177FFFh |  |

| 32          | SA47   | 178000h-17FFFFh |  |

| 32          | SA48   | 180000h-187FFFh |  |

| 32          | SA49   | 188000h-18FFFFh |  |

| 32          | SA50   | 190000h-197FFFh |  |

| 32          | SA51   | 198000h-19FFFFh |  |

| 32          | SA52   | 1A0000h-1A7FFFh |  |

| 32          | SA53   | 1A8000h-1AFFFFh |  |

| 32          | SA54   | 1B0000h-1B7FFFh |  |

| 32          | SA55   | 1B8000h-1BFFFFh |  |

| 32          | SA56   | 1C0000h-1C7FFFh |  |

| 32          | SA57   | 1C8000h-1CFFFFh |  |

| 32          | SA58   | 1D0000h-1D7FFFh |  |

| 32          | SA59   | 1D8000h-1DFFFFh |  |

| 32          | SA60   | 1E0000h-1E7FFFh |  |

| 32          | SA61   | 1E8000h-1EFFFFh |  |

| 32          | SA62   | 1F0000h-1F7FFFh |  |

| 8           | SA63   | 1F8000h-1F9FFFh |  |

| 8           | SA64   | 1FA000h-1FBFFFh |  |

| 8           | SA65   | 1FC000h-1FDFFFh |  |

| 8           | SA66   | 1FE000h-1FFFFFh |  |

| Sector Size | Sector       | Addrose Dense                      |

|-------------|--------------|------------------------------------|

| Kwords      | Sector       | Address Range                      |

| 32          | SA0          | 000000h-007FFFh                    |

| 32          | SA1          | 008000h-00FFFFh                    |

| 32          | SA2          | 010000h-017FFFh                    |

| 32          | SA3          | 018000h-01FFFFh                    |

| 32          | SA4          | 020000h-027FFFh                    |

| 32          | SA5          | 028000h-02FFFFh                    |

| 32          | SA6          | 030000h-037FFFh                    |

| 32          | SA7          | 038000h-03FFFFh                    |

| 32          | SA8          | 040000h-047FFFh                    |

| 32          | SA9          | 048000h-04FFFFh                    |

| 32          | SA10         | 050000h-057FFFh                    |

| 32          | SA11         | 058000h-05FFFFh                    |

| 32          | SA12         | 060000h-067FFFh                    |

| 32          | SA13         | 068000h-06FFFFh                    |

| 32          | SA14         | 070000h-077FFFh                    |

| 32          | SA15         | 078000h-07FFFFh                    |

| 32          | SA16         | 080000h-087FFFh                    |

| 32          | SA17         | 088000h-08FFFFh                    |

| 32          | SA17<br>SA18 | 090000h-097FFFh                    |

| -           |              | 098000h-09FFFFh                    |

| 32          | SA19         | 040000h-047FFFh                    |

| 32          | SA20         | 0A8000h-0AFFFh                     |

| 32          | SA21         |                                    |

| 32          | SA22         | 0B0000h-0B7FFFh                    |

| 32          | SA23         | 0B8000h-0BFFFFh                    |

| 32          | SA24         | 0C0000h-0C7FFFh                    |

| 32          | SA25         | 0C8000h-0CFFFFh                    |

| 32          | SA26         | 0D0000h-0D7FFFh                    |

| 32<br>32    | SA27         | 0D8000h-0DFFFFh                    |

| 32          | SA28<br>SA29 | 0E0000h-0E7FFFh<br>0E8000h-0EFFFFh |

| 32          | SA30         | 0F0000h-0F7FFFh                    |

| 32          | SA31         | 0F8000h-0FFFFFh                    |

| 32          | SA32         | 100000h-107FFFh                    |

| 32          | SA33         | 108000h-10FFFFh                    |

| 32          | SA34         | 110000h-117FFFh                    |

| 32          | SA35         | 118000h-11FFFFh                    |

| 32          | SA36         | 120000h-127FFFh                    |

| 32          | SA37         | 128000h-12FFFFh                    |

| 32          | SA38         | 130000h-137FFFh                    |

| 32          | SA39         | 138000h-13FFFFh                    |

| 32          | SA40         | 140000h-147FFFh                    |

| 32          | SA41         | 148000h-14FFFFh                    |

| 32          | SA42         | 150000h-157FFFh                    |

| 32          | SA43         | 158000h-15FFFFh                    |

| 32          | SA44         | 160000h-167FFFh                    |

| 32          | SA45         | 168000h-16FFFFh                    |

## Table 1-2. Sector Address Table (MX29NS640E)

| 40E)<br>Sector Size |              |                                   |

|---------------------|--------------|-----------------------------------|

| Kwords              | Sector       | Address Range                     |

| 32                  | SA47         | 178000h-17FFFFh                   |

| 32                  | SA48         | 180000h-187FFFh                   |

| 32                  | SA49         | 188000h-18FFFFh                   |

| 32                  | SA50         | 190000h-197FFFh                   |

| 32                  | SA51         | 198000h-19FFFFh                   |

| 32                  | SA52         | 1A0000h-1A7FFFh                   |

| 32                  | SA53         | 1A8000h-1AFFFFh                   |

| 32                  | SA54         | 1B0000h-1B7FFFh                   |

| 32                  | SA55         | 1B8000h-1BFFFFh                   |

| 32                  | SA56         | 1C0000h-1C7FFFh                   |

| 32                  | SA57         | 1C8000h-1CFFFFh                   |

| 32                  | SA58         | 1D0000h-1D7FFFh                   |

| _                   | SA59         | 1D8000h-1DFFFFh                   |

| 32                  | SA60         | 1E0000h-1E7FFFh                   |

| 32                  | SA60<br>SA61 |                                   |

| 32                  |              | 1E8000h-1EFFFh                    |

| 32                  | SA62         | 1F0000h-1F7FFFh                   |

| 32                  | SA63         | 1F8000h-1FFFFFh                   |

| 32                  | SA64         | 200000h-207FFFh                   |

| 32                  | SA65         | 208000h-20FFFFh                   |

| 32                  | SA66         | 210000h-217FFFh                   |

| 32                  | SA67         | 218000h-21FFFFh                   |

| 32                  | SA68         | 220000h-227FFFh                   |

| 32                  | SA69         | 228000h-22FFFFh                   |

| 32                  | SA70         | 230000h-237FFFh                   |

| 32                  | SA71         | 238000h-23FFFFh                   |

| 32                  | SA72         | 240000h-247FFFh                   |

| 32                  | SA73         | 248000h-24FFFFh                   |

| 32                  | SA74         | 250000h-257FFFh                   |

| 32                  | SA75         | 258000h-25FFFFh                   |

| 32                  | SA76         | 260000h-267FFh                    |

| 32<br>32            | SA77<br>SA78 | 268000h-26FFFh<br>270000h-277FFFh |

| 32                  | SA79         | 278000h-2F7FFFh                   |

| 32                  | SA80         | 280000h-287FFFh                   |

| 32                  | SA81         | 288000h-28FFFFh                   |

| 32                  | SA82         | 290000h-297FFFh                   |

| 32                  | SA83         | 298000h-29FFFFh                   |

| 32                  | SA84         | 2A0000h-2A7FFFh                   |

| 32                  | SA85         | 2A8000h-2AFFFFh                   |

| 32                  | SA86         | 2B0000h-2B7FFFh                   |

| 32                  | SA87         | 2B8000h-2BFFFFh                   |

| 32                  | SA88         | 2C0000h-2C7FFFh                   |

| 32                  | SA89         | 2C8000h-2CFFFFh                   |

| 32                  | SA90         | 2D0000h-2D7FFFh                   |

| 32                  | SA91         | 2D8000h-2DFFFFh                   |

| 32                  | SA92         | 2E0000h-2E7FFFh                   |

| Sector Size |        |                 |

|-------------|--------|-----------------|

| Kwords      | Sector | Address Range   |

| 32          | SA93   | 2E8000h-2EFFFFh |

| 32          | SA94   | 2F0000h-2F7FFFh |

| 32          | SA95   | 2F8000h-2FFFFFh |

| 32          | SA96   | 300000h-307FFFh |

| 32          | SA97   | 308000h-30FFFFh |

| 32          | SA98   | 310000h-317FFFh |

| 32          | SA99   | 318000h-31FFFFh |

| 32          | SA100  | 320000h-327FFFh |

| 32          | SA101  | 328000h-32FFFFh |

| 32          | SA102  | 330000h-337FFFh |

| 32          | SA103  | 338000h-33FFFFh |

| 32          | SA104  | 340000h-347FFFh |

| 32          | SA105  | 348000h-34FFFFh |

| 32          | SA106  | 350000h-357FFFh |

| 32          | SA107  | 358000h-35FFFFh |

| 32          | SA108  | 360000h-367FFFh |

| 32          | SA109  | 368000h-36FFFFh |

| 32          | SA110  | 370000h-377FFFh |

| 32          | SA111  | 378000h-37FFFFh |

| 32          | SA112  | 380000h-387FFFh |

| 32          | SA113  | 388000h-38FFFFh |

| 32          | SA114  | 390000h-397FFFh |

| 32          | SA115  | 398000h-39FFFFh |

| 32          | SA116  | 3A0000h-3A7FFFh |

| 32          | SA117  | 3A8000h-3AFFFFh |

| 32          | SA118  | 3B0000h-3B7FFFh |

| 32          | SA119  | 3B8000h-3BFFFFh |

| 32          | SA120  | 3C0000h-3C7FFFh |

| 32          | SA121  | 3C8000h-3CFFFFh |

| 32          | SA122  | 3D0000h-3D7FFFh |

| 32          | SA123  | 3D8000h-3DFFFFh |

| 32          | SA124  | 3E0000h-3E7FFFh |

| 32          | SA125  | 3E8000h-3EFFFFh |

| 32          | SA126  | 3F0000h-3F7FFFh |

| 8           | SA127  | 3F8000h-3F9FFFh |

| 8           | SA128  | 3FA000h-3FBFFFh |

| 8           | SA129  | 3FC000h-3FDFFFh |

| 8           | SA130  | 3FE000h-3FFFFFh |

## Table 1-3. Sector Address Table (MX29NS128E)

| Sector Size<br>Kwords<br>64<br>64<br>64 | Sector | Address Range   | Sector Size | Contor |                 | Sector Size |                |                                    |

|-----------------------------------------|--------|-----------------|-------------|--------|-----------------|-------------|----------------|------------------------------------|

| 64                                      | 0.1.0  |                 | Kwords      | Sector | Address Range   | Kwords      | Sector         | Address Range                      |

| }                                       | SA0    | 000000h-00FFFFh | 64          | SA42   | 2A0000h-2AFFFFh | 64          | SA85           | 550000h-55FFFFh                    |

| 64                                      | SA1    | 010000h-01FFFFh | 64          | SA43   | 2B0000h-2BFFFFh | 64          | SA86           | 560000h-56FFFFh                    |

|                                         | SA2    | 020000h-02FFFFh | 64          | SA44   | 2C0000h-2CFFFFh | 64          | SA87           | 570000h-57FFFFh                    |

| 64                                      | SA3    | 030000h-03FFFFh | 64          | SA45   | 2D0000h-2DFFFFh | 64          | SA88           | 580000h-58FFFFh                    |

| 64                                      | SA4    | 040000h-04FFFFh | 64          | SA46   | 2E0000h-2EFFFFh | 64          | SA89           | 590000h-59FFFFh                    |

| 64                                      | SA5    | 050000h-05FFFFh | 64          | SA47   | 2F0000h-2FFFFFh | 64          | SA90           | 5A0000h-5AFFFFh                    |

| 64                                      | SA6    | 060000h-06FFFFh | 64          | SA48   | 300000h-30FFFFh | 64          | SA91           | 5B0000h-5BFFFFh                    |

|                                         |        |                 | 64          | SA49   | 310000h-31FFFFh | 64          | SA92           | 5C0000h-5CFFFFh                    |

| 64                                      | SA7    | 070000h-07FFFFh | 64          | SA50   | 320000h-32FFFFh | 64          | SA93           | 5D0000h-5DFFFFh                    |

| 64                                      | SA8    | 080000h-08FFFFh |             |        |                 | 64          | SA94           | 5E0000h-5EFFFFh                    |

| 64                                      | SA9    | 090000h-09FFFFh | 64          | SA51   | 330000h-33FFFFh | 64          | SA95           | 5F0000h-5FFFFFh                    |

| 64                                      | SA10   | 0A0000h-0AFFFFh | 64          | SA52   | 340000h-34FFFFh | 64          | SA96           | 600000h-60FFFFh                    |

| 64                                      | SA11   | 0B0000h-0BFFFFh | 64          | SA53   | 350000h-35FFFFh | 64          | SA97           | 610000h-61FFFh                     |

| 64                                      | SA12   | 0C0000h-0CFFFFh | 64          | SA54   | 360000h-36FFFFh | 64          | SA98           | 620000h-62FFFFh                    |

|                                         | SA13   | 0D0000h-0DFFFFh | 64          | SA55   | 370000h-37FFFFh | 64          | SA99           | 630000h-63FFFFh                    |

|                                         |        |                 | 64          | SA56   | 380000h-38FFFFh | 64          | SA100          | 640000h-64FFFFh                    |

| -                                       | SA14   | 0E0000h-0EFFFFh | 64          | SA57   | 390000h-39FFFFh | 64          | SA101          | 650000h-65FFFFh                    |

| 64                                      | SA15   | 0F0000h-0FFFFh  | 64          | SA58   | 3A0000h-3AFFFFh | 64          | SA102          | 660000h-66FFFFh                    |

| 64                                      | SA16   | 100000h-10FFFFh | 64          | SA59   | 3B0000h-3BFFFFh | 64          | SA103          | 670000h-67FFFFh                    |

| 64                                      | SA17   | 110000h-11FFFFh | 64          | SA60   | 3C0000h-3CFFFFh | 64          | SA104          | 680000h-68FFFFh                    |

| 64                                      | SA18   | 120000h-12FFFFh | 64          | SA61   | 3D0000h-3DFFFFh | 64          | SA105          | 690000h-69FFFh                     |

| 64                                      | SA19   | 130000h-13FFFFh | 64          | SA62   | 3E0000h-3EFFFFh | 64          | SA106          | 6A0000h-6AFFFh                     |

| 64                                      | SA20   | 140000h-14FFFFh | 64          | SA63   | 3F0000h-3FFFFFh | 64          | SA107          | 6B0000h-6BFFFFh                    |

|                                         |        |                 | 64          | SA64   | 400000h-40FFFFh | 64<br>64    | SA108<br>SA109 | 6C0000h-6CFFFFh                    |

| -                                       | SA21   | 150000h-15FFFFh | 64          | SA65   | 410000h-41FFFFh | 64          | SA109<br>SA110 | 6D0000h-6DFFFFh<br>6E0000h-6EFFFFh |

| 64                                      | SA22   | 160000h-16FFFFh | 64          | SA66   | 420000h-42FFFFh | 64          | SA110<br>SA111 | 6F0000h-6FFFFh                     |

| 64                                      | SA23   | 170000h-17FFFFh | 64          | SA67   | 430000h-43FFFFh | 64          | SA112          | 700000h-70FFFFh                    |

| 64                                      | SA24   | 180000h-18FFFFh | 64          | SA68   | 440000h-44FFFFh | 64          | SA113          | 710000h-71FFFFh                    |

| 64                                      | SA25   | 190000h-19FFFFh | 64          | SA69   |                 | 64          | SA114          | 720000h-72FFFFh                    |

| 64                                      | SA26   | 1A0000h-1AFFFFh |             |        | 450000h-45FFFFh | 64          | SA115          | 730000h-73FFFFh                    |

| 64                                      | SA27   | 1B0000h-1BFFFFh | 64          | SA70   | 460000h-46FFFFh | 64          | SA116          | 740000h-74FFFFh                    |

| 64                                      | SA28   | 1C0000h-1CFFFFh | 64          | SA71   | 470000h-47FFFFh | 64          | SA117          | 750000h-75FFFFh                    |

| 64                                      | SA29   | 1D0000h-1DFFFFh | 64          | SA72   | 480000h-48FFFFh | 64          | SA118          | 760000h-76FFFh                     |

| 64                                      | SA30   | 1E0000h-1EFFFFh | 64          | SA73   | 490000h-49FFFFh | 64          | SA119          | 770000h-77FFFFh                    |

| 64                                      | SA31   | 1F0000h-1FFFFFh | 64          | SA74   | 4A0000h-4AFFFFh | 64          | SA120          | 780000h-78FFFFh                    |

| 64                                      | SA32   | 200000h-20FFFFh | 64          | SA75   | 4B0000h-4BFFFFh | 64          | SA121          | 790000h-79FFFFh                    |

| 64                                      | SA33   | 210000h-21FFFFh | 64          | SA76   | 4C0000h-4CFFFFh | 64          | SA122          | 7A0000h-7AFFFFh                    |

| <b>├</b> ─── <b>├</b>                   | SA34   | 220000h-22FFFFh | 64          | SA77   | 4D0000h-4DFFFFh | 64          | SA123          | 7B0000h-7BFFFFh                    |

| }                                       | SA35   | 230000h-23FFFFh | 64          | SA78   | 4E0000h-4EFFFFh | 64          | SA124          | 7C0000h-7CFFFh                     |

|                                         | SA36   | 240000h-24FFFFh | 64          | SA79   | 4F0000h-4FFFFFh | 64          | SA125          | 7D0000h-7DFFFFh                    |

| 64                                      | SA37   | 250000h-25FFFFh | 64          | SA80   | 500000h-50FFFFh | 64          | SA126          | 7E0000h-7EFFFFh                    |

| 64                                      | SA38   | 260000h-26FFFFh | 64          | SA81   | 510000h-51FFFFh | 16          | SA127          | 7F0000h-7F3FFFh                    |

| 64                                      | SA39   | 270000h-27FFFFh | 64          | SA82   | 520000h-52FFFFh | 16          | SA128          | 7F4000h-7F7FFFh                    |

| 64                                      | SA40   | 280000h-28FFFFh | 64          | SA83   | 530000h-53FFFFh | 16          | SA129          | 7F8000h-7FBFFFh                    |

| 64                                      | SA41   | 290000h-29FFFFh | 64          | SA84   | 540000h-54FFFFh | 16          | SA130          | 7FC000h-7FFFFFh                    |

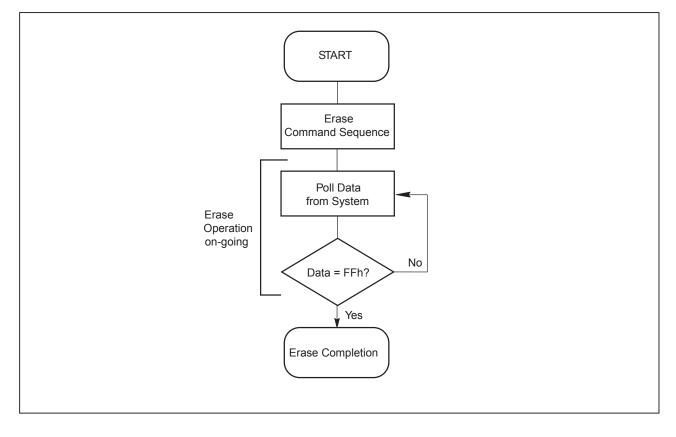

## 5. BUS OPERATIONS

This chapter indicates the functions and utilizations of Bus Operations. Bus operations are initiated through the internal command register and executed by a bus interface or similar logic circuitry. The command register itself does not occupy any memory addresses. The register is formed of latches that store the commands, along with the address and data information needed for executing the command.

The content of the register acts as inputs to the internal state machine. The state machine outputs determine the function of the device.

**Table 2.** shows all the bus operations, inputs and control levels required, and the resulting output.

All the operations are described in the following sections in details.

**NOTE**: Falling edge of AVD# determines when to disable the current burst cycle while a new burst read cycle is started by the rising edge of CLK.

| Operation                                                            | CE# | OE#    | WE#    | CLK    | AVD#  | Address | Data              | RDY   | RESET# |

|----------------------------------------------------------------------|-----|--------|--------|--------|-------|---------|-------------------|-------|--------|

|                                                                      | Syı | nchror | nous ( | Operat | ions  |         |                   |       |        |

| Latch Starting Burst Address by CLK                                  | L   | н      | Н      | R      | L     | Addr In | Output<br>Invalid | X     | Н      |

| Advance Burst Read to Next Address                                   | L   | L      | Н      | R      | Н     | Х       | Output<br>Valid   | н     | Н      |

| Terminate Current Burst Read Cycle                                   | н   | х      | х      | х      | Х     | Х       | HighZ             | HighZ | н      |

| Terminate Current Burst Read Cycle through RESET#                    | х   | х      | Х      | х      | Х     | х       | HighZ             | HighZ | L      |

| Terminate Current Burst Read Cycle<br>and Start New Burst Read Cycle | L   | н      | Н      | R      | L     | Addr In | Output<br>Invalid | x     | Н      |

|                                                                      | Asy | nchro  | nous   | Opera  | tions |         |                   |       |        |

| Asynchronous Read - Addresses<br>Latched                             | L   | н      | Н      | L      | R     | Addr In | Х                 | н     | Н      |

| Asynchronous Read - Data on Bus                                      | L   | L      | Н      | L      | Н     | Х       | Output<br>Data    | н     | Н      |

| Asynchronous Program (AVD#<br>Latched Addresses)                     | L   | н      | L      | L      | R     | Addr In | Х                 | н     | Н      |

| Asynchronous Program (WE#<br>Latched Data)                           | L   | Н      | R      | L      | Н     | Х       | Input<br>Valid    | н     | Н      |

|                                                                      |     | Non    | Opera  | ations |       |         |                   |       |        |

| Standby (CE#)                                                        | н   | х      | х      | Х      | Х     | Х       | HighZ             | HighZ | Н      |

| Hardware Reset                                                       | Х   | Х      | х      | Х      | Х     | Х       | HighZ             | HighZ | L      |

#### Table 2. Bus Operations

#### Legend:

L = 0; H = 1; X = VIL or VIH; R = Rising ege; h-I = High to low.

#### NOTES:

- 1. WP# protects the top two sectors.

- 2. ACC low protects all sectors.

- 3. Q0~Q15 are input (DIN) or output (DOUT) pins according to the requests of command sequence, sector protection, or data polling algorithm.

- 4. In Word Mode, the addresses are AM to A0, AM: MSB of address.

## 5-1. Non-Burst (Asynchronous) Read Operation

Upon device's power-up, non-burst mode read is as the default state. To perform a read operation, the system addresses the desired memory array or status register location by providing its address on the address pins and simultaneously enabling the chip by driving AVD# & CE# LOW, and WE# HIGH. The CLK keeps low during asynchronous read operation. The address is latched on the rising edge of AVD#; OE# will be driven low afterwards. A/Q15-A/Q0 output the data after previous operations is complete.

## 5-2. Burst (Synchronous) Read Operation

The device supports the following burst read modes:

- Continuous burst read

- Linear burst reads (8/16 words) with/without wrap around

#### 5-2-1. Continuous Burst Read

Burst read mode is enabled when first CLK rising edge meets AVD# low period. The AVD# keeps low for no more than one clock cycle.

The number of dummy cycles should be set (for tIACC for each burst session) before the clock signal is being activated. Before the burst read mode is activated, the number of dummy cycle will be determined by the setting configuration register command.

The process of the continuous burst read operation is as follows:

First CLK cycle's rising edge --> Initial word output tIACC --> Wait for dummy cycle --> Rising rising edge of each consecutive clock, following words output (tBACC) (Automatically increase the internal address counter)

- 1. For address boundary every 8 words, the first boundary starts with 000007h, next with 00000Fh by adding 8 words address; and etc.

- 2. For address boundary every 128 words, the first boundary starts with 00007Fh, next with 0000FFh by adding 128 words address; and etc.

- 3. Additional dummy cycles are needed if the start address for the output cannot be divided by 4.

RDY status indicates the condition of the device by de-asserting.

**NOTE**: There is a permanent internal address boundary in the device that occurs 8 or 128 words. Boundary crossing latency is needed when the device operates with dummy cycles set from 5 to 10.

| Word |       |    |     |     |     |     |    |    |     |     |     |     |     |     |     |     |     |     |

|------|-------|----|-----|-----|-----|-----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0    |       | D0 | D1  | D2  | D3  | D4  | D5 | D6 | D7  | 1dc | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 |

| 1    |       | D1 | D2  | D3  | 1dc | D4  | D5 | D6 | D7  | 1dc | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 |

| 2    | 10, 9 | D2 | D3  | 1dc | 1dc | D4  | D5 | D6 | D7  | 1dc | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 |

| 3    | and   | D3 | 1dc | 1dc | 1dc | D4  | D5 | D6 | D7  | 1dc | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 |

| 4    |       | D4 | D5  | D6  | D7  | 1dc | D8 | D9 | D10 | D11 | D12 | D13 | D14 | D15 | 1dc | D16 | D17 | D18 |

| 5    | 8 dc  | D5 | D6  | D7  | 1dc | 1dc | D8 | D9 | D10 | D11 | D12 | D13 | D14 | D15 | 1dc | D16 | D17 | D18 |

| 6    | ] [   | D6 | D7  | 1dc | 1dc | 1dc | D8 | D9 | D10 | D11 | D12 | D13 | D14 | D15 | 1dc | D16 | D17 | D18 |

| 7    |       | D7 | 1dc | 1dc | 1dc | 1dc | D8 | D9 | D10 | D11 | D12 | D13 | D14 | D15 | 1dc | D16 | D17 | D18 |

## Table 3-2. Address Latency for 7, 6, and 5 Dummy Cycles

| Word |          |    |      |      |      |    |    |    |    |    |

|------|----------|----|------|------|------|----|----|----|----|----|

| 0    |          | D0 | D1   | D2   | D3   | D4 | D5 | D6 | D7 | D8 |

| 1    | 7, 6,    | D1 | D2   | D3   | 1 dc | D4 | D5 | D6 | D7 | D8 |

| 2    | and 5 dc | D2 | D3   | 1 dc | 1 dc | D4 | D5 | D6 | D7 | D8 |

| 3    |          | D3 | 1 dc | 1 dc | 1 dc | D4 | D5 | D6 | D7 | D8 |

#### Table 3-3. Address Latency for 4 Dummy Cycles

| Word |      |    |      |      |    |    |    |    |    |    |

|------|------|----|------|------|----|----|----|----|----|----|

| 0    |      | D0 | D1   | D2   | D3 | D4 | D5 | D6 | D7 | D8 |

| 1    | 4 dc | D1 | D2   | D3   | D4 | D5 | D6 | D7 | D8 | D9 |

| 2    | 4 uc | D2 | D3   | 1 dc | D4 | D5 | D6 | D7 | D8 | D9 |

| 3    |      | D3 | 1 dc | 1 dc | D4 | D5 | D6 | D7 | D8 | D9 |

#### Table 3-4. Address Latency for 3 Dummy Cycles

| Word |      |    |      |    |    |    |    |    |    |     |

|------|------|----|------|----|----|----|----|----|----|-----|

| 0    |      | D0 | D1   | D2 | D3 | D4 | D5 | D6 | D7 | D8  |

| 1    | 3 dc | D1 | D2   | D3 | D4 | D5 | D6 | D7 | D8 | D9  |

| 2    | 5 00 | D2 | D3   | D4 | D5 | D6 | D7 | D8 | D9 | D10 |

| 3    |      | D3 | 1 dc | D4 | D5 | D6 | D7 | D8 | D9 | D10 |

## Table 3-5. Address/8-word Boundary Crossing Latency for 10, 9 and 8 Dummy Cycles

| Word |       |    |     |     |     |     |    |    |     |     |     |     |     |     |     |     |     |     |

|------|-------|----|-----|-----|-----|-----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0    |       | D0 | D1  | D2  | D3  | D4  | D5 | D6 | D7  | 1dc | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 |

| 1    |       | D1 | D2  | D3  | 1dc | D4  | D5 | D6 | D7  | 1dc | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 |

| 2    | 10, 9 | D2 | D3  | 1dc | 1dc | D4  | D5 | D6 | D7  | 1dc | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 |

| 3    | and   | D3 | 1dc | 1dc | 1dc | D4  | D5 | D6 | D7  | 1dc | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 |

| 4    | 8 dc  | D4 | D5  | D6  | D7  | 1dc | D8 | D9 | D10 | D11 | D12 | D13 | D14 | D15 | 1dc | D16 | D17 | D18 |

| 5    |       | D5 | D6  | D7  | 1dc | 1dc | D8 | D9 | D10 | D11 | D12 | D13 | D14 | D15 | 1dc | D16 | D17 | D18 |

| 6    |       | D6 | D7  | 1dc | 1dc | 1dc | D8 | D9 | D10 | D11 | D12 | D13 | D14 | D15 | 1dc | D16 | D17 | D18 |

| 7    |       | D7 | 1dc | 1dc | 1dc | 1dc | D8 | D9 | D10 | D11 | D12 | D13 | D14 | D15 | 1dc | D16 | D17 | D18 |

|   | Word |          |    |      |      |      |      |    |    |    |    |

|---|------|----------|----|------|------|------|------|----|----|----|----|

|   | 0    |          | D0 | D1   | D2   | D3   | 1 dc | D4 | D5 | D6 | D7 |

|   | 1    | 7, 6,    | D1 | D2   | D3   | 1 dc | 1 dc | D4 | D5 | D6 | D7 |

|   | 2    | and 5 dc | D2 | D3   | 1 dc | 1 dc | 1 dc | D4 | D5 | D6 | D7 |

| ĺ | 3    |          | D3 | 1 dc | 1 dc | 1 dc | 1 dc | D4 | D5 | D6 | D7 |

#### Table 3-7. Address/128-word Boundary Crossing Latency for 4 Dummy Cycles

| Word |      |    |      |      |      |    |    |    |    |    |

|------|------|----|------|------|------|----|----|----|----|----|

| 0    |      | D0 | D1   | D2   | D3   | D4 | D5 | D6 | D7 | D8 |

| 1    | 1 do | D1 | D2   | D3   | 1 dc | D4 | D5 | D6 | D7 | D8 |

| 2    | 4 dc | D2 | D3   | 1 dc | 1 dc | D4 | D5 | D6 | D7 | D8 |

| 3    |      | D3 | 1 dc | 1 dc | 1 dc | D4 | D5 | D6 | D7 | D8 |

#### Table 3-8. Address/128-word Boundary Crossing Latency for 3 Dummy Cycles

| Word |      |    |      |      |    |    |    |    |    |    |

|------|------|----|------|------|----|----|----|----|----|----|

| 0    |      | D0 | D1   | D2   | D3 | D4 | D5 | D6 | D7 | D8 |

| 1    | 3 dc | D1 | D2   | D3   | D4 | D5 | D6 | D7 | D8 | D9 |

| 2    | 5 UC | D2 | D3   | 1 dc | D4 | D5 | D6 | D7 | D8 | D9 |

| 3    |      | D3 | 1 dc | 1 dc | D4 | D5 | D6 | D7 | D8 | D9 |

#### 5-2-2. 8-, 16-Word Modes Linear Burst with Wrap Around

Fixed amount of data (8 or 16 words) is output from continuous address for the linear wrap around mode. (in the unit of words). The origin burst read address is decided by the group where the origin address falls. The definition of groups is as illustrated in Table 4 below.

#### Table 4. Burst Address Groups

| Mode    | Group Size | Group Address Ranges         |

|---------|------------|------------------------------|

| 8-word  | 8 words    | 0-7h, 8-Fh, 10-17h, 18-1Fh   |

| 16-word | 16 words   | 0-Fh, 10-1Fh, 20-2Fh, 30-3Fh |

#### 5-2-3. Reading Memory Array

Read mode is the default state after a power-up or a reset operation.

An erase operation will be paused (after a time delay less than tESL) and the device will enter Erase-Suspended Read mode if the device receives an Erase Suspend command while in the Sector Erase state. While in the Erase-Suspended Read mode, data can be programmed or read from any sector which is not being erased. Reading from addresses within sector (s) being erased will only return the contents of the status register, which is the current status of the device.

If a program command is issued to any inactive (not currently being erased) sector during Erase-Suspended Read mode, the device will perform the program operation and automatically return to Erase-Suspended Read mode after the program operation completes successfully.

While in Erase-Suspended Read mode, an Erase Resume command must be issued by the system to reactivate the erase operation. The erase operation will resume from where it was suspended and will continue the operation until it completely finishes or another Erase Suspend command is received.

After the memory device completes an embedded operation (automatic Chip Erase, Sector Erase, or Program) successfully, it will automatically return to Read mode and data can be read from any address in the array. If the embedded operation fails to complete, as indicated by status register bit Q5 (exceeds time limitation flag) going HIGH during the operations, the system must perform a reset operation to set the device back to Read mode.

There are several situations requiring a reset operation to return to Read mode:

- A program or erase failure – can be indicated by status register bit Q5 going HIGH during the operation. Failures happened during the both operations will not cause the device automatically returning to Read mode.

- The device is in Auto Select, CFI mode or read configure register mode – All of the states will remain active until they are terminated by a reset operation.

In the two situations above, if a reset operation (either hardware reset or software reset command) is not performed, the device will not return to Read mode and the system will not be able to read array data.

#### 5-3. Set Configuration Register Command Sequence

The burst mode parameter is set by the configuration register. The following modes are configured: Burst read mode, RDY configuration, synchronous mode active & number of dummy cycles. Before entering burst mode, the configuration register needs to be set. It's consisted of 4 cycles. Cycle 1 & 2: Unlock sequences. Cycle 3: Data D0h & address 555h. Cycle 4: Configuration code with address (000h). To reset the device to read or suspended read, a software reset command needs to be issued. The device's default state after power up or hardware reset is asynchronous read mode. Before entering synchronous mode, the register needs to be set. During bus operation, the register can not be modified.

#### 5-3-1. Programmable Dummy Cycle

This feature is able to indicate the device the configurable period of time for the number of additional clock cycles. And then address data will be available after the time elapsed and AVD# is driven active. The dummy cycle will be set to default value after power up. The total number of dummy cycles is programmable from 3rd to 10th cycles. Refer to **Section 5.3 Set Configuration Register Command Sequence** in above section for more details.

#### 5-3-2. Configurable Dummy Cycle

The Configurable Dummy Cycle settings can be decided by the input frequency of the device - The Configuration Bit (CR14–CR11) determines the setting. Refer to **Table 5. Configurable Dummy Cycles vs. Frequency** as below.

The certain number of cycles for original burst read is set by the dummy cycle command sequence. The clock frequency determines the number of dummy cycles configured.

**NOTE:** After a power-up or hardware reset, the default setting of dummy cycle will be set to 10.

In order to ensure the device is set as expected, it is recommended that dummy cycle command sequence should to be written even if the default dummy cycle value is desired. Default state can also be obtained by hardware reset.

Other setting not listed in the table above will be reserved as invalid.

If the setting CR[14:11] is not in legal setting as table listed, the device will output CR[14:11] to 0001 and RDY will be disasserted.

#### 5-3-3. Burst Length Configuration

Three different burst read modes are supported: 8 & 16 word linear burst read with wrap around; continuous burst read. The device's default burst read is continuous read. It launches with starting address till the burst read ends. When reaches the highest address, it wraps around to the lowest address. The wrap around occurs in the 8 or 16 word boundary.

| CR [14:11] | Dummy Cycles | Freq Max<br>(Mhz) |

|------------|--------------|-------------------|

| 0001       | 3            | 25                |

| 0010       | 4            | 38                |

| 0011       | 5            | 50                |

| 0100       | 6            | 63                |

| 0101       | 7            | 75                |

| 0110       | 8            | 87                |

| 0111       | 9            | 98                |

| 1000       | 10           | 108               |

### Table 5. Configurable Dummy Cycles vs. Frequency

#### 5-3-4. Burst Wrap Around

CR3 is set to "1" by default. When it changes to "0", the burst warp around mode is disabled.

#### 5-3-5. Output Drive Strength

User may tune the strength of output driver from full strength to half strength depends on the configuration bit CR7.

The default setting is CR7=1; with full strength.

If CR7=0, the strength of output buffer will be reduced to half strength.

### 5-4. Program Operation

All three devices provide the ability to program the memory array in Word mode. As long as users enter the correct cycle defined in the *Chapter 7. Command Definitions* (including 2 unlock cycles and the AOH program command), word data provided on the data lines by the system will automatically be programmed into the array at the specified location.

After the program command sequence has been executed, the internal write state machine (WSM) automatically executes the algorithms and timings necessary for programming and verification, which includes generating suitable program pulses, checking cell threshold voltage margins, and repeating the program pulse if any cells do not pass verification or have low margins. The internal controller protects cells that do pass verification and margin tests from being over-programmed by inhibiting further program pulses to these passing cells as weaker cells continue to be programmed.

With the internal WSM automatically controlling the programming process, users only need to enter the program command and data once.

Programming will only change the bit status from "1" to "0". It is not possible to change the bit status from "0" to "1" by programming. This can only be done with an erase operation. Furthermore, the internal write verification only checks and detects errors in cases where a "1" is not successfully programmed to "0".

Any commands written to the device during programming will be ignored except hardware reset or program suspend. Hardware reset will terminate the program operation after a period of time not more than tPSL. When the program is complete or the program operation is terminated by a hardware reset, the device will return to Read mode. When program suspend is ready, the device will enter program suspend read mode.

After the embedded program operation has begun, users can check for completion by reading the following bits in the status register table below:

| Status            | Q7 <sup>*1</sup> | Q6       | Q5 | Q1  |

|-------------------|------------------|----------|----|-----|

| In progress       | Q7#              | Toggling | 0  | 0   |

| Exceed Time Limit | Q7#              | Toggling | 1  | N/A |

**NOTE:** DQ7 (Data# Polling bit) shows the status of on-going or completion for program and erase operations or in erase suspend mode.

#### 5-4-1. Programming Commands/Command Sequences

To perform a program operation, the system provides the desired address on the address pins, enables the chip by asserting CE# & WE# LOW & OE# to HIGH, and disables the Data (I/O) pins by holding OE# HIGH. To Latch address, AVD# needs to be asserted LOW. On 1st falling edge of WE#, address latched. On 1st rising edge of WE#, data latched.

Table2. Bus Operation on page 16, described the detail of the combinations.

To see an example of the implementation on waveform, please refer to **Figure 17. Program Operation Timings Waveform**. The system is not allowed to write invalid commands (commands not defined in this datasheet) to the device. Writing an invalid command may put the device in an undefined state.

#### 5-4-2. Accelerated Program and Erase Operations

By applying high voltage (Vhv) to the ACC pin, the device will enter the Accelerated Programming mode. This mode permits the system to skip the normal command unlock sequences and program locations directly. During accelerated programming, the current drawn from the ACC pin is no more than ICP1.

#### 5-4-3. Write Buffer Programming Operation

The devices program 32 words in a programming operation. To trigger the Write Buffer Programming, start with the first two unlock cycles, then third cycle writes the Write Buffer Load command at the predefined programming Sector Address. The fourth cycle writes the "word locations subtract one" number.

Following the above operations, system starts to write the mingling of address and data. After the programming of the first address or data, the "write-buffer-page" is selected. The following data should be within the above mentioned page. The "write-buffer-page" is selected by choosing address Amax-A5. "Write-Buffer-Page" address has to be the same for all address/data write into the write buffer. If not, operation will be aborted.

To program the content of the write buffer page this command must be followed by a write to buffer Program confirm command. The operation of write-buffer can be suspended or resumed by the standard commands, once the write buffer programming operation is finished, it will return to normal READ mode.

"Abort" will be executed for the Write Buffer Programming Sequence if the following conditions occurred:

- The value loaded is bigger than the page buffer size during "Number of Locations to Program"

- Address written in a sector is not the same as the one assigned during the Write-Buffer-Load command.

- Address/ Data pair written to a different write-buffer-page than the one assigned by the "Starting Address" during the "write buffer data loading" operation.

- Writing not "Confirm Command" after the assigned number of "data load" cycles.

At Write Buffer Abort mode, the status register will be Q1=1, Q7=DATA# (last address written), Q6=toggle, Q5=0. A Write-to-Buffer-Abort Reset command sequence has to be written to reset the device for the next operation.

Write buffer programming can be conducted in any sequence. However the CFI functions, Autoselect, Secured Silicon sectors are not functional when program operation is in progress. Multiple write buffer programming operations on the same write buffer address range without intervening erases is available. Any bit in a write buffer address range can not be programmed from 0 back to 1.

#### 5-4-4. Write Buffer Programming Command Sequence

Write Buffer Programming Sequence is able to facilitate faster programming as compared to the standard Program Command Sequence.

See Table 7. and Figure 1. below for the program command sequence.

#### **5-4-5. Buffer Write Abort**

In the table below, Q1 is the indicator of Buffer Write Abort. When Q1=1, the device will abort from buffer write and go back to read status register:

| Status                           | Q7  | Q6     | Q5 | Q3  | Q2  | Q1 |

|----------------------------------|-----|--------|----|-----|-----|----|

| Buffer Write Busy                | Q7# | Toggle | 0  | N/A | N/A | 0  |

| Buffer Write Abort               | Q7# | Toggle | 0  | N/A | N/A | 1  |

| Buffer Write Exceeded Time Limit | Q7# | Toggle | 1  | N/A | N/A | 0  |

#### Table 6. Write Buffer Command Sequence

| Sequence | Command                                                                                         | Address                  | Data          | Remarks                                                                                                 |

|----------|-------------------------------------------------------------------------------------------------|--------------------------|---------------|---------------------------------------------------------------------------------------------------------|

| 1        | Unlock (1)                                                                                      | 555                      | 00AA          |                                                                                                         |

| 2        | Unlock (2)                                                                                      | 2AA                      | 0055          |                                                                                                         |

| 3        | Load Write Buffer                                                                               | Start Address            | 0025h         |                                                                                                         |

| 4        | Indicate # of Program<br>Locations                                                              | Start Address            | Word<br>Count | (# of locations) - 1                                                                                    |

| 5        | Load 1st word                                                                                   | Start Address            | Write         | Addresses need to be within write-buffer-<br>page boundaries, but no need to be<br>loaded in any order. |

| 6-X      | Load next word                                                                                  | Write Buffer<br>Location | Write         | Same as above                                                                                           |

| X+1      | Load last word                                                                                  | Write Buffer<br>Location | Write         | Same as above                                                                                           |

| X+2      | Write Buffer Program<br>Confirm                                                                 | Sector<br>Address        | 0029h         | This command must come after the last write buffer location loaded, or the operation will ABORT.        |

| X+3      | Device goes busy                                                                                |                          |               |                                                                                                         |

| Last     | Status monitoring<br>through Q pins (Conduct<br>Data Bar Polling on the<br>Last Loaded Address) |                          |               |                                                                                                         |

#### NOTES:

- 1. For programming, valid address means program address. For erasing, valid address means erase sectors address.

- 2. Q7 should be rechecked even Q5="1" because Q7 may change simultaneously with Q5.

## 5-5. Erase Operation

There are two types of erase operations performed on the memory array -- Sector Erase and Chip Erase. Sector Erase operation erases one selected sector.

Chip erase will not be conducted if any of the sectors is protected. It can be done after the sector is being un-protected.

#### 5-5-1. Sector Erase

The sector erase operation is used to clear data within a sector by returning all the memory location to the "1" state. It requires six command cycles to initiate the erase operation.

The first two are "unlock cycles", the third is a configuration cycle, the fourth and fifth ones are also "unlock cycles", and the last cycle is the Sector Erase command. After the sector erase command sequence has been issued, the embedded sector erase operation will then begin.

After the embedded sector erase operation begins, all commands except Erase Suspend will be ignored. The only way to interrupt the operation is with an Erase Suspend command or with a hardware reset. The hardware reset will completely abort the operation and return the device to Read mode.

The system can determine the status of the embedded sector erase operation by the following methods:

| Status              | Q7 | Q6       | Q5 | Q3 | Q2       |

|---------------------|----|----------|----|----|----------|

| In progress         | 0  | Toggling | 0  | NA | Toggling |

| Exceeded time limit | 0  | Toggling | 1  | NA | Toggling |

#### NOTE:

Q2 is a localized indicator showing a specified sector is undergoing erase operation or not. Q2 toggles when user reads at addresses where the sectors are actively being erased (in erase mode) or to be erased (in erase suspend mode).

#### 5-5-2. Chip Erase

The Chip Erase operation is used to erase all the data within the memory array. All memory cells containing a "0" will be returned to the erased state of "1". This operation requires 6 write cycles to initiate the action. The first two cycles are "unlock" cycles, the third is a configuration cycle, the fourth and fifth are also "unlock" cycles, and the sixth cycle initiates the chip erase operation.

During the chip erase operation, no other software commands will be accepted, but if a hardware reset is received or the working voltage is too low, that chip erase will be terminated. After Chip Erase operation completes, the chip will automatically return to Read mode. If any of the sectors is locked, chip erase will not start.

The system is able to determine the status of the embedded chip erase operation by the following methods:

| Status            | Q7 | Q6       | Q5 | Q2       |

|-------------------|----|----------|----|----------|

| In progress       | 0  | Toggling | 0  | Toggling |

| Exceed time limit | 0  | Toggling | 1  | Toggling |

#### 5-5-3. Sector Erase Command Sequence