## SINGLE CHIP 10/100 FAST ETHERNET CONTROLLER WITH uP INTERFACE

## 1.0 Features

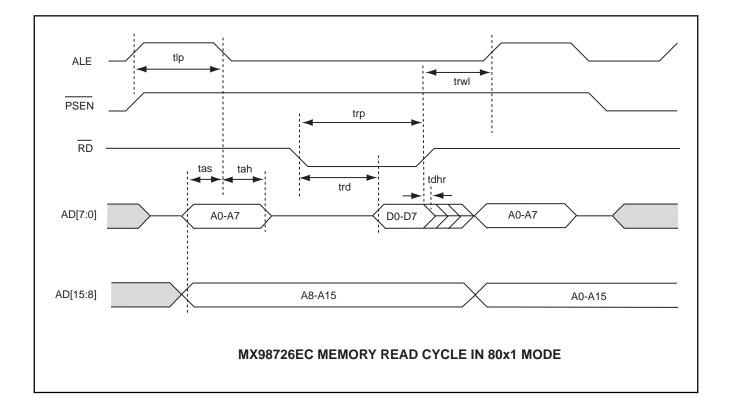

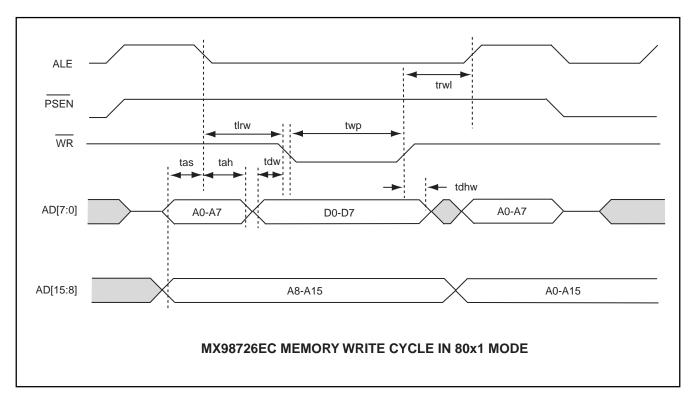

- Direct interface to 80188/186 up to 40Mhz.

- Integrated 10/100 TP tranceiver on chip to reduce overall cost

- Optional MII interface for external tranceiver.

- Fully comply to IEEE 802.3u spec.

- Best fit in network printer and hub/switch management application

- A local DMA channel between on-chip FIFOs and packet memory

- Shared memory architecture allow host and MX98726EC to use only one single SRAM

- Host DMA can share packet memory with local DMA with simple hand shake protocol for x188/186 type of processor

- Supports proprietary local DMA channel to share packet memory

## **1.1 Introduction**

MX98726EC (Generic MAC, or GMAC) is a cost effective solution as a generic single chip 10/100 Fast Ethernet controller. It is designed to directly interface 80188, 80186 (host) without glue logic. Two types of memory sharing schemes are supported, i.e. interleaved and shared mode to support a variety of applications. Single chip solution will help reduce system cost not only on the components but also the board size. Full NWAY function with 10/100 tranceiver will ease the field installation, simply plug the chip in and it will connect itself with the best protocol available.

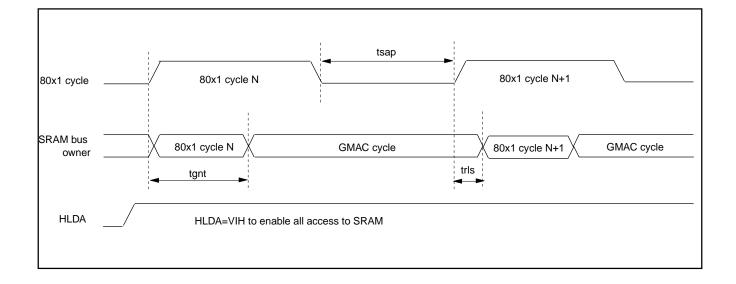

The interleaved mode allow uP to access SRAM ( packet/host buffer ) through MX98726EC's local DMA channel. This way, no extra SRAM interface logic is needed on the host side. If high performance is desired, then shared memory mode is another alternative which allow host to access SRAM on its own by denying SRAM bus grant to MX98726EC using simple hand shake protocol. Without SRAM bus grant, MX98726EC will float its interface connected to the SRAM, therefore host can utilize its own memory subsystem to conduct its own SRAM access.

- Support bus size configuration: - CPU : 8 bits, SRAM: 8 bits

- CPU : 16 bits, SRAM: 8/16 bits

- Flexible packet buffer partition and addressing space for 32k, 64k up to 512K bytes

- NWAY autonegotiation function to automatically set up network speed and protocol

- 3 loop back modes for system level diagnostics

- Rich on-chip register set to support a wide variety of network management functions

- Support 64 bits hash table for multicast addressing

- Support software EEPROM interface for easy upgrade of EEPROM content

- Support 1K bits and 4K bits EEPROM interface

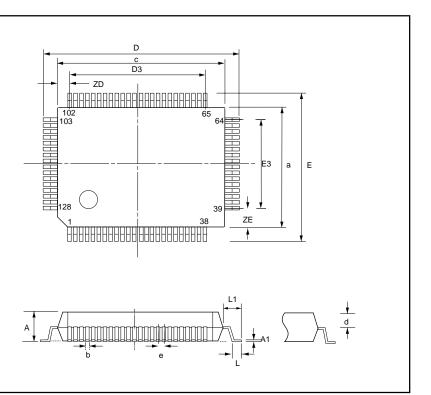

- 5V CMOS in 128 PQFP package for minimum board size application

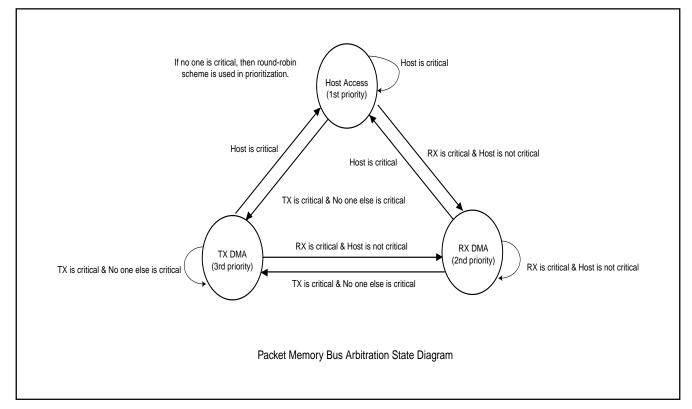

A intelligent built-in SRAM bus arbitor will manage all the SRAM access requests from host, on-chip transmit channel and on-chip receive channel. The throughput of these network channels and MX98726EC's DMA burst length can be easily adjusted by option bits on the chip. These options can help system developers to "fine tune" a best cost/performance ratio.

MX98726EC is also equipped with fast back-to-back transmit capability which allow software to "fire" as many transmit packets as needed in a single command. Receive FIFO also allow back-to-back reception. Optional EEPROM can be used to stored network network address and other information. In case cost is really a concern, most configuration options including network address can be programmed through uP.

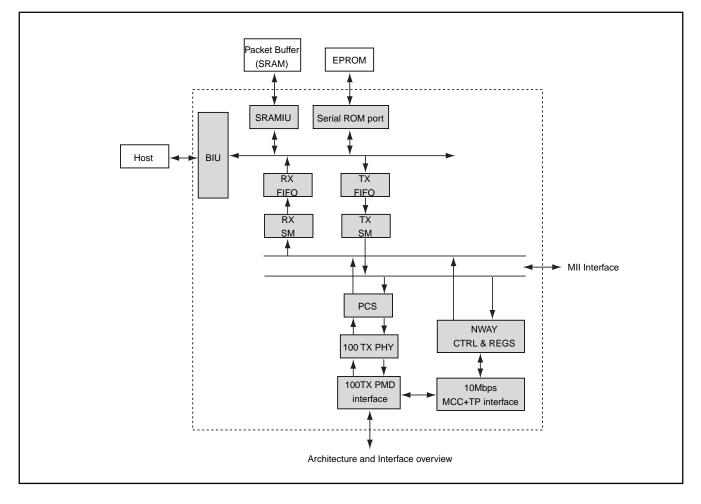

## 1.2 Internal Block Diagram

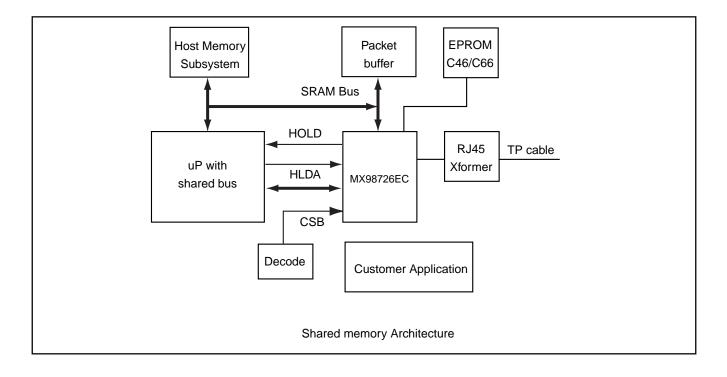

## **1.3 Typical Applications**

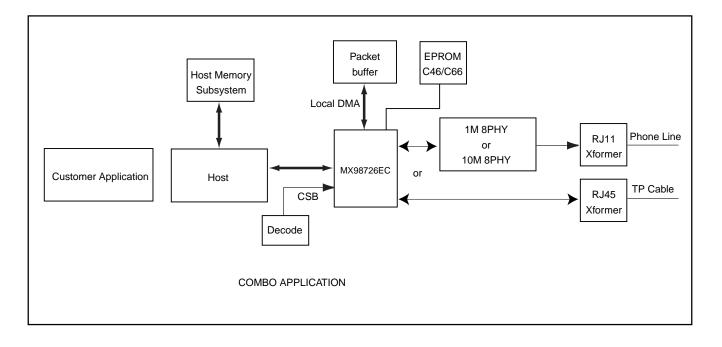

## 1.4 Combo Application

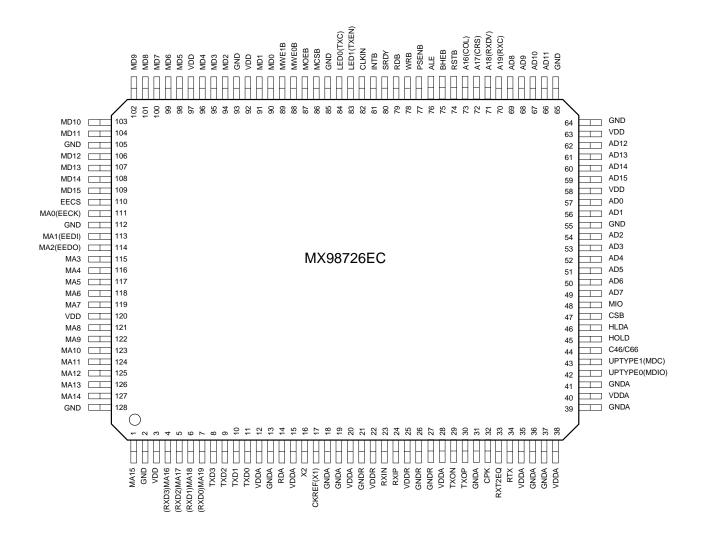

## 2.0 Pin Configuration and Description

## 2.1 Pin Description :

| PIN#   | Pin Name  | Туре              | Description                                                                                                                                                                                                                                                                                                               |  |  |

|--------|-----------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 82     | CLKIN     | I, TTL            | Host Clock Input : 8M to 40 Mhz.                                                                                                                                                                                                                                                                                          |  |  |

| 49-54, | AD[7:0]   | I/O, 4ma<br>56,57 | Multiplexed Address/Data Bit [7:0] : Internal pull-down                                                                                                                                                                                                                                                                   |  |  |

| 59-62, | AD[15:8]  | I/O, 4ma<br>66-69 | Multiplexed Address/Data Bit [15:8] : Internal pull-down                                                                                                                                                                                                                                                                  |  |  |

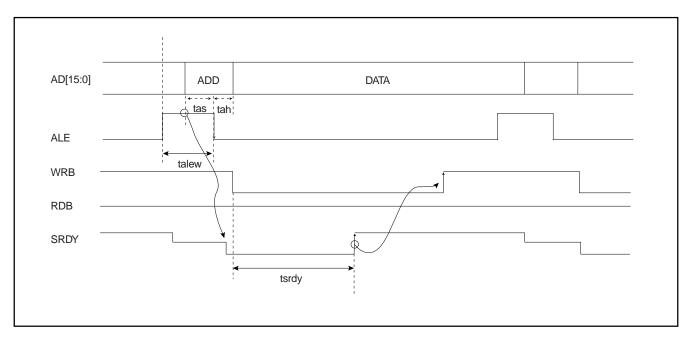

| 76     | ALE       | I,TTL             | Address Latch Enable : Active high                                                                                                                                                                                                                                                                                        |  |  |

| 70     | A19(RXC)  | I, TTL            | Host Bus Address Bit19, when on-chip tranceiver is used, it is used in A[19:16], when in MII mode, it is defined as receive clock RXC (25MHz o 2.5MHz) When this pin is used as address bit, it is internally grounded unti Reg50.6 (A19A16EN bit) is set to enable decoding of this pin as address bit. Internal pull-up |  |  |

| 71     | A18(RXDV) | I,TTL             | Host Bus Address Bit18, when on-chip tranceiver is used, it is used in A[19:16], when in MII mode, it is defined as receive data valid RXDV signal. When this pin is used as address bit, it is internally grounded unti Reg50.6 (A19A16EN bit) is set to enable decoding of this pin as address bit. Internal pull-up.   |  |  |

| 72     | A17(CRS)  | I,TTL             | Host Bus Address Bit17, when on-chip tranceiver is used, it is used in A[19:16], when in MII mode, it is defined as carrier same CRS signal When this pin is used as address bit, it is internally grounded until Reg50.6 (A19A16EN bit) is set to enable decoding of this pin as address bit. Inter nal pull-up.         |  |  |

| 73     | A16(COL)  | I,TTL             | Host Bus Address Bit16, when on-chip tranceiver is used, it is used in A[19:16], when in MII mode, it is defined as collision COL signal. When this pin is used as address bit, it is internally grounded until Reg50.6 (A19A16EN bit) is set to enable decoding of this pin as address bit. Inter nal pull-up.           |  |  |

| 79     | RDB       | I, TTL            | Host Read Strobe: Active low. Internal pull-up                                                                                                                                                                                                                                                                            |  |  |

| 78     | WRB       | I, TTL            | Host Write Strobe : Active low. Internal pull-up                                                                                                                                                                                                                                                                          |  |  |

| 81     | INTB      | O/D, 4ma          | Host Interrupt Output : Polarity can be programmed, default is active low.<br>For active Low interrupt application, external pull-up is reguired. For active<br>high interrupt application, external pull-down is required.                                                                                               |  |  |

| 75     | BHEB      | I,TTL             | Host Byte High Enable : Internal pull-up.BHEBA0Function00Word Transfer01Upper Byte Transfer10Lower Byte Transfer11Lower Byte Transfer                                                                                                                                                                                     |  |  |

| 80     | SRDY      | O, 4ma            | Synchronous Host Ready Output : Active high synchronized to CLKIN to<br>indicate data is ready to be transferred. Initially low at the beginning of a<br>host cycle.                                                                                                                                                      |  |  |

| 47     | CSB       | I, TTL            | Chip Select : Active low, used to enable GMAC to decode host address<br>When high, no host cycle is recognized by MAC.                                                                                                                                                                                                    |  |  |

| 48     | MIO       | I, TTL            | Host Memory/IO cycle indicator : Set for memory access and reset for IC access. Internal pull-up. Decode of MIO can be disable by DISMIO register bit. Default is enabled.                                                                                                                                                |  |  |

| M  | ۲IC   |        | MX98726EC                                                                |

|----|-------|--------|--------------------------------------------------------------------------|

| 45 | HOLD  | O, 4ma | Packet Memory Bus Hold Request : Active high to request Host to "float"  |

|    |       |        | its interface of the packet memory. Host grants the packet buffer bus to |

|    |       |        | MX98726EC by asserting HLDA = 1.                                         |

| 46 | HLDA  | I, TTL | Packet Memory Bus Hold Acknowledge: Packet buffer bus is granted to      |

|    |       |        | MX98726EC. If HLDA=0 then MX98726EC will float its interface on the      |

|    |       |        | packet buffer. Internal pull-up.                                         |

| 77 | PSENB | I, TTL | Host Program Strobe Enable : Active low to indicate current cycle is a   |

|    |       |        | ROM access and MX98726EC will not decode this ROM cycle. PSENB           |

|    |       |        | must high for packet memory access. Internal pull-up.                    |

| 74 | RSTB  | I,TTL  | Host Reset Input : Active low, Schmitt trigger input, Internal pull-up.  |

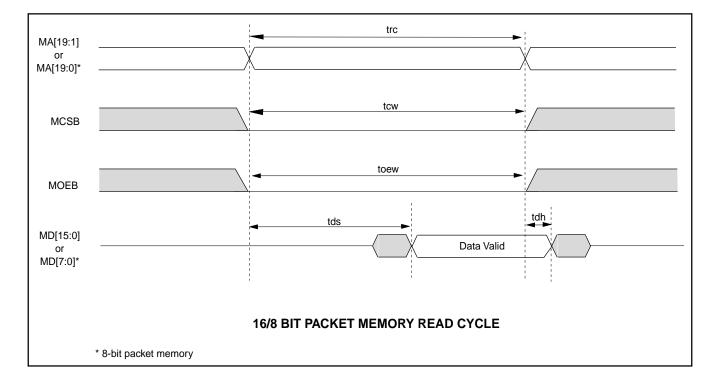

## Packet Buffer Interface :

| PIN#    | Pin Name   | Туре     | Description                                                                |

|---------|------------|----------|----------------------------------------------------------------------------|

| 1,      | MA[19:3]   | O,4ma    | Memory Address Bit 19-0: If HLDA = 0 then all these address lines are tri- |

| 115-119 |            |          | stated.                                                                    |

| 7       | MA19(RXD0) | I/O, 4ma | Memory Address Bit19, when on-chip tranceiver is used, it is defined as    |

|         |            |          | MA19, while in MII mode, it is used as receive data bit RXD0 pin.          |

| 6       | MA18(RXD1) | I/O, 4ma | Memory Address Bit18, when on-chip tranceiver is used, it is defined as    |

|         |            |          | MA18, while in MII mode, it is used as receive data bit RXD1 pin.          |

| 5       | MA17(RXD2) | I/O, 4ma | Memory Address Bit17, when on-chip tranceiver is used, it is defined as    |

|         |            |          | MA17, while in MII mode, it is used as receive data bit RXD2 pin.          |

| 4       | MA16(RXD3) | I/O, 4ma | Memory Address Bit16, when on-chip tranceiver is used, it is defined as    |

|         |            |          | MA16, while in MII mode, it is used as receive data bit RXD3 pin.          |

| 90-96,  | MD[15:0]   | I/O,4ma  | Memory Data Bit 15-0 : Internal pull-down.                                 |

| 98-104, |            |          |                                                                            |

| 106-109 |            |          |                                                                            |

| 114     | MA2(EEDO)  | 1/O,4ma  | Memory Address Bit 2 or EEPROM Data Out bit: Right after host reset        |

|         |            |          | GMAC automatically load configuration information from external EEPROM.    |

|         |            |          | During this period, MA2 pin acts as a EEDO pin that read in output data    |

|         |            |          | stream from EEPROM. After EEPROM auto load sequence is done, this          |

|         |            |          | pin becomes MA2 together with MA[19:3] forms packet buffer address         |

|         |            |          | line 19 - 0. Internally pull-down.                                         |

| 113     | MA1(EEDI)  | 1/O,4ma  | Memory Address Bit 1 or EEPROM Data In bit: During EEPROM auto load        |

|         |            |          | sequence, MA1 pin acts as EEDI pin that write data stream into EEPROM.     |

|         |            |          | After EEPROM auto load sequence is done, this pin becomes MA1, to-         |

|         |            |          | gether with MA[19:2] forms packet buffer address lines.                    |

| 111     | MA0(EECK)  | 1/O,4ma  | Memory Address Bit 0 or EEPROM Clock Input : During EEPROM auto            |

|         |            |          | load sequence, MA0 pin acts as EECK pin that provides clock to EEPROM      |

|         |            |          | After EEPROM auto load sequence is done, this pin becomes MA0, to-         |

|         |            |          | gether with MA[19:1] forms packet buffer address lines.                    |

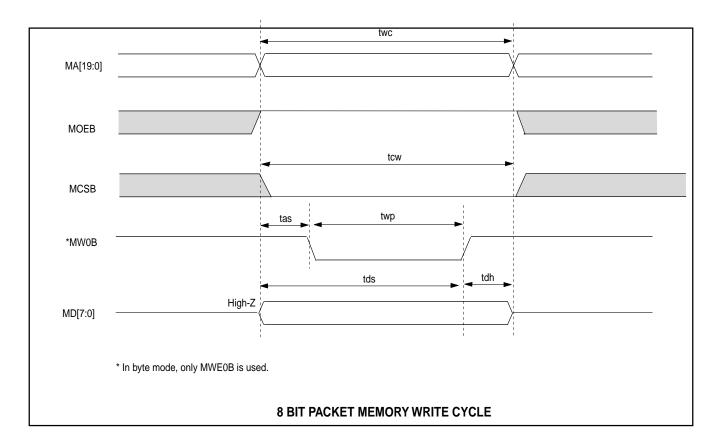

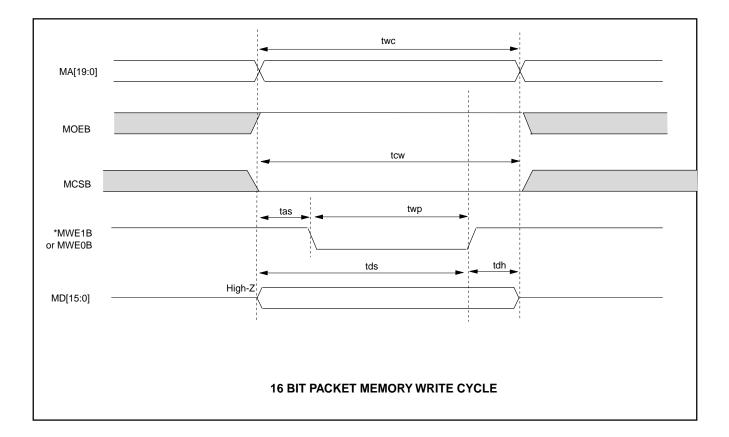

| 87      | MOEB       | O,4ma    | Memory Output Enable: Active low during packet buffer read access.         |

| 86      | MCSB       | O,4ma    | Memory Chip Select: Active low during packet buffer accesses.              |

| 88, 89  | MWEB[1:0]  | O,4ma    | Byte Write Enable: Active low during packet buffer write cycle. MWEB1 for  |

|         |            |          | high byte and MWEB0 for low byte.                                          |

### 10/100 Tranceiver interface :

| Description<br>RDA external resistor to ground: 10K ohm, 5%                                                                                                                                                                                                                                 |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                                                                                                                                                                                             |  |  |

|                                                                                                                                                                                                                                                                                             |  |  |

| 25Mhz , 30 PPM external osc./crystal input :                                                                                                                                                                                                                                                |  |  |

| 25Mhz , 30 PPM external crystal output :                                                                                                                                                                                                                                                    |  |  |

| Twisted pair receive differential input: support both 10/100 Mbps speed                                                                                                                                                                                                                     |  |  |

| Twisted pair receive differential input: support both 10/100 Mbps speed                                                                                                                                                                                                                     |  |  |

| Twisted pair transmit differential output: support both 10/100 Mbps spee                                                                                                                                                                                                                    |  |  |

| meet 802.3/802.3u spec.                                                                                                                                                                                                                                                                     |  |  |

| Twisted pair transmit differential output: support both 10/100 Mbps spee                                                                                                                                                                                                                    |  |  |

| meet 802.3/802.3u spec.                                                                                                                                                                                                                                                                     |  |  |

| NC pin : used in test mode only                                                                                                                                                                                                                                                             |  |  |

| RTX2EQ external resistor to ground: 1.4K ohm, 5%                                                                                                                                                                                                                                            |  |  |

| RTX external resistor to ground: 560 ohm, 5%                                                                                                                                                                                                                                                |  |  |

|                                                                                                                                                                                                                                                                                             |  |  |

|                                                                                                                                                                                                                                                                                             |  |  |

| Description                                                                                                                                                                                                                                                                                 |  |  |

| EEPROM Chip Select Signal : Active high                                                                                                                                                                                                                                                     |  |  |

| EEPROM Size Select : Set for C46, reset for C66. Internal pull-up.                                                                                                                                                                                                                          |  |  |

| LED0 (TXC in MII mode) : When on-chip tranceiver is used, it is defined                                                                                                                                                                                                                     |  |  |

| SPEED LED. When the light is on, it indicates the 100 Mbps speed. Wh                                                                                                                                                                                                                        |  |  |

| off, it indicates the 10 Mbps speed. When both LED0 and LED1 are flas                                                                                                                                                                                                                       |  |  |

| ing identically, it means the bus integrity error. (Internal pull-up). When                                                                                                                                                                                                                 |  |  |

| MII mode, this pin is defined as transmit clock TXC (25 MHz or 2.5 MH                                                                                                                                                                                                                       |  |  |

| input.                                                                                                                                                                                                                                                                                      |  |  |

| LED1 (TXEN in MII mode) :When on-chip tranceiver is used, it is define                                                                                                                                                                                                                      |  |  |

| as Link/Activity LED. When the light is stable and on, it indicates a go                                                                                                                                                                                                                    |  |  |

| link. When flashing, it indicates TX and RX activities. When off, it mea                                                                                                                                                                                                                    |  |  |

| a bad link. (Internal pull-up). When in MII mode, this pin is defined as tran                                                                                                                                                                                                               |  |  |

| mit enable TXEN pin.                                                                                                                                                                                                                                                                        |  |  |

| uP type select control bit 1-0: UPTYPE1 and UPTYPE0 must be exte                                                                                                                                                                                                                            |  |  |

| nally pull-up or down through $\leq$ 4.7K ohm resistors to configure the b                                                                                                                                                                                                                  |  |  |

| interface for different uP.                                                                                                                                                                                                                                                                 |  |  |

|                                                                                                                                                                                                                                                                                             |  |  |

| UPTYPE1 UPTYPE0 uP selected                                                                                                                                                                                                                                                                 |  |  |

| 0 0 reserved 0                                                                                                                                                                                                                                                                              |  |  |

| 0 0 reserved 0<br>0 1 80x1                                                                                                                                                                                                                                                                  |  |  |

| 0   reserved 0     0   1   80x1     1   0   80188                                                                                                                                                                                                                                           |  |  |

| 0   0   reserved 0     0   1   80x1     1   0   80188     1   1   80186                                                                                                                                                                                                                     |  |  |

| 0 0 reserved 0   0 1 80x1   1 0 80188   1 1 80186   uP type select control bit 0 (MDIO in MII mode ): UPTYPE0 is                                                                                                                                                                            |  |  |

| 0   0   reserved 0     0   1   80x1     1   0   80188     1   1   80186     uP type select control bit 0 (MDIO in MII mode ): UPTYPE0 is internally pull-down and used as uP type selection during host reset (                                                                             |  |  |

| 00reserved 00180x110801881180186uP type select control bit 0 ( MDIO in MII mode ): UPTYPE0 isinternally pull-down and used as uP type selection during host reset (<br>RSTB=0). After host reset sequence is completed, this pin become MD                                                  |  |  |

| 0 0 reserved 0   0 1 80x1   1 0 80188   1 1 80186   uP type select control bit 0 (MDIO in MII mode ): UPTYPE0 is internally pull-down and used as uP type selection during host reset (   RSTB=0 ). After host reset sequence is completed, this pin become MD pin if MII mode is selected. |  |  |

| 00reserved 00180x110801881180186uP type select control bit 0 ( MDIO in MII mode ): UPTYPE0 isinternally pull-down and used as uP type selection during host reset (<br>RSTB=0). After host reset sequence is completed, this pin become MD                                                  |  |  |

|                                                                                                                                                                                                                                                                                             |  |  |

## Vdd/Gnd Pins :

| PIN#                         | Pin Name | Description                                                 |

|------------------------------|----------|-------------------------------------------------------------|

| 12,15,20,28,35,38,40         | VDDA     | Analog Vdd Pins : Must be carefully isolated in a separted  |

|                              |          | vdd plane.                                                  |

| 13,18,19,31,36,37,39,41      | GNDA     | Analog Ground Pins : Must be carefully isolated in a        |

|                              |          | separted ground plane.                                      |

| 22,25                        | VDDR     | RX Vdd Pins : Must be carefully isolated in a separted      |

|                              |          | Vdd plane.                                                  |

| 21,26,27                     | GNDR     | RX Ground Pins : Must be carefully isolated in a separted   |

|                              |          | ground plane.                                               |

| 3,58,63,92,97,120            | VDD      | Digital Vdd Pins : Must be carefully isolated in a separted |

|                              |          | Vdd plane.                                                  |

| 2,55,64,65,85,93,105,112,128 | GND      | Digital Ground Pins : Must be carefully isolated in a       |

|                              |          | separted ground plane.                                      |

|                              |          |                                                             |

## 3.0 Register (Default value is defined after hardware/power-up reset)

Reset logic : All register bits are cleared by hardware reset, while register bit with an "\*" in its symbol name is also cleared by software reset.

| Network Control Register A : NCRA | (Reg00h),R/W, default=00h |

|-----------------------------------|---------------------------|

|-----------------------------------|---------------------------|

| Bit      | Symbol    | Description                                                                       |          |        |            |                                                       |  |

|----------|-----------|-----------------------------------------------------------------------------------|----------|--------|------------|-------------------------------------------------------|--|

| 0.0      | RESET     | Software reset.                                                                   |          |        |            |                                                       |  |

| 0.1      | ST0*      | Start Transmit Command/Status : Write to issue commands. When done, both bits are |          |        |            |                                                       |  |

| 0.2      | ST1*      | cleared automatically.                                                            |          |        |            |                                                       |  |

|          |           | Transmit command                                                                  | 1.011    | ет     | h          |                                                       |  |

|          |           | IDLE state                                                                        |          |        |            | indiante TV DMA idla atata jurita haa na affact       |  |

|          |           |                                                                                   | 0        | 0      |            | indicate TX DMA idle state, write has no effect.      |  |

|          |           | TX DMA Poll                                                                       | 0        | 1      |            | K DMA, send packets stored in packet memory.          |  |

|          |           | TX FIFO Send                                                                      | 1        | 0      |            | ately send the packet stored in the TX FIFO.          |  |

|          |           | TX DMA Poll                                                                       | 1        | 1      | Start D    | K DMA, send packets stored in packet memory.          |  |

|          |           | All transmit comma                                                                | ands ai  | re cle | eared to ( | 00 when the operation is done to indicate idle        |  |

|          |           | state. When the T                                                                 | X DMA    | poll   | and the -  | TX FIFO Send can not be used at the same time.        |  |

|          |           | New packet can be                                                                 | e writte | n to t | the FIFO   | directly only when ST1, ST0=IDLE and                  |  |

|          |           | TXDMA[3:0]=1h.Tl                                                                  | heTXI    | DMA    | poll and   | the TX FIFO Send commands can be issued only          |  |

|          |           |                                                                                   |          |        | •          | ]=1h, regardless of any error status in previous      |  |

|          |           | transmission.                                                                     |          |        | -          |                                                       |  |

| 0.3      | SR*       | Start Receive: Enable the MAC receive packets. Default is disabled.               |          |        |            |                                                       |  |

| 0.4, 0.5 | LB0*,LB1* | Loopback Mode:                                                                    | LB1      |        | LB0        | •                                                     |  |

|          |           | Mode0                                                                             | 0        |        | 0 1        | Normal mode                                           |  |

|          |           | Mode1                                                                             | 0        |        | 1          | nternal FIFO Loopback                                 |  |

|          |           | Mode2                                                                             | 1        |        | 0          | nternal NWAY Loopback                                 |  |

|          |           | Mode3                                                                             | 1        |        | 1          | nternal PMD Loopback                                  |  |

|          |           | Mode 2 and 3 are                                                                  | rosorv   | od fo  | or IC tost | purpose. Only mode 1 can be used on bench.            |  |

|          |           |                                                                                   |          |        |            | one by full duplex normal mode with real cable        |  |

|          |           | hooked up from TX                                                                 |          |        |            | one by full duplex normal mode with real cable        |  |

| 0.6      | INTMODE   |                                                                                   | •        |        | ·          | rrupt, reset for active low interrupt case.           |  |

| 0.0      | CLKSEL    | •                                                                                 |          |        | -          | z clock for all internal DMA, default is reset to use |  |

| 0.7      | OLNOEL    | internal 50MHz clo                                                                |          |        |            |                                                       |  |

|          |           | Internal SUMPZ CIO                                                                | UCKIO    | an m   | iemai DN   | //八、                                                  |  |

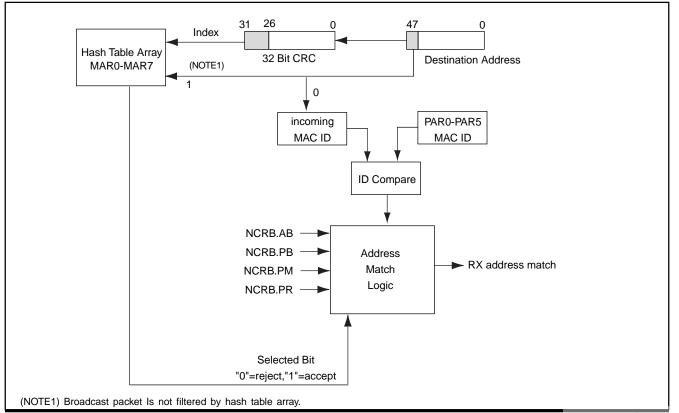

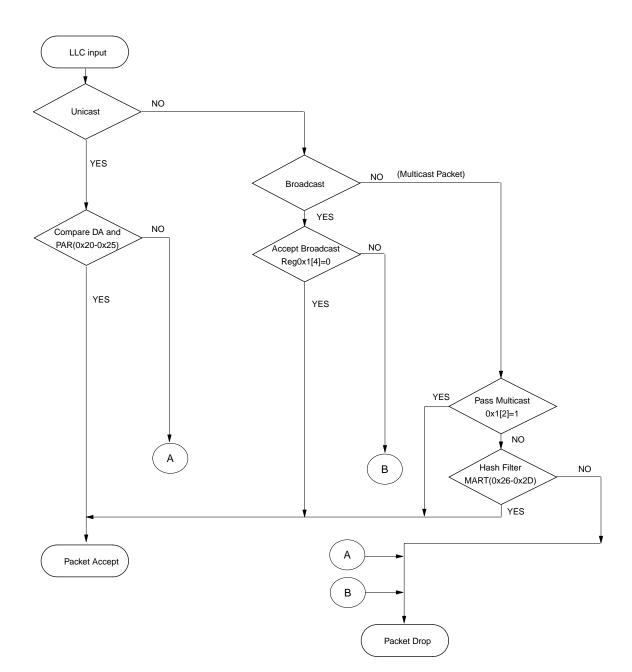

## Network Control Register : NCRB (Reg01h),R/W, default=01h

| Bit    | Symbol | Description                                                                          |  |  |  |

|--------|--------|--------------------------------------------------------------------------------------|--|--|--|

| 1.0    | PR*    | Promiscuous mode: Set to receive any incoming valid frames received, regardless of   |  |  |  |

|        |        | its destination address. Default is set.                                             |  |  |  |

| 1.1    | CA*    | Capture Effect Mode: Set to enable an enhanced backoff algorithm to avoid network    |  |  |  |

|        |        | capture effect.                                                                      |  |  |  |

| 1.2    | PM*    | Pass Multicast: Set to accept all multicast packets including broadcast address (1st |  |  |  |

|        |        | bit in destination address is 1), default is reset                                   |  |  |  |

| 1.3    | PB*    | Pass Bad Frame: Enable GMAC to accept Runt frame. Default is reset.                  |  |  |  |

| 1.4    | AB*    | Accept Broadcast: Default is reset. Set to accept all broadcast packets.             |  |  |  |

| 1.5    | HBD*   | Reserved for test purpose. Default is 0.                                             |  |  |  |

| Reserv | ed     | Must be 00.                                                                          |  |  |  |

## GMAC Test Register A : TRA (Reg02h), R/W, default=00h

| Bit     | Symbol     | Description                                                                                |

|---------|------------|--------------------------------------------------------------------------------------------|

| 2.0     | TEST       | Test mode enable: Set to enable test modes defined by TMODE[2:0], default is reset         |

|         |            | for normal operation.                                                                      |

| 2.1-2.3 | TMODE[2:0] | Test Mode Select bits[2:0]: Reserved for GMAC's internal tests, only meaningful when       |

|         |            | the TEST bit is set, except when TMODE [2:0] = "110" which is also used as normal          |

|         |            | mode with EEPROM interface disabled. When TMODE [2:0] = "110" & Test =0, then              |

|         |            | MA19~MA16 are still SRAM address bit19~16, while Test = 1, MA19~MA16 are de-               |

|         |            | fined as test pins reserved for debug purpose.                                             |

| 2.4     | RWR        | Receive Watchdog Release : When set, the receive watchdog is released 40 to 48 bit         |

|         |            | times from the last carrier deassertion. When reset, the receive watchdog is released      |

|         |            | 16 to 24 bits times from the last carrier deassertion.                                     |

| 2.5     | RWD        | Receive Watchdog Disable : When set, the receive watchdog is disabled. When reset,         |

|         |            | receive carriers longer than 2560 bytes are guaranteed to cause the watchdog timeout.      |

|         |            | Packets shorted than 2048 bytes are guaranteed to pass.                                    |

| 2.6     | FC         | Forced Collision : Set to force collision at every transmit packet, this bit works only in |

|         |            | internal FIFO loopback mode, i.e. LB0=1, LB1=0, to test excessive collision. Default       |

|         |            | is reset.                                                                                  |

| 2.7     | SB         | Start/Stop Backoff counter: When set, indicates internal backoff counter stops count-      |

|         |            | ing when any carrier is detected. Counter resumed when carrier drops. When reset,          |

|         |            | the internal backoff counter is not affected by carrier activity. Default is reset.        |

## GMACTest Register : TRB (Reg03h), R/W, default=00h

| Bit | Symbol           | Description                                                              |

|-----|------------------|--------------------------------------------------------------------------|

| 3.0 | FKD*             | Flaky Oscillator Disable: When set, indicates that the internal flaky    |

|     |                  | oscillator is disabled. Pseudo random numbers are chosen instead of      |

|     |                  | fully random numbers, used for the internal diagnostic purpose. Set to   |

|     |                  | disable the normal clocking scheme in the timer's test. Reset to enable  |

|     |                  | the timer test. Default is reset.                                        |

| 3.1 | RDNCNTCB*        | Reserved for test                                                        |

| 3.2 | RDNCNTSB*        | Reserved for test                                                        |

| 3.3 | COLCNTCB*        | Reserved for test                                                        |

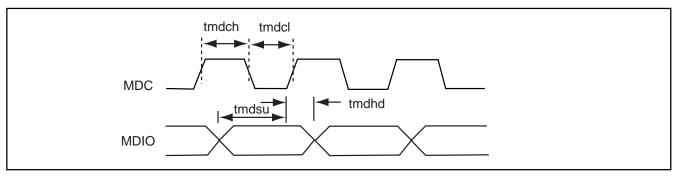

| 3.4 | BFS0*(MDC)       | Normally used as BFS0 pin for test purpose, while in MII mode, it is     |

|     |                  | defined as MII management clock signal (MDC) to be used as a timing      |

|     |                  | reference of MDIO pin.                                                   |

| 3.5 | BKCNTLB*(MDIOEN) | Normally used as BKCNTLB pin for test purpose, while in MII mode, it is  |

|     |                  | used to control the direction of MDIO pin. Set MDIOEN = 1 will make      |

|     |                  | MDIO pin as input pin, the value can be read from MDI bit.               |

|     |                  | Set MDIOEN = 0 will make MDIO pin as output pin, the value of MDO bit    |

|     |                  | is driven out to MDIO pin.                                               |

| 3.6 | BFS1*(MDO)       | Normally used as BFS1 pin for test purpose, while in MII mode, it is     |

|     |                  | used as MII management write data (MDO) for MDIO pin's output data.      |

| 3.7 | BFSTATUS*(MDI)   | Normally used as BFSTATUS pin for test purpose, while in MII mode, it is |

|     |                  | used as MII management read data (MDI) for MDIO pin's input data.        |

## Last Transmitted Packet Status: LTPS (Reg04h), RO, default=00h

| Bit | Symbol   | Description                                                                             |

|-----|----------|-----------------------------------------------------------------------------------------|

| 4.0 | CC0*     | Collision Count Bit 0 :                                                                 |

| 4.1 | CC1*     | Collision Count Bit 1 :                                                                 |

| 4.2 | CC2*     | Collision Count Bit 2 :                                                                 |

| 4.3 | CC3*     | Collision Count Bit 3 : when CC[3:0] = 1111 and a new collision is detected, then it is |

|     |          | called excessive collision error which will abort the current packet, TEI interrupt bit |

|     |          | will be set.                                                                            |

| 4.4 | CRSLOST* | Carrier Sense Lost : Set to indicate CRS was lost during the transmission, default is   |

|     |          | reset for normal packet transmission.                                                   |

| 4.5 | UF*      | TX FIFO underflow : Set to indicate a underflow problem in TX FIFO an FIFOEI            |

|     |          | interrupt is generated for driver to resolve this problem.                              |

| 4.6 | OWC*     | Out of Window Collision : Set to indicate an collision occured after 64 bytes of data   |

|     |          | has been transmitted, no retransmission will be issued                                  |

| 4.7 | TERR*    | Transmit Error: Set to indicate packet transmitted with error, reset for normal packet  |

|     |          | transmission.                                                                           |

|     |          |                                                                                         |

#### Last Received Packet Status: LRPS (Reg05h), RO, default=00h

| Dit | Sumbol | Description                                                                              |

|-----|--------|------------------------------------------------------------------------------------------|

| Bit | Symbol | Description                                                                              |

| 5.0 | BF*    | RX Packet Buffer Full Error : 1 indicates RX packet buffer is full.                      |

| 5.1 | CRC*   | CRC error : Calculation is based on integer multiple of bytes, set to indicate CRC error |

|     |        | for received packet.                                                                     |

| 5.2 | FAE*   | Frame Alignment Error : Set to indicate extra nibble is received which is not at octet   |

|     |        | boundary. This error is independent of CRC detection.                                    |

| 5.3 | FO*    | FIFO overrun : When set, an interrupt is generated, driver must resolve this error.      |

| 5.4 | RW*    | Receive Watchdog : Set to indicate the frame length exceeds 2048 bytes. An interrupt     |

|     |        | will be generated to driver.                                                             |

| 5.5 | MF*    | Multicast address : Set to indicate current frame has multicast address.                 |

| 5.6 | RF*    | Runt Frame : Set to indicate a frame length less than 64 bytes, only meaningful when     |

|     |        | Reg01h.3 PB bit =1 is set.                                                               |

| 5.7 | RERR*  | Receive Error : Set to indicate a packet received with errors including CRC, FAE, FO,    |

|     |        | RW, ( RF and PB=1 ).                                                                     |

|     |        |                                                                                          |

Notes : This LRPS register contains the same status byte as in the description field of the last received packet in the packet memory.

### Missed Packet Counter: MPC (Reg07/06h), R/W, default=0000h

| Bit   | Symbol         | Description                                                       |

|-------|----------------|-------------------------------------------------------------------|

| 6.7-0 | MISSCNT[7:0]*  | Miss Packet Counter Bit [7:0]: Lower byte of Miss packet counter  |

| 7.7-0 | MISSCNT[15:8]* | Miss Packet Counter Bit [15:8]: Upper byte of Miss packet counter |

## Interrupt Mask Register: IMR (Reg08h), R/W, default=00h

| Bit | Symbol  | Description                                                                                 |

|-----|---------|---------------------------------------------------------------------------------------------|

| 8.0 | CNTOFIM | Miss Counter Over Flow Interrupt Mask : Set to enable Miss counter overflow interrupt       |

|     |         | default is reset. When Overflow condition of the miss packet counter occures, counter is    |

|     |         | halt and driver need to resolve this condition in order to reset the counter if counter is  |

|     |         | ever used.                                                                                  |

| 8.1 | RIM     | Received Interrupt Mask: Set to enable Packet Received Interrupt, default is reset which    |

|     |         | disable RI interrupt.                                                                       |

| 8.2 | TIM     | Transmit Interrupt Mask: Set to enable Packet transmit OK interrupt, default is reset       |

|     |         | which disable TI interrupt.                                                                 |

| 8.3 | RXEIM   | Receive Error Mask: Set to enable Receive Error interrupt, default is reset which disable   |

|     |         | RXEI interrupt.                                                                             |

| 8.4 | TXEIM   | Transmit Error Mask: Set to enable transmit error interrupt, default is reset which disable |

|     |         | TXEI interrupt.                                                                             |

| 8.5 | FIFOEIM | FIFO Error Interrupt Mask: Set to enable FIFO Error interrupt, default is reset which       |

|     |         | disable FIFOEI interrupt.                                                                   |

| 8.6 | BUSEIM  | Bus Error Interrupt Mask: Set to enable Bus Error interrupt, default is reset which dis-    |

|     |         | able BUSEI interrupt.                                                                       |

| 8.7 | RBFIM   | RX Buffer Full Interrupt Mask: Set to enable RX Buffer full interrupt, default is reset     |

|     |         | which disable BFI interrupt.                                                                |

|     |         |                                                                                             |

### Interrupt Register: IR (Reg09h), R/W, default=00h

| Bit | Symbol  | Description                                                                                   |

|-----|---------|-----------------------------------------------------------------------------------------------|

| 9.0 | CNTOFI* | Miss Counter Over Flow Interrupt : Set to assert interrupt when Miss packet counter is        |

|     |         | overflow, write 1 to this bit will clear the bit and interrupt, write 0 has no effect.        |

| 9.1 | RI*     | Receive OK interrupt : Set to assert interrupt, write 1 to this bit will clear the bit and    |

|     |         | interrupt, write 0 has no effect                                                              |

| 9.2 | TI*     | Transmit OK interrupt: Set to assert interrupt, write 1 to this bit will clear the bit and    |

|     |         | interrupt, write 0 has no effect                                                              |

| 9.3 | REI*    | Receive Error Interrupt: Set to assert interrupt when packet is received with error , write   |

|     |         | 1 to this bit will clear the bit and interrupt, write 0 has no effect                         |

| 9.4 | TEI*    | Transmit Error Interrupt : Set to assert interrupt when packet is transmitted with error,     |

|     |         | write 1 to this bit will clear the bit and interrupt, write 0 has no effect                   |

| 9.5 | FIFOEI* | FIFO Error Interrupt: Set to assert interrupt when either TX FIFO is overrun or RX FIFO       |

|     |         | is overrun, write 1 to this bit will clear the bit and interrupt, write 0 has no effect       |

| 9.6 | BUSEI*  | Bus Error Interrupt: Set to assert interrupt when Bus integrity check is enabled and          |

|     |         | failed. Write 1 to this bit will clear the bit and interrupt, write 0 has no effect           |

| 9.7 | RBFI*   | RX Buffer Full Interrupt: Set to assert interrupt when RX buffer area is being overwritten    |

|     |         | by new received packets, write 1 to this bit will clear the bit and interrupt, write 0 has no |

|     |         | effect                                                                                        |

|     |         |                                                                                               |

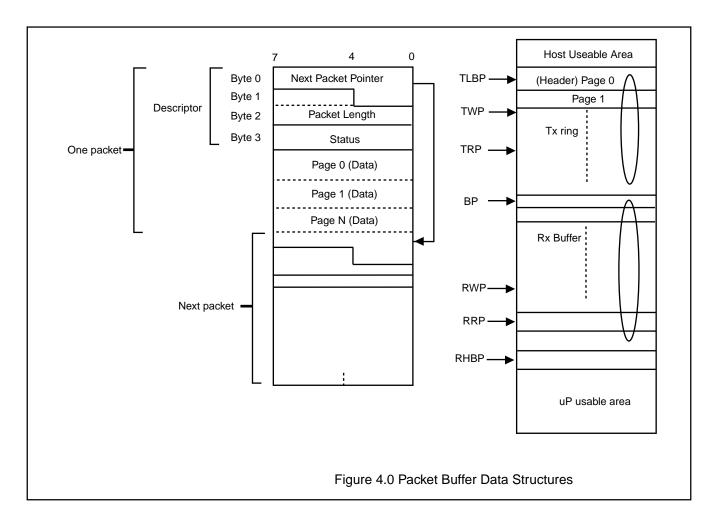

Note : All page pointer bit [11:0] are mapped to MA[19:8] in the same bit ordering.

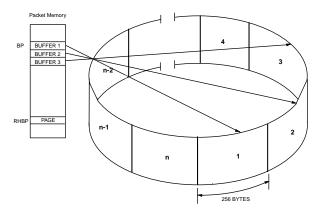

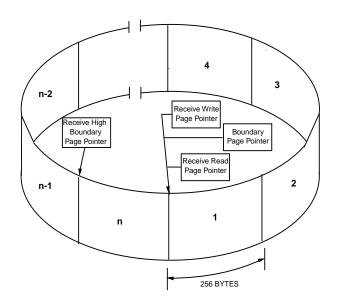

### Boundary Page Pointer Register: BP (Reg0Bh/0Ah), R/W, default=x000h

| Bit     | Symbol   | Description                                                                   |

|---------|----------|-------------------------------------------------------------------------------|

| 0A.7-0, | BP[11:0] | Boundary Page Pointer between tx/rx buffer: page TLBP[11:0] to page BP[11:0]  |

| 0B.3-0  |          | is tx buffer. page BP[11:0] to RHBP[11:0] is rx buffer. BP[11:0] is mapped to |

|         |          | MA[19:8]. MSB bit is Reg0BH.3 bit. LSB is Reg0AH.0 bit.                       |

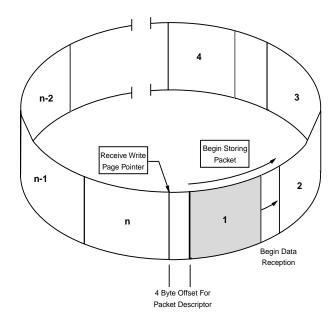

### TX Low Boundary Page Pointer Register: TLBP (Reg0Dh/0Ch), R/W, default=x000h

| Bit     | Symbol     | Description                                                                      |

|---------|------------|----------------------------------------------------------------------------------|

| 0C.7-0, | TLBP[11:0] | TX Low Boundary Page Pointer : Points to the first page of transmit buffer ring. |

| 0D.3-0  |            | It's a static pointer that is used by GmAC to link to the last page pointed by   |

|         |            | boundary pointer. TLBP[11:0] MSB bit is Reg0Fh.3 bit. LSB is Reg0Ch.0 bit.       |

#### Transmit Buffer Write Page Pointer : TWP (Reg.0Fh/0Eh), R/W, default=x000h

| Bit     | Symbol    | Description                                                                     |

|---------|-----------|---------------------------------------------------------------------------------|

| 0E.7-0, | TWP[11:0] | Transmit Buffer Write Page Pointer: TWP[11:0] are mapped to MA[19:8] with       |

| 0F.3-0  |           | the same bit ordering. The MSB is the Reg0Fh.3 bit. The LSB is the              |

|         |           | Reg0Eh.0 bit. TWP is normally controlled by the device driver. An internal Byte |

|         |           | Counter (TWPBC) is associated with this page register.                          |

### IO Base Page Register: IOB (Reg11h/10h), R/W, default=x000h

| Bit     | Symbol    | Description                                                                  |

|---------|-----------|------------------------------------------------------------------------------|

| 10.7-0, | IOB[11:0] | IO Base Address Register: On-chip register IO base address register. This    |

| 11.3-0  |           | page address register defines the base page address of all on-chip registers |

|         |           | in a IO address space.(00h-FFh). MIO=0 and CSB=0 will force GMAC to          |

|         |           | decode IO address for on chip register access. if MIO=1 and CSB=0, then all  |

|         |           | on chip registers are localed in memory page 0. IOB register is mapped to    |

|         |           | physical address [19:8] during decoding. IOB is 0000h after Reset, software  |

|         |           | can assign new base address by writing new page number to this register.     |

### Transmit Buffer Read Page Pointer Register: TRP (Reg13h/12h), R/W, default=x000h

| Bit     | Symbol    | Description                                                                         |

|---------|-----------|-------------------------------------------------------------------------------------|

| 12.7-0, | TRP[11:0] | The Page Index of transmit buffer read pointer: Current transmit read page pointer. |

| 13.0-3  |           | MSB bit is Reg13h.3 bit. LSB is Reg12h.0 bit. TRP is controlled by GMAC only.       |

|         |           | An internal Byte Counter (TRPBC) is associated with this page register.             |

### Receive Interrupt Timer: RXINTT (Reg15h/14h), R/W

| Bit     | Symbol       | Description                                           |

|---------|--------------|-------------------------------------------------------|

| 14.7-0, | RXINTT[7:0], | Receive Interrupt Timer: Default is 0000h "not used". |

| 15.7-0, | RXINTT[15:8] |                                                       |

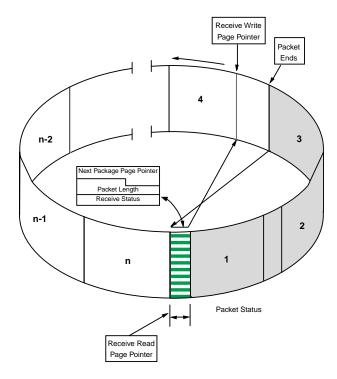

### Receive Buffer Write Page Pointer Register: RWP (Reg17h/16h), R/W, default=x000h

| Bit     | Symbol    | Description                                                                         |

|---------|-----------|-------------------------------------------------------------------------------------|

| 16.7-0, | RWP[11:0] | Receive Buffer Write Page Pointer: Current receive write page pointer. MSB          |

| 17.0-3  |           | bit is Reg17h.3 bit. LSB is Reg16h.0 bit. This register is controlled by GMAC only. |

|         |           | An internal Byte Counter (RWPBC) is associated with this page register.             |

### Receive Buffer Read Page Pointer Register: RRP (Reg19h/18h), R/W, default=000h

| Bit     | Symbol    | Description                                                                     |

|---------|-----------|---------------------------------------------------------------------------------|

| 18.7-0, | RRP[11:0] | Receive Buffer Read Page Pointer: MAC current receive read page pointer.        |

| 19.0-3  |           | RRP[11:0] is mapped to MA[19:8]. MSB bit is Reg19h.3 bit. LSB is Reg18h.0 bit.  |

|         |           | This register is normally controlled by device driver. An internal byte Counter |

|         |           | (RRPBC) is associated with this page register.                                  |

### 64K Memory Bank Address : Reg19h (R/W), default=0h

| Bit    | Symbol    | Description                |

|--------|-----------|----------------------------|

| 19.7-4 | BANK[3:0] | Reserved : Default is 0000 |

### RX High Boundary Page Pointer Register: RHBP (Reg1Bh/1Ah), R/W, default=x000h

| Bit     | Symbol     | Description                                                                 |

|---------|------------|-----------------------------------------------------------------------------|

| 1A.7-0. | RHBP[11:0] | Receive High Boundary Page Pointer : RX packet buffer is defined as between |

| 1B.0-3  |            | RHBP [11:0] and BP[11:0]. MSB bit is Reg1Bh.3 bit. LSB is Reg1Ah.0 bit.     |

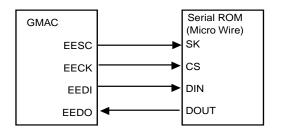

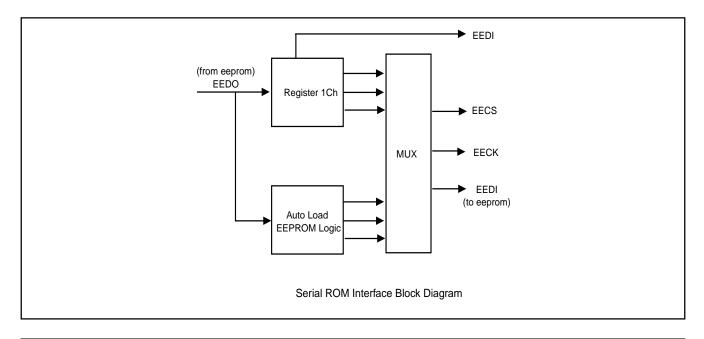

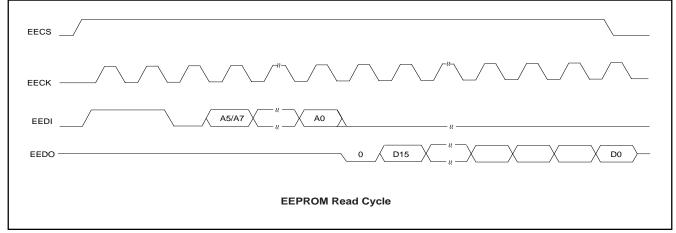

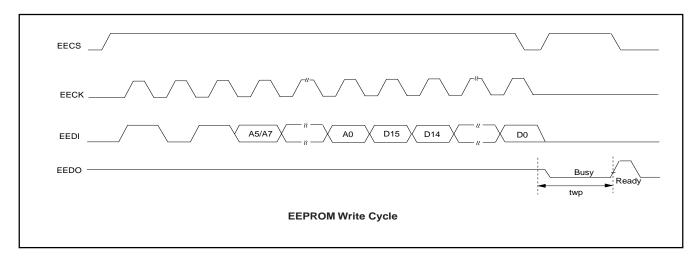

## EEPROM Interface Register: Reg1Ch, R/W, default=00h

| Bit  | Symbol  | Description                                                                       |

|------|---------|-----------------------------------------------------------------------------------|

| 1C.0 | EECS*   | Chip select output to external EEPROM clock device                                |

| 1C.1 | EECK*   | Serial clock output to external EEPROM clock device, <1MHz                        |

| 1C.2 | EEDI*   | Serial data input to external EEPROM clock device                                 |

| 1C.3 | EEDO*   | Serial data output from external EEPROM clock device                              |

| 1C.4 | EESEL*  | Set to enable external EEPROM write operation, default 0 is read.                 |

| 1C.5 | EELD*   | Set to enable reloading the entire content of EEPROM just like power-on reset or  |

|      |         | hardware reset. When loading is done, this bit will be set by GMAC automatically. |

| 1C.6 | HOLDREQ | Reserved, default = 0, set to hold host access to SRAM in order to access         |

|      |         | EEPROM by software.                                                               |

| 1C.7 | HLDAACK | Reserved, Read only, set to indicate that request to hold host is granted, GMAC   |

|      |         | can access EEPROM through Reg. IC by software.                                    |

|      |         |                                                                                   |

#### Reserved (Reg 1Dh), default=00h

| Bit      | Symbol | Description |

|----------|--------|-------------|

| Reserved |        | Must be 00h |

## Reserved (Reg1Fh/1Eh), R/W, default=0000h

| Bit     | Symbol   | Description |  |

|---------|----------|-------------|--|

| 1E.7-0, |          |             |  |

| 1F.7-0  | reserved |             |  |

## Network Address Registers : Reg20h~25h (R/W), 26h~2Dh (R/W), default=00h

| Bit      | Symbol | Description                             |

|----------|--------|-----------------------------------------|

| 20.[7:0] | PAR0   | Physical Address Byte 0: PAR[7:0]       |

| 21.[7:0] | PAR1   | Physical Address Byte 1: PAR[15:8]      |

| 22.[7:0] | PAR2   | Physical Address Byte 2 : PAR[23:16]    |

| 23.[7:0] | PAR3   | Physical Address Byte 3 : PAR[31:24]    |

| 24.[7:0] | PAR4   | Physical Address Byte 4 : PAR[39:32]    |

| 25.[7:0] | PAR5   | Physical Address Byte 5 : PAR[47:40]    |

| 26.[7:0] | MAR0   | Hash Table Register Byte 0 : MAR[7:0]   |

| 27.[7:0] | MAR1   | Hash Table Register Byte 1 : MAR[15:8]  |

| 28.[7:0] | MAR2   | Hash Table Register Byte 2 : MAR[23:16] |

| 29.[7:0] | MAR3   | Hash Table Register Byte 3 : MAR[31:24] |

| 2A.[7:0] | MAR4   | Hash Table Register Byte 4 : MAR[39:32] |

| 2B.[7:0] | MAR5   | Hash Table Register Byte 5 : MAR[47:40] |

| 2C.[7:0] | MAR6   | Hash Table Register Byte 6 : MAR[56:48] |

| 2D.[7:0] | MAR7   | Hash Table Register Byte 7 : MAR[63:57] |

|          |        |                                         |

## Transceiver Control Register : ANALOG (Reg 2Eh), R/W, default=07h

| Bit    | Symbol   | Description                                                                      |

|--------|----------|----------------------------------------------------------------------------------|

| 2E.0   | DS120    | Must be 1 for NORMAL mode with auto-compensation.                                |

| 2E.1   | DS130    | Must be 1 for NORMAL mode with auto-compensation                                 |

| 2E.2   | PWD10B   | Set for NORMAL mode, write 0 followed by write 1 will power down 10 Base-T       |

|        |          | analog circuit.                                                                  |

| 2E.3   | PWD100   | Reset for NORMAL mode, write 1 followed by write 0 will power down 100 Base-     |

|        |          | T analog circuit.                                                                |

| 2E.4   | RSQ      | Reduced SQuelch Enable : Set to enable the reduced squelch circuit in the 10     |

|        |          | Base-T mode for the receive channel. This can help the reception in a long cable |

|        |          | application. Default is reset, meaning the normal CAT-5 cable is used.           |

| 2E.5   | RST100   | Reset for NORMAL mode, write 1 followed by write 0 will reset 100 Bare-T analog  |

|        |          | circuit.                                                                         |

| 2E.6-7 | Reserved | must be zero.                                                                    |

|        |          |                                                                                  |

### Reserved, default=00h

| Bit    | Symbol   | Description |

|--------|----------|-------------|

| 2F.7-0 | Reserved |             |

## NWAY Configuration Register : NWAYC (Reg 30h), R/W, default=84h

| Bit      | Symbol   | Description                                                                       |

|----------|----------|-----------------------------------------------------------------------------------|

| 30.0     | FD       | Full Duplex Mode: Set 1 to force the full duplex mode. The default is 0, meaning  |

|          |          | the half duplex mode. This bit is meaningful only if $ANE = 0$                    |

| 30.1     | PS100/10 | Port Select 100/10 bit : Default is 0, meaning the 10 Base-T mode.                |

| 30.2     | ANE      | Autonegotiation Enable: Set to enable the NWAY function. Default is set. ANS[2:0] |

|          |          | should be written 001 to restart the autonegotiation sequence after ANE is set.   |

| 30.[5:3] | ANS[2:0] | Autonegotiation status bits: Read only for the NWAY status, except when write     |

|          |          | 001 will restart the autonegotiation sequence. The MSB is the Reg30h.5 bit when   |

|          |          | Nway settles down in one network mode, one bit of Reg31.4~Reg 31.7 will be set    |

|          |          | to indicate the chosen network mode.                                              |

|          |          | Autonegotiation Arbitration State, arbitration states are defined                 |

|          |          | 000 = Autonegotiation disable                                                     |

|          |          | 001 = Transmit disable                                                            |

|          |          | 010 = ability detect                                                              |

|          |          | 011 = Acknowledge detect                                                          |

|          |          | 100 = Complete acknowledge detect                                                 |

|          |          | 101 = FLP link good; autonegotiation complete                                     |

|          |          | 110 = Link check                                                                  |

| 30.6     | NTTEST   | Reserved                                                                          |

| 30.7     | LTE      | Link Test Enable : Default is high, meaning the link check is always enabled      |

|          |          | Reset forces a good link in the 10 Base-T mode for the testing purpose.           |

|          |          |                                                                                   |

## NWAY Status Register : NWAYS (Reg 31h), RO, default=00h

| Bit  | Symbol | Description                                                                        |

|------|--------|------------------------------------------------------------------------------------|

| 31.0 | LS10   | Physical Link Status of 10 Mbps TP : Set for good link in 10 Base-T.               |

| 31.1 | LS100  | Physical Link Status of 100 Mbps TP : Set for good link in 100 Base-TX.            |

| 31.2 | LPNWAY | Link Partner Status : 1 to indicate link partner is capable of NWAY support, reset |

|      |        | for non-NWAY link partner.                                                         |

| 31.3 | ANCLPT | Autonegotiation Completion : Set to indicate that a normal NWAY state machine      |

|      |        | completion. Reset for incomplete.                                                  |

| 31.4 | 100TXF | NWAY 100 TX Full_duplex Mode : Set to indicate NWAY is settle down in 100 TX       |

|      |        | full duplex mode.                                                                  |

| 31.5 | 100TXH | NWAY 100 TX Half_dulpex Mode : Set to indicate NWAY is settle down in 100          |

|      |        | Base-T half duplex mode.                                                           |

| 31.6 | 10TXF  | NWAY 10 TX Full_duplex Mode : Set to indicate NWAY is settle down in 10 Base-      |

|      |        | T full duplex mode.                                                                |

| 31.7 | 10TXH  | NWAY 10 TX Half_duplex Mode : Set to indicate NWAY is settle down in 10            |

|      |        | Base-T half duplex mode.                                                           |

## GMAC Configuration A Register: GCA (Reg32h), R/W, default=00h

| Bit  | Symbol      | Description                                                                          |

|------|-------------|--------------------------------------------------------------------------------------|

| 32.0 | BPSCRM      | Bypass 100TX Scrambler: Default is 0, meaning enable scrambler during 100TX          |

|      |             | mode, set to disable scrambler.                                                      |

| 32.1 | PBW         | Packet Buffer Data Width : Default is 0. Meaning packet buffer data width is byte    |

|      |             | wide. Set for word (16 bit) wide packet buffer. For 8 bit system bus, the packet     |

|      |             | buffer bus width must be byte wide.                                                  |

| 32.2 | SLOWSRAM    | Slow SRAM select bit: Default is 0 meaning fast SRAM must be used (Taa <= 20ns       |

|      |             | ), if set , then Taa<= 70ns can be used. Slow SRAM will reduce packet through put,   |

|      |             | therefore, if high speed host is intended, then SRAM should be fast otherwise, FIFO  |

|      |             | underrun or overrun can happen.                                                      |

| 32.3 | ARXERRB     | Accept RX packet with error : Default is reset to receive packets with error, set to |

|      |             | reject packets with error, packet memory will not contain packet with RW, FO, CRC    |

|      |             | errors.                                                                              |

| 32.4 | MIISEL      | Default = 0 after reset, on-chip tranceiver is used. Set by software to enable MII   |

|      |             | interface.                                                                           |

| 32.5 | AUTOPUB     | Auto Page Update option :                                                            |

|      |             | Set to disable the automatic host page update during the host DMAs. Reset to         |

|      |             | enable the host page update for the RRP, TWP registers. Default is reset.            |

| 32.6 | TXFIFOCNTEN | Default=0, after rest which means Reg 3E & 3F (TXFIFOCNT) are not used. This         |

|      |             | option is only good for a byte-base host transfer. For host which do word/double     |

|      |             | word transfer, this bit must be set to 1 to force TXFIFO use actual packet length    |

|      |             | for transmission.                                                                    |

| 32.7 | reserved    |                                                                                      |

## GMAC Configuration B Register: GCB (Reg33h), R/W

| Bit    | Symbol    | Description |                   |                     |                |

|--------|-----------|-------------|-------------------|---------------------|----------------|

| 33.1-0 | TTHD[1:0] | Transmit Fl | FO Threshold : [  | Default is 00       |                |

|        |           | TTHD1       | TTHD0             | FIFO depth          | aggressiveness |

|        |           | 0           | 0                 | 1/2                 | medium         |

|        |           | 0           | 1                 | 1/4                 | least          |

|        |           | 1           | 0                 | 3/4                 | most           |

|        |           | 1           | 1                 | reserved            | reserved       |

| 33.3-2 | RTHD[1:0] | Receive FI  | FO Threshold : D  | efault is 00        |                |

|        |           | RTHD1       | RTHD0             | FIFO depth          | aggressiveness |

|        |           | 0           | 0                 | 1/2                 | medium         |

|        |           | 0           | 1                 | 1/4                 | most           |

|        |           | 1           | 0                 | 3/4                 | least          |

|        |           | 1           | 1                 | reserved            | reserved       |

| 33.4   | SRAMELEN  | SRAM Ear    | y Latch Enable :  | Default = 0. Set    | to enable.     |

| 33.5   | X4ELEN    | X4 FIFO Ea  | arly Latch Enable | e : Defautl = 0. Se | et to enable.  |

| 33.6   | DREQB2EN  | DREQB NE    | EW Timing Enabl   | e : Default = 0. S  | et to enable.  |

| 33.7   | reserved  |             |                   |                     |                |

|        |           |             |                   |                     |                |

## Reserved (Reg34h/35h/36h/37h), R/W

| Bit    | Symbol   | Description |

|--------|----------|-------------|

| 34.7-0 | Reserved |             |

| 35,7-0 |          |             |

| 36.7-0 |          |             |

| 38.8-0 |          |             |

| 34.7-0 | Reserved |             |

| 35,7-0 |          |             |

| 36.7-0 |          |             |

| 37.7-0 |          |             |

## Reserved (Reg39h/38h), R/W, default=0000h

| Bit    | Symbol   | Description |

|--------|----------|-------------|

| 38.7-0 | Reserved |             |

| 39.7-0 | Reserved |             |

#### Reserved (Reg3Ah), default=00h

| Bit    | Symbol   | Description |  |

|--------|----------|-------------|--|

| 3A.7-0 | Reserved |             |  |

## Link Partner Link Code Register : LPC, Reg3Bh, RO

| Bit  | Symbol | Description                                                 |

|------|--------|-------------------------------------------------------------|

| 3B.0 | LPC[0] | Link Partner Link Code A0 : 10 Base-T half duplex ability   |

| 3B.1 | LPC[1] | Link Partner Link Code A1 : 10 Base-T full duplex ability   |

| 3B.2 | LPC[2] | Link Partner Link Code A2 : 100 Base-TX half duplex ability |

| 3B.3 | LPC[3] | Link Partner Link Code A3 : 100 Base-TX full duplex ability |

| 3B.4 | LPC[4] | Link Partner Link Code A4 : 100 Base-T4 ability             |

| 3B.5 | LPC[5] | Link Partner Link Code RF bit : Remote Fault bit            |

| 3B.6 | LPC[6] | Link Partner Link Code Ack bit : Acknowledge bit            |

| 3B.7 | LPC[7] | Link Partner Link Code NP bit : Next Page bit               |

|      |        |                                                             |

#### TX/RX DMA Status Register: Reg3Ch, R/W, default=00h

| Bit    | Symbol      | Description                                                                   |

|--------|-------------|-------------------------------------------------------------------------------|

| 3C.7-4 | TXDMA[3:0]* | TX DMA State Indicators : For internal diagnostic purpose indicating TX DMA's |

|        |             | current status.                                                               |

|        |             | TXDMA3 is TX status error bit, set to indicate error during transmission.     |

|        |             | TXDMA2 is TX FIFO underflow error.                                            |

| 3C.3-0 | RXDMA[3:0]* | RX DMA State Indicators : For internal diagnostic purpose indicating RX DMA's |

|        |             | current status.                                                               |

|        |             | RXDMA3 is RX status error bit, set to indicate error during receive.          |

|        |             | RXDMA2 is RX FIFO overflow error.                                             |

| TXDMA[1:0] | State Description       | RXDMA[1:0] | State Description       |

|------------|-------------------------|------------|-------------------------|

| 00         | Idle                    | 00         | Idle                    |

| 01         | Read TX Description     | 01         | Receive Current Packet  |

| 10         | Transmit Current Packet | 10         | Write TX Description    |

| 11         | Write TX Description    | 11         | Run Frame/Reset RX FIFO |

## MISC Control Register : MISC1, Reg3Dh, R/W, default=3Ch

| Bit  | Symbol    | Description                                                                           |

|------|-----------|---------------------------------------------------------------------------------------|

| 3D.0 | BURSTDMA  | reserved for internal DMA burst control, default = 0 after reset.                     |

| 3D.1 | DISLDMA*  | Disable Local DMA arbitration : Default is 0 after reset, meaning local DMAs an       |

|      |           | enabled in the SRAM bus arbitration. Set to disable the local DMA arbitration on      |

|      |           | when the Reg02h.0 TEST bit is also set. It is used to force the overrun or the        |

|      |           | underrun error for the test purpose.                                                  |

| 3D.2 | TPF       | 10 Base-T Port Full Duplex capability bit in the linkcode word : Default is set       |

|      |           | enable advertising the 10 Base-T Full duplex capability. Reset to disable adverti     |

|      |           | ing this capability in the outgoing NWAY's linkcode word.                             |

| 3D.3 | TPH       | 10 Base-T Port Half Duplex capability bit in the linkcode word : Default is set       |

|      |           | enable advertising the 10 Base-T Half duplex capability. Reset to disable adverti     |

|      |           | ing this capability in the outgoing NWAY's linkcode word.                             |

| 3D.4 | TXF       | 100 Base-TX Full Duplex capability bit in the linkcode word : Default is set to enab  |

|      |           | advertising the 100 Base-TX Full duplex capability. Reset to disable advertising      |

|      |           | this capability in the outgoing NWAY's linkcode word.                                 |