# 16-Channel Constant Current LED Driver With Ghost Image Abatement

### **General Description**

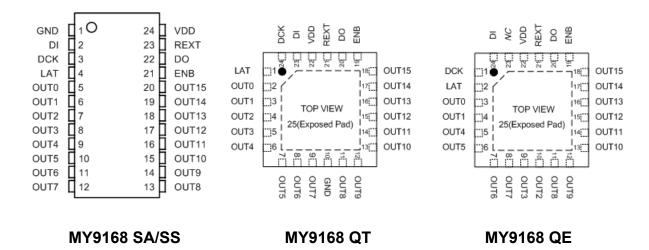

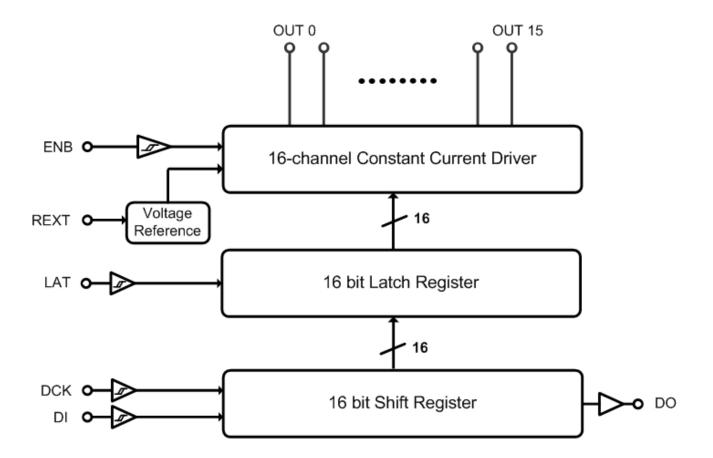

The MY9168 16-channel constant current LED driver with ghost image abatement is suitable for multiplexing display system. The device has wide supply voltage range (3.0V ~ 5.5V) and provides 16 open-drain constant current sinking outputs that are rated to 16V and delivers up to 55mA of high accuracy current to each string of LED. The current at each output is programmable by means of an external current-sensing resistor. The MY9168 features a fast 30MHz DCK input, allowing a wide LED dimming (on/off) range to be implemented. The MY9168 offers a 4-wire serial interface, a 16-bit shift register, and a 16-bit transparent latch. The serial interface microcontroller to configure the output channels using four inputs (DI, DCK, LAT, and ENB) and a data output (DO). DO allows multiple drivers to be cascaded and operated together.

The MY9168's on-board pass elements minimize the need for external components, while at the same time, providing  $\pm 1\%$  (typ.) LED current accuracy. Additional features include a  $\pm 0.1\%$  regulated output current capability and 30ns fast output transient response.

The MY9168 is available in a 24-pin SOP/SSOP/QFN package and specified over the -40°C to +85°C ambient temperature range.

### **Applications**

- ☐ Indoor and Outdoor LED Video Displays

- □ Variable Message Sign (VMS)

- Dot Matrix Module

- □ Architectural and Decorative Lighting

- □ Industrial Lighting

- ☐ LCD Display Backlighting

#### **Features**

- **♦** 3.0V ~ 5.5V Operating supply voltage

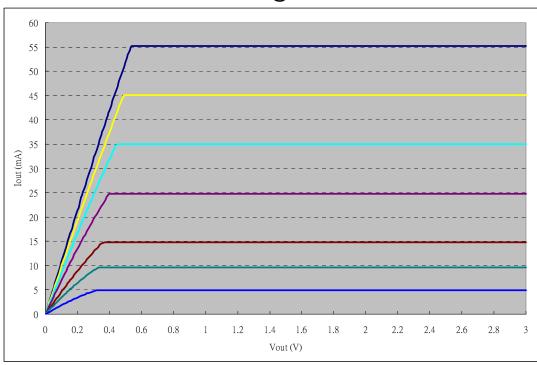

- ♦ 3~55mA/5V Constant current output range

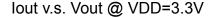

- ♦ 3~35mA/3.3V Constant current output range

- ◆ 16V Rated output channels for long LED strings

- → ±1% (typ.) Current accuracy between channels

- ◆ ±0.1% Output current regulation capability

- **◆ 30MHz Clock frequency for data transfer**

- **♦** Current setting by one external resister

- **♦** Schmitt trigger input

- **♦** Power on reset

- ◆ Stagger output delay

- ◆ Fast current transient response

- **♦** Ghost image abatement

- ◆ Low knee voltage for constant current

- ♦ High level HBM ESD protection (lout pin > 8000V)

- → -40°C to +85°C Ambient temperature range

#### Order information

| Part     | Package Information   |               |  |  |  |  |  |

|----------|-----------------------|---------------|--|--|--|--|--|

| MY9168SA | SOP24-236mil-1.0mm    | 2000 pcs/Reel |  |  |  |  |  |

| MY9168SS | SSOP24-150mil-0.635mm | 2500 pcs/Reel |  |  |  |  |  |

| MY9168QT | QFN24-4mmx4mm-0.5mm   | 3000 pcs/Reel |  |  |  |  |  |

| MY9168QE | QFN24-4mmx4mm-0.5mm   | 3000 pcs/Reel |  |  |  |  |  |

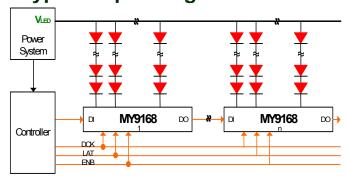

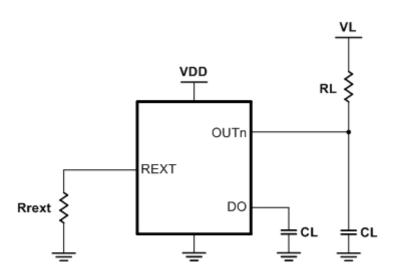

#### **Typical Operating Circuits**

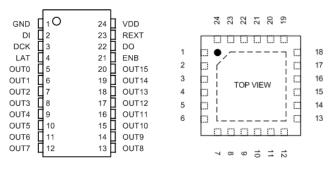

### **Pin Configuration**

Nov. 2012 Ver. 0.2 MY-Semi Inc. \_ 0

#### **Pin Description**

|       | PIN No.    |                            | PIN No.  |                                                                                                       | DIN NAME | FUNCTION |  |  |  |

|-------|------------|----------------------------|----------|-------------------------------------------------------------------------------------------------------|----------|----------|--|--|--|

| SA/SS | QT         | QE                         | PIN NAME | FUNCTION                                                                                              |          |          |  |  |  |

| 1     | 10, 25     | 25                         | GND      | Ground terminal.                                                                                      |          |          |  |  |  |

| 2     | 23         | 24                         | DI       | Serial data input terminal.                                                                           |          |          |  |  |  |

| 3     | 24         | 1                          | DCK      | Synchronous clock input terminal for serial data transfer. Data is sampled at the rising edge of DCK. |          |          |  |  |  |

| 4     | 1          | 2                          | LAT      | Input terminal of data strobe. Data on shift register is sampled at the rising edge of LAT.           |          |          |  |  |  |

| 5~20  | 2~9, 11~18 | 3, 4, 10, 9, 5~8,<br>11~18 | OUT0~15  | Sink constant-current outputs (open-drain).                                                           |          |          |  |  |  |

| 21    | 19         | 19                         | ENB      | Output enable terminal:  'H' for all outputs are turned off,  'L' for all outputs are active.         |          |          |  |  |  |

| 22    | 20         | 20                         | DO       | Serial data output terminal.                                                                          |          |          |  |  |  |

| 23    | 21         | 21                         | REXT     | External resistors connected between REXT and GND for output current value setting.                   |          |          |  |  |  |

| 24    | 22         | 22                         | VDD      | Supply voltage terminal.                                                                              |          |          |  |  |  |

| _     | _          | 23                         | NC       | No connection.                                                                                        |          |          |  |  |  |

### **Block Diagram**

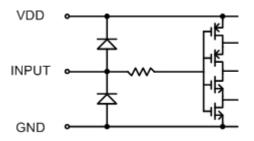

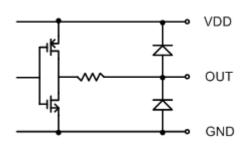

### **Equivalent Circuit of Inputs and Output**

#### 1. DCK, DI, LAT, ENB terminals

#### 2. DO terminal

### **Maximum Ratings** (Ta=25°C, Tj(max) = 150°C)

| maximam radings (1a-25 6, 1)(max) - 150 6) |          |                                |      |  |  |  |  |  |

|--------------------------------------------|----------|--------------------------------|------|--|--|--|--|--|

| CHARACTERISTIC                             | SYMBOL   | RATING                         | UNIT |  |  |  |  |  |

| Supply Voltage                             | VDD      | -0.3 ~ 7.0                     | V    |  |  |  |  |  |

| Input Voltage                              | VIN      | -0.3 ~ VDD+0.3                 | V    |  |  |  |  |  |

| Output Current                             | IOUT     | 55                             | mA   |  |  |  |  |  |

| Output Voltage                             | VOUT     | -0.3 ~ 16                      | V    |  |  |  |  |  |

| Input Clock Frequency                      | FDCK     | 30                             | MHz  |  |  |  |  |  |

| GND Terminal Current                       | IGND     | 900                            | mA   |  |  |  |  |  |

|                                            |          | 53.2 (SA:SOP-236mil-1.0mm )    |      |  |  |  |  |  |

| Thermal Resistance (On PCB)                | Rth(j-a) | 70.5 (SS:SSOP-150mil-0.635mm ) | °C/W |  |  |  |  |  |

|                                            |          | 36.9 (QT/QE:QFN24-4mmx4mm)     |      |  |  |  |  |  |

| Operating Supply Voltage                   | VDD      | 3.0 ~ 5.5                      | V    |  |  |  |  |  |

| Operating Ambient Temperature              | Тор      | -40 ~ 85                       | °C   |  |  |  |  |  |

| Storage Temperature                        | Tstg     | -55 ~ 150                      | °C   |  |  |  |  |  |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only and functional operation of the device at these or any other condition beyond those specified is not supported.

<sup>(2)</sup> All voltage values are with respect to ground terminal.

### Electrical Characteristics (VDD = 5.0 V, Ta = 25°C unless otherwise noted)

| CHARACTERISTIC                                | SYMBOL                    | CONDITION                                                                       | MIN.    | TYP.  | MAX.   | UNIT     |

|-----------------------------------------------|---------------------------|---------------------------------------------------------------------------------|---------|-------|--------|----------|

| Input Voltage "H" Level                       | VIH                       | CMOS logic level                                                                | 0.7VDD  | _     | VDD    |          |

| Input Voltage "L" Level                       | VIL                       | CMOS logic level                                                                | GND     | _     | 0.3VDD | V        |

| Output Leakage Current                        | ILK                       | VOUT = 16 V                                                                     | _       | _     | 0.1    | uA       |

| 0.44\/-14 (D0)                                | VOL                       | IOL = 1 mA                                                                      | _       | _     | 0.4    |          |

| Output Voltage (DO)                           | VOH                       | IOH= 1 mA                                                                       | VDD-0.4 | _     | _      | V        |

| Output Current Skew (Channel-to-Channel)*1    | dIOUT1                    | VOUT = 1.0 V                                                                    | _       | ±1.0  | ±3.0   | %        |

| Output Current Skew (Chip-to-Chip)*2          | dIOUT2                    | Rrext = 960 $\Omega$                                                            | _       | ±1.0  | ±3.0   | %        |

| Output Current Skew<br>(Channel-to-Channel)*1 | dIOUT3                    | VOUT = 1.0 V                                                                    | _       | ±1.5  | ±3.0   | %        |

| Output Current Skew (Chip-to-Chip)*2          | dIOUT4                    | Rrext = $6.4 \text{ K}\Omega$                                                   | _       | ±1.5  | ±3.0   | %        |

| Output Voltage Regulation*3                   | age Regulation*3 % / VOUT |                                                                                 | _       | ±.0.1 | _      | 0/ / / / |

| Supply Voltage Regulation*4                   | % / VDD                   | Rrext = 960 $\Omega$<br>VDD = 3 V ~ 5.5 V                                       | _       | ±0.6  | ±1     | - %/V    |

|                                               | I <sub>DD1(off)</sub>     | all pins are open<br>unless VDD and GND                                         | _       | 1.3   | 1.8    |          |

|                                               | I <sub>DD2(off)</sub>     | input signal is static<br>Rrext = $6.4 \text{ K}\Omega$<br>all outputs turn off | _       | 2.3   | 3.0    |          |

| Supply Current <sup>*5</sup>                  | I <sub>DD3(on)</sub>      | input signal is static<br>Rrext = 6.4 K $\Omega$<br>all outputs turn on         | _       | 2.6   | 3.4    | mA       |

|                                               | I <sub>DD4(off)</sub>     | input signal is static Rrext = $960 \Omega$ all outputs turn off                | _       | 4.7   | 6.1    |          |

|                                               | I <sub>DD5(on)</sub>      | input signal is static<br>Rrext = 960 $\Omega$<br>all outputs turn on           |         | 4.8   | 6.3    |          |

$$\Delta(\%) = \left[ \frac{Iout_n}{(Iout_0 + Iout_1 + ... + Iout_{15})} - 1 \right] * 100\%$$

Chip-to-Chip skew is defined by the formula below:

$$\Delta(\%) = \left[ \begin{array}{c} \frac{(Iout_0 + Iout_1 + ... + Iout_{15})}{16} - (Ideal \ Output \ Current) \\ \hline (Ideal \ Output \ Current) \end{array} \right] *100\%$$

\*1 Channel-to-channel skew is defined by the formula below: \*3 Output voltage regulation is defined by the formula below:

$$\Delta(\%) = \left[ \frac{Iout_n}{(Iout_0 + Iout_1 + ... + Iout_{15})} - 1 \right] *100\%$$

$$\Delta(\%/V) = \left[ \frac{Iout_n(@Vout_n = 3V) - Iout_n(@Vout_n = 1V)}{Iout_n(@Vout_n = 3V)} \right] * \frac{100\%}{3V - 1V}$$

$$\Delta \big(\%/V\big) = \left[\begin{array}{c} Iout_n(@V_{DD} = 5.5V) - Iout_n(@V_{DD} = 3V) \\ Iout_n(@V_{DD} = 3V) \end{array}\right] * \frac{100\%}{5.5V - 3V}$$

<sup>\*2</sup> Chip-to-Chip skew is defined by the formula below:

<sup>\*4</sup> Supply voltage regulation is defined by the formula below:

<sup>\*5</sup> IO excluded.

## **MY9168**

### Electrical Characteristics (VDD = 3.3 V, Ta = 25°C unless otherwise noted)

| CHARACTERISTIC                                | SYMBOL                | SYMBOL CONDITION                                                                |         | TYP. | MAX.   | UNIT     |  |

|-----------------------------------------------|-----------------------|---------------------------------------------------------------------------------|---------|------|--------|----------|--|

| Input Voltage "H" Level                       | VIH                   | CMOS logic level                                                                | 0.7VDD  |      | VDD    |          |  |

| Input Voltage "L" Level                       | VIL                   | CMOS logic level                                                                | GND     |      | 0.3VDD | V        |  |

| Output Leakage Current                        | ILK                   | VOUT = 16 V                                                                     | _       | _    | 0.1    | uA       |  |

| 0 4 434 % (DO)                                | VOL                   | IOL = 1 mA                                                                      | _       |      | 0.4    |          |  |

| Output Voltage (DO)                           | VOH                   | IOH= 1 mA                                                                       | VDD-0.4 |      |        | V        |  |

| Output Current Skew (Channel-to-Channel)*1    | dIOUT1                | VOUT = 1.0 V                                                                    | _       | ±1.0 | ±3.0   | %        |  |

| Output Current Skew (Chip-to-Chip)*2          | dIOUT2                | Rrext = 960 Ω                                                                   | _       | ±1.0 | ±3.0   | %        |  |

| Output Current Skew<br>(Channel-to-Channel)*1 | dIOUT3                | VOUT = 1.0 V                                                                    |         | ±1.5 | ±3.0   | %        |  |

| Output Current Skew<br>(Chip-to-Chip)*2       | dIOUT4                | Rrext = $6.4 \text{ K}\Omega$                                                   |         | ±1.5 | ±3.0   | %        |  |

| Output Voltage Regulation*3 % / VO            |                       | Rrext = 960 $\Omega$<br>VOUT = 1 V ~ 3 V                                        |         | ±0.1 | _      | - %/V    |  |

| Supply Voltage Regulation*4                   | % / VDD               | Rrext = 960 Ω<br>VDD = 3 V ~ 5.5 V                                              |         | ±0.7 | ±1     | - 70 / V |  |

|                                               | I <sub>DD1(off)</sub> | all pins are open unless VDD and GND                                            | _       | 0.7  | 1.0    |          |  |

|                                               | I <sub>DD2(off)</sub> | input signal is static<br>Rrext = $6.4 \text{ K}\Omega$<br>all outputs turn off | _       | 2.0  | 2.6    |          |  |

| Supply Current <sup>*5</sup>                  | I <sub>DD3(on)</sub>  | input signal is static<br>Rrext = 6.4 KΩ<br>all outputs turn on                 |         | 2.3  | 3.0    | mA       |  |

|                                               | IDD4(off)             | input signal is static Rrext = 960 $\Omega$ all outputs turn off                | _       | 4.1  | 5.4    |          |  |

|                                               | I <sub>DD5(on)</sub>  | input signal is static Rrext = 960 $\Omega$ all outputs turn on                 | _       | 4.2  | 5.5    |          |  |

<sup>\*1</sup> Channel-to-channel skew is defined by the formula below:

$\Delta(\%) = \left[\begin{array}{c} Iout_n \\ \hline (Iout_0 + Iout_1 + ... + Iout_{15}) \end{array} - 1\right] * 100\%$

\*3 Output voltage regulation is defined by the formula below:

$$\Delta \big(\% / V \big) = \Big[ \frac{Iout_n(@Vout_n = 3V) - Iout_n(@Vout_n = 1V)}{Iout_n(@Vout_n = 3V)} \Big] * \frac{100\%}{3V - 1V}$$

$$\Delta(\%) = \left[ \begin{array}{c} \frac{(Iout_0 + Iout_1 + ... + Iout_{15})}{16} - (Ideal \ Output \ Curren) \\ \hline (Ideal \ Output \ Curren) \end{array} \right] *100\%$$

$$\Delta(\%/V) = \left[ \frac{Iout_n(@V_{DD} = 5.5V) - Iout_n(@V_{DD} = 3V)}{Iout_n(@V_{DD} = 3V)} \right] * \frac{100\%}{5.5V - 3V}$$

$<sup>^{*2}</sup>$  Chip-to-Chip skew is defined by the formula below:

<sup>\*5</sup> IO excluded.

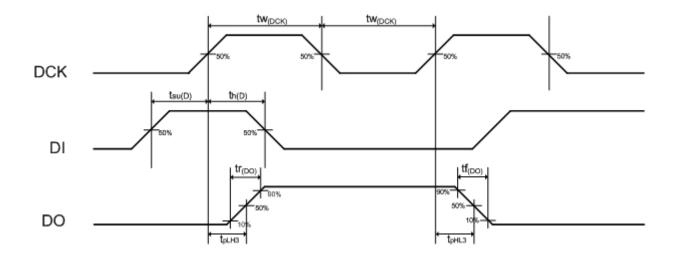

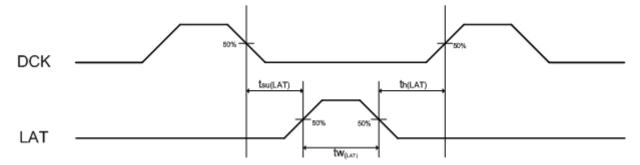

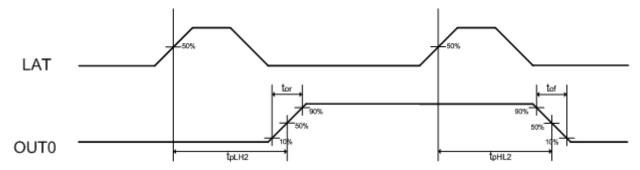

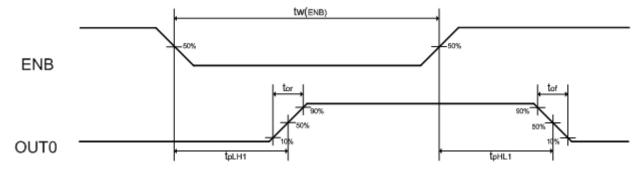

### **Switching Characteristics** (VDD = 5.0V, Ta = 25°C unless otherwise noted)

| CHAR                           | ACTERISTIC                                         | SYMBOL               | CONDITION            | MIN. | TYP. | MAX. | UNIT |

|--------------------------------|----------------------------------------------------|----------------------|----------------------|------|------|------|------|

|                                | ENB-to-OUT0                                        | tpLH1                |                      | _    | 26.9 | _    |      |

| Propagation Delay              | LAT-to-OUT0                                        | tpLH2                |                      | _    | 25.1 | _    |      |

| (LIOTI)                        | ('L to 'H')  DCK-DO tpLH3                          |                      | _                    | 22.8 | _    |      |      |

|                                | ENB-to-OUT0                                        | tpHL1                |                      | _    | 24.7 | _    |      |

| Propagation Delay ('H' to 'L') | LAT-to-OUT0                                        | tpHL2                |                      |      | 21.8 | _    |      |

| (11 to L)                      | DCK-DO                                             | tpHL3                | VIH = VDD            | _    | 26.3 | _    |      |

|                                | ENB                                                | tw <sub>(ENB)</sub>  | VIL = GND            | 20   |      | _    |      |

| Pulse Duration                 | LAT                                                | tw <sub>(LAT)</sub>  | Rrext = 960 $\Omega$ | 20   |      |      |      |

| Puise Duration                 | DCK                                                | tw <sub>(DCK)</sub>  | VL =5.0 V            | 15   |      |      | ns   |

| Setup Time                     | LAT                                                | tsu <sub>(LAT)</sub> | RL = 150 Ω           | 5    | _    |      |      |

| Setup Time                     | DI                                                 | tsu <sub>(D)</sub>   |                      | 3    |      |      |      |

| Hold Time                      | LAT                                                | th <sub>(LAT)</sub>  | CL = 13 pF           | 20   |      |      |      |

| Hold Time                      | DI                                                 | th <sub>(D)</sub>    |                      | 4    |      |      |      |

| DO Rise Time                   |                                                    | tr <sub>(DO)</sub>   |                      |      | 14.2 | _    |      |

| DO Fall Time                   |                                                    | tf <sub>(DO)</sub>   |                      |      | 15.1 |      |      |

| Output Current Rise Time       |                                                    | tor                  |                      |      | 10.0 |      |      |

| Output Current Fa              | II Time                                            | tof                  |                      |      | 20.0 | _    |      |

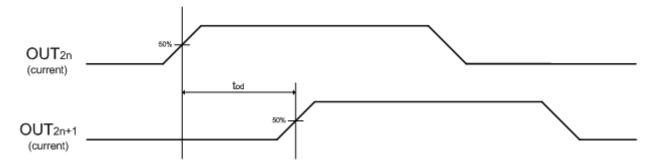

| Output Delay Time              | e (OUT <sub>(2n)</sub> -to-OUT <sub>(2n+1)</sub> ) | tod                  |                      |      | 0.5  | _    |      |

### **Switching Characteristics** (VDD = 3.3V, Ta = 25°C unless otherwise noted)

| CHAR                           | ACTERISTIC                                         | SYMBOL               | CONDITION                       | MIN. | TYP. | MAX. | UNIT |

|--------------------------------|----------------------------------------------------|----------------------|---------------------------------|------|------|------|------|

|                                | ENB-to-OUT0                                        | tpLH1                |                                 | _    | 43.2 |      |      |

| Propagation Delay              | LAT-to-OUT0                                        | tpLH2                |                                 | _    | 35.9 | _    |      |

| ('L to 'H')  DCK-to-DO tpLH3   |                                                    | _                    | 28.4                            | _    |      |      |      |

|                                | ENB-to-OUT0                                        | tpHL1                |                                 | _    | 34.1 | _    |      |

| Propagation Delay ('H' to 'L') | LAT-to-OUT0                                        | tpHL2                |                                 | _    | 30.1 | _    |      |

| (H to L)                       | DCK-DO                                             | tpHL3                | VIH = VDD                       | _    | 29.9 | _    |      |

| Pulse Duration                 | ENB                                                | tw <sub>(ENB)</sub>  | VIL = GND  Rrext = 960 $\Omega$ | 20   |      |      |      |

|                                | LAT                                                | tw <sub>(LAT)</sub>  |                                 | 20   |      |      |      |

|                                | DCK                                                | tw <sub>(DCK)</sub>  | VL =5.0 V                       | 15   |      |      | ns   |

| Setup Time                     | LAT                                                | tsu <sub>(LAT)</sub> | RL = 150 Ω                      | 5    |      |      |      |

| Setup Time                     | DI                                                 | tsu <sub>(D)</sub>   |                                 | 3    |      |      |      |

| Hold Time                      | LAT                                                | th <sub>(LAT)</sub>  | CL = 13 pF                      | 20   |      |      |      |

| Hold Time                      | DI                                                 | th <sub>(D)</sub>    |                                 | 4    |      |      |      |

| DO Rise Time                   |                                                    | tr <sub>(DO)</sub>   |                                 |      | 18.2 |      |      |

| DO Fall Time                   |                                                    | tf <sub>(DO)</sub>   |                                 |      | 19.9 |      |      |

| Output Current Rise Time       |                                                    | tor                  |                                 |      | 15.0 |      |      |

| Output Current Fa              | Output Current Fall Time                           |                      |                                 |      | 30.0 |      |      |

| Output Delay Time              | e (OUT <sub>(2n)</sub> -to-OUT <sub>(2n+1)</sub> ) | tod                  |                                 | _    | 0.5  |      |      |

Switching Characteristics Test Circuit

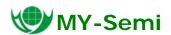

### **Timing Diagram**

### 1. DCK-DI, DO

### 2. DCK-LAT

### 3. LAT-OUT0

#### 4. ENB-OUT0

#### 5. OUT<sub>2n</sub>-OUT<sub>2n+1</sub>

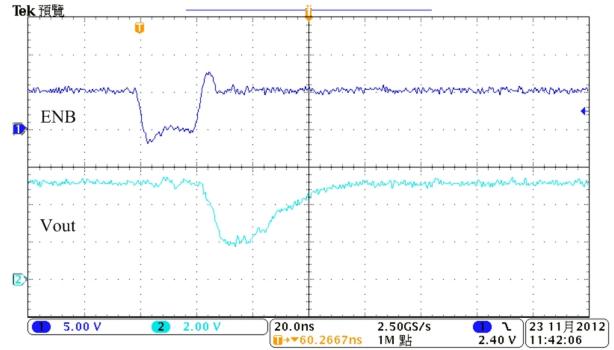

### **Fast Transient Response**

The MY9168 supports the fast transient response to make high image resolution possible. The ENB pulse width of 20ns is also good enough to get a complete Vout waveform. Following shows the waveform of VDD=5V, Rext=960  $\Omega$ , VLED=5V, RL=150  $\Omega$

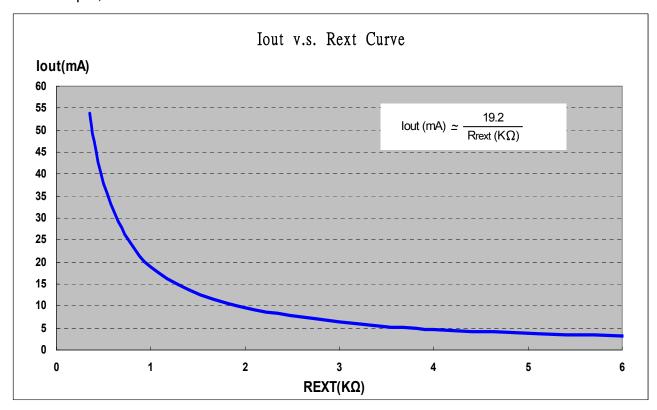

#### **Reference Resistor**

The constant current values are determined by an external resistor placed between REXT pin and GND pin. The following formula is utilized to calculate the current value:

$$Iout(mA) = \frac{19.2}{Rrext (K\Omega)}$$

Where Rrext is a resistor placed between REXT and GND

For example, lout is 20mA when Rrext=960 $\Omega$  and lout is 3mA when Rrext=6.4K $\Omega$

### **Constant-Current Output**

The current characteristics could maintain invariable in the influence of loading voltage. Therefore, the MY9168 could minimize the interference of different LED forward voltages and produce the constant current. The following figures illustrate the suitable output voltage should be determined in order to keep an excellent performance.

lout v.s. Vout @ VDD=5.0V

#### **Serial Data Interface**

The MY9168 will shifts the data to the register from the DI pin on the rising edge of data clock (DCK). After whole given frame data are transferred into 16bits shift register, the frame data are loaded into the latch register by a strobe signal (LAT). The latch action is triggered at the rising edge of LAT signal. And the serial data will be shifted out from the DO pin on the synchronization of the rising edge of DCK. Furthermore, the enable signal (ENB) will turn on all outputs when it is set to the low level.

### **Stagger Outputs Delay**

Large in-rush currents will be induced when the system activates all the outputs at once. To reduce this interference of EMI, the MY9168 is designed to have a constant length of delay time between two output groups. The two output groups individually are the first group OUT2n and the second group OUT2n+1.

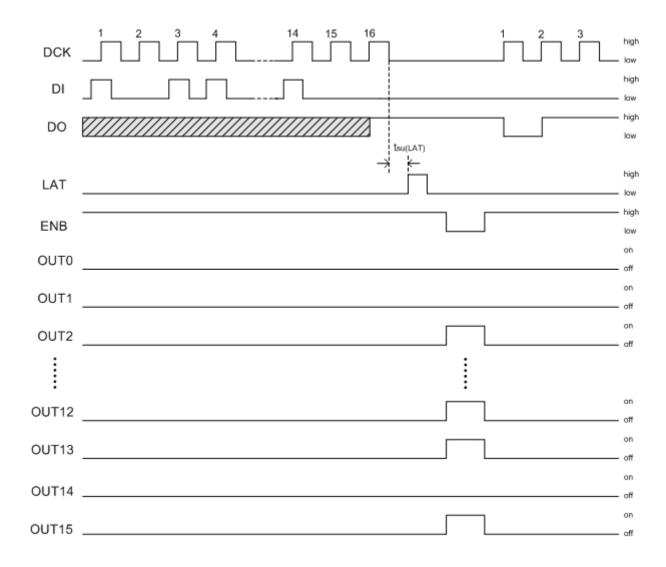

### **Power Dissipation**

When the 16 output channels are turned on, the practical power dissipation is determined by the following equation:

$$PD$$

(practical) =  $V_{DD} \times I_{DD} + V_{Out_{(0)}} \times I_{Out_{(0)}} \times Duty_{(0)} + \cdots + V_{Out_{(N)}} \times I_{Out_{(N)}} \times Duty_{(N)}$ , where  $N=1$  to 15

In secure operating conditions, the power consumption of an integrated chip should be less than the maximum permissible power dissipation which is determined by the package types and ambient temperature. The formula for maximum power dissipation is described as follows:

$$PD (max) = \frac{Tj(max)(\mathcal{C}) - Ta(\mathcal{C})}{Rth(j-a)(\mathcal{C}/Watt)}$$

The PD(max) declines as the ambient temperature raises. Therefore, suitable operating conditions should be designed with caution according to the chosen package and the ambient temperature. The following figure illustrates the relation between the maximum power dissipation and the ambient temperature in the four different packages.

#### Maximum Power Dissipation v.s. Ambient Temperature

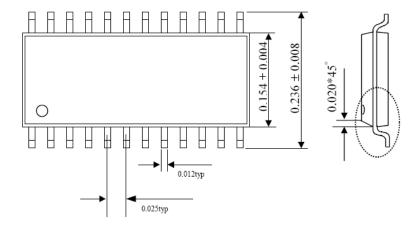

### **Package Outline Dimension**

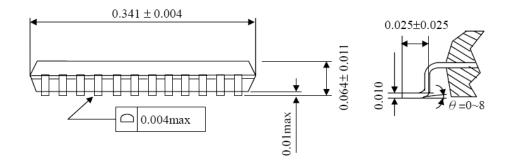

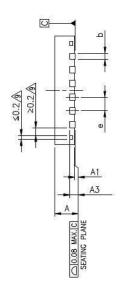

SSOP-150mil-0.635mm

Unit: inch

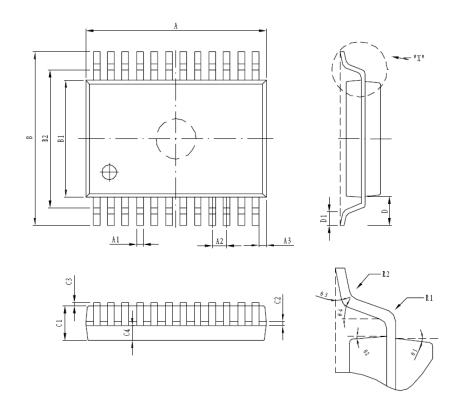

### **Package Outline Dimension**

SOP-236mil-1.0mm

| SYMBOL | DIMENS | ION(mm) | SYMBOL     | DIMENSION(mm) |      |  |  |

|--------|--------|---------|------------|---------------|------|--|--|

| SIMBOL | MIN.   | MAX.    | STMIDUL    | MIN.          | MAX. |  |  |

| A      | 12.9   | 13.1    | С3         | 0.05          | 0.2  |  |  |

| A1     | 0.30   | 0.50    | C4         | 0.80TYP       |      |  |  |

| A2     | 1.00   | TYP     | D          | 0.95TYP       |      |  |  |

| A3     | 0.87   | ГҮР     | D1         | 0.33          | 0.73 |  |  |

| В      | 7.60   | 8.20    | R1         | 0.2TYP        |      |  |  |

| B1     | 5.90   | 6.10    | R2         | 0.2TYP        |      |  |  |

| B2     |        |         | $\theta$ 1 | 8°TYP         |      |  |  |

| С      |        | 2.20    | $\theta 2$ | 10°TYP        |      |  |  |

| C1     | 1.70   | 1.90    | θ3         | 4°TYP         |      |  |  |

| C2     | 0.15   | 0.30    | $\theta 4$ | 5°TYP         |      |  |  |

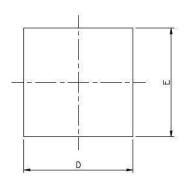

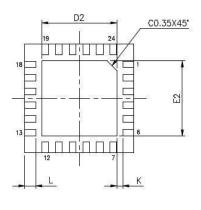

### **Package Outline Dimension**

#### QFN24-4mm x 4mm

| JEDEC OUTLINE | MO-220     |        |       |  |  |  |  |

|---------------|------------|--------|-------|--|--|--|--|

| PKG CODE      | WQFN(X424) |        |       |  |  |  |  |

| SYMBOLS       | MIN.       | MAX.   |       |  |  |  |  |

| Α             | 0.70       | 0.75   | 0.80  |  |  |  |  |

| A1            | 0.00       | 0.02   | 0.05  |  |  |  |  |

| A3            | 0.20 REF.  |        |       |  |  |  |  |

| b             | 0.18       | 0.25   | 0.30  |  |  |  |  |

| D             | 4          | .00 BS | C     |  |  |  |  |

| Е             | 4.00 BSC   |        |       |  |  |  |  |

| e             | 0.50 BSC   |        |       |  |  |  |  |

| K             | 0.20       | 0.000  | 88-88 |  |  |  |  |

- ALL DIMENSIONS ARE IN MILLIMETERS.

DIMENSION & APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.15mm AND 0.30mm FROM THE TERMINAL TIP. IF THE TERMINAL HAS THE OPTIONAL RADIUS ON THE OTHER END OF THE TERMINAL, THE DIMENSION & SHOULD NOT BE MEASURED IN THAT RADIUS AREA.

- 3. BILATERAL COPLANARITY ZONE APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

|      | E2   |      |      | D2   |      | L    |      | LEAD | FINISH   | JEDEC CODE |            |

|------|------|------|------|------|------|------|------|------|----------|------------|------------|

| MIN. | NOM. | MAX. | MIN. | NOM. | MAX. | MIN. | NOM. | MAX. | Pure Tin | PPF        | JEDEC CODE |

| 2.40 | 2.50 | 2.55 | 2.40 | 2.50 | 2.55 | 0.35 | 0.40 | 0.45 | ٧        | Х          | W(V)GGD-8  |

The products listed herein are designed for ordinary electronic applications, such as electrical appliances, audio-visual equipment, communications devices and so on. Hence, it is advisable that the devices should not be used in medical instruments, surgical implants, aerospace machinery, nuclear power control systems, disaster/crime-prevention equipment and the like. Misusing those products may directly or indirectly endanger human life, or cause injury and property loss.

MY-Semi Inc. will not take any responsibilities regarding the misusage of the products mentioned above. Anyone who purchases any products described herein with the above-mentioned intention or with such misused applications should accept full responsibility and indemnify. MY-Semi Inc. and its distributors and all their officers and employees shall defend jointly and severally against any and all claims and litigation and all damages, cost and expenses associated with such intention and manipulation.