NanoAmp Solutions, Inc. 670 N. McCarthy Blvd. Suite 220, Milpitas, CA 95035 ph: 408-935-7777, FAX: 408-935-7770 www.nanoamp.com

# N64T1630C1B

Advance Information

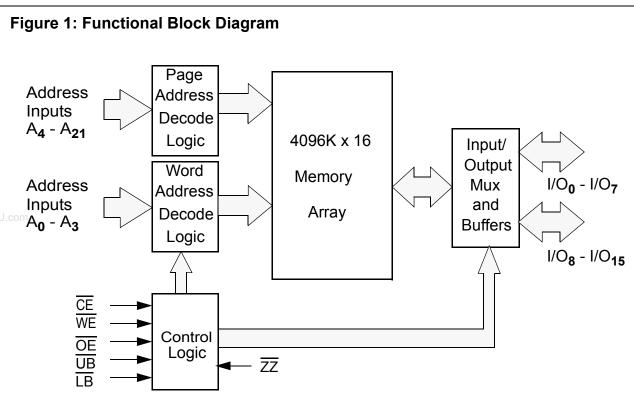

# 64Mb Ultra-Low Power Asynchronous CMOS PSRAM $4M \times 16$ Bits

## Overview

The N64T1630C1B is an integrated memory device containing a 64 Mbit Pseudo Static Random Access Memory using a self-refresh DRAM array organized as 4,194,304 words by 16 bits. It is designed to be compatible in operation and interface to standard 6T SRAMS. The device is designed for low standby and operating current and includes a power-down feature to automatically enter standby mode. The device includes a ZZ input for deep sleep as well as several other power saving modes: Partial Array Self Refresh mode where data is retained in a portion of the array and Temperature Compensated Refresh. Both these modes reduce standby current drain. The N64T1630C1B can be operated in a standard asynchronous mode and data can also be read in a 4-word page mode for fast access times. The die has separate power rails, VccQ and VssQ for the I/O to be run from a separate power supply from the device core.

## **Features**

· Dual voltage rails for optimum power & performance Vcc - 2.7V - 3.3V

Vccg - 2.7V to 3.3V

- Fast Cycle Times  $T_{ACC}$  < 70 nS (60ns future)  $T_{PACC} < 25 \text{ nS}$

- · Very low standby current I<sub>SB</sub> < 170µA

- Very low operating current Icc < 25mA

- PASR (Partial Array Self Refresh)

- TCR (Temperature Compensated Refresh)

#### **Table 1: Product Family**

| Part Number  | Package<br>Type | Operating<br>Temperature | Power<br>Supply | I/O Supply | Speed | Standby<br>Current (I <sub>SB</sub> ),<br>Max |

|--------------|-----------------|--------------------------|-----------------|------------|-------|-----------------------------------------------|

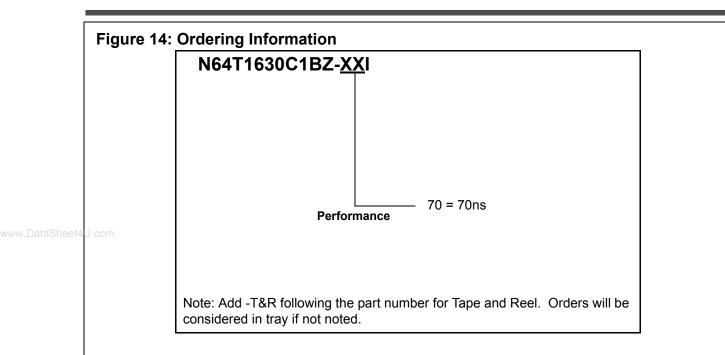

| N64T1630C1BZ | BGA             | -25°C to +85°C           | 2.7 - 3.3V      | 2.7 - 3.3V | 70ns  | 170μA                                         |

#### **Ball Congiguration**

| <b>U</b>              |                                                                                                 |                   |                 |                 |                  |                            |  |

|-----------------------|-------------------------------------------------------------------------------------------------|-------------------|-----------------|-----------------|------------------|----------------------------|--|

|                       | 1                                                                                               | 2                 | 3               | 4               | 5                | 6                          |  |

| А                     | LB                                                                                              | OE                | A <sub>0</sub>  | A <sub>1</sub>  | A <sub>2</sub>   | zz                         |  |

| В                     | I/O <sub>8</sub>                                                                                | UB                | A <sub>3</sub>  | A <sub>4</sub>  | CE               | I/O <sub>0</sub>           |  |

| С                     | I/O <sub>9</sub>                                                                                | I/O <sub>10</sub> | A <sub>5</sub>  | A <sub>6</sub>  | I/O <sub>1</sub> | I/O <sub>2</sub>           |  |

| D                     | V <sub>SSQ</sub>                                                                                | I/O <sub>11</sub> | A <sub>17</sub> | A <sub>7</sub>  | I/O <sub>3</sub> | $\mathbf{v}_{\mathrm{cc}}$ |  |

| Е                     | v <sub>ccq</sub>                                                                                | I/O <sub>12</sub> | A <sub>21</sub> | A <sub>16</sub> | I/O <sub>4</sub> | $\mathbf{v}_{\text{ss}}$   |  |

| F                     | I/O <sub>14</sub>                                                                               | I/O <sub>13</sub> | A <sub>14</sub> | A <sub>15</sub> | I/O <sub>5</sub> | I/O <sub>6</sub>           |  |

| G                     | I/O <sub>15</sub>                                                                               | A <sub>19</sub>   | A <sub>12</sub> | A <sub>13</sub> | WE               | I/O <sub>7</sub>           |  |

| Н                     | H A <sub>18</sub> A <sub>8</sub> A <sub>9</sub> A <sub>10</sub> A <sub>11</sub> A <sub>20</sub> |                   |                 |                 |                  |                            |  |

| 48 Pin BGA (top view) |                                                                                                 |                   |                 |                 |                  |                            |  |

| 6 x 8 mm              |                                                                                                 |                   |                 |                 |                  |                            |  |

|                       |                                                                                                 |                   |                 |                 |                  |                            |  |

### **Ball Description**

| Pin Name                            | Pin Function            |

|-------------------------------------|-------------------------|

| A <sub>0</sub> -A <sub>21</sub>     | Address Inputs          |

| WE                                  | Write Enable Input      |

| CE                                  | Chip Enable Input       |

| ZZ                                  | Deep Sleep Input        |

| OE                                  | Output Enable Input     |

| LB                                  | Lower Byte Enable Input |

| UB                                  | Upper Byte Enable Input |

| I/O <sub>0</sub> -I/O <sub>15</sub> | Data Inputs/Outputs     |

| V <sub>CC</sub>                     | Power                   |

| V <sub>SS</sub>                     | Ground                  |

| V <sub>CCQ</sub>                    | Power I/O only          |

| V <sub>SSQ</sub>                    | Ground I/O only         |

Stock No. 23357- Rev E 07/05

#### **Table 2: Functional Description**

| CE | WE | OE             | UB/LB          | ZZ | I/O <sup>1</sup> | MODE                 | POWER                |

|----|----|----------------|----------------|----|------------------|----------------------|----------------------|

| Н  | Х  | Х              | Х              | Н  | High Z           | Standby <sup>2</sup> | Standby              |

| L  | L  | Х <sup>3</sup> | L <sup>1</sup> | Н  | Data In          | Write                | Active               |

| L  | Н  | L              | L <sup>1</sup> | Н  | Data Out         | Read                 | Active               |

| L  | Н  | Н              | L              | Н  | High Z           | Active               | Standby <sup>4</sup> |

| L  | L  | Х              | Х              | L  | High-Z           | Set register         | Active               |

| Н  | Х  | Х              | Х              | L  | High-Z           | Deep Sleep           | Deep Sleep           |

1. When  $\overline{\text{UB}}$  and  $\overline{\text{LB}}$  are in select mode (low), I/O<sub>0</sub> - I/O<sub>15</sub> are affected as shown. When  $\overline{\text{LB}}$  only is in the select mode only I/O<sub>0</sub> - IO<sub>7</sub> are affected as shown. When  $\overline{\text{UB}}$  is in the select mode only I/O<sub>8</sub> - I/O<sub>15</sub> are affected as shown.

2. When the device is in standby mode, control inputs ( $\overline{WE}$ ,  $\overline{OE}$ ), address inputs and data input/outputs are internally isolated from any external influence and disabled from exerting any influence externally.

3. When  $\overline{\text{WE}}$  is invoked, the  $\overline{\text{OE}}$  input is internally disabled and has no effect on the circuit.

#### Table 3: Capacitance<sup>1</sup>

| ltem              | Symbol           | Test Condition                                                      | Min | Мах | Unit |

|-------------------|------------------|---------------------------------------------------------------------|-----|-----|------|

| Input Capacitance | C <sub>IN</sub>  | V <sub>IN</sub> = 0V, f = 1 MHz, T <sub>A</sub> = 25 <sup>o</sup> C |     | 6   | pF   |

| I/O Capacitance   | C <sub>I/O</sub> | V <sub>IN</sub> = 0V, f = 1 MHz, T <sub>A</sub> = 25 <sup>o</sup> C |     | 6   | pF   |

1. These parameters are verified in device characterization and are not 100% tested

# Table 4: Absolute Maximum Ratings<sup>1</sup>

| Item                                                           | Symbol              | Rating                        | Unit |

|----------------------------------------------------------------|---------------------|-------------------------------|------|

| Voltage on any pin relative to $V_{SS}$                        | V <sub>IN,OUT</sub> | -0.5 to V <sub>CCQ</sub> +0.3 | V    |

| Voltage on $V_{CC}$ Supply Relative to $V_{SS}$                | V <sub>CC</sub>     | -0.2 to 3.6                   | V    |

| Voltage on $V_{\mbox{CCQ}}$ Supply Relative to $V_{\mbox{SS}}$ | V <sub>CCQ</sub>    | -0.2 to 4.0                   | V    |

| Power Dissipation                                              | PD                  | 500                           | mW   |

| Storage Temperature                                            | T <sub>STG</sub>    | –55 to 150                    | °C   |

| Operating Temperature                                          | T <sub>A</sub>      | -25 to +85                    | °C   |

1. Stresses greater than those listed above may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### Table 5: Operating Characteristics (Over Specified Temperature Range)

| Item                                                                    | Symbol           | Comments                                                                                     | Min.                | Max.                  | Unit |

|-------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------|---------------------|-----------------------|------|

| Supply Voltage                                                          | V <sub>CC</sub>  |                                                                                              | 2.7                 | 3.3                   | V    |

| Supply Voltage for I/O                                                  | V <sub>CCQ</sub> |                                                                                              | Vcc                 | 3.3                   | V    |

| Input High Voltage                                                      | V <sub>IH</sub>  |                                                                                              | 0.8V <sub>CCQ</sub> | V <sub>CCQ</sub> +0.2 | V    |

| Input Low Voltage                                                       | V <sub>IL</sub>  |                                                                                              | -0.2                | 0.4                   | V    |

| Output High Voltage                                                     | V <sub>OH</sub>  | I <sub>OH</sub> = -0.2mA                                                                     | 0.8V <sub>CCQ</sub> |                       | V    |

| Output Low Voltage                                                      | V <sub>OL</sub>  | I <sub>OL</sub> = 0.2mA                                                                      |                     | 0.2V <sub>CCQ</sub>   | V    |

| Input Leakage Current                                                   | ILI              | $V_{IN}$ = 0 to $V_{CC}$                                                                     |                     | 1                     | μA   |

| Output Leakage Current                                                  | I <sub>LO</sub>  | OE = V <sub>IH</sub> or Chip Disabled                                                        |                     | 1                     | μA   |

| Read/Write Operating Current <sup>1</sup>                               | I <sub>CC</sub>  | V <sub>IN</sub> =V <sub>CCQ</sub> or 0V<br>Chip Enabled, I <sub>OUT</sub> = 0                |                     | 25                    | mA   |

| Page Mode Operating Current                                             | I <sub>CCP</sub> | V <sub>IN</sub> =V <sub>CCQ</sub> or 0V<br>Chip Enabled, I <sub>OUT</sub> = 0                |                     | 15                    | mA   |

| Standby Current <sup>2</sup><br>V <sub>IN</sub> = V <sub>CC</sub> or 0V | I <sub>SB</sub>  | $V_{IN} = V_{CC} \text{ or } 0V$<br>Chip Disabled<br>$V_{CC} = V_{CC}MAX, t_A = 85^{\circ}C$ | 100                 | 170                   | μA   |

1. This parameter is specified with the outputs disabled to avoid external loading effects. The user must add current required to drive output capacitance expected in the actual system.

2. This device assumes a standby mode if the chip is disabled ( $\overline{CE}$  high). In order to achieve low standby current all inputs must be within 0.2 volts of either VCC or VSS.

#### Table 6: Timing Test Conditions

| Item                                  |                                     |

|---------------------------------------|-------------------------------------|

| Input Pulse Level                     | V <sub>SS</sub> to V <sub>CCQ</sub> |

| Input Rise and Fall Time (10% to 90%) | 1.6ns                               |

| Input Timing Reference Levels         | 0.5 V <sub>CCQ</sub>                |

| Output Timing Reference Levels        | 0.5 V <sub>CCQ</sub>                |

| Operating Temperature                 | -25 °C to +85 °C                    |

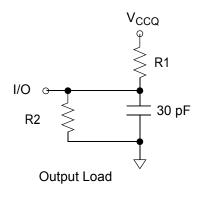

### Figure 2: Output Load Circuit

www.DataSheet4U.com

### Table 7: Ouput Load

| VCCQ | R1/R2 |

|------|-------|

| 3.0V | 4.5KΩ |

# N64T1630C1B **Advance Information**

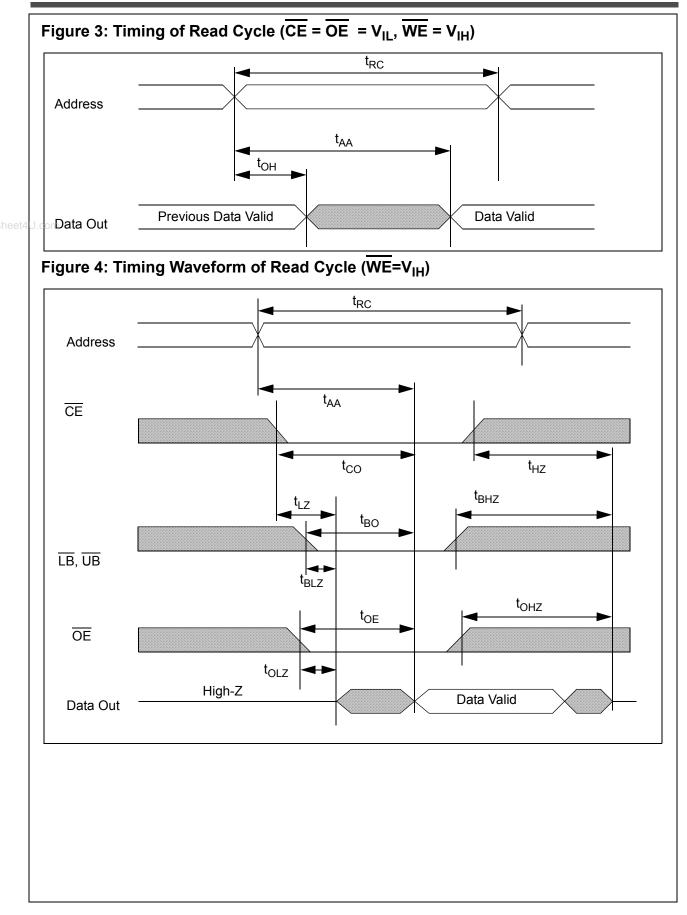

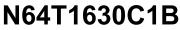

Table 8. Timings

|       | <b>H</b> ereit                       |                                     | -   | 70                                                                                                                                                                                                                                                                         |        |

|-------|--------------------------------------|-------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|       | Item                                 | Symbol                              | Min | Max                                                                                                                                                                                                                                                                        | – Unit |

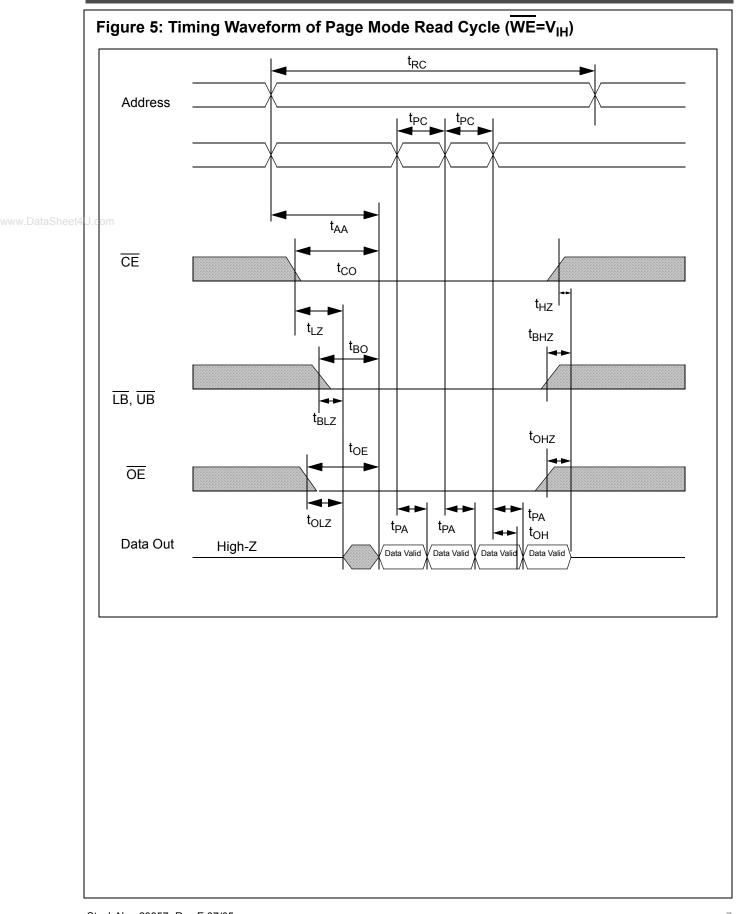

|       | Read Cycle Time                      | t <sub>RC</sub>                     | 70  | 20k                                                                                                                                                                                                                                                                        | ns     |

|       | Page Mode Cycle Time                 | t <sub>PC</sub>                     | 25  |                                                                                                                                                                                                                                                                            | ns     |

|       | Address Access Time                  | t <sub>AA</sub>                     |     | 70                                                                                                                                                                                                                                                                         | ns     |

|       | Page Mode Access Time                | t <sub>PA</sub>                     |     | 25                                                                                                                                                                                                                                                                         | ns     |

|       | Chip Enable to Valid Output          | t <sub>co</sub>                     |     | 70                                                                                                                                                                                                                                                                         | ns     |

|       | Output Enable to Valid Output        | $t_{RC}$ 70         20k $t_{PC}$ 25 | ns  |                                                                                                                                                                                                                                                                            |        |

| Read  | Byte Select to Valid Output          | t <sub>BO</sub>                     |     | 70                                                                                                                                                                                                                                                                         | ns     |

| Cycle | Chip Enable to Low-Z output          | t <sub>LZ</sub>                     | 10  |                                                                                                                                                                                                                                                                            | ns     |

| -     | Output Enable to Low-Z Output        | t <sub>OLZ</sub>                    | 5   |                                                                                                                                                                                                                                                                            | ns     |

| -     | Byte Select to Low-Z Output          |                                     | 10  |                                                                                                                                                                                                                                                                            | ns     |

|       | Chip Disable to High-Z Output        | t <sub>HZ</sub>                     | 0   | 8                                                                                                                                                                                                                                                                          | ns     |

| -     | Output Disable to High-Z Output      | t <sub>онz</sub>                    | 0   | 8                                                                                                                                                                                                                                                                          | ns     |

| -     | Byte Select Disable to High-Z Output |                                     | 0   | Max         20k         70         25         70         20         70         20         70         20         70         20         70         20         70         20k         20k         20k         20k         20k         20k         20k         20k         20k | ns     |

|       | Output Hold from Address Change      | t <sub>OH</sub>                     | 5   | Max<br>20k<br>70<br>25<br>70<br>20<br>70<br>20<br>70<br>20k<br>20k<br>20k<br>20k<br>20k                                                                                                                                                                                    | ns     |

|       |                                      |                                     | L   |                                                                                                                                                                                                                                                                            |        |

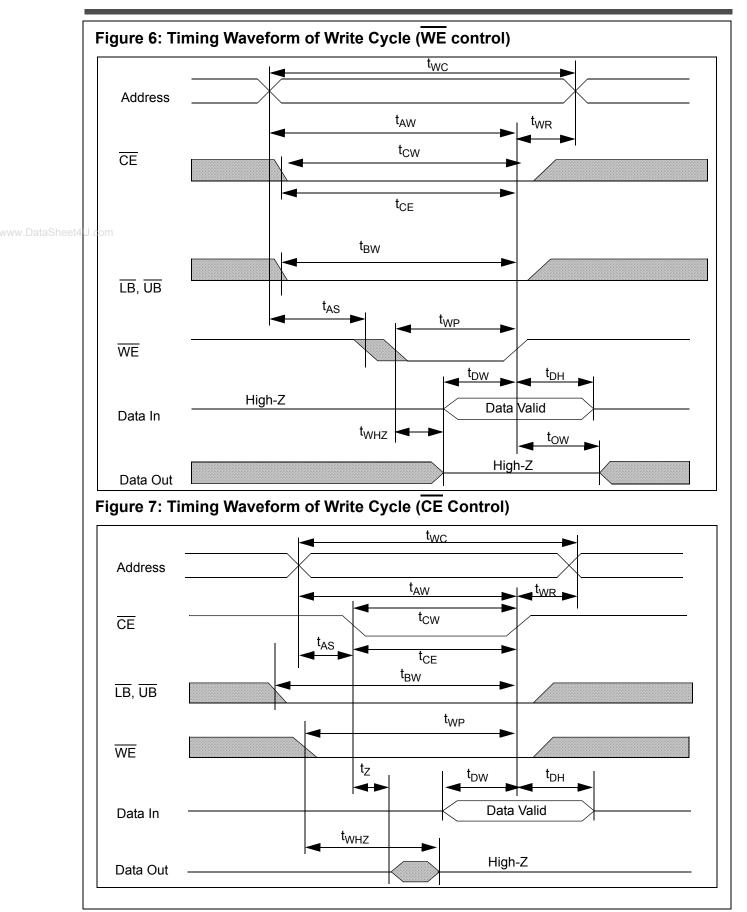

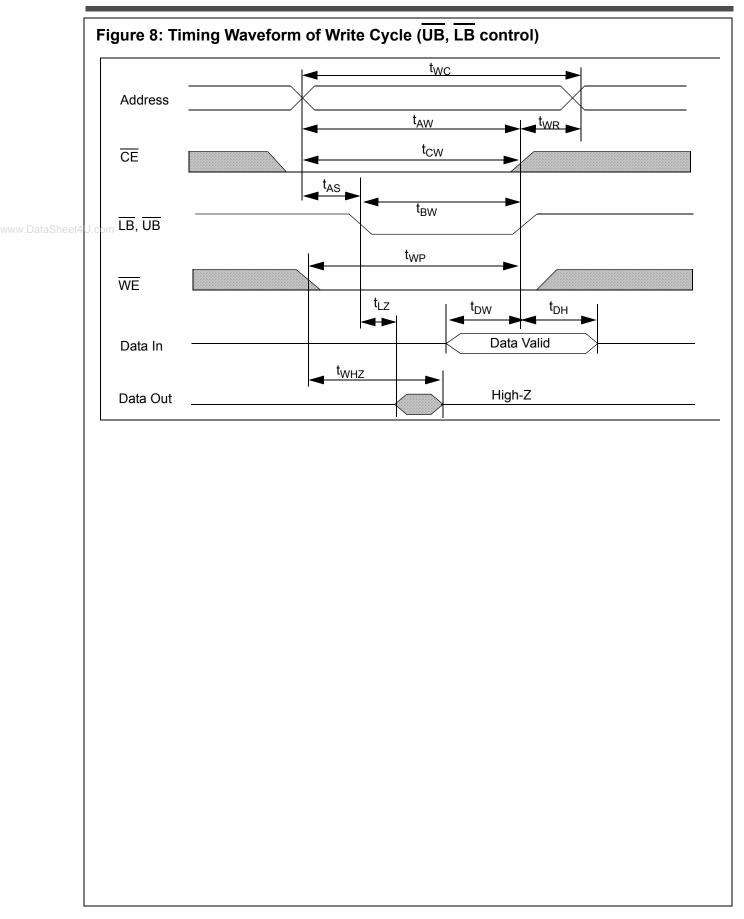

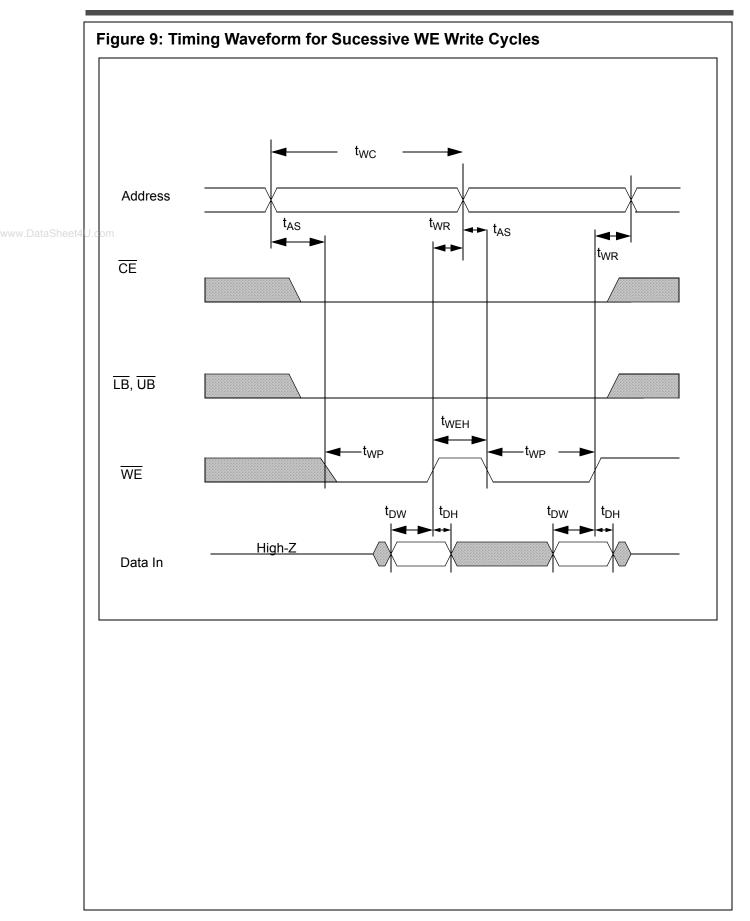

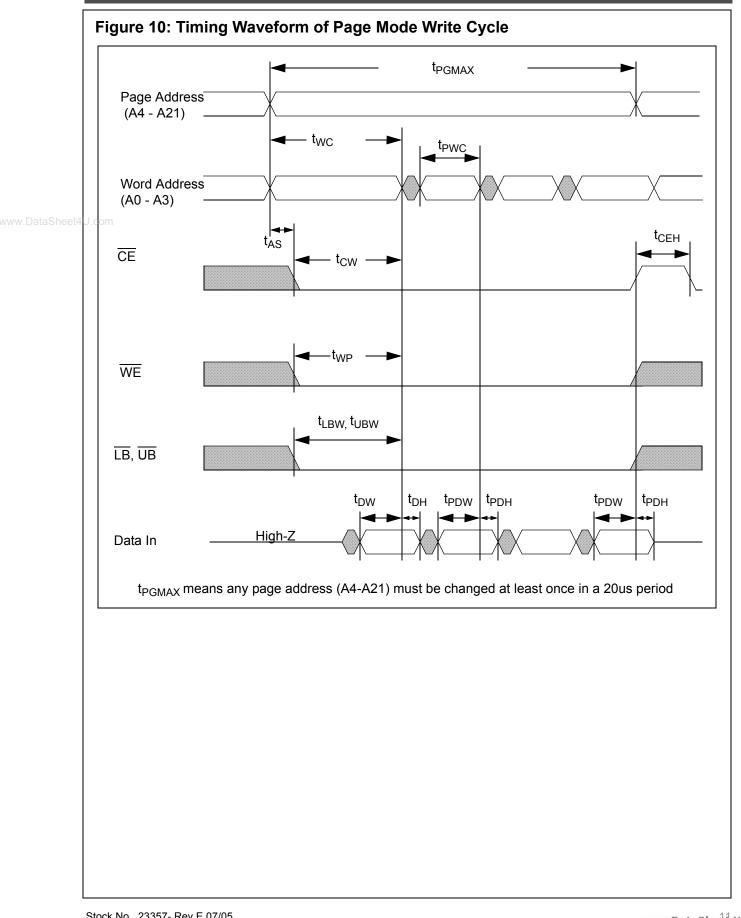

| -     | Write Cycle Time                     | t <sub>WC</sub>                     | 70  | 20k                                                                                                                                                                                                                                                                        | ns     |

|       | Page Mode Max Write Cycle            | t <sub>PGMAX</sub>                  |     | 20k                                                                                                                                                                                                                                                                        | ns     |

|       | Chip Enable Active Time              | t <sub>CE</sub>                     |     | 20k                                                                                                                                                                                                                                                                        | ns     |

|       | Chip Enable HIGH Time                | t <sub>CEH</sub>                    | 5   |                                                                                                                                                                                                                                                                            | ns     |

|       | Chip Enable to End of Write          | t <sub>CW</sub>                     | 70  |                                                                                                                                                                                                                                                                            | ns     |

|       | Address Valid to End of Write        | t <sub>AW</sub>                     | 70  |                                                                                                                                                                                                                                                                            | ns     |

|       | Byte Select to End of Write          | t <sub>BW</sub>                     | 70  |                                                                                                                                                                                                                                                                            | ns     |

| Write | Chip Enable to Low-Z                 | t <sub>LZ</sub>                     | 10  |                                                                                                                                                                                                                                                                            | ns     |

| Cycle | Write Pulse Width                    | t <sub>WP</sub>                     | 45  |                                                                                                                                                                                                                                                                            | ns     |

|       | Write Recovery Time                  | t <sub>WR</sub>                     | 0   |                                                                                                                                                                                                                                                                            | ns     |

|       | Write to High-Z Output               | t <sub>WHZ</sub>                    | 0   | 8                                                                                                                                                                                                                                                                          | ns     |

|       | Address Setup Time                   | t <sub>AS</sub>                     | 0   |                                                                                                                                                                                                                                                                            | ns     |

|       | Data to Write Time Overlap           | t <sub>DW</sub>                     | 25  |                                                                                                                                                                                                                                                                            | ns     |

|       | Data Hold from Write Time            | t <sub>DH</sub>                     | 0   |                                                                                                                                                                                                                                                                            | ns     |

|       | End Write to Low-Z Output            | t <sub>ow</sub>                     | 5   |                                                                                                                                                                                                                                                                            | ns     |

|       | WE High Time                         | t <sub>WEH</sub>                    | 7.5 | Max         20k         70         25         70         20         70         20         70         20         70         20         70         20         70         20k         20k         20k         20k         20k         20k         20k         20k         20k | ns     |

|       | Page Write Cycle Time                | t <sub>PW/C</sub>                   | 25  |                                                                                                                                                                                                                                                                            | ns     |

|       | Page Mode Data to Write Time Overlap |                                     |     |                                                                                                                                                                                                                                                                            | ns     |

|       | Page Mode Data Hold From Write Time  |                                     |     |                                                                                                                                                                                                                                                                            | ns     |

The specifications of this device are subject to change without notice. For latest documentation see http://www.nanoamp.com.

# N64T1630C1B

# N64T1630C1B

#### Advance Information

The specifications of this device are subject to change without notice. For latest documentation see http://www.nanoamp.com.

# N64T1630C1B

## N64T1630C1B Advance Information

# N64T1630C1B

## **Power Up Requirements**

After power is applied to bring Vcc and VccQ up,  $\overline{CE}$  should be brought high. Once  $\overline{CE}$  is high, a 150µs delay is required to ensure proper operation. After a 150µs delay, the device is now ready for operation or programming of the mode register.

www.DataSheet4U.com

## **Power Savings Modes**

In the N64T1630C1B device there are several power savings modes. The three modes are:

- Partial Array Self Refresh

- Temperature Compensated Refresh

- Deep Sleep Mode

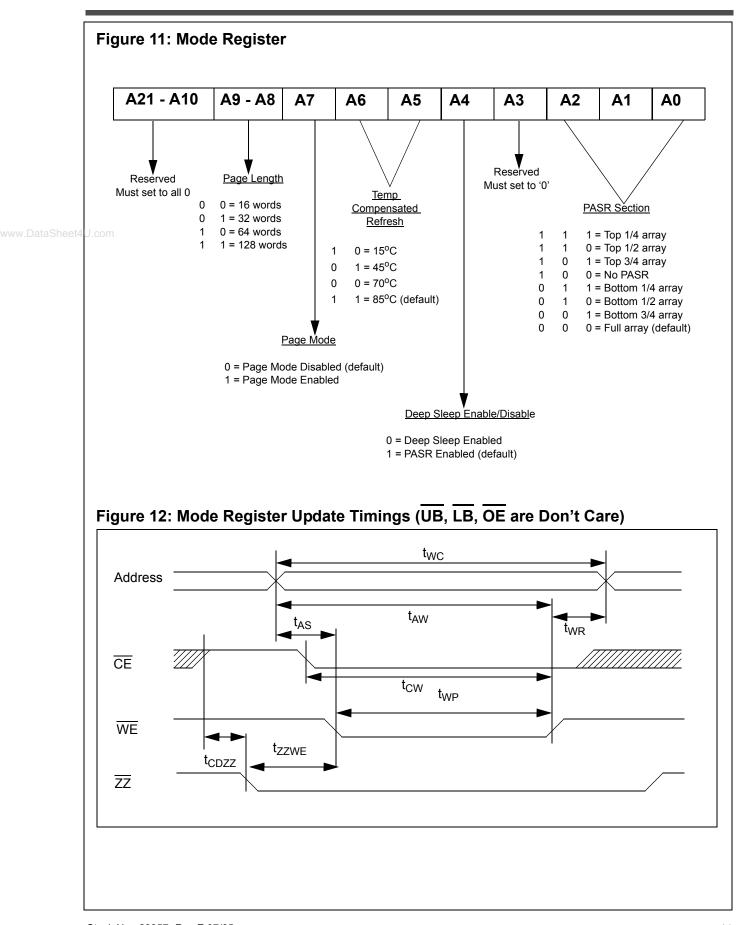

The operation of the power saving modes is controlled by the settings of bits contained in the Mode Register. This definition of the Mode Register is shown in Figure 11 and the various bits are used to enable and disable the various low power modes as well as enabling Page Mode operation. The Mode Register is set by using the timings defined in Figure 12.

#### 1) Partial Array Self Refresh (PAR)

In this mode of operation, the internal refresh operation can be restricted to a 16Mb, 32Mb or 48Mb portion of the array. The array partition to be refreshed is determined by the respective bit settings in the Mode Register. The register settings for the PASR operation are defined in Table 10. In this PASR mode, when  $\overline{ZZ}$  is active low, only the portion of the array that is set in the register is refreshed. The data in the remainder of the array will be lost. The PASR operating mode is only available during standby time ( $\overline{ZZ}$  low) and once  $\overline{ZZ}$  is returned high, the device resumes full array refresh. All future PASR cycles will use the contents of the Mode Register that has been previously set. To change the address space of the PASR mode, the Mode Register must be reset using the previously defined procedures. For PASR to be activated, the register bit, A4 must be set to a '1' value, "PASR Enabled". If this is the case, PASR will be activated 10us after  $\overline{ZZ}$  is brought low. If the A4 register bit is set equal to '0', PASR will not be activated.

#### 2) Temperature Compensated Refresh (TCR)

In this mode of operation, the internal refresh rate can be optimized for the operating temperature used an this can then lower standby current. The DRAM array in the PSRAM must be refreshed internally on a regular basis. At higher temperatures, the DRAM cell must be refreshed more often than at lower tempertures. By setting the temperature of operation in the Mode Register, this refresh rate can be optimized to yield the lowest standby current at the given operating temperature. There are four different temperature settings that can be programmed in to the PSRAM. These are defined in Figure 11.

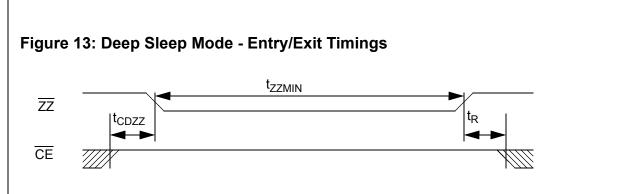

#### 3) Deep Sleep Mode

In this mode of operation, the internal refresh is turned off and all data integrity of the array is lost. Deep Sleep is entered by bringing  $\overline{ZZ}$  low with the A4 register bit set to a '0', "Deep Sleep Enabled". If this is the case, Deep Sleep will be entered 10us after  $\overline{ZZ}$  is brought low. The device will remain in this mode as long as  $\overline{ZZ}$  remains low. If the A4 register bit is set equal to '1', Deep Sleep will not be activated.

#### Other Mode Register Settings

The Page Mode operation can also be enabled and disabled using the Mode Register. Register bit A7 controls the operation of Page Mode and setting this bit to a '1', enables Page Mode. If the register bit A7 is set to a '0', Page Mode operation is disabled.

The specifications of this device are subject to change without notice. For latest documentation see http://www.nanoamp.com.

www.DataSheet4U.com

#### Table 9: Mode Register Update and Deep Sleep Timings

| ltem                          | Symbol             | Min   | Max | Unit | Note |

|-------------------------------|--------------------|-------|-----|------|------|

| Chip deselect to ZZ low       | t <sub>CDZZ</sub>  | 5     |     | ns   |      |

| ZZ low to WE low              | t <sub>ZZWE</sub>  | 10    | 500 | ns   |      |

| Write register cycle time     | t <sub>WC</sub>    | 70/85 |     | ns   | 1    |

| Chip enable to end of write   | t <sub>CW</sub>    | 70/85 |     | ns   | 1    |

| Address valid to end of write | t <sub>AW</sub>    | 70/85 |     | ns   | 1    |

| Write recovery time           | t <sub>WR</sub>    | 0     |     | ns   |      |

| Address setup time            | t <sub>AS</sub>    | 0     |     | ns   |      |

| Write pulse width             | t <sub>WR</sub>    | 40    |     | ns   |      |

| Deep Sleep Pulse Width        | t <sub>ZZMIN</sub> | 10    |     | us   |      |

| Deep Sleep Recovery           | t <sub>R</sub>     | 150   |     | us   |      |

1) Minimum cycle time for writing register is equal to speed grade of product.

#### Table 10: Address Patterns for PASR (A4 = 1)

| A2 | A1 | A0 | Active Section              | Address space     | Size     | Density |

|----|----|----|-----------------------------|-------------------|----------|---------|

| 1  | 1  | 1  | Top quarter of die          | 300000h - 3FFFFFh | 1Mb x 16 | 16Mb    |

| 1  | 1  | 0  | Top half of die             | 200000h - 3FFFFFh | 2Mb x 16 | 32Mb    |

| 1  | 0  | 1  | Top three quarter of die    | 100000h - 3FFFFFh | 3Mb x 16 | 48Mb    |

| 1  | 0  | 0  | No PASR                     | None              | 0        | 0       |

| 0  | 1  | 1  | Bottom quarter of die       | 000000h - 0FFFFFh | 1Mb x 16 | 16Mb    |

| 0  | 1  | 0  | Bottom half of die          | 000000h - 1FFFFFh | 2Mb x 16 | 32Mb    |

| 0  | 0  | 1  | Bottom three quarter of die | 000000h - 2FFFFh  | 3Mb x 16 | 48Mb    |

| 0  | 0  | 0  | Full array                  | 000000h - 3FFFFFh | 4Mb x 16 | 64Mb    |

# N64T1630C1B Advance Information

## Table 11: Deep ICC Characteristics for N64T1630C1B

|  | Item                         | Symbol            | Test                                                                                          | Array<br>Partition | Тур | Max | Unit |

|--|------------------------------|-------------------|-----------------------------------------------------------------------------------------------|--------------------|-----|-----|------|

|  | PASR Mode<br>Standby Current | I <sub>PASR</sub> | V <sub>IN</sub> = V <sub>CC</sub> or 0V,<br>Chip Disabled, t <sub>A</sub> = 85 <sup>o</sup> C | None               |     | 70  | μΑ   |

|  |                              |                   |                                                                                               | 1/4 Array          |     | 105 |      |

|  |                              |                   |                                                                                               | 1/2 Array          |     | 110 |      |

|  |                              |                   |                                                                                               | 3/4 Array          |     | 115 |      |

|  |                              |                   | Full Array                                                                                    |                    | 170 |     |      |

| Item                    | Symbol           | Max<br>Temperature | Тур | Max | Unit |

|-------------------------|------------------|--------------------|-----|-----|------|

|                         | I <sub>TCR</sub> | 15°C               |     | 70  |      |

| Temperature Compensated |                  | 45°C               |     | 85  |      |

| Refresh Current         |                  | 70°C               |     | 105 | μA   |

|                         |                  | 85°C               |     | 170 |      |

| Item               | Symbol          | Test                                                                                   | Тур | Max | Unit |

|--------------------|-----------------|----------------------------------------------------------------------------------------|-----|-----|------|

| Deep Sleep Current | I <sub>ZZ</sub> | $V_{IN} = V_{CC} \text{ or } 0V,$<br>Chip in $\overline{ZZ}$ mode, $t_A = 25^{\circ}C$ | 30  |     | μΑ   |

#### Table 12: Revision History

| Revision | Date         | Change Description          |  |

|----------|--------------|-----------------------------|--|

| A        | June 2004    | Original ADVANCED Datasheet |  |

| В        | January 2005 | Changed maximum Vcc rating  |  |

| С        | January 2005 | General Update              |  |

| D        | May 2005     | Isb change to 170uA         |  |

| E        | July 2005    | Changed Vih to 0.8VccQ      |  |

© 2004 NanoAmp Solutions, Inc. All rights reserved.

NanoAmp Solutions, Inc. ("NanoAmp") reserves the right to change or modify the information contained in this data sheet and the products described therein, without prior notice. NanoAmp does not convey any license under its patent rights nor the rights of others. Charts, drawings and schedules contained in this data sheet are provided for illustration purposes only and they vary depending upon specific applications.

NanoAmp makes no warranty or guarantee regarding suitability of these products for any particular purpose, nor does NanoAmp assume any liability arising out of the application or use of any product or circuit described herein. NanoAmp does not authorize use of its products as critical components in any application in which the failure of the NanoAmp product may be expected to result in significant injury or death, including life support systems and critical medical instrument.