## NAU88L11 Ultra-Low Power Audio CODEC With ClassAB Power Amplifier

#### **GENERAL DESCRIPTION**

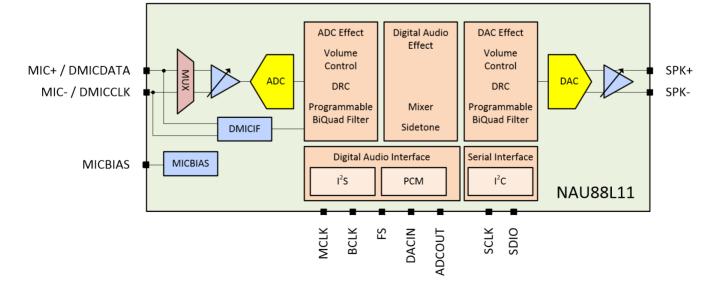

The NAU88L11 is a cost effective ultra-low power high performance MONO audio CODEC. It's suitable for wide range of applications including industrial or portable audio applications. This CODEC includes I2S/PCM interface, Analog/Digital microphone interface, integrated DSP functions, high quality DAC and ADC, and a Class-AB power amplifier. The advanced on-chip digital signal processing features include a dynamic range compressor (DRC) and programmable biquad filter. The NAU88L11 digital and analog voltage can be operated as low as 1.62V, with Speaker Driver voltage operated from 2.5 ~ 3.6V.

#### FEATURES

- DAC SNR(A-weighted): 105dB@1.8V, R<sub>L</sub>= 8Ω, DAC gain=11dB, THD= -85dB

- ADC SNR(A-weighted): 103dB@1.8V, MIC gain=0dB,Fs=48kHz, THD =-93dB

- Low Noise Microphone PGA SNR: 100dB@+18dB gain, 256x OSR

- Digital I2S/PCM I/O port

- Mono differential analog microphone input, or mono digital microphone input

- Low noise Microphone bias:

<10 uV<sub>RMS</sub> noise between 20~20kHz;

- Class AB Power Amplifier: 350mW @ 8Ω, 1% THD+N

- Lineout Mode with Pop&Click Noise Suppression during startup

- Sampling rate from 8k to 96kHz

- Integrated DSP with specific functions:

- o Programmable Biquad filter

- Dynamic Range Compressor (DRC)

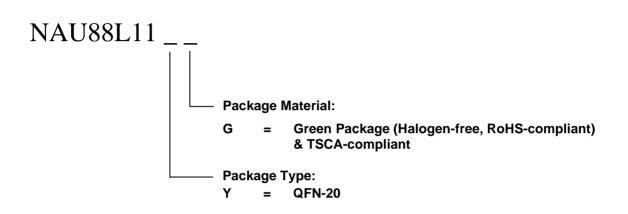

- Package: QFN-20

Package is Halogen-free, RoHScompliant and TSCA-compliant

#### Applications

- Intercom

- Doorbell

- Portable Recording Device

- Wireless handsets /headsets

- Surveillance Camera

- Dash CAM

- Sports CAM

- Digital Still Cameras

- Speakerphone

#### **Block Diagram**

# nuvoTon

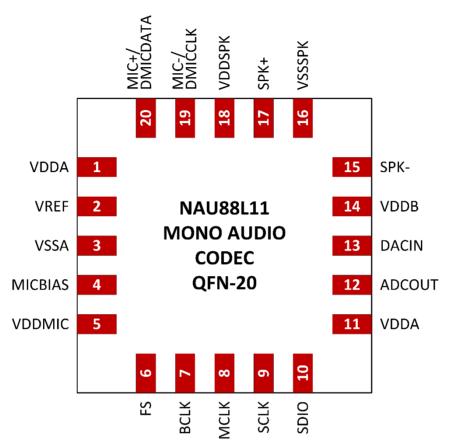

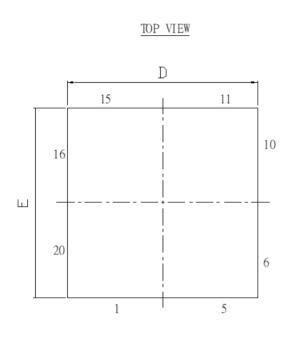

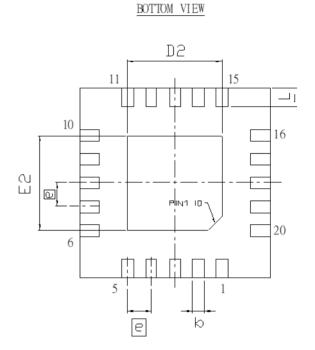

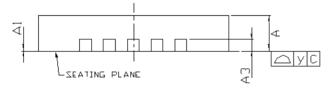

# Pin Diagram :

QFN 20-pin (4mm x 4mm)

# **Pin Description**

| Pin # | Name             | Туре           | Functionality                                           |

|-------|------------------|----------------|---------------------------------------------------------|

| 1     | VDDA             | Supply         | 1.8V Analog Supply                                      |

| 2     | VREF             | Analog I/O     | Internal DAC & ADC voltage reference decoupling I/O     |

| 3     | VSSA             | Ground         | Analog Ground                                           |

| 4     | MICBIAS          | Analog Output  | Microphone Bias Output                                  |

| 5     | VDDMIC           | Supply         | Microphone supply                                       |

| 6     | FS               | Digital I/O    | Frame Sync input / output for I2S / PCM data            |

| 7     | BCLK             | Digital I/O    | Serial data bit clock input / output for I2S / PCM data |

| 8     | MCLK             | Digital Input  | CODEC external Master clock source input                |

| 9     | SCLK             | Digital Input  | Serial Data Clock for I2C                               |

| 10    | SDIO             | Digital I/O    | Serial Data for I2C                                     |

| 11    | VDDA             | Supply         | 1.8V Analog Supply                                      |

| 12    | ADCOUT           | Digital Output | Serial Audio data Output for I2S / PCM data             |

| 13    | DACIN            | Digital Input  | Serial Audio data input for I2S / PCM data              |

| 14    | VDDB             | Supply         | 3.3V Digital I/O supply                                 |

| 15    | SPK -            | Analog Output  | Speaker - channel output                                |

| 16    | VSSSPK           | Ground         | Speaker Driver Ground                                   |

| 17    | SPK+             | Analog Output  | Speaker + channel output                                |

| 18    | VDDSPK           | Supply         | Speaker Driver Supply                                   |

| 19    | MIC - / DMICCLK  | Analog Input   | Microphone - channel input / Digital Mic Clock pin      |

| 20    | MIC + / DMICDATA | Analog Input   | Microphone + channel input / Digittal Mic Data Pin      |

Notes:

1. Unused MIC input pins should be left as no-connection.

2. Digial Microphone should be power by MICBIAS, with setting to  $V_{DDA}$

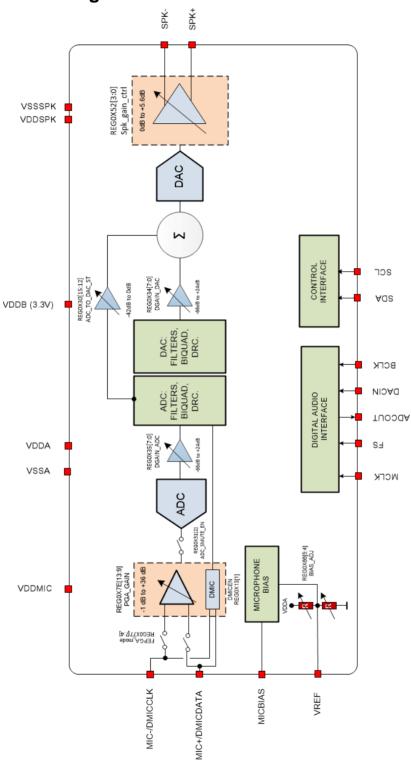

# **Functional Block Diagram**

## **Electrical Characteristics**

Conditions: V<sub>DDA</sub>=1.8V, V<sub>DDB</sub> = 3.3V; V<sub>DDSPK</sub>= 3.6V, V<sub>DDMIC</sub>= 3.6V.  $R_{L}$ = 8  $\Omega$ , f = 1KHz, MCLK=12.88MHz, unless otherwise specified. Limits apply for T<sub>A</sub> = 25°C

| Symbol                    | Parameter                         | Conditions                                                                                     | Typical   | Limit | Units<br>(Limit)  |

|---------------------------|-----------------------------------|------------------------------------------------------------------------------------------------|-----------|-------|-------------------|

|                           |                                   | Vdda                                                                                           | 4         | 16    |                   |

| I <sub>SB</sub>           | Standby Current                   | Vddb                                                                                           | 1         | 5     | μA                |

| la                        | Quiescent Current                 | V <sub>DDMIC</sub><br>fs = 48kHz, DAC On, SPK_DRV On,                                          | 1<br>20   | 5     | mA                |

|                           |                                   | $P_{OUT} = 0$ mW. $R_L = 8\Omega$                                                              | 20        |       |                   |

|                           | -                                 | Driver (V <sub>DDSPK</sub> = $3.6V$ , R <sub>L</sub> = $8\Omega$ , BTL)                        | -         | _     | 1                 |

|                           | Full-Scale output signal          | $V_{DDSPK}$ = 3.6V, RL=8 $\Omega$                                                              | 2.        | 0     | Vrms              |

| Po                        | Output Power                      | DAC Gain = 0dB, THD+N = 1%                                                                     | 350       |       | mW                |

| THD+N                     | Total Harmonic Distortion + Noise | F=1020Hz, RL=8Ohm                                                                              | -85       |       | dB                |

| SNR                       | Signal to Noise Ratio             | VOUT = 2V <sub>RMS</sub> ,<br>SPK_DRV Gain=4.4dB,<br>DAC_Gain = 11dB, A-Weighted               | 105       |       | dB                |

| PSRR                      | Power Supply Rejection Ratio      | Ripple on V <sub>DDA</sub> = 200mVpp at 217Hz                                                  | 80        |       | dB                |

|                           | Frequency Response                | F = 20Hz ~ 20kHz                                                                               | +0.1/-0.2 |       | dB                |

|                           |                                   | ADC                                                                                            |           |       |                   |

| FSADC                     | ADC Full Scale Input Level        | V <sub>DDA</sub> = 1.8V                                                                        | 1         |       | VRMS              |

|                           | Total Harmonic Distortion + Noise | MIC Input=0.8V <sub>RMS</sub> , MIC GAIN=0dB,<br>f=1KHz, fs = 48kHz, Differential Input        | -90       |       | dB                |

| THD+N                     |                                   | MIC Input=0.8V <sub>RMS</sub> , MIC GAIN=30dB,<br>f=1KHz, fs=16kHz, Differential Input         | -90       |       | dB                |

| SNR Signal to Noise Ratio |                                   | A-Weighted, MIC Gain = 0dB,<br>fs = 48kHz, Differential Input                                  | 102       |       | dB                |

| SNK                       | Signal to Noise Ratio             | A-Weighted, MIC Gain = 6 dB,<br>fs = 48kHz, Differential Input                                 | 100       |       | dB                |

| PSRR                      | Power Supply Rejection Ratio      | Ripple on V <sub>DDA</sub> = 200mVpp at 217Hz<br>MIC GAIN = 0dB Differential Input             | 70        |       | dB                |

| CMRR                      | Common Mode Rejection Ratio       | Differential Input 100 mV <sub>RMS</sub> ,<br>PGA gain = 20dB,<br>frequency sweep 20Hz ~ 20KHz | 65        |       | dB                |

|                           | Minimum Input Impedance           |                                                                                                | 10        |       | kOhm              |

|                           | Frequency Response                | f = 20Hz ~ 20kHz                                                                               | +0.1/-0.2 |       | dB                |

|                           | Power Consumption                 | No Signal, ADC on<br>f <sub>s</sub> = 44.1kHz                                                  | 7.9       |       | mW                |

|                           |                                   | MICBIAS                                                                                        |           |       |                   |

| Іоит                      | Output Current                    | Low Noise Mode                                                                                 |           | 4     | mA                |

| eos                       | Output Noise                      | Low Noise Mode, f = 20Hz ~ 20kHz<br>MICBIAS=2.7V                                               |           | 10    | uV <sub>RMS</sub> |

#### Digital I/O

| Parameter         | Symbol | Comments/Conditions     |                        | Min                    | Мах                    | Units |

|-------------------|--------|-------------------------|------------------------|------------------------|------------------------|-------|

| Input LOW level   | VIL    | Vdd                     | <sub>B</sub> = 1.8V    |                        | 0.33* V <sub>DDB</sub> | V     |

|                   | VIL    | $V_{DDB} = 3.3V$        |                        |                        | 0.37* V <sub>DDB</sub> | v     |

| Input HIGH level  | VIH    | Vdd                     | <sub>B</sub> = 1.8V    | 0.57* V <sub>DDB</sub> |                        | V     |

| Input HIGH level  | VIH    | Vdd                     | <sub>B</sub> = 3.3V    | 0.63* V <sub>DDB</sub> |                        | v     |

| Output HIGH level | Vон    | I <sub>Load</sub> = 1mA | V <sub>DDB</sub> =1.8V | 0.9* V <sub>DDB</sub>  |                        | V     |

| Output high level | VOH    | ILoad= IIIA             | $V_{DDB} = 3.3V$       | 0.95* Vddb             |                        | v     |

| Output LOW level  | Vol    | I <sub>Load</sub> = 1mA | $V_{DDB} = 1.8V$       |                        | 0.1* V <sub>DDB</sub>  | V     |

|                   | VOL    | ILoad= IIIIA            | V <sub>DDB</sub> =3.3V |                        | 0.05* V <sub>DDB</sub> | v     |

#### **Recommended Operating Conditions**

| Condition                      | Symbol             | Min  | Typical | Max  | Units |

|--------------------------------|--------------------|------|---------|------|-------|

|                                |                    |      |         |      |       |

| Digital I/O Supply Range       | V <sub>DDB</sub>   | 1.62 | 3.3     | 3.6  | V     |

| 1.8V Supply Range**            | Vdda               | 1.62 | 1.8     | 1.98 | V     |

| Speaker Drvier Supply Range    | V <sub>DDSPK</sub> | 2.5  | 3.3     | 3.6  | V     |

| Microphone Bias Supply Voltage | V <sub>DDMIC</sub> | 3.0  | 3.3     | 3.6  | V     |

| Temperature Range              | T <sub>A</sub>     | -40  |         | +85  | °C    |

\*\* Note: DMIC Supply power should connected to MICBIAS, and set same as V<sub>DDA</sub>.

#### Absolute Maximum Ratings

| Parameter                      | Min                    | Мах                    | Units |

|--------------------------------|------------------------|------------------------|-------|

|                                |                        |                        |       |

| Digital I/O Supply Range       | -0.3                   | 4.0                    | V     |

| 1.8V Supply Range              | -0.3                   | 2.2                    | V     |

| Speaker Driver Supply Range    | -0.3                   | 4.0                    | V     |

| Microphone Bias Supply Voltage | -0.3                   | 4.0                    | V     |

| Voltage Input Digital Range    | V <sub>SSD</sub> - 0.3 | V <sub>DDA</sub> + 0.3 | V     |

| Voltage Input Analog Range     | Vssa - 0.3             | V <sub>DDA</sub> + 0.3 | V     |

| Junction Temperature, TJ       | -40                    | +150                   | °C    |

| Storage Temperature            | -65                    | +150                   | °C    |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods. Exposure to such conditions may adversely influence product reliability and result in failures not covered by warranty.

# nuvoTon

| Table of Co | ntents                                                       |    |

|-------------|--------------------------------------------------------------|----|

| PIN D       | DIAGRAM :                                                    | 2  |

|             | DESCRIPTION                                                  |    |

|             | CTIONAL BLOCK DIAGRAM                                        |    |

|             | CTRICAL CHARACTERISTICS                                      |    |

|             |                                                              |    |

| 1. 0        | GENERAL DESCRIPTION                                          |    |

| 1.1         | Analog and Digital Inputs                                    |    |

| 1.2         | Analog Output                                                |    |

| 1.3         | ADC, DAC and Digital Signal Processing<br>Digital Interfaces |    |

| 1.4         | 0                                                            |    |

|             | OWER SUPPLY                                                  |    |

| 2.1         |                                                              |    |

|             | NPUT PATH DETAILED DESCRIPTIONS                              |    |

| 3.1         | Analog Microphone Inputs                                     |    |

| 3.2         | Digital Microphone Input<br>VREF                             |    |

| 3.3<br>3.4  | VREF                                                         |    |

| 3.4<br>3.5  | MIC detect                                                   |    |

| 3.6         | Key Detect                                                   |    |

|             | ADC DIGITAL BLOCK                                            |    |

| 4.1         | ADC Dynamic Range Compressors (DRC)                          |    |

|             | 1.1 Level Estimation                                         |    |

| 4.1         | 1.2 Static Curve                                             |    |

| 4.2         | ADC Digital Volume Control                                   |    |

| 4.3         | ADC Programmable Biquad Filter                               |    |

| 4.4         | Additional ADC Application Notes                             |    |

| 5. C        | DAC DIGITAL BLOCK                                            |    |

| 5.1         | DAC Digital Volume Control, Mute and Channel selection       |    |

| 5.2         | DAC Soft Mute                                                |    |

| 5.3         | DAC Auto Mute                                                | 19 |

| 5.4         | DAC Programmable Biquad Filter                               |    |

| 5.5         | DAC Dynamic Range Control (DRC)                              |    |

| -           | 5.1 Level Estimation                                         |    |

| 5.5         | 5.2 Static Curve                                             |    |

| 5.6         | DAC Path with Sidetone                                       |    |

| 5.7         | Speaker Output                                               |    |

| 5.8         |                                                              |    |

| 5.9<br>5.10 | Speaker Driver Short Circuit Protection                      |    |

| 5.10<br>5   | Companding<br>10.1 µ-law                                     |    |

| -           | 10.1 µ-таw<br>10.2 А-таw                                     |    |

| 5.          | 10.2 / 10.W                                                  |    |

| 6. P   | OWER UP AND START SEQUENCE                                    |    |

|--------|---------------------------------------------------------------|----|

| 6.1    | Basic Register Sequence                                       | 27 |

| 6.2    | Clock Detection                                               | 29 |

| 6.3    | MCLK / FS Clock Setting in Slave Mode                         | 30 |

| 6.4    | ADC/DAC Oversampling Rate                                     | 32 |

| 7. C   | ONTROL INTERFACES                                             | 33 |

| 7.1    | 2-Wire-Serial Control Mode (I <sup>2</sup> C Style Interface) | 33 |

| 7.2    | 2-Wire Protocol Convention                                    | 33 |

| 7.3    | 2-Wire Write Operation                                        | 34 |

| 7.4    | 2-Wire Read Operation                                         | 35 |

| 7.5    | Digital Serial Interface Timing                               | 36 |

| 7.6    | Software Reset                                                | 37 |

| 7.7    | I <sup>2</sup> C Addresses                                    | 37 |

| 8. D   | IGITAL AUDIO INTERFACES                                       | 38 |

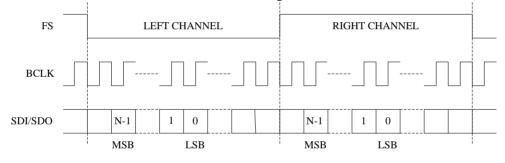

| 8.1    | Right-Justified Audio Data                                    | 38 |

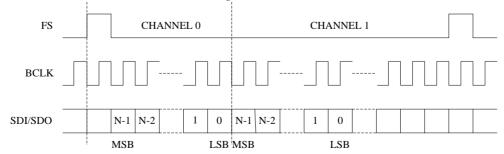

| 8.2    | Left-Justified Audio Data                                     | 39 |

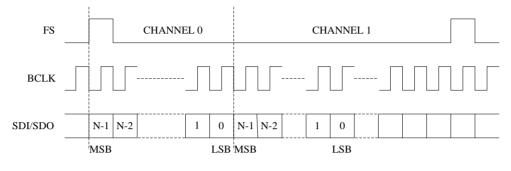

| 8.3    | I2S Audio Data                                                | 39 |

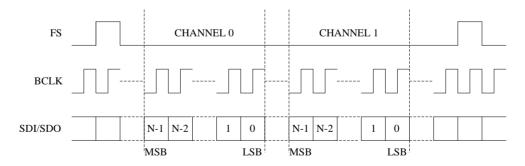

| 8.4    | PCMA Audio Data                                               | 39 |

| 8.5    | PCMB Audio Data                                               | -  |

| 8.6    | PCM Time Slot Audio Data                                      | 40 |

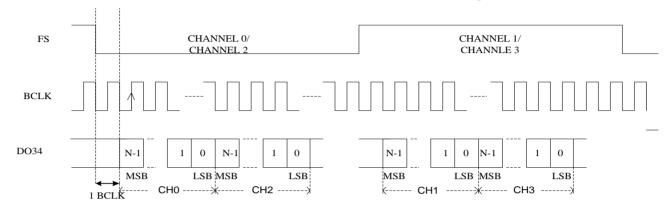

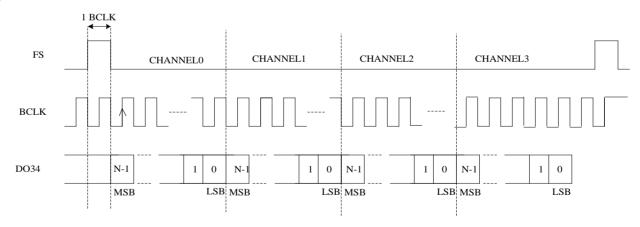

| 8.7    | TDM I2S Audio Data                                            | 41 |

| 8.8    | TDM PCMA Audio Data                                           | 41 |

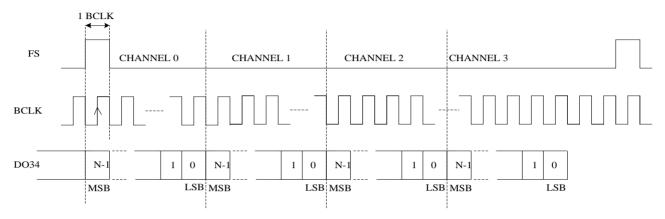

| 8.9    | TDM PCMB Audio Data                                           |    |

| 8.10   | TDM PCM Offset Audio Data                                     |    |

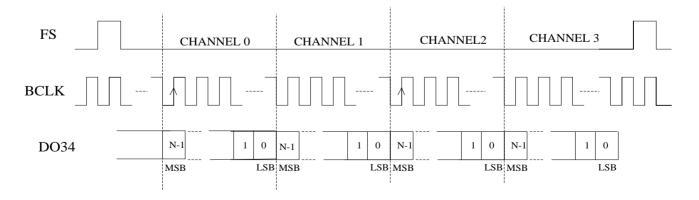

| 8.11   | Digital Audio Interface Timing Diagrams                       |    |

| 8.11.1 | 1 Digital Audio Interface Slave Mode                          | 43 |

| 9. C   | ONTROL AND STATUS REGISTERS                                   | 44 |

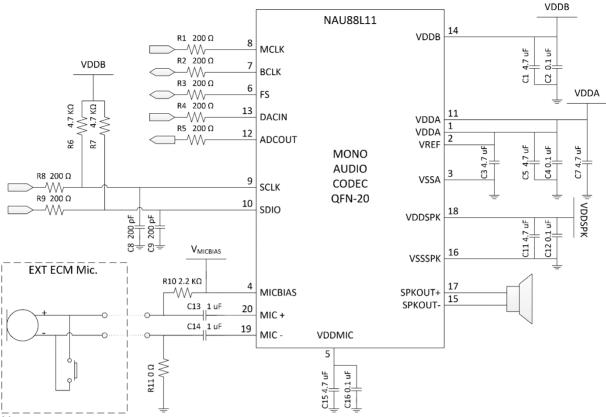

| 10. T  | YPICAL APPLICATION DIAGRAM WITH ANALOG                        |    |

| MICR   | OPHONE                                                        | 59 |

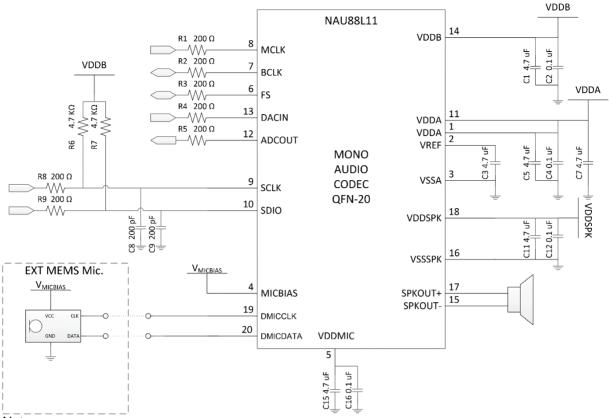

| 10.1   | Typical Application Diagram with Digital Microphone           |    |

| 11. P  | ACKAGE INFORMATION                                            | 61 |

| 12. A  | PPENDIX                                                       | 62 |

| 12.1   | MCLK/FS Table: Group 1 MCLK_INT/FS ratio of 256               | 62 |

| 12.2   | MCLK/FS Table: Group 1 MCLK_INT/FS ratio of 400               |    |

| 12.3   | MCLK/FS Table: Group 1 MCLK_INT/FS ratio of 500               |    |

|        | RDERING INFORMATION                                           |    |

|        | EVISION HISTORY                                               |    |

|        | RTANT NOTICE                                                  |    |

## 1. General Description

NAU88L11 is an ultra-low power, highly integrated CODEC, which features mono audio DAC, and mono audio ADC, that supports Analog and Digital Microphone Input. NAU88L11 includes DSP functions including DRCs (Dynamic Range Compression) and programmable biquad filters. The NAU88L11 supports a full range of audio formats including Left-justified, I<sup>2</sup>S, and multiple PCM formats. The NAU88L11 device is controlled through 2-wire digital control interface. The NAU88L11 digital and analog voltage can be operated as low as 1.62V, with Speaker Driver voltage operated from 2.5 to 3.6V. Mic bias voltage supply is upgraded to support voltages up to 3.6V.

## **1.1 Analog and Digital Inputs**

The NAU88L11 provides an analog input to acquire and process audio signals from a microphone with high fidelity and flexibility. The mono input path that can be used to capture signals from single-ended or a differential source. The channel has a fully differential programmable gain amplifier (PGA). The outputs of the PGA connect to the ADC.

The NAU88L11 also has an input for a digital microphone. The NAU88L11 provides a DMICCLK, (the clock signal) for the digital microphones. Note that the analog and the digital microphone inputs cannot be used simultaneously.

## 1.2 Analog Output

NAU88L11 has a Class AB speaker driver that is fed by the high quality DAC. The speaker driver has a gain control from 0dB to +5.6dB and Mute. The Speaker driver output can also be used as lineout. The speaker driver is capable of delivering 350mW into 8 $\Omega$  with 1% THD+N.

## **1.3 ADC, DAC and Digital Signal Processing**

The NAU88L11 has a high quality ADC and DAC. These are high performance 24-bit sigma-delta converters, which are suitable for a very wide range of applications.

The ADC and DAC have functions that individually support digital mixing and routing. The ADC and DAC blocks also support advanced digital signal processing subsystems that enable a very wide range of programmable signal conditioning and signal optimizing functions. All digital processing is done with 24-bit precision to minimize processing artifacts and maximize the audio dynamic range supported by the NAU88L11.

The ADC and DAC digital signal process can support two-point dynamic range compressors (DRCs), programmable biquad filters configurable for low pass filters, high pass filters, Notch filter, Bell, low shelf, and high shelf filters with various gain, Q, and frequency controls. Two-point DRCs can be programmed to limit the maximum output level and/or boost a low output level. The biquad filters can be configured as high pass filters intended for DC-blocking or low frequency noise reduction, such as reducing unwanted ambient noise or "wind noise" on a microphone input.

## **1.4 Digital Interfaces**

Command and control of the device is accomplished by using the I<sup>2</sup>C interface.

The digital audio I/O data streams transfer separately from command and control using either I<sup>2</sup>S or PCM audio data protocols These simple but highly flexible interface protocols are compatible with most commonly used serial data protocols, host drivers, and industry standard I<sup>2</sup>S and PCM devices.

## 2. Power Supply

This NAU88L11 has been designed to operate reliably using a wide range of power supply conditions and power-on/power-off sequences. Because of this, there are no special requirements for the sequence or rate at which the various power supply pins change. Any supply can rise or fall at any time without harming the device. However, pops and clicks may result from some coditions. For Lineout mode, optimum handling of hardware and software power-on and power-off sequences are described in more detail in the Lineout configuation section.

## 2.1 Power on and off reset

The NAU88L11 includes a power on reset circuit on chip. The circuit resets the internal logic control at  $V_{DDA}$  supply power up and this reset function is automatically generated internally when power supplies are too low for reliable operation. The reset threshold is approximately 0.55Vdc and 1.0Vdc for  $V_{DDA}$ . It should be noted that these values are much lower than the required voltage for normal operation of the chip.

The reset is held on while the power levels for both  $V_{DDA}$  are below their respective thresholds. Once the power levels rise above their thresholds, the reset is released. Once the reset is released, the registers are ready to be written to. It is also important to note that all the registers should be kept in their reset state for at least 6µs.

An additional internal RC filter based circuit is added which helps the circuit respond for fast ramp rates (~10µs) and generate the desired reset period width (~10µs at typical corner). This filter is also used to eliminate supply glitches which can generate a false reset condition, typically 50ns.

For reliable operation, it is recommended to write **SOFTWARE\_RST**, REG 0x00 upon power up. This will reset all registers to the known default state. Note that when  $V_{DDA}$  is below the power on reset threshold, then the digital IO pins will go into a tri-state condition.

Note that when  $V_{DDA}$  are below the power on reset threshold, then the digital IO pins will go into a tri-state condition.

## 3. Input Path Detailed Descriptions

NAU88L11 is design with a low noise, high common mode rejection ratio analog microphone differential input. The microphone input MIC+/- are followed by -1dB to 36dB PGA gain stage that has a fixed 12kOhm input impedance.

The input is maintained at a DC bias of approximately ½ of the V<sub>DDA</sub> supply voltage. Connections to the input should be AC-coupled by means of external DC blocking capacitors suitable for the device application.

The differential microphone input structure is essential in noisy digital systems where amplification of low-amplitude analog signals is necessary such as in portable digital devices.

A differential input is also very useful to reduce ground noise in systems in which there are ground voltage differences between different chips and components. When properly implemented, the differential input architecture offers an improved power-supply rejection ratio (PSRR) and higher ground noise immunity.

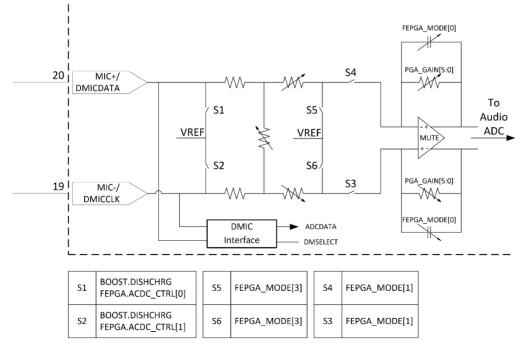

### 3.1 Analog Microphone Inputs

The analog microphone input is routed to a Front End Programmable Gain Amplifier(FEPGA). The input stage can be configured in different modes by using **FEPGA\_MODE**. The FEPGA gain can be varied from -1dB to 36dB in 1dB steps. The gain stage has a fixed  $12k\Omega$  input impedance and can be individually enabled or disabled using the powerup control signal, **PUPL**, REG 0x7F[15].

As shown below:

The input path control is done through S1~S6. Related Register and configuration is provided in blow input block diagram.

Figure 1: Microphone Input Block Diagram with Registers

Page 11 of 67

## 3.2 Digital Microphone Input

The MIC- and MIC+ pins can be used for the digital microphone input. MIC- is the clock for the digital microphone and the MIC+ is the data in. DMIC supply voltage must be provided by MICBIAS, and set the same as  $V_{DDA}$ .

## 3.3 VREF

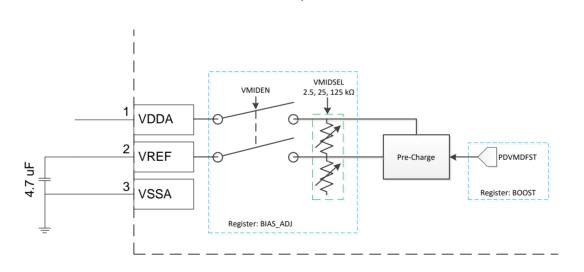

The NAU88L11 includes a mid-supply reference circuit that produces a voltage close to V<sub>DDA</sub>/2. This "VREF" pin should be decoupled to VSS through an external bypass capacitor. Because V<sub>REF</sub> is used as a reference voltage inside the NAU88L11, a large capacitance is required to achieve good power supply rejection at low frequency. Typically, a value of 4.7µF should be used. The V<sub>REF</sub> voltage can be enabled by setting **VMIDEN**, REG 0x66[6] and the output impedance can be set using **VMIDSEL**.

| VMIDSEL | VREF Resistor Selection    | VREF Impedance               |

|---------|----------------------------|------------------------------|

| 00      | Open, no resistor selected | Open, no impedance installed |

| 01      | 50kOhm                     | 25kOhm                       |

| 10      | 250kOhm                    | 125kOhm                      |

| 11      | 5kOhm                      | 2.5kOhm                      |

Table 1: VREF Impedance Selection

Figure 2: VREF Circuitry

## 3.4 MIC Bias

The NAU88L11 provides a MICBIAS pin to power an electret type microphone. The MICBIAS pin is the low impedance output of the MIC Bias LDO. An external  $2k\Omega$  resistor has to be used if the analog microphone is biased by this pin. This pin can be enabled by using **POWERUP**, REG 0x74[8] and the level can be set by using **MICBIASLVL1**,REG 0x74[2:0].

MICBIAS has three modes of operation selected by **MB\_LPMODE**, REG 0x74[4:3]. It can be operated as low noise mode, low power mode or ultra low power mode. See electrical characteristics for expected operating values. Ultra Low Power Mode can be used for Voice wakeup applications. Low power mode is ideally suited for digital MIC applications.

### 3.5 MIC detect

The MIC detect is used to detect whether a microphone is connected to the MICBIAS output. The detection is made internally to the MICBIAS block by determining current draw from the MICBIAS pin. The status of the Mic detect can be read from **IRQ\_STATUS.MICDET**. Mic detection is triggered when MICBIAS voltage drops 25mV below MICBIAS1 value set by **MICBIASLVL1**.

## 3.6 Key Detect

Key detect is used to detect when a key is pressed on the microphone (e.g. to answer/end a call). In this mode, the MICBIAS output is shunted through an external  $2k\Omega$  resistor to GND and a key detect inturupt status is set in **IRQ\_STATUS.KEYDET**, REG 0x10[11]. Key detection is triggered at 85mV reference to GND.

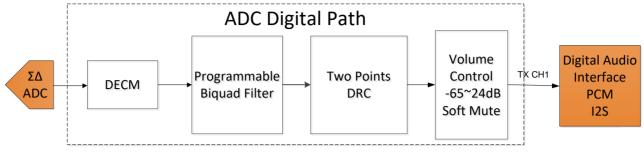

## 4. ADC Digital Block

The ADC digital block takes the output of the 24-bit Analog-to-Digital converter and performs signal processing aimed at producing a high quality audio sample stream to the audio path digital interface. The above figure shows the functional blocks associated with the ADC digital path.

This block can be enabled by using **ENA\_CTRL.ADCEN**, REG 0x01[12]. Oversampling is used to improve noise and distortion performance without affecting the final audio sample rate. The **ADC\_RATE**, REG 0x2B[1:0]can be used to set the ADC OSR and **SMPL\_RATE**, REG 0x2B[7:5] should be set to the value closest to the actual sample rate. The polarity of the ADC output signal can be controlled independently. This data management feature can help minimize subsequent audio processing that may be otherwise required, as the data is passed through stages in the system.

The full-scale input level is proportional to  $V_{DDA}$ . For example, with a 1.8V supply voltage, the full-scale level is  $1.0V_{RMS}$ .

## 4.1 ADC Dynamic Range Compressors (DRC)

The ADC in the digital signal path is design with a a two-point dynamic range compressor (DRC) for advanced signal processing. The DRC can be programmed to limit the maximum output level and/or boost a low output level signal. The DRC function consists of level estimation and static curve control.

## 4.1.1 Level Estimation

The NAU88L11 uses Peak level estimation that depends on the attack and decay time settings, which can be programmable by register settings as in below table.

# nuvoTon

| Вітѕ | DRC_PK_COEF1_ADC | DRC_PK_COEF2_ADC |

|------|------------------|------------------|

| 0000 | Ts               | 63*Ts            |

| 0001 | 3*Ts             | 127*Ts           |

| 0010 | 7*Ts             | 255*Ts           |

| 0011 | 15*Ts            | 511*Ts           |

| 0100 | 31*Ts            | 1023*Ts          |

| 0101 | 63*Ts            | 2047*Ts          |

| 0110 | 127*Ts           | 4095*Ts          |

| 0111 | 255*Ts           | 8191*Ts          |

Table 2: ADC Level Estimation - Attack and Decay Time Register Settings

Please note that Ts is the sampling time given by 1/(Sampling Frequency)

## 4.1.2 Static Curve

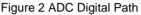

The DRC static curve supports up to five programmable sections as below figure.

Figure 3 DRC Static Characteristic

Each section on the characteristic (labeled NG, EXP, CMP2, CMP1, and LMT) can be controlled by setting the slope and knee point values, in their respective registers.

The table below provides the corresponding register locations.

| Static Curve Section | Slope                                    | Knee Point                  |

|----------------------|------------------------------------------|-----------------------------|

| LMT                  | 0, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64,<br>1 |                             |

| CMP1                 | 0, 1/2, 1/4, 1/8, 1/16, 1                | 0 to -31dB with -1dB step   |

| CMP2                 | 0, 1/2, 1/4, 1/8, 1/16, 1                | 0 to -63dB with -1dB step   |

| EXP                  | 1, 2, 4                                  | -18 to -81dB with -1dB step |

| NG                   | 1, 2, 4, 8 s                             | -35 to -98dB with -1dB step |

Table 3: ADC DRC Static Curve control registers

The output Y values can be determined based on the slopes and knee points selected. Y1 is always equal to Knee 1, as an initial and default condition.

Y1 = Knee 1 Y0 = Y1 - (Knee 1) \* (LMT Slope) Y2 = (Knee 2 - Knee 1) \* (CMP1 Slope) + Y1 Y3 = (Knee 3 - Knee 2) \* (CMP2 Slope) + Y2 Y4 = (Knee 4 - Knee 3) \* (EXP Slope) + Y3

The attack time and decay time is programmable as shown in the Table 4. And the smooth knee filter can be also enabled by register setting.

Application Notes:

- The Y axis distance adjusting along curve cannot exceed 36dB.

- Smooth Knee filter function can be enabled by using DRC\_SMTH\_ENA\_ADC, REG 0x36[7].

- The attack time can be set using DRC\_ATK\_ADC,REG 0x39[7:4].

- The decay time can be set using DRC\_DCY\_ADC, REG 0x39[3:0]

| Вітѕ | DRC_ATK_ADC | DRC_DCY_ADC |

|------|-------------|-------------|

| 0000 | Ts          | 63*Ts       |

| 0001 | 3*Ts        | 127*Ts      |

| 0010 | 7*Ts        | 255*Ts      |

| 0011 | 15*Ts       | 511*Ts      |

| 0100 | 31*Ts       | 1023*Ts     |

| 0101 | 63*Ts       | 2047*Ts     |

| 0110 | 127*Ts      | 4905*Ts     |

| 0111 | 255*Ts      | 8191*Ts     |

| 1000 | 511*Ts      | 16383*Ts    |

| 1001 | 1023*Ts     | 32757*Ts    |

| 1010 | 2047*Ts     | 65535*Ts    |

| 1011 | 4095*Ts     |             |

| 1100 | 8191*Ts     |             |

Table 4: ADC Attack and Decay Time Register Settings

## 4.2 ADC Digital Volume Control

The digital volume control feature allows adjustment of the audio volume coming from ADC using a two-stage volume control. This allows the gain to be adjusted from -66dB to +24dB in 0.5dB steps. Also included is a mute value that will reduce the output signal of the ADCs to zero To adjust the channel volume controls, use register: **DGAIN\_ADC, REG 0x35[7:0].**

### 4.3 ADC Programmable Biquad Filter

The NAU88L11 has 2 dedicated digital biquad filters. One for the ADC path, and another for the DAC path. The biquad filter is a second-order recursive linear filter with two poles and two zeros. Its transfer function is the Z-domain consists of two quadratic functions:

$$H(z) = \frac{B_0 + B_1 Z^{-1} + B_2 Z^{-2}}{1 + A_1 Z^{-1} + A_2 Z^{-2}}$$

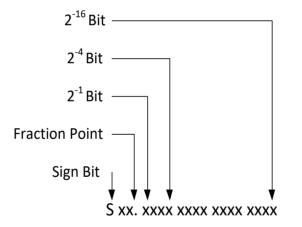

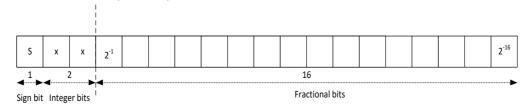

The coefficients A1, A2, B0, B1, B2 are represented in the 3.16 format described below

Each Biquad Coefficient has 19 bits in total, as formatted below

- S is the sign bit (1 bit),

- xx are integers (2bits)

- 16 fractional bits (16 bits)

Figure 5: Number format description for biquad filters coefficients.

# nuvoTon

**Application Notes:**

- Biquad filter coefficients for the ADC with 3.16 format for A1, A2, B0, B1, and B3 are located in below registers.

- BIQ0\_COF2.BIQ\_A1\_H and BIQ0\_COF1.BIQ\_A1\_L

- BIQ0\_COF4.BIQ\_A2\_H and BIQ0\_COF3.BIQ\_A2\_L

- BIQ0\_COF6.BIQ\_B0\_H and BIQ0\_COF5.BIQ\_B0\_L

- BIQ0\_COF8.BIQ\_B1\_H and BIQ0\_COF7.BIQ\_B1\_L

- BIQ0\_COF10.BIQ\_B2\_H and BIQ0\_COF9.BIQ\_B2\_L

- To program the biquad filter in the ADC path, write **BIQ0\_COF1** to **BIQ0\_COF10** for coefficients.

- To turn on the biquad filter in the ADC path, write '1' to **BIQ0\_COF10.BIQ0\_EN**.

## **4.4 Additional ADC Application Notes**

- **CLK\_ADC\_PL**, REG 0x03[10] sets the ADC clock polarity

- CLK\_ADC\_SRC, REG 0x03[7:6] can reduce the clock speed

- **ADC\_TX\_SEL**, REG 0x1B[3:2] allows ADC data be placed in selected time slots to output on the I<sup>2</sup>S interface

- It is recommended to match ADC\_RATE, REG 0x2B[1:0] with CLK\_ADC\_SRC according to the table below

| ADC_RATE    | CLK_ADC_SRC   |

|-------------|---------------|

| 00(OSR=32)  | 11(CODEC 1/8) |

| 01(OSR=64)  | 10(CODEC1/4)  |

| 10(OSR=128) | 01(CODEC 1/2) |

| 11(OSR=256) | 00(CODEC CLK) |

Table 5: ADC\_RATE and CLK\_ADC\_SRC Pairs

# nuvoTon

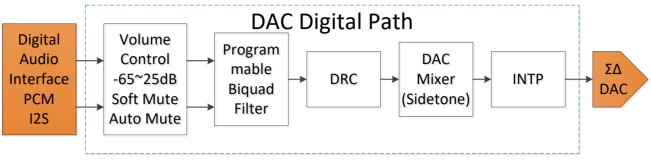

## 5. DAC Digital Block

Figure 4 DAC Digital Path

The DAC digital block uses 24-bit signal processing to generate analog audio with a 16-bit digital sample stream input. This block consists of a sigma-delta modulator, programmable biquad filter, and a DRC. The full-scale output level is proportional to V<sub>DDA</sub>. For example, with a 1.8V supply voltage, the full-scale level is 1.0 V<sub>RMS</sub>. The oversampling feature of the DAC can be changed from 32x to 256x for improved audio performance at higher power consumption. The DAC output signal polarity can be changed using register setting. This can help minimize any audio processing that may be required as the data is passed from other stages of the system. The DAC channel is enabled by **DACEN**, REG 0x01[13]

## 5.1 DAC Digital Volume Control, Mute and Channel selection

The DAC has a digital volume controls that allow the user to adjust the gain from -66dB to +24dB in 0.5dB steps. DGAIN\_DAC, REG 0x34[7:0]. Also included is a mute setting that will reduce the path gain to a minimum, control is through register DGAIN DAC. When using full scale input or DGAIN DAC above 0dB, it is recommended performance to the DAC for best set control bit. DAC CTRL1.CICCLP OFF as 0, and set DAC CTRL1.CIC GAIN ADJ for optimal output amplitude.

## 5.2 DAC Soft Mute

The soft mute function works for both the DAC and the ADC and gradually attenuates the volume of the signal to zero. The soft mute ramps the DAC digital volume down to zero when enabled by register **SMUTE\_EN**, REG0X31[9]. When disabled, the volume increases to the specified volume level. This soft mute feature provides for pop and click reduction in DAC signal path when the chip powers up.ADC soft mute features is controlled by **ADC\_SMUTE\_EN**.

## 5.3 DAC Auto Mute

This feature is implemented for DAC in NAU88L11. In the automatic mode, first the signal **AMUTE\_EN**, REG 0x31[11] needs to be enabled. When 1024 consecutive zeros samples are detected, the analog mute signal is asserted and its status is written to **ANALOG\_MUTE**, REG 0x59[10]. As soon as the first non-zero sample is detected, analog mute signal is de-asserted. If at any time there is a non-zero sample value, the DAC will be unmuted, and the 1024 count will be reinitialized to zero.

## 5.4 DAC Programmable Biquad Filter

**Application Notes:**

- Biquad filter coefficients for the DAC with 3.16 format for A1, A2, B0, B1, and B3 are located in below registers.

- BIQ1\_COF2.BIQ\_A1\_H and BIQ1\_COF1.BIQ\_A1\_L

- BIQ1\_COF4.BIQ\_A2\_H and BIQ1\_COF3.BIQ\_A2\_L

- BIQ1\_COF6.BIQ\_B0\_H and BIQ1\_COF5.BIQ\_B0\_L

- BIQ1\_COF8.BIQ\_B1\_H and BIQ1\_COF7.BIQ\_B1\_L

- BIQ1\_COF10.BIQ\_B2\_H and BIQ1\_COF9.BIQ\_B2\_L

- To program the biquad filter in the DAC path, write **BIQ1\_COF1** to **BIQ1\_COF10** for coefficients.

To turn on the biquad filter in the DAC path, write '1' to **BIQ1\_COF10.BIQ1\_EN**.

## 5.5 DAC Dynamic Range Control (DRC)

The DAC DRC functions in the same way as the ADC DRC explained in Section 4.1. However, different control registers are used.

## 5.5.1 Level Estimation

The Table 6 shows the attack and decay times for the peak level estimation. And, the time constant Ts is the the sampling time given by 1/(Sampling Frequency).

| Вітѕ | DRC_PK_COEF1_ADC | DRC_PK_COEF2_ADC |

|------|------------------|------------------|

| 0000 | Ts               | 63*Ts            |

| 0001 | 3*Ts             | 127*Ts           |

| 0010 | 7*Ts             | 255*Ts           |

| 0011 | 15*Ts            | 511*Ts           |

| 0100 | 31*Ts            | 1023*Ts          |

| 0101 | 63*Ts            | 2047*Ts          |

| 0110 | 127*Ts           | 4095*Ts          |

| 0111 | 255*Ts           | 8191*Ts          |

Table 6: DAC Level Estimation Attack and Decay Time Register Settings

## 5.5.2 Static Curve

The DRC static curve supports five programmable sections, and slope and knee points can be configured as shown in the Table 7.

| Static Curve<br>Section | Slope                                 | Knee Point                  |

|-------------------------|---------------------------------------|-----------------------------|

| LMT                     | 0, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64, 1 |                             |

| CMP1                    | 0, 1/2, 1/4, 1/8, 1/16, 1             | 0 to -31dB with -1dB step   |

| CMP2                    | 0, 1/2, 1/4, 1/8, 1/16, 1             | 0 to -63dB with -1dB step   |

| EXP                     | 1, 2, 4, 8                            | -18 to -81dB with -1dB step |

| NG                      | 1, 2, 4, 8                            | -35 to -98dB with -1dB step |

Table 7: DAC DRC Static Curve Control Registers

The Table 8 shows the attack and decay time for DRC. And, it needs to be carefully used combination with cross talk function because DRC is the last blocks in the path after mixer. Small cross-talk signal might be filtered out by DRC. The smooth knee function can be also enabled by register setting.

| Вітз | DRC_ATK_DAC | DRC_DCY_DAC |

|------|-------------|-------------|

| 0000 | Ts          | 63*Ts       |

| 0001 | 3*Ts        | 127*Ts      |

| 0010 | 7*Ts        | 255*Ts      |

| 0011 | 15*Ts       | 511*Ts      |

| 0100 | 31*Ts       | 1023*Ts     |

| 0101 | 63*Ts       | 2047*Ts     |

| 0110 | 127*Ts      | 4095*Ts     |

| 0111 | 255*Ts      | 8191*Ts     |

| 1000 | 511*Ts      | 16383*Ts    |

| 1001 | 1023*Ts     | 32757*Ts    |

| 1010 | 2047*Ts     | 65535*Ts    |

| 1011 | 4095*Ts     |             |

| 1100 | 8191*Ts     |             |

Table 8: DAC Static Curve Attack and Delay Time Register Settings

Application Notes:

- Smooth Knee function can be enabled by DRC\_SMTH\_ENA\_DAC, REG 0x3A[7].

- The attack time can be set using DRC\_ATK\_DAC, REG 0x3D[7:4].

- The decay time can be set using DRC\_DCY\_DAC, REG 0x3D[3:0].

- DRC needs to be carefully used combination with cross talk function because DRC is the last blocks in the path after mixer. Small cross-talk signal might be filtered out by DRC.

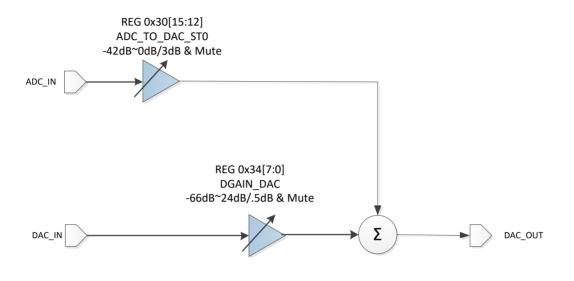

### 5.6 DAC Path with Sidetone

The ADC input channel and I2S channel are capable of being mixed into the output of the DAC. The figure below shows a block diagram of how this works along with the related registers

Figure 5 DAC Path Digital Mixer with Sidetone

DAC channel sidetone calculation: DAC Mixer = DAC Data \* DGAIN\_DAC + ADC Data \* ADC\_TO\_DAC\_STO

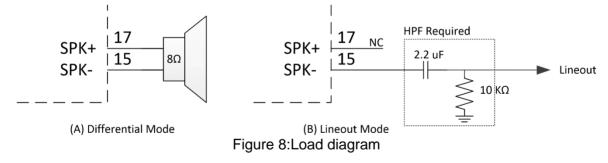

## 5.7 Speaker Output

The NAU88L11 features a differential speaker output (SPKOUT+ and SPKOUT-). The speaker amplifier is designed to drive a load differentially; a configuration referred to as Bridge-Tied Load (BTL). The gain of the speaker driver can be controlled in steps of 0.4dB from 0 to 5.6dB using **SPK\_GAIN\_CNTRL**, REG 0x52[3:0].

The differential speaker outputs can drive a single  $8\Omega$  speaker or two headphone loads of  $16\Omega$  or  $32\Omega$  or a line output. Driving the load differentially doubles the output voltage. The output of the speaker can be manipulated by changing attenuation and the volume (loudness of the output signal).

The output stage is powered by the speaker supply, VDDSPK, which are capable of driving up to  $2.0V_{RMS}$  signals (equivalent to  $4V_{RMS}$  into a BTL speaker). The speaker outputs can be controlled and can be muted individually. The output pins are at reference DC level when the output is muted.

## 5.8 Lineout Configuratioin

The Class AB amplifier includes a control circuit used in Lineout mode to precharge the amplifier output to the common mode voltage VCM (default 1.65V @ 3.3V). The precharge control smoothly charges the amplifier output towards VCM with negligible pop noise. Below is the code sequence to enable the precharge control and charge the output to VCM level with minimum pop noise.

| Step | REG   | Value | Comments                                                                                           |

|------|-------|-------|----------------------------------------------------------------------------------------------------|

| 1    | 0076  | 2000  | [13] = 1 to keep slow rising V <sub>REF</sub>                                                      |

| 2    | 002C  | 0072  | [7:4] = 0x7 to turn on CIC and set CIC_GAIN_ADJ = x7, OSR128                                       |

|      | DELAY |       | //600ms by I <sup>2</sup> C dummy write                                                            |

| 3    | 0073  | 1108  | [12] = 1 to enable DAC, [8] = 1 to enable DAC clock, [3:2] = 2'b10 to select DAC V_{REF} = 1.61V   |

| 4    | 0066  | 0062  | [6] = 1 to enable VMID, [5:4]= 1,0 VMID tie-off selection options                                  |

| 5    | 0076  | 3000  | [13] = 1 to keep slow rising V <sub>REF</sub> ; $[12] = 1$ for global bias enable                  |

| 6    | 0051  | 0220  | [9:6] VCM = 1.65V, [5] = 1 to enable VCM buffer, [4] = 0 to enable precharge, [3:2] = 2'b00 R-bias |

| 7    | DELAY |       | //600ms by I <sup>2</sup> C dummy write                                                            |

| 8    | 0001  | 3FC2  | enable DAC, ADC in digital domain                                                                  |

| 9    | 0008  | 8000  | [15] = 1 to power up the V <sub>REF</sub> buffer                                                   |

| 10   | 0052  | 00A0  | [5] = 1 to power up the main speaker driver, [3:0] = 0 for gain                                    |

| 11   | 0051  | 220   | [4] = 1 to disable precharge                                                                       |

Table 9 Lineout configuration for minimizing pop/click noise

With the above sequence, the rise time is a function of  $C_{ext}$  and can be approximated by the equation  $t_{rise} = 1 + 27*10^{4*}C_{ext}$  (example: for  $C_{ext}=2.2uF$ ,  $R_L=10k$ , the rise time is ~ 1.6 secs).

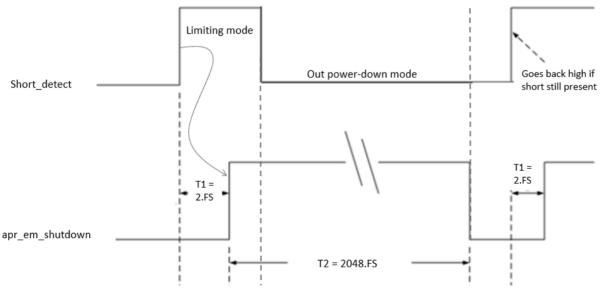

## 5.9 Speaker Driver Short Circuit Protection

The short circuit protection is enabled by default with **DISABLE\_SHRT\_DET**, REG 0x76[6] set to 0.

When a ground short is detected, the chip starts limiting the short circuit current locally in the output driver. If FS clock is running and there is a short present, the **APR\_EMERGENCY\_SHUTDOWN** will be generated and the output driver will be in shut-down mode. If FS is not running, then the output driver will stay in the limiting mode when there is a short. A short to VDD will also activate the limiting-mode protection and may trigger an interrupt flag. INT will only be generated if MCLK is running.

When a short is detected, a short\_detect signal is generated and sent to the APR digital block. After T1(2.FS) cycles, the apr\_em\_shutdown is generated and turns off the output driver. Then a counter is started and the driver is kept in the power-down mode for T2(2048.FS) cycles. The counter time is a function of FS clock frequency which is from 8KHz (min) to 96kHz (max). At the end of time T2, if a short is still present, the operation will restart the timer and the cycle is repeated. The user can read the **APR\_EMRG\_SHTDWN**, REG 0x10[9], short detect interrupt flag status bit. After reading, the interrupt flag the status can be cleared by writing to register **INT\_CLR\_KEY\_STATUS[9]**.

Figure 6 Speaker driver short-circuit protection timing

## 5.10 Companding

Companding is used in digital communication systems to optimize signal-to-noise ratios with reduced data bit rates using non-linear algorithms. The NAU88L11 supports the two main telecommunications companding standards on both transmit and receive sides: A-law and  $\mu$ -law. The A-law algorithm is primarily used in European communication systems and the  $\mu$ -law algorithm is primarily used by North America, Japan, and Australia.

Companding converts 14 bits ( $\mu$ -law) or 13 bits (A-law) to 8 bits using non-linear quantization resulting in 1 sign bit, 3 exponent bits and 4 mantissa bits. When the companding mode is enabled, 8 bit word operation must be enabled.

Below two subsections contain the compression equations set by the ITU-T G.711 standard and implemented in the NAU88L11.

Both NAU88L11 ADC, DAC path supports companding format control.

- ADC: I2S\_PCM\_CTRL1. ADCCM0

- DAC: I2S\_PCM\_CTRL1.DACCM0

### 5.10.1 µ-law

$$F(x) -1 < x < 1 = \frac{\ln (1 + \mu \times |x|)}{\ln (1 + \mu)}, \qquad \mu = 255$$

#### 5.10.2 A-law

$$F(x) = \frac{A \times |x|}{(1 + \ln(A))'}, \qquad 0 < x < \frac{1}{A}$$

$$F(x) = \frac{(1 + \ln(A \times |x|))}{(1 + \ln(A))}, \qquad \frac{1}{A} \le x \le 1$$

*A* = 87.6

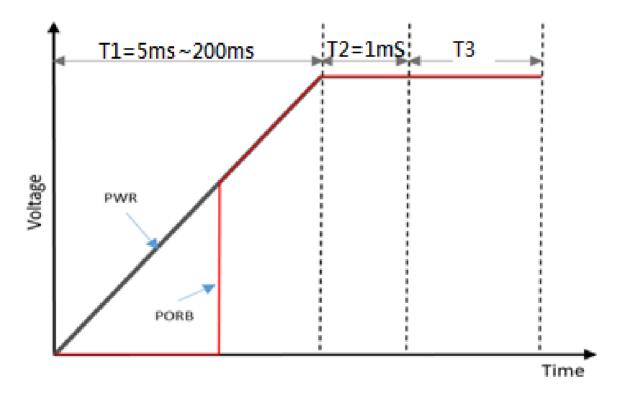

## 6. Power Up and Start Sequence

The power up sequence to bring up the analog blocks smoothly is illustrated below and involves three different time segments (T1 - T3). The power supply ramp rate depends on a number of factors such as the power source drive strength, board parasitics and the decopling capacitor size on the supply line. Typically, a power supply ramp time can be as fast as 5mS or as slow as 200mS.

During time T1, the power supply ramps-up. The internal PORB reset is generated when  $V_{DDA}$  is lower than 1.1V for reliable maintenance of internal logic circuits. While PORB signal is low, it clears internal digital flops. Most of the flops will be cleared to '0' while some flops can be set to '1' during the PORB pulse depending on the required default state of the register.

After time T1, wait another time 1mS so that the power supply is stable before writing to the registers. During time T2, the chip is in stand-by mode and all registers are in a default state. In stand-by, the chip only consumes leakage current and all analog blocks are turned-off. At time T3, the user can start to write data into the registers via the I2C serial bus to setup the chip for their application.

Figure 7 Power Up Sequence

#### 6.1 Basic Register Sequence

The following register sequence in the table below is a general guide to help setup the NAU88L11. This can be done after time T3 shown in Figure above following the power up sequence.

Below sequence is based on MCLK = 12.288MHz, FS=48KHz, with MIC enabled to ADC, Sidetone to DAC/SPK, and I2S to DAC/SPK features enabled.

| Function         | Register Name        | REG      | Value                                          | Config Comment                                                                                                                              | Default<br>Setting |  |

|------------------|----------------------|----------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|

|                  | -                    |          | P                                              | ower Up                                                                                                                                     |                    |  |

| Power<br>Setting | SOFTWARE_RST         | 0x00     | 0x0000                                         | Software Reset                                                                                                                              | 0x0000             |  |

|                  | MCU                  | delay 10 | ms                                             |                                                                                                                                             |                    |  |

| ADC<br>Path      | MUTE_CTRL            | 0x31     | 0x31 0x0200 <b>SMUTE_EN</b> =1 (ADC soft-mute) |                                                                                                                                             | 0x0000             |  |

| DAC<br>Path      | DAC_CTRL1            | 0x2C     | 0x0072                                         | <b>CIC_GAIN_ADJ</b> = 3b'111<br>(fine tuning DAC output glich)                                                                              | 0x0082             |  |

| ADC/DAC Path     |                      |          |                                                |                                                                                                                                             |                    |  |

| DAC<br>Path      | VCM_BUF              | 0x51     | 0x0230                                         | <b>PDB_VCMBUF</b> = 1 (VCM buffer Power Up)<br><b>VOUT_PRECHG_DISABLE</b> = 1<br>(Output VCM precharge disable)                             | 0x0210             |  |

| DAC<br>Path      | SPK_DRV              | 0x52     | 0x00AB                                         | PUP_MAIN_DRV = 1<br>(main speaker driver Power Up)<br>SPK_GAIN_CNTRL = 4b'1011<br>(SPK 4-bit gain = 4.4dB)                                  | 0x0080             |  |

| ADC<br>Path      | BIAS_ADJ             | 0x66     | 0x0060                                         | VMIDEN=1 (VMID enable)<br>VMIDSEL=2b'10 (VMID 125k ohm)                                                                                     | 0x0000             |  |

| DAC<br>Path      | SPARE_ ANALOG1       | 0x69     | 0x0020                                         | THD_BOOST = 1 (thd_boost path enable)                                                                                                       | 0x0000             |  |

| ADC<br>Path      | ANALOG_ADC_2         | 0x72     | 0x0140                                         | <b>PDNOT</b> = 1 (ADC Power Up)                                                                                                             | 0x0100             |  |

| DAC<br>Path      | DAC                  | 0x73     | 0x1108                                         | DAC_EN = 1 (DAC enable)<br>CLK_DAC_EN = 1 (DAC clock enable)                                                                                | 0x0008             |  |

| ADC<br>Path      | MIC_BIAS             | 0x74     | 0x0104                                         | <b>POWERUP</b> = 1 (MICBIAS Power Up)                                                                                                       | 0x0004             |  |

| Power<br>Setting | BOOST                | 0x76     | 0x3040                                         | <b>STG2_SEL</b> = 1 (PGA in class A mode)<br><b>PDVMDFST</b> = 1 (VMID Pre-charge disable)<br><b>BIASEN</b> = 1 (Global Analog Bias enable) | 0x0040             |  |

| ADC<br>Path      | PGA_GAIN             | 0x7E     | 0x0B00                                         | <b>PGA_GAIN</b> = 6b'001011 (PGA gain 10dB)                                                                                                 | 0x0000             |  |

| ADC<br>Path      | POWER_UP_<br>CONTROL | 0x7F     | 0x8000                                         | <b>PUPL</b> = 1 (PGA Power Up)                                                                                                              | 0x0000             |  |

# nuvoTon

NAU88L11

| Function         | Register Name  | REG  | Value      | Config Comment                                                                                                                                                                                                                                                                                                                              | Default<br>Setting |

|------------------|----------------|------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

|                  |                | Α    | udio Syste | em Control System                                                                                                                                                                                                                                                                                                                           | _                  |

| Power<br>Setting | ENA_CTRL       | 0x01 | 0x3FC6     | DACEN = 1 (DAC enable)<br>ADCEN = 1 (ADC enable)<br>DCLK_ADC_EN = 1 (ADC clock enable)<br>DCLK_DAC_EN = 1 (DAC clock enable)<br>CLK_BIST_EN = 1 (BIST clock Enable)<br>CLK_I2S_EN = 1 (I2S clock enable)<br>CLK_DRC_EN = 1 (DRC clock enable)<br>MCLK_RNG_SEL = 3b'000<br>(15.74MHz or lower frequency)<br>SYSCLK_SEL = 0 (SYSCLK = 1*MCLK) | 0x03FE             |

| Clock<br>Setting | CLK_DIVIDER    | 0X03 | 0x0050     | CLK_ADC_SRC = 2b'01 (Scaling for ADC clock<br>from MCLK_INT – div by 1)<br>CLK_DAC_SRC = 2b'01 (Scaling for DAC clock<br>from MCLK_INT – div by 1)<br>MCLK_DIV = 3b'000 (Scaling for MCLK_INT<br>from SYSCLK_SRC – div by 1)                                                                                                                | 0x0050             |

| ADC<br>Path      | ADC_DGAIN_CTRL | 0x30 | 0xF000     | ADC_TO_DAC_ST0 = 4b'1111<br>(ADC to DAC Sidetone = 0dB)                                                                                                                                                                                                                                                                                     | 0x0000             |

| ADC<br>Path      | MUTE_CTRL      | 0x31 | 0x0000     | SMUTE_EN =0 (ADC soft-unmute)                                                                                                                                                                                                                                                                                                               | 0x0000             |

Table 10 Reference Setup Sequence

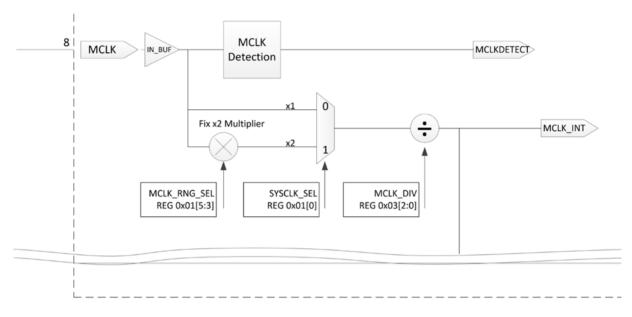

#### 6.2 Clock Detection

The NAU88L11 includes a Clock Detection circuit that can be used to enable and disable the audio path, based on an initialized audio path setting. If MCLK is detected on the input, a status flag in **MCLK\_DET\_INT**, REG 0x10[5] will be set, when MCLKDETECT signal going active, as described by the block diagram below.

Figure 8 NAU88L11 Clock Detection

For MCLK/FS input pin in slave mode, the range of input frequency are defined here.

| Input Signal | Pin Name | Min   | Max    | Unit |

|--------------|----------|-------|--------|------|

| Frame Sync   | FS       | 8     | 96     | kHz  |

| Master Clock | MCLK     | 2.048 | 24.576 | MHz  |

|  | Table 11 | Range of MCL | K/FS for Sla | ave Mode |

|--|----------|--------------|--------------|----------|

|--|----------|--------------|--------------|----------|

System design should be checked that MCLK/FS adhere to the frequency range, then follow the later section to pick out the correct setting, and supported combinations.

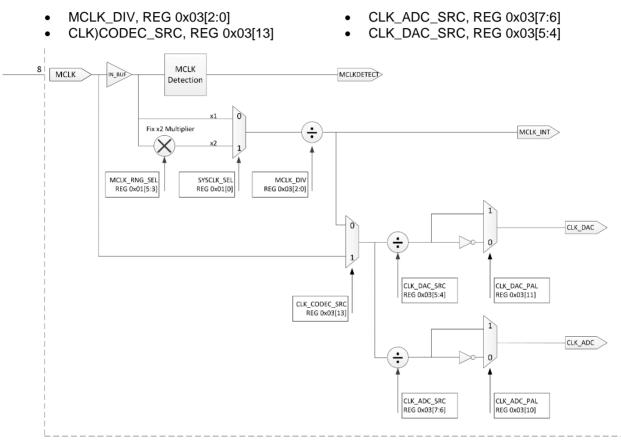

From MCLK input pin, the MCLK signal can be routed for two path, controlled by **SYSCLK\_SEL**, REG 0x01[0]. Aside from the direct path (x1), the multipler path applies a fix multiplier to double the MCLK frequency. In order to adjust for 50% duty cycle, **MCLK\_RNG\_SEL**, REG 0x01[5:3] is a required frequency range setting while the multipler path is selected. The MCLK input frequency range is divided into three band, from 2.048MHz~ 15.74MHz, 15.74MHz ~ 21.6MHz, 21.6MHz to 24.576MH by setting **MCLK\_RNG\_SEL**.

#### 6.3 MCLK / FS Clock Setting in Slave Mode

For slave mode, the NAU88L11 can accept exteral clocks from MCLK/FS input pin. Based on the MCLK and FS input with internal logic to derive MCLK\_INT, and CLK\_DAC, CLK\_ADC for related internal ADC/DAC, DSP, Digital Audio Interface and other internal subsystems.

The figure below provides the full clock distribution diagram, and the key registers are liste here:

Figure 9 NAU88L11 MCLK and Clock Distribution

The NAU88L11 Clock distribution and subsystem is design to minize design effort with simplified setting. The relationship of MCLK/FS input frequency combianations will be described in details below.

The MCLK/FS input frequency range is described in previous section where MCLK input frequency should be between 2.048MHz  $\sim$  24.567MHz. And, FS should be between 8KHz  $\sim$  96KHz.

The internal clock distribution of NAU88L11 is designed support 3 MCLK\_INT/FS ratios, which are 256, 400, 500. Please note MCLK\_INT refers to the internal MCLK frequency after MCLK Divider. This means the MCLK/FS input frequency combation should consider the Multiplier/direct path selected by **SYSCLK\_SEL**, and also the **MCLK\_DIV** divider.

Below table are the key criterion for MCLK/FS input frequencies supported organized by the MCLK\_INT/FS Ratio into 3 group.

| Group1: MCLK_INT/FS Ratio of 256  |                                                                                                                    |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------|

| SYSCLK_SEL set x1 path            |                                                                                                                    |

| Target FS                         | 8/16/2444.1/96KHz                                                                                                  |

| MCLK                              | Target FS * MCLK_DIV*256                                                                                           |

| Register Related                  | MCLK_DIV, SYSCLK_SEL                                                                                               |

| SYSCLK_SEL set x2 path            |                                                                                                                    |

| Target FS                         | 8/16/2444.1/96KHz                                                                                                  |

| MCLK                              | Target FS * MCLK_DIV*256/2                                                                                         |

| Register Related                  | MCLK_DIV, MCLKSEL, SYSCLK_SEL                                                                                      |

| Group2: MCLK_INT/FS Ratio of 400  |                                                                                                                    |

| SYSCLK_SEL set x1 path            |                                                                                                                    |

| Target FS                         | 8/16/2444.1/96KHz                                                                                                  |

| MCLK                              | Target FS * MCLK_DIV*400                                                                                           |

| Register Related                  | MCLK_DIV, SYSCLK_SEL<br>CLK_ADC_SRC, CLK_DAC_SRC must set as 1/4                                                   |

| SYSCLK_SEL set x2 path            |                                                                                                                    |

| Target FS                         | 8/16/2444.1/96KHz                                                                                                  |

| MCLK                              | Target FS * MCLK_DIV*400/2                                                                                         |

| Register Related                  | MCLK_DIV, MCLKSEL, SYSCLK_SEL<br>CLK_ADC_SRC, CLK_DAC_SRC must set as 1/4                                          |

| Group 3: MCLK_INT/FS Ratio of 500 |                                                                                                                    |

| SYSCLK_SEL x1/x2                  |                                                                                                                    |

| Notes                             | <ul> <li>Support list is provided in appendix</li> <li>No need to set CLK_DAC_SRC, CLK_DAC_SRC is fixed</li> </ul> |

| Register Related                  | MCLK_DIV, MCLKSEL, SYSCLK_SEL                                                                                      |

Table 12 Criterion for supported MCLK/FS for slave mode

Following above table, one more limit is added, which is from generating CLK\_ADC, CLK\_DAC, which should be less than or equal to 6.144MHz.

- CLK\_DAC = MCLK\_INT \* CLK\_DAC\_SRC

- CLK\_ADC = MCLK\_INT \* CLK\_ADC\_SRC

Following the above 3 group of criterion to pick out the correct MCLK/FS combinations is essential for system design. A full list of supported MCLK/FS combinations and related settings can be found in the apptediex section for Group 1~3.

#### 6.4 ADC/DAC Oversampling Rate

ADC/DAC Oversample rate setting is used in the NAU88L11 ADC/DAC blocks beyond the CLK\_DAC, CLK\_ADC signal described in previous clock distribution figure.

The the conditions to set **OSR\_ADC\_RATE**, **OSR\_DAC\_RATE** for MCLK\_INT/FS ratio of 256 is listed below.

- CLK\_ADC = **OSR\_ADC\_RATE** \* FS (<=6.144MHz)

- CLK\_DAC = **OSR\_DAC\_RATE** \* FS (<=6.144MHz)

For MCLK\_INT/FS ratios of 400/500, oversample rate is fixed as 100, therefore no need to set **OSR\_ADC\_RATE/OSR\_DAC\_RATE**

#### Example 1:

MCLK=24.576MHz, FS=96KHz

- The Ratio here is picked as 24.576MHz = 256 \* 96KHz

- **SYSCLK\_SEL** can be set either x1 or x2 path

- For x1 path, MCLK\_DIV is set as divid by 1, MCLK\_INT=24.576MHz

- For x2 path, MCLK\_DIV is set as divid by 2, MCLK\_INT=24.575MHz

- Based on CLK\_ADC = MCLK\_INT \* CLK\_ADC\_SRC (<=6.144MHz)</li>

- Avialble OSR\_ADC\_RATE option for each CLK\_ADC\_SRC are listed below in Green for each CLK\_ADC

- For CLK\_ADC as 6.144MHz, the ORS\_ADC\_RATE should be set as 64, so the clock would match as below table in green

- For CLK\_ADC as 3.072 MHz, the ORS\_ADC\_RATE should be set as 32, so the clock would match as below table in green

|             |     | CLK_ADC=MCLK_INT*CLK_ADC_SRC (<=6.144MHz) |        |        |        |  |  |

|-------------|-----|-------------------------------------------|--------|--------|--------|--|--|

|             |     | 24.576                                    | 12.288 | 6.144  | 3.072  |  |  |

| Hz)         | 32  | -                                         | -      | 3.072  | 3.072  |  |  |

| $\sim \leq$ | 64  | -                                         | -      | 6.144  | 6.144  |  |  |

| FS*<br>6.1  | 128 | -                                         | -      | 12.288 | 12.288 |  |  |

| =>)         | 256 | -                                         | -      | 24.576 | 24.576 |  |  |

#### Example 2:

MCLK=19.2MHz, FS=32KHz

- The Ratio here is picked as MCLK\_INT 12.8MHz = 400 \* 32KHz

- o SYSCLK\_SEL is set as x2 path

- For x2 path, MCLK\_DIV is set as divid by 3, MCLK\_INT=12.8MHz

- With MCLK\_INT/FS Ratio of 400.

- **CLK\_ADC\_SRC/CLK\_DAC\_SRC** must be set as divid by 4.

- No need to set OSR\_ADC\_RATE/OSR\_DAC\_RATE

## 7. Control Interfaces

The NAU88L11 includes a serial control bus that provides access to all the device control registers, it may be configured as a 2-wire interface that conforms to industry standard implementations of the I<sup>2</sup>C serial bus protocol.

## 7.1 2-Wire-Serial Control Mode (I<sup>2</sup>C Style Interface)

The 2-wire bus is a bidirectional serial bus protocol. This protocol defines any device that sends data onto the bus as a transmitter (or master), and any device receiving data as the receiver (or slave). The NAU88L11 can function only as a slave when in the 2-wire interface configuration.

## 7.2 2-Wire Protocol Convention

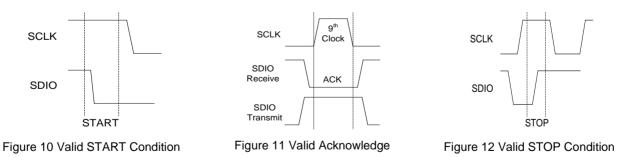

All 2-Wire interface operations must begin with a START condition, which is a HIGHto-LOW transition of SDIO while SCLK is HIGH. All 2-Wire interface operations are terminated by a STOP condition, which is a LOW to HIGH transition of SDIO while SCLK is HIGH. A STOP condition at the end of a read or write operation places the device in a standby mode.

An acknowledge (ACK), is a software convention used to indicate a successful data transfer. To allow for the ACK response, the transmitting device releases the SDIO bus after transmitting eight bits. During the ninth clock cycle, the receiver pulls the SDIO line LOW to acknowledge the reception of the eight bits of data.

Following a START condition, the master must output a device address byte. This consists of a 7-bit device address, and the LSB of the device address byte is the R/W (Read/Write) control bit. When R/W=1, this indicates the master is initiating a read operation from the slave device, and when R/W=0, the master is initiating a write operation to the slave device. If the device address matches the address of the slave device, the slave will output an ACK during the period when the master allows for the ACK signal.

Please Note:

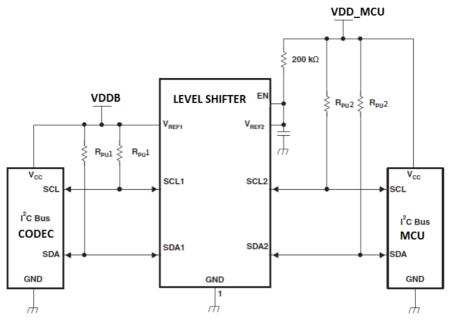

Sometimes, I<sup>2</sup>C needs to use level shifter between different supplies domains. During Acknowledge as below figure, receiver side (CODEC) will pull low, and transmit side (MCU) is disable and pull high by pull high resistor. Because NAU88L11 SDIO can sink 2mA by default setting (maximum up to 8mA,) shown as below Error! Reference source not found., RPU1 and RPU2 need to be select such that total current V<sub>DDB</sub>/R<sub>PU1</sub>+ VDD\_MCU/R<sub>PU2</sub> during Acknowledge should not be too large to exceed SDIO sinking capability.

Figure 13 Typical I2C level shifter circuit

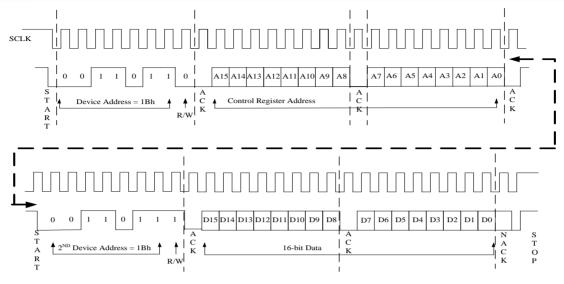

## 7.3 2-Wire Write Operation

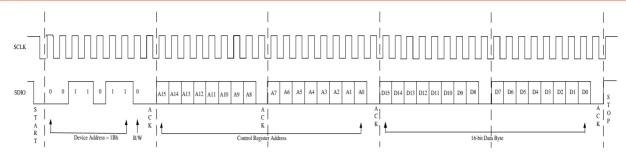

A Write operation consists of a three-byte instruction followed by one or more Data Bytes. A Write operation requires a START condition, followed by a valid device address byte with R/W=0, a valid control address byte, data byte(s), and a STOP condition. The Device Address of the NAU88L11 is fixed to 0x1B. If the Device Address matches this value, the NAU88L11 will respond with the expected ACK signaling as it accepts the data being transmitted to it.

| Device |     |    |     |     |     |     |     |     |

|--------|-----|----|-----|-----|-----|-----|-----|-----|

| Addres | R/W | 1  | 1   | 0   | 1   | I   | 0   | 0   |

| Byte   |     |    |     |     |     |     |     |     |

| Contro | A8  | A9 | A10 | A11 | A12 | A13 | A14 | A15 |

| Addres |     |    |     |     |     |     |     |     |

| Bytes  | A0  | Al | A2  | A3  | A4  | A5  | A6  | A7  |

|        |     |    |     |     |     |     |     |     |

| Data   | D8  | D9 | D10 | D11 | D12 | D13 | D14 | D15 |

| Bytes  |     |    |     |     |     |     |     |     |

| Dynes  | D0  | DI | D2  | D3  | D4  | D5  | D6  | D7  |

|        |     |    |     |     |     |     |     |     |

Figure 14 Slave Address Byte, Control Address Byte, and Data Byte

Figure 15 2-Wire Write Sequence

## 7.4 2-Wire Read Operation

A Read operation consists of a three-byte Write instruction followed by a Read instruction of one or more data bytes. The bus master initiates the operation issuing the following sequence: a START condition, device address byte with the R/W bit set to "0", and a Control Register Address byte. This indicates to the slave device which of its control registers is to be accessed.

If the device address matches this value, the NAU88L11 will respond with the expected ACK signaling as it accepts the Control Register Address being transmitted into it. After this, the master transmits a second START condition, and a second instantiation of the same device address, but now with R/W=1.

After again recognizing its device address, the NAU88L11 transmits an ACK, followed by a two byte value containing the 16 bits of data from the selected control register inside the NAU88L11.

During this phase, the master generates the ACK signaling with each byte transferred from the NAU88L11. If there is no STOP signal from the master, the NAU88L11 will internally auto-increment the target Control Register Address and then output the two data bytes for this next register in the sequence.

This process will continue as long as the master continues to issue ACK signaling. If the Control Register Address being indexed inside the NAU88L11 reaches the value 0xFFFF (hexadecimal) and the value for this register is output, the index will roll over to 0x0000. The data bytes will continue to be output until the master terminates the read operation by issuing a STOP condition.

Figure 16 Two-wire Read Sequence

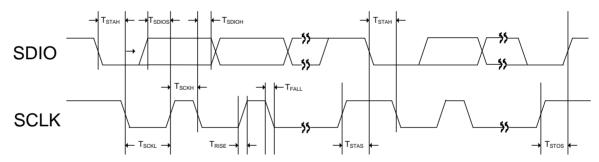

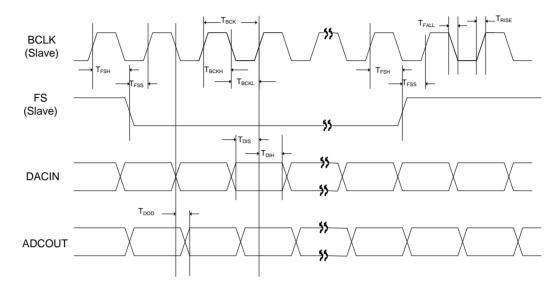

## 7.5 Digital Serial Interface Timing

Figure 17 Two-wire Control Mode Timing

| Symbol             | Description                                                                             | min   | typ | max | unit |

|--------------------|-----------------------------------------------------------------------------------------|-------|-----|-----|------|

| Тѕтан              | SDIO falling edge to SCLK falling edge hold timing in<br>START / Repeat START condition | 600   | -   | -   | ns   |

| TSTAS              | SCLK rising edge to SDIO falling edge setup timing in Repeat START condition            | 600   | -   | -   | ns   |

| Тѕтоѕ              | SCLK rising edge to SDIO rising edge setup timing in STOP condition                     | 600   | -   | -   | ns   |

| Т <sub>SCKH</sub>  | SCLK High Pulse Width                                                                   | 600   | -   | -   | ns   |

| TSCKL              | SCLK Low Pulse Width                                                                    | 1,300 | -   | -   | ns   |

| T <sub>RISE</sub>  | Rise Time for all 2-wire Mode Signals                                                   | -     | -   | 300 | ns   |

| T <sub>FALL</sub>  | Fall Time for all 2-wire Mode Signals                                                   | -     | -   | 300 | ns   |

| Tsdios             | SDIO to SCLK Rising Edge DATA Setup Time                                                | 100   | -   | -   | ns   |

| T <sub>SDIOH</sub> | SCLK falling Edge to SDIO DATA Hold Time                                                | 0     | -   | 600 | ns   |

Table 13 2-Wire Serial Interface Timing

#### 7.6 Software Reset

The NAU88L11 and all of its control registers can be reset to "default", initial conditions by writing any value to REG 0x00 using the two-wire interface mode.

#### 7.7 I<sup>2</sup>C Addresses

The NAU88L11 has 7 bits assigned to the device for I<sup>2</sup>C address, the eighth bit of the command byte is a R/W bit. The 7 I<sup>2</sup>C address bits are hard coded by metal layer internal to the device. The default set for read and write is shown below:

|               | Bit<6> | Bit<5> | Bit<4> | Bit<3> | Bit<2> | Bit<1> | Bit<0> | R/W |

|---------------|--------|--------|--------|--------|--------|--------|--------|-----|

| Read Address  | 0      | 0      | 1      | 1      | 0      | 1      | 1      | 1   |

| Write Address | 0      | 0      | 1      | 1      | 0      | 1      | 1      | 0   |

Table 14 I<sup>2</sup>C Adress Table

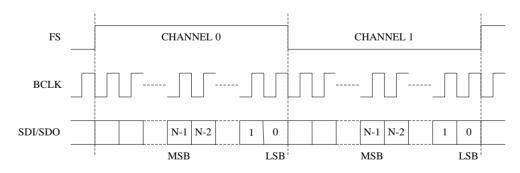

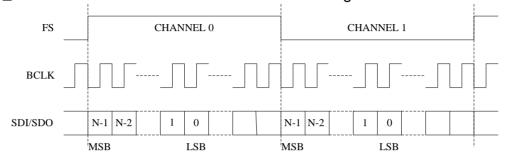

#### 8. Digital Audio Interfaces

The NAU88L11 can be configured as either the master or the slave, by setting register **MS0**, in REG 0x1D[3], to 1 for master mode and to 0 for slave mode. Slave mode is the default if this bit is not written. In master mode, NAU88L11 outputs both Frame Sync (FS) and the audio data bit clock (BCLK) and has full control of the data transfer. In the slave mode, an external controller supplies BCLK and FS. Data is latched on the rising edge of BCLK; SDO clocks out ADC data, while SDI clocks in data for the DACs.