# High-Voltage Current-Mode PWM Controller Featuring Peak Power Excursion and Self-Relaxing Off Mode

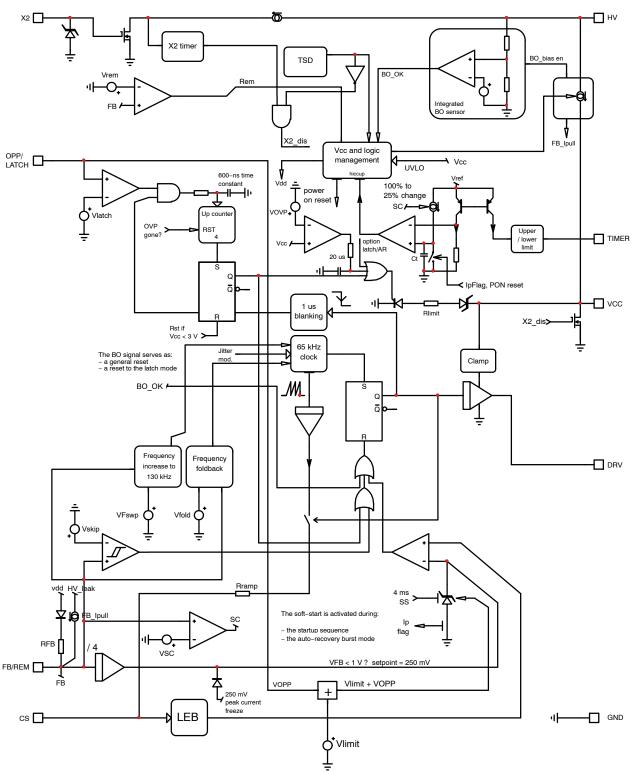

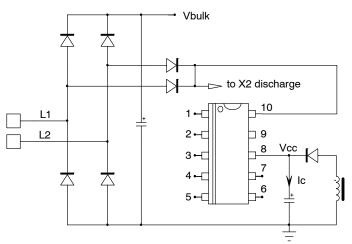

The NCP1249 is a highly integrated high–voltage PWM controller capable of delivering a rugged and high performance offline power supply with extremely low no–load consumption. With a supply range up to 30 V, the controller hosts a jittered 65 kHz switching circuitry operated in peak current mode control. When the power on the secondary side starts to decrease, the controller automatically folds back its switching frequency down to a minimum level of 26 kHz. As the power further goes down, the part enters skip cycle while freezing the peak current setpoint.

To help build rugged converters, the controller features several key protective features: a internal brown–out, a non–dissipative Over Power Protection for a constant maximum output current regardless of the input voltage and two latched over voltage protection inputs – either through a dedicated pin or via the VCC input.

The controller architecture is arranged to authorize a transient peak power excursion when the peak current hits the limit. At this point, the switching frequency is increased from 65 kHz to 130 kHz until the peak requirement disappears. The timer duration is then modulated as the converter crosses a peak power excursion mode (long) or undergoes a short circuit (short).

#### Features

- High-Voltage Current Source for Lossless Start-up Sequence

- Automatic and Lossless X2 Capacitors Discharge Function

- 65 kHz Fixed-Frequency Current-Mode Control Operation with 130 kHz Excursion

- Internal and Adjustable Over Power Protection (OPP) Circuit

- Internal Brown-Out Protection Circuit

- Frequency Foldback Down to 26 kHz and Skip-Cycle in Light Load Conditions

- Adjustable Ramp Compensation

- Internally Fixed 4 ms Soft-Start

- Adjustable Timer-Based Auto-Recovery Overload/Short-Circuit Protection

- 100% to 25% Timer Reduction from Overload to Short-Circuit Fault

- Frequency Jittering in Normal and Frequency Foldback Modes

- Latched OVP Input for Improved Robustness and Latched OVP on VCC

.

XXXXX = Specific Device Code

= Wafer Lot

= Work Week

= Year

= Assembly Location

= Pb-Free Package

• Up to 30 V VCC Maximum Rating

**D SUFFIX**

CASE 751BP

Α

L

Y

W

- +300 mA/ –500 mA Source/Sink Drive Capability

- Extremely Low No-Load Standby Power via Controlled Self-Relaxing Off Mode

- Option for Auto-Recovery or Latched Short-Circuit Protection

- Internal Thermal Shutdown with Hysteresis

- These are Pb–Free Devices

#### **Typical Applications**

• Converters Requiring Peak–power Capability such as Printers Power Supplies, ac–dc Adapters for Game Stations

# ORDERING INFORMATION

See detailed ordering and shipping information on page 2 of this data sheet.

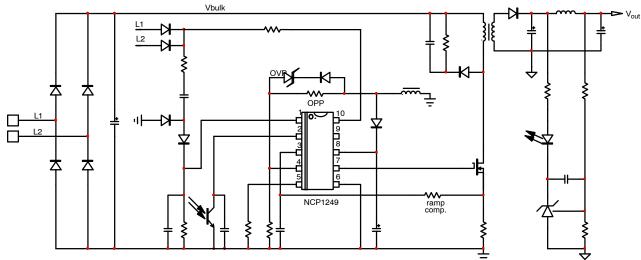

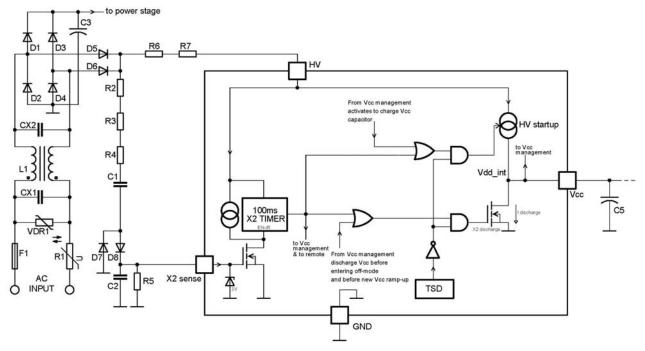

Figure 1. Typical Application Example

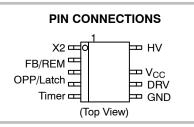

## Table 1. PIN FUNCTIONS

| Pin No | Pin Name      | Function                                                    | Pin Description                                                                                                                                           |

|--------|---------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | X2            | X2-capacitors discharge                                     | When the voltage on this pin disappears, the controller ensures the X2-capacitors discharge.                                                              |

| 2      | FB/REM        | Combined feedback and remote pin                            | Connecting an opto-coupler to this pin allows regulation. The opto-coupler can pull the feedback pin down and brings the controller in a deep sleep mode. |

| 3      | CS            | Current sense + ramp<br>compensation                        | This pin monitors the primary peak current but also offers a means to introduce slope compensation.                                                       |

| 4      | OPP/LATC<br>H | Adjust the Over Power<br>Protection<br>Latches off the part | A resistive divider from the auxiliary winding to this pin sets the OPP compensation level. When brought above 3 V, the part is fully latched off.        |

| 5      | TIMER         | Fault timer adjustment                                      | A resistor to ground adjusts the timer duration in fault condition.                                                                                       |

| 6      | GND           | -                                                           | The controller ground.                                                                                                                                    |

| 7      | DRV           | Driver output                                               | The driver's output to an external MOSFET gate.                                                                                                           |

| 8      | VCC           | Supplies the controller                                     | This pin is connected to an external auxiliary voltage and supplies the controller. When above a certain level, the part fully latches off.               |

| 9      | NC            | -                                                           | Increases insulation distance between high and low voltage pins.                                                                                          |

| 10     | HV            | High-voltage input                                          | This pin provides a charging current during start-up and auto-recovery faults but also a means to efficiently discharge the input X2 capacitors.          |

### Table 2. OPTIONS AND ORDERING INFORMATION

| Device         | Overload<br>Protection | Switching<br>Frequency | Peak Frequency | Package             | Shipping <sup>†</sup> |

|----------------|------------------------|------------------------|----------------|---------------------|-----------------------|

| NCP1249CD65R2G | Latched                | 65 kHz                 | 130 kHz        | SOIC-9<br>(Pb-Free) | 2500 / Tape &<br>Reel |

| NCP1249DD65R2G | Autorecovery           | 65 kHz                 | 130 kHz        | SOIC-9<br>(Pb-Free) | 2500 / Tape &<br>Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging. Specifications Brochure, BRD8011/D.

#### Table 3. MAXIMUM RATINGS TABLE

| Symbol              | Rating                                                                                    | Value                         | Unit |

|---------------------|-------------------------------------------------------------------------------------------|-------------------------------|------|

| V <sub>CC</sub>     | Power Supply voltage, VCC pin, continuous voltage                                         | -0.3 to 30                    | V    |

| V <sub>HV</sub>     | High Voltage (HV) Pin (pin 10)                                                            | -0.3 to 500                   | V    |

| Vpin_x              | Maximum voltage on low power pins (X2, CS, OPP, Timer)                                    | –0.3 to 10                    | V    |

| V <sub>FB/REM</sub> | Maximum voltage on FB/REM pin                                                             | –0.3 to 5                     | V    |

| V <sub>DRV</sub>    | Maximum voltage on drive pin                                                              | –0.3 to V <sub>CC</sub> + 0.3 | V    |

| I <sub>OPP</sub>    | Maximum injected current into the OPP pin                                                 | -2                            | mA   |

| $R_{\theta J-A}$    | Thermal Resistance Junction-to-Air                                                        | 211                           | °C/W |

| T <sub>J,max</sub>  | Maximum Junction Temperature                                                              | 150                           | °C   |

|                     | Storage Temperature Range                                                                 | -60 to +150                   | °C   |

|                     | ESD Capability, HBM model (All pins except HV) per JEDEC standard JESD22,<br>Method A114E | 2                             | kV   |

|                     | ESD Capability, Machine Model per JEDEC standard JESD22, Method A115A                     | 200                           | V    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. This device contains latch-up protection and exceeds 100 mA per JEDEC Standard JESD78.

| Table 4. ELECTRICAL CHARACTERISTICS (For typical values T <sub>J</sub> = 25°C, for min/max values | ; T <sub>J</sub> = −40°C to +125°C, |

|---------------------------------------------------------------------------------------------------|-------------------------------------|

| Max $T_J = 150^{\circ}C$ , $V_{CC} = 12$ V unless otherwise noted)                                |                                     |

| Symbol                       | Rating                                                                                   | Pin   | Min | Тур | Max  | Unit |

|------------------------------|------------------------------------------------------------------------------------------|-------|-----|-----|------|------|

| HV STARTUP CU                | RRENT SOURCE                                                                             | -     |     | -   | -    |      |

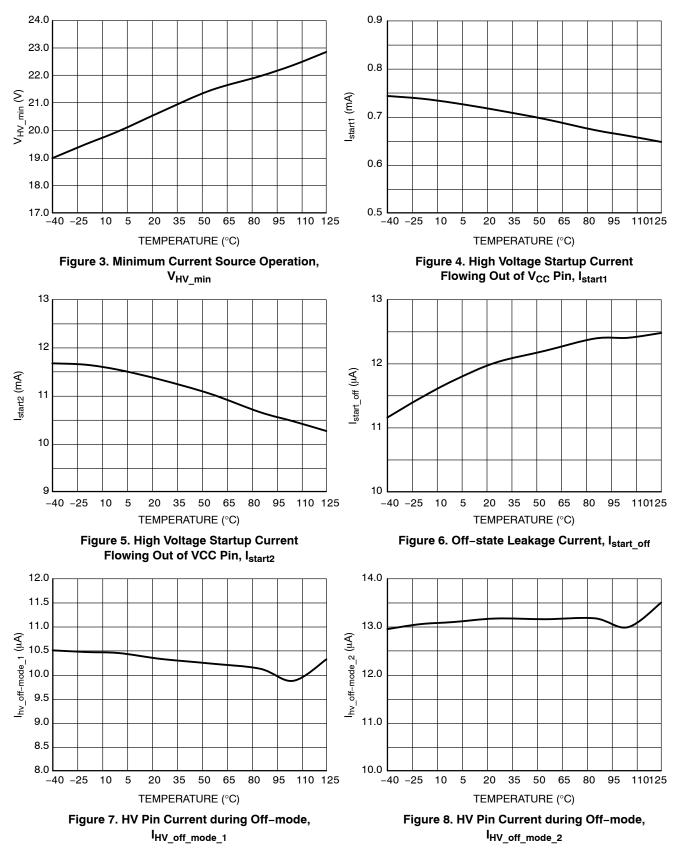

| V <sub>HV_min</sub>          | Minimum voltage for current source operation ( $V_{CC}$ = 4 V)                           | 10    | -   | 30  | 60   | V    |

| I <sub>start1</sub>          | Current flowing out of VCC pin ( $V_{CC} = 0 V$ )                                        | 8, 10 | 0.2 | 0.7 | 1    | mA   |

| I <sub>start2</sub>          | Current flowing out of VCC pin ( $V_{CC} = V_{CC_{ON}} - 0.5 V$ )                        | 8, 10 | 6   | 10  | 16   | mA   |

| V <sub>CC_inhibit</sub>      | $V_{CC}$ level for I <sub>start1</sub> to I <sub>start2</sub> transition                 | 8     | 0.5 | 1   | 1.25 | V    |

| I <sub>start_off</sub>       | Off-state leakage current ( $V_{HV}$ = 500 V, $V_{CC}$ = 15 V)                           | 10    | -   | 15  | -    | μA   |

| I <sub>HV_off</sub> -mode_1  | HV pin leakage current when off-mode is active ( $V_{HV}$ = 141 V)                       | 10    | -   | -   | 15   | μA   |

| I <sub>HV_off</sub> -mode_2  | HV pin leakage current when off-mode is active ( $V_{HV}$ = 325 V)                       | 10    | -   | -   | 19   | μA   |

| V <sub>HV_min_off-mode</sub> | Minimum voltage on HV pin during off-mode (V <sub>FB</sub> = 0 V, V <sub>CC</sub> = 0 V) | 10    | -   | -   | 10   | V    |

| SUPPLY SECTIO                | N                                                                                        | -     |     |     |      |      |

| V <sub>CC_ON</sub>           | $V_{CC}$ increasing level at which driving pulses are authorized                         | 8     | 16  | 18  | 20   | V    |

| V <sub>CC_OFF</sub>          | $V_{CC}$ decreasing level at which driving pulses are stopped                            | 8     | 9.5 | 10  | 11   | V    |

| V <sub>CC_HYST</sub>         | Hysteresis V <sub>CC_ON</sub> – V <sub>CC_OFF</sub>                                      | 8     | 6   | -   | -    | V    |

| V <sub>CC_bias</sub>         | V <sub>CC</sub> level during a fault                                                     | 8     | 4.7 | 5.5 | 6.5  | V    |

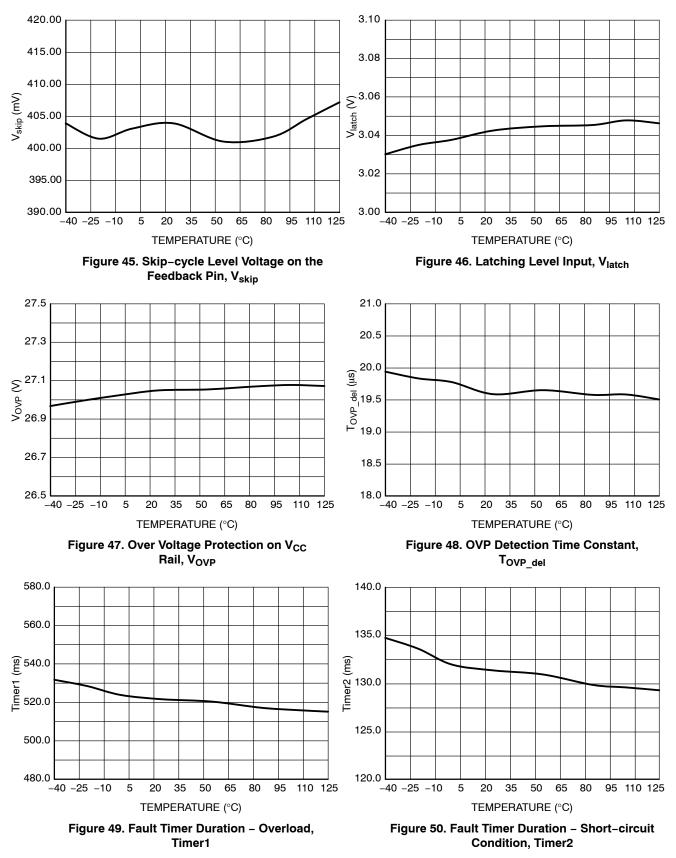

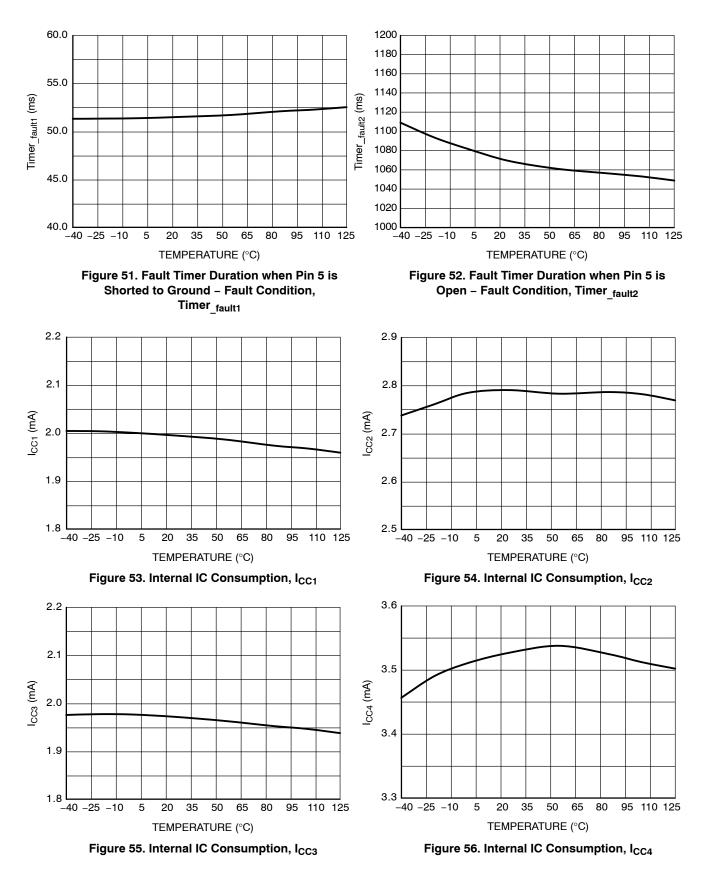

| I <sub>CC1</sub>             | Internal IC consumption with $I_{FB}$ = 75 $\mu A,f_{SW}$ = 65 kHz and $C_L$ = 0         | 8     | -   | 1.6 | 2.6  | mA   |

| I <sub>CC2</sub>             | Internal IC consumption with $I_{FB}$ = 75 $\mu A,f_{SW}$ = 65 kHz and $C_L$ = 1 nF      | 8     | -   | 2.3 | 3.4  | mA   |

| I <sub>CC3</sub>             | Internal IC consumption with $I_{FB}$ = 75 $\mu\text{A},f_{SW}$ = 130 kHz and $C_L$ = 0  | 8     | -   | 1.9 | 2.9  | mA   |

| I <sub>CC4</sub>             | Internal IC consumption with $I_{FB}$ = 75 $\mu A,f_{SW}$ = 130 kHz and $C_L$ = 1 nF     | 8     | -   | 3.3 | 4.4  | mA   |

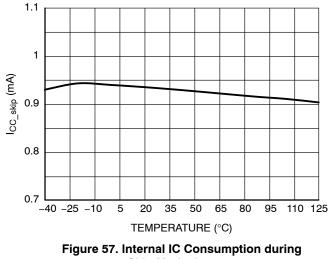

| I <sub>CC_skip</sub>         | Internal IC consumption while in skip mode                                               | 8     | 660 | 960 | 1360 | μA   |

| I <sub>CC_latch</sub>        | Internal IC consumption during Latch – off mode                                          | 8     | -   | 350 | 520  | μA   |

| BROWN-OUT                    |                                                                                          |       |     |     |      |      |

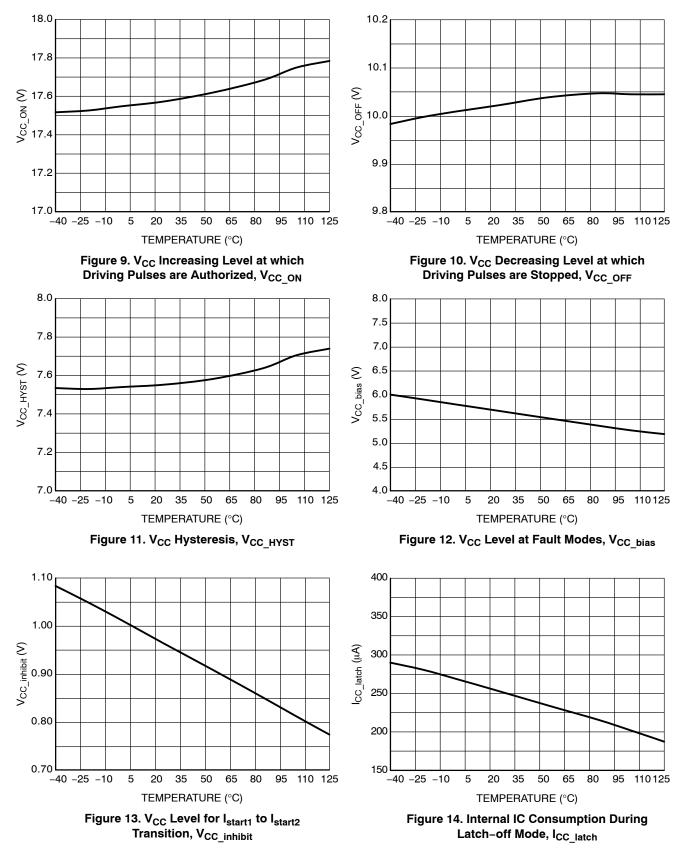

| V_BO_on                      | Brown–Out turn–on threshold (V <sub>HV</sub> going up)                                   | 10    | 92  | 101 | 110  | V    |

2. Guaranteed by design

3. See characterization table for linearity over negative bias voltage – we recommend keeping the level on pin 5 below –300 mV.

4. A 1 M $\Omega$  resistor is connected from pin 4 to the ground for the measurement.

| Table 4. ELECTRICAL CHARACTERISTICS (For typical values $T_J = 25^{\circ}C$ , for min/max values $T_J = -40^{\circ}C$ to $+125^{\circ}C$ , |  |

|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| Max $T_J = 150^{\circ}C$ , $V_{CC} = 12$ V unless otherwise noted)                                                                         |  |

| Symbol                  | Rating                                                                                              | Pin | Min   | Тур  | Max   | Unit |

|-------------------------|-----------------------------------------------------------------------------------------------------|-----|-------|------|-------|------|

| BROWN-OUT               |                                                                                                     | -   |       |      |       |      |

| V_ <sub>BO_off</sub>    | Brown–Out turn–off threshold (V <sub>HV</sub> going down)                                           | 10  | 84    | 93   | 102   | V    |

| BO_Timer                | Timer duration for line cycle drop-out                                                              | 10  | 40    | -    | 100   | ms   |

| X2 DISCHARGE            | CIRCUITRY                                                                                           | -   | -     |      |       |      |

| V <sub>th_X2</sub>      | X2 timer disable switch threshold voltage                                                           | 1   | 1     | 1.5  | 2     | V    |

| V <sub>th_X2_hyst</sub> | Hysteresis on the X2 pin                                                                            | 1   | -     | 100  | -     | mV   |

| V_X2_clamp              | X2 input clamp voltage                                                                              | 1   | -     | 4    | -     | V    |

| X2_Timer                | X2 timer duration                                                                                   | 1   | 70    | -    | 140   | ms   |

| I_X2_leak               | X2 input leakage current (V <sub>_X2</sub> = 2.5 V)                                                 | 1   | -     | -    | 0.3   | μA   |

| I_x2_dis                | Maximum discharge switch current (V <sub>CC</sub> = 10 V)                                           | 10  | 6     | 10   | 13    | mA   |

| DRIVE OUTPUT            |                                                                                                     |     |       |      |       |      |

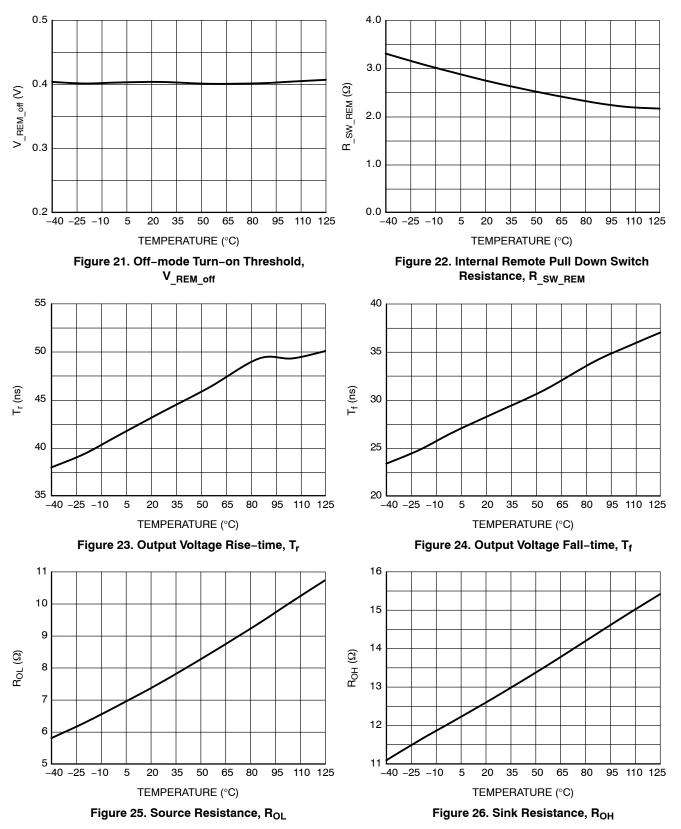

| T <sub>r</sub>          | Output voltage rise-time @ C <sub>L</sub> = 1 nF, 10-90% of output signal                           | 7   | -     | 40   | 80    | ns   |

| T <sub>f</sub>          | Output voltage fall-time @ $C_L = 1 \text{ nF}$ , 10–90% of output signal                           | 7   | -     | 30   | 70    | ns   |

| R <sub>OH</sub>         | Source resistance                                                                                   | 7   | -     | 13   | -     | Ω    |

| R <sub>OL</sub>         | Sink resistance                                                                                     | 7   | -     | 6    | -     | Ω    |

| I <sub>source</sub>     | Peak source current, V <sub>GS</sub> = 0 V (Note 2)                                                 | 7   |       | 300  |       | mA   |

| I <sub>sink</sub>       | Peak sink current, V <sub>GS</sub> = 12 V (Note 2)                                                  | 7   |       | 500  |       | mA   |

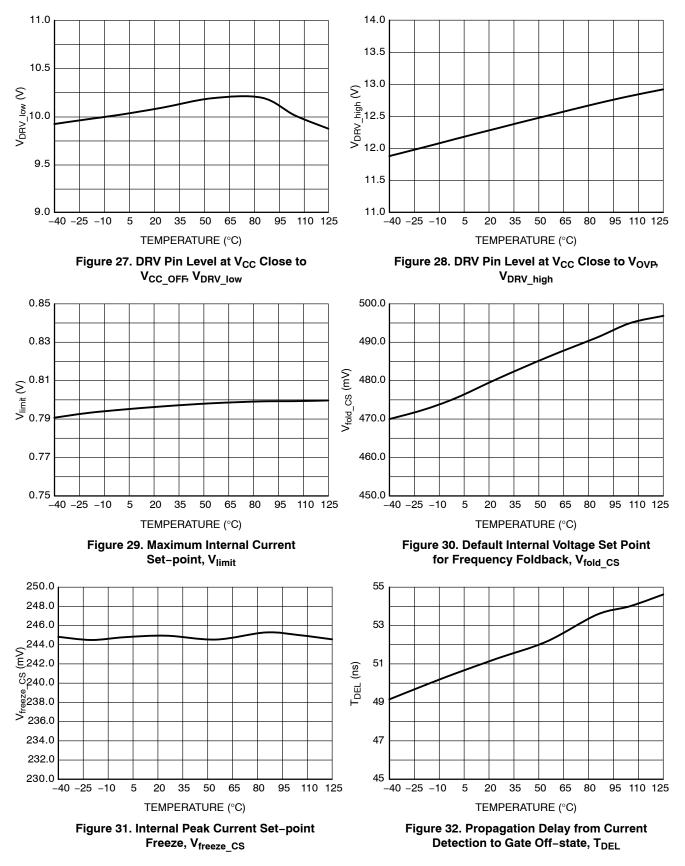

| V <sub>DRV_low</sub>    | DRV pin level at V_{CC} close to V_{CC} _ OFF with a 33 k $\!\Omega$ resistor to GND                | 7   | 8     | -    | -     | V    |

| V <sub>DRV_high</sub>   | DRV pin level at V <sub>CC</sub> = V <sub>OVP</sub> -0.2 V, DRV unloaded                            | 7   | 10    | 12   | 14    | V    |

| CURRENT COMP            | PARATOR                                                                                             |     |       |      |       |      |

| I <sub>IB</sub>         | Input Bias Current @ 0.8 V input level on pin 3                                                     | 3   |       | 0.02 |       | μA   |

| V <sub>limit</sub>      | Maximum internal current setpoint – $T_J$ = 25°C – pin 4 grounded                                   | 3   | 0.744 | 0.8  | 0.856 | V    |

| V <sub>limit</sub>      | Maximum internal current setpoint –<br>T <sub>J</sub> from –40°C to 125°C – pin 4 grounded          | 3   | 0.72  | 0.8  | 0.88  | V    |

| V <sub>fold_cs</sub>    | Default internal voltage set point for frequency foldback trip point $\approx$ 47% of $V_{limit}$   | 3   |       | 475  |       | mV   |

| V <sub>freeze_cs</sub>  | Internal peak current setpoint freeze (≈31% of V <sub>limit</sub> )                                 | 3   |       | 250  |       | mV   |

| T <sub>DEL</sub>        | Propagation delay from current detection to gate off-state                                          | 3   |       | 100  | 150   | ns   |

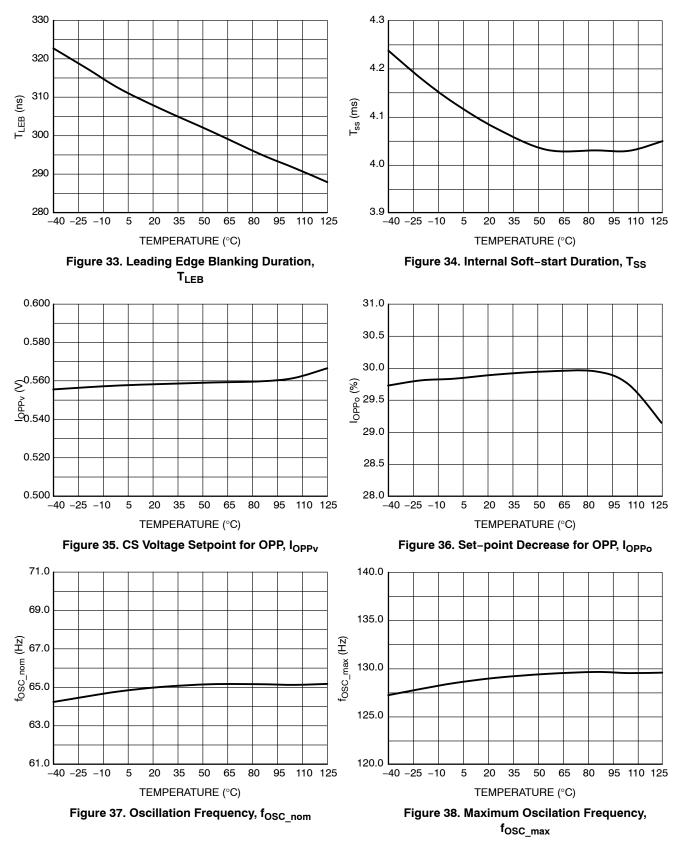

| T <sub>LEB</sub>        | Leading Edge Blanking Duration                                                                      | 3   |       | 300  |       | ns   |

| T <sub>SS</sub>         | Internal soft-start duration activated upon startup, auto-recovery                                  | -   |       | 4    | 1     | ms   |

| I <sub>OPPo</sub>       | Setpoint decrease for pin 5 biased to –250 mV – (Note 3)                                            | 3   |       | 31.3 | 1     | %    |

| I <sub>OOPv</sub>       | Voltage setpoint for pin 5 biased to –250 mV – (Note 3) $T_J$ from –40 $^\circ C$ to 125 $^\circ C$ | 3   | 0.5   | 0.55 | 0.62  | V    |

| I <sub>OPPs</sub>       | Setpoint decrease for pin 4 grounded                                                                | 3   |       | 0    | 1     | %    |

| INTERNAL OSCI           | LLATOR                                                                                              |     |       |      |       | •    |

| f <sub>OSC_nom</sub>    | Oscillation frequency, V <sub>FB</sub> < V <sub>FBtrans</sub> , pin 4 grounded                      | -   | 57    | 65   | 71    | kHz  |

| V <sub>FBtrans</sub>    | Feedback voltage above which f <sub>sw</sub> increases                                              | 2   | 1     | 3.2  | 1     | V    |

| f <sub>OSC_nom</sub> | Oscillation frequency, V <sub>FB</sub> < V <sub>FBtrans</sub> , pin 4 grounded | - | 57  | 65  | 71  | kHz |

|----------------------|--------------------------------------------------------------------------------|---|-----|-----|-----|-----|

| V <sub>FBtrans</sub> | Feedback voltage above which f <sub>sw</sub> increases                         | 2 |     | 3.2 |     | V   |

| f <sub>OSC_max</sub> | Maximum oscillation frequency for $V_{FB}$ above $V_{FBmax}$                   | - | 115 | 130 | 140 | kHz |

| V <sub>FBmax</sub>   | Feedback voltage above which f <sub>sw</sub> is constant                       | 2 | 3.8 | 4   | 4.2 | V   |

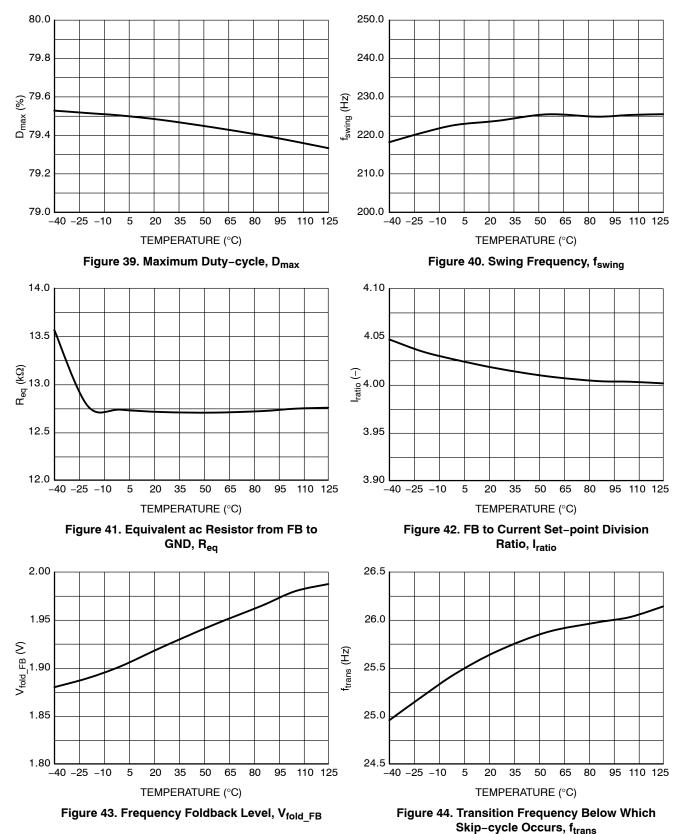

| D <sub>max</sub>     | Maximum duty ratio                                                             | - | 76  | 80  | 84  | %   |

Guaranteed by design

See characterization table for linearity over negative bias voltage – we recommend keeping the level on pin 5 below –300 mV.

A 1 MΩ resistor is connected from pin 4 to the ground for the measurement.

| <b>Table 4. ELECTRICAL CHARACTERISTICS</b> (For typical values $T_J = 25^{\circ}C$ , for min/max values $T_J = -40^{\circ}C$ to $+125^{\circ}C$ , |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Max $T_J = 150^{\circ}C$ , $V_{CC} = 12$ V unless otherwise noted)                                                                                |  |

| Symbol                   | Rating                                                                                        | Pin | Min | Тур  | Max | Unit |

|--------------------------|-----------------------------------------------------------------------------------------------|-----|-----|------|-----|------|

| INTERNAL OSCI            | LLATOR                                                                                        |     |     |      |     |      |

| f <sub>jitter</sub>      | Frequency jittering in percentage of fOSC                                                     | -   |     | ±5   |     | %    |

| f <sub>swing</sub>       | Swing frequency over the whole frequency range                                                | -   |     | 240  |     | Hz   |

| FEEDBACK / RE            | MOTE SECTION                                                                                  |     |     | -    | -   | -    |

| R <sub>up(FB)</sub>      | Internal pull-up resistor                                                                     | 2   |     | 17   |     | kΩ   |

| R <sub>eq</sub>          | Equivalent ac resistor from FB to GND                                                         | 2   | 10  | 15   | 20  | kΩ   |

| I <sub>ratio</sub>       | Pin 2 to current setpoint division ratio                                                      | 2,3 |     | 4    |     | -    |

| V <sub>freeze_FB</sub>   | Feedback voltage below which the peak current is frozen                                       | 2   |     | 1    |     | V    |

| V_REM_off                | Feedback voltage below which the part enters into off-mode                                    | 2   |     | 0.4  |     | V    |

| V_REM_on                 | Feedback voltage above which is the off-mode deactivated                                      | 2   | 1.5 | 2    | 2.5 | V    |

| I <sub>FBREM</sub>       | Feedback current that lifts the feedback pin upon off-mode exit                               | 2   |     | 2.4  | 4   | μA   |

| FREQUENCY FO             | LDBACK                                                                                        |     |     |      |     |      |

| $V_{fold\_FB}$           | Frequency foldback level on the feedback pin –<br>≈47% of maximum peak current                | 2   |     | 1.9  |     | V    |

| f <sub>trans</sub>       | Transition frequency below which skip-cycle occurs                                            | -   | 22  | 26   | 30  | kHz  |

| V <sub>fold_end</sub>    | End of frequency foldback feedback level, $f_{sw} = f_{min}$                                  | 2   |     | 1.5  |     | V    |

| V <sub>skip</sub>        | Skip-cycle level voltage on the feedback pin                                                  | 2   |     | 400  |     | mV   |

| Skip hysteresis          | Hysteresis on the skip comparator (Note 2)                                                    | 2   |     | 30   |     | mV   |

| INTERNAL SLOP            | E COMPENSATION                                                                                |     |     | -    | -   | -    |

| V <sub>ramp</sub>        | Internal ramp level @ 25°C (Note 4)                                                           | 3   |     | 2.5  |     | V    |

| R <sub>ramp</sub>        | Internal ramp resistance to CS pin                                                            | 3   |     | 20   |     | kΩ   |

| PROTECTIONS              |                                                                                               |     |     |      |     |      |

| V <sub>latch</sub>       | Latching level input                                                                          | 4   | 2.7 | 3    | 3.3 | V    |

| T <sub>latch-blank</sub> | Blanking time after drive turn off                                                            | 4   |     | 1    |     | μs   |

| T <sub>latch-count</sub> | Number of clock cycles before latch confirmation                                              | -   |     | 4    |     | -    |

| T <sub>latch-del</sub>   | OVP detection time constant                                                                   | 4   |     | 600  |     | ns   |

| V <sub>OVL</sub>         | Feedback voltage at which an overload is considered – OPP pin is grounded                     | 2   |     | 3.2  |     | V    |

| V <sub>SC</sub>          | Feedback voltage above which a short-circuit is considered                                    | 2   | 3.9 | 4.1  | 4.3 | V    |

| Timer <sub>1</sub>       | Fault timer duration for a 22 $k\Omega$ resistor from pin 5 to ground – overload              | 5   | 350 | 500  | 650 | ms   |

| Timer <sub>2</sub>       | Fault timer duration when $V_{FB} > 4.1 V$ is Timer <sub>1</sub> /4 – short–circuit condition | 5   | 88  | 125  | 162 | ms   |

| Timer_fault1             | Timer duration when pin 5 is shorted to ground – fault condition                              | 5   |     | 50   |     | ms   |

| Timer_ <sub>fault2</sub> | Timer duration when pin 5 is open – fault condition                                           | 5   |     | 1000 |     | ms   |

| V <sub>OVP</sub>         | Latched Over voltage protection on the $V_{CC}$ rail                                          | 8   | 26  | 27.5 | 29  | V    |

| T <sub>OVP_del</sub>     | Delay before OVP on V <sub>CC</sub> confirmation                                              | 8   |     | 20   | 30  | μs   |

| T <sub>A-rec_timer</sub> | Auto-recovery timer duration                                                                  | -   | 1.4 | -    | -   | s    |

#### **TEMPERATURE SHUTDOWN**

| T <sub>TSD</sub>      | Temperature shutdown $T_J$ going up | - | 150 | °C |

|-----------------------|-------------------------------------|---|-----|----|

| T <sub>TSD(HYS)</sub> | Temperature shutdown hysteresis     | - | 30  | °C |

Guaranteed by design

See characterization table for linearity over negative bias voltage – we recommend keeping the level on pin 5 below –300 mV.

A 1 MΩ resistor is connected from pin 4 to the ground for the measurement.

Skip Mode, I<sub>CC\_skip</sub>

# **APPLICATION INFORMATION**

#### Introduction

The NCP1249 implements a standard current mode architecture where the switch-off event is dictated by the peak current setpoint. This component represents the ideal candidate where low part-count and cost effectiveness are the key parameters, particularly in low-cost ac-dc adapters, open-frame power supplies etc. The NCP1249 brings all the necessary components normally needed in today modern power supply designs, bringing several enhancements such as a non-dissipative OPP, a brown-out protection or peak power excursion for loads exhibiting variations over time. Accounting for the new needs of extremely low standby power requirements, the part includes an automatic X2-capacitor discharge circuitry that prevents the designer from installing power-consuming resistors across the front-end filtering capacitors. The controller is also able to enter a deep sleep mode via combined for feedback/remote pin.

- High-Voltage start-up: low standby power results cannot be obtained with the classical resistive start-up network. In this part, a high-voltage current-source provides the necessary current at start-up and turns off afterwards.

- Internal Brown–Out protection: a portion of the bulk voltage is internally sensed via the high–voltage pin monitoring (pin 10). When the voltage on this pin is too low, the part stops pulsing. No re–start attempt is made until the controller senses that the voltage is back within its normal range. When the brown–out comparator senses the voltage is acceptable, it sends a general reset to the controller (de–latch occurs) and authorizes to re–start.

- X2-capacitors discharge capability: per IEC-950 standard, the time constant of the front-end filter capacitors and their associated discharge resistors must be less than 1 s. This is to avoid electrical stress when the user unplugs the converter and inadvertently touches the power cord terminals. By providing an automatic means to discharge the X2 capacitors, the NCP1249 prevents the designer from installing the discharge resistors, helping to further save power.

- Combined feedback/remote control pin: the controller features a combined feedback/remote pin that forces the adapter to enter a deep off mode. When the FB pin is pulled down (slightly below the skip cycle mode), the part obviously stops all drive pulses. The auxiliary voltage disappears and IC goes into sleep mode. As the pull-down signal on the feedback pin is secondary-side driven, a wake-up signal releases the feedback pin and allows a fresh start-up sequence. If a dedicated circuitry is implemented on the secondary side, a self-relaxing mode can be implemented with very low standby power consumption.

- Current-mode operation with internal slope compensation: implementing peak current mode control at a fixed 65 kHz frequency, the NCP1249 offers an internal ramp compensation signal that can easily by summed up to the sensed current. Sub harmonic oscillations can thus be compensated via the inclusion of a simple resistor in series with the current-sense information.

- Frequency excursion: when the power demand forces the peak current setpoint to reach the internal limit (0.8 V/R<sub>sense</sub> typically), the frequency is authorized to increase to let the converter deliver more power. The frequency excursion stops when 130 kHz are reached.

- Internal OPP: by routing a portion of the negative voltage present during the on-time on the auxiliary winding to the dedicated OPP pin (pin 5), the user has a simple and non-dissipative means to alter the maximum peak current setpoint as the bulk voltage increases. If the pin is grounded, no OPP compensation occurs. If the pin receives a negative voltage down to -250 mV, then a peak current reduction down to 31.3% typical can be achieved. For an improved performance, the maximum voltage excursion on the sense resistor is limited to 0.8 V.

- EMI jittering: an internal low-frequency modulation signal varies the pace at which the oscillator frequency is modulated. This helps spreading out energy in conducted noise analysis. To improve the EMI signature at low power levels, the jittering will not be disabled in frequency foldback mode (light load conditions).

- Frequency foldback capability: a continuous flow of pulses is not compatible with no-load/light-load standby power requirements. To excel in this domain, the controller observes the feedback pin and when it reaches a level of 1.5 V, the oscillator then starts to reduce its switching frequency as the feedback level continues to decrease. When the feedback pin reaches 1 V, the peak current setpoint is internally frozen and the frequency continues to decrease. It can go down to 26 kHz (typical) reached for a feedback level of 450 mV roughly. At this point, if the power continues to drop to 400 mV, the controller enters classical skip-cycle mode.

- Internal soft-start: a soft-start precludes the main power switch from being stressed upon start-up. In this controller, the soft-start is internally fixed to 4 ms. Soft-start is activated when a new startup sequence occurs or during an auto-recovery hiccup.

- Latch input: the NCP1249 includes a latch input (pin 4) that can be used to sense an overvoltage condition on the adapter. If this pin is brought higher

than the internal reference voltage  $V_{latch}$ , then the circuit permanently latches off. The VCC pin is pulled down to a fixed level, keeping the controller latched. The latch reset occurs when the user disconnects the adapter from the mains.

- V<sub>CC</sub> OVP: a latched OVP protects the circuit against V<sub>CC</sub> runaways. The fault must be present at least 20 µs to be validated. Reset occurs when the user disconnects the adapter from the mains.

- Short-circuit protection: short-circuit and especially over-load protections are difficult to implement when a strong leakage inductance between auxiliary and power windings affects the transformer (the aux winding level does not properly collapse in presence of an output short). Here, every time the internal 0.8-V maximum peak current limit is activated (or less when OPP is used), an error flag is asserted and a time period starts, thanks to the programmable timer. The controller can distinguish between two faulty situations:

- There is an extra demand of power, still within the power supply capabilities. In that case, the feedback level is in the vicinity of 3.2–4 V. It corresponds to 0.8 V as the maximum peak current setpoint without

OPP. The timer duration is then 100% of its normal value. If the fault disappears, e.g. the peak current setpoint no longer hits the maximum value (e.g. 0.8 V at no OPP), then the timer is reset.

- The output is frankly shorted. The feedback level is thus pushed to its upper stop (4.5 V) and the timer is reduced to 25% of its normal value.

- In either mode, when the fault is validated, all pulses are stopped and the controller enters an auto-recovery burst mode, with a soft-start sequence at the beginning of each cycle. Please note the presence of a divider by two which ignores one hiccup cycle over two (double hiccup type of burst).

- As soon as the fault disappears, the SMPS resumes operation. Please note that some version offers an auto-recovery mode as we just described, some do not and latch off in case of a short circuit.

### Start-up Sequence

The start-up sequence of the NCP1249 involves a high-voltage current source whose input is in pin 10. As this start-up source also performs line sensing for brown-out operation, it is recommended to wire it according to Figure 58 sketch.

Figure 58. The Startup Resistor can be Connected to the Input Mains for Further Power Dissipation Reduction

In this drawing, the high–voltage pin is not connected to the bulk, but to the full–wave rectified ac input. It is important to keep this configuration as the X2 circuitry will also use it.

The first step starts with the calculation of the needed  $V_{CC}$  capacitor which will supply the controller until the auxiliary winding takes over. Experience shows that this time  $t_1$  can be between 5 and 20 ms. Considering that we need at least an energy reservoir for a  $t_1$  time of 10 ms, the  $V_{CC}$  capacitor must be larger than:

$$C_{Vcc} \geq \frac{I_{CC4} \times t_1}{V_{CC \ ON} - V_{CC \ OFF}} \geq \frac{3 \ m \times 10 \ m}{18 - 10} \geq 3.75 \ \mu F^{(eq. \ 1)}$$

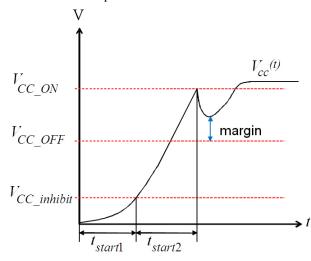

In this calculation, we adopted the consumption at the highest switching frequency since this is the point at which the IC will work in cold-start case. Let us select a 4.7  $\mu$ F capacitor at first and experiments in the laboratory will let us know if we were too optimistic for t<sub>1</sub>. The V<sub>CC</sub> capacitor being known, we can now evaluate the charging time to bring the V<sub>CC</sub> voltage from 0 to the V<sub>CC\_ON</sub> of the IC, 18 V typical. This time sequence can actually be split into two events: 0 V to V<sub>CC\_inhibit</sub> and V<sub>CC\_inhibit</sub> to V<sub>CC\_ON</sub>. This is because the HV source is protected from short-circuits on the V<sub>CC</sub> voltage is less than V<sub>CC\_inhibit</sub> and only delivers I<sub>start1</sub> which is below 1 mA: the die power consumption is maintained to the lowest value. In normal operation, when the voltage has normally reached V<sub>CC\_inhibit</sub>, the source toggles to the full current and charges the V<sub>CC</sub> capacitor at

a larger current,  $I_{start2}$ . The first time duration involves  $I_{start1}$  and  $V_{CC}$  inhibit.

$$t_{start1} = \frac{V_{CC\_inhibit} \times C_{Vcc}}{I_{start1}} = \frac{1 \times 4.7 \,\mu}{700 \,\mu} \approx 6.7 \,\text{ms} \tag{eq. 2}$$

The second duration involves V<sub>CC ON</sub> and I<sub>start2</sub>:

$$t_{start2} = \frac{\left(V_{CC\_ON} - V_{CC\_inhibit}\right)C_{Vcc}}{I_{start2}} = \frac{(18 - 1) \times 4.7 \,\mu}{10 \text{ m}} \approx 8 \text{ ms} \qquad (eq. 3)$$

The total start-up time is thus around 14-15 ms.

Figure 59. The VCC at Start-up is Made of Two Segments Given the Short-circuit Protection Implemented on the HV Source

In case the V<sub>CC</sub> capacitor must be increased to cope with no-load standby requirements, there is plenty of margin to keep the total start-up sequence duration below 1 s. Assume the V<sub>CC</sub> capacitor is 100  $\mu$ F, then the total start-up time would be below 400 ms.

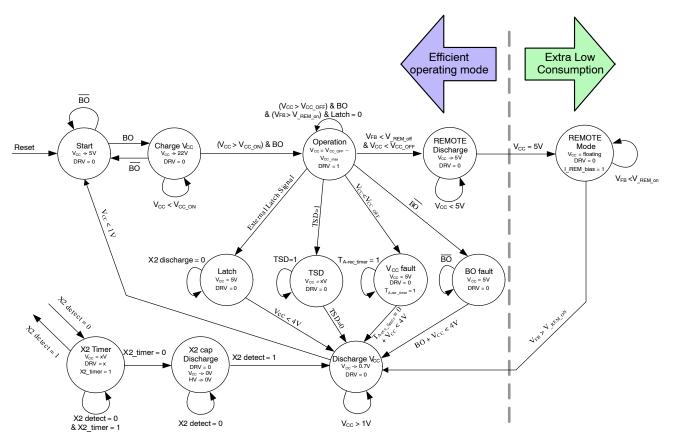

#### **Brown-out Circuitry**

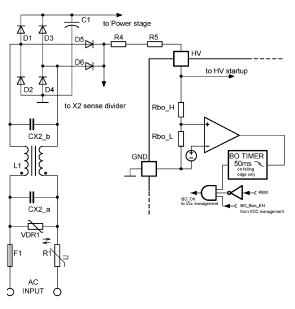

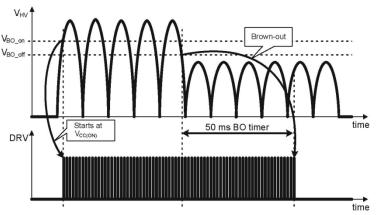

The NCP1249 features, on its HV pin, a true AC line monitoring circuitry – refer to Figure 60. This system includes a minimum start–up threshold and auto–recovery brown–out protection; both of them independent of the input voltage ripple. The thresholds are fixed, but they are designed to fit most of the standard AC–DC converter applications. When the HV pin voltage drops below  $V_{BO_off}$ threshold for more than 50 ms, the brown–out condition is detected and confirmed. Thus the controller stops operation – refer to Figure 61. The V<sub>CC</sub> capacitor is discharged to  $Vcc_{bias}$  level. The HV current source maintains V<sub>CC</sub> at  $Vcc_{bias}$  level until the input voltage is back above  $V_{BO_on}$ . The controller then fully discharges V<sub>CC</sub> capacitor first to restart internal logic. Standard startup attempt is then placed by the controller.

The Internal HV BO sensing network is formed by high impedance resistor divider with minimum resistance of 20 M $\Omega$ . This solution reducing power losses during off-mode and thus helps to pass maximum standby power consumption limit. The internal BO network solution provides excellent noise and PCB leakage currents immunity that is hard to achieve when using external resistor divider built from SMT chip resistors.

Figure 61. Brown-out Event Detection

### X2 and $V_{CC}$ Discharge Circuitry

The NCP1249 X2 discharge circuitry uses dedicated pin (X2) together with external charge pump sensing network to detect whether is application plugged into the mains or not. Advantage of this solution is that the internal IC consumption can be reduced to extremely low level by keeping all internal blocks unbiased except simple and low

consuming X2 timer disable circuitry. The internal X2 timer with typical duration of 100 ms is used to overcome unwanted activation of the X2 discharge switch in case of AC line dropout. The internal X2 discharge switch is activated once the X2 timer elapses. The HV startup current source is enabled in the same time thus the discharge path for X2 capacitor exists – refer to Figure 62.

Figure 62. Simplified Block Diagram of X2 and Vcc Capacitor Discharge Circuitry

The time duration of X2 capacitors discharging could be calculated by:

$$t = \frac{U_{C_{X1,2}}}{I_{X2_{dis}}} \cdot C_{X1,2}$$

(eq. 4)

The X2 capacitor discharging process can be interrupted by increasing voltage on X2 pin back above  $V_{th X2}$ .

The over temperature protection block is active during discharging process to protect controller chip against

unwanted overheat that could occur in case the X2 pin is opened and the high voltage is present on the HV pin (like during open – short pins testing for instance).

The X2 discharge switch is also activated to discharge  $V_{CC}$  capacitor when entering into fault mode (latch mode, auto-recovery mode or the HV pin voltage drops below  $V_{BO_off}$  threshold for more than 50 ms), off-mode and also before controller  $V_{CC}$  restart.

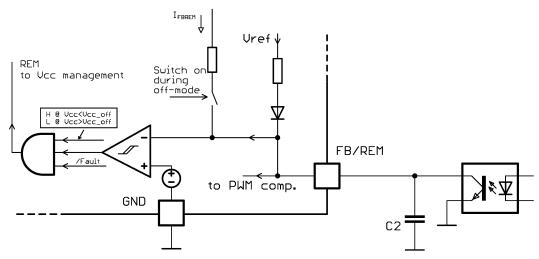

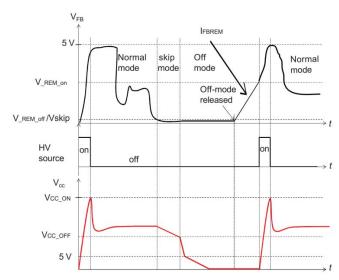

#### Feedback/Remote Input

The off mode is activated when the remote pin is low and  $V_{CC\_OFF}$  threshold is crossed i.e. when the skip mode takes so long time that  $V_{CC}$  is lost.  $V_{CC}$  capacitor is then discharged by internal consumption. Maximum skip mode

duration before the NCP1249 enters off-mode is thus given by value of  $V_{CC}$  capacitor, total consumption during skip mode and voltage level on  $V_{CC}$  capacitor in the time when flyback controller enters skip mode.

Figure 63. Simplified Block Diagram of FB/REM Control Input

To force the controller entering the off mode, the voltage on the feedback pin has to go below the skip cycle level, 400 mV typically. At this moment, all pulses are blocked and the auxiliary  $V_{CC}$  declines down to 0 V at a pace fixed by the  $V_{CC}$  capacitor and the controller consumption. When it passes below the  $V_{CC_OFF}$  threshold, because the FB pin is still maintained low, the controller does not reactivate the high-voltage start-up source and the circuit remains locked, consuming the least power. The circuit remains off as long as the feedback pin pulled to ground.

When the feedback pin is released, an internal current source  $(I_{FBREM})$ , pulls the feedback voltage up, above the

inhibition comparator. At this moment, the high-voltage source is good to go and it refuels the V<sub>CC</sub> capacitor until a new start-up sequence occurs. If the feedback pin is driven by a dedicated off-mode controller, shortly after the new start-up sequence, the feedback pin will go down again, initiating another off cycle. The resulting output voltage exhibits a large low-frequency ripple, naturally decreasing the overall consumption budget of the converter. Typical V<sub>CC</sub> and feedback signals while in this mode are drawn in Figure 64.

Figure 64. Combined FB/REM Pin Behavior

#### **Operating Status Diagram**

The NCP1249A/B  $V_{CC}$  management behavior is clearly described in status diagram on Figure 65.

Figure 65. V<sub>CC</sub> Management Status Diagram

#### **Internal Over Power Protection**

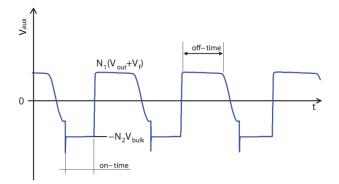

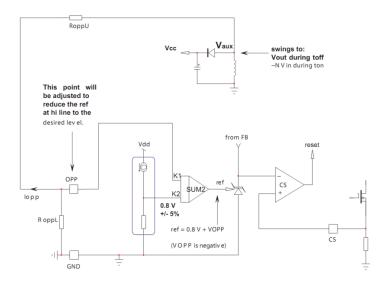

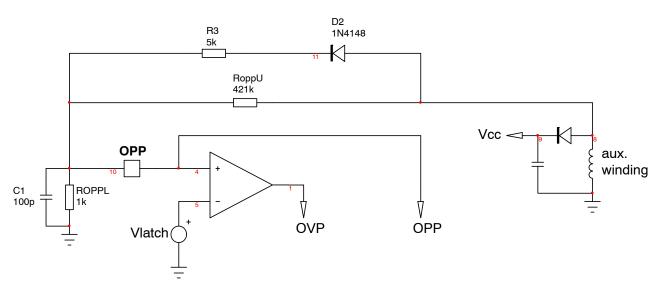

There are several known ways to implement Over Power Protection (OPP), all suffering from particular problems. These problems range from the added consumption burden on the converter or the skip-cycle disturbance brought by the current-sense offset. A way to reduce the power capability at high line is to capitalize on the negative voltage swing present on the auxiliary diode anode. During the turn-on time, this point dips to  $-NV_{in}$ , N being the turns ratio between the primary winding and the auxiliary winding. The negative plateau observed on Figure 66 will have amplitude depending on the input voltage. The idea implemented in this chip is to sum a portion of this negative swing with the 0.8 V internal reference level. For instance, if the voltage swings down to -150 mV during the on time, then the internal peak current set point will be fixed to 0.8 - 0.150 =650 mV. The adopted principle appears in Figure 67 and shows how the final peak current set point is constructed.

#### Figure 66. The Signal Obtained on the Auxiliary Winding Swings Negative During the On–Time

Let's assume we need to reduce the peak current from 2.5 A at low line, to 2 A at high line. This corresponds to a 20% reduction or a set point voltage of 640 mV. To reach this level, then the negative voltage developed on the OPP pin must reach:

$$V_{OPP} = 640 \text{ m} - 800 \text{ m} = -160 \text{ mV}$$

(eq. 5)

Figure 67. The OPP Circuitry Affects the Maximum Peak Current Set Point by Summing a Negative Voltage to the Internal Voltage Reference

Let us assume that we have the following converter characteristics:

$$\begin{split} V_{out} &= 19 \ V \\ V_{in} &= 85 \ to \ 265 \ V \ rms \\ N_1 &= N_p : N_s = 1 : 0.25 \\ N_2 &= N_p : N_{aux} = 1 : 0.18 \end{split}$$

Given the turns ratio between the primary and the auxiliary windings, the on-time voltage at high line (265 Vac) on the auxiliary winding swings down to:

$$V_{aux} = -N_2 V_{in max} = -0.18 \times 375 = -67.5 V$$

(eq. 6)

To obtain a level as imposed by (Equation 5), we need to install a divider featuring the following ratio:

Div

$$= \frac{0.16}{67.5} \approx 2.4 \text{ m}$$

(eq. 7)

If we arbitrarily fix the pull-down resistor  $R_{OPPL}$  to 1 k $\Omega$ , then the upper resistor can be obtained by:

$$\mathsf{R}_{\mathsf{OPPU}} = \frac{67.5 - 0.16}{0.16/1 \ \mathsf{k}} \approx 421 \ \mathsf{k}\Omega \qquad (\mathsf{eq. 8})$$

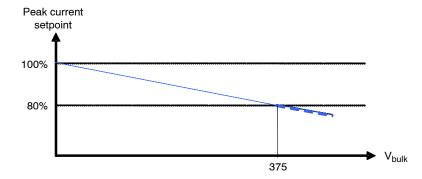

If we now plot the peak current set point obtained by implementing the recommended resistor values, we obtain the following curve (Figure 68):

Figure 68. The peak current regularly reduces down to 20% at 375 V dc

The OPP pin is surrounded by Zener diodes stacked to protect the pin against ESD pulses. These diodes accept some peak current in the avalanche mode and are designed to sustain a certain amount of energy. On the other side, negative injection into these diodes (or forward bias) can cause substrate injection which can lead to an erratic circuit behavior. To avoid this problem, the pin is internal clamped slightly below –300 mV which means that if more current is injected before reaching the ESD forward drop, then the maximum peak reduction is kept to 40%. If the voltage finally forward biases the internal zener diode, then care must be taken to avoid injecting a current beyond -2 mA. Given the value of  $R_{OPPU}$ , there is no risk in the present example. Finally, please note that another comparator internally fixes the maximum peak current set point to 0.8 V even if the OPP pin is adversely biased above 0 V.

For optimum performance over temperature, we recommend keeping the low-side OPP resistor below 3 k $\Omega$ .

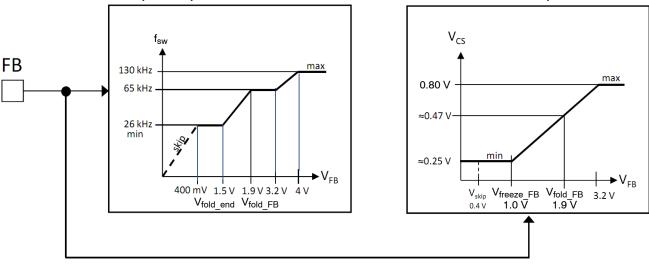

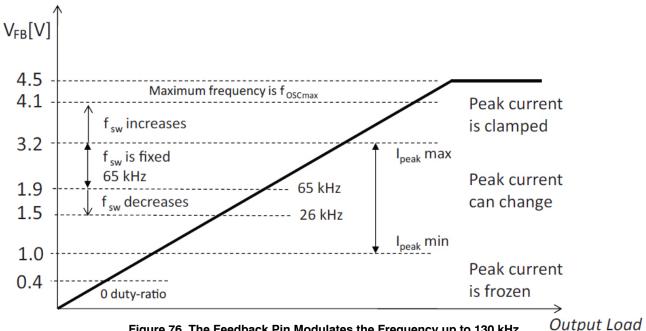

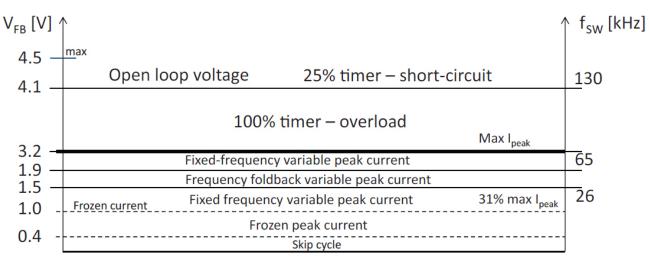

### **Frequency Foldback**

The reduction of no-load standby power associated with the need for improving the efficiency, requires a change in the traditional fixed-frequency type of operation. This controller implements a switching frequency foldback when the feedback voltage passes below a certain level,  $V_{fold\_FB}$ , set around 1.9 V. At this point, the oscillator turns into a Voltage-Controlled Oscillator and reduces its switching frequency. The peak current setpoint is following the

Frequency

feedback pin until its level reaches 1 V. Below this value, the peak current freezes to  $V_{\text{freeze}_FB/4}$  (250 mV or  $\approx 31\%$  of the maximum 0.8 V setpoint) and the only way to further reduce the transmitted power is to diminish the operating frequency down to 26 kHz. This value is reached at a voltage feedback level of 450 mV typically. Below this point, if the output power continues to decrease, the part enters skip cycle for the best noise–free performance in no–load conditions. Figure 69 depicts the adopted scheme for the part.

# Peak current setpoint

Figure 69. By Observing the Voltage on the Feedback Pin, the Controller Reduces its Switching Frequency for an Improved Performance at Light Load

#### Auto-recovery Short-circuit Protection

In case of output short-circuit or if the power supply experiences a severe overloading situation, an internal error flag is raised and starts a countdown timer. If the flag is asserted longer than fault timer duration, the driving pulses are stopped and the  $V_{CC}$  capacitor is discharged down to 10 V ( $V_{CC OFF}$  threshold) by controller ICC consumption. At this point, the controller activates 2 s auto-recovery timer that starts to count down the time to new restart attempt. The total restart time from fault confirmation is thus given by sum of two times:  $V_{\mbox{\scriptsize CC}}$  capacitor discharge time from given Vcc level (present at fault confirmation event) to V<sub>CC OFF</sub> level and 2 s internal auto-recovery timer duration. The  $V_{CC}$ capacitor is discharged to V<sub>CC bias</sub> level when auto-recovery timer starts counting. The V<sub>CC</sub> is maintained at V<sub>CC bias</sub> level during this operation to keep timer and other internal circuitry running.

The V<sub>CC</sub> capacitor is fully discharged by X2 discharge switch before controller tries for restart from fault condition. The restart from fault condition is caused when auto-recovery timer elapses or V<sub>CC</sub> is forced below 4 V externally. The HV startup current source is activated to charge the V<sub>CC</sub> capacitor in fast manner to V<sub>CC</sub> ON level and

thus to restart converter operation in case the input line voltage is above  $V_{BO_on}$  threshold. The controller is then checking for the absence of the fault. If the fault is still there, the supply enters another cycle of so-called hiccup. If the fault has disappeared, the power supply resumes operations. Please note that the soft-start is activated during each of the re-start sequence.

#### **Slope Compensation**

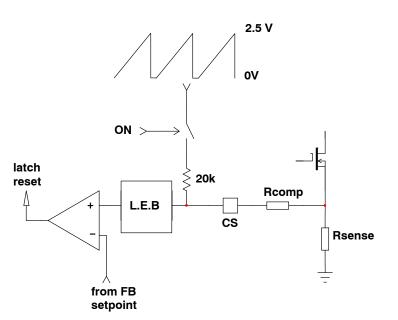

The NCP1249 includes an internal ramp compensation signal. This is the buffered oscillator clock delivered during the on time only. Its amplitude is around 2.5 V at the maximum authorized duty-ratio. Ramp compensation is a known means used to cure sub harmonic oscillations in CCM-operated current-mode converters. These oscillations take place at half the switching frequency and occur only during Continuous Conduction Mode (CCM) with a duty-ratio greater than 50%. To lower the current loop gain, one usually mixes between 50% and 100% of the inductor downslope with the current-sense signal. Figure 70 depicts how internally the ramp is generated. Please note that the ramp signal will be disconnected from the CS pin, during the off-time.

Figure 70. Inserting a Resistor in Series with the Current Sense Information Brings Slope Compensation and Stabilizes the Converter in CCM Operation

In the NCP1249 controller, the oscillator ramp exhibits a 2.5 V swing reached at a 80% duty-ratio. If the clock operates at a 65 kHz frequency, then the available oscillator slope corresponds to:

$$S_{ramp} = \frac{V_{ramp}}{D_{max} \times T_{sw}} = \frac{2.5}{0.8 \times 15 \,\mu} = 208 \text{kV/s or } 208 \text{mV/}\mu\text{s}$$

In our flyback design, let's assume that our primary inductance  $L_p$  is 770 µH, and the SMPS delivers 19 V with a  $N_p:N_s$  turns ratio of 1:0.25. The off-time primary current slope  $S_p$  is thus given by:

$$S_{p} = \frac{\left(V_{out} + V_{f}\right)\frac{N_{p}}{N_{s}}}{L_{p}} = \frac{(19 + 0.8) \times 4}{770 \,\mu} = 103 \,\text{kA/s}$$

Given a sense resistor of  $330 \text{ m}\Omega$ , the above current ramp turns into a voltage ramp of the following amplitude:

(eq. 11)  $S_{sense} = S_p R_{sense} = 103 \text{ k} \times 0.33 = 34 \text{ kV/s or } 34 \text{ mV/}\mu\text{s}$

If we select 50% of the downslope as the required amount of ramp compensation, then we shall inject a ramp whose slope is 17 mV/ $\mu$ s. Our internal compensation being of 208 mV/ $\mu$ s, the divider ratio (*divratio*) between  $R_{comp}$  and the internal 20 k $\Omega$  resistor is:

divratio =

$$\frac{17 \text{ m}}{208 \text{ m}}$$

= 0.082 (eq. 12)

The series compensation resistor value is thus:

$$(\mbox{eq. 13}) \label{eq:Rcomp} R_{comp} \,=\, R_{ramp} \,\, \mbox{divratio} \,=\, 20 \, k \, \times \, 0.082 \, \approx \, 1.64 \, k \Omega$$

A resistor of the above value will then be inserted from the sense resistor to the current sense pin. We recommend adding a small 100 pF capacitor, from the current sense pin to the controller ground for improved noise immunity. Please make sure both components are located very close to the controller.

#### Latching Off the Controller

The OPP pin not only allows a reduction of the peak current set point in relationship to the line voltage, it also offers a means to permanently latch-off the part. When the part is latched-off, the VCC pin is internally pulled down to V<sub>CC bias</sub> and the part stays in this state until the user un-plugs the converter from the mains outlet or V<sub>CC</sub> is forced below 4 V externally. The latch detection is made by observing the OPP pin by a comparator featuring a 3 V reference voltage. However, for noise reasons and in particular to avoid the leakage inductance contribution at turn off, a 1 µs blanking delay is introduced before the output of the OVP comparator is checked. Then, the OVP comparator output is validated only if its high-state duration lasts a minimum of 600 ns. Below this value, the event is ignored. Then, a counter ensures that only four successive OVP events have occurred before actually latching the part. There are several possible implementations, depending on the needed precision and the parameters you want to control.

The first and easiest solution is the additional resistive divider on top of the OPP one. This solution is simple and inexpensive but requires the insertion of a diode to prevent disturbing the OPP divider during the on-time.

Figure 71. Simple Resistive Divider Brings the OPP Pin Above 3 V in case of a V<sub>CC</sub> Voltage Runaway Above 18 V

First, calculate the OPP network with the above equations. Then, suppose we want to latch off our controller when  $V_{out}$  exceeds 25 V. On the auxiliary winding, the plateau reflects the output voltage by the turns ratio between the power and the auxiliary windings. In case of voltage runaway for our 19 V adapter, the plateau will go up to:

$$V_{aux,OVP} = 25 \times \frac{0.18}{0.25} = 18 V$$

(eq. 14)

Since our OVP comparator trips at a 3 V level, across the 1 k $\Omega$  selected OPP pull-down resistor, it implies a 3 mA current. From 3 V to go up to 18 V, we need an additional 15 V. Under 3 mA and neglecting the series diode forward drop, it requires a series resistor of:

$$R_{OVP} = \frac{V_{latch} - V_{VOP}}{V_{OVP}/R_{OPPL}} = \frac{18 - 3}{3/1 \ k} = \frac{15}{3 \ m} = 5 \ k\Omega \ \ (eq. \ 15)$$

In nominal conditions, the plateau establishes to around 14 V. Given the divide–by ratio 6, the OPP pin will swing to 14/6 = 2.3 V during normal conditions, leaving 700 mV for the noise immunity. A 100 pF capacitor can be added to improve it and avoids erratic trips in presence of external surges. Do not increase this capacitor too much otherwise the OPP signal will be affected by the integrating time constant.

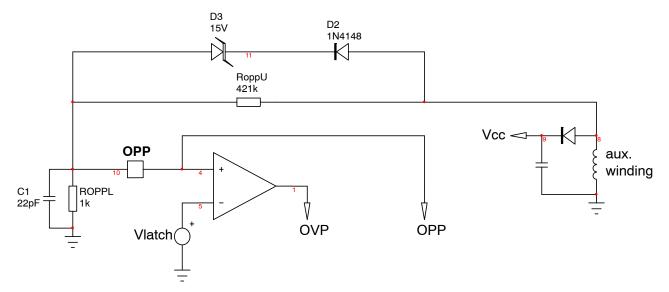

A second solution for the OVP detection alone, is to use a Zener diode wired as recommended by Figure 72.

Figure 72. Zener Diode in Series with a Diode Helps to Improve the Noise Immunity of the System

In this case, to still trip at a 18 V level, we have selected a 15 V Zener diode. In nominal conditions, the voltage on the OPP pin is almost 0 V during the off time as the Zener is fully blocked. This technique clearly improves the noise immunity of the system compared to that obtained from a resistive string as in Figure 71. Please note the reduction of the capacitor on the OPP pin to 10 pF - 22 pF. This is because of the potential spike going through the Zener parasitic capacitor and the possible auxiliary level shortly exceeding its breakdown voltage during the leakage inductance reset period (hence the internal 1 us blanking delay at turn off). This spike despite its very short time is energetic enough to charge the added capacitor  $C_1$  and given the time constant, could make it discharge slower, potentially disturbing the blanking circuit. When implementing the Zener option, it is important to carefully observe the OPP pin voltage (short probe connections!) and check that enough margin exists to that respect.

#### Internal and External Over Temperature Protection

The NCP1249 includes a temperature shutdown protection. When the temperature rises above the high threshold during stable operation - i.e. start–up sequence is

ended and V<sub>CC</sub> is between V<sub>CC\_ON</sub> and V<sub>CC\_OFF</sub> levels, the controller immediately stops driver pulses. After the temperature falls back below the lower threshold, the V<sub>CC</sub> capacitor is fully discharged by X2 discharge switch to restart the controller.

The TSD protection can be activated at some other cases (charging  $V_{CC}$  capacitor – start–up sequence and discharging X2 or  $V_{CC}$  capacitors). The TSD protection only interrupts current operating sequence – i.e. the operation sequence continue after the temperature falls back below the lower threshold. The controller is not reset by TSD activation in these cases.

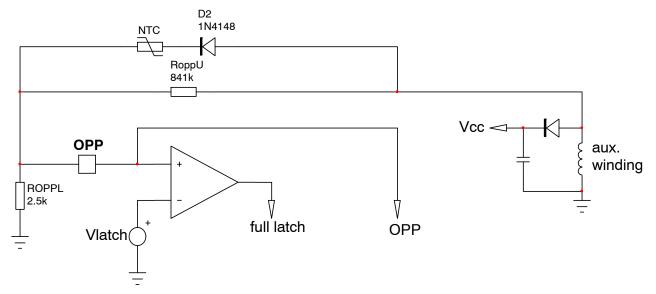

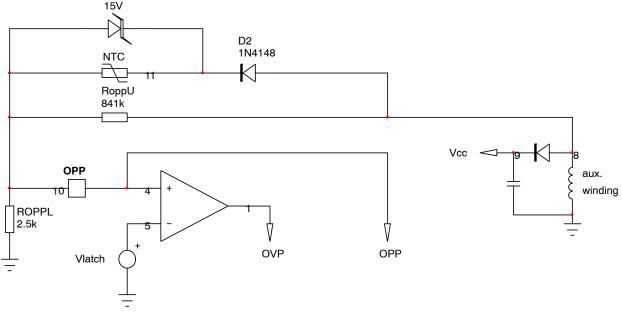

In a lot of designs, the adapter must be protected against thermal runaways, e.g. when the temperature inside the adapter box increases beyond a certain value. Figure 73 shows how to implement a simple OTP using an external NTC and a series diode. The principle remains the same: make sure the OPP network is not bothered by the additional NTC hence the presence of this diode. When the NTC resistor will diminish as the temperature increases, the voltage on the OPP pin during the off time will slowly increase and, once it crosses 3 V for 4 consecutive clock cycles, the controller will permanently latch off.

Figure 73. The Internal Circuitry Hooked to Pin 1 Can Be Used to Implement Over Temperature Protection (OTP)

Back to our 19 V adapter, we have found that the plateau voltage on the auxiliary diode was 13 V in nominal conditions. We have selected an NTC which offers a 470 k $\Omega$  resistor at 25°C and drops to 8.8 k $\Omega$  at 110°C. If our auxiliary winding plateau is 14 V and we consider a 0.6 V forward drop for the diode, then the voltage across the NTC in fault mode must be:

$$V_{\rm NTC} = 14 - 3 - 0.6 = 10.4 \, {\rm V}$$

(eq. 16)

Based on the 8.8 k $\Omega$  NTC resistor at 110°C, the current inside the device must be:

$$I_{\text{NTC}} = \frac{10.4}{8.8 \text{ k}} \approx 1.2 \text{ mA}$$

(eq. 17)

As such, the bottom resistor *R<sub>OPPL</sub>*, can easily be calculated:

$$R_{OPPL} = \frac{3}{1.2 \text{ m}} = 2.5 \text{ k}\Omega$$

(eq. 18)

Now that the pull-down OPP resistor is known, we can calculate the upper resistor value  $R_{OPPU}$  to adjust the power

D3

limit at the chosen output power level. Suppose we need a 200 mV decrease from the 0.8 V set point and the on-time swing on the auxiliary anode is -67.5 V, then we need to drop over  $R_{OPPU}$  a voltage of:

$$V_{R_{OPPU}} = 67.5 - 0.2 = 67.3 V$$

(eq. 19)

The current circulating in the pull down resistor  $R_{OPPL}$  in this condition will be:

$$I_{R_{OPPL}} = \frac{200 \text{ m}}{2.5 \text{ k}} = 80 \text{ }\mu\text{A} \tag{eq. 20}$$

The *R*<sub>OPPU</sub> value is therefore easily derived:

$$R_{OPPU} = \frac{67.3}{80 \ \mu} = 841 \ k\Omega$$

(eq. 21)

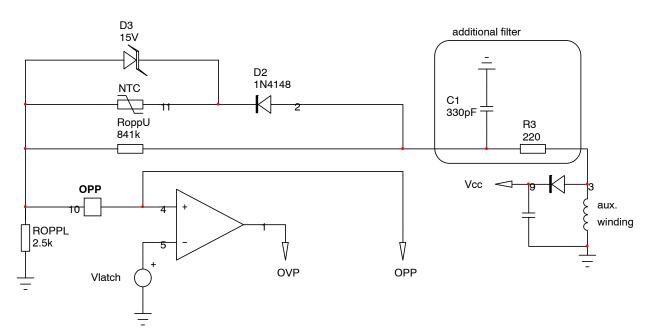

#### **Combining OVP and OTP**

The OTP and Zener–based OVP can be combined together as illustrated by Figure 74.

Figure 74. With the NTC Back in Place, the Circuit Nicely Combines OVP, OTP and OPP on the Same Pin

In nominal  $V_{CC}$ /output conditions, when the Zener is not activated, the NTC can drive the OPP pin and trigger the adapter in case of a fault. On the contrary, in nominal temperature conditions, if the loop is broken, the voltage runaway will be detected and acknowledged by the controller.

In case the OPP pin is not used for either OPP or OVP, it can simply be grounded.

#### **Filtering the Spikes**

The auxiliary winding is the seat of spikes that can couple to the OPP pin via the parasitic capacitances exhibited by the Zener diode and the series diode. To prevent an adverse triggering of the Over Voltage Protection circuitry, it is possible to install a small RC filter before the detection network. Typical values are those given in Figure 75 and must be selected to provide the adequate filtering function without degrading the stand-by power by an excessive current circulation.

Figure 75. A Small *RC* Filter Avoids the Fast Rising Spikes from Reaching the Protection Pin of the NCP1249 in Presence of Energetic Perturbations Superimposed on the Input Line

#### Latching Off with the VCC Pin

The NCP1249 hosts a dedicated comparator on the VCC pin. When the voltage on this pin exceeds 27.5 V typically for more than 20  $\mu$ s, a signal is sent to the internal latch and the controller immediately stops the driving pulses while remaining in a lockout state. The part can be reset when the user disconnects the adapter from the mains. This technique offers a simple and cheaper means to protect the converter against optocoupler failures without using the OPP pin and a Zener diode.

### **Peak Power Excursions**

There are applications where the load profile heavily changes from a nominal to a peak value. For instance, it is possible that a 30 W ac-dc adapter accepts power excursions up to 60 W in certain conditions. Inkjet printers typically fall in that category of peak power adapters. However, to avoid growing the transformer size, an existing technique consists in freezing the peak current to a maximum value  $(0.8/R_{sense})$  in our case) but authorizes frequency increase to a certain point. This point is internally fixed at 130 kHz.

Figure 76 shows the voltage evolution from almost 0 V to the open-loop level, around 4.5 V. At low power levels or in no-load operation, the feedback voltage stays in the vicinity of 400 mV and ensures skip-cycle operation. In this mode, the peak current is frozen to 31% of its maximum value and the operating frequency is 26 kHz. This freeze lasts as long as VFB stays below 1 V. Beyond 1 V, the peak current is authorized to follow V<sub>FB</sub> through a ratio of 4. When the power demand goes further up, the feedback pin crosses a level of 1.5 V where the switching frequency linearly increases from 26 kHz up to 65 kHz, a value reached when the feedback voltage exceeds 1.9 V. Beyond 1.9 V, the frequency no longer changes. As VFB still increases, the controller is in a fixed-frequency variable peak current mode control type of operation until the feedback voltage hits 3.2 V. At this point, the maximum current is limited to  $0.8 \text{ V/R}_{sense}$ . If V<sub>FB</sub> further increases, it means the converter undergoes an overload and requires more power from the source. As the peak current excursion is stopped, the only way to deliver more power is to increase the switching frequency. From 3.2 V up to 4.1 V, the frequency linearly increases from 65 kHz to 130 kHz. Beyond 4.1 V, the frequency is fixed to 130 kHz. The maximum power delivered by the converter depends whether it operates in Discontinuous Conduction Mode (DCM) or in Continuous Conduction Mode (CCM):

$$\mathsf{P}_{\max,\text{DCM}} = \frac{1}{2} \mathsf{L}_{\mathsf{p}} f_{\text{OSC}_{\max}} \mathsf{I}_{\text{peak},\max}^2 \eta \qquad (\text{eq. 22})$$

$\mathsf{P}_{\max,\text{CCM}} = \frac{1}{2} \mathsf{L}_{\mathsf{p}} f_{\text{OSC}_{\max}} \left( \mathsf{I}_{\text{peak},\max}^2 - \mathsf{I}_{\text{valley}}^2 \right) \eta \quad \text{(eq. 23)}$

Where  $I_{peak,max}$  is the maximum peak current authorized by the controller and  $I_{valley}$  the valley current reached just before a new switching cycle begins. This current is expressed by the following formula:

$$I_{\text{valley}} = I_{\text{peak}} - \frac{V_{\text{out}} + V_f}{NL_p} t_{\text{off}}$$

(eq. 24)

In DCM, the valley current is equal to 0.

Figure 77. Depending on the Feedback Level, the Timer Will Take Two Different Values: It Will Authorize a Transient Overload, but Will Reduce a Short–Circuit Duration

#### **Two Levels of Protection**

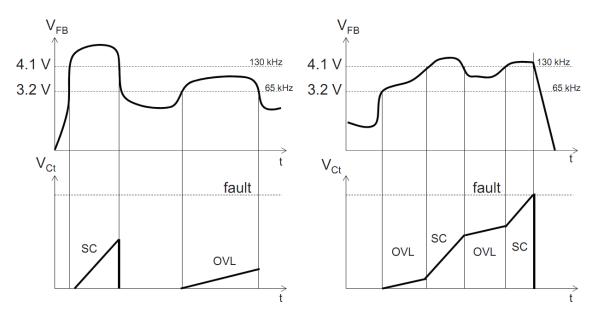

Once the feedback voltage asks for the maximum peak current, the controller knows that an overload condition has started. An internal timer is operated as soon as the maximum peak is reached. This timer duration is adjusted by a pull-down resistor to ground. Let's assume it is set to 200 ms. If the feedback voltage continues its rise, it means that the converter output voltage is going down further, close to a short-circuit situation. When the feedback voltage reaches the open-loop level (above 4.1 V typically), the original timer duration is divided by 4. For instance, at start-up, even if the overload timer is programmed to 200 ms, when the feedback voltage jumps to 4.5 V, the controller will wait 50 ms before fault detection occurs (the timer is reset upon start-up). Of course, if the feedback does not stay that long in the region of concern, the timer is reset when returning to a normal level. Figure 75 shows the timer values versus the feedback voltage.

Figure 78. Depending on the Feedback Level, the Timer will Take Two Different Values: It will Authorize a Transient Overload, but will Reduce a Short–circuit Duration

Please note that the overload situation (OVL) is detected when the maximum peak current limit is hit. It can be 3.2 V as indicated in the graph in case of no Over Power Protection (OPP). If you have programmed an OPP level of -200 mV for instance, the OVL threshold becomes $(0.8 - 0.2) \ge 4 =$ 2.4 V. When the maximum peak current situation is lifted, the converter returns to a normal situation, the timer is reset. The short circuit situation is detected by sensing a feedback voltage beyond 4.1 V. For the sake of the explanation, we have gathered two different events in Figure 79 ( $V_{Ct}$  is voltage on internal capacitor which defines fault timer duration).

Figure 79. When the Feedback Voltage Exits a Fault Region Before Time Completion, the Timer is Reset. On the Contrary, if the Timer Elapses, the Part Enters an Auto-recovery Hiccup or Latches Off Depending on the Operated Version

In the first case, the feedback is pushed to the maximum upon start-up. The timer starts with a charging slope of the short-circuit condition (SC). If the timer would be externally set to 200 ms, the timer duration in this start-up sequence would be 50 ms. As soon as regulation occurs, the timer gets reset. An overload occurs shortly after (OVL). The internal timer immediately starts to count when the 3.2 V level is crossed ( $V_{FB}$  with no OPP). As the overload lasts less than 200 ms (in this example the timer is set to 200 ms), the feedback returns to its regulation level and resets the timer.

In the second case, the overload occurs after regulation but the feedback voltage quickly jumps into the short-circuit area. At this point, the countdown is accelerated as the charging slope changed to a steeper one. The load goes back to an OVL mode and the counter slows down. Finally, back to short circuit again and the timer trips the fault circuitry after completion: all pulses are immediately stopped.

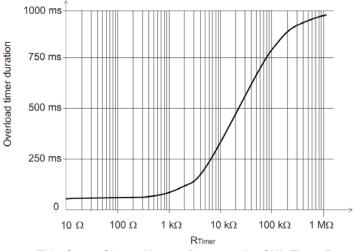

The OVL timer is adjusted by wiring a resistor ( $R_{Timer}$ ) from pin 5 to ground. The below chart shows what value to

adopt to fit your timer duration needs. Typically, a 22 k $\Omega$  pull-down resistor will set the OVL duration to 500 ms. In case of the pin short-circuit to ground (safety test), the duration will be reduced to 500/4 or 125 ms.

Figure 80. This Curve Shows How to Program the OVL Timer Duration

Please note that pin 5 includes a circuitry that manages the timer current in case of pin opening or shortening to ground. In both cases, the timer is set to known value as listed in the

parameters sheet. The given duration is that of the OVL timer.

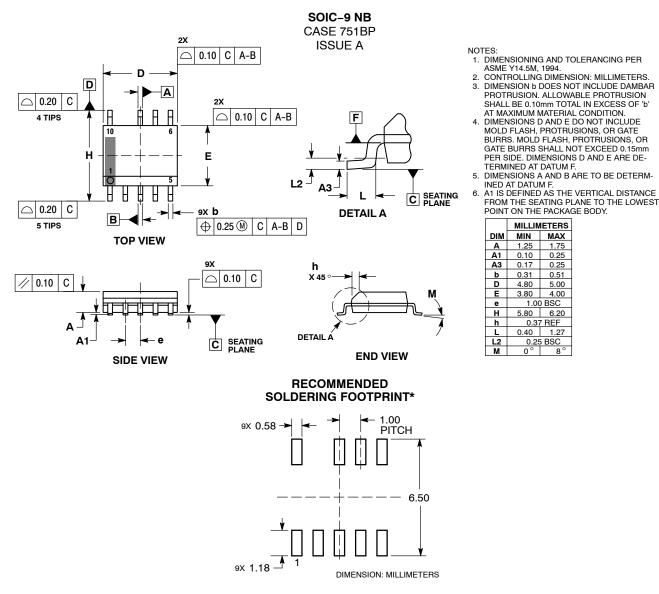

#### PACKAGE DIMENSIONS

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and 💷 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without particular purpose, for does SCILLC assume any inability arising out of the application of use of any product of clubter of the applications and a real mathing, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and a catual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the applications intended to support or sustain life, or for any other application in which the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors hamless against all claims, costs, damages, and exponses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employeer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

1.75

0.25

0.51

5.00 4.00

0.25

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative