# Adjustable Front End Overvoltage Protection Controller with Protected Vbus Output

The NCP392D is an overvoltage front end protection controller and is able to disconnect the systems from its output pin in case wrong input operating conditions are detected, up to +28 V. Thanks to this device using internal NMOS, no external device is necessary, reducing the system cost and the PCB area of the application board.

Internal OVLO threshold is available, or can be adjusted if an external resistor bridge is used.

At power up  $(\overline{EN} \text{ pin} = \text{low level})$ , the Vout turns on tstart time after internal timer elapsed.

The NCP392D features an  $\overline{ACOK}$  pin that indicates faulty condition.

#### **Features**

- Over-voltage Protection Up to + 28 V

- On–chip Low R<sub>DS(on)</sub> NMOS Transistors: Typical 34 mΩ

- Over-voltage Lockout (OVLO)

- Externally Adjustable OVLO

- Internal 15 ms Startup Delay

- Shutdown EN Input

- ACOK Status Pin

- + 100 V Surge Capability, in Compliance with IEC61000-4-5 Standard

- Compliance to IEC61000-4-2 (Level 4) Standard 8 kV (Contact) 15 kV (Air)

- ESD Ratings:

Machine Model = B (200 V) Human Body Model = 2 (2 kV)

- CSP-12 Package 1.3 x 2.0 mm, 0.4 mm Pitch

- This is a Pb-Free Device

# **Typical Applications**

- Cell Phones

- Tablets

- Camera Phones

- Digital Still Cameras

- Personal Digital Applications

# ON Semiconductor®

www.onsemi.com

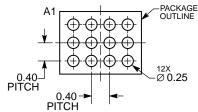

# WLCSP 12 FCC SUFFIX CASE 567JM

# MARKING DIAGRAM

392DR AYWW

392DR = Specific Device Number

A = Assembly Location

Y = Year

WW = Work Week

= Pb-Free Package

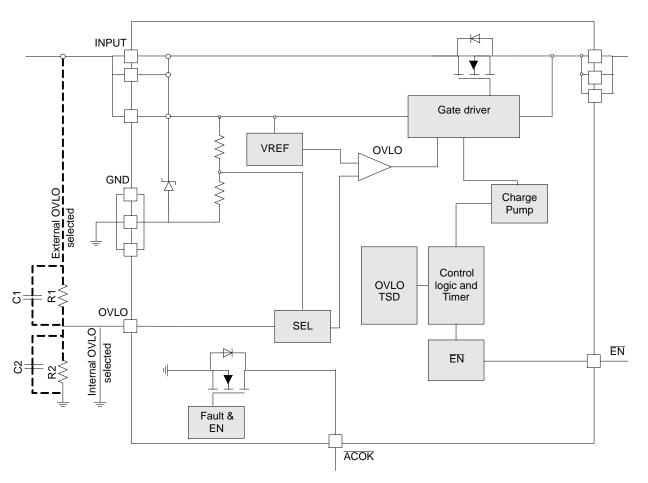

#### **PIN CONNECTION**

(Top View)

# **ORDERING INFORMATION**

See detailed ordering, marking and shipping information on page 9 of this data sheet.

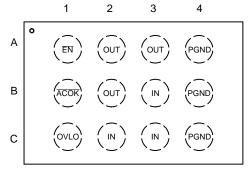

Figure 1. Typical Application Circuit

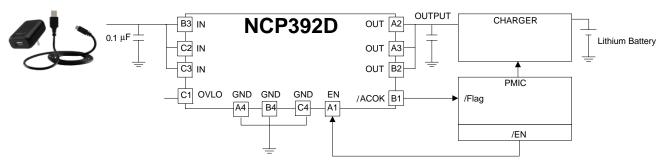

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Functional Block Diagram

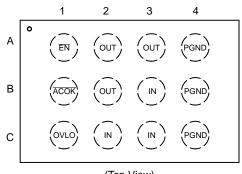

# **PIN FUNCTION DESCRIPTION**

(Top View)

Figure 3. Pinout

**Table 1. NCP392 PIN DESCRIPTION**

| Pin           | Pin<br>Name | Туре   | Description                                                                                                                                                                                                                                                                                                                                   |   |                                              |  |

|---------------|-------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------------------------------|--|

| A1            | ĒN          | I/O    | Enable pin bar. The device enters in shutdown mode when this pin is tied to a high level. In this case the output is disconnected from the input. To allow normal functionality, the $\overline{\text{EN}}$ pin is tied low with internal pull down.                                                                                          |   |                                              |  |

| A2, A3,<br>B2 | OUT         | OUTPUT | Output voltage pins. These pins follow IN pins, with debounce time, when "no fault" are detected. The outputs are disconnected from the Vin power supply when the input voltage is below UVLO, above OVLO threshold or internal thermal protection is exceeded. The three OUT pins must be hardwired together and used for power dissipation. |   |                                              |  |

| A4, B4,<br>C4 | PGND        | POWER  | Ground. The three GND pins must be hardwired together and connect to the system GND.                                                                                                                                                                                                                                                          |   |                                              |  |

| B1            | ACOK        | OUTPUT | ACOK pin: fault indication pin. Open drain. This pied in tied                                                                                                                                                                                                                                                                                 | 1 | $V_{IN} < V_{UVLO}$ or $V_{IN} \ge V_{OVLO}$ |  |

|               |             |        | low if Vin is within UVLO and OVLO range.                                                                                                                                                                                                                                                                                                     | 0 | Voltage stable                               |  |

| B3, C2,<br>C3 | IN          | POWER  | Input voltage pins. These pins are connected to the power supply. The three IN pins must be hardwired together.                                                                                                                                                                                                                               |   |                                              |  |

| C1            | OVLO        | INPUT  | External OVLO Adjustment. Connect external resistor bridge to OVLO pin to select a different OVLO threshold. Connect OVLO pin to GND if not used. In this case internal OVLO will be selected.                                                                                                                                                |   |                                              |  |

**Table 2. MAXIMUM RATINGS**

| Rating                                                                                                                 | Symbol               | Value                                      | Unit         |

|------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------|--------------|

| Minimum Voltage (IN, OVLO to GND)                                                                                      | Vmin <sub>IN</sub>   | -0.3                                       | V            |

| Minimum Voltage (All others to GND)                                                                                    | Vmin                 | -0.3                                       | V            |

| Maximum Voltage (IN to GND)                                                                                            | Vmax <sub>IN</sub>   | 29                                         | V            |

| Maximum Voltage (OVLO to GND)                                                                                          | Vmax <sub>OVLO</sub> | 14                                         | V            |

| Maximum Voltage (OUT to GND)                                                                                           | Vmax <sub>OUT</sub>  | 22                                         | V            |

| Maximum Voltage (All others to GND)                                                                                    | Vmax                 | 7                                          | V            |

| Maximum DC current                                                                                                     | Imax                 | 4.5                                        | Α            |

| Peak input current                                                                                                     | lpeak                | 8                                          | А            |

| Thermal Resistance, Junction-to-Air                                                                                    | $R_{	heta JA}$       | 70                                         | °C/W         |

| Operating Ambient Temperature Range                                                                                    | T <sub>A</sub>       | -40 to +85                                 | °C           |

| Storage Temperature Range                                                                                              | T <sub>stg</sub>     | -65 to +150                                | °C           |

| Junction Operating temperature                                                                                         | T <sub>J</sub>       | + 125                                      | °C           |

| ESD Withstand Voltage (IEC 61000–4–2) Human Body Model (HBM), model = 2 (Note 1) Machine Model (MM) model = B (Note 2) | V <sub>esd</sub>     | 15 kV air, 8 kV contact<br>2000 V<br>200 V | kV<br>V<br>V |

| Moisture Sensitivity                                                                                                   | MSL                  | Level 1                                    |              |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Human Body Model, 100 pF discharged through a 1.5 kΩ resistor following specification JESD22/A114.

2. Machine Model, 200 pF discharged through all pins following specification JESD22/A115

# **Table 3. ELECTRICAL CHARACTERISTICS**

Min / Max limits values ( $-40^{\circ}C < T_A < +85^{\circ}C$ ) and  $V_{in} = +5$  V (Unless otherwise noted). Typical values are  $T_A = +25^{\circ}C$ .

| Characteristics                            | Symbols                 | Conditions                                                                      |                          | Min  | Тур   | Max  | Unit |

|--------------------------------------------|-------------------------|---------------------------------------------------------------------------------|--------------------------|------|-------|------|------|

| Input Voltage Range                        | $V_{in}, V_{OVLO}$      |                                                                                 |                          | 2.8  |       | 28   | V    |

| Under voltage Lockout                      | UVLO                    | V <sub>in</sub> rising                                                          |                          |      |       | 2.8  | V    |

| Under voltage Lockout hysteresis           | UVLO <sub>hyst</sub>    | V <sub>in</sub> falling                                                         |                          | -    | 60    | -    | mV   |

| Internal Over voltage<br>Lockout threshold | OVLO                    | V <sub>in</sub> rising (Note 3)<br>OVLO pin tied to GND – 25°C                  | NCP392DR                 | 6.6  | 6.8   | 7.0  | V    |

| Internal Over voltage Lockout hysteresis   | OVLO <sub>hyst</sub>    | V <sub>in</sub> falling (Note 3)<br>OVLO pin tied to GND -                      | - 25°C                   | 1.5  |       | 2.5  | %    |

| External OVLO Reference                    | OVLO_EXT                |                                                                                 | NCP392DR                 | 1.18 | 1.221 | 1.26 | V    |

| External Adjustable OVLO                   |                         |                                                                                 |                          | 4    |       | 20   | V    |

| Over–Voltage Lockout<br>Hysteresis         | OVLO <sub>EXThyst</sub> | V <sub>in</sub> falling                                                         |                          |      | 2     |      | %    |

| External OVLO select threshold             | OVLO <sub>SEL</sub>     |                                                                                 |                          | 0.2  |       | 0.3  | V    |

| Vin versus Vout Resistance                 | R <sub>DSon</sub>       | V <sub>in</sub> = 5 V, <del>EN</del> = GND, -40°C <                             | : T <sub>J</sub> < 125°C |      | 34    | 50   | mΩ   |

| Supply Quiescent Current                   | I <sub>DD</sub>         | No load, $\overline{\text{EN}} = 0.4$                                           | V                        |      | 58    | 100  | μΑ   |

| Standby Current                            | I <sub>STB</sub>        | No load, EN = 1.2                                                               | V,                       |      |       | 6    | μΑ   |

| OVLO Supply current                        | I <sub>IN_OVLO</sub>    | V <sub>OVLO</sub> = 3 V, V <sub>IN</sub> = 5 V, V <sub>O</sub>                  | out = 0 V                |      | 60    | 100  | μΑ   |

| OVLO select leakage                        | I <sub>OVLO</sub>       |                                                                                 |                          |      |       | 100  | nA   |

| LOGIC                                      |                         |                                                                                 |                          |      |       |      |      |

| EN Voltage High                            | V <sub>IH</sub>         |                                                                                 |                          | 1.2  |       |      | V    |

| EN Voltage Low                             | $V_{IL}$                |                                                                                 |                          |      |       | 0.4  | V    |

| ACOK Output Low Voltage                    | V <sub>OL</sub>         | I <sub>SINK</sub> = 1 mA                                                        |                          |      | 0.4   |      | V    |

| TIMINGS                                    |                         |                                                                                 |                          |      |       |      |      |

| Start up time                              | t <sub>START</sub>      | From V <sub>in</sub> > 2.8 V to 10% V <sub>o</sub>                              | <sub>ut,</sub> EN low    |      | 15    |      | ms   |

| Enable time                                | t <sub>EN</sub>         | V <sub>in</sub> present, From EN high to low, 10% V <sub>out</sub>              |                          |      | 15    |      | ms   |

| Soft Start                                 | t <sub>RISE</sub>       | From 10% to 90% of $V_{out}$ , C load 100 $\mu$ F, Rload, 100 $\Omega$ , EN low |                          |      | 1     |      | ms   |

| ACOK Start up time                         | t <sub>START2</sub>     | From Vin Valid to ACOK tied low, EN low or high                                 |                          |      | 30    |      | ms   |

| Turn off time                              | t <sub>OFF</sub>        | Surge off time                                                                  |                          |      | 100   |      | ns   |

| Disable time                               | t <sub>DIS</sub>        | From EN >1.2 V to 90% V <sub>out.</sub> No load                                 |                          |      | 20    |      | μS   |

| OVLO Turn off time                         | t <sub>OVLO</sub>       | V <sub>in</sub> rising 2 V/μs                                                   |                          |      | 1.5   |      | μS   |

| TSD                                        |                         |                                                                                 |                          |      |       |      |      |

| Thermal shutdown                           | al shutdown TSD         |                                                                                 |                          | 140  |       | °C   |      |

| Thermal shutdown rearming                  | TSD rearm               |                                                                                 |                          |      | 115   |      | °C   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

3. Please contact your ON Semiconductor representative for additional OVLO threshold.

Electrical parameters are guaranteed by correlation across the full range of temperature.

#### Operation

The NCP392D provides over-voltage protection for positive voltage surge, up to +28 V. An additional clamp, between IN and GND, protects the part against surge test, in compliance with IEC 61000-4-5 standard.

A ACOK open drain fault indicator is provided. This signal indicates whether input voltage is within the valid range.

# Under-voltage Lockout (UVLO)

To ensure proper operation under any conditions, the device has a built—in under—voltage lock out (UVLO) circuit. This circuit has a built—in hysteresis to provide noise immunity to transient conditions.

# Over-voltage Lockout (OVLO)

To protect connected systems on Vout pin from over-voltage, the device has a built-in over-voltage lock out (OVLO) circuit. During over-voltage condition, the output remains disabled until the input voltage is above OVLO – hysteresis.

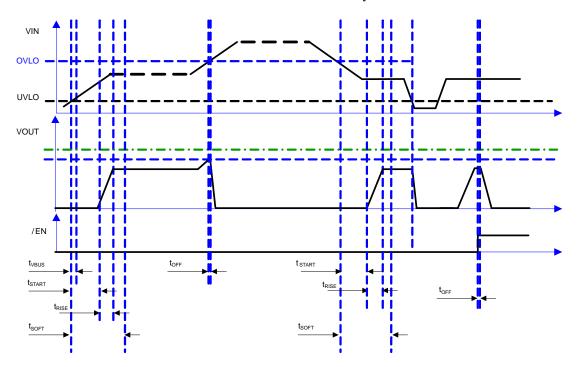

Figure 4. UVLO, OVLO and EN Functionality

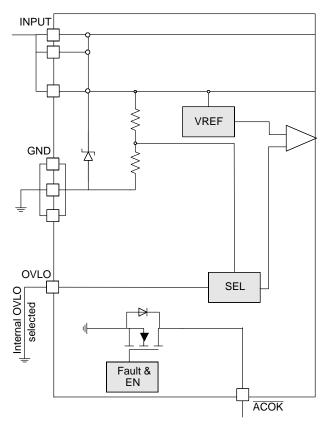

Figure 5. External Connection to GND of OVLO

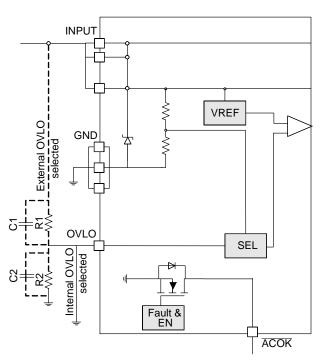

If OVLO pin is not grounded, and by adding external bridge resistor on OVLO pin, between IN and GND, overvoltage protection can be adjusted as following:

Figure 6. External Connection to Resistor Bridge of OVLO

$$\text{NEW\_OVLO}_{\text{TH}} = \frac{\text{OVLO}_{\text{EXT}} \times \left(\text{R}_1 + \text{R}_2\right)}{\text{R}_2} \text{(eq. 1)}$$

With:  $OVLO_{EXT} = 1.221 \text{ V}$  Typical (OVLO External Reference)

Example:

NEW\_OVLO<sub>TH</sub> target 12 V.

(eq. 2)

R1 = R2 ×

$$\left(\frac{\text{OVLO}}{1.221} - 1\right)$$

= R2 ×  $\left(\frac{12}{1.221} - 1\right)$  = 8.828 × R2

Taking into account external input bridge doesn't have excessive current consumption, and 1% is recommended:

$R_2$  arbitrarily fixed at 1.05 M $\Omega$ .

$R_1 = 9.269~M\Omega$  (9.31  $M\Omega$  standard value)

Obtained typical OVLO = 12.04 V

$C_1$  and  $C_2$  should be selected in such a way that the time constant  $R_1C_1=R_2C_2$ .

# **EN** Input

To enable normal operation, the  $\overline{EN}$  pin has to be at low level. Internal pull down is embedded in the part.

A high level on the pin, disconnects OUT pin from IN pin.

**Table 4. CONTROL LOGIC MODES**

| OVP | State | OVLO EXT                       |      |  |

|-----|-------|--------------------------------|------|--|

| _   | 392D  | Low                            | High |  |

| ĒΝ  | Low   | ON<br>T <sub>start</sub> 15 ms | OFF  |  |

|     | High  | OFF                            | OFF  |  |

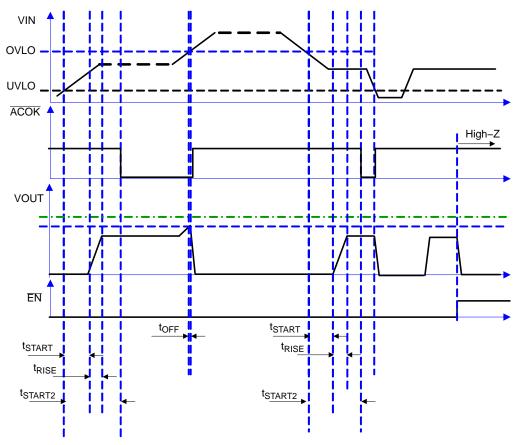

Figure 7. EN and ACOK Associated Timers

# **ACOK** Pin

The NCP392D version integrates a  $\overline{\text{ACOK}}$  status indicator. This is an open drain pin tied low when no fault is present (no TSd, no under voltage, no over voltage).

When disabled, the  $\overline{ACOK}$  feature is disabled too and the output pin is in high impedance mode.

#### **Thermal Shutdown Protection**

In case of internal overheating, the integrated thermal shutdown (TSD) protection allows to open the internal MOSFET in order to instantaneously decrease the device temperature.

Embedded hysteresis allows to reengage the MOSFET when the junction temperature decreases.

If the fault event is still present, the temperature increases again and engages the thermal shutdown one more time until fault event disappeared.

# **PCB Recommendations**

To limit internal power dissipation, PCB routing must be carefully done to improve current capability.

The NCP392D is declined in a CSP package. So power dissipation can be decreased on each pin connection but main thermal area must be as large as possible around IN and OUT pins. Taking into account and respectively, four IN and OUT pins must be hardwired together on the PCB.

Maximum power dissipation can be calculated with the following formula:

$$T_J - T_A = R_{\theta JA} \times P_d$$

(eq. 3)

T<sub>J</sub>: junction temperature

T<sub>A</sub>: ambient temperature

$R_{\theta JA}\!\!:$  thermal resistance of the junction to air through the case and board.

$P_d$ : power dissipation =  $R_{DS(on)} \times I^2$

#### **ESD Tests**

The NCP392D fully supports the IEC61000–4–2, level 4 (Input pin, 1  $\mu$ F mounted on board).

That means, in Air condition,  $V_{in}$  has a  $\pm 15~kV$  ESD protected input. In Contact condition,  $V_{in}$  has  $\pm 8~kV$  ESD protected input.

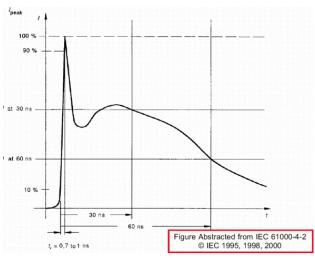

Please refer to Figure 8 to see the IEC 61000-4-2 electrostatic discharge waveform.

Figure 8.  $I_{peak} = f(t) / IEC61000-4-2$

# **USB OTG Support**

When used in an application that has to supply voltage to an external accessory (i.e. USB OTG), the part is able to supply 1.8 A to the accessory. If  $V_{\rm IN}=0$  V when +5.0 V OTG is applied to the OUT pin, current will flow through the MOSFET body diode and, as soon as the output voltage will be higher than the  $V_{\rm UVLO}$  voltage (2.8 V) plus Body diode forward voltage, the part will turn fully ON and current will be supplied to the accessory with minimum drop.

In that case, the ACOK pin will keep High–Z state.

#### **ORDERING INFORMATION**

|      | Device     | Marking | Option     | Package            | Shipping <sup>†</sup> |

|------|------------|---------|------------|--------------------|-----------------------|

| NCP3 | 92DRFCCT1G | 392DR   | OVLO 6.8 V | WLCSP<br>(Pb-Free) | 3000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

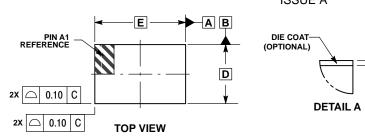

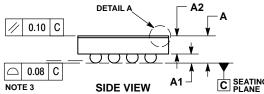

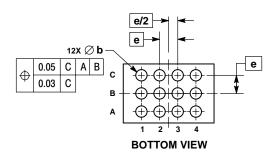

#### PACKAGE DIMENSIONS

# WLCSP12, 1.3x2.0

CASE 567JM **ISSUE A**

#### NOTES:

**A3**

- DIMENSIONING AND TOLERANCING PER

- ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

COPLANARITY APPLIES TO SPHERICAL

CROWNS OF SOLDER BALLS.

| ONOTHING OF COEDETE |             |      |  |  |

|---------------------|-------------|------|--|--|

|                     | MILLIMETERS |      |  |  |

| DIM                 | MIN         | MAX  |  |  |

| Α                   |             | 0.60 |  |  |

| A1                  | 0.17 0.23   |      |  |  |

| A2                  | 0.36 REF    |      |  |  |

| A3                  | 0.04 REF    |      |  |  |

| b                   | 0.24        | 0.30 |  |  |

| D                   | 1.26        | 1.31 |  |  |

| E                   | 2.01        | 2.04 |  |  |

| е                   | 0.40 BSC    |      |  |  |

#### RECOMMENDED **SOLDERING FOOTPRINT\***

DIMENSIONS: MILLIMETERS

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and the (III) are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

# **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative