# Dual MOSFET Gate Driver, High Performance

# NCP81085

#### Introduction

The NCP81085 is a high performance dual MOSFET gate driver optimized to drive the gates of both high and low side power MOSFETs in a synchronous buck converter. The NCP81085 uses an on-chip bootstrap diode to eliminate the external discrete diode. A high floating top driver design can accommodate HB voltage as high as 180 V. The low-side and high-side are independently controlled and match to 4 ns between the turn-on and turn-off of each other. Independent Under-Voltage lockout is provided for the high side and low side driver forcing the output low when the drive voltage is below a specific threshold.

#### Features

- Drives Two N-Channel MOSFETs in High-Side and Low-Side Configuration

- Floating Top Driver Accommodates Boost Voltage up to 180 V

- Switching Frequency up to 1 MHz

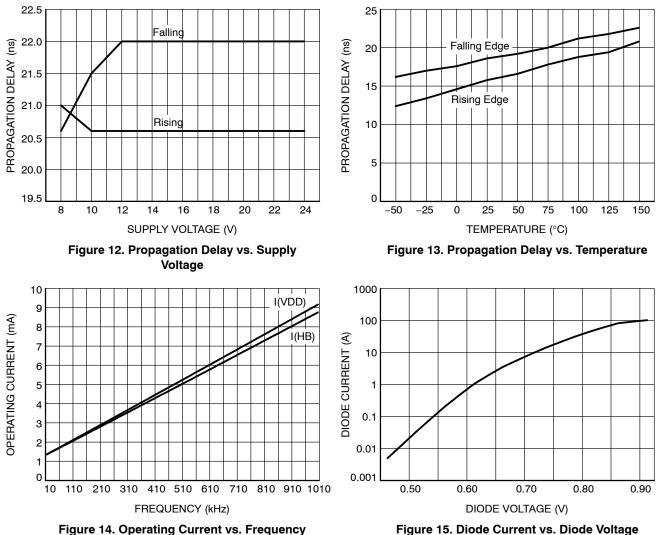

- 20 ns Propagation Delay Times

- 4 A Sink, 4 A Source Output Currents

- 8 ns Rise / 7 ns Fall Times with 1000 pF Load

- UVLO Protection

- Specified from -40°C to 140°C

- Offered in WDFN9 (MT) Package

- This Device is Pb–Free, Halogen Free/BFR Free and is RoHS Compliant

# Applications

- Telecom and Datacom

- Isolated Non-Isolated Power Supply Architectures

- Class D Audio Amplifiers

- Two Switch and Active Clamp Forward Converters

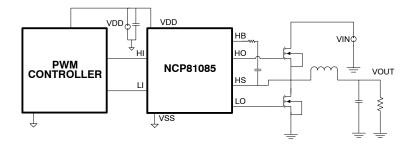

#### **Simplified Application Diagram**

# **ON Semiconductor®**

www.onsemi.com

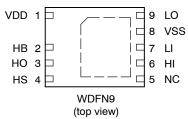

WDFN9 CASE 511EF

#### MARKING DIAGRAMS

NCP81085 = Specific Device Code

- = Assembly Location

- = Wafer Lot

- Y = Year W = Work

А

L

- = Work Week

- = Pb-Free Package

(Note: Microdot may be in either location)

# **ORDERING INFORMATION**

| Device        | Package            | Shipping <sup>†</sup> |

|---------------|--------------------|-----------------------|

| NCP81085MTTXG | WDFN9<br>(Pb-Free) | 4000 /<br>Tape & Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

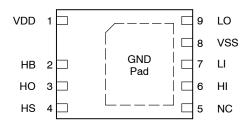

#### Table 1. PIN DESCRIPTION

| Pin No.<br>DFN9 | Symbol | Description                              |

|-----------------|--------|------------------------------------------|

| 1               | VDD    | Positive Supply to the Lower Gate Driver |

| 2               | HB     | High Side Bootstrap Supply               |

| 3               | НО     | High Side Output                         |

| 4               | HS     | High-Side Source                         |

| 5               | NC     | No Connect                               |

| 6               | HI     | High-Side Input                          |

| 7               | LI     | Low-Side Input                           |

| 8               | VSS    | Negative Supply Return                   |

| 9               | LO     | Low Side Output                          |

#### **Table 2. MAXIMUM RATINGS**

|                 | Parameter                          | Value                                                                    | Units |

|-----------------|------------------------------------|--------------------------------------------------------------------------|-------|

|                 | VDD                                | -0.3 to 24                                                               | V     |

|                 | V <sub>HB</sub>                    | -0.3 to 200                                                              | V     |

| V <sub>HO</sub> | DC                                 | $V_{HS}{-}0.3$ to $V_{HB}$ + 0.3                                         | V     |

|                 | Repetitive Pulse < 100 ns          | $V_{\rm HS}$ – 2 to $V_{\rm HB}$ + 0.3, (V_{\rm HB} – $V_{\rm HS}$ < 24) |       |

| V <sub>HS</sub> | DC                                 | -20 to 200 - VDD                                                         | V     |

| V <sub>LO</sub> | DC                                 | -0.3 to VDD + 0.3                                                        | V     |

|                 | Repetitive pulse < 100 ns          | -2 to VDD + 0.3                                                          |       |

|                 | V <sub>HI</sub> , V <sub>LI</sub>  | -10 to 24                                                                | V     |

|                 | V <sub>HB – HS</sub>               | -0.3 to 24                                                               | V     |

| Operating J     | Junction Temperature Range, TJ     | -40 to 170                                                               | °C    |

| Sto             | rage Temperature, T <sub>STG</sub> | -65 to 150                                                               | °C    |

| Lead Ter        | nperature (Soldering, 10 sec)      | +300                                                                     | °C    |

|                 | НВМ                                | 1000                                                                     | V     |

| -               | CDM                                | 2000                                                                     | V     |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. 1.  $V_{HB} - V_{HS}$  should be in the range of -0.3 V to +20 V.

#### **Table 3. RECOMMENDED OPERATING CONDITIONS**

|                 | Parameter                            | Min                                         | Nom | Max                          | Units  |

|-----------------|--------------------------------------|---------------------------------------------|-----|------------------------------|--------|

| V <sub>DD</sub> | Supply Voltage Range                 | 8.5                                         | 12  | 20                           | V      |

| V <sub>HS</sub> | Voltage on HS (DC)                   | -10                                         |     | 180 – VDD                    |        |

| $V_{HB}$        | Voltage on HB                        | V <sub>HS</sub> + 8,<br>V <sub>DD</sub> – 1 |     | V <sub>HS</sub> + 20,<br>180 |        |

|                 | Voltage Slew Rate on HS              |                                             |     | 50                           | V / ns |

| TJ              | Operating Junction Temperature Range | -40                                         |     | +140                         | °C     |

| V <sub>HO</sub> |                                      | V <sub>HS</sub> – 0.3                       |     | V <sub>HB</sub> + 0.3        | V      |

| V <sub>LO</sub> |                                      | -0.3                                        |     | V <sub>DD</sub> + 0.3        | V      |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

# **ABSOLUTE MAXIMUM RATINGS**

| Thermal Characteristic                                                    | Value | Unit |

|---------------------------------------------------------------------------|-------|------|

| $\theta_{JA}$ Junction to Ambient thermal resistance                      | 68.1  | °C/W |

| $\theta_{\text{JC(top)}}$ Junction to case (Top) thermal resistance       | 30    |      |

| $\theta_{\text{JC(Bottom)}}$ Junction to case (Bottom) thermal resistance | 2.3   |      |

| $\psi_{\text{JT}}$ Junction to top characterization parameter             | 0.7   |      |

| $\psi_{JB}$ Junction to board characterization parameter                  | 2.2   |      |

| Moisture Sensitivity Level (MSL)                                          |       | 1    |

2. This data was taken using the JEDEC proposed High-K Test PCB.

**Table 5. ELECTRICAL CHARACTERISTICS** Unless otherwise stated:  $T_A = T_1 = -40^{\circ}$ C to 140°C; VDD = VHB = 12 V. VHS = VSS = 0 V. No load on LO or HO

|                                     | Parameter                               | Test Condition                            | Min | Тур  | Max | Units |

|-------------------------------------|-----------------------------------------|-------------------------------------------|-----|------|-----|-------|

| SUPPLY CI                           | JRRENTS                                 |                                           | •   |      | •   |       |

| I <sub>DD</sub>                     | VDD quiescent current                   | $V_{LI} = V_{HI} = 0$                     |     | 0.85 | 1.8 | mA    |

| I <sub>DDO</sub>                    | VDD operating current                   | f = 500 kHz, C <sub>LOAD</sub> = 0        |     | 7.3  | 15  |       |

|                                     |                                         | f = 300 kHz, C <sub>LOAD</sub> = 0        |     | 4.9  | 11  |       |

| I <sub>HB</sub>                     | Boot voltage quiescent current          | $V_{LI} = V_{HI} = 0 V$                   |     | 0.92 | 1.8 |       |

| I <sub>HBO</sub>                    | Boot voltage operating current          | f = 500 kHz, C <sub>LOAD</sub> = 0        |     | 6.55 | 12  |       |

|                                     |                                         | f = 300 kHz, C <sub>LOAD</sub> = 0        |     | 4.5  | 7.0 |       |

| I <sub>HBS</sub>                    | HB to V <sub>SS</sub> quiescent current | V <sub>HS</sub> = V <sub>HB</sub> = 110 V |     | 5.0  | 25  | μA    |

| I <sub>HBSO</sub>                   | HB to V <sub>SS</sub> operating current | f = 500 kHz, C <sub>LOAD</sub> = 0        |     | 0.1  |     | mA    |

| INPUT                               |                                         |                                           | ·   | ·    |     |       |

| V <sub>HIH</sub> , V <sub>LIH</sub> | Input rising threshold                  |                                           | 2.7 |      |     | V     |

| V <sub>HIL</sub> , V <sub>LIL</sub> | Input falling threshold                 |                                           |     |      | 0.8 |       |

| R <sub>IN</sub>                     | Input Pulldown Resistance               |                                           | 100 | 170  | 350 | kΩ    |

| UNDERVO                             | LTAGE PROTECTION (UVLO)                 |                                           |     |      |     |       |

|                                     | VDD rising threshold                    |                                           | 6.2 | 7.1  | 8.0 | V     |

|                                     | VDD threshold hysteresis                | ]                                         |     | 0.58 |     | 1     |

|                                     | VHB rising threshold                    | 1                                         | 5.5 | 6.5  | 7.5 | 1     |

|                                     | VHB threshold hysteresis                | 1                                         |     | 0.5  |     |       |

#### **BOOTSTRAP DIODE**

| V <sub>F</sub>  | Low-current forward voltage              | I <sub>VDD</sub> – HB = 100 μA    | 0.59 | 0.95 | V |

|-----------------|------------------------------------------|-----------------------------------|------|------|---|

| V <sub>FI</sub> | High-current forward voltage             | I <sub>VDD</sub> – HB = 100 mA    | 0.85 | 1.1  |   |

| R <sub>D</sub>  | Dynamic resistance, $\Delta VF/\Delta I$ | $I_{VDD}$ – HB = 100 mA and 80 mA | 0.94 | 2.0  | Ω |

#### LO GATE DRIVER

| V <sub>LOL</sub> | Low level output voltage  | I <sub>LO</sub> = 100 mA                            | 0.1  | 0.40 | V |

|------------------|---------------------------|-----------------------------------------------------|------|------|---|

| V <sub>LOH</sub> | High level output voltage | $I_{LO}$ = -100 mA, $V_{LOH}$ = $V_{DD}$ - $V_{LO}$ | 0.15 | 0.40 |   |

|                  | Peak pull-up current      | V <sub>LO</sub> = 0 V                               | 4    |      | А |

|                  | Peak pull-down current    | V <sub>LO</sub> = 12 V                              | 4    |      |   |

#### **Table 5. ELECTRICAL CHARACTERISTICS**

Unless otherwise stated:  $T_A = T_J = -40^{\circ}C$  to  $140^{\circ}C$ ; VDD = VHB = 12 V, VHS = VSS = 0 V, No load on LO or HO

|                  | Parameter                 | Test Condition                                    | Min | Тур  | Max  | Units |

|------------------|---------------------------|---------------------------------------------------|-----|------|------|-------|

| HO GATE          | DRIVER                    |                                                   |     |      |      |       |

| V <sub>HOL</sub> | Low level output voltage  | I <sub>HO</sub> = 100 mA                          |     | 0.1  | 0.40 | V     |

| V <sub>HOH</sub> | High level output voltage | $I_{HO}$ = -100 mA, $V_{HOH}$ = $V_{HB} - V_{HO}$ |     | 0.15 | 0.40 |       |

|                  | Peak pull-up current      | V <sub>LO</sub> = 0 V                             |     | 4    |      | А     |

|                  | Peak pull-down current    | V <sub>LO</sub> = 12 V                            |     | 4    |      |       |

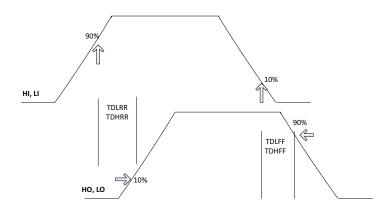

#### **PROPAGATION DELAYS**

| t <sub>DLFF</sub> | $\rm V_{LI}$ falling to $\rm V_{LO}$ falling | $C_{LOAD} = 0 (-40 \text{ to } 125^{\circ}\text{C})$ | 20 | 45 | ns |

|-------------------|----------------------------------------------|------------------------------------------------------|----|----|----|

|                   |                                              | C <sub>LOAD</sub> = 0 (-40 to 140°C)                 | 20 | 50 |    |

| t <sub>DHFF</sub> | $V_{HI}$ falling to $V_{HO}$ falling         | C <sub>LOAD</sub> = 0 (-40 to 125°C)                 | 20 | 45 |    |

|                   |                                              | C <sub>LOAD</sub> = 0 (-40 to 140°C)                 | 20 | 50 |    |

| t <sub>DLRR</sub> | $V_{LI}$ rising to $V_{LO}$ rising           | $C_{LOAD} = 0 \ (-40 \ to \ 125^{\circ}C)$           | 20 | 45 |    |

|                   |                                              | C <sub>LOAD</sub> = 0 (-40 to 140°C)                 | 20 | 50 |    |

| t <sub>DHRR</sub> | $V_{HI}$ rising to $V_{HO}$ rising           | C <sub>LOAD</sub> = 0 (-40 to 125°C)                 | 20 | 45 |    |

|                   |                                              | C <sub>LOAD</sub> = 0 (-40 to 140°C)                 | 20 | 50 |    |

#### **DELAY MATCHING**

| tMON  | LI ON, HI OFF |  | 3.5 | 14 | ns |

|-------|---------------|--|-----|----|----|

| tMOFF | LI OFF, HI ON |  | 3.5 | 14 |    |

#### OUTPUT RISE AND FALL TIME

| t <sub>R</sub> | LO, HO              | C <sub>LOAD</sub> = 1000 pF | 8    |      | ns |

|----------------|---------------------|-----------------------------|------|------|----|

| t <sub>F</sub> | LO, HO              | C <sub>LOAD</sub> = 1000 pF | 7    |      |    |

| t <sub>R</sub> | LO, HO (3 V to 9 V) | $C_{LOAD} = 0.1 \ \mu F$    | 0.2  | 0.55 | μs |

| t <sub>F</sub> | LO, HO (3 V to 9 V) | $C_{LOAD} = 0.1 \ \mu F$    | 0.25 | 0.45 |    |

#### MISCELLANEOUS

| t <sub>1</sub> | Minimum input pulse width that changes the output |                                                                        | 30 | ns |

|----------------|---------------------------------------------------|------------------------------------------------------------------------|----|----|

| t <sub>2</sub> | Bootstrap diode turn-off time                     | I <sub>F</sub> = 100 mA, I <sub>REV</sub> = -100 mA<br>(Notes 3 and 4) | 50 |    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

3. Typical values for  $T_A = 25^{\circ}C$

4. IF: Forward current applied to bootstrap diode, IREV: Reverse current applied to bootstrap diode.

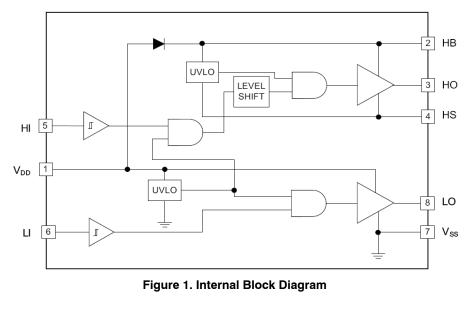

# Internal Block Diagram

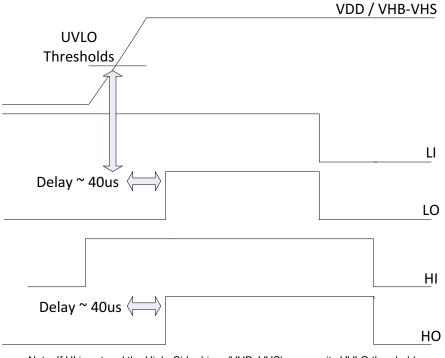

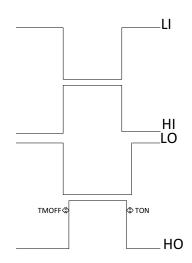

# **Timing Diagrams**

Note: If HI is set and the High–Side driver (VHB–VHS) crosses its UVLO threshold 100ns after the VDD UVLO then a rising edge on HI is required to pull HO High.

Figure 2. UVLO

Figure 4. Propagation Delays

| LOGIC TABLE |    |    |    |  |  |

|-------------|----|----|----|--|--|

| н           | LI | НО | LO |  |  |

| L           | L  | L  | L  |  |  |

| L           | Н  | L  | Н  |  |  |

| Н           | L  | Н  | L  |  |  |

| Н           | Н  | Н  | Н  |  |  |

# **PINOUT DIAGRAMS**

Note: The  $\mathsf{V}_{SS}$  Pin and the GND Pad are internally connected.

Figure 5. NCP81085 Top View

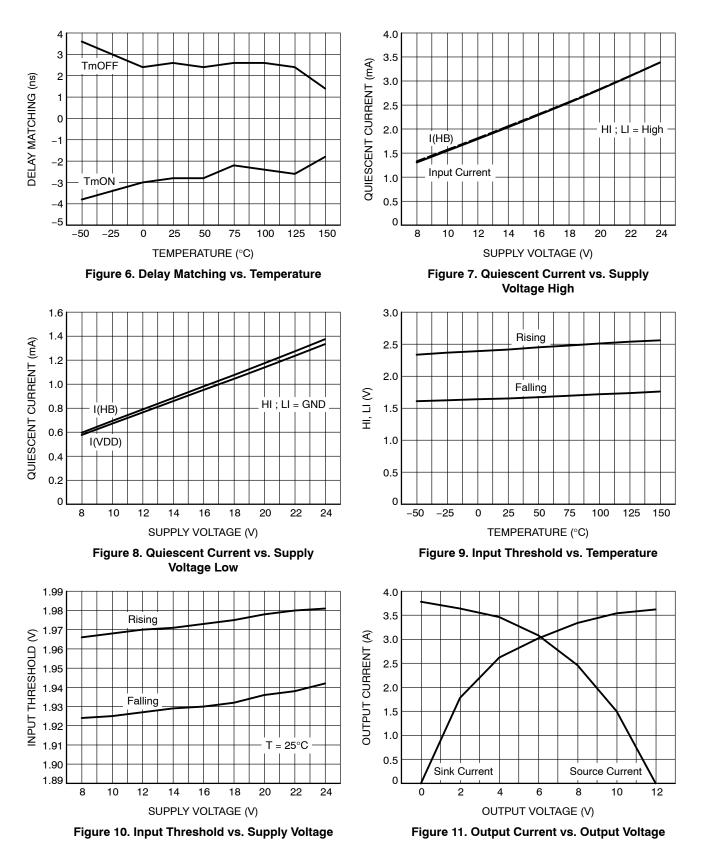

# **TYPICAL CHARACTERISTICS**

# **TYPICAL CHARACTERISTICS**

#### **APPLICATION INFORMATION**

The NCP81085 is a high performance dual MOSFET gate driver optimized for driving the gates of both high side and low side power MOSFETs in a synchronous buck converter topology. A high and a Low input signals are all that is required to properly drive the high side and low side MOSFETs.

#### Low-Side Driver

The low side driver is designed to drive low  $RDS_{ON}$  N-channel MOSFETs. The typical output resistances for the driver are 1.5 ohms for sourcing and 1 ohm for sinking gate current. Due to the parasitic inductances of the packages, drive circuits and the nonlinearity of the MOSFETs output resistances the recorded peak current is close to 4 A.

The low output resistances allow the driver to have 8 ns rise and 7 ns fall times into a 1 nF load. When the driver is enabled, the driver's output is in phase with LI. When the NCP81085 is disabled, the low side gate is held low.

#### **High-Side Driver**

The high side driver is designed to drive a floating low  $RDS_{ON}$  N-channel MOSFET. The output resistances for the driver are 1.5 ohms for sourcing and 1 ohm for sinking gate current. The bias voltage for the high side driver is realized by an external bootstrap supply circuit which is connected between the HB and HS Pins.

The bootstrap circuit is comprised only of the bootstrap capacitor since the bootstrap diode is internal. When the NCP81085 is starting up, the HS Pin is at ground, the bootstrap capacitor will charge up to VDD through the internal diode. When the HI goes high, the high side driver will begin to turn the high side MOSFET On by pulling charge out of the bootstrap capacitor. As the external MOSFET turns ON, the HS Pin will rise up to VIN, forcing the HB Pin to VIN +  $V_{BstCap}$  which is enough gate to source voltage to hold the switch On. To complete the cycle, the MOSFET is switched OFF by pulling the gate down to the voltage at the HS Pin. When the low side MOSFET turns On, the HS Pin is pulled to ground. This allows the bootstrap capacitor to charge up to VDD again. The high-side driver's output is in phase with the HI input. When the driver is disabled, the high side gate is held low.

Unlike a Buck regulator at power–up, Boost regulators typically require starting when the HS pin is at the  $V_{IN}$  level, instead of GND or the prevailing  $V_{OUT}$ . Care should be

taken by the system designer to pre-charge the bootstrap capacitor ( $C_{BST}$ ) to ensure sufficient voltage levels for proper operation. If the capacitor is discharged, the high-side power MOSFET relies on the driver's internal 20 K $\Omega$  pull down resistor to prevent charge from building up across its V<sub>GS</sub> during the initial low side FET turn on events. High dV/dt on HS, when turning on the low-Side MOSFET, creates a capacitive divider across the high side FET gate, possibly resulting in cross-conduction. With proper biasing across C<sub>BST</sub> (V<sub>HB</sub>-V<sub>HS</sub>), the internal low-impedance pull down at HO ensures the high-side FET remains off.

The external BST resistor, which connects HB pin and BST cap, should avoid excessive resistance. NCP81085 has high–side UVLO protection based on the voltage across HB and HS pins. High resistance on HB pin may falsely trigger UVLO protection at the moment when high–side MOSFET is turning on.

#### UVLO (Under Voltage Lockout)

The bias supplies of the high-side and low-side drivers have UVLO protection. The VDD UVLO disables both drivers when the VDD voltage crosses the specified threshold. The typical rising threshold is 7.1 V with 0.58 V hysteresis. The VHB UVLO disables only the high-side driver when the VHB to VHS is below the specified threshold. The typical VHB UVLO rising threshold is 6.5 V with 0.5 V hysteresis. The designer must take into account a 40 µs delay before the output channels can react to a logic input. (Refer to the UVLO Timing Diagram).

#### **Input Stages**

The input stage of the NCP81085 is TTL compatible. The logic rising threshold level is 2.4 V and the logic falling threshold is 1.6 V.

#### Layout Guidelines

Gate drivers experience high di/dt during the switching transitions. So, the inductance at the gate drive traces must be minimized to avoid excessive ringing on the switch node. Gate drive traces should be kept as short and wide (> 20 mil) as practical. The input capacitor must be placed as close as possible to the IC. Connect the VSS pin of the NCP81085 as close as possible to the source of the lower MOSFET. The use of vias is highly desirable to maximize thermal conduction away from driver.

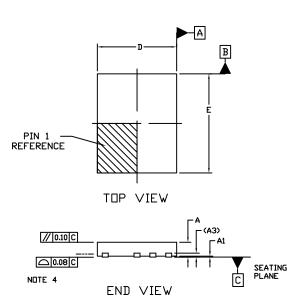

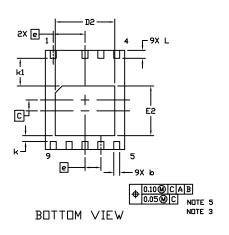

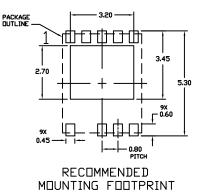

#### PACKAGE DIMENSIONS

WDFN9 4x5, 0.8P CASE 511EF

ISSUE 0

NDTES

- 1. DIMENSIONING AND TOLERANCING PER

- ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- 3. DIMENSION & APPLIES TO THE PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30 MM FROM THE TERMINAL TIP.

- 4. COPLANARITY APPLIES TO ALL OF THE TERMINALS AND THE EXPOSED PAD.

- 5. POSITIONAL TOLERANCE APPLIES TO ALL OF THE TERMINALS AND THE EXPOSED PAD.

|     | MILLIMETERS |      |      |  |

|-----|-------------|------|------|--|

| DIM | MIN.        | NDM  | MAX. |  |

| Α   | 0.70        | 0.75 | 0.80 |  |

| A1  | 0.00        |      | 0.05 |  |

| A3  | 0.20 REF    |      |      |  |

| Ø   | 0.25        | 0.30 | 0.35 |  |

| С   | 0.55 BSC    |      |      |  |

| D   | 3.90        | 4.00 | 4.10 |  |

| D2  | 2.90        | 3.00 | 3.10 |  |

| Е   | 4.90        | 5.00 | 5.10 |  |

| E2  | 2.40        | 2.50 | 2.60 |  |

| e   | 0.80 BSC    |      |      |  |

| к   | 0.30 REF    |      |      |  |

| k1  | 1.40 REF    |      |      |  |

| L   | 0.30        | 0.40 | 0.50 |  |

For additional information on our Pb-Free strategy and soldering details, please download the DN Semiconductor Soldering and Mounting Techniques Reference Manual, SDLDERRM/D.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor hardus for multionized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors ha

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

ON Semiconductor Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada Phone: 011 421 33 790 2910 **Europe, Middle East and Africa Technical Support:** Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative