# Wireless Power Transmitter ASIC

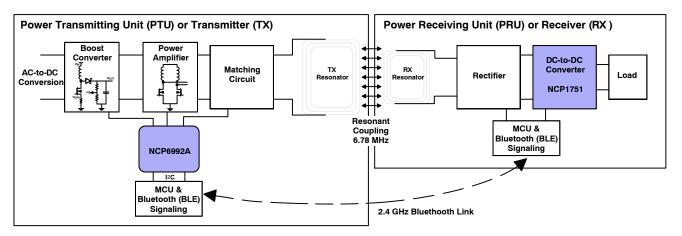

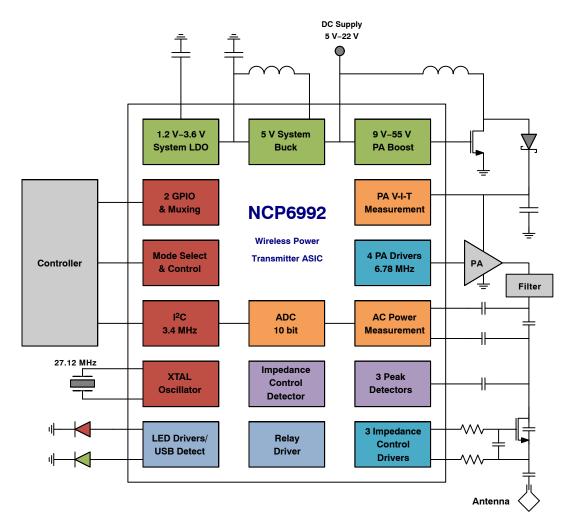

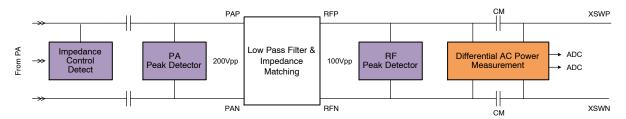

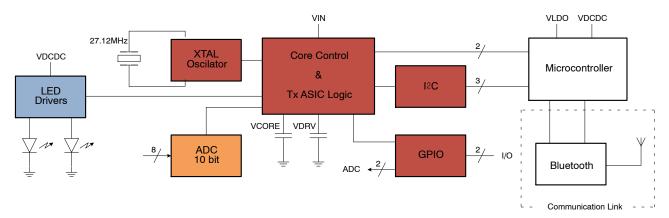

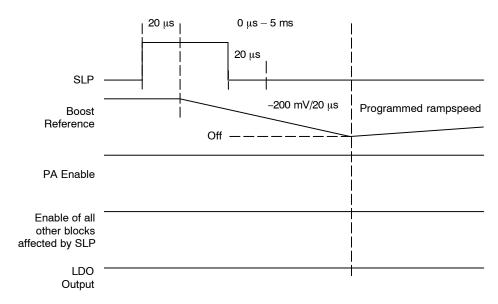

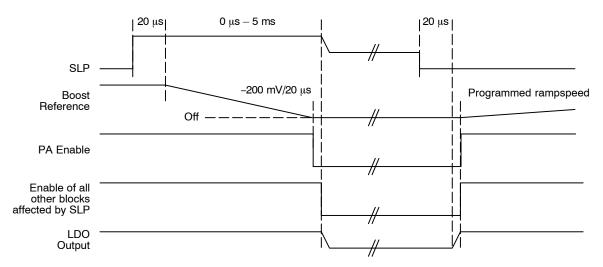

The NCP6992A is a Wireless Power Transmitter ASIC that provides power, measurement and supporting functions required for AIRFUEL ™-MR-compliant Power Transmitting Unit (PTU). Using an I<sup>2</sup>C series link, the NCP6992A interfaces a control processor with a boost converter, a power amplifier, its matching circuit and power transmitting resonator. Coupled to the Bluetooth<sup>®</sup> Low Energy (BLE) signaling protocol embedded in the control processor, the NCP6992A adjusts and optimizes the power applied to the transmitter coil by managing power transfer including efficiency as well as monitoring fault conditions. The NCP6992 has been designed for scalable power covering Class 2 (10 W) up to Class 5 (50 W) types of transmitters. The NCV6992A is the automotive release of this Wireless Power Transmitter ASIC.

#### **Features**

- Input Voltage Range from 4.5 V to 22 V (AV<sub>IN</sub> & PV<sub>IN</sub>)

Direct Supply from Wall Adapter or USB-Type Port

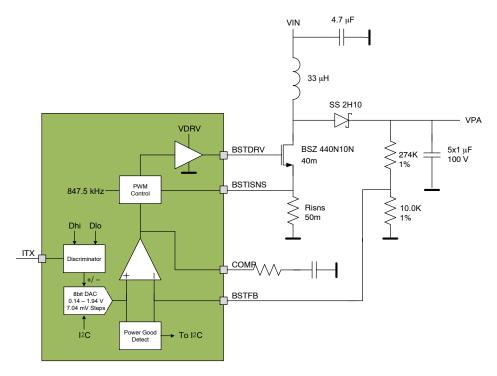

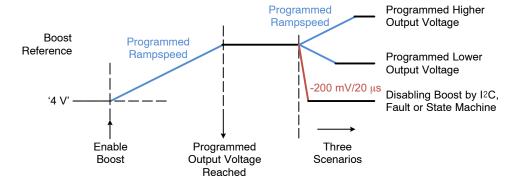

- 50-W PA Boost Controller Featuring Converter Programmable from 9 V to 55.2 V in 200 mV Steps with Over-Voltage Protection and Automatic Control Input Option Featuring Continuous and Window Control Modes.

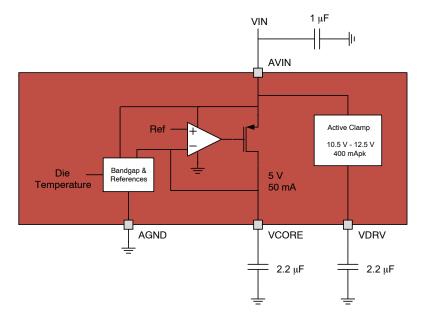

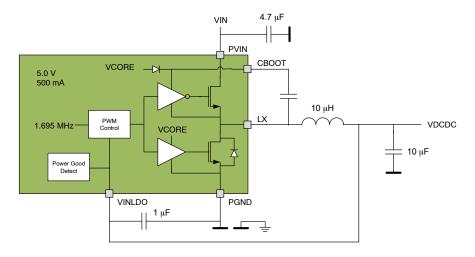

- Fixed-5 V & 500 mA Output, Fully Integrated System Buck Converter

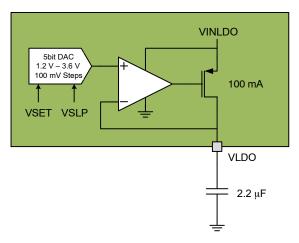

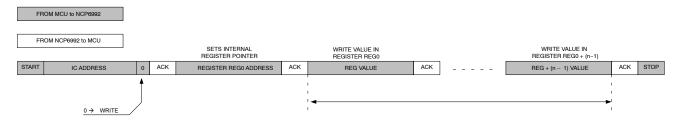

- System LDO, Programmable from 1.2 V to 3.6 V in 100 mV steps with Dynamic Voltage Scaling (DVS)

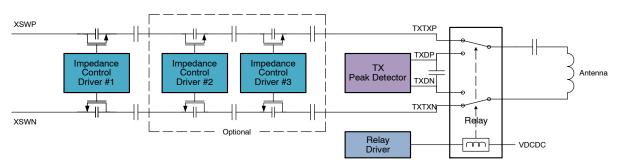

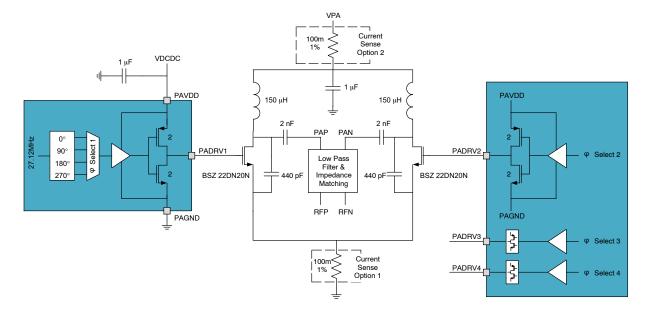

- Four Phase Selectable 6.78 MHz PA Drivers with Over-Current Protection

- 10-Bit ADC for PA Supply Voltage, Current & Temperature Measurements

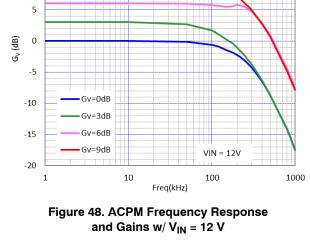

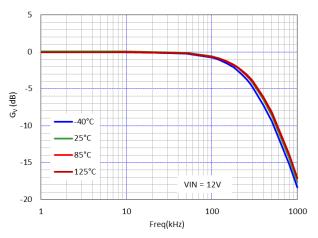

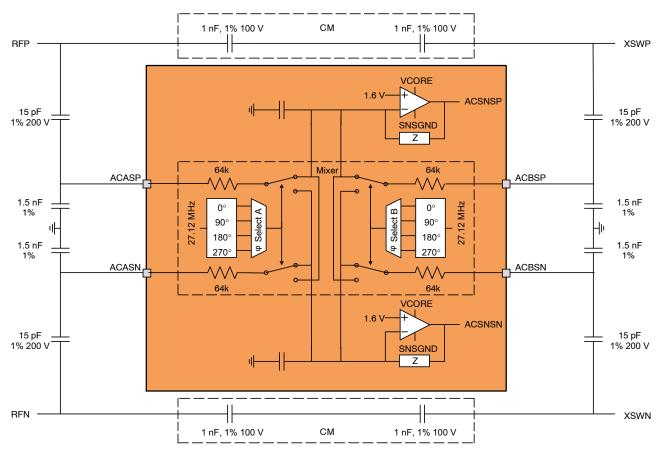

- Differential AC Power Measurement Circuit with ADC Reading

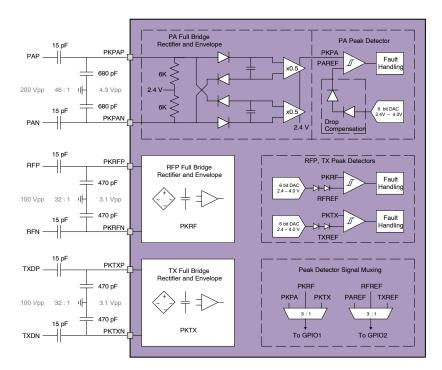

- 3 Full-Bridge Peak Detectors with 6-Bit Programmable Thresholds and Fault Handling

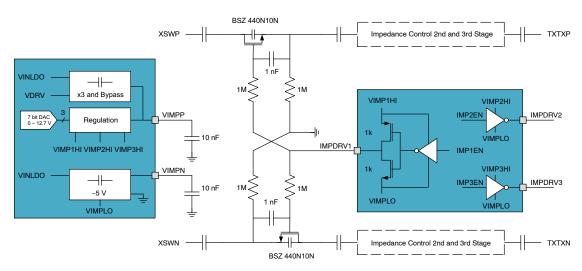

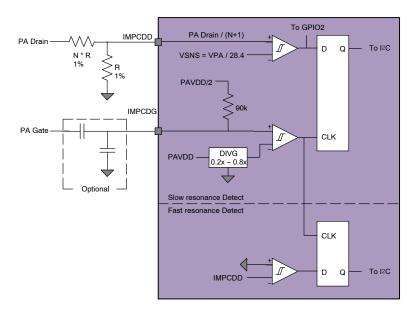

- 3 Impedance Control Drivers and One Impedance Control Detector

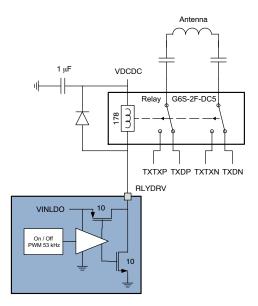

- PWM Controlled Relay Driver for Antenna Switching

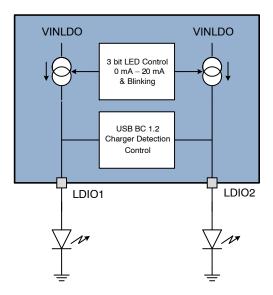

- 2 Programmable LED Drivers w/ Blinking and Protection

- Frontend for USB BC 1.2 Detection and QC 2.0/QC 3.0 Control Capability

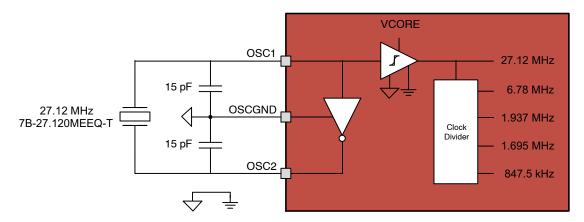

- Integrated 27.12 MHz Crystal Oscillator Driver

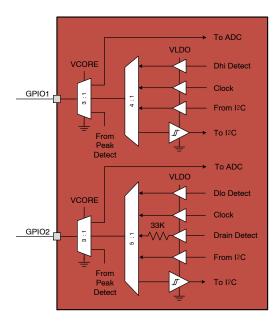

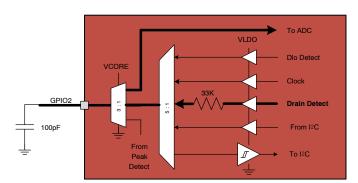

- 2 Versatile GPIO Usable for Logic I/O, ADC Input or Clock Output.

- Configurable Sleep Mode and Fast Wakeup Cycling with Direct Input Control

#### ON Semiconductor®

www.onsemi.com

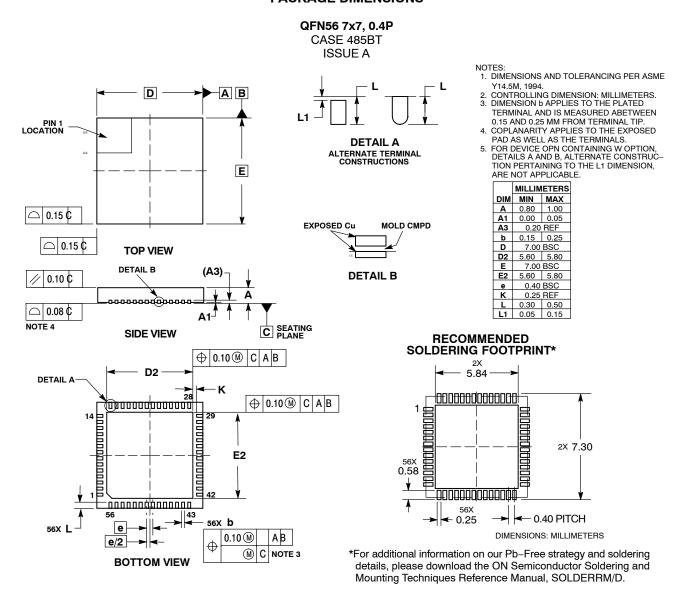

QFN56 7×7, 0.4P CASE 485BT

#### **MARKING DIAGRAM**

NCP6992A GLLYYWW NCV6992A GLLYYWW

G = Assembly Location

LL = Lot Trace Code

YY = Year WW = Work Week

Pb-Free indicator, microdot (•), may or may not be present

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 85 of this data sheet.

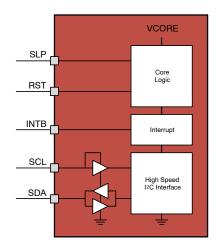

- Widely programmable through 3.4-MHz I<sup>2</sup>C Interface

- Available in a Small 7 × 7 mm<sup>2</sup> Wettable Flank Plated OFN-56 at Pitch 0.4 mm

- AEC-Q100 Qualified (Grade 3) and PPAP Capable

# **Typical Applications**

1

AIRFUEL-MR (Magnetic Resonance) Compliant (A4WP/Rezence<sup>™</sup>) for Wireless Charging Pad or Charging Station

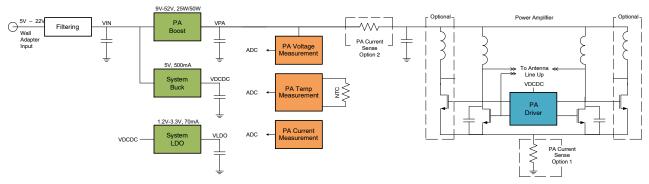

Figure 1. Typical Application

Figure 2. Block Diagram

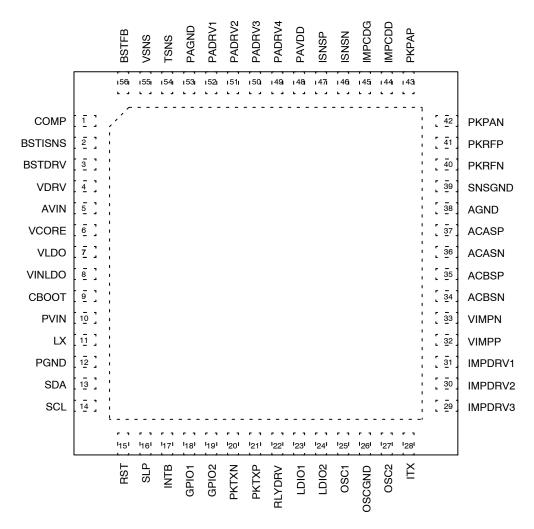

Figure 3. Package Pinout - QFN-56

**Table 1. PIN FUNCTION DESCRIPTION**

| Pin      | Name       | Туре         | Description                                                                        |

|----------|------------|--------------|------------------------------------------------------------------------------------|

| CORE SUF | PPLY       | •            | •                                                                                  |

| 4        | VDRV       | Power        | Supply for Drivers                                                                 |

| 5        | AVIN       | Power        | IC Core Input Supply                                                               |

| 6        | VCORE      | Power        | IC Core Supply                                                                     |

| 38       | AGND       | Ground       | Small Signal Ground                                                                |

| CRYSTAL  | OSCILLATOR | •            |                                                                                    |

| 25       | OSC1       | -            | Crystal Oscillator Connection 1     Or External Clock Input                        |

| 26       | OSCGND     | Ground       | Crystal Oscillator Ground                                                          |

| 27       | OSC2       | Input        | Crystal Oscillator Connection 2     Or Connected to OSCGND if External Clock Input |

| CONTROL  |            | •            |                                                                                    |

| 13       | SDA        | Input/Output | I <sup>2</sup> C Data Line                                                         |

| 14       | SCL        | Input        | I <sup>2</sup> C Clock Line                                                        |

| 15       | RST        | Input        | Reset Input                                                                        |

| 16       | SLP        | Input        | Sleep Mode Select Input                                                            |

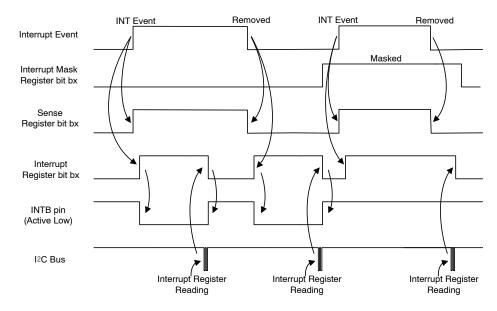

| 17       | INTB       | Output       | Interrupt Output                                                                   |

Table 1. PIN FUNCTION DESCRIPTION (continued)

| Pin       | Name              | Туре         | Description                                  |

|-----------|-------------------|--------------|----------------------------------------------|

| GPIOS     | •                 | •            | -                                            |

| 18        | GPIO1             | Input/Output | General Purpose Input/Output 1               |

| 19        | GPIO2             | Input/Output | General Purpose Input/Output 2               |

| SYSTEM S  | UPPLIES           | 1            |                                              |

| 7         | VLDO              | Power        | Linear Regulator Output                      |

| 8         | VINLDO            | Power        | 1. Linear Regulator Supply Input             |

|           |                   |              | 2. Buck Converter Output/Feedback            |

| 9         | CBOOT             | -            | Bootstrap Capacitor Connection               |

| 10        | PVIN              | Power        | Power Supply Input                           |

| 11        | LX                | -            | Buck Converter Switching Node                |

| 12        | PGND              | Ground       | Power Ground                                 |

| PA BOOST  | CONVERTER         | 1            |                                              |

| 1         | COMP              | Input        | Boost Converter Compensation Network         |

| 2         | BSTISNS           | Input        | Boost Converter Current Sense                |

| 3         | BSTDRV            | Output       | Boost Converter Low Side Driver Output       |

| 28        | ITX               | Input        | Transmit Current Discriminator Input         |

| 56        | BSTFB             | Power        | Boost Converter Feedback                     |

| PA DRIVER | RS                |              |                                              |

| 48        | PAVDD             | Power        | PA Driver Supply Input                       |

| 49        | PADRV4            | Output       | PA Driver Output 4                           |

| 50        | PADRV3            | Output       | PA Driver Output 3                           |

| 51        | PADRV2            | Output       | PA Driver Output 2                           |

| 52        | PADRV1            | Output       | PA Driver Output 1                           |

| 53        | PAGND             | Ground       | PA Driver Ground and Boost Controller Ground |

| IMPEDANC  | E CONTROL DRIVERS | 1            |                                              |

| 29        | IMPDRV3           | Output       | Impedance Control Driver 3                   |

| 30        | IMPDRV2           | Output       | Impedance Control Driver 2                   |

| 31        | IMPDRV1           | Output       | Impedance Control Driver 1                   |

| 32        | VIMPP             | -            | Charge Pump Positive Voltage Rail            |

| 33        | VIMPN             | _            | Charge Pump Negative Voltage Rail            |

| IMPEDANC  | E CONTROL DETECT  | 1            |                                              |

| 44        | IMPCDD            | Input        | Impedance Control Detect PA FET Drain Input  |

| 45        | IMPCDG            | Input        | Impedance Control Detect PA FET Gate Input   |

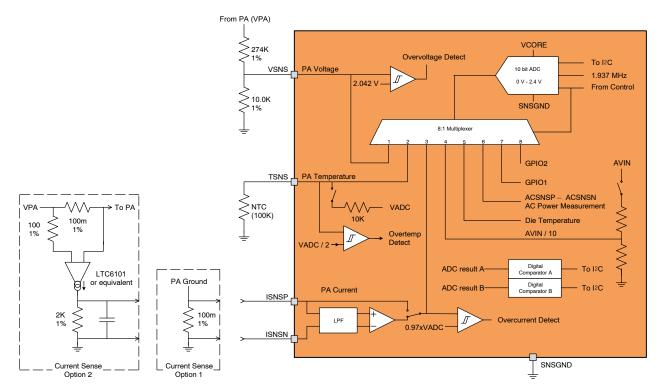

| ADC       |                   |              |                                              |

| 39        | SNSGND            | Ground       | ADC Ground                                   |

| 46        | ISNSN             | Input        | PA Current Sense Negative Input              |

| 47        | ISNSP             | Input        | PA Current Sense Positive Input              |

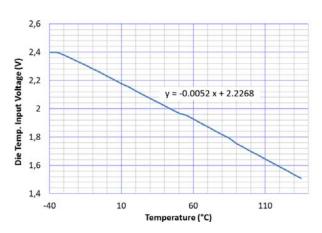

| 54        | TSNS              | Input        | PA Temperature Sense Input                   |

| 55        | VSNS              | Input        | PA Voltage Sense Input                       |

| AC POWER  | RMEASUREMENT      | 1            |                                              |

| 34        | ACBSN             | Input        | AC Power B Measurement Positive Input        |

| 35        | ACBSP             | Input        | AC Power B Measurement Negative Input        |

| 36        | ACASN             | Input        | AC Power A Measurement Positive Input        |

| 37        | ACASP             | Input        | AC Power A Measurement Negative Input        |

Table 1. PIN FUNCTION DESCRIPTION (continued)

| Pin       | Name   | Туре         | Description                     |                                       |

|-----------|--------|--------------|---------------------------------|---------------------------------------|

| PEAK DET  | ECTOR  |              |                                 |                                       |

| 20        | PKTXN  | Input        | TX Peak Detector Negative Input |                                       |

| 21        | PKTXP  | Input        | TX Peak Detector Positive Input |                                       |

| 40        | PKRFN  | Input        | RF Peak Detector Negative Input |                                       |

| 41        | PKRFP  | Input        | RF Peak Detector Positive Input |                                       |

| 42        | PKPAN  | Input        | PA Peak Detector Negative Input |                                       |

| 43        | PKPAP  | Input        | PA Peak Detector Positive Input |                                       |

| RELAY DR  | IVER   |              |                                 |                                       |

| 22        | RLYDRV | Output       | Relay Driver Output             |                                       |

| LED DRIVE | RS     |              |                                 |                                       |

| 23        | LDIO1  | Input/Output | LED Driver 1 or USB Detect      |                                       |

| 24        | LDIO2  | Input/Output | LED Driver 2 or USB Detect      |                                       |

| FLAG      |        |              |                                 | · · · · · · · · · · · · · · · · · · · |

| -         | _      | -            | Thermal Ground                  |                                       |

#### **Table 2. MAXIMUM RATINGS**

| Rating                                                                                                                                                   | Symbol                               | Value                                                  | Unit    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------|---------|

| Analog Power Input Pins: AV <sub>IN</sub> , PV <sub>IN</sub> (Non Operating (e.g.: Hot-Plug))                                                            | V <sub>HP</sub>                      | -0.3 to +30.0                                          | V       |

| Analog Power Input Pins: AV <sub>IN</sub> , PV <sub>IN</sub> , LX (Operating)                                                                            | V <sub>P</sub>                       | -0.3 to +26.0                                          | V       |

| Analog Power Input Pins: PAVDD                                                                                                                           | V <sub>A</sub>                       | -0.3 to +6.0                                           | V       |

| Analog Power Output Pins: V <sub>DRV</sub> , VIMPP, BSTDRV                                                                                               | V <sub>PO</sub>                      | $-0.3$ to $V_P + 0.3 V \le 16.0$                       | V       |

| Analog Power Output Pins: VIMPN                                                                                                                          | V <sub>NO</sub>                      | $-6 \le -V_P - 0.3 \text{ to } +0.3$                   | V       |

| Analog Outputs: IMPDRV1, IMPDRV2, IMPDRV3                                                                                                                | V <sub>AP</sub>                      | $-6 \le -V_{PO} - 0.3 \text{ to } V_{PO} + 0.3 \le 16$ | V       |

| Analog Power Output Pins V <sub>CORE</sub> , VLDO, VINLDO                                                                                                | Vo                                   | $-0.3 \text{ to V}_A + 0.3 \le 6.0$                    | V       |

| CBOOT with respect to LX                                                                                                                                 | V <sub>CBOOT_LX</sub>                | $-0.3 \text{ to V}_A + 0.3 \le 6.0$                    | V       |

| Digital Input Pins : SCL, SDA, SLP, RST, GPIO1, GPIO2<br>Input Voltage<br>Input Current                                                                  | V <sub>IDG</sub><br>I <sub>IDG</sub> | -0.3 to V <sub>A</sub> + 0.3 ≤ 6.0<br>10               | V<br>mA |

| Digital Output Pins: SDA, GPIO1, GPIO2, INTB Output Voltage                                                                                              | V <sub>ODG</sub>                     | -0.3 to 6.0                                            | ٧       |

| Analog Inputs: ISNSN, ISNSP, TSNS, VSNS, ACBSN, ACBSP, ACASN, ACASP, PKPAP, PKPAN, PKRFP, PKRFN, PKTXP, PKTXN, IMPCDD, IMPCDG, BSTFB, COMP, ITX, BSTISNS | V <sub>AN</sub><br>I <sub>AN</sub>   | -0.3 to V <sub>A</sub> + 0.3 ≤ 6.0<br>10               | V<br>mA |

| Crystal Pins: OSC1, OSC2                                                                                                                                 | V <sub>OSC</sub>                     | $-0.3 \text{ to V}_A + 0.3 \le 6.0$<br>10              | V<br>mA |

| Analog Outputs: PADRV1, PADRV2, PADRV3, PADRV4, RLYDRV, LDIO1, LDIO2                                                                                     | V <sub>AO</sub>                      | $-0.3$ to $V_A + 0.3 \le 6.0$                          | V       |

| Operating Ambient Temperature Range                                                                                                                      | T <sub>A</sub>                       | -40 to +85                                             | °C      |

| Operating Junction Temperature Range (Note 1)                                                                                                            | TJ                                   | -40 to +125                                            | °C      |

| Storage Temperature Range                                                                                                                                | T <sub>STG</sub>                     | -55 to +150                                            | °C      |

| Maximum Junction Temperature                                                                                                                             | T <sub>JMAX</sub>                    | -40 to + TSD (150)                                     | °C      |

| Thermal Resistance Junction-to-Ambient (Note 2)                                                                                                          | $R_{\Theta JA}$                      | 30                                                     | °C/W    |

| Moisture Sensitivity (Note 3)                                                                                                                            | MSL                                  | MSL1                                                   |         |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

The thermal shutdown set to 150°C (typical) avoids potential irreversible damage on the device due to power dissipation.

The Junction-to-Ambient thermal resistance is a function of Printed Circuit Board (PCB) layout and application. These data are measured using 4-layer PCBs (2s2p). For a given ambient temperature T<sub>A</sub> it has to be pay attention to not exceed the max junction temperature T<sub>JMAX</sub>.

3. Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020A.

#### **Table 3. GLOBAL OPERATING CONDITIONS**

| Symbol             | Parameter                                                                                       | Conditions                     | Min   | Тур   | Max       | Unit |

|--------------------|-------------------------------------------------------------------------------------------------|--------------------------------|-------|-------|-----------|------|

| AV <sub>IN</sub>   | IC Core Supply Input (Note 4)                                                                   |                                | 4.5   |       | 22        | V    |

| PV <sub>IN</sub>   | Power Supply Input (Note 4)                                                                     |                                | 4.5   |       | 22        | V    |

| F <sub>CLK</sub>   | Valid Clock Range                                                                               | At OSC1                        | 27.06 | 27.12 | 27.18     | MHz  |

| $V_{CLKpp}$        | External Clock Level                                                                            | Peak-to-Peak                   | 0.5   | -     | $V_{LDO}$ | V    |

| DC <sub>CLK</sub>  | External Clock Duty Cycle                                                                       |                                | 49    | _     | 51        | %    |

| Cout               | Charge Pump Converters Min Recommended<br>Output Capacitors on VIMPN and VIMPP<br>(Notes 5 & 6) | Capacitor Bias Voltage ≥ 16 V  | _     | 10    | -         | nF   |

| Cout               | V <sub>CORE</sub> and V <sub>LDO</sub> Min Recommended Output Capacitors (Note 5)               | Capacitor Bias Voltage ≥ 10 V  | _     | 2.2   | -         | μF   |

| Cout               | VDRV Min Recommended Output Capacitor (Notes 5 & 6)                                             | Capacitor Bias Voltage ≥ 16 V  | -     | 2.2   | -         | μF   |

| Cout               | Buck Converter Min Recommended Output Capacitor (Notes 5 & 6)                                   | Capacitor Bias Voltage ≥ 16 V  | _     | 10    | -         | μF   |

| Cout               | Boost Converter Min Recommended Output Capacitor (Notes 5 & 6)                                  | Capacitor Bias Voltage ≥ 100 V | _     | 5     | -         | μF   |

| L_Boost            | Boost Converter Recommended Inductor (Note 6)                                                   |                                | _     | 33    | -         | μН   |

| L_ <sub>Buck</sub> | Buck Converter Recommended Inductor (Note 6)                                                    |                                | _     | 10    | -         | μН   |

<sup>4.</sup> Operation above 22 V input voltage may affect device reliability.

5. CMS capacitor values vary with voltage applied across their terminals. Capacitance de-rating with bias across has to be taken into account when selecting decoupling capacitors.

6. See corresponding applications details for external component selection, implementation and converter set-up conditions.

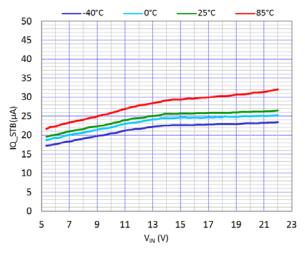

# Table 4. ELECTRICAL CHARACTERISTICS: SUPPLY INPUTS AVIN & PVIN AND CORE SUPPLIES

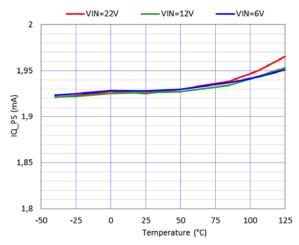

(Min & Max Limits apply for  $T_A$  from  $-40^{\circ}C$  to  $+85^{\circ}C$ ;  $AV_{IN} = PV_{IN} = 12$  V. Typical values are given for  $T_A = +25^{\circ}C$  and default configuration. These conditions are true unless otherwise noted.)

| Symbol              | Parameter                                                                   | Conditions                                                                                                                                               | Min | Тур  | Max | Unit |

|---------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| NCP6992A            | SUPPLY INPUTS AVIN & PVIN                                                   |                                                                                                                                                          |     |      |     |      |

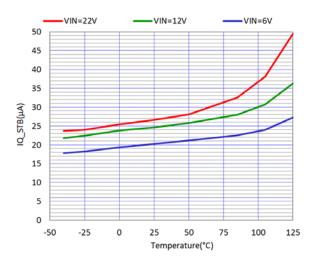

| IQ                  | Operating Quiescent Current with AV <sub>IN</sub> = PV <sub>IN</sub> = 12 V | Standby = Core + VDRV Clamp (Note 7).<br>Standby ON, all other blocks OFF.                                                                               | -   | 25   | 100 | μΑ   |

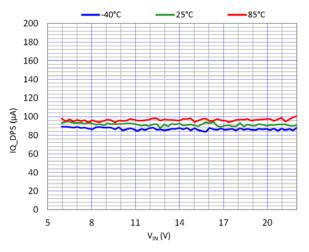

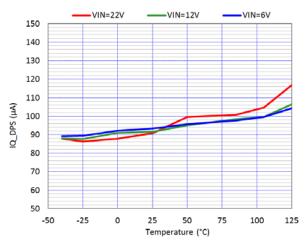

|                     |                                                                             | Deep Power Save (DPS) Conditions DPS = Standby + On-Chip Clock Core + Buck (PFM) + LDO, no load, no switching DPS ON, all the other blocks OFF           | _   | 100  | -   | μΑ   |

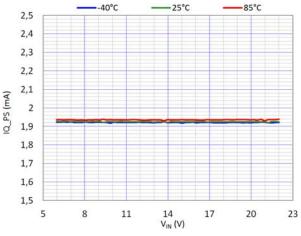

|                     |                                                                             | Power Save (PS) Conditions PS = DPS + Crystal Oscillator (crystal included), no load, no switching PS ON, all the other blocks OFF                       | _   | 2.0  | _   | mA   |

|                     |                                                                             | Full Chip Enabled with ADC input stages activated, Impedance Control Detectors and ADC are not enabled (Note 8), no load, no switching                   | _   | 4.0  | -   | mA   |

| CORE SUF            | PPLIES (Note 9)                                                             |                                                                                                                                                          |     |      |     |      |

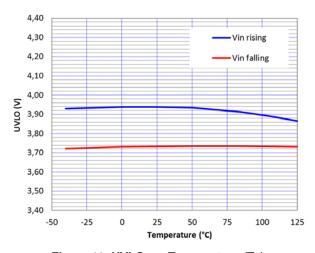

| UVLO                | Under-Voltage Lockout                                                       | Rising Edge of AV <sub>IN</sub>                                                                                                                          | 3.8 | -    | 4   | V    |

|                     |                                                                             | Hysteresis                                                                                                                                               | _   | 200  | -   | mV   |

| V <sub>CORE</sub>   | Core Supply voltage                                                         | AV <sub>IN</sub> > 6 V                                                                                                                                   | -   | 5    | -   | V    |

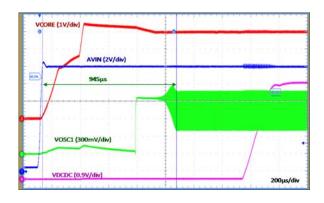

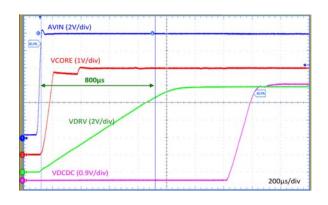

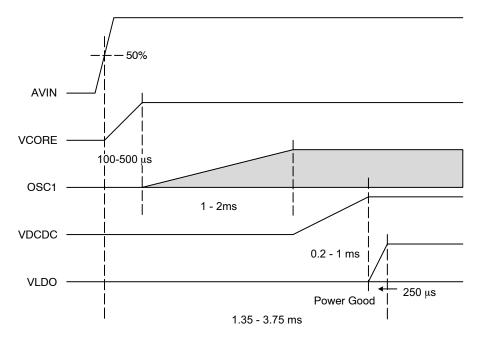

| T <sub>SSCORE</sub> | Core Supply Soft-Start<br>(Note 11)                                         | From AV <sub>IN</sub> = $0.9 \times 12$ V to $0.9 \times V_{CORE}$ nominal (AV <sub>IN</sub> from 0 to 12 V with rise time > $0.6$ V/ $\mu$ s)           | 0.1 | -    | 1   | ms   |

| V <sub>DRV</sub>    | Driver Supply Clamp Voltage                                                 | Low Voltage Value (default)                                                                                                                              | -   | 10.5 | -   | V    |

|                     |                                                                             | High Voltage Value                                                                                                                                       | -   | 12.5 | -   |      |

| T <sub>SSDRV</sub>  | Driver Supply Soft-Start (Note 11)                                          | From AV <sub>IN</sub> = $0.9 \times 12$ V to V <sub>DRV</sub> = $0.9 \times V_{DRV}$ (AV <sub>IN</sub> from 0 to 12 V with rise time > $0.6$ V/ $\mu$ s) | 0.1 | -    | 1.5 | ms   |

| T <sub>WRN</sub>    | Thermal Warning                                                             |                                                                                                                                                          | _   | 135  | -   | °C   |

| T <sub>SD</sub>     | Thermal Shutdown                                                            |                                                                                                                                                          | -   | 150  | -   | °C   |

| T <sub>ReA</sub>    | Thermal Re-Arming                                                           |                                                                                                                                                          | -   | 120  | -   | °C   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- 7. Core Includes V<sub>CORE</sub>, bandgap, references, logic and detectors.

- 8. ADC enabled only during conversion.

- 9. External Components:  $C_{VCORE}$  = 2.2  $\mu$ F,  $C_{VDRV}$  = 2.2  $\mu$ F.

#### Table 5. ELECTRICAL CHARACTERISTICS: BUCK CONVERTER & REGULATOR

(Min & Max Limits apply for  $T_A$  from  $-40^{\circ}C$  to  $+85^{\circ}C$ ;  $AV_{IN} = PV_{IN} = 12$  V. Typical values are given for  $T_A = +25^{\circ}C$  and default configuration. These conditions are true unless otherwise noted.)

| Symbol               | Parameter                                                  | Conditions                                                     | Min             | Тур  | Max  | Unit |

|----------------------|------------------------------------------------------------|----------------------------------------------------------------|-----------------|------|------|------|

| SYSTEM BU            | JCK CONVERTER (Note 10)                                    |                                                                |                 |      |      |      |

| $PV_{IN}$            | Operating Input Voltage<br>Range (Note 11)                 |                                                                | 6               | _    | 22   | ٧    |

| V <sub>DCDC</sub>    | Output Voltage                                             | AV <sub>IN</sub> = 12 V, I <sub>OUT</sub> = 250 mA, Forced PWM | 4.75            | -    | 5.25 | V    |

| lo_DCDC              | Output Current Capability (Note 11)                        |                                                                | 500             | _    | -    | mA   |

| I <sub>Peak</sub>    | Current Limit                                              |                                                                | 0.9             | -    | 2.0  | Α    |

| F <sub>SW_BUCK</sub> | Buck Switching Frequency (Note 12)                         | F <sub>CLK_INT</sub> /2                                        | -               | 1700 | -    | kHz  |

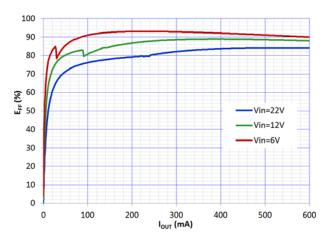

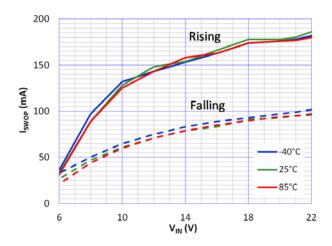

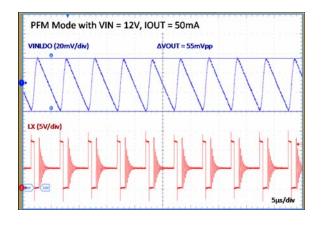

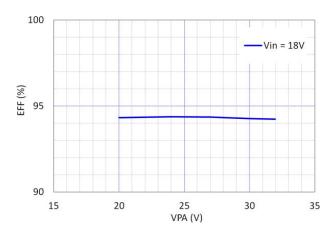

| η                    | Efficiency (Note 11)                                       | I <sub>Load</sub> = 50 mA, PFM, Xtal Off                       | -               | 81   | _    | %    |

|                      |                                                            | I <sub>Load</sub> = 250 mA, PWM                                | -               | 90   | _    | %    |

| T <sub>SSDCDC</sub>  | Soft-Start                                                 | From Buck Enable to $0.9 \times V_{DCDC}$ , No Load            | 0.2             | -    | 0.8  | ms   |

| R <sub>BUCKDIS</sub> | Output Discharge Path                                      | At V <sub>DCDC</sub> = 5 V                                     | -               | 65   | _    | Ω    |

| $V_{PG}$             | Power Good Threshold                                       | Low (PV <sub>IN</sub> Falling)                                 | -               | 4.25 | _    | V    |

|                      |                                                            | High (PV <sub>IN</sub> Rising)                                 | -               | 4.50 | _    | V    |

| V <sub>PG_acc</sub>  | Power Good Threshold<br>Accuracy                           |                                                                | -5              | _    | 5    | %    |

| $\DeltaT_{PG}$       | Power Good Detection<br>Debounce Period<br>(Notes 11 & 12) |                                                                | -               | 30   | _    | μs   |

| SYSTEM RE            | EGULATOR (Note 13), V <sub>LDO</sub> = 3                   | 3.3 V                                                          |                 |      |      |      |

| V <sub>INLDO</sub>   | Operating Input Voltage<br>Range (Note 11)                 | at VINLDO                                                      | V <sub>PG</sub> | -    | 5.5  | V    |

| $V_{LDO}$            | Output Voltage Range                                       | VSET, VSLP (Note 14)                                           | 1.20            | -    | 3.60 | V    |

| V <sub>STEP</sub>    | Output Voltage Ramp Step                                   |                                                                | -               | 100  | _    | mV   |

| T <sub>SPEED</sub>   | Output Voltage Ramp<br>Speed                               |                                                                | -               | 10   | -    | μs   |

| V <sub>LDO_Acc</sub> | Regulator Output Voltage<br>Accuracy                       | VINLDO = 5 V                                                   | -2              | _    | 2    | %    |

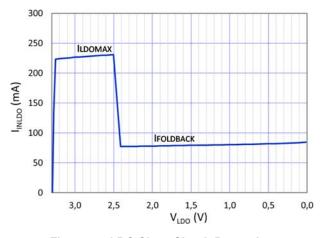

| I <sub>LDO</sub>     | Output Current Capability                                  |                                                                | 100             | -    | _    | mA   |

| I <sub>LDOMAX</sub>  | Current Limit                                              |                                                                | 180             | -    | 350  | mA   |

| I <sub>FB</sub>      | Fold Back current                                          |                                                                |                 | 100  |      | mA   |

| T <sub>SS LDO</sub>  | Soft Start                                                 | VDCDC Power Good to 2.5 V                                      | -               | 280  | -    | μs   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

At VLDO = 3.3 V

Ω

65

Output Discharge Path

**R**LDODIS

<sup>10.</sup> Buck DC-DC External Components: L = 10  $\mu$ H, C = 10  $\mu$ F. 11. Characterized and guaranteed by design.

<sup>12.</sup> Tested by scan.

<sup>13.</sup> LDO External Components: C = 2.2 μF.

<sup>14.</sup> Represents Programmable Range (bits VLDOSET[4:0] & VLDOSLP[4:0]), the Default VSET level is selectable through factory fuse and VSLP = VSET.

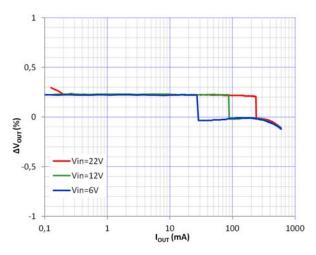

# Table 6. ELECTRICAL CHARACTERISTICS: BOOST CONTROLLER

(Min & Max Limits apply for  $T_A$  from  $-40^{\circ}$ C to  $+85^{\circ}$ C;  $AV_{IN} = PV_{IN} = 12$  V. Typical values are given for  $T_A = +25^{\circ}$ C and default configuration. These conditions are true unless otherwise noted.)

| Symbol                 | Parameter                                                                                 | Conditions                                                                                                                   | Min    | Тур   | Max  | Unit   |

|------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------|-------|------|--------|

| PA BOOST CO            | ONVERTER (Notes 15 & 16)                                                                  |                                                                                                                              |        |       |      |        |

| $PV_{IN}$              | Operating Input Voltage Range (Note 11)                                                   | At PV <sub>IN</sub>                                                                                                          | 8      | -     | 22   | V      |

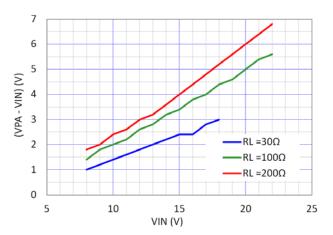

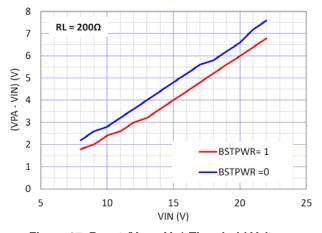

| P <sub>OUT</sub>       | Output Power Capability (Notes 11 & 17)                                                   | Standard Range (Default)<br>(BSTPWR = 0)                                                                                     | 0      | -     | 25   | W      |

|                        |                                                                                           | High Power Range<br>(BSTPWR = 1)                                                                                             | 10     | -     | 50   | W      |

| V <sub>BSTFB</sub>     | Boost Feedback Voltage (Note 15)                                                          | VPA = 28.4 V                                                                                                                 | -      | 1     | -    | V      |

| V <sub>OUT</sub>       | Output Voltage Range                                                                      | PV <sub>IN</sub> < VPA                                                                                                       | 9      | -     | 55.2 | V      |

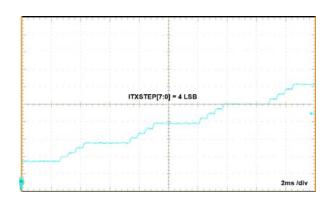

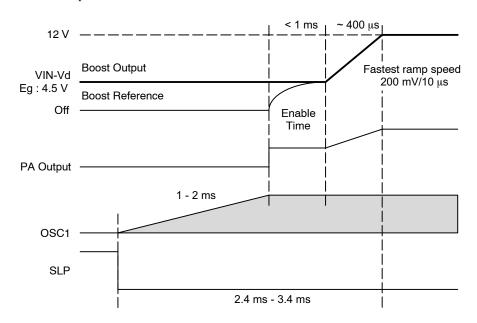

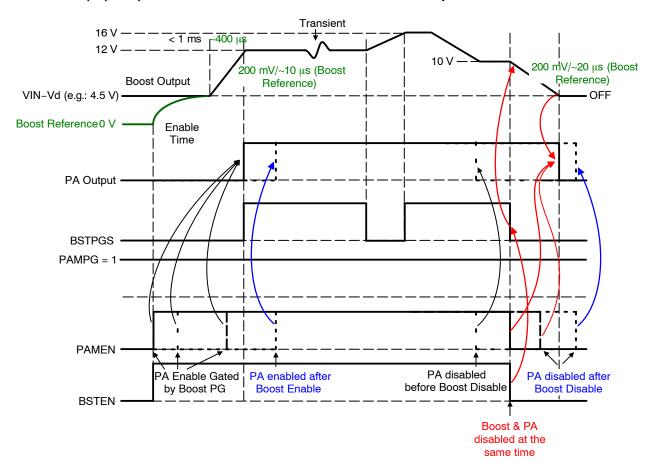

| ΔV <sub>OUT_STEP</sub> | Ramp Step                                                                                 |                                                                                                                              | -      | 200   | -    | mV     |

| T <sub>BST</sub>       | Ramp Speed Range<br>(Notes 12 & 18)                                                       |                                                                                                                              | 9.4375 | -     | 1208 | μs     |

| T <sub>BSTDIS</sub>    | Disable Ramp Speed                                                                        | Per Ramp Step                                                                                                                | -      | 18.88 | -    | μs     |

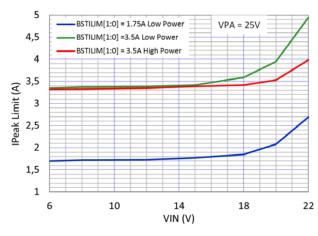

| I <sub>PKlim</sub>     | Peak Current Limit (Note 19)                                                              | Power Standard Range                                                                                                         | -      | 1.75  | -    | Α      |

|                        |                                                                                           | (BSTPWR = 0)                                                                                                                 | _      | 2.25  | -    |        |

|                        |                                                                                           |                                                                                                                              | 3      | 3.5   | 4    |        |

|                        |                                                                                           |                                                                                                                              | 4      | 4.5   | 5    |        |

|                        |                                                                                           | High Power Range                                                                                                             | -      | 3.5   | -    | Α      |

|                        |                                                                                           | (BSTPWR = 1)                                                                                                                 | _      | 4.5   | -    |        |

|                        |                                                                                           |                                                                                                                              | _      | 7     | -    | ]      |

|                        |                                                                                           |                                                                                                                              | _      | 9     | -    |        |

| T <sub>deb_ILIM</sub>  | Peak Current Limit Debounce Time<br>(Number of Boost Clock Cycle<br>F <sub>SW_BST</sub> ) | (Note 12)                                                                                                                    | -      | 64    | -    | Cycles |

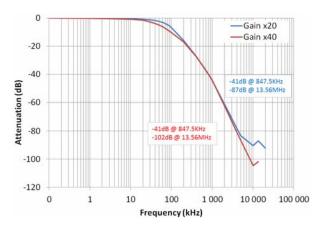

| F <sub>SW_BST</sub>    | Boost Switching Frequency (Note 12)                                                       | 27.12 MHz / 32                                                                                                               | -      | 847.5 | -    | kHz    |

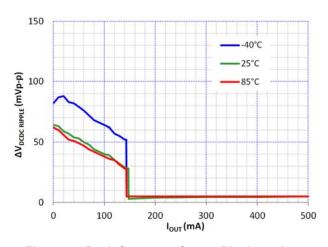

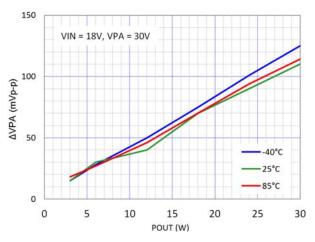

|                        | Output Ripple (Note 11)                                                                   | $PV_{IN} = 12 \text{ V, VPA} = 50 \text{ V,} \\ I_{LOAD} = 400 \text{ mA, P}_{OUT} = 20 \text{ W,} \\ C_{OUT} = 5 \mu F$     | -      | -     | 200  | mVpp   |

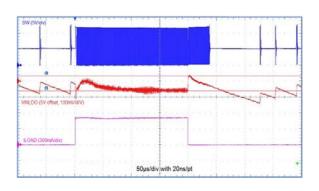

| LOAD <sub>TR</sub>     | Load Transient Response (Note 11)                                                         | $PV_{IN} = 12 \text{ V, VPA} = 50 \text{ V,}$<br>$I_{LOAD} = 0 \text{ to } 500 \text{ mA,}$<br>$T_R = T_F = 20  \mu\text{s}$ | -3     | -     | 3    | V      |

|                        |                                                                                           | $PV_{IN} = 12 \text{ V, VPA} = 36 \text{ V,} \\ I_{LOAD} = 0 \text{ to } 360 \text{ mA,} \\ T_R = T_F = 20  \mu \text{s}$    | -2     | -     | 2    | V      |

| V <sub>GBST</sub>      | Gate Drive Voltage (Note 11)                                                              |                                                                                                                              | 0      | -     | VDRV | V      |

| T <sub>R</sub>         | Rise Time                                                                                 | 1 nF, 10% – 90%                                                                                                              | _      | 10    | -    | ns     |

| T <sub>F</sub>         | Fall Time                                                                                 | 1 nF, 10% – 90%                                                                                                              | _      | 10    | -    | ns     |

| $\Delta V_{PG}$        | Power Good Detection Window                                                               | At BSTFB Compared to DAC Setting                                                                                             | -      | -7    | -    | mV     |

|                        |                                                                                           | At VPA                                                                                                                       | -      | -200  | -    | mV     |

| $\Delta T_{DEB\_PG}$   | Power Good Debounce                                                                       |                                                                                                                              | -      | 20    | -    | μs     |

| T <sub>EN</sub>        | Enable Time                                                                               | PV <sub>IN</sub> = 12 V, from BSTEN to<br>Boost Ramping Start                                                                | -      | -     | 1    | ms     |

#### Table 6. ELECTRICAL CHARACTERISTICS: BOOST CONTROLLER (continued)

(Min & Max Limits apply for  $T_A$  from  $-40^{\circ}C$  to  $+85^{\circ}C$ ;  $AV_{IN} = PV_{IN} = 12$  V. Typical values are given for  $T_A = +25^{\circ}C$  and default configuration. These conditions are true unless otherwise noted.)

| Symbol            | Parameter                            | Conditions | Min   | Тур    | Max    | Unit |  |  |  |  |

|-------------------|--------------------------------------|------------|-------|--------|--------|------|--|--|--|--|

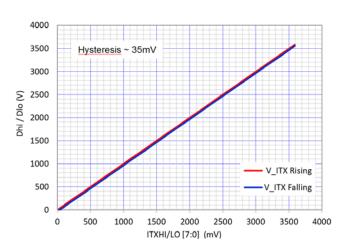

| DISCRIMINAT       | DISCRIMINATOR                        |            |       |        |        |      |  |  |  |  |

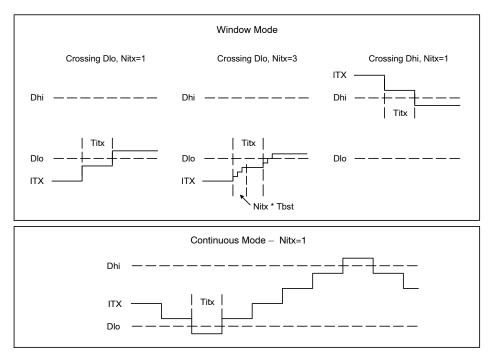

| Dhi               | Discriminator High Threshold Range   |            | 0     | -      | 3.5915 | V    |  |  |  |  |

| Dlo               | Discriminator Low Threshold Range    |            | 0     | -      | 3.5915 | V    |  |  |  |  |

| $\Delta V_{TH}$   | Thresholds Granularity               | 8 bits     | -     | 14.084 | -      | mV   |  |  |  |  |

| TH <sub>ACC</sub> | Thresholds Accuracy                  |            |       | ±0.5   |        | LSB  |  |  |  |  |

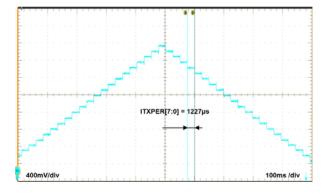

| T <sub>ITX</sub>  | Sampling Speed Range (Note 12)       |            | 18.88 | -      | 1208   | μs   |  |  |  |  |

| T <sub>ITXG</sub> | Sampling Speed Granularity (Note 12) | 8 bits     | -     | 18.88  | -      | μs   |  |  |  |  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- 15. External Feedback Network Using 10  $k\Omega$  and 274  $k\Omega$  for a 1/28.4 divider.

- 16. External Components: L = 33  $\mu$ H, C = 5  $\mu$ F, R<sub>ISNS</sub> = 50 m $\Omega$ , NMOS = BSZ440N10N, Rectifier = D = SS2H10. 17. The appropriate transistor and rectifier have to be selected for satisfying the power dissipation requirements in regards to the Boost output power.

- 18. Eg: Enable to 36 V, 200 mV/604  $\mu$ s, ramp starts at 0.1479 V  $\times$  28.4 = 4.2 V, ramp duration is 96.4 ms.

- 19. Peak current limit is tested in Open Loop.

#### Table 7. ELECTRICAL CHARACTERISTICS: CORE CONTROL

(Min & Max Limits apply for  $T_A$  from  $-40^{\circ}$ C to  $+85^{\circ}$ C;  $AV_{IN} = PV_{IN} = 12$  V. Typical values are given for  $T_A = +25^{\circ}$ C and default configuration. These conditions are true unless otherwise noted.)

| Symbol               | Parameter                                               | Conditions                                             | Min                    | Тур           | Max                  | Unit |

|----------------------|---------------------------------------------------------|--------------------------------------------------------|------------------------|---------------|----------------------|------|

| CONTROL:             | SCL, SDA, RST, SLP, GPIO1, GPI                          | O2, INTB                                               |                        |               | •                    | •    |

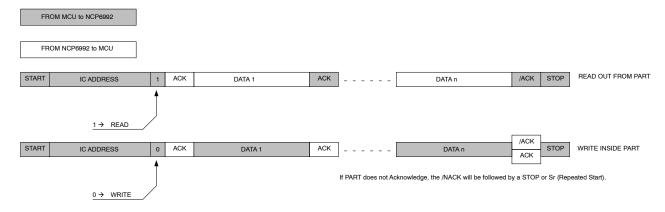

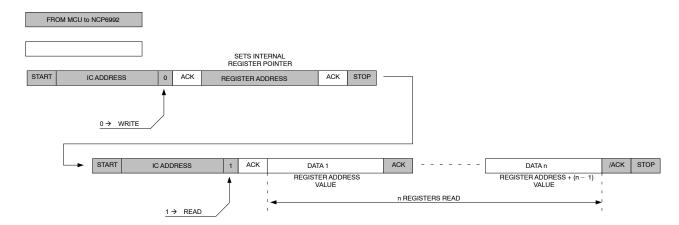

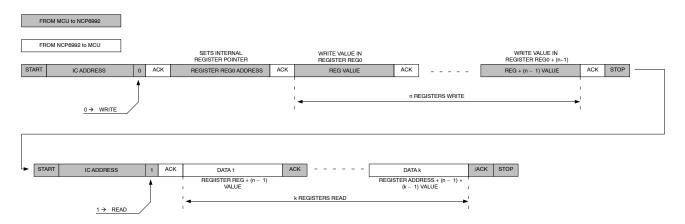

| F <sub>I2C</sub>     | I <sup>2</sup> C Operating Frequency<br>(Notes 11 & 20) |                                                        | -                      | _             | 3.4                  | MHz  |

| V <sub>IH</sub>      | High Input Voltage<br>SCL<br>SDA                        |                                                        | 1.6<br>1.2             | <u>-</u><br>- | -<br>-               | V    |

| $V_{IL}$             | SCL, SDA, Low Input Voltage                             |                                                        | -                      | -             | 0.4                  | V    |

| $V_{OL}$             | SDA, Low Output Voltage                                 | Sink 3 mA                                              | -                      | -             | 0.4                  | V    |

| $V_{IH}$             | RST, SLP Logic High Input<br>Voltage                    |                                                        | 1.1                    | _             | 5.5                  | ٧    |

| $V_{IL}$             | RST, SLP Logic Low Input<br>Voltage                     |                                                        | -                      | -             | 0.4                  | V    |

| V <sub>OH</sub>      | INTB Logic High Output Voltage (Note 11)                | Open Drain                                             | -                      | _             | V <sub>INLDO</sub>   | V    |

| V <sub>OL</sub>      | INTB Logic Low Output Voltage                           | 1 mA                                                   | -                      | -             | 0.2                  | V    |

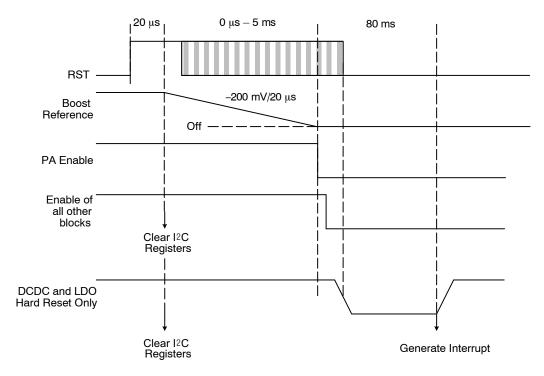

| T <sub>DEB</sub>     | RST, SLP Debounce Period (Note 12)                      |                                                        | -                      | 20            | -                    | μs   |

| V <sub>IH</sub>      | GPIO1, GPIO2 Logic High Input<br>Voltage                |                                                        | $0.7 \times V_{LDO}$   | -             | V <sub>LDO</sub>     | V    |

| V <sub>IL</sub>      | GPIO1, GPIO2 Logic Low Input<br>Voltage                 |                                                        | 0                      | _             | $0.3 \times V_{LDO}$ | V    |

| V <sub>OH</sub>      | GPIO1, GPIO2 Logic High<br>Output Voltage               | 1 mA                                                   | V <sub>LDO</sub> – 0.2 | _             | V <sub>LDO</sub>     | V    |

| V <sub>OL</sub>      | GPIO1, GPIO2 Logic Low<br>Output Voltage                | 1 mA                                                   | 0                      | _             | 0.2                  | V    |

| T <sub>R</sub>       | GPIO1 & GPIO2 Rise Times                                | $V_{LDO} > 1.7 \text{ V, } C_{LOAD} \le 20 \text{ pF}$ | -                      | _             | 5                    | ns   |

| T <sub>F</sub>       | GPIO1 & GPIO2 Fall Times                                | (Note 11)                                              | -                      | -             | 5                    | ns   |

| V <sub>I_Range</sub> | GPIO1 & GPIO2 Analog Input<br>Voltage Range             | To ADC                                                 | 0                      | -             | 2.4                  | ٧    |

| R <sub>O_IO2</sub>   | GPIO2 Output Impedance<br>(Note 22)                     | Drain Detect Out                                       | -                      | 33            | -                    | kΩ   |

| CLOCKING             | : CRYSTAL OSCILLATOR (Note 23                           | 3)                                                     |                        |               |                      |      |

| T <sub>SU_XTAL</sub> | Crystal Oscillator Start-Up Time (Note 11)              | From Clock Enable to Clock<br>Valid and Stable         | -                      | 0.9           | 1                    | ms   |

| T <sub>CLKTO</sub>   | Oscillator Clock Validation<br>Timeout (Note 12)        |                                                        | -                      | 10            | -                    | ms   |

| F <sub>CLK_INT</sub> | Internal Clock Frequency                                |                                                        | 3.0                    | -             | 3.75                 | MHz  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

<sup>20.</sup> The 4 available I<sup>2</sup>C addresses are 0010000, 0010100, 0011000, 0011100 with A7 MSB bit programmable (see Table 17). Through I<sup>2</sup>C the MSB can be programmed to a 1 for a software initiated address change.

<sup>21.</sup> If the SCL and SDA pull-ups are not connected to VLDO, the I2C bus cannot be operated for the lower voltage settings of VLDO.

<sup>22.</sup> See § "GPIOs" and Figure 83 for Drain Detect ADC reading.

<sup>23.</sup> Crystal Used: 7B-27.120MEEQ-T.

<sup>24.</sup> Quiescent current depends on the amplitude of the clock signal. Higher is the amplitude lower is IQ.

#### **Table 8. ELECTRICAL CHARACTERISTICS: DRIVERS**

(Min & Max Limits apply for  $T_A$  from  $-40^{\circ}C$  to  $+85^{\circ}C$ ;  $AV_{IN} = PV_{IN} = 12$  V. Typical values are given for  $T_A = +25^{\circ}C$  and default configuration. These conditions are true unless otherwise noted.)

| Symbol                          | Parameter                                             | Conditions                                                                                                                                                                                     | Min             | Тур  | Max               | Unit |

|---------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-------------------|------|

| POWER AMPL                      | IFIER DRIVERS (Note 25)                               |                                                                                                                                                                                                |                 |      |                   |      |

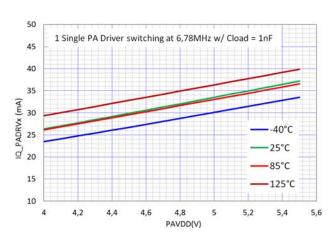

| PAV <sub>DD</sub>               | Operating Input Voltage Range (Note 11)               | At PAV <sub>DD</sub>                                                                                                                                                                           | V <sub>PG</sub> | _    | 5.5               | V    |

| F <sub>S</sub>                  | Signal Frequency (Note 12)                            | 27.12 MHz Divided by 4                                                                                                                                                                         | -               | 6.78 | -                 | MHz  |

| V <sub>PADRV</sub>              | Gate Drive Voltage                                    |                                                                                                                                                                                                | 0               | -    | PAV <sub>DD</sub> | V    |

| GD <sub>Delay</sub>             | Relative Gate Drive Delay                             | Between Rising Edges                                                                                                                                                                           | -               | ±1   | -                 | ns   |

|                                 | (Notes 26 & 11)                                       | Between Falling Edges                                                                                                                                                                          | -               | ±1   | 1                 | ns   |

|                                 |                                                       | Rising versus Falling Edges                                                                                                                                                                    | -               | ±1   | -                 | ns   |

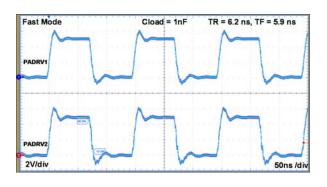

| T <sub>R</sub> & T <sub>F</sub> | Rise & Fall Times                                     | Fast (Default)                                                                                                                                                                                 | -               | 6    | 10                | ns   |

|                                 | (Notes 27 & 11)                                       | Mid                                                                                                                                                                                            | -               | _    | 20                | ns   |

|                                 |                                                       | Slow                                                                                                                                                                                           | -               | -    | 40                | ns   |

| T <sub>EN</sub>                 | Enable Time (Note 11)                                 |                                                                                                                                                                                                | -               | _    | 10                | μs   |

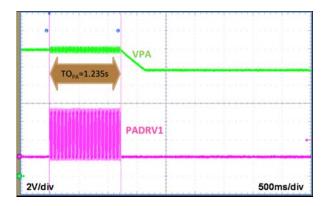

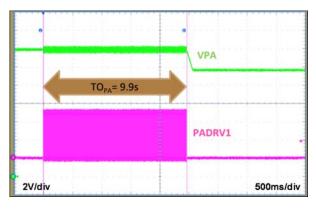

| TO <sub>PA</sub>                | PA Time Out (Note 12)                                 | Short                                                                                                                                                                                          | -               | 0.3  | -                 | s    |

|                                 |                                                       | Medium                                                                                                                                                                                         | -               | 1.2  | -                 | S    |

|                                 |                                                       | Long                                                                                                                                                                                           | -               | 9.8  | _                 | S    |

| IMPEDANCE C                     | ONTROL DRIVERS (Note 28)                              |                                                                                                                                                                                                |                 |      |                   |      |

| VINLDO                          | Operating Input Voltage Range (Note 11)               |                                                                                                                                                                                                | V <sub>PG</sub> | -    | 5.5               | V    |

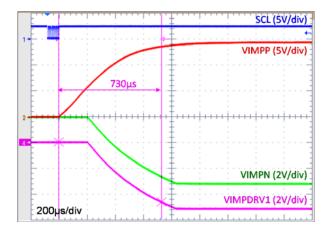

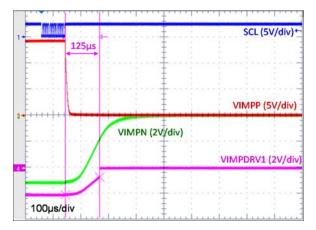

| F <sub>SW_CP</sub>              | Charge Pump Switching Frequency (Note 12)             | 27.12 MHz / 6                                                                                                                                                                                  | _               | 4.52 | _                 | MHz  |

| VIMPN                           | Charge Pump Negative Voltage (Note 29)                | - V <sub>INLDO</sub>                                                                                                                                                                           | -               | -5   | -                 | V    |

| VIMPP                           | Charge Pump Positive Voltage (Note 29)                | 3 × V <sub>INLDO</sub>                                                                                                                                                                         | -               | 14   | -                 | V    |

| VIMPxHI                         | Driver Output High Voltage<br>Programmability Range   |                                                                                                                                                                                                | 0               | -    | 12.7              | V    |

| ΔVIMPxHI                        | Driver Output High Voltage<br>Granularity             |                                                                                                                                                                                                | _               | 100  | _                 | mV   |

| R <sub>OUT_OFF</sub>            | Output Impedance in OFF Mode (Master Enable Disabled) |                                                                                                                                                                                                | _               | 0.5  | _                 | kΩ   |

| V <sub>IMPDOH_ACC</sub>         | Driver Output High Voltage<br>Accuracy (Note 30)      | $V_{IMPP} = 3 \times V_{INLDO} \text{ or } V_{DRV,}$<br>$V_{IMPxHI} \le 3.0 \text{ V, } I_{OH} = +3 \times 10  \mu A$                                                                          | -100            | -    | +100              | mV   |

|                                 |                                                       | $V_{IMPP} = 3 \times V_{INLDO} \text{ or } V_{DRV,}$<br>$V_{IMPxHI} \ge 3.0 \text{ V, } I_{OH} = + 3 \times 10  \mu\text{A}$                                                                   | -3              | -    | +3                | %    |

| I <sub>OUT_MAX</sub>            | Maximum Source Capability (Note 31)                   | $\begin{split} &V_{IMPP} = V_{DRV}, 150 \text{ mV Drop} \\ &VIMPxHI \leq 9.0 \text{ V for } V_{DRV} = 10.5 \text{ V} \\ &VIMPxHI \leq 9.5 \text{ V for } V_{DRV} = 12.5 \text{ V} \end{split}$ | 100             | -    | -                 | μΑ   |

|                                 |                                                       | $\begin{split} &V_{IMPP} = V_{DRV}, 100 \text{ mV Drop} \\ &VIMPxHI \leq 10 \text{ V for } V_{DRV} = 10.5 \text{ V} \\ &VIMPxHI \leq 11.5 \text{ V for } V_{DRV} = 12.5 \text{ V} \end{split}$ | 10              | -    | -                 | μΑ   |

| V <sub>IMPDROL</sub>            | Driver Output Low Voltage                             | VIMPDRVx = VIMPN, IOL = -50 μA                                                                                                                                                                 | -               | -5   | -4.8              | V    |

|                                 | (Note 31)                                             | VIMPDRVx = GND, IOL = -100 μA                                                                                                                                                                  | -               | 0    | +0.1              | V    |

| T <sub>ZC_SU</sub>              | Start-Up Time (Note 11)                               | Charge Pump, No Load From IMPMEN to VIMPDRVx = 0.9 × VIMPLO or to VIMPDRVx = 0.9 × VIMPxHI                                                                                                     | -               | -    | 1                 | ms   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- 25. External Components: NMOS = BSZ22DN20N.

- 26. Valid For Fastest Rise/Fall Time Setting.

- 27. C<sub>LOAD</sub> = 1 nF, Rise and Fall Times Considered between 10% and 90% of PAVDD. 28. External Components: NMOS = BSZ440N10N, VIMPN and VIMPP C<sub>LOAD</sub> = 10 nF.

- 29. Charge Pump & All Drivers at no load.

- 30. Load equally distributed over the 3 impedance control drivers.

31. Current values are indicated for one single driver

# Table 9. ELECTRICAL CHARACTERISTICS: MISCELLANEOUS DRIVERS

(Min & Max Limits apply for  $T_A$  from  $-40^{\circ}C$  to  $+85^{\circ}C$ ;  $AV_{IN} = PV_{IN} = 12$  V. Typical values are given for  $T_A = +25^{\circ}C$  and default configuration. These conditions are true unless otherwise noted.)

| Symbol                            | Parameter                                         | Conditions                                                                      | Min                      | Тур   | Max                      | Unit |

|-----------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------|--------------------------|-------|--------------------------|------|

| RELAY DRIVE                       | R                                                 |                                                                                 | •                        | -     |                          |      |

| VINLDO                            | Operating Input Voltage Range (Note 11)           |                                                                                 | V <sub>PG</sub>          | _     | 5.5                      | V    |

| T <sub>ON</sub> /T <sub>OFF</sub> | Turn On/Off Delay                                 | From RLYEN to Relay<br>Driver Low Side<br>MOSFET On or Off<br>(100% Duty Cycle) | _                        | -     | 50                       | μs   |

| $R_{RLY}$                         | Relay Driver Impedance                            |                                                                                 | _                        | -     | 15                       | Ω    |

| $I_{RLY}$                         | Relay Driver Current Handling                     |                                                                                 | 50                       | -     | -                        | mA   |

| V <sub>Detect_Open</sub>          | Relay Open Detection                              | At RLYDRV                                                                       | -                        | 30    | -                        | mV   |

| TO <sub>RLY_Open</sub>            | Relay Open Timeout (Note 12)                      |                                                                                 | _                        | 80    | _                        | ms   |

| V <sub>OH_RLY</sub>               | Output Voltage High                               |                                                                                 | _                        | -     | 5.5                      | V    |

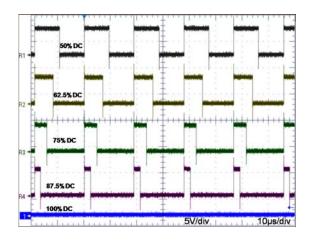

| F <sub>PWM</sub>                  | PWM Frequency (Note 12)                           | 27.12 MHz / 512                                                                 | _                        | 53    | -                        | kHz  |

| DC <sub>PWM</sub>                 | PWM Duty Cycle Range<br>(Note 12)                 |                                                                                 | 50                       | _     | 100                      | %    |

| $\Delta DC_{PWM}$                 | PWM Duty Cycle Granularity (Note 12)              |                                                                                 | -                        | 12.5  | -                        | %    |

| LED DRIVER                        | (LDIO1, LDIO2)                                    |                                                                                 |                          | •     |                          |      |

| VINLDO                            | Operating Input Voltage Range (Note 11)           |                                                                                 | V <sub>PG</sub>          |       | 5.5                      | V    |

| I <sub>LED</sub>                  | LED Current Range Programming                     | 3 bits                                                                          | 2.5                      | -     | 20                       | mA   |

| $\Delta I_{LED}$                  | LED Current Granularity                           |                                                                                 | _                        | 2.5   | _                        | mA   |

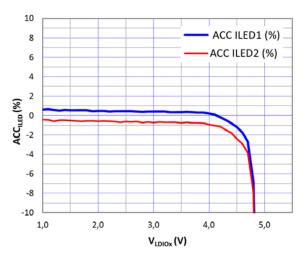

| ACC <sub>ILED</sub>               | LED Current Accuracy                              | VLED = 1.8 V                                                                    | -10                      | -     | +10                      | %    |

| M <sub>ILED</sub>                 | LED Current Matching                              | VLED = 1.8 V                                                                    | _                        | ±5    | -                        | %    |

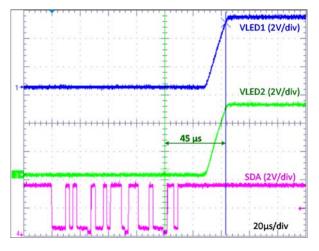

| SR <sub>ILED</sub>                | LED Current Slew Rate                             | 2.5 mA (10% – 90%)                                                              | _                        | 5     | -                        | μs   |

|                                   | (Note: Tested w/ a LED)                           | 20 mA (10% – 90%)                                                               | -                        | 20    | -                        | μs   |

| V <sub>OH_LDR</sub>               | LED Driver Output Voltage High<br>Level (Note 11) | 20 mA                                                                           | 1.2                      | -     | V <sub>INLDO</sub> – 1.0 | V    |

| V <sub>OPEN</sub>                 | LED Open Detect                                   |                                                                                 | V <sub>INLDO</sub> – 0.6 | -     | -                        | V    |

| V <sub>SC</sub>                   | LED Short Detect                                  |                                                                                 | _                        | -     | 1.0                      | V    |

| T <sub>ON_BLINK</sub>             | Blinking Pattern on Period                        | No Blinking (Note 32)                                                           | _                        | 0     | _                        | ms   |

|                                   | (Note 12)                                         | Very Short                                                                      | _                        | 250   | _                        | ms   |

|                                   |                                                   | Short                                                                           | -                        | 500   | _                        | ms   |

|                                   |                                                   | Long                                                                            | _                        | 1,000 | -                        | ms   |

| T <sub>REP_BLINK</sub>            | Blinking Pattern Repetition Rate                  | Very Fast                                                                       | _                        | 500   | -                        | ms   |

| _                                 | (Note 12)                                         | Fast                                                                            | _                        | 1,000 | -                        | ms   |

|                                   |                                                   | Slow                                                                            | _                        | 2,000 | -                        | ms   |

|                                   |                                                   | Very Slow                                                                       | _                        | 4,000 | -                        | ms   |

| ΔT <sub>ON/OFF</sub>              | Turn On/Off Delay (Note 11)                       | From LED Driver EN<br>(Through I <sup>2</sup> C bit<br>LDIOxCTRL)               | -                        | -     | 100                      | μs   |

# Table 9. ELECTRICAL CHARACTERISTICS: MISCELLANEOUS DRIVERS (continued)

(Min & Max Limits apply for  $T_A$  from  $-40^{\circ}$ C to  $+85^{\circ}$ C;  $AV_{IN} = PV_{IN} = 12$  V. Typical values are given for  $T_A = +25^{\circ}$ C and default configuration. These conditions are true unless otherwise noted.)

| Symbol               | Parameter                                         | Conditions                      | Min  | Тур  | Max  | Unit |  |  |  |

|----------------------|---------------------------------------------------|---------------------------------|------|------|------|------|--|--|--|

| USB BC 1.2 D         | USB BC 1.2 DETECT & QC 3.0 CONTROL (LDIO1, LDIO2) |                                 |      |      |      |      |  |  |  |

| VD <sub>SRC</sub>    | USB Source Voltage Low                            | I <sub>LOAD</sub> < 250 μA      | 0.5  | -    | 0.7  | V    |  |  |  |

| ID <sub>SINK</sub>   | USB Sink Current (Note 33)                        |                                 | 50   | -    | 150  | μΑ   |  |  |  |

| V <sub>DATREF</sub>  | USB Detect Voltage                                |                                 | 0.25 | -    | 0.35 | V    |  |  |  |

| VD <sub>UP</sub>     | USB Source Voltage High                           | From V <sub>LDO</sub> (Note 34) | 3.0  | 3.3  | 3.6  | V    |  |  |  |

| $RD_{UP}$            | USB Source Voltage High Serial<br>Resistance      | From VD <sub>UP</sub> to LDIO   | 0.90 | 1.24 | 1.57 | kΩ   |  |  |  |

| RD <sub>SRC</sub>    | USB Source Voltage Low Serial<br>Resistance       | From VD <sub>SRC</sub> to LDIO  | -    | 150  | -    | Ω    |  |  |  |

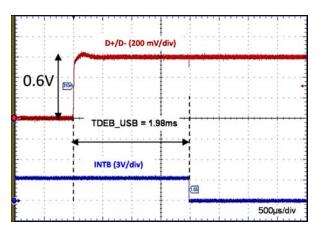

| T <sub>DEB_USB</sub> | USB Debounce Time (Note 12)                       |                                 | -    | 2    | -    | ms   |  |  |  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

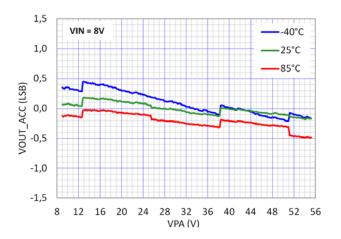

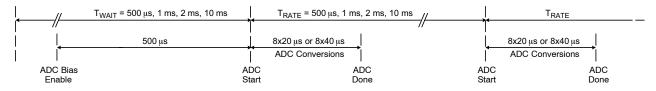

# Table 10. ELECTRICAL CHARACTERISTICS: ANALOG-TO-DIGITAL CONVERTER

(Min & Max Limits apply for T<sub>A</sub> from -40°C to +85°C; AV<sub>IN</sub> = PV<sub>IN</sub> = 12 V. Typical values are given for T<sub>A</sub> = +25°C and default configuration. These conditions are true unless otherwise noted.)

| Symbol                 | Parameter                                                                                       | Conditions                    | Min      | Тур   | Max       | Unit |

|------------------------|-------------------------------------------------------------------------------------------------|-------------------------------|----------|-------|-----------|------|

| ANALOG-TO              | -DIGITAL CONVERTER                                                                              |                               |          |       |           |      |

| VINLDO                 | Operating Input Voltage Range (Note 11)                                                         |                               | $V_{PG}$ | _     | 5.25      | V    |

| V <sub>ADC</sub>       | Reference Voltage                                                                               |                               | -        | 2.4   | -         | V    |

| F <sub>CLK_REF</sub>   | Reference Clock Frequency (Note 12)                                                             | 27.12 MHz / 14                | -        | 1.937 | _         | MHz  |

| V <sub>IN_adc</sub>    | Input Range                                                                                     | From Zero to Full<br>Scale    | 0        | -     | 2.4 – LSB | V    |

| LSB                    | Resolution                                                                                      | 10 bits                       | -        | 2.344 | _         | mV   |

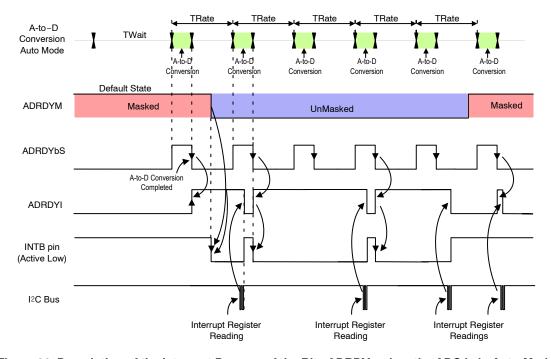

| T <sub>CONV</sub>      | Conversion Time (Note 12)                                                                       | Per Channel                   | -        | -     | 20        | μs   |

|                        |                                                                                                 | AC Power per<br>Configuration | -        | -     | 40        | μs   |

| T <sub>WAIT</sub>      | Conversion Request Wait Timer (Note 12)                                                         | Very Short                    | -        | 0.5   | _         | ms   |

|                        |                                                                                                 | Short                         | -        | 1     | -         | ms   |

|                        |                                                                                                 | Medium                        | _        | 2     | -         | ms   |

|                        |                                                                                                 | Long                          | -        | 10    | -         | ms   |

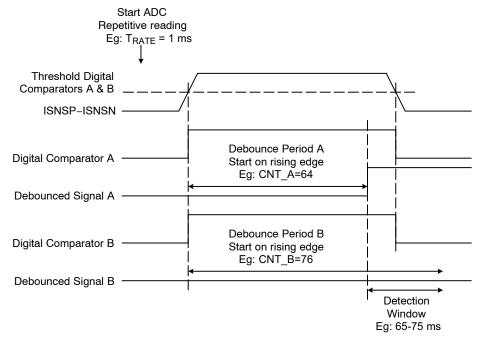

| T <sub>RATE</sub>      | Conversion Repetition Rate (Note 12)                                                            | Very Fast                     | _        | 0.5   | -         | ms   |

|                        |                                                                                                 | Fast                          | -        | 1     | _         | ms   |

|                        |                                                                                                 | Medium                        | -        | 2     | -         | ms   |

|                        |                                                                                                 | Slow                          | -        | 10    | _         | ms   |

| ERR <sub>Offset</sub>  | Offset Error (Note 11)                                                                          |                               | -        | _     | 1         | LSB  |

| ERR <sub>Gain</sub>    | Gain Error (Note 11)                                                                            |                               | -        | -     | 1.5       | LSB  |

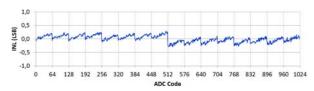

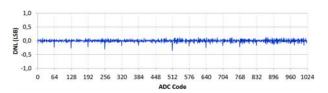

| INL                    | Integral Non-linearity (Note 11)                                                                |                               | -1.5     | -     | 1.5       | LSB  |

| DNL                    | Differential Non-linearity (Note 11)                                                            |                               | -1       | -     | 1         | LSB  |

| TUE                    | Total Unadjusted Error TUE = $\sqrt{(ERR_{Offset}^2 + ERR_{Gain}^2 + INL^2 + DNL^2)}$ (Note 35) |                               | -        | _     | +0.5      | %    |

| RangeD <sub>IG</sub> C | Digital Comparator Range                                                                        |                               | 0        | -     | 255       |      |

| LSBC                   | Digital Comparator Resolution                                                                   | 8 bits                        | -        | 9.375 | =         | mV   |

| CNT                    | Digital Comparator Counter                                                                      | 7 bits                        | 0        | _     | 127       |      |

<sup>32.</sup> The fourth setting of the blinking pattern will maintain the LED driver on (no Blinking).

<sup>33.</sup> Limits are applicable for the combined V<sub>DATREF</sub> and VD<sub>SRC</sub> ranges.

34. VD<sub>UP</sub> is based on the regulator output VLDO which has to be set equal to 3.3 V typically.

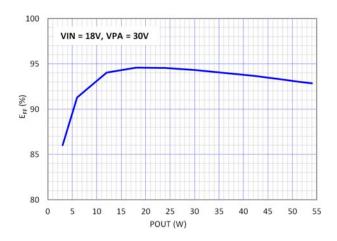

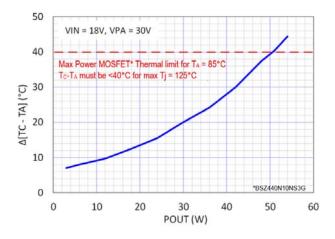

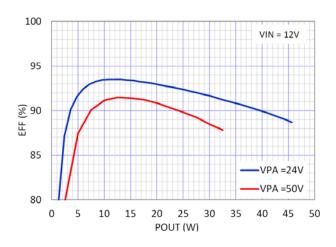

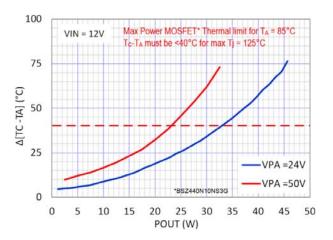

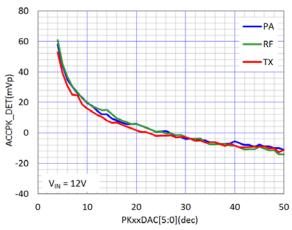

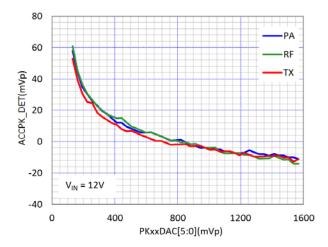

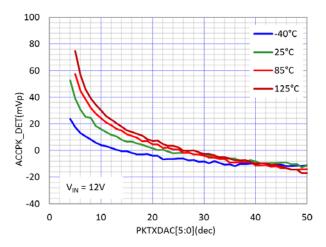

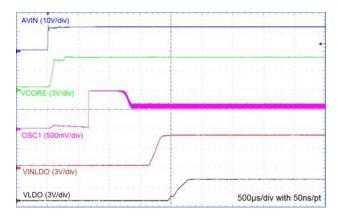

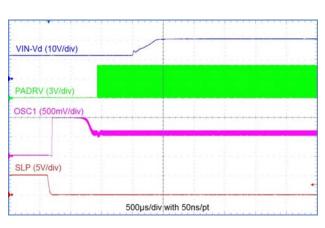

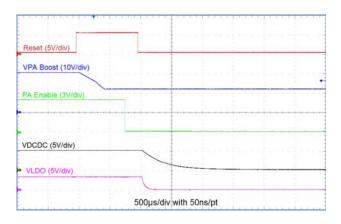

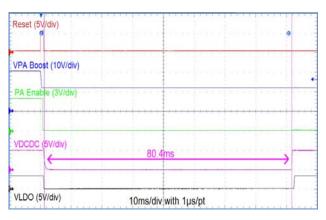

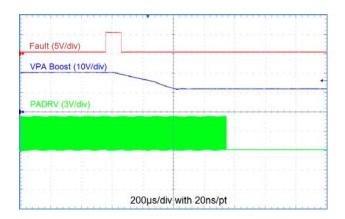

#### Table 10. ELECTRICAL CHARACTERISTICS: ANALOG-TO-DIGITAL CONVERTER (continued)