# Self-Protected High Side Driver With IDLE Mode & Analog Current Sense

## Product Preview **NCV84003G**

The NCV84003G is a fully protected single channel high side driver that can replace mechanical fuses and provide power in a smart power distribution architecture. It can also switch a wide variety of loads, such as bulk capacitors, bulbs, solenoids, and other actuators. The device incorporates advanced features designed for zonal applications such as a smart low power IDLE mode, a dedicated capacitive load charging mode, adjustable overcurrent thresholds and built-in  $I^2t$  profiles for fuse replacement. The device also features over-temperature shutdown with automatic latch-off. A Current Sense pin provides precision analog current monitoring of the output as well as fault indication.

### Features

- 5 V/3.3 V compatible control input

- Low standby current

- Smart Low Power IDLE Mode with extremely low operating current & auto transition to Normal Mode

- Dual-purpose IDLE status feedback and control

- Capacitive charge mode for active inrush management with auto-entry and exit

- Adjustable overcurrent threshold

- Adjustable Intelligent  $I^2t$  protection

- Absolute and Differential thermal shutdown

- Intelligent retry with latch off in fault state

- Proportional analog current sense output multiplexed with discrete fault output levels for fault differentiation

- Off State Open Load and Short Circuit to  $V_{BATT}$  Detection

- Under-voltage shutdown and Over-voltage protection

- Protection against loss of ground and loss of  $V_{BATT}$

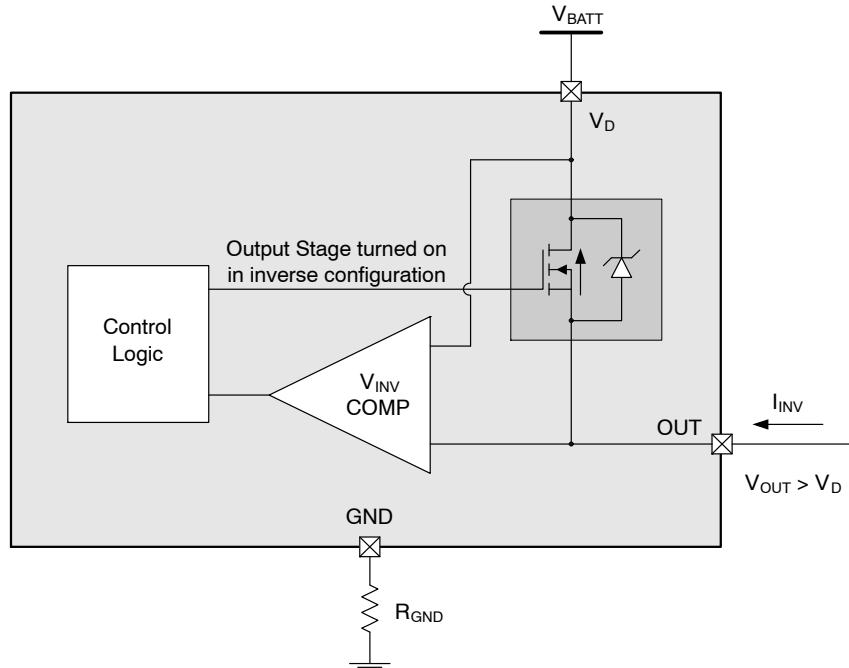

- Inverse Current protection with FET turn on in inverse mode

- ESD protection

- Reverse battery protection with external components

- AEC-Q100 qualified

### FEATURE SUMMARY

|                                                            |           |         |                  |

|------------------------------------------------------------|-----------|---------|------------------|

| Nominal Operating Voltage Range                            | $V_D$     | 6 to 18 | V                |

| $R_{ON}$ @ $T_J = 25^\circ\text{C}$                        | $R_{ON}$  | 3       | $\text{m}\Omega$ |

| Default Output Current Limit (typ)                         | $I_{lim}$ | 125     | A                |

| IDLE mode GND Operating Current @ $T_J = 85^\circ\text{C}$ | $I_{GND}$ | 80      | $\mu\text{A}$    |

This document contains information on a product under development. onsemi reserves the right to change or discontinue this product without notice.

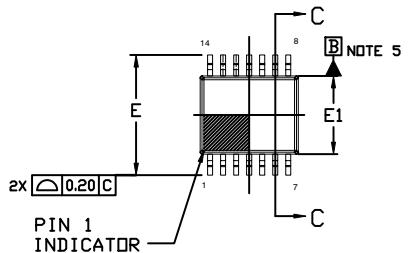

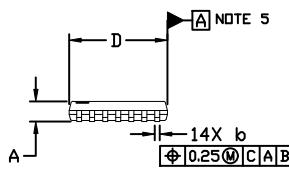

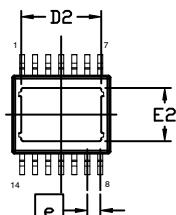

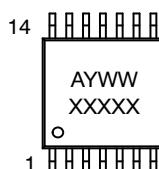

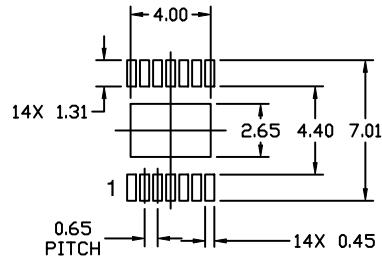

TSSOP14 EP

CASE 948BZ

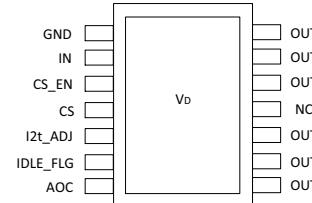

### PINOUT

### ORDERING INFORMATION

| Device    | Package                 | Shipping <sup>†</sup> |

|-----------|-------------------------|-----------------------|

| NCV84003G | TSSOP14-EP<br>(Pb-Free) | XXX                   |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

### Typical Applications

- Replace fuses in zonal car platforms

- Power on Bulk Capacitors, Resistive, and Inductive Loads

- Automotive / Industrial

Table 1. PIN DESCRIPTIONS

| Pin #        | Symbol               | Description                               |

|--------------|----------------------|-------------------------------------------|

| 1            | GND                  | Ground Reference                          |

| 2            | IN                   | Logic Level Input for Output Activation   |

| 3            | CS_EN                | Logic Level Input for Diagnosis Enable    |

| 4            | CS                   | Current Sense/Diagnostic Output           |

| 5            | I <sup>2</sup> t_ADJ | Adjustable I <sup>2</sup> t Profile Input |

| 6            | IDLE_FLG             | IDLE State Flag for MCU                   |

| 7            | AOC                  | Adjustable Over-Current Threshold Input   |

| 11           | NC                   | No Connect                                |

| 08-10, 12-14 | OUT                  | Output                                    |

| E-pad        | VD                   | Battery Connection                        |

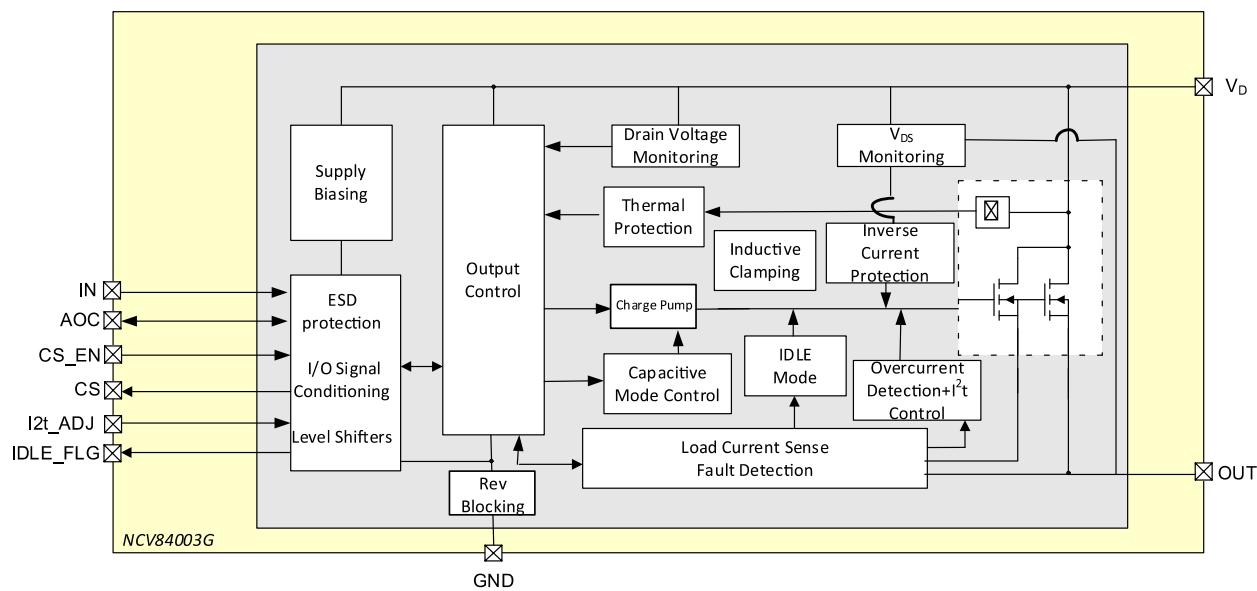

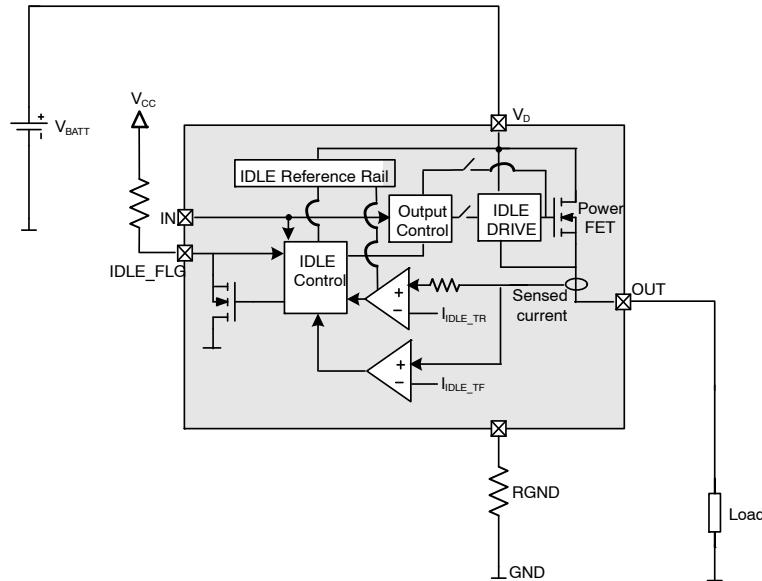

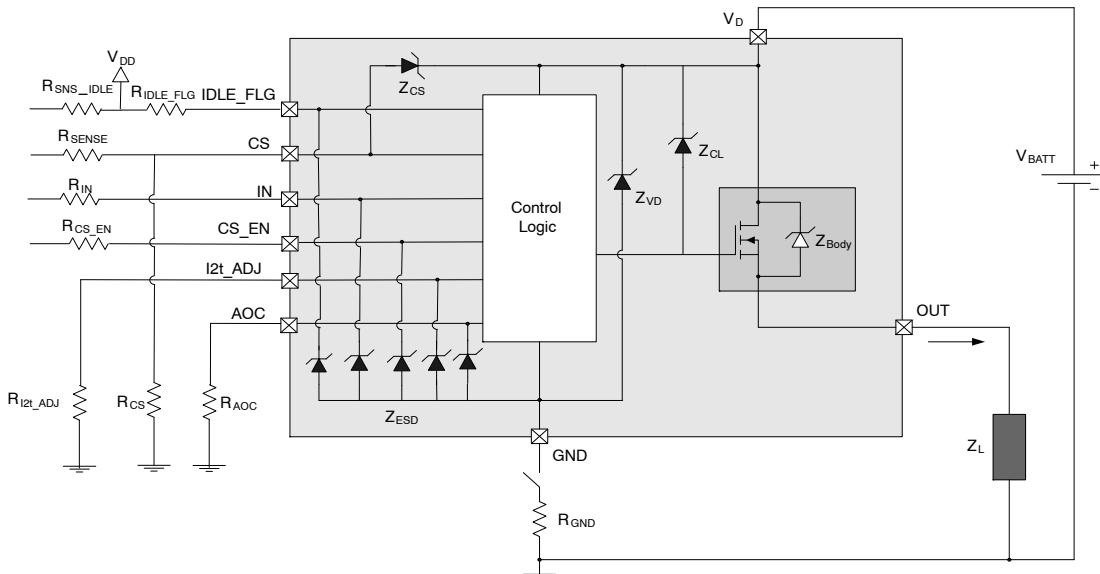

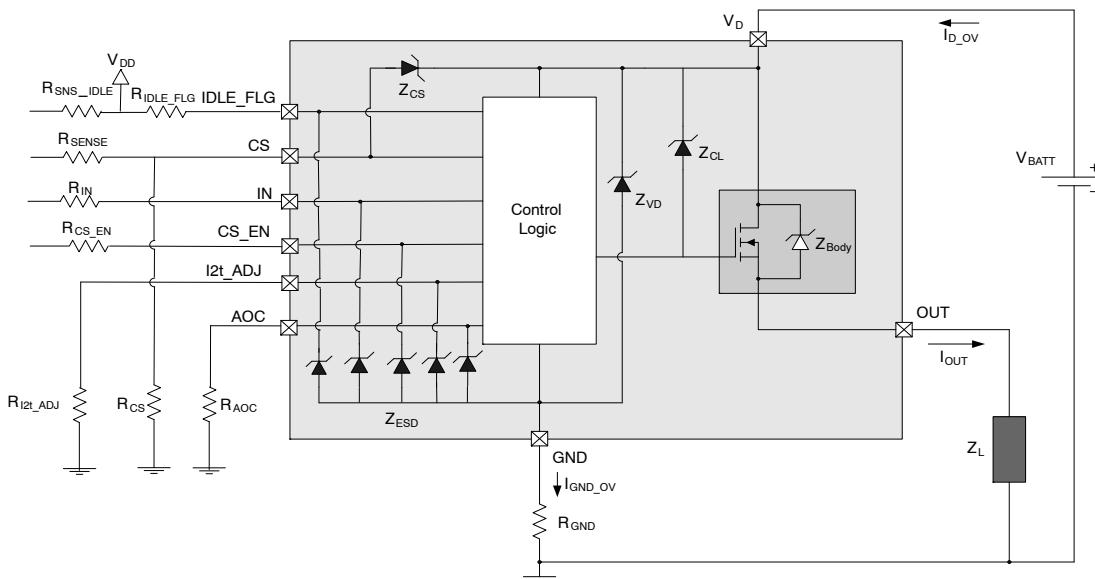

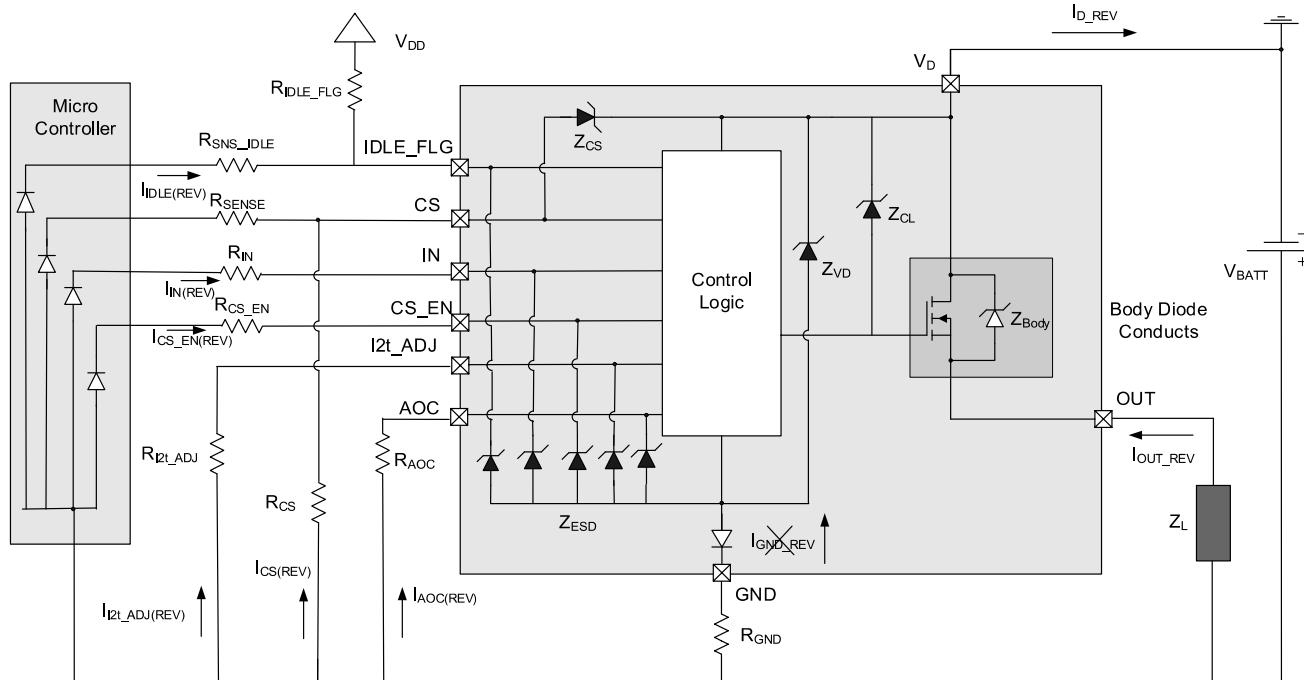

Figure 1. Block Diagram

# NCV84003G

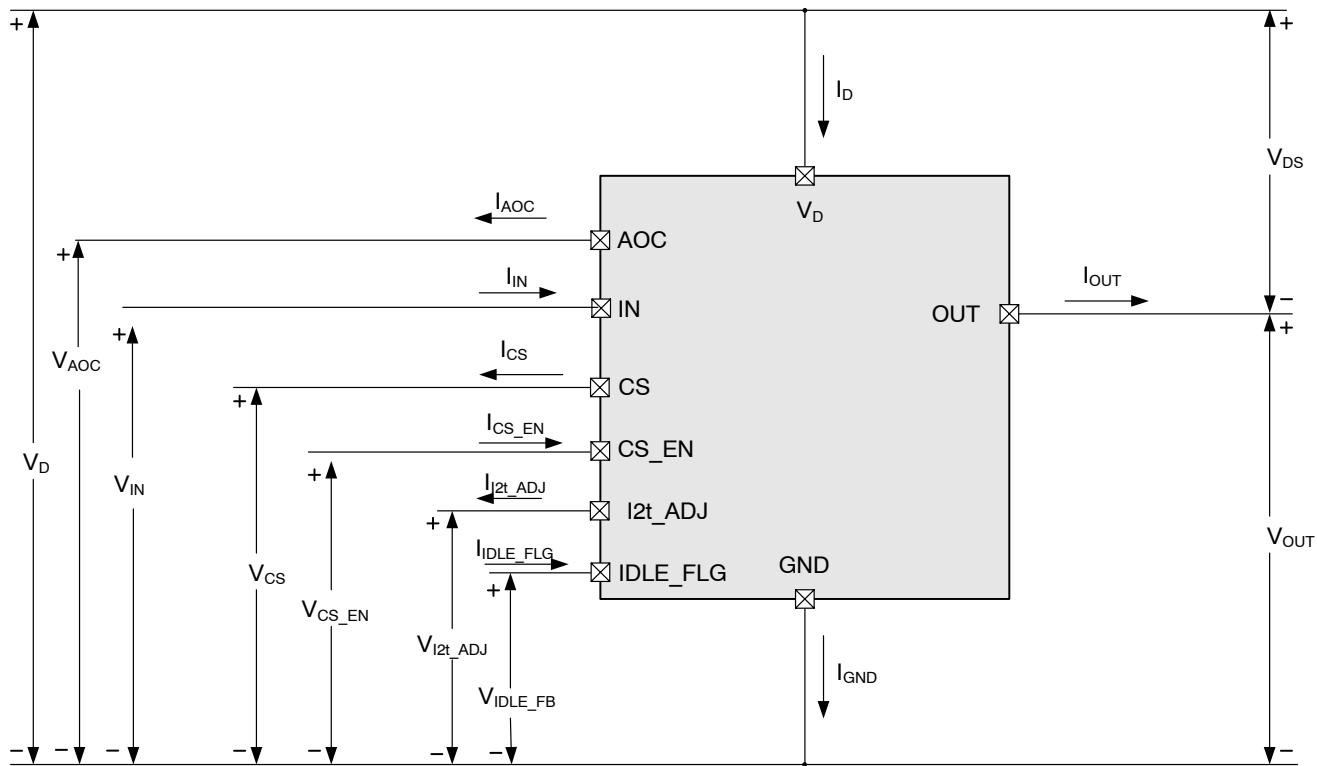

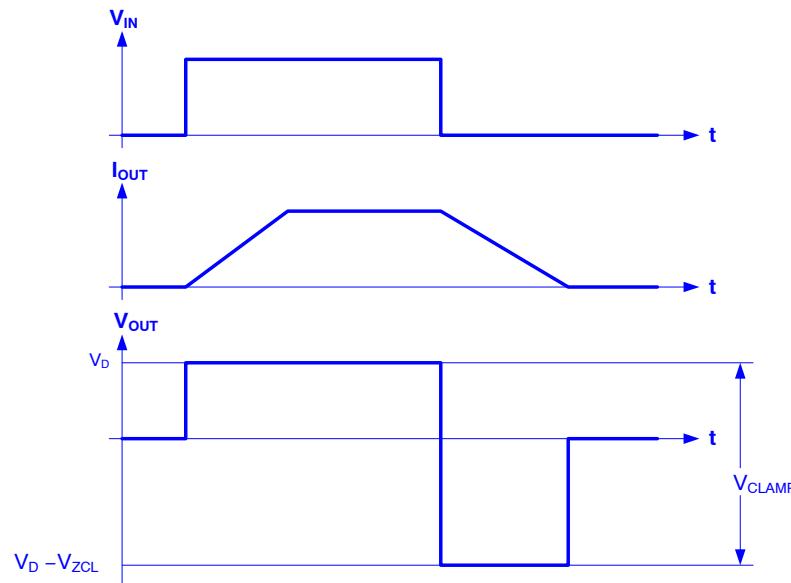

Figure 2. Voltage and Current Definitions

## Electrical Specifications

**Table 2. MAXIMUM RATINGS** (Note 1)-40°C ≤ T<sub>J</sub> ≤ 150°C unless otherwise specified

| Rating                                                                                                                                        | Symbol                      | Value           |                            | Unit        |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|----------------------------|-------------|

|                                                                                                                                               |                             | Min             | Max                        |             |

| <b>GENERAL</b>                                                                                                                                |                             |                 |                            |             |

| Supply Voltage (Note 2)                                                                                                                       | V <sub>D</sub>              | -0.3            | 28                         | V           |

| Supply Voltage for Load Dump Protection                                                                                                       | V <sub>D_LD</sub>           |                 | 35                         | V           |

| Supply Voltage for Short Circuit Protection                                                                                                   | V <sub>D_SC</sub>           | 0               | 24                         | V           |

| Reverse Polarity Voltage, t < 2 min, load : 2 Ω, Setup : Refer to Figure 19                                                                   | V <sub>D_REV</sub>          | 0               | 16                         | V           |

| <b>SHORT CIRCUIT CAPABILITY</b>                                                                                                               |                             |                 |                            |             |

| Repetitive Short Circuit Capability per AEC Q100-12, LSC and TSC, 100 ppm, 300 ms                                                             | RSC                         | 1000<br>Grade A | -                          | k<br>cycles |

| <b>DIGITAL INPUT PINS: IN, CS_EN</b>                                                                                                          |                             |                 |                            |             |

| Current at Input Pins                                                                                                                         | I <sub>DIG_IN_MAX</sub>     | -1              | 1                          | mA          |

| Current at Input Pins in Rev Battery, t < 2 min                                                                                               | I <sub>DIG_IN_MAX_REV</sub> | -1              | 10                         | mA          |

| Voltage at Input Pins                                                                                                                         | V <sub>DIG_IN_MAX</sub>     | -0.3            | 6.5                        | V           |

| <b>IDLE_FLG PIN</b>                                                                                                                           |                             |                 |                            |             |

| Current at IDLE_FLG Pin                                                                                                                       | I <sub>IDLE_MAX</sub>       | -1              | 1                          | mA          |

| Current at IDLE_FLG Pin in Rev Battery, t < 2 min                                                                                             | I <sub>IDLE_MAX_REV</sub>   | -1              | 10                         | mA          |

| Voltage at IDLE_FLG Pin                                                                                                                       | V <sub>IDLE_MAX</sub>       | -0.3            | 6.5                        | V           |

| <b>CURRENT SENSE OUTPUT</b>                                                                                                                   |                             |                 |                            |             |

| Current at Current Sense Output                                                                                                               | I <sub>CS_MAX</sub>         | -25             | I <sub>CS_Fault_ILIM</sub> | mA          |

| Voltage at Current Sense Output                                                                                                               | V <sub>CS_MAX</sub>         | -0.3            | V <sub>D</sub>             | V           |

| <b>ANALOG INPUT PINS: AOC PIN, I2T_ADJ PIN</b>                                                                                                |                             |                 |                            |             |

| Current at input pin                                                                                                                          | I <sub>ANA_IN_MAX</sub>     | -1              | 1                          | mA          |

| Voltage at input pin                                                                                                                          | V <sub>ANA_IN_MAX</sub>     | -0.3            | 6.5                        | V           |

| <b>OUTPUTS</b>                                                                                                                                |                             |                 |                            |             |

| Power Dissipation T <sub>A</sub> = 85°C, T <sub>J</sub> = 150°C (Note 5)                                                                      | P <sub>MAX</sub>            |                 | 3                          | W           |

| Drain-Source Voltage at Power Transistor                                                                                                      | V <sub>DS_MAX</sub>         |                 | V <sub>ZCL</sub>           | V           |

| Single Pulse Inductive Load Switching Energy<br>(L = 1 mH, V <sub>D</sub> = 13.5 V, I <sub>L_PEAK</sub> = 6.5 A, T <sub>JSTART</sub> = 150°C) | E <sub>AS</sub>             | TBD             |                            | mJ          |

| <b>GROUND TERMINAL</b>                                                                                                                        |                             |                 |                            |             |

| Current through GND pin                                                                                                                       | I <sub>GND</sub>            | -50             | 50                         | mA          |

| <b>TEMPERATURES</b>                                                                                                                           |                             |                 |                            |             |

| Operating Junction Temperature                                                                                                                | T <sub>J</sub>              | -40             | 150                        | °C          |

| Storage Temperature                                                                                                                           | T <sub>J_storage</sub>      | -55             | 150                        | °C          |

**Table 2. MAXIMUM RATINGS** (Note 1)

$-40^\circ\text{C} \leq T_J \leq 150^\circ\text{C}$  unless otherwise specified

| Rating                                               | Symbol                     | Value |     | Unit |

|------------------------------------------------------|----------------------------|-------|-----|------|

|                                                      |                            | Min   | Max |      |

| <b>ESD</b>                                           |                            |       |     |      |

| ESD Susceptibility all pins HBM                      | $V_{\text{ESD\_HBM}}$      | -2    | +2  | kV   |

| ESD Susceptibility OUTx to GND, $V_D$ connected, HBM | $V_{\text{ESD\_OUT\_HBM}}$ | -4    | 4   | kV   |

| ESD Susceptibility all pins CDM                      | $V_{\text{ESD\_CDM}}$      | -500  | 500 | V    |

| ESD Susceptibility pin (corner pins), CDM            | $V_{\text{ESD\_NC}}$       | -750  | 750 | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Not subject to production testing.

2. For transient application only. Extended operation at absolute maximum voltage may affect device reliability.

3. HBM test setup per AEC-Q100:EIA-JESD22-A114-B.

4. CDM test setup per AEC-Q100:EIA-JESD22-C101-A.

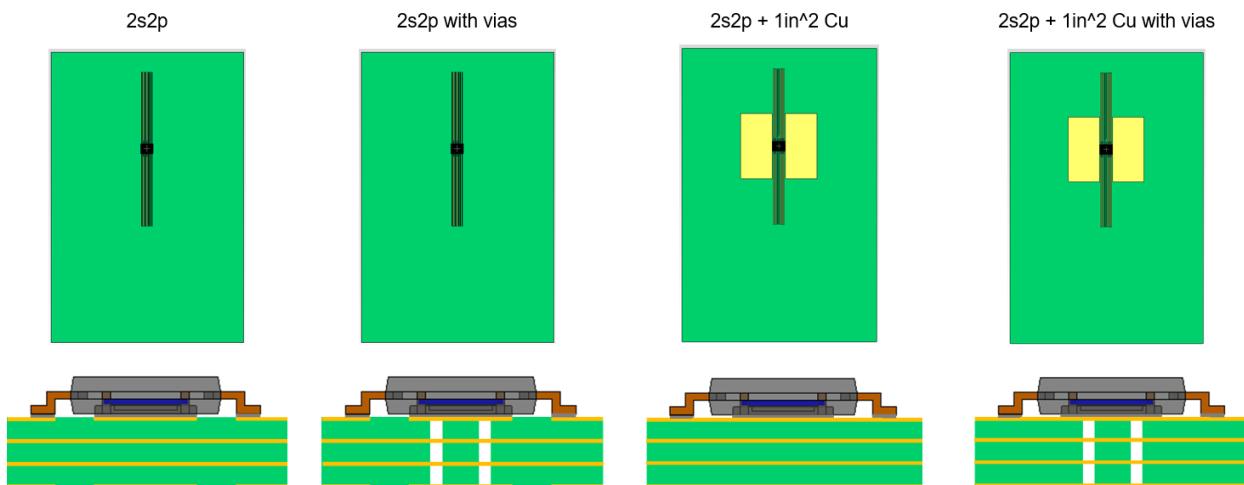

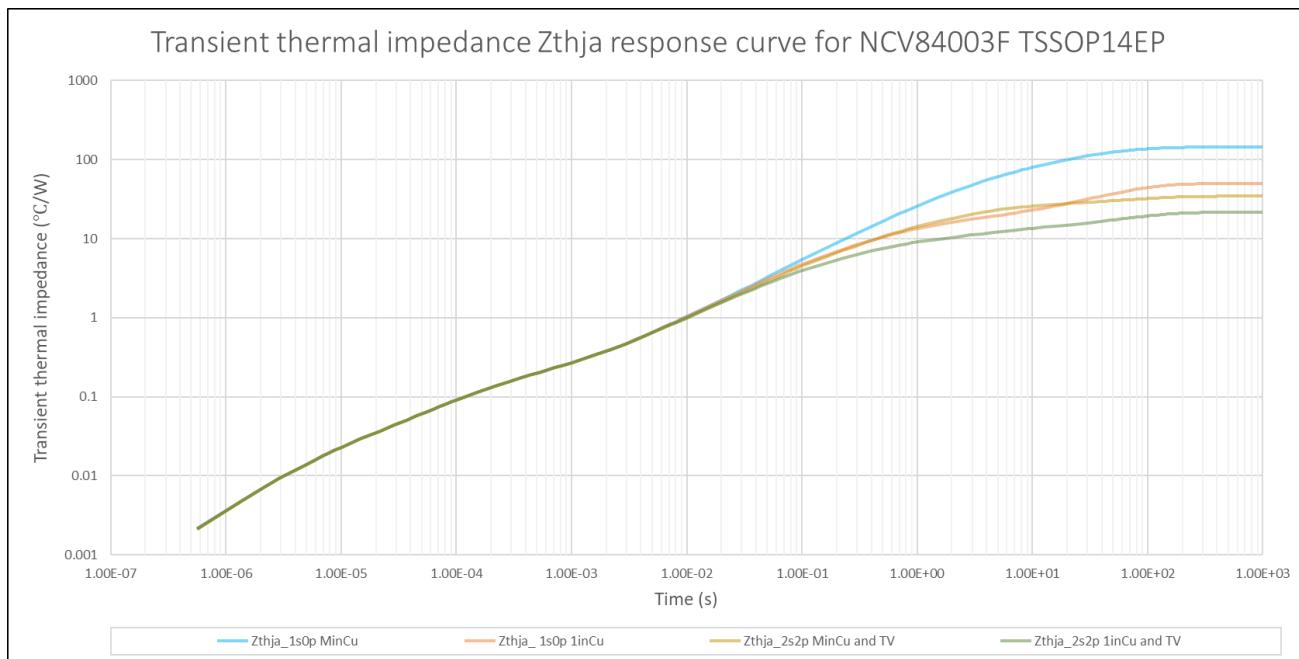

5. Board construction based on JEDEC JESD 51-7 for a four layer 2s2p board with forced air convection. Vias were added under the exposed pad as shown in Figure 3.

**Table 3. THERMAL RESISTANCE RATINGS**

| Parameter                                                | Symbol                 | Max Value | Unit                      |

|----------------------------------------------------------|------------------------|-----------|---------------------------|

| Thermal Resistance                                       |                        |           |                           |

| Junction-to-Top (Note 6)                                 | $P_{\text{Si\_JT}}$    | 1.7       | $^\circ\text{C}/\text{W}$ |

| Junction-to-EPAD (Note 6)                                | $P_{\text{Si\_e-PAD}}$ | 0.27      | $^\circ\text{C}/\text{W}$ |

| Junction-to-Ambient - 1s0p min pad (Note 6)              | $R_{\text{thJA}}$      | 144       | $^\circ\text{C}/\text{W}$ |

| Junction-to-Ambient - 1s0p +1in <sup>2</sup> Cu (Note 6) | $R_{\text{thJA}}$      | 50        | $^\circ\text{C}/\text{W}$ |

| Junction-to-Ambient - 2s2p min pad (Note 7)              | $R_{\text{thJA}}$      | 34        | $^\circ\text{C}/\text{W}$ |

| Junction-to-Ambient - 2s2p +1in <sup>2</sup> Cu (Note 7) | $R_{\text{thJA}}$      | 22        | $^\circ\text{C}/\text{W}$ |

6. Board construction based on JEDEC JESD 51-3 for a single layer 1s0p board with forced air convection.

7. Board construction based on JEDEC JESD 51-7 for a four layer 2s2p board with forced air convection. Vias were added under the exposed pad as shown below.

**Figure 3. Board Construction for Thermal Performance**

**Table 4. SUPPLY ELECTRICAL CHARACTERISTICS** ( $6 \leq V_D \leq 18 \text{ V}$ ;  $-40^\circ\text{C} \leq T_J \leq 150^\circ\text{C}$  unless otherwise specified)Typical Values measured @  $V_D = 13.5 \text{ V}$ ,  $T_J = 25^\circ\text{C}$

| Rating                                                   | Symbol                  | Conditions                                                                                                                                                                                                               | Value |      |     | Unit |

|----------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-----|------|

|                                                          |                         |                                                                                                                                                                                                                          | Min   | Typ  | Max |      |

| Nominal Supply Voltage Range (Note 8)                    | $V_{D\_NOM}$            |                                                                                                                                                                                                                          | 6     | 13.5 | 18  | V    |

| Extended Supply Voltage Range (Notes 8, 9)               | $V_{DS\_EX}$            | $V_{IN} = 5 \text{ V}$ , $R_L = 4 \Omega$ , $3.1 \text{ V} \leq V_D \leq 28 \text{ V}$<br>Ramp down $V_D$ from 28 V to 3.1 V                                                                                             |       |      | 0.5 | V    |

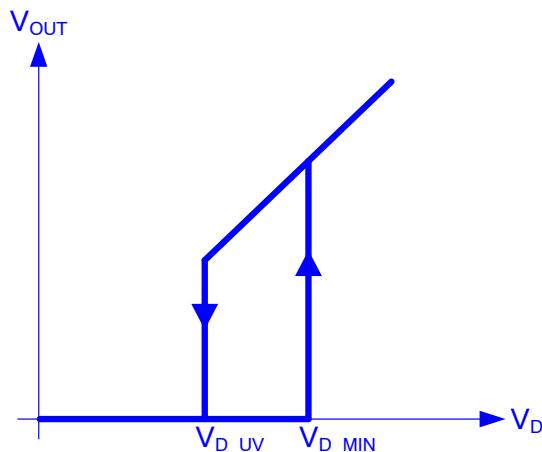

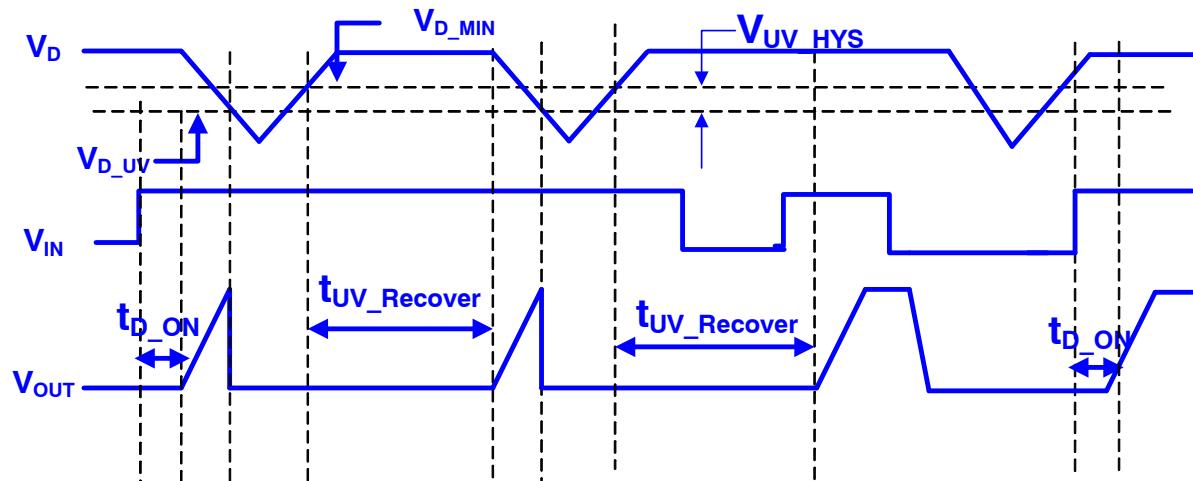

| Under Voltage Shutdown                                   | $V_{D\_UV}$             | $V_{IN} = 5 \text{ V}$ , $V_D$ Falling,<br>From $V_{DS} < 0.5 \text{ V}$ to $I_{OUT} = 0$                                                                                                                                | 2.4   | 2.9  | 3.1 | V    |

| Minimum Operating Voltage                                | $V_{D\_MIN}$            | $V_{IN} = 5 \text{ V}$ , $V_D$ Rising,<br>From $I_{OUT} = 0$ to $V_{DS} < 0.5 \text{ V}$                                                                                                                                 | 2.9   | 3.4  | 4.1 | V    |

| Under Voltage Shutdown Hysteresis                        | $V_{D\_UV\_HYS}$        |                                                                                                                                                                                                                          |       | 0.5  |     | V    |

| Supply Undervoltage Recovery Time – Normal Mode (Note 8) | $t_{UV\_Recover\_Norm}$ | $V_{CS\_EN} = 5 \text{ V}$ , $V_{IN} = 0 \text{ V} \rightarrow 5 \text{ V}$ after $t > t_{Norm}$ , $V_D$ Rising,<br>From $V_D = 0 \text{ V} \rightarrow V_D \geq V_{D\_MIN}$ to $V_{DS} < 0.5 \text{ V}$ (See Figure 17) | 2.5   | 5    | 7.5 | ms   |

| Supply Undervoltage Recovery Time – CL Mode (Note 8)     | $t_{UV\_Recover\_CL}$   | $V_{CS\_EN} = V_{IN} = 0 \text{ V}$ 5 V, $V_D$ Rising,<br>From $V_D = 0 \text{ V} \rightarrow V_D \geq V_{D\_MIN}$ to $V_{DS} < 0.5 \text{ V}$ (See Figure 17)                                                           | 250   | 500  | 750 | μs   |

| Quiescent Current                                        | $I_{Q\_85}$             | $V_D = 18 \text{ V}$ , $T_J \leq 85^\circ\text{C}$ ,<br>$V_{IN} = V_{CS\_EN} = 0 \text{ V}$ , $V_{OUT} = 0 \text{ V}$                                                                                                    |       |      | 500 | nA   |

| Quiescent Current                                        | $I_{Q\_150}$            | $V_D = 18 \text{ V}$ , $T_J = 150^\circ\text{C}$ ,<br>$V_{IN} = V_{CS\_EN} = 0 \text{ V}$ , $V_{OUT} = 0 \text{ V}$                                                                                                      |       | 5    | 20  | μA   |

| Quiescent Current, Diagnostic Active                     | $I_{Q\_DIAG}$           | $V_D = 18 \text{ V}$ , $V_{IN} = 0 \text{ V}$ , $V_{CS\_EN} = 5 \text{ V}$                                                                                                                                               |       | 1.8  | 2.4 | mA   |

| Normal Operating Current                                 | $I_{GND\_ON}$           | $V_D = 18 \text{ V}$ , $V_{IN} = V_{CS\_EN} = 5 \text{ V}$ ,<br>$V_{CS} < 5 \text{ V}$                                                                                                                                   |       | 5    | 6   | mA   |

| Operating Current in IDLE Mode                           | $I_{GND\_IDLE}$         | $V_D = 18 \text{ V}$ , $V_{IN} = 5 \text{ V}$ , $V_{CS\_EN} = 0 \text{ V}$ ,<br>$I_{OUT} = 0.5 \text{ A}$ , $T_J \leq 85^\circ\text{C}$                                                                                  |       |      | 80  | μA   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

8. Not subject to production testing.

9. Extended operation outside the nominal supply voltage range may affect device reliability. Parametric performance not guaranteed.

**Table 5. POWER OUTPUT ELECTRICAL CHARACTERISTICS** ( $6 \leq V_D \leq 18 \text{ V}$ ;  $-40^\circ\text{C} \leq T_J \leq 150^\circ\text{C}$  unless otherwise specified)

Typical Values measured @  $V_D = 13.5 \text{ V}$ ,  $T_J = 25^\circ\text{C}$

| Rating                                               | Symbol             | Conditions                                                                                | Value |     |     | Unit                   |

|------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------|-------|-----|-----|------------------------|

|                                                      |                    |                                                                                           | Min   | Typ | Max |                        |

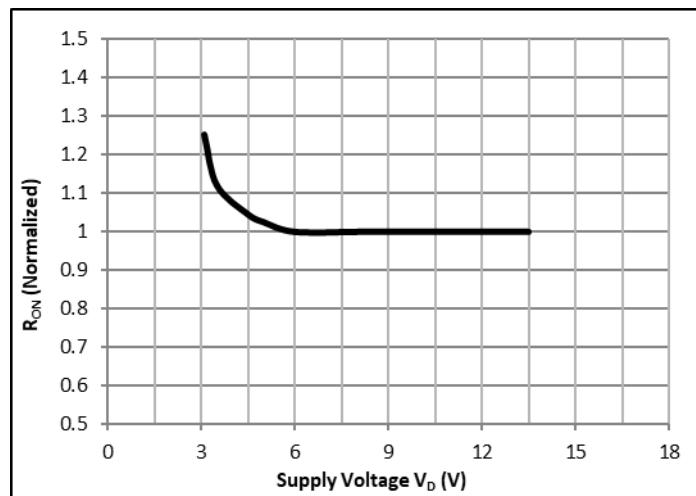

| On-state Resistance                                  | $R_{ON\_25}$       | $I_{OUT} = I_{NOM} = 15 \text{ A}$ , $V_{IN} = 5 \text{ V}$ , $T_J = 25^\circ\text{C}$    |       | 3   |     | $\text{m}\Omega$       |

| On-state Resistance                                  | $R_{ON\_150}$      | $I_{OUT} = I_{NOM} = 15 \text{ A}$ , $V_{IN} = 5 \text{ V}$ , $T_J = 150^\circ\text{C}$   |       |     | 5   | $\text{m}\Omega$       |

| On-state Resistance – Low Voltage                    | $R_{ON\_LV}$       | $I_{OUT} = 2 \text{ A}$ , $V_D = 3.4 \text{ V}$ , $T_J = 150^\circ\text{C}$               |       |     | 6   | $\text{m}\Omega$       |

| On-state Resistance – Inverse Current                | $R_{ON\_INV\_25}$  | $I_{OUT} = -4 \text{ A}$ , $V_D = 13.5 \text{ V}$ , $T_J = 25^\circ\text{C}$              |       | 3   |     | $\text{m}\Omega$       |

| On-state Resistance – Inverse Current                | $R_{ON\_INV\_150}$ | $I_{OUT} = -4 \text{ A}$ , $V_D = 13.5 \text{ V}$ , $T_J = 150^\circ\text{C}$             |       |     | 6   | $\text{m}\Omega$       |

| On-state Resistance – IDLE Mode                      | $R_{ON\_IDLE\_85}$ | $I_{OUT} = 0.5 \text{ A}$ , $V_D = 13.5 \text{ V}$ , $T_J \leq 85^\circ\text{C}$          |       |     | 300 | $\text{m}\Omega$       |

| Normal Mode Threshold                                | $V_{DS\_Norm}$     | $V_{IN} = 0 \text{ V}$ , $V_{CS\_EN} = 5 \text{ V}$                                       |       | 1   |     | $\text{V}$             |

| Output Leakage Current                               | $I_{LEAK\_85}$     | $V_{IN} = V_{CS\_EN} = 0 \text{ V}$ , $V_{OUT} = 0 \text{ V}$ , $T_J < 85^\circ\text{C}$  |       |     | 0.5 | $\mu\text{A}$          |

| Output Leakage Current                               | $I_{LEAK\_150}$    | $V_{IN} = V_{CS\_EN} = 0 \text{ V}$ , $V_{OUT} = 0 \text{ V}$ , $T_J < 150^\circ\text{C}$ |       |     | 15  | $\mu\text{A}$          |

| IDLE Mode Enable Threshold – Falling                 | $I_{IDLE\_TF}$     | $V_{IN} = 5 \text{ V}$ , $V_{IDLE\_FLG} = \text{Low} \rightarrow \text{High}$             | 1.3   | 1.5 | 1.7 | $\text{A}$             |

| IDLE Mode Disable Threshold – Rising                 | $I_{IDLE\_TR}$     | $V_{IN} = 5 \text{ V}$ , $V_{IDLE\_FLG} = \text{High} \rightarrow \text{Low}$             | 1.8   | 2.5 | 3.5 | $\text{A}$             |

| Drain-to-Source Clamping Voltage ( $V_D - V_{OUT}$ ) | $V_{ZCL}$          | $I_{OUT} = 5 \text{ mA}$ , $V_{IN} = 0 \text{ V}$                                         | 35    | 36  | 39  | $\text{V}$             |

| Body Diode Forward Voltage                           | $V_F$              | $I_{OUT} = -1 \text{ A}$ , $T_J = 150^\circ\text{C}$ ,<br>$V_F = V_{OUT} - V_D$           |       |     | 0.7 | $\text{V}$             |

| OUT slew in H-Bridge Configuration (Note 10)         | $ dV_{OUT}/dt $    |                                                                                           |       |     | 10  | $\text{V}/\mu\text{s}$ |

10. Not subject to production testing.

**Input Pins**

All low-voltage control inputs are compatible with 3.3 V and 5 V microcontroller supply voltages. All inputs comprise of a voltage Schmitt-trigger circuit to enable direct drive from voltage sources and prevent uncontrolled

oscillations due to slow transitions at the inputs. Each input features a pull-down element to prevent uncontrolled input states in case of an open pin condition. Unused inputs should be left open or connected to device GND through a 4.7 k $\Omega$  resistor.

**Table 6. DIGITAL INPUT (IN, CS\_EN), AND IDLE\_FLG PIN CHARACTERISTICS**(6  $\leq$  V<sub>D</sub>  $\leq$  18 V; -40°C  $\leq$  T<sub>J</sub>  $\leq$  150°C unless otherwise specified)

| Rating                           | Symbol                    | Conditions                                                              | Value |      |     | Unit    |

|----------------------------------|---------------------------|-------------------------------------------------------------------------|-------|------|-----|---------|

|                                  |                           |                                                                         | Min   | Typ  | Max |         |

| Low Level Digital Input Voltage  | V <sub>DIG_IN_L</sub>     |                                                                         |       |      | 0.8 | V       |

| High Level Digital Input Voltage | V <sub>DIG_IN_H</sub>     |                                                                         | 2     |      |     | V       |

| Digital Input Voltage Hysteresis | V <sub>DIG_IN_HYS</sub>   |                                                                         |       | 0.25 |     | V       |

| Digital Input Pull-down Current  | I <sub>IN_PD</sub>        | 0.8 V $\leq$ V <sub>IN</sub> $\leq$ 2 V                                 | 1     |      | 25  | $\mu$ A |

| IDLE_FLG Pin Output Voltage Low  | V <sub>IDLE_low</sub>     | I <sub>IDLE_FLG</sub> = 0.5 mA                                          |       | 0.2  | 0.5 | V       |

| IDLE_FLG Pin Leakage Current     | I <sub>IDLE_leakage</sub> | V <sub>IDLE_FLG</sub> = 5 V, V <sub>IN</sub> = V <sub>CS_EN</sub> = 0 V |       | 0.5  | 2   | $\mu$ A |

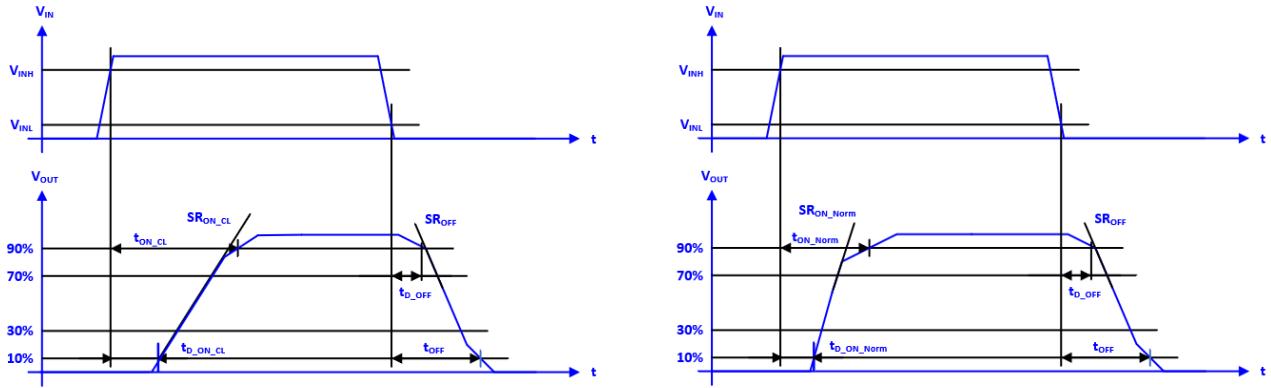

**Table 7. SWITCHING CHARACTERISTICS** (6  $\leq$  V<sub>D</sub>  $\leq$  18 V; -40°C  $\leq$  T<sub>J</sub>  $\leq$  150°C unless otherwise specified) (See Figure 11)

| Rating                                                                                                      | Symbol                       | Conditions                                                                                                                          | Value |      |       | Unit       |

|-------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------|

|                                                                                                             |                              |                                                                                                                                     | Min   | Typ  | Max   |            |

| Turn ON Delay – CL Mode (V <sub>IN</sub> Lo $\rightarrow$ Hi to V <sub>OUT</sub> = 10% V <sub>D</sub> )     | t <sub>D_ON_CL</sub>         | V <sub>D</sub> = 13.5 V, R <sub>L</sub> = 2 $\Omega$                                                                                | 80    | 200  | 400   | $\mu$ s    |

| Turn ON Time – CL Mode (V <sub>IN</sub> Lo $\rightarrow$ Hi to V <sub>OUT</sub> = 90% V <sub>D</sub> )      | t <sub>ON_CL</sub>           |                                                                                                                                     | 200   | 700  | 1200  | $\mu$ s    |

| Turn ON Delay – Normal Mode (V <sub>IN</sub> Lo $\rightarrow$ Hi to V <sub>OUT</sub> = 10% V <sub>D</sub> ) | t <sub>D_ON_Norm</sub>       |                                                                                                                                     | 20    | 70   | 140   | $\mu$ s    |

| Turn ON Time – Normal Mode (V <sub>IN</sub> Lo $\rightarrow$ Hi to V <sub>OUT</sub> = 90% V <sub>D</sub> )  | t <sub>ON_Norm</sub>         |                                                                                                                                     | 50    | 130  | 200   | $\mu$ s    |

| Turn OFF Delay (V <sub>IN</sub> Hi $\rightarrow$ Lo to V <sub>OUT</sub> = 90% V <sub>D</sub> )              | t <sub>D_OFF</sub>           |                                                                                                                                     | 10    | 50   | 130   | $\mu$ s    |

| Turn OFF time (V <sub>IN</sub> Hi $\rightarrow$ Lo to V <sub>OUT</sub> = 10% V <sub>D</sub> )               | t <sub>OFF</sub>             |                                                                                                                                     | 30    | 100  | 200   | $\mu$ s    |

| Turn ON / OFF Matching – Normal Mode: t <sub>ON</sub> – t <sub>OFF</sub>                                    | $\Delta$ t <sub>ON-OFF</sub> |                                                                                                                                     | -20   | 20   | 60    | $\mu$ s    |

| Slew Rate ON – CL Mode (V <sub>OUT</sub> = 30% to 70% V <sub>D</sub> )                                      | SR <sub>ON_CL</sub>          |                                                                                                                                     | 0.015 | 0.03 | 0.045 | V/ $\mu$ s |

| Slew Rate ON – Normal Mode (V <sub>OUT</sub> = 30% to 70% V <sub>D</sub> )                                  | SR <sub>ON_Norm</sub>        |                                                                                                                                     | 0.15  | 0.3  | 0.45  | V/ $\mu$ s |

| Slew Rate OFF (V <sub>OUT</sub> = 70% to 30% V <sub>D</sub> )                                               | SR <sub>OFF</sub>            |                                                                                                                                     | -0.45 | -0.3 | -0.15 | V/ $\mu$ s |

| Slew Rate Matching Normal Mode: SR <sub>ON_Norm</sub> – SR <sub>OFF</sub>                                   | $\Delta$ SR                  |                                                                                                                                     | -0.15 | 0    | 0.15  | V/ $\mu$ s |

| Turn ON Energy – Normal Mode (Note 11)                                                                      | W <sub>ON</sub>              | V <sub>D</sub> = 18 V, R <sub>L</sub> = 2 $\Omega$ , V <sub>OUT</sub> : 10% V <sub>D</sub> $\longleftrightarrow$ 90% V <sub>D</sub> |       | 1.5  |       | mJ         |

| Turn OFF Energy – Normal Mode (Note 11)                                                                     | W <sub>OFF</sub>             |                                                                                                                                     |       | 1.5  |       | mJ         |

11. Not subject to production testing.

## Protection

**Table 8. PROTECTION CHARACTERISTICS** ( $6 \leq V_D \leq 18$  V;  $-40^\circ C \leq T_J \leq 150^\circ C$  unless otherwise specified)

| Parameter Characteristic                                                 | Symbol         | Conditions                                                                               | Value |                |     | Unit |

|--------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------|-------|----------------|-----|------|

|                                                                          |                |                                                                                          | Min   | Typ            | Max |      |

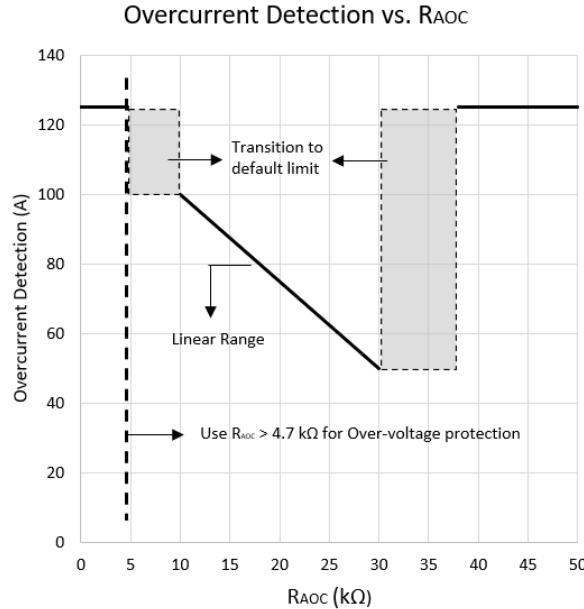

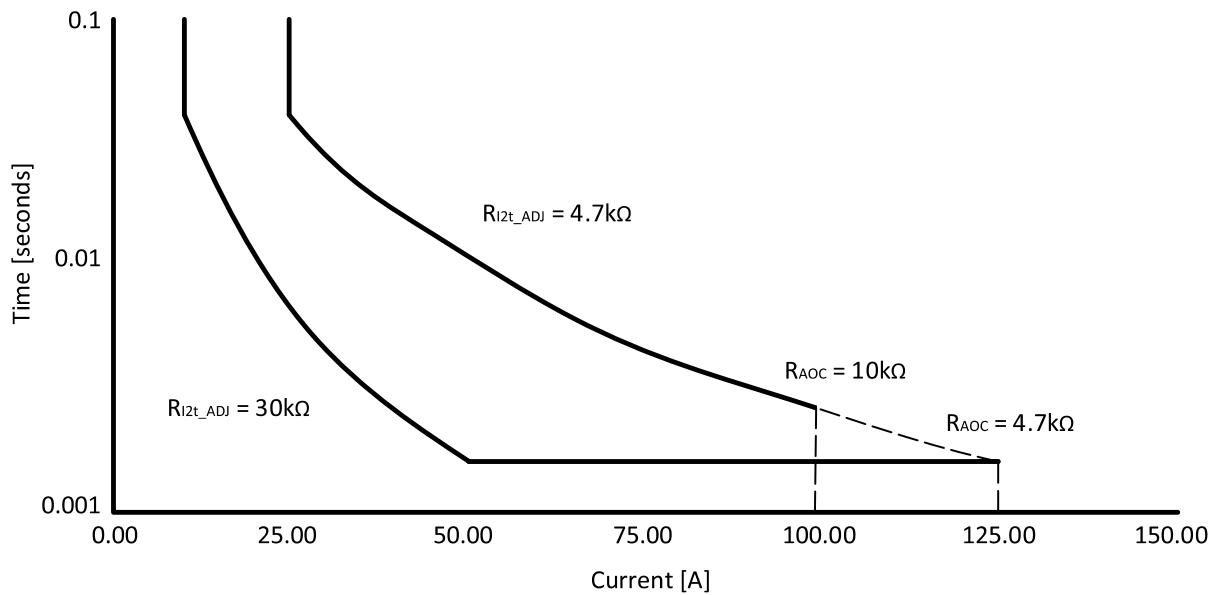

| Over-current Detection (Adjustable) (Note 12)                            | $I_{LIM}$      | $V_D = 15$ V, $R_{AOC} = 4.7$ k $\Omega$ , Setup based on AECQ100-012 Load Short Circuit | 112   | 125            | 138 | A    |

|                                                                          |                | $V_D = 15$ V, $R_{AOC} = 10$ k $\Omega$ , Setup based on AECQ100-012 Load Short Circuit  | 90    | 100            | 110 |      |

|                                                                          |                | $V_D = 15$ V, $R_{AOC} = 20$ k $\Omega$ , Setup based on AECQ100-012 Load Short Circuit  | 64    | 75             | 86  |      |

|                                                                          |                | $V_D = 15$ V, $R_{AOC} = 30$ k $\Omega$ , Setup based on AECQ100-012 Load Short Circuit  | 40    | 50             | 60  |      |

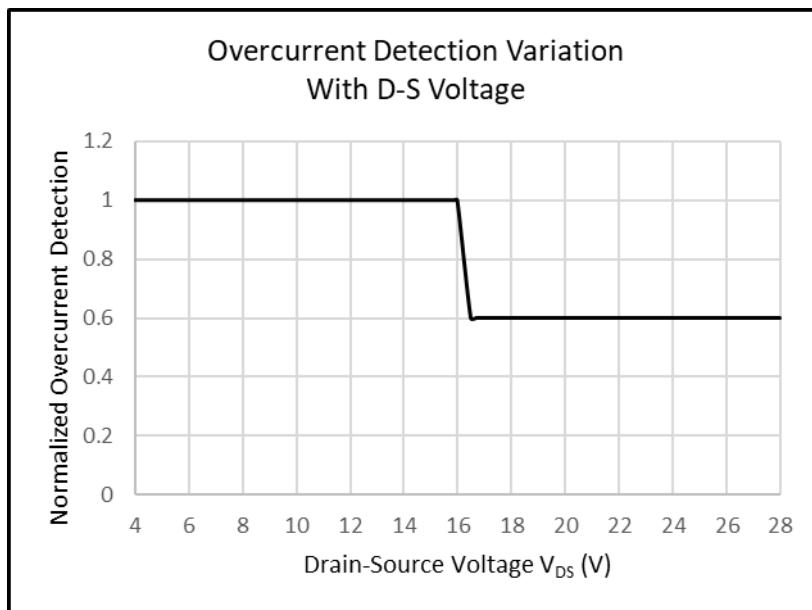

| Normalized Over-current detection at High $V_{DS}$ (Note 12)             | $I_{LIM(FB)}$  | $V_{DS} \geq 17$ V                                                                       |       | 0.6* $I_{LIM}$ |     | A    |

| Normalized Over-current detection at High $V_D$ for Jump Start (Note 12) | $I_{LIM(JS)}$  | $V_D > V_{D\_JS}$                                                                        |       | 0.6* $I_{LIM}$ |     | A    |

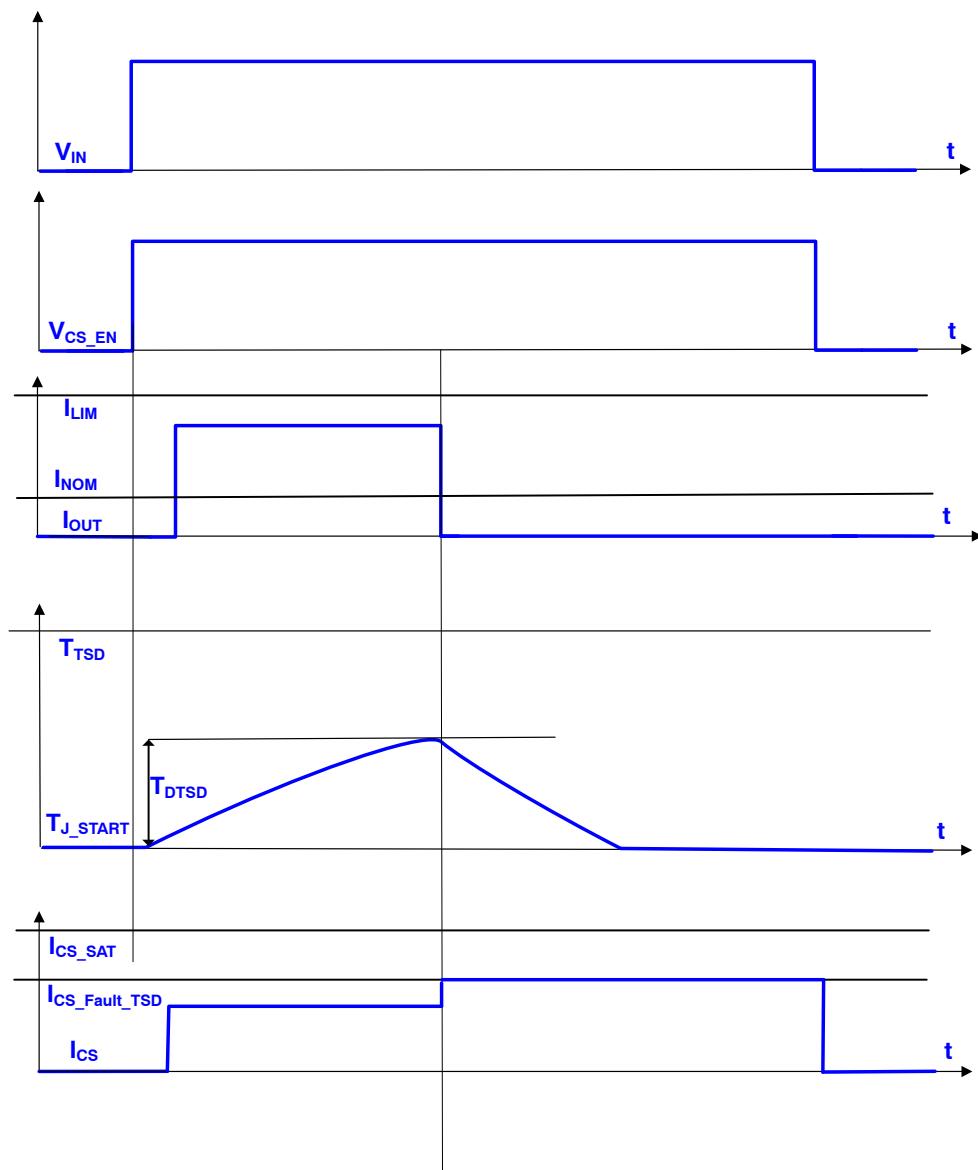

| Differential Thermal Shutdown Threshold – Normal Mode (Note 12)          | $T_{DTSD}$     |                                                                                          |       | 80             |     | °C   |

| Differential Thermal Shutdown Threshold – Capacitive load Mode (Note 12) | $T_{DTSD\_CL}$ |                                                                                          |       | 30             |     | °C   |

| Max allowed time in capacitive switching mode (Note 12)                  | $t_{max\_Cap}$ |                                                                                          |       | 50             |     | ms   |

| Thermal Shutdown Threshold (Note 12)                                     | $T_{TSD}$      |                                                                                          | 150   | 175            | 200 | °C   |

| Thermal Shutdown Hysteresis (Note 12)                                    | $T_{TSD\_HYS}$ |                                                                                          |       | 15             |     | °C   |

| Over-Voltage Protection Clamp                                            | $V_{ZOV}$      | Current into the $V_D$ pin, $I_D = 5$ mA, $V_{IN} = 0$ V                                 | 35    | 36             | 39  | V    |

| Drain Voltage for Current Limitation Reduction in Jump Start (Note 12)   | $V_{D\_JS}$    |                                                                                          | 20.5  | 22.5           | 24  | V    |

12. Not Subject to production testing.

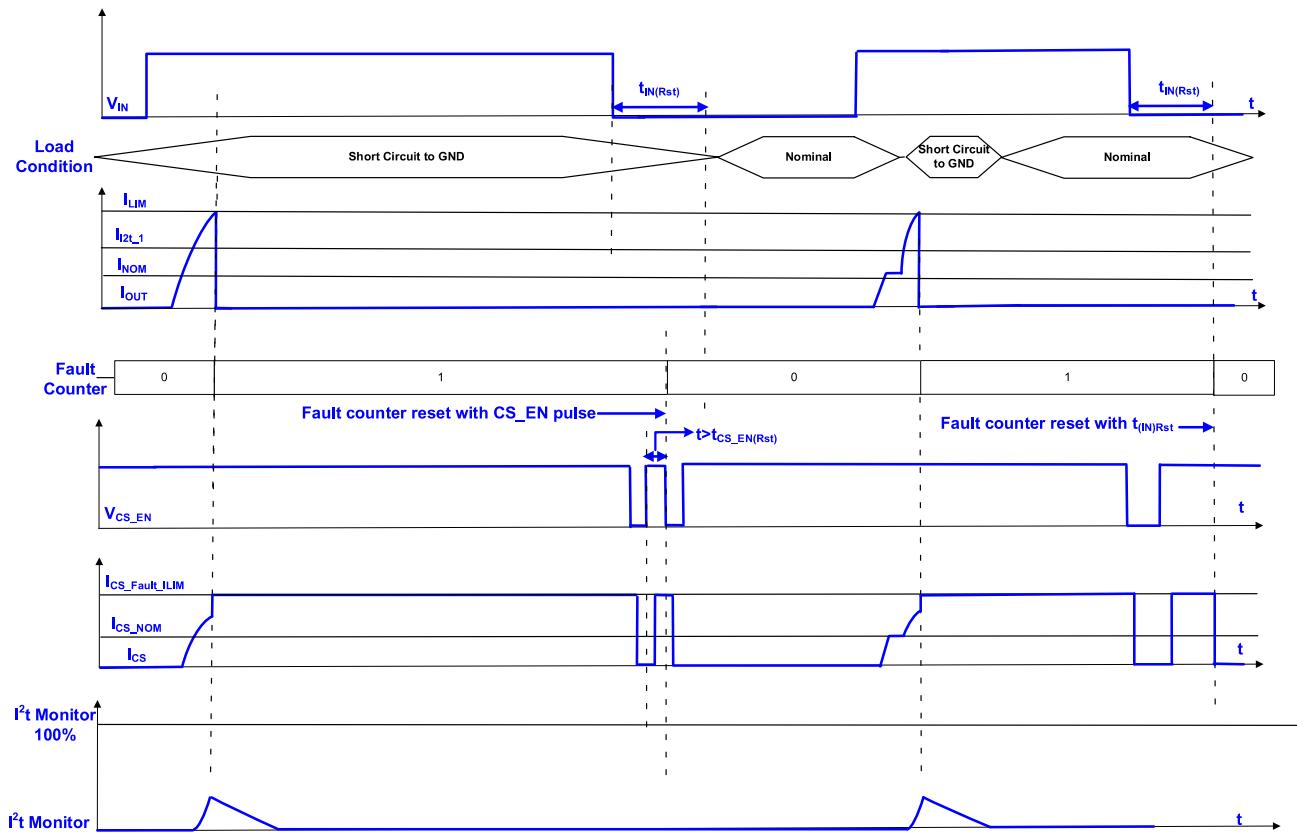

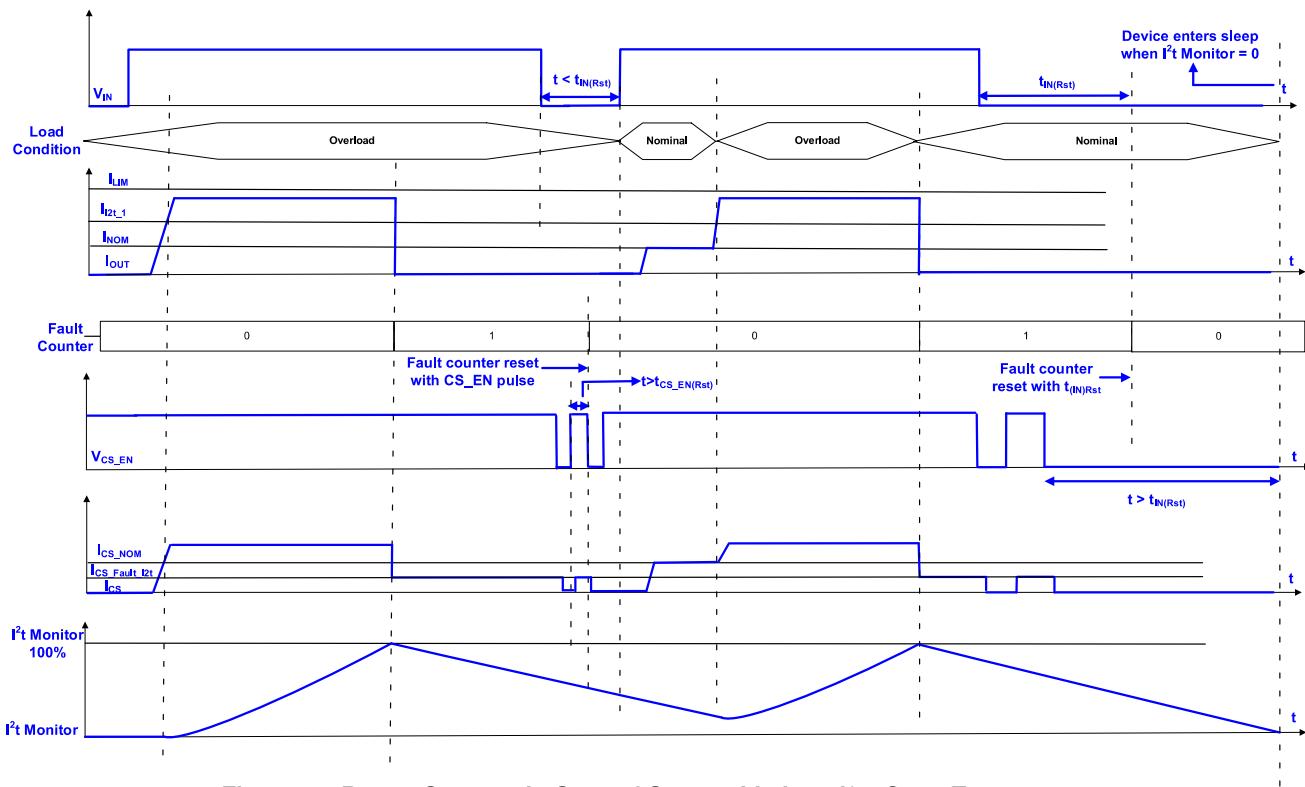

**Table 9. RETRY STRATEGY** (See Figure 17)

| Parameter Characteristic                                      | Symbol            | Conditions                                                                                            | Value |     |     | Unit |

|---------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------|-------|-----|-----|------|

|                                                               |                   |                                                                                                       | Min   | Typ | Max |      |

| Number of Retries in Fault after Counter Reset (Notes 13, 14) | $n_{COUNT}$       | $I_{OUT} = I_{LIM}$ , or $T_{J(ABS)} > T_{TSD}$ , or $T_{J(DIFF)} > T_{DTSD}$ , $I^2t$ Monitor = 100% |       | 1   |     |      |

| IN based Counter Reset Time (Note 13)                         | $t_{IN(Rst)}$     | $V_{IN} = 0$ V, Fault Counter > 0                                                                     | 40    | 70  | 100 | ms   |

| CS_EN based Counter Reset Time (Note 13)                      | $t_{CS\_EN(Rst)}$ | $V_{IN} = 0$ V, Fault Counter > 0                                                                     | 150   |     |     | μs   |

13. Not Subject to production testing.

14. Not valid in Capacitive load mode.

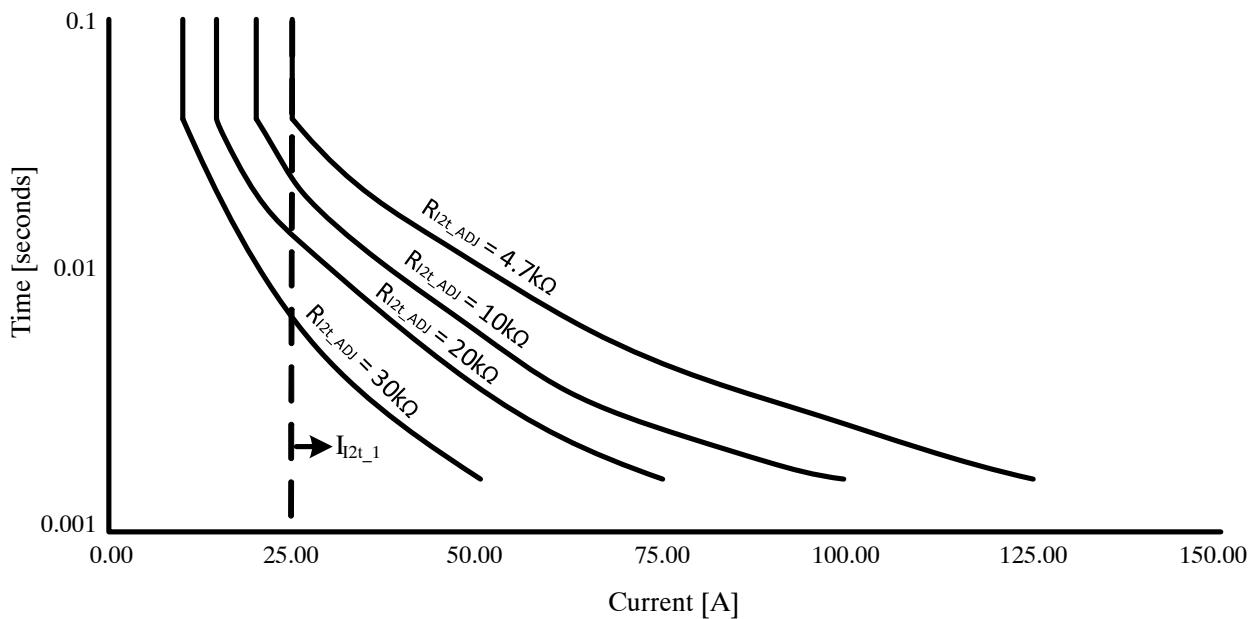

**Table 10. I<sup>2</sup>t PROTECTION THRESHOLDS** (6 ≤ V<sub>D</sub> ≤ 18 V; -40°C ≤ T<sub>J</sub> ≤ 150°C unless otherwise specified)

| Rating                                             | Symbol              | Conditions                    | Value |                            |     | Unit |

|----------------------------------------------------|---------------------|-------------------------------|-------|----------------------------|-----|------|

|                                                    |                     |                               | Min   | Typ                        | Max |      |

| I <sup>2</sup> t Current Thresholds (Notes 15, 16) | I <sub>I2t_1</sub>  | R <sub>I2t_ADJ</sub> = 4.7 kΩ | TBD   | 0.2 * I <sub>I2t_11</sub>  | TBD | A    |

|                                                    | I <sub>I2t_2</sub>  |                               | TBD   | 0.25 * I <sub>I2t_11</sub> | TBD | A    |

|                                                    | I <sub>I2t_3</sub>  |                               | TBD   | 0.3 * I <sub>I2t_11</sub>  | TBD | A    |

|                                                    | I <sub>I2t_4</sub>  |                               | TBD   | 0.35 * I <sub>I2t_11</sub> | TBD | A    |

|                                                    | I <sub>I2t_5</sub>  |                               | TBD   | 0.4 * I <sub>I2t_11</sub>  | TBD | A    |

|                                                    | I <sub>I2t_6</sub>  |                               | TBD   | 0.5 * I <sub>I2t_11</sub>  | TBD | A    |

|                                                    | I <sub>I2t_7</sub>  |                               | TBD   | 0.6 * I <sub>I2t_11</sub>  | TBD | A    |

|                                                    | I <sub>I2t_8</sub>  |                               | TBD   | 0.7 * I <sub>I2t_11</sub>  | TBD | A    |

|                                                    | I <sub>I2t_9</sub>  |                               | TBD   | 0.8 * I <sub>I2t_11</sub>  | TBD | A    |

|                                                    | I <sub>I2t_10</sub> |                               | TBD   | 0.9 * I <sub>I2t_11</sub>  | TBD | A    |

|                                                    | I <sub>I2t_11</sub> |                               |       | 125                        |     | A    |

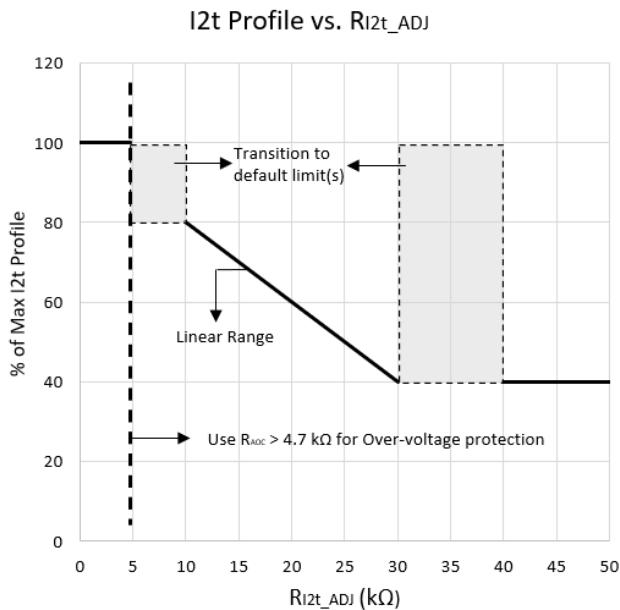

|                                                    | I <sub>I2t_11</sub> | R <sub>I2t_ADJ</sub> = 10 kΩ  | TBD   | 100                        | TBD | A    |

|                                                    | I <sub>I2t_11</sub> | R <sub>I2t_ADJ</sub> = 20 kΩ  | TBD   | 75                         | TBD | A    |

|                                                    | I <sub>I2t_11</sub> | R <sub>I2t_ADJ</sub> = 30 kΩ  | TBD   | 50                         | TBD | A    |

15. Not Subject to production testing.

16. R<sub>AOC</sub> = 4.7 kΩ to ensure full I<sup>2</sup>t range.**Table 11. I<sup>2</sup>t PROTECTION THRESHOLDS** (6 ≤ V<sub>D</sub> ≤ 18 V; -40°C ≤ T<sub>J</sub> ≤ 150°C unless otherwise specified)

| Rating                                           | Symbol               | Conditions                             | Value |      |     | Unit |

|--------------------------------------------------|----------------------|----------------------------------------|-------|------|-----|------|

|                                                  |                      |                                        | Min   | Typ  | Max |      |

| I <sup>2</sup> t Time Control (Notes 17, 18)     | t <sub>I2t_1</sub>   | I <sub>OUT</sub> = I <sub>I2t_1</sub>  | TBD   | 31.6 | TBD | ms   |

|                                                  | t <sub>I2t_2</sub>   | I <sub>OUT</sub> = I <sub>I2t_2</sub>  | TBD   | 21.2 | TBD | ms   |

|                                                  | t <sub>I2t_3</sub>   | I <sub>OUT</sub> = I <sub>I2t_3</sub>  | TBD   | 15.1 | TBD | ms   |

|                                                  | t <sub>I2t_4</sub>   | I <sub>OUT</sub> = I <sub>I2t_4</sub>  | TBD   | 11.4 | TBD | ms   |

|                                                  | t <sub>I2t_5</sub>   | I <sub>OUT</sub> = I <sub>I2t_5</sub>  | TBD   | 7.9  | TBD | ms   |

|                                                  | t <sub>I2t_6</sub>   | I <sub>OUT</sub> = I <sub>I2t_6</sub>  | TBD   | 5.3  | TBD | ms   |

|                                                  | t <sub>I2t_7</sub>   | I <sub>OUT</sub> = I <sub>I2t_7</sub>  | TBD   | 3.8  | TBD | ms   |

|                                                  | t <sub>I2t_8</sub>   | I <sub>OUT</sub> = I <sub>I2t_8</sub>  | TBD   | 2.8  | TBD | ms   |

|                                                  | t <sub>I2t_9</sub>   | I <sub>OUT</sub> = I <sub>I2t_9</sub>  | TBD   | 2.2  | TBD | ms   |

|                                                  | t <sub>I2t_10</sub>  | I <sub>OUT</sub> = I <sub>I2t_10</sub> | TBD   | 1.8  | TBD | ms   |

|                                                  | t <sub>I2t_11</sub>  | I <sub>OUT</sub> = I <sub>I2t_11</sub> |       | 1.6  |     | ms   |

| I <sup>2</sup> t Time Control Accuracy (Note 17) | t <sub>I2t_acc</sub> |                                        | -20   |      | 20  | %    |

17. Not Subject to production testing.

18. R<sub>AOC</sub> = 4.7 kΩ to ensure full I<sup>2</sup>t range.

**Diagnostic Functions**

NCV84003G provides diagnostic information and dynamic current sensing on the diagnostic output pin CS.

**Table 12. DIAGNOSTIC TRUTH TABLE**

| Operating Condition                           | IN | CS_EN | IDLE MODE | Output Voltage         | CS Output                                                              |

|-----------------------------------------------|----|-------|-----------|------------------------|------------------------------------------------------------------------|

| Normal Operation                              | L  | H     | X         | ~ GND                  | HiZ, if Fault Counter = 0<br>Ics_FAULT if Fault Counter > 0            |

| Short Circuit to GND – Overcurrent            |    |       |           | GND                    | HiZ, if Fault Counter = 0<br>Ics_FAULT_ILIM if Fault Counter > 0       |

| Over Temperature                              |    |       |           | ~ GND                  | HiZ, if Fault Counter = 0<br>Ics_FAULT_TSD if Fault Counter > 0        |

| Short Circuit to $V_{BATT}$                   |    |       |           | $V_{BATT}$             | Ics_FAULT_OSOL, if Fault Counter = 0<br>Ics_FAULT if Fault Counter > 0 |

| Open Load                                     |    |       |           | $< V_D - V_{DS\_OSOL}$ | HiZ, if Fault Counter = 0<br>Ics_FAULT if Fault Counter > 0            |

|                                               |    |       |           | $> V_D - V_{DS\_OSOL}$ | Ics_FAULT_OSOL, if Fault Counter = 0<br>Ics_FAULT if Fault Counter > 0 |

| Inverse Current                               |    |       |           | $> V_D$                | Ics_FAULT_OSOL, if Fault Counter = 0<br>Ics_FAULT if Fault Counter > 0 |

| Normal Operation                              |    | H     | Disabled  | ~ $V_D$                | Ics = Iout / Knom                                                      |

|                                               |    |       |           |                        | Ics = Iout / Knom if Iout > Iidle_tf<br>HiZ if Iout ≤ Iidle_tf         |

| Short Circuit to GND – Over Current Detection |    |       | X         | ~ GND                  | Ics_FAULT_ILIM                                                         |

| Over Temperature (Absolute or Differential)   |    |       | X         | ~ GND                  | Ics_FAULT_TSD                                                          |

| Short Circuit to $V_{BATT}$                   |    |       | Disabled  | $V_{BATT}$             | Ics_Ol < Ics < Iout / Knom                                             |

|                                               |    |       | Enabled   | $V_{BATT}$             | HiZ                                                                    |

| Open Load                                     |    |       | Disabled  | ~ $V_D$                | Ics ≤ Ics(Ol)                                                          |

|                                               |    |       | Enabled   | ~ $V_D$                | HiZ                                                                    |

| Underload                                     |    |       | Disabled  | ~ $V_D$                | Ics(Ol) < Ics < Iout / Knom                                            |

|                                               |    |       | Enabled   | ~ $V_D$                | HiZ                                                                    |

| Inverse Current                               |    |       | X         | $> V_D$                | HiZ                                                                    |

| Diagnostics Disabled                          | X  | L     | X         | X                      | HiZ                                                                    |

**Current Sense Ratio K**

The accuracy in load current estimation through sensed current can be improved by performing a calibration routine

during end of line (EOL) testing. The calibration procedure can be performed at the nominal load current at one single temperature (25°C).

## Diagnostics

Table 13. CURRENT SENSE CHARACTERISTICS ( $6 \leq V_D \leq 18 \text{ V}$ ;  $-40^\circ\text{C} \leq T_J \leq 150^\circ\text{C}$  unless otherwise specified)

| Rating                                                              | Symbol                     | Conditions                                                                                                                             | Value |       |       | Unit          |

|---------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|---------------|

|                                                                     |                            |                                                                                                                                        | Min   | Typ   | Max   |               |

| CS Leakage Current, CS Output Disabled                              | $I_{Q\_CS\_DIS}$           | $V_{IN} = 5 \text{ V}$ , $V_{CS\_EN} = 0 \text{ V}$ , $I_L = 15 \text{ A}$                                                             |       |       | 0.5   | $\mu\text{A}$ |

| CS Leakage Current, CS Output Enabled                               | $I_{Q\_CS\_EN}$            | $V_{IN} = 5 \text{ V}$ , $V_{CS\_EN} = 5 \text{ V}$ , $I_L = 0 \text{ A}$                                                              |       |       | 1     | $\mu\text{A}$ |

| CS Operation Voltage for nominal operation (Note 19)                | $V_{CS\_SAT(NOM)}$         | $V_D = 6 \text{ V}$ , $V_{IN} = V_{CS\_EN} = 5 \text{ V}$ , $I_L = 15 \text{ A}$ , $I_{CS} > 0.5 * I_{CS\_NOM}$                        | 0     | 0.5   | 1     | $\text{V}$    |

| CS Operation Voltage for in-fault operation (Note 19)               | $V_{CS\_SAT(Fault)\_ILIM}$ | $V_D = 6 \text{ V}$ , $V_{IN} = V_{CS\_EN} = 5 \text{ V}$ , $I_{CS} > 0.5 * I_{CS\_Fault\_ILIM}$                                       | 0     | 0.5   | 1     | $\text{V}$    |

| CS Operation Voltage for in-fault operation (Note 19)               | $V_{CS\_SAT(Fault)\_TSD}$  | $V_D = 6 \text{ V}$ , $V_{IN} = V_{CS\_EN} = 5 \text{ V}$ , $I_{CS} > 0.5 * I_{CS\_Fault\_TSD}$                                        | 0     | 0.5   | 1     | $\text{V}$    |

| CS Operation Voltage for in-fault operation (Note 19)               | $V_{CS\_SAT(Fault)\_I2t}$  | $V_D = 6 \text{ V}$ , $V_{IN} = V_{CS\_EN} = 5 \text{ V}$ , $I_{CS} > 0.5 * I_{CS\_Fault\_I2t}$                                        | 0     | 0.5   | 1     | $\text{V}$    |

| CS Operation Voltage for OFF State Open Load operation (Note 19)    | $V_{CS\_SAT(Fault)\_OSOL}$ | $V_D = 6 \text{ V}$ , $V_{IN} = 0 \text{ V}$ , $V_{CS\_EN} = 5 \text{ V}$ , $I_L = 0 \text{ A}$ , $I_{CS} > 0.5 * I_{CS\_Fault\_OSOL}$ | 0     | 0.5   | 1     | $\text{V}$    |

| CS Saturation Current in normal mode (Note 19)                      | $I_{CS\_SAT}$              |                                                                                                                                        | 8     | 10    |       | $\text{mA}$   |

| CS Fault Indication Current: Overcurrent detection (Note 19)        | $I_{CS\_FAULT\_ILIM}$      | $V_{IN} = 5 \text{ V}$ , $V_{CS\_EN} = 5 \text{ V}$<br>Fault Counter > 0, $I_{OUT} = I_{ILIM}$                                         | 6.7   | 8.5   | 10    | $\text{mA}$   |

| CS Fault Indication Current: TSD/DTSD (Note 19)                     | $I_{CS\_FAULT\_TSD}$       | $V_{IN} = 5 \text{ V}$ , $V_{CS\_EN} = 5 \text{ V}$<br>Fault Counter > 0, $T_J > T_{TSD}$ or $T_{J(DIFF)} > T_{DTSD}$                  | 3.8   | 5     | 6.5   | $\text{mA}$   |

| CS Fault Indication Current: $I^2t$ Activation (Note 19)            | $I_{CS\_FAULT\_I2t}$       | $V_{IN} = 5 \text{ V}$ , $V_{CS\_EN} = 5 \text{ V}$<br>Fault Counter > 0, $I^2t$ Monitor = 100%                                        | 1     | 1.4   | 1.8   | $\text{mA}$   |

| CS Fault Indication Current in OFF State Open Load                  | $I_{CS\_FAULT\_OSOL}$      | $V_{IN} = 0 \text{ V}$ , $V_{CS\_EN} = 5 \text{ V}$<br>Fault Counter = 0, $V_{DS} < V_{DS\_OSOL}$                                      | 1.9   | 2.5   | 3.5   | $\text{mA}$   |

| CS Pin Clamp to Power Supply                                        | $V_{CS\_CL}$               | $I_{CS} = 1 \text{ mA}$                                                                                                                | 35    | 36    | 39    | $\text{V}$    |

| Current Sense Ratio 1                                               | $K_1$                      | $I_{OUT} = 0.5 \text{ A}$                                                                                                              | 14000 | 20000 | 26000 |               |

| Current Sense Ratio 2                                               | $K_2$                      | $I_{OUT} = 0.75 \text{ A}$                                                                                                             | 16000 | 20000 | 24000 |               |

| Current Sense Ratio 3                                               | $K_3$                      | $I_{OUT} = 2 \text{ A}$                                                                                                                | 18000 | 20000 | 22000 |               |

| Current Sense Ratio 4                                               | $K_4$                      | $I_{OUT} = 8.5 \text{ A}$                                                                                                              | 19000 | 20000 | 21000 |               |

| Current Sense Ratio 5                                               | $K_5$                      | $I_{OUT} = 15 \text{ A}$                                                                                                               | 19400 | 20000 | 20600 |               |

| Max Current Sense Ratio Drift After Two-Point Calibration (Note 20) | $K_{rel4}$                 | $K_4 / K_5$ , including temperature drift                                                                                              | 0.97  | 1     | 1.03  |               |

19. Not Subject to production testing.

20. Not subjected to production testing. For more information, refer to the AND9733/D Applications Note.

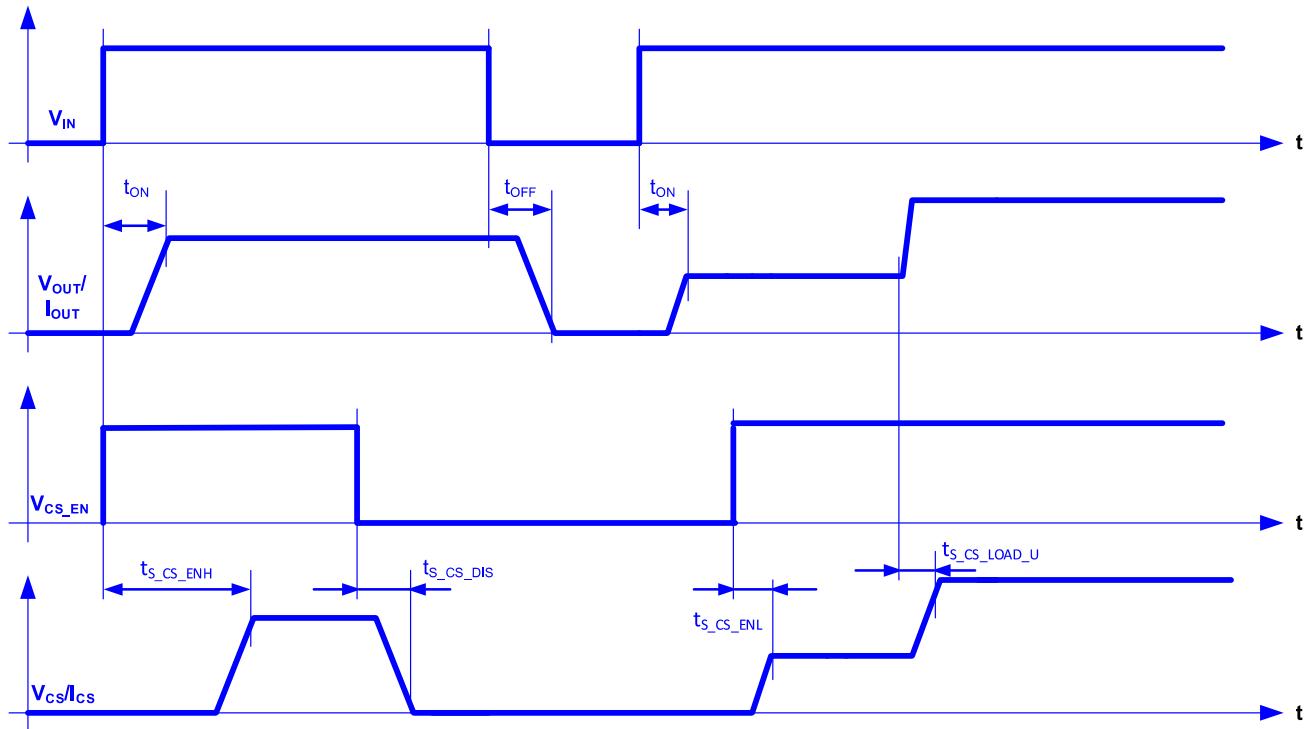

**Table 14. CURRENT SENSE TIMING** ( $6 \leq V_D \leq 18 \text{ V}$ ;  $-40^\circ\text{C} \leq T_J \leq 150^\circ\text{C}$  unless otherwise specified) (See Figure 29)

| Rating                                                                                                              | Symbol               | Conditions                                                                                                                                                                                                                                                       | Value |     |     | Unit          |

|---------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-----|---------------|

|                                                                                                                     |                      |                                                                                                                                                                                                                                                                  | Min   | Typ | Max |               |

| Current Sense Settling Time after Diagnostic Activation, Stable Output and Load Conditions – Nominal Load (Note 21) | $t_{S\_CS\_ENH}$     | $V_{IN} = 5 \text{ V}$ , $V_{CS\_EN} = 0 \text{ V} \rightarrow 5 \text{ V}$<br>$V_D = 13.5 \text{ V}$ , $I_L = 15 \text{ A}$ ,<br>$I_{CS} = 90\% I_{CS\_STATIC}$<br>$R_{CS} = 1.2 \text{ k}\Omega$ , $C_{CS} < 100 \text{ pF}$                                   |       |     | 20  | $\mu\text{s}$ |

| Current Sense Settling Time after Diagnostic Activation, Stable Output and Load Conditions – Light Load (Note 21)   | $t_{S\_CS\_ENL}$     | $V_{IN} = 5 \text{ V}$ , $V_{CS\_EN} = 0 \text{ V} \rightarrow 5 \text{ V}$<br>$V_D = 13.5 \text{ V}$ , $V_{IDLE\_FLG} = 5 \text{ V}$ ,<br>$I_L = 0.75 \text{ A}$ , $I_{CS} = 90\% I_{CS\_STATIC}$<br>$R_{CS} = 1.2 \text{ k}\Omega$ , $C_{CS} < 100 \text{ pF}$ |       |     | 60  | $\mu\text{s}$ |

| Current Sense Settling Time after Load Current Change (Note 21)                                                     | $t_{S\_CS\_LOAD\_U}$ | $V_{IN} = V_{CS\_EN} = 5 \text{ V}$ , $V_D = 13.5 \text{ V}$<br>$I_L = 10 \text{ A} \rightarrow 15 \text{ A}$ , $I_{CS} = 90\% I_{CS\_STATIC}$<br>$R_{CS} = 1.2 \text{ k}\Omega$ , $C_{CS} < 100 \text{ pF}$                                                     |       |     | 20  | $\mu\text{s}$ |

| Current Sense Output Disable Time (Note 21)                                                                         | $t_{S\_CS\_DIS}$     | $V_{IN} = 5 \text{ V}$ , $V_{CS\_EN} = 5 \text{ V} \rightarrow 0 \text{ V}$<br>$V_D = 13.5 \text{ V}$ , $I_L = 15 \text{ A}$ ,<br>$I_{CS} = 10\% I_{CS\_STATIC}$<br>$R_{CS} = 1.2 \text{ k}\Omega$ , $C_{CS} < 100 \text{ pF}$                                   |       |     | 20  | $\mu\text{s}$ |

| Current Sense Output Disable Time – In Fault (Note 21)                                                              | $t_{S\_CS\_DIS\_F}$  | $V_{IN} = 0 \text{ V}$ , $V_{CS\_EN} = 5 \text{ V} \rightarrow 0 \text{ V}$<br>$V_D = V_{OUT} = 13.5 \text{ V}$ ,<br>$I_{CS} = 10\% I_{CS\_STATIC}$<br>$R_{CS} = 1.2 \text{ k}\Omega$ , $C_{CS} < 100 \text{ pF}$                                                |       |     | 20  | $\mu\text{s}$ |

| Standby Mode activation after Diagnostic activation (Note 21)                                                       | $t_{Norm}$           | $V_{CS\_EN} = 0 \text{ V} \rightarrow 5 \text{ V}$ to $V_{IN} = 0 \text{ V} \rightarrow 5 \text{ V}$ for normal mode entry (See Figure 11)                                                                                                                       | 200   |     |     | $\mu\text{s}$ |

21. Not Subject to production testing.

**Table 15. OPEN LOAD / UNDERLOAD DETECTION AND TIMING**(6  $\leq V_D \leq 18 \text{ V}$ ;  $-40^\circ\text{C} \leq T_J \leq 150^\circ\text{C}$  unless otherwise specified)

| Rating                                                                 | Symbol            | Conditions                                                                                                                                                                                                       | Value |     |     | Unit          |

|------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-----|---------------|

|                                                                        |                   |                                                                                                                                                                                                                  | Min   | Typ | Max |               |

| Open Load Detection Threshold, OFF State (Note 22)                     | $V_{DS\_OSOL}$    | $V_{IN} = 0 \text{ V}$ , $V_{CS\_EN} = 5 \text{ V}$                                                                                                                                                              | 1.3   | 1.8 | 2.3 | $\text{V}$    |

| Open Load Detection Delay OFF State                                    | $t_{OSOL\_Blank}$ | $V_{IN} = 5 \text{ V} \rightarrow 0 \text{ V}$ , $V_{CS\_EN} = 5 \text{ V}$<br>$V_D = V_{OUT} = 13.5 \text{ V}$ ,<br>$I_{CS} = 90\% I_{CS\_FAULT}$<br>$R_{CS} = 1.2 \text{ k}\Omega$ , $C_{CS} < 100 \text{ pF}$ | 70    | 150 | 250 | $\mu\text{s}$ |

| Open Load Detection Threshold, ON State (IDLE Mode Disabled) (Note 23) | $I_{OL\_ON}$      | $V_{IN} = 5 \text{ V}$ , $V_{CS\_EN} = 5 \text{ V}$<br>$I_{CS} = I_{CS(OI)} = 4 \mu\text{A}$                                                                                                                     | 30    |     | 150 | $\text{mA}$   |

22. Not subject to production testing.

23. Limits may be widened.

**Table 16. IDLE MODE DETECTION AND TIMING** ( $6 \leq V_D \leq 18 \text{ V}$ ;  $-40^\circ\text{C} \leq T_J \leq 150^\circ\text{C}$  unless otherwise specified)

| Rating                          | Symbol          | Conditions                                                                                                                                           | Value |     |     | Unit          |

|---------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-----|---------------|

|                                 |                 |                                                                                                                                                      | Min   | Typ | Max |               |

| IDLE Mode Exit Detection Delay  | $t_{IDLE\_Ext}$ | $V_{IN} = 5 \text{ V}$ , $I_{OUT} = 0.5 \text{ A} \rightarrow 15 \text{ A}$ to<br>$V_{IDLE\_FLG} = 10\% \max V_{IDLE\_FLG}$                          |       | 50  |     | $\mu\text{s}$ |

| IDLE Mode Entry Detection Delay | $t_{IDLE\_Ent}$ | $V_{IN} = 5 \text{ V}$ , $I_{OUT} = 15 \text{ A} \rightarrow 0.5 \text{ A}$ to<br>$V_{IDLE\_FLG} = 90\% \max V_{IDLE\_FLG}$ ,<br>$I^2t$ Monitor = 0% |       | 250 |     | $\mu\text{s}$ |

| IDLE Mode Entry Blanking Time   | $t_{IDLE\_Blk}$ | $V_{IN} = 0 \rightarrow 5 \text{ V}$ , $V_{CS\_EN} = 5 \text{ V}$ ,<br>$I_{OUT} = 0.5 \text{ A}$<br>$V_{IDLE\_FLG} = 90\% \max V_{IDLE\_FLG}$        |       | 350 |     | $\mu\text{s}$ |

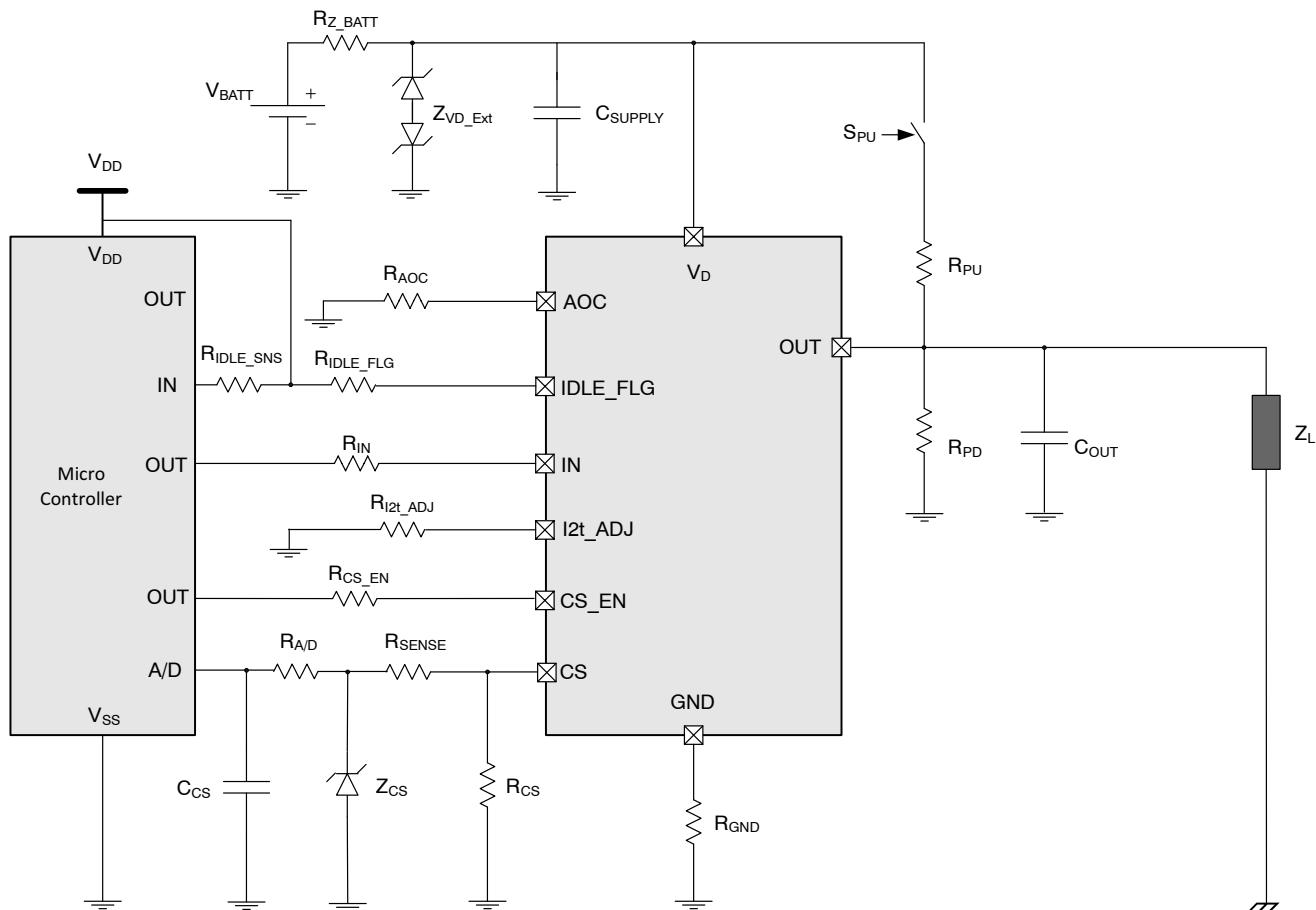

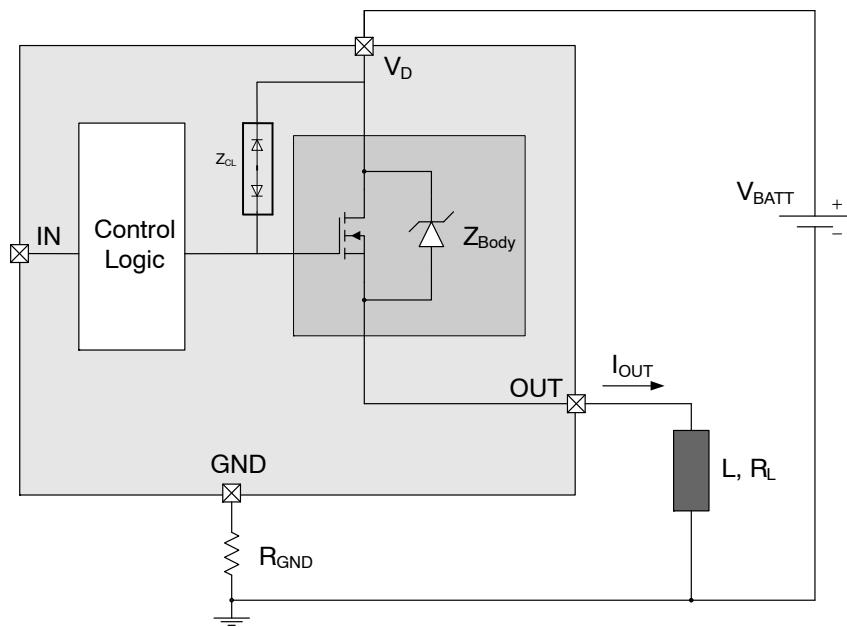

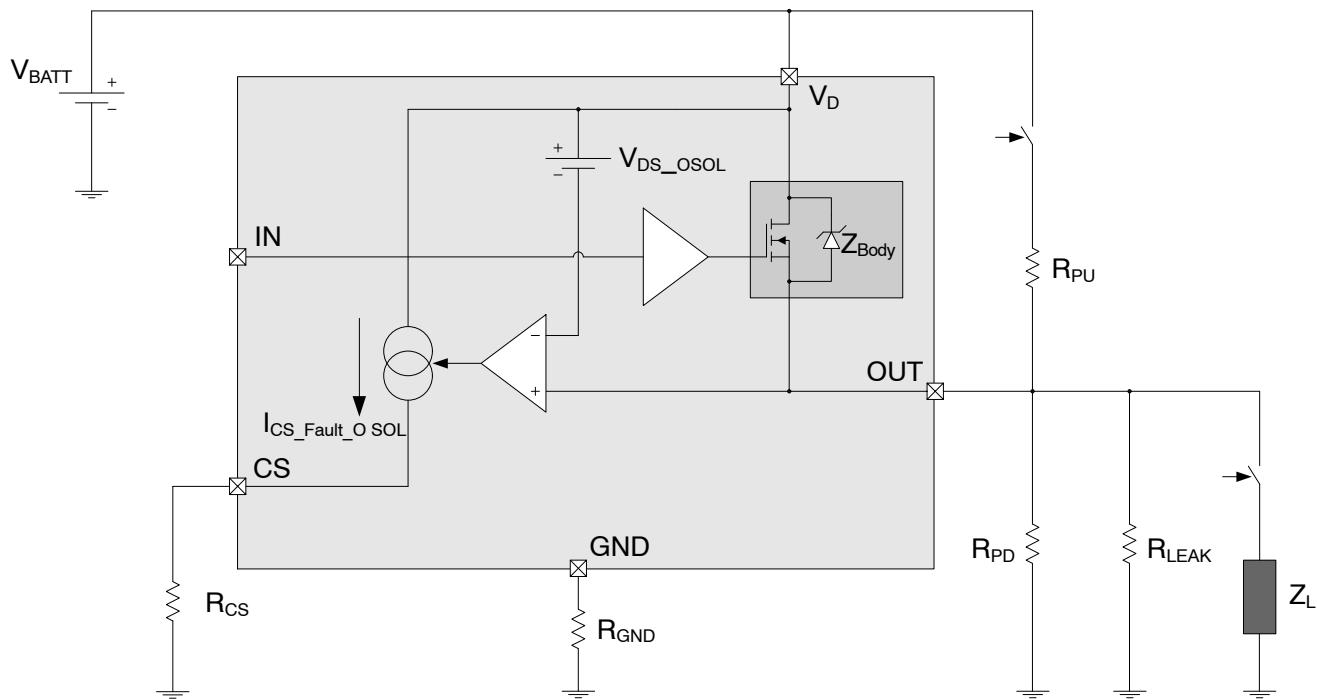

### Application Diagram and Pin Description

NCV84003G is a single channel smart high-side driver with a very low resistance n-channel output transistor. The required gate overdrive voltage for the transistor is generated by a charge pump that is integrated into the device. The output driver's protection scheme is designed to support linear resistive loads as well as loads with high inrush current, e.g. bulk capacitors and lighting bulbs. The embedded control and protection functions provide full protection to the device as well as full-featured load diagnostic for open load, underload and short circuit through

a current sense output that delivers a fraction of the load current in nominal operation multiplexed with a fixed current output in a fault state. An accurate slew rate control is provided to minimize conducted EMI in case of a constant PWM operation. The device features an ultra-low operating current in IDLE mode to address system leakage requirements in zonal applications.

The device provides direct control input (IN) and a diagnostic enable input (CS\_EN) to control the information to be provided at the current sense output.

Figure 4. Application Diagram

NCV84003G is supplied by the  $V_D$  pin, which can be directly connected to the battery net. The  $V_D$  pin is used as power supply to the control circuitry as well as the common drain supply for output channels. In order to support all board net transients following ISO7637-1, an external protection concept as shown in Figure 4 is recommended.

The zener diode  $Z_{VD\_Ext}$  is used to clamp overvoltage events as well as to provide a free-wheeling path in the event

of loss of battery ( $V_D$ ) with charged inductive loads.  $R_{GND}$  is required to limit the maximum current flowing through  $Z_{VD}$  (see Figure 18) in case of an over-voltage event. Since all low-voltage I/O pins feature input protection diodes, it is required to insert series resistances into the connection lines between the controlling device (e.g. microcontroller) and NCV84003G.

**Table 17. RECOMMENDED EXTERNAL COMPONENTS**

| Reference       | Value                          | Function                                                                                                                                                           |

|-----------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $R_{IN}$        | 4.7 k $\Omega$                 | Provides protection of the micro controller during overvoltage and reverse polarity. Ensures the channel is OFF during loss of GND.                                |

| $R_{CS\_EN}$    | 4.7 k $\Omega$                 | Provides protection of the micro controller during overvoltage and reverse polarity. Ensures the channel is OFF during loss of GND.                                |

| $R_{I2t\_ADJ}$  | 4.7 k $\Omega$ ~ 30 k $\Omega$ | Recommended range for selecting $I^2t$ . Open circuit and short to GND not recommended (See Overcurrent Shutdown).                                                 |

| $R_{IDLE\_FLG}$ | 10 k $\Omega$                  | Open drain resistor to logic level voltage.                                                                                                                        |

| $R_{IDLE\_SNS}$ | 4.7 k $\Omega$                 | Provides protection of the micro controller during overvoltage and reverse polarity. Ensures the channel is OFF during loss of GND.                                |

| $R_{AOC}$       | 4.7 k $\Omega$ ~ 30 k $\Omega$ | Recommended range for selecting overcurrent threshold. Open circuit and short to GND not recommended (See Overcurrent Shutdown).                                   |

| $R_{CS}$        | 1.2 k $\Omega$                 | Current Sense resistor.                                                                                                                                            |

| $R_{SENSE}$     | 4.7 k $\Omega$                 | Provides protection against overvoltage, reverse polarity, and loss of GND. The value of this resistor should be selected with the micro controller specification. |

| $C_{CS}$        | 100 pF                         | Current Sense signal filtering.                                                                                                                                    |

| $R_{A/D}$       | 4.7 k $\Omega$                 | Current Sense signal filtering.                                                                                                                                    |

| $Z_{CS}$        | 10 V Zener Diode               | Provides protection micro controller during overvoltage at CS. Should be selected with the micro controller specification.                                         |

| $R_{PU}$        | 1.5 k $\Omega$                 | Polarizes the NCV84003G output during OFF state open load diagnosis.                                                                                               |

| $R_{PD}$        | 47 k $\Omega$                  | Output polarization. Improves the NCV84003G immunity to electromagnetic noise and also used for short to $V_{BATT}$ detection.                                     |

| $S_{PU}$        | BC807                          | Switches the battery voltage for OFF state open load diagnostic.                                                                                                   |

| $R_{GND}$       | 47 $\Omega$                    | Provides protection during overvoltage.                                                                                                                            |

| $Z_{VD\_Ext}$   | 30 V Zener Diode               | Provides protection of the device during overvoltage.                                                                                                              |

| $C_{SUPPLY}$    | 100 nF                         | Filtering of voltage spikes on the battery line.                                                                                                                   |

| $C_{OUT}$       | 4.7 nF                         | Protection during ESD and BCI on output.                                                                                                                           |

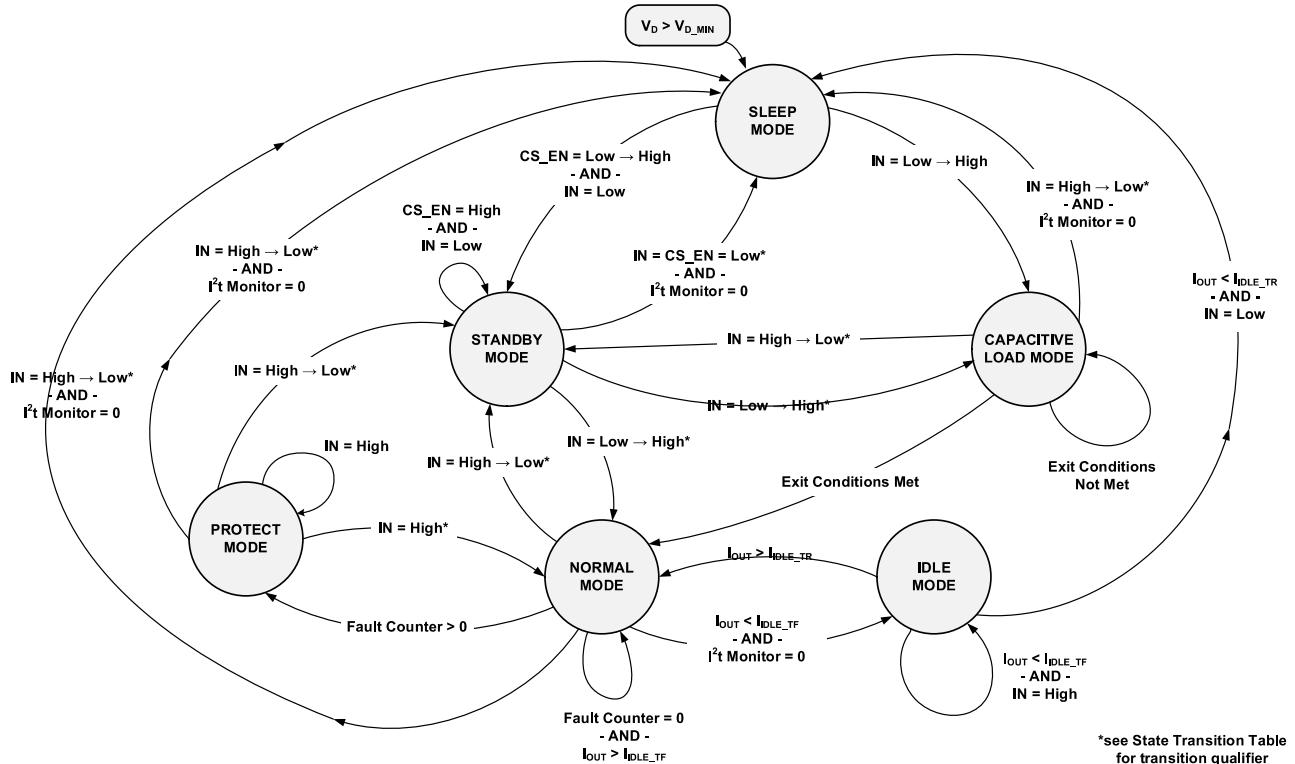

### Modes of Operation

NCV84003G is designed to operate in the following distinct modes of operation as stated below. Irrespective of the modes below, it should be noted that if  $V_D < V_{D(UV)}$ , then the internal logic may be reset to default, and values of timers/counters cannot be guaranteed.

#### a. Sleep Mode

If IN and CS\_EN have been observed as low for a duration longer than  $t_{IN(Rst)}$  and  $I^2t$  Monitor is zero, then the device enters sleep mode. The output FET is off, and the internal reference blocks are shut down and digital logic is reset (as in case of supply-based reset) in this mode to offer extremely low quiescent current (See Table 4).

#### b. Standby Mode

If IN has been observed low for a duration more than  $t_{IN(Rst)}$  and CS\_EN is high then device operates in standby mode. The output FET is off, and the off state diagnosis for open load and short circuit to  $V_{BATT}$  are available and  $I^2t$  monitor is active in this mode. If CS\_EN continues to be high, device stays in standby mode.

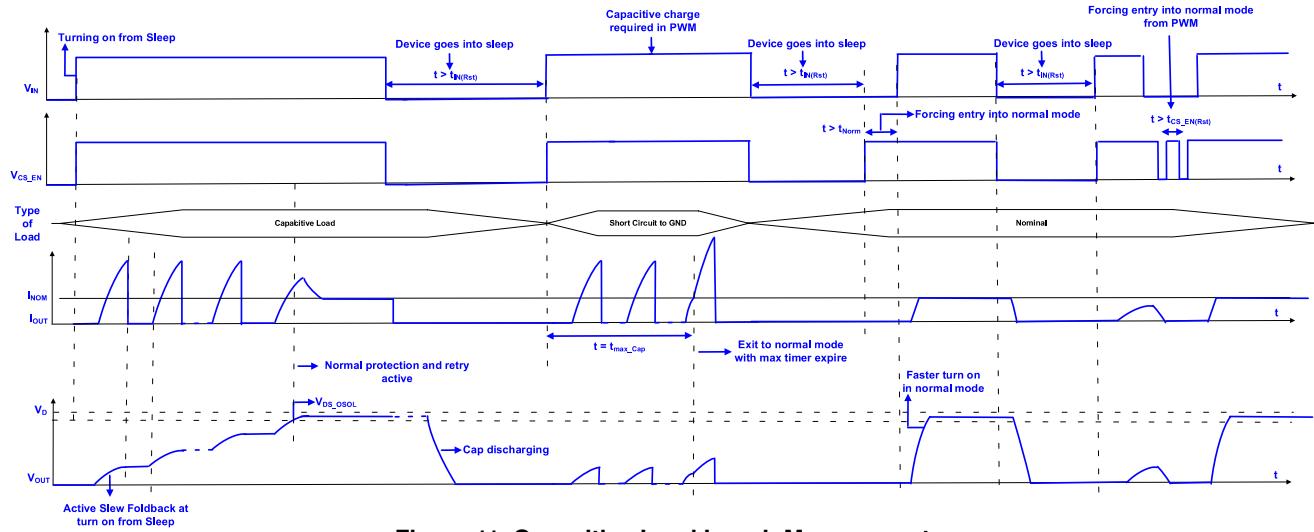

#### c. Capacitive Load (CL) Mode

If IN is set to high, the output stage is powered on, and device enters normal or CL mode of operation depending on the state prior to turn on. In case of turn on (IN = Lo  $\rightarrow$  Hi) from sleep mode, the device automatically transitions into CL (capacitive load) mode where the turn on slew rate is reduced and corresponding turn on time is increased. This allows for a delayed turn on profile to charge any capacitive loads connected to the output of the device. The retry strategy and protection features are tailored to charge a capacitive load as described in the section Capacitive Load Switching. Further, the exit conditions from CL mode are also described in this section. In case of PWM operation, device stays in CL mode unless one of the exit conditions is met. PWM frequency and duty cycle should be set externally to ensure that load is sufficiently charged in required time. If CS\_EN is set to High, then diagnosis is available in CL mode.

#### d. Normal Mode

Once the capacitive load is fully charged, the device transitions to normal mode. The turn on timing and slew in this mode are designed to support faster switching operation. The current sense pin outputs a current proportional to the load current if CS\_EN is set to high. In case the capacitive load switching is not required in the application, it is recommended to switch on CS\_EN before forcing the input Lo → Hi from sleep. This ensures that device enters normal mode once input is enabled. The minimum time between CS\_EN: Lo → Hi and IN: Lo → Hi should be more than  $t_{Norm.}$  for the output stage to turn subsequently on in normal mode. If already in CL mode, the normal mode can still be entered by meeting one of the exit conditions described in Capacitive Load Switching mode. Similar to the CL mode, device can be driven in PWM operation in normal mode. If IN and CS\_EN are both forced low for a period greater than  $t_{IN(Rst)}$  and  $I^2t$  monitor equals zero, then device enters sleep mode.

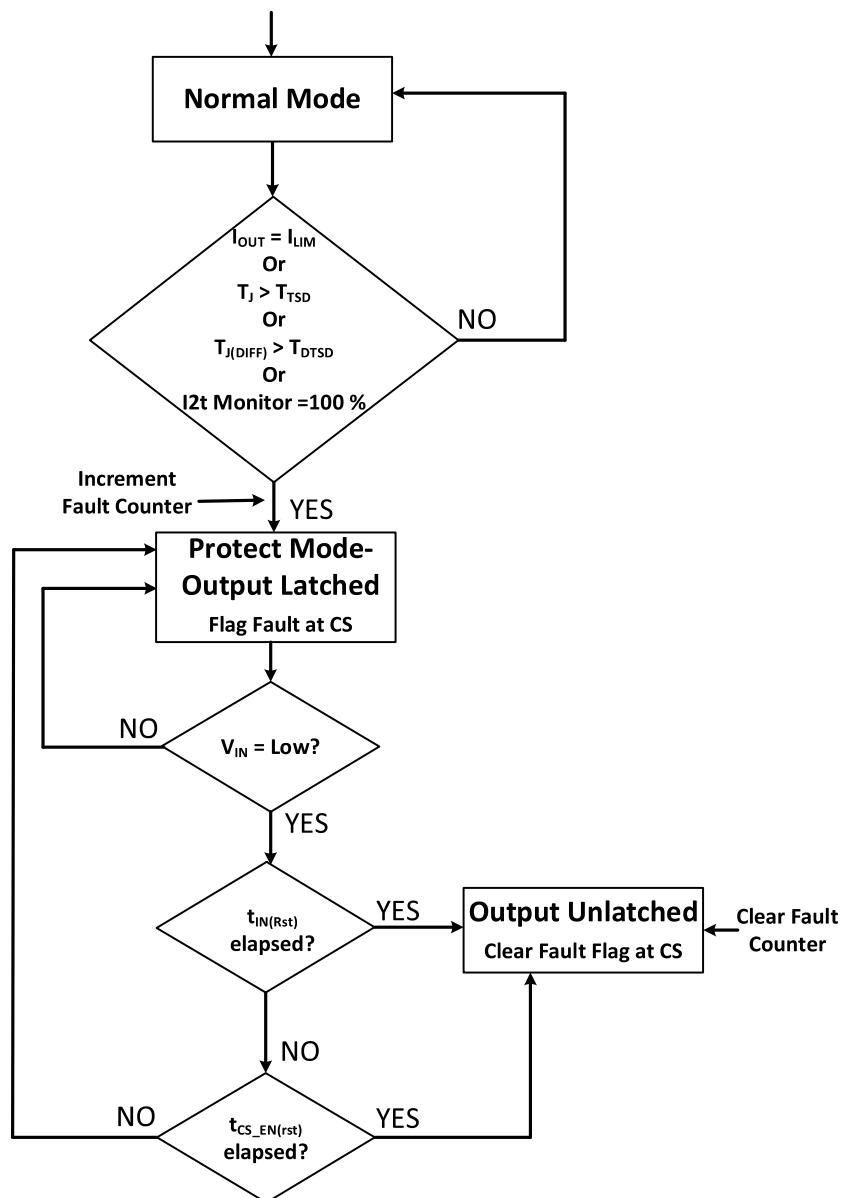

#### e. Protect Mode

While operating in normal mode, the device may observe either of the fault conditions described in Protection Features, that trigger protect mode and lead to latching-off of the output stage. A fault current output on the CS pin will be provided if CS\_EN is enabled. The reset conditions for the fault counter are described in section ON State Fault Retry Strategy. If any of the reset conditions are met, device exits protect mode. ON state fault takes precedence over Off State Open Load (OSOL) in off state if fault counter is greater than zero.

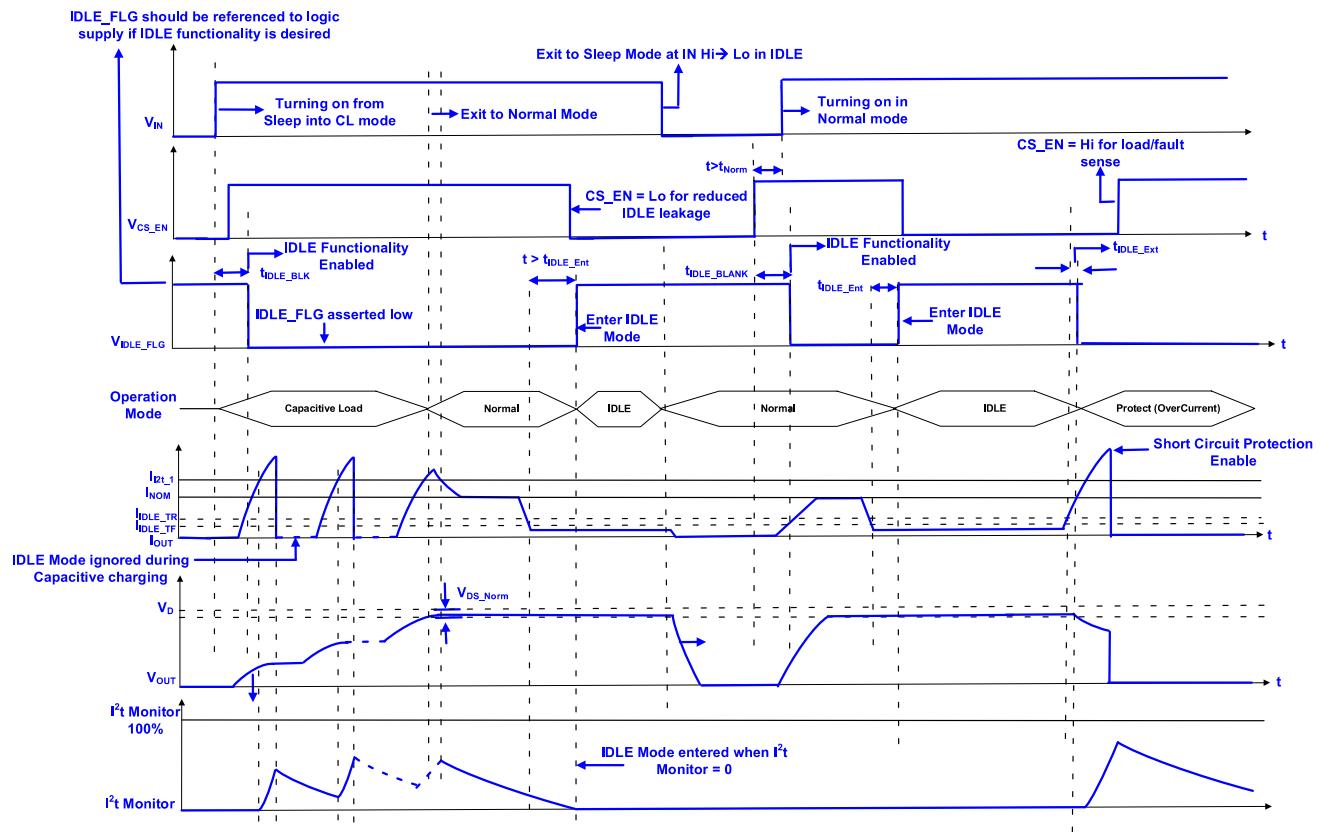

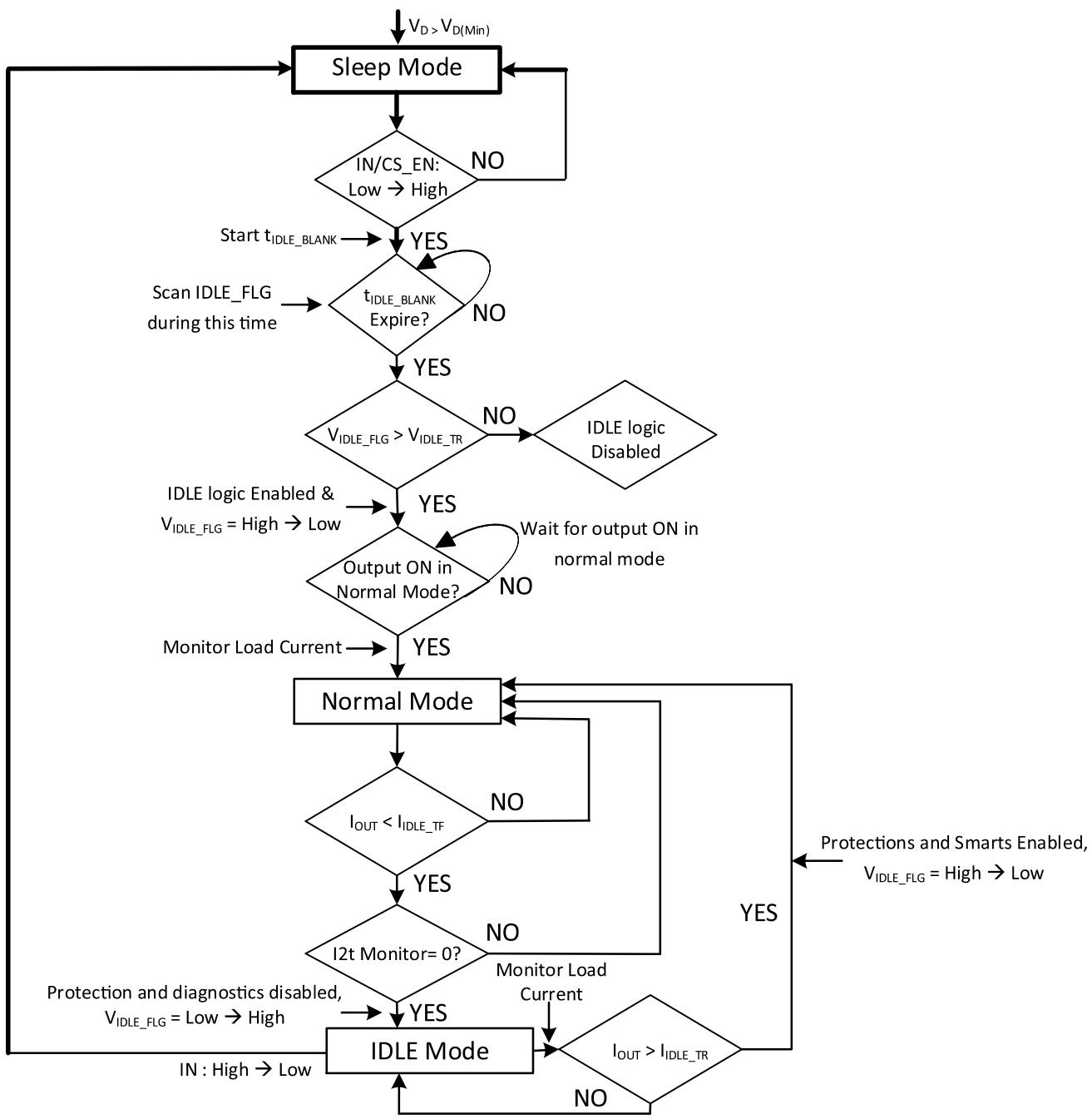

#### f. IDLE mode

A dedicated IDLE mode has been designed in NCV84003G for applications that require reduced operating current while the output stage is turned on (at relatively small output current levels) over extended periods. These applications may, for example, involve the SmartFET providing power to electronic modules that require a software routine to be executed while the car is parked. In such case, limiting the operating current is very critical to reduce the current consumption of the automotive system. The open drain IDLE\_FLG pin allows the microcontroller to control the IDLE functionality as explained below.

If IDLE mode is desired in an application, IDLE\_FLG pin needs to be supplied with logic level voltage with a pull-up resistor. As the internal logic is activated from sleep mode (by asserting either/both IN/CS\_EN high), it executes an internal routine to sense the voltage referenced at this pin. If the sensed voltage is greater than the threshold described in

Table 6, then IDLE mode detection is enabled. This routine is associated with a blanking time, per Table 14, during which, a decision to enable IDLE functionality is still being determined.

Once the blanking time has elapsed and IDLE functionality is enabled, NCV84003G automatically detects an entry into IDLE mode by sensing the level of output current. Current thresholds for IDLE mode entry and exit are defined in Table 5. If the output current falls below  $I_{IDLE\_TF}$  while IN = Hi, then device enters IDLE mode. The  $R_{ON}$  of the output stage in this mode is higher than normal mode  $R_{ON}$  (See Table 5) while conducting extremely low operating current out of the GND pin (See Table 4). Protection mechanisms in the form of overcurrent, undervoltage and thermal shutdown are not available during operation in this mode. In addition, the current sense output and diagnosis are turned off. The CS\_EN input is recommended to be forced low in this mode to limit the operating current.

If the IDLE\_FLG pin is connected to GND (via a resistor), then IDLE functionality is disabled, and device continues to operate in normal mode even if load transitions to current levels below  $I_{IDLE\_TF}$  while IN = High. Current sense output and protection features also operate as usual in such case. This implementation lets the application microcontroller to decide if IDLE functionality should be present or not by controlling the reference supply to IDLE\_FLG pin.

It should be noted that the internal routine for activating IDLE mode detection is only performed once at exit from sleep mode, or in case of digital logic reset with  $V_D < V_{D\_UV}$ , i.e., the reference supply at IDLE\_FLG pin will not be continuously sensed for in normal operation. Therefore, for applications that do require IDLE mode functionality, this pin should always be supplied with logic voltage before attempting to switch on the output or activate any diagnostics.

Further, an entry into IDLE mode is prohibited, a.) in CL mode, or b.) if  $I^2t$  monitor is greater than zero or c.) if the sensed current is low because of a fault counter being latched in case of an ON-State fault (See ON State Fault Retry Strategy). For example, if  $I_{OUT} < I_{IDLE\_TF}$  as the output stage is turned on from sleep into CL mode, the decision to enter IDLE mode will not be made until the IDLE blanking time (as defined above) has elapsed and the device has transitioned to normal mode. In typical cases, this time is at-least  $t_{ON\_CL} + t_{IDLE\_Ent}$ , where  $t_{IDLE\_Ent}$  is the transition time to IDLE mode from normal mode (note that IDLE blank routine executes in parallel with the output stage turn on).

The IDLE\_FLG pin serves a dual purpose by also indicating the status of the IDLE mode in the application. If the IDLE mode functionality is enabled and the output current reduces below  $I_{IDLE\_TF}$ , then open drain IDLE\_FLG output observes a logic high voltage to indicate operation in IDLE mode, and vice versa. The state of this pin should be

disregarded during the IDLE blanking time during which IDLE functionality is being sensed for.

While operating in IDLE mode, if the output current increases above  $I_{IDLE\_TR}$ , such as in case of overload, short circuit to GND or normal load activation, then device exits into Normal mode and all the protection features are enabled. The voltage at IDLE\_FLG pin is asserted low indicating an entry into normal mode. The response time for the device to enter normal mode is described in Table 7.

If the input is asserted high → low during operation in IDLE mode to switch off the output stage, then the device directly enters the sleep mode.

The following timing diagram depicts the transitions in and out of IDLE mode and the block diagram in Figure 6 describes IDLE operation internal to the device.

The flowchart in Figure 8 summarizes the sequence of operations associated with IDLE functionality.

**Figure 5. NCV84003G Operation Modes and Transitions**

**Table 18. STATE TRANSITION TABLE**

| Present State | Target State         | Transition Criteria                                      | Transition Qualifier                                                                                   |

|---------------|----------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| UNPOWERED     | SLEEP MODE           | $V_D > V_{D\_MIN}$                                       | -                                                                                                      |

| SLEEP MODE    | CAPACITIVE LOAD MODE | $IN = Low \rightarrow High$                              | -                                                                                                      |

| SLEEP MODE    | STANDBY MODE         | $CS\_EN = Low \rightarrow High$<br>- AND -<br>$IN = Low$ | -                                                                                                      |