### **Integrated Driver and MOSFET**

PQFN31-5x5 Halogen-Free & Lead-Free

NDC300RA

### Table 1. PIN LIST AND DESCRIPTIONS

| Pin No. | Symbol | Description                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1       | PWM    | PWM Signal Input. Connect this pin to the PWM output of the controller.                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 2       | SMOD#  | <ul> <li>SMOD# is used to control diode emulation mode. When SMOD# is "LOW", diode emulation mode is allowed . When SMOD# is "HIGH", continuous conduction mode is forced. SMOD# can also be put in a high impedance mode by floating the pin. I both SMOD# and PWM are floated, the device shuts down and operates at low current consumption mode.</li> </ul> |  |  |  |  |

| 3       | VCC    | Power supply of internal control logic. The required bias voltage for VCC is 5V. For avoiding noise disturbance, the supplied bias voltage must be stable.                                                                                                                                                                                                      |  |  |  |  |

| 4       | CGND   | Internally connected to PGND paddle.                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 5       | BOOT   | Bootstrap Supply for High Side Gate Drive.                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 6       | NC     | No Connect                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 7       | PHASE  | Phase pad. Connect this pad to the Source of the high side FET and the Drain of the low side FET.                                                                                                                                                                                                                                                               |  |  |  |  |

| 8-11    | VIN    | Power stage High Voltage Input (Drain connection of High-Side MOSFET).                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 12-15   | PGND   | Power Ground.                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 16-26   | VSW    | Switching node connected to the Source of High-Side MOSFET and the Drain of Low-Side MOSFET. These pins are used for Zero Cross Detection and Anti-Overlap Control as well as main inductor terminal.                                                                                                                                                           |  |  |  |  |

| 27,33   | GL     | Low Side FET Gate Access (pin 27 and pad 33 are internally connected)                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 28,32   | PGND   | Power Ground pin for High-Side and Low-Side MOSFET Gate Drivers.                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 29      | VCCD   | Power supply of gate driver. The required bias voltage for VCCD is 5V.                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 30      | NC     | No Connect                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 31      | NC     | No Connect                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

### Integrated Driver and MOSFET

### NDC300RA PQFN31-5x5 Halogen-Free & Lead-Free

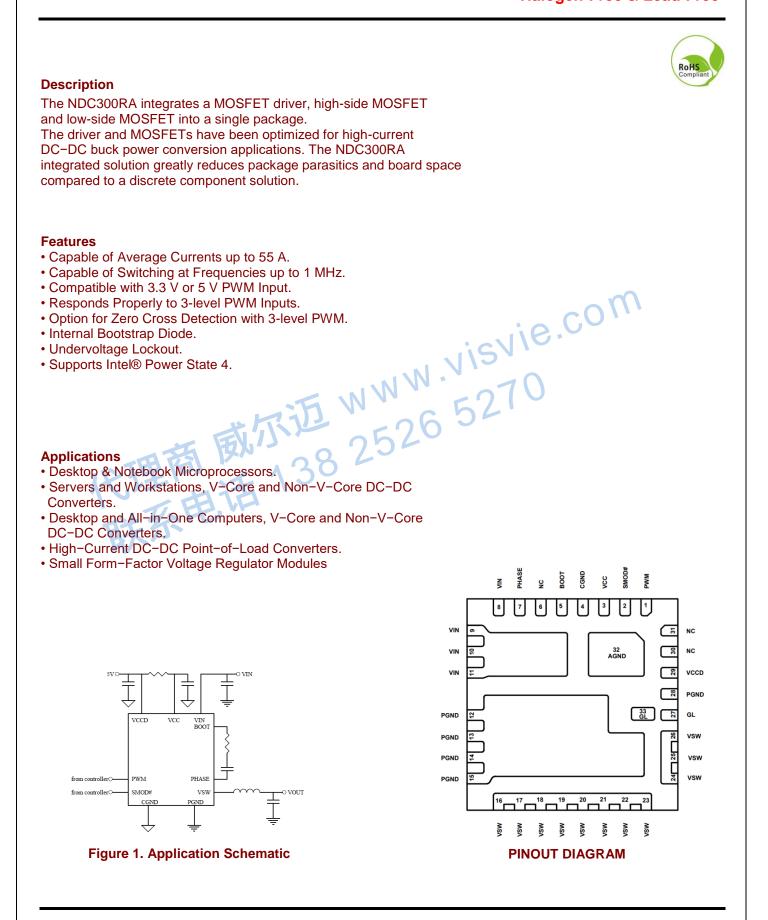

### POR (Power On Reset)

POR block detects the voltage of the VCC pin. When the VCC pin voltage is higher than POR rising hreshold, POR block output is high. POR output is low when VCC is not higher than POR rising threshold. When the POR block output is high, UGATE and LGATE can be controlled by PWM input voltage. If the POR block output is low, both UGATE and LGATE will be pulled to low.

#### **Enable Detect**

When SMOD# pin input voltage is higher/lower than SMOD# rising threshold, MOSFET driver is enabled/disabled. When the SMOD# input and POR output are high, UGATE and LGATE can be controlled by PWM input voltage. When SMOD# input is low, both UGATE and LGATE are pulled to low, and the PWM input terminal is opened.

#### **Tri-State Detect**

When both POR block output and SMOD# pin voltages are high, UGATE and LGATE can be controlled by PWM input. There are three PWM input modes, which are high, low, and tri-state. If PWM input is within the tri-state window, both UGATE and LGATE outputs are low. When PWM input is higher than its rising threshold, UGATE is high and LGATE is low. When PWM input is lower than its falling threshold, UGATE is low and LGATE is high

#### **Bootstrap Control**

Bootstrap control block controls the integrated bootstrap switch. When LGATE is high (low side MOSFET is turned on), the bootstrap switch is turned on to charge the bootstrap capacitor connected to the BOOT pin. When LGATE is low (low side MOSFET is turned off), the bootstrap switch is turned off to disconnect the VCC pin and BOOT pin

### **Turn-Off Detection**

Turn-off detection block detects whether high side MOSFET is turned off by monitoring PHASE pin voltage. To avoid shoot-through between high side and low side MOSFETs, low side MOSFET can be turned on only after high side MOSFET is effectively turned off.

#### **Shoot-Through Protection**

Shoot-through protection block implements the dead time when both high side and low side MOSFETs are turned off. With shoot-through protection block, high side and low side MOSFETs are never turned on simultaneously. Thus, shoot through between high side and low side MOSFETs is prevented.

### **Integrated Driver and MOSFET**

NDC300RA PQFN31-5x5 Halogen-Free & Lead-Free

# Table 2. ABSOLUTE MAXIMUM RATINGS (Electrical Information-all signals referenced to PGND unless noted otherwise)

| Pin Name/Parameter | Min  | Max  | Unit |

|--------------------|------|------|------|

| Supply Voltage     | -0.3 | +6.5 | V    |

| VIN                |      | 30   | V    |

| BOOT to PHASE      | -0.3 | +6.8 | V    |

| PHASE to GND       | -0.3 | +50  | V    |

| LGTAE to GND       | -0.3 | +6.8 | V    |

| UGATE to PHASE     | -0.3 | +6.8 | V    |

| EN, PWM to GND     | -0.3 | 6.8  | V    |

| Tstg               | -65  | +150 | 0.7  |

| TJ                 |      | 150  | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

### Table 3. THERMAL INFORMATION

| Rating                     | Symbol        | Value | Unit  |

|----------------------------|---------------|-------|-------|

| Thermal Resistance         | $\theta_{JA}$ | 12.5  | °C /W |

| Maximum Power Dissipation  |               | 10.4  | W     |

| Moisture Sensitivity Level | MSL           | 1     |       |

1. JESD 51-5 (1S2P Direct-Attach Method) with 0 LFM.

2. JESD 51-7 (1S2P Direct-Attach Method) with 0 LFM.

### Table 4. RECOMMENDED OPERATING CONDITIONS

| Parameters                 | Pin Name        | Conditions                                                                                              | Min. | Тур. | Max. | Unit |

|----------------------------|-----------------|---------------------------------------------------------------------------------------------------------|------|------|------|------|

| Supply Voltage             | V <sub>CC</sub> |                                                                                                         | 4.5  |      | 5.5  | V    |

| Junction Temperature Range |                 |                                                                                                         | -10  |      | 105  | °C   |

| Continuous Output Current  |                 | $F_{SW} = 1 \text{ MHz}, V_{IN} = 12 \text{ V},$<br>$V_{OUT} = 1.0 \text{ V}, T_A = 25^{\circ}\text{C}$ |      |      | 55   | А    |

### Integrated Driver and MOSFET

### NDC300RA PQFN31-5x5

Halogen-Free & Lead-Free

| Peak Output Current V <sub>OUT</sub> = 1 | = 10 ms, Period = 1 s, | A |

|------------------------------------------|------------------------|---|

|------------------------------------------|------------------------|---|

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

### Table 5. ELECTRICAL CHARACTERISTICS

VIN = 12 V, VCC = 5 V, TA =-40 °C to 125 °C, unless otherwise noted.(UG\_CISS=6000pF, LG\_CISS=10000pF).

| Parameters                                  | Symbol                                   | Conditions                          | Min. | Тур. | Max. | Unit |  |

|---------------------------------------------|------------------------------------------|-------------------------------------|------|------|------|------|--|

| POWER SUPPLY                                |                                          |                                     |      |      |      |      |  |

| PS4 power supply current                    | I <sub>IN Stby</sub>                     | PWM=Hi-Z, V <sub>SMOD#</sub> = Hi-Z |      |      | 5    |      |  |

|                                             |                                          | V <sub>PWM</sub> = FLOAT            |      | 20   |      | uA   |  |

| Control Logic Supply Current                | I <sub>VCC</sub>                         | $V_{PWM} = FLOAT, V_{SMOD\#} = 0 V$ |      | 112  |      | UA   |  |

|                                             |                                          | f <sub>s</sub> = 1MHz, D = 0.1      |      | 131  |      |      |  |

| Drive Supply Current                        |                                          | f <sub>s</sub> = 300 kHz, D = 0.1   |      | 9    |      | mA   |  |

| Drive Supply Current                        | I <sub>VCCD</sub>                        | f <sub>S</sub> = 1 MHz, D = 0.1     |      | 31   |      |      |  |

| PWM CONTROL INPUT                           |                                          |                                     |      |      |      |      |  |

| Rising Threshold(5V logic)                  | $V_{\text{TH}_{PWM}_{R}}$                |                                     | 3.55 | 3.8  | 4.05 | V    |  |

| Falling Threshold(5V logic)                 | V <sub>TH_PWM_F</sub>                    |                                     | 0.72 | 1    | 1.3  | V    |  |

| PWM Tri-state Threshold window (5V logic)   | V <sub>TRI_TH</sub>                      | $V_{PWM} = FLOAT$                   | 1.2  |      | 3.7  | V    |  |

| Tri-state Voltage                           | V <sub>TRI</sub>                         | V <sub>PWM</sub> = FLOAT            |      | 1.8  |      | V    |  |

| DW/M Input Current                          |                                          | $V_{PWM} = 5V$                      |      |      | 350  | uA   |  |

| PWM Input Current                           | I <sub>PWM</sub>                         | $V_{PWM} = 0V$                      |      |      | -350 | uA   |  |

| SMOD# CONTROL INPUT                         |                                          |                                     |      |      |      |      |  |

| Rising Threshold(5V logic)                  | $V_{TH\_SMOD\#\_R}$                      |                                     | 3.55 | 3.8  | 4.05 |      |  |

| Falling Threshold(5V logic)                 | $V_{\text{TH}\_\text{SMOD}\#\_\text{F}}$ |                                     | 0.72 | 0.9  | 1.3  |      |  |

| SMOD# Tri-state Threshold window (5V logic) | V <sub>TRI_TH_SMOD#</sub>                | $V_{SMOD\#} = FLOAT$                | 1.2  |      | 3.7  | V    |  |

| Tri-state Voltage                           | V <sub>TRI_SMOD#</sub>                   | $V_{ZCD\_EN00\#} = FLOAT$           |      | 1.7  |      |      |  |

| SMOD# Input Current                         |                                          | $V_{SMOD\#} = 5V$                   |      |      | 100  | uA   |  |

| SMOD# Input Current                         | I <sub>SMOD#</sub>                       | $V_{SMOD\#} = 0V$                   |      |      | -100 | uA   |  |

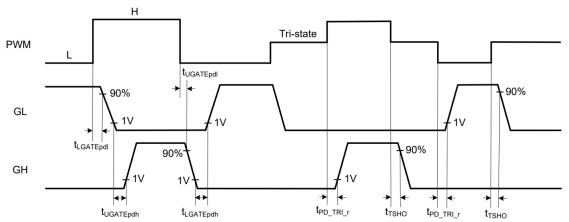

| TIMING SPECIFICATIONS                       |                                          |                                     |      |      |      |      |  |

| Minimum UG On-time                          | TONmin                                   |                                     |      | 56   |      | ns   |  |

| Dead time(rising/falling)                   | DT                                       |                                     |      | 30   |      | ns   |  |

### Integrated Driver and MOSFET

# NDC300RA

PQFN31-5x5 Halogen-Free & Lead-Free

| Tri-State Hold-Off Time                        | t <sub>тsно</sub>      |                            |     | 50  |     | ns |

|------------------------------------------------|------------------------|----------------------------|-----|-----|-----|----|

| Tri-State to GH/GL Rising<br>Propagation Delay | t <sub>PD_TRI_R</sub>  |                            |     | 20  |     | ns |

| GH - Turn Off Propagation<br>Delay             | t <sub>PD_OFF_GH</sub> |                            |     | 18  |     | ns |

| GL - Turn Off Propagation<br>Delay             | t <sub>PD_OFF_GL</sub> |                            |     | 10  |     | ns |

| PROTECTION                                     |                        |                            |     |     |     |    |

| Linder Veltage Leekeut                         | M                      | VCC rising, on threshold   |     | 4   | 4.3 | V  |

| Under Voltage Lockout                          | V <sub>UVLO</sub>      | VCC falling, off threshold | 3.6 | 3.7 |     | V  |

| Under Voltage Lockout<br>Hysteresis            | V <sub>UVLO_HYST</sub> |                            |     | 335 |     | mV |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product per- formance may not be indicated by the Electrical Characteristics if operated under different conditions.

### Table 6. LOGIC TABLE

| PWM       | SMOD# | GH | GL                                             | DISB# |

|-----------|-------|----|------------------------------------------------|-------|

| L         | L     | L  | H, I <sub>L</sub> >0A<br>L, I <sub>L</sub> <0A | Н     |

| Н         | L     | Н  | L                                              | Н     |

| L         | Н     | L  | Н                                              | Н     |

| Н         | Н     | Н  | L                                              | Н     |

| Tri-State | L     | L  | L                                              | Н     |

| Tri-State | Н     | L  | L                                              | Н     |

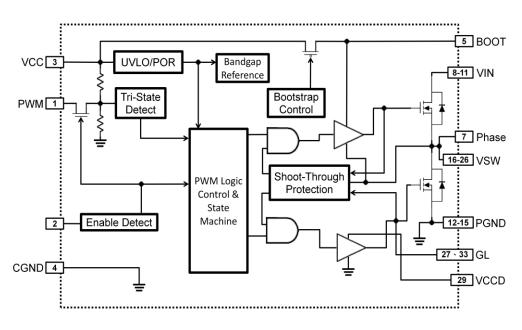

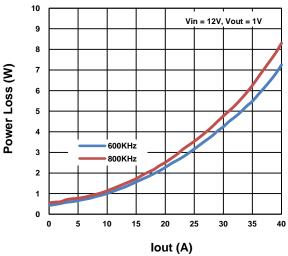

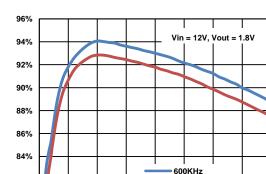

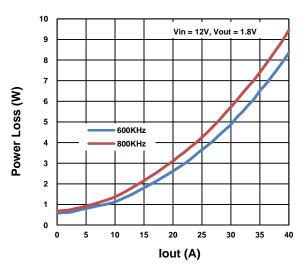

### **Typical Performance Characteristics**

(Test Conditions: VIN = 12 V, VCC = PVCC =5 V, VOUT =1 V & 1.8V, TA = 25°C, unless otherwise noted.)

Figure 3. Efficiency

Figure 4. Power Loss vs. Output Current

10

5

15

20

lout (A)

Figure 5. Efficiency

800KHz

25

35

40

30

Figure 6. Power Loss vs. Output Current

Efficiency (%)

82%

80%

78%

0

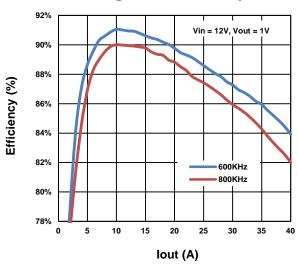

### **Typical Performance Characteristics**

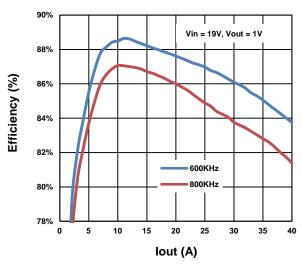

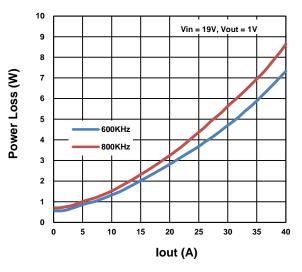

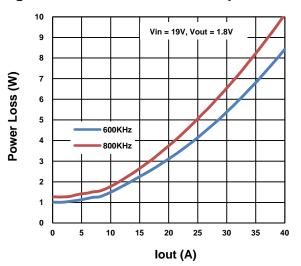

(Test Conditions: VIN = 19 V, VCC = PVCC =5 V, VOUT =1 V & 1.8V, TA = 25°C, unless otherwise noted.)

Figure 7. Efficiency

Figure 8. Power Loss vs. Output Current

94% Vin = 19V. Vout = 1.8V 92% 90% Efficiency (%) 88% 86% 84% 82% 600KHz 800KHz 80% 78% 0 5 10 15 20 25 30 35 40 lout (A)

**Figure 9. Efficiency**

Figure 10. Power Loss vs. Output Current

**Integrated Driver and MOSFET**

### NDC300RA PQFN31-5x5 Halogen-Free & Lead-Free

#### **Timing Diagram**

### **Application Information**

The NDC300RA is a high frequency, synchronous rectified, single phase dual MOSFET driver containing advanced MOSFET driver technologies. The NDC300RA is designed to be able to adapt from normal MOSFET driving applications to high performance CPU/GPU VR driving capabilities.

#### Supply Voltage and Power On Reset

The NDC300RA can be utilized under VCC = 5V application. The NDC300RA is designed to drive both high side and low side N-MOSFET through external input PWM control signal. It has a power on protection function which held UGATE and LGATE low before the VCC voltage rises to higher than rising threshold voltage.

#### **Enable and Disable**

The NDC300RA includes a SMOD# pin for sequence control.When the SMOD# pin rises above the  $V_{TH\_SMOD#\_R}$  trip point, the NDC300RA begins a new initialization and follows the PWM command to control the UGATE and LGATE. When the SMOD# pin falls below the  $V_{TH\_SMOD#\_F}$  trip point, the NDC300RA shuts down to keep UGATE and LGATE low and keep the PWM input terminal open. To avoid noise coupled, EN pin is recommended adding a bypass capacitor with de-glitch time of 400ns for the EN shutdown function.

### **Tri-state PWM Input**

After the initialization, the PWM signal takes control. The rising PWM signal first forces the LGATE signal to turn low then the UGATE signal is allowed to go high just after a non-overlapping time to avoid shootthrough current. The falling of the PWM signal first forces UGATE to go low. When UGATE and PHASE signals reach a predetermined low level, LGATE signal is allowed to turn high. The PWM signal acted as "High" if the signal is above the rising threshold and acted as "Low" if the signal is below the falling threshold. When the PWM signal level enters and remains within the tri-state window, the output drivers are disabled and both MOSFET gates are pulled and held low. If the PWM signal is left floating, the pin will be kept around 2.5V by the internal divider and provide the PWM controller with a recognizable level.

#### **Internal Bootstrap Power Switch**

The NDC300RA builds in an internal bootstrap power switch to replace the external bootstrap diode, and this can facilitate PCB design and reduce the total BOM cost of the system. Hence, no external bootstrap diode is required in real applications.

### **Integrated Driver and MOSFET**

### NDC300RA PQFN31-5x5 Halogen-Free & Lead-Free

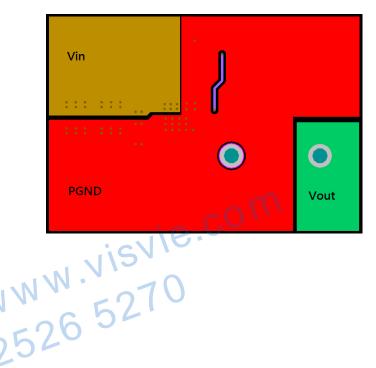

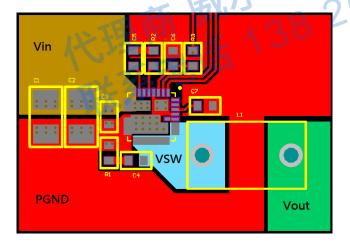

#### NDC300RA PCB layout guide

NDC300RA is a high-current-rated device capable of operating up to 1 MHz. Achieving such high frequency requires extremely fast switching speeds to keep switching losses and device temperatures within limits. Integrating a robust gate driver with MOSFETs in one package eliminates the parasitic components or PCB associated with the driver-to-MOSFET and between high side and low side MOSFETs, thus resulting in excellent switching speeds. However, correspondingly high levels of dv/dt and di/dt will be present throughout the power train which requires careful attention to PCB layout to minimize voltage spikes and other transients.

The PCB design is somewhat simplified because of the package integration and optimized pin assignment. The VIN and PGND pins are located adjacent to each other, and the input bypass capacitors (C1, C2, C3) should be placed as close as possible to these pins. The PHASE switching loop, formed by PHASE (VSW), output inductor (L1), and output capacitor COUT is the next critical current loop. This requires a second layer with an uninterrupted PGND plane with sufficient GND vias placed as close as possible to the bypass capacitor PGND pads.

To simplify thermal management, both VIN and GND pads should be attached to larger VIN and PGND planes directly using a number of vias. These vias provide a thermal connection to the copper layers under the NDC300RA, which then conduct heat away from the heat source, whereby the "electrical vias" also function as "thermal vias", It is essential to ensure that the cooper plane is not interrupted by tracks that run perpendicular to the thermal path away from the power component. The VCCD bypass capacitor CVCCD (C7) should connect directly to the

PGND plane, and a via should be used to connect CVCCD directly to the PGND plane. Finally, CBOOT (C5) and RBOOT(R2) should be connected directly to pins 5, and 7.