# NEX92X30-Q100

300 mA, dual-channel antenna LDO with current sensing

Rev. 1 — 1 August 2025 Product data sheet

# 1. General description

The NEX92x30-Q100 devices are dual-channel, high-voltage low-dropout (LDO) regulators with current sensing, they are designed to operate with a wide range of voltage from 4 V to 40 V (45 V load dump protection). These devices provide power supply for low noise amplifiers with an active antenna through a coax cable with 300 mA per channel. It provides an adjustable output voltage from 1.5 V to 20 V for each channel.

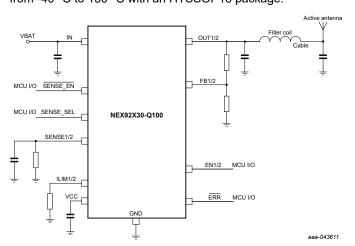

These devices provide diagnostics through current sensing and error pins. To monitor the load current, a high-side current-sense circuitry provides a proportional analog output to the sensed load current. Accurate current sensing allows detection of open, normal, and short-circuit conditions without the need for further calibration, and current sensing multiplexing is allowed between channels to conserve analog-to-digital converter (ADC) resources. Each channel also implements adjustable current limits with an external resistor. Fig. 1 shows the typical application.

The device integrates short-circuit, over-current, thermal shutdown, short-to-battery and reverse current protections. Each channel has internal inductive clamp protection on the output during inductive switch-off. It can operate at ambient temperatures ranging from -40 °C to 125 °C and junction temperatures ranging from -40 °C to 150 °C with an HTSSOP16 package.

Fig. 1. Typical application

### 2. Features and benefits

- AEC-Q100 qualified for automotive applications

- Ambient temperature (T<sub>amb</sub>): -40 °C to 125 °C

- Junction temperature (T<sub>i</sub>): -40 °C to 150 °C

- Input voltage range: 4 V to 40 V (45 V transient)

- Output voltage range: 1.5 V to 20 V adjustable

- Maximum output current: 300 mA per channel

- High accuracy current sensing to detect antenna/ MIC open conditions at low current

- · Adjustable current limit by an external resistor

- High power supply ripple rejection (PSRR): typical 80 dB at 100 Hz

- Low dropout voltage:

- 500 mV typical at 300 mA (V<sub>OUT</sub> = 8.5 V)

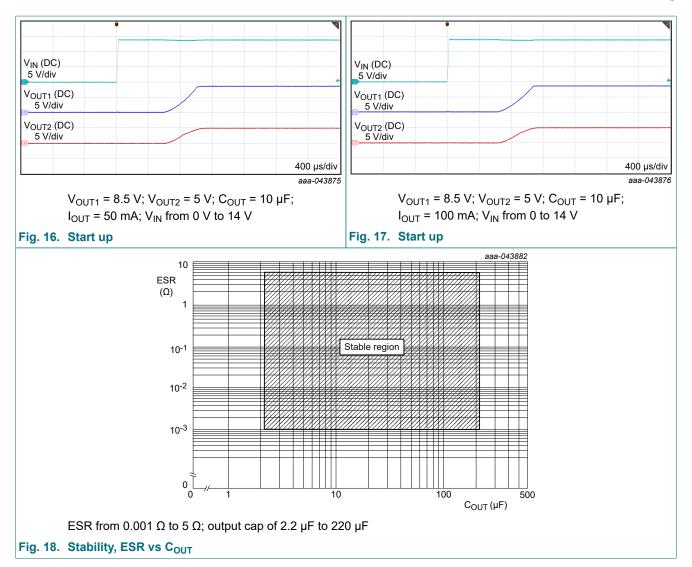

- Stable with a wide range of ceramic output-stability cap:

- ESR from 0.001  $\Omega$  to 5  $\Omega;$  output cap of 2.2  $\mu F$  to 220  $\mu F$

- Integrated various fault protections:

- · Thermal shutdown

- · Short-circuit and over-current protection

- · Reverse-current protection

- Output short-to-battery protection

- · Output inductive load clamp

- Multiplexing current sensing between channels and devices

- · Ability to identify all faults with current sensing

- 16-pin HTSSOP enhanced thermal pad package

# 3. Applications

- Infotainment active-antenna power supplies

- Automotive MIC power supplies

- Camera power supplies

- High-side power switches for small current applications

#### **Table 1. Device information**

| Part number       | Channel | Version    |  |  |  |  |  |

|-------------------|---------|------------|--|--|--|--|--|

| NEX92730DPCD-Q100 | Dual    | Latch      |  |  |  |  |  |

| NEX92830DPCD-Q100 | Dual    | Auto-retry |  |  |  |  |  |

# 4. Ordering information

### **Table 2. Ordering information**

| Type number       | Temperature range (T <sub>j</sub> ) | Name | Description                                                             | Version   |

|-------------------|-------------------------------------|------|-------------------------------------------------------------------------|-----------|

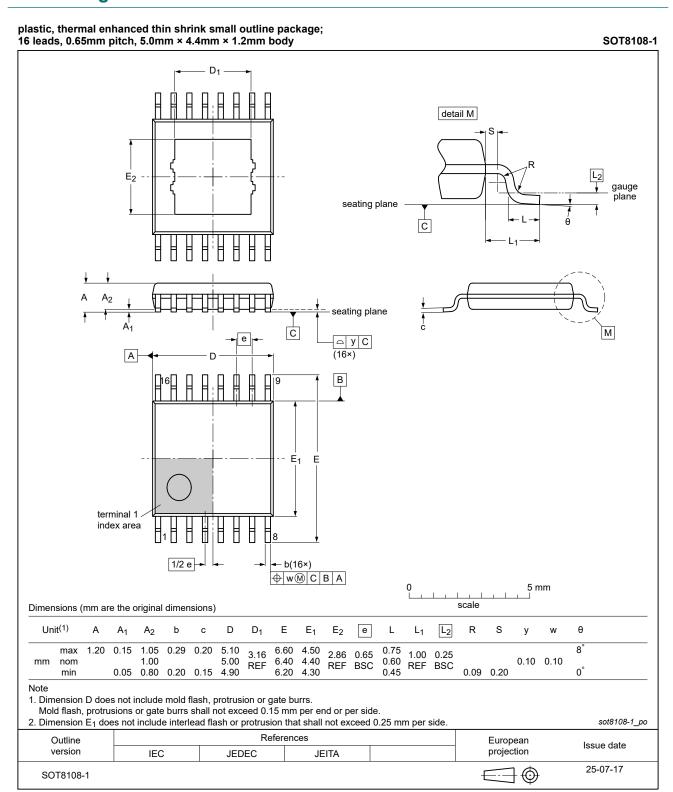

| NEX92730DPCD-Q100 |                                     |      | plastic, thermal enhanced thin shrink small                             |           |

| NEX92830DPCD-Q100 | 1-40 °C to 150 °C                   |      | outline package; 16 leads; 0.65 mm pitch; 5.0 mm x 4.4 mm x 1.2 mm body | SOT8108-1 |

# 5. Marking

### Table 3. Marking code

| Type number       | Marking code |

|-------------------|--------------|

| NEX92730DPCD-Q100 | N92730D      |

| NEX92830DPCD-Q100 | N92830D      |

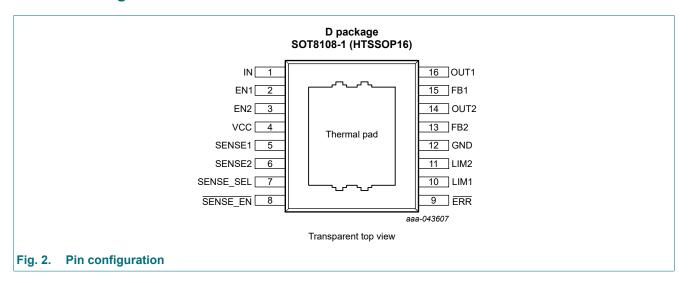

# 6. Pin configuration and description

# 6.1. Pin configuration

# 6.2. Pin description

| Symbol    | Pin                                                                                     | Description |                                                                                                                                                                                                                                                                                                                                |  |

|-----------|-----------------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IN 1 PWR  |                                                                                         | PWR         | The input power-supply voltage pin should take the recommended value or a larger ceramic capacitor from IN to ground for optimal transient response and minimal input impedance. Place the input capacitor as close to the device's input as possible.                                                                         |  |

| EN1       | 2 I The enable logic pin activates the device when at a high level and disables it at a |             |                                                                                                                                                                                                                                                                                                                                |  |

| EN2       | 3                                                                                       | I           | The enable logic pin activates the device when at a high level and disables it at a low level.                                                                                                                                                                                                                                 |  |

| VCC       | 4                                                                                       | 0           | Internal 4.5 V regulator. Connect a 1 µF ceramic capacitor between VCC and GND for frequency compensation.                                                                                                                                                                                                                     |  |

| SENSE1    | 5                                                                                       | 0           | Output of current sensing for channel 1 sensing when SENSE_SEL and SENSE_EN are low.  To set the SENSE1 output voltage level, connect a resistor between this pin and GND. In addition, connect a 1 µF capacitor from this pin to GND for frequency compensation of the current-sense loop. Short this pin to GND if not used. |  |

| SENSE2    | 6                                                                                       | 0           | Output of current sensing for channel 2 sensing when SENSE_SEL and SENSE_EN are low.  To set the SENSE1 output voltage level, connect a resistor between this pin and GND. In addition, connect a 1 µF capacitor from this pin to GND for frequency compensation of the current-sense loop. Short this pin to GND if not used. |  |

| SENSE_SEL | 7                                                                                       | I           | This pin selects the current sensing between channel 1 and channel 2.                                                                                                                                                                                                                                                          |  |

| SENSE_EN  | 8                                                                                       | I           | This pin enables and disables the current sensing pin for multiplexing, active-low enabled.                                                                                                                                                                                                                                    |  |

| ERR       | 9                                                                                       | 0           | Fault pin. It is an open-drain fault indicator for general faults.                                                                                                                                                                                                                                                             |  |

| LIM1      | 10                                                                                      | O           | Programmable current-limit pin for channel 1. Connect a resistor to GND to set the current-limit level. This pin does not need an external capacitor. To set to internal current limit, short this pin to GND.                                                                                                                 |  |

| LIM2      | 11                                                                                      | 0           | Programmable current-limit pin for channel 2. Connect a resistor to GND to set the current-limit level. This pin does not need an external capacitor. To set to internal current limit, short this pin to GND.                                                                                                                 |  |

| Symbol      | Pin | I/O | Description                                                                                            |

|-------------|-----|-----|--------------------------------------------------------------------------------------------------------|

| GND         | 12  | G   | Ground pin. Connect this pin to the thermal pad with a low-impedance connection.                       |

| FB2         | 13  | I   | Feedback input for setting OUT2 voltage. Connect FB2 to GND for switch mode operation.                 |

| OUT2        | 14  | PWR | Regulated output voltage pin for channel 2. A capacitor is required from OUT2 to ground for stability. |

| FB1         | 15  | I   | Feedback input for setting OUT1 voltage. Connect FB1 to GND for switch mode operation.                 |

| OUT1        | 16  | PWR | Regulated output voltage pin for channel 1. A capacitor is required from OUT1 to ground for stability. |

| Thermal pad | Pad | -   | The exposed thermal pad should be soldered to GND for improved thermal performance.                    |

# 7. Limiting values

#### **Table 4. Limiting values**

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).[1]

| Symbol                                                            | Parameter                       | Conditions        | Min  | Max       | Unit |

|-------------------------------------------------------------------|---------------------------------|-------------------|------|-----------|------|

| V <sub>IN</sub>                                                   | input voltage                   | unregulated input | -42  | 45        | V    |

| V <sub>EN1</sub> , V <sub>EN2</sub>                               | enable voltage                  |                   | -0.3 | 45        | V    |

| V <sub>OUT1</sub> , V <sub>OUT2</sub>                             | output voltage                  |                   | -0.3 | 45        | V    |

| VCC                                                               | output voltage                  |                   | -0.3 | 6.6       | V    |

| V <sub>SENSE1</sub> , V <sub>SENSE2</sub>                         | sense voltage                   |                   | -0.3 | VCC + 0.3 | V    |

| V <sub>LIM1</sub> , V <sub>LIM2</sub> ,                           | limit voltage                   |                   | -0.3 | 6.6       | V    |

| V <sub>SENSE_EN</sub> , V <sub>SENSE_SEL</sub> , V <sub>ERR</sub> | sense control and fault voltage |                   | -0.3 | 6.6       | V    |

| V <sub>FB1</sub> , V <sub>FB2</sub>                               | feedback voltage                |                   | -0.3 | 6.6       | V    |

| T <sub>amb</sub>                                                  | ambient temperature             |                   | -40  | 125       | °C   |

| T <sub>j</sub>                                                    | junction temperature            |                   | -40  | 150       | °C   |

| T <sub>stg</sub>                                                  | storage temperature             |                   | -65  | 165       | °C   |

<sup>[1]</sup> Stresses beyond those conditions under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 8. ESD ratings

#### **Table 5. ESD ratings**

| Symbol           | Parameter         | Conditions                               | Min   | Тур | Max  | Unit |

|------------------|-------------------|------------------------------------------|-------|-----|------|------|

| V <sub>ESD</sub> | electrostatic     | HBM: ANSI/ESDA/JEDEC JS-001 class 2 [1]  | -2000 | -   | 2000 | V    |

| VESD             | discharge voltage | CDM: ANSI/ESDA/JEDEC JS-002 class C3 [2] | -1000 | -   | 1000 | V    |

<sup>[1]</sup> HBM stress testing was performed in accordance with AEC-Q100-002.

<sup>[2]</sup> CDM stress testing was performed in accordance with AEC-Q100-011.

# 9. Thermal information

#### **Table 6. Thermal information**

Thermal resistance according to JEDEC51-5 and -7.

| Symbol               | Parameter                                 | SOT8108-1 (HTSSOP16) | Unit |

|----------------------|-------------------------------------------|----------------------|------|

| $R_{\theta JA}$      | junction to ambient thermal resistance    | 41.2                 | °C/W |

| $R_{\theta JC(top)}$ | junction to case (top) thermal resistance | 25.0                 | °C/W |

| $R_{\theta JB}$      | junction to board thermal resistance      | 24.5                 | °C/W |

| $\Psi_{JT}$          | junction to top char parameter            | 3.4                  | °C/W |

# 10. Recommended operating conditions

Table 7. Recommended operating conditions

| Symbol                                                            | Parameter                         | Conditions  | Min   | Тур | Max | Unit |

|-------------------------------------------------------------------|-----------------------------------|-------------|-------|-----|-----|------|

| V <sub>IN</sub>                                                   | input voltage                     |             | 4     |     | 40  | V    |

| V <sub>EN1</sub> , V <sub>EN2</sub>                               | enable voltage                    |             | 0     |     | 40  | V    |

| V <sub>OUT1</sub> , V <sub>OUT2</sub>                             | output voltage                    | normal-mode | 1.5   | -   | 20  | V    |

| VOUT1, VOUT2                                                      | output voltage                    | switch-mode | 2     | -   | 36  | V    |

| VCC                                                               | output voltage                    |             | 0     | -   | 5.3 | V    |

| V <sub>SENSE1</sub> , V <sub>SENSE2</sub>                         | sense voltage                     |             | 0     | -   | 5.3 | V    |

| V <sub>LIM1</sub> , V <sub>LIM2</sub> ,                           | limit voltage                     |             | 0     | -   | 5.3 | V    |

| V <sub>SENSE_EN</sub> , V <sub>SENSE_SEL</sub> , V <sub>ERR</sub> | sense control and fault voltage   |             | 0     | -   | 5.3 | V    |

| V <sub>FB1</sub> , V <sub>FB2</sub>                               | feedback voltage                  |             | 0     | -   | 5.3 | V    |

| C <sub>OUT</sub>                                                  | output capacitor stability range  | [1]         | 2.2   | -   | 220 | μF   |

| ESR                                                               | output capacitor ESR requirements | [2]         | 0.001 | -   | 5   | Ω    |

| T <sub>amb</sub>                                                  | ambient temperature               |             | -40   | -   | 125 | °C   |

| Tj                                                                | junction temperature              |             | -40   | -   | 150 | °C   |

<sup>[1]</sup> Effective output capacitance of 1  $\mu F$  minimum required for stability.

<sup>[2]</sup> Relevant ESR value at f = 10 kHz. If a large ESR capacitor is used, it is recommended to decouple it with a 100 nF ceramic capacitor to improve transient performance.

# 11. Electrical characteristics

#### **Table 8. Electrical characteristics**

At recommended operating conditions,  $T_j$  = -40 °C to 150 °C;  $C_{OUT}$  = 2.2  $\mu$ F;  $V_{IN}$  = 13.5 V;  $I_{OUT}$  = 100  $\mu$ A;  $V_{EN}$  = 2 V; unless otherwise noted, voltages are referenced to GND (ground = 0 V).

| Symbol                       | abol Parameter Conditions          |                                                                                                                                                                             | T <sub>amb</sub> = | -40 °C to | 125 °C | Unit |

|------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------|--------|------|

| Symbol                       | Parameter                          | Conditions                                                                                                                                                                  | Min                | Typ[1]    | Max    | Unit |

| Power supply                 | y                                  |                                                                                                                                                                             |                    |           |        |      |

| V <sub>IN</sub>              | input voltage range                |                                                                                                                                                                             | 4                  | -         | 40     | V    |

|                              |                                    | V <sub>IN</sub> rising                                                                                                                                                      | 3.4                | 3.6       | 3.8    | V    |

| $V_{IN(UVLO)}$               | under voltage<br>lockout threshold | V <sub>IN</sub> falling                                                                                                                                                     | 3.0                | 3.2       | 3.4    | V    |

|                              | lookout un correiu                 | hysteresis                                                                                                                                                                  | -                  | 400       | -      | mV   |

| $V_{FB}$                     | feedback voltage                   | voltage on FB pin                                                                                                                                                           | -1.5%              | 1.177     | 1.5%   | V    |

| I <sub>q</sub>               | quiescent current                  | $V_{IN}$ = 5.5 V to 40 V; $V_{OUT}$ = 5 V; $I_{OUT1}$ = $I_{OUT2}$ = 0 $\mu$ A                                                                                              | -                  | 340       | 550    | μA   |

| $I_GND$                      | operating current                  | $V_{IN}$ = 13.5 V; $V_{EN1}$ and $V_{EN2}$ ≥ 1.3 V; $V_{OUT1}$ = $V_{OUT2}$ = 5 V; $I_{OUT1}$ or $I_{OUT2}$ = 300 mA                                                        | -                  | -         | 5.5    | mA   |

| I <sub>SHUT</sub>            | shutdown current                   | $V_{EN1} = V_{EN2} = 0 \text{ V}; V_{IN} = 4 \text{ V to } 40 \text{ V}$                                                                                                    | -                  | 1         | 5      | μΑ   |

| Enable input                 | (EN, EN1, EN2, SEN                 | SE_EN, and SENSE_SEL)                                                                                                                                                       |                    |           |        |      |

| V <sub>IL</sub>              | logic input low level              | for EN, EN1, EN2, SENSE_EN, and SENSE_SEL                                                                                                                                   | -                  | -         | 0.55   | V    |

| V <sub>IH</sub>              | logic input high level             | for EN, EN1, EN2, SENSE_EN, and SENSE_SEL                                                                                                                                   | 1.4                | -         | -      | V    |

| I <sub>EN</sub>              | EN pin current                     | V <sub>EN</sub> ≤ 40 V                                                                                                                                                      | -                  | -         | 5      | μΑ   |

| SENSE_EN                     | SENSE_EN input current             | V <sub>SENSE_EN</sub> = 5 V; V <sub>ENx</sub> ≥ 1.3 V                                                                                                                       | -                  | -         | 1      | μΑ   |

| SENSE_SEL                    | SENSE_SEL input current            | V <sub>SENSE_SEL</sub> = 5 V; V <sub>ENx</sub> ≥ 1.3 V                                                                                                                      | -                  | -         | 1.2    | μA   |

| Output                       |                                    |                                                                                                                                                                             | ·                  |           |        |      |

| V <sub>OUT</sub>             | output accuracy                    | $V_{IN} = V_{OUT} + 1.5 \text{ V to } 40 \text{ V } (V_{IN} \ge 4 \text{ V})$<br>$I_{OUT} = 100  \mu\text{A to } 300 \text{ mA}$                                            | [2] -1.5           | -         | 1.5    | %    |

| $\Delta V_{OUT(\Delta VIN)}$ | line regulation                    | $V_{IN} = V_{OUT} + 1.5 \text{ V to } 40 \text{ V } (V_{IN} \ge 4 \text{ V});$<br>$I_{OUT} = 10 \text{ mA};$<br>voltage variation on FB pin                                 | -                  | -         | 10     | mV   |

| ΔV <sub>Ουτ(ΔΙΟυτ)</sub>     | load regulation                    | $V_{IN} = V_{OUT} + 1.5 \text{ V to } 40 \text{ V; } (V_{IN} \ge 4 \text{ V});$<br>$I_{OUT} = 100  \mu\text{A to } 300 \text{ mA; } \text{voltage variation on }$<br>FB pin | -                  | -         | 10     | mV   |

| V                            | dropout voltage                    | V <sub>OUTx</sub> = 8.5 V; I <sub>OUT</sub> = 100 mA                                                                                                                        | -                  | 165       | 320    | mV   |

| $V_{DO}$                     | diopout voitage                    | V <sub>OUTx</sub> = 8.5 V; I <sub>OUT</sub> = 300 mA                                                                                                                        | -                  | 500       | 950    | mV   |

| Гоит                         | output current                     | V <sub>IN</sub> = V <sub>OUT</sub> + 1.5 V                                                                                                                                  | -                  | -         | 300    | mA   |

| I <sub>CL</sub>              | output current limit               | V <sub>IN</sub> = V <sub>OUT</sub> + 1.5 V; LIMx shorted to GND                                                                                                             | 340                | -         | 550    | mA   |

| PSRR                         | power supply ripple rejection      | $V_{IN}$ = 13.5 V; $V_{Ripple}$ = 0.5 $V_{pp}$ ; $I_{OUT}$ = 10 mA; $V_{OUT}$ = 5 V; $C_{OUT}$ = 2.2 $\mu$ F; frequency = 100 Hz                                            | [3] -              | 80        | -      | dB   |

| Symbol                               | Parameter                                                                | Conditions                                                                                                                                |     | $T_{amb}$ = -40 °C to 125 °C |        |      |      |

|--------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------|--------|------|------|

| Symbol                               | Parameter                                                                | Conditions                                                                                                                                |     | Min                          | Typ[1] | Max  | Unit |

| Current sens                         | sing and current limit                                                   |                                                                                                                                           | ·   |                              |        |      |      |

|                                      | OUTx to SENSEx current ratio (I <sub>OUT</sub> / I <sub>SENSE</sub> )    | V <sub>IN</sub> = 4 V to 40 V; I <sub>OUT</sub> = 5 mA to 300 mA                                                                          |     | -                            | 198    | -    | -    |

| I <sub>OUT</sub> /I <sub>SENSE</sub> |                                                                          | I <sub>OUT</sub> = 100 mA to 300 mA                                                                                                       |     | -3                           | -      | 3    | %    |

| 00. 01.101                           | OUTx to SENSEx current ratio                                             | I <sub>OUT</sub> = 50 mA to 100 mA                                                                                                        |     | -4                           | -      | 6    | %    |

|                                      | accuracy                                                                 | I <sub>OUT</sub> = 10 mA to 50 mA                                                                                                         |     | -15                          | -      | 20   | %    |

|                                      |                                                                          | I <sub>OUT</sub> = 5 mA to 10 mA                                                                                                          |     | -25                          | -      | 30   | %    |

| I <sub>OUT</sub> /I <sub>LIM</sub>   | OUTx to LIMx<br>current ration (I <sub>OUT</sub> /<br>I <sub>LIM</sub> ) | V <sub>IN</sub> = 4 V to 40 V; I <sub>OUT</sub> = 50 mA to 300 mA                                                                         |     | -                            | 198    | -    | _    |

| I <sub>LIMx</sub>                    | programmable<br>current-limit<br>accuracy                                | V <sub>IN</sub> = 4 V to 40 V; I <sub>OUT</sub> = 50 mA to 300 mA                                                                         |     | -8                           | -      | 8    | %    |

| l <sub>lkg</sub>                     | SENSE, SENSE1,<br>SENSE2, LIM,<br>LIM1, and LIM2<br>leakage current      | ENx = GND; T <sub>amb</sub> = 25 °C                                                                                                       |     | -                            | -      | 1    | μΑ   |

| $V_{LIMx\_th}$                       | current-limit<br>threshold voltage                                       | voltage on the LIM; LIM1; and LIM2 pins when output current is limited                                                                    |     | -                            | 1.177  | -    | V    |

| $V_{SENSEx\_stb}$                    | current-sense<br>short-to-battery<br>fault voltage                       | voltage on SENSEx pin when short-to-battery or reverse current conditions are detected                                                    |     | 3.05                         | 3.2    | 3.3  | V    |

| $V_{SENSEx\_tsd}$                    | current-sense<br>thermal shutdown<br>fault voltage                       | voltage on SENSEx pin when thermal shutdown is detected                                                                                   |     | 2.7                          | 2.85   | 3    | V    |

| $V_{SENSEx\_cl}$                     | current-sense<br>current-limit fault<br>voltage                          | voltage on SENSEx pin when current-limit conditions are detected                                                                          |     | 2.4                          | 2.55   | 2.65 | V    |

| I <sub>SENSEX_</sub> H               | current-sense fault condition current                                    | current source current capacity when short-to-<br>battery; reverse current; thermal shutdown; or<br>current-limit conditions are detected | [4] | 3.3                          | -      | -    | mA   |

| Fault detecti                        | ion                                                                      |                                                                                                                                           | •   |                              |        |      |      |

| V <sub>stb_th</sub>                  | short-to-battery<br>threshold                                            | V <sub>OUTx</sub> – V <sub>IN</sub> ; checked during turn-on sequence                                                                     |     | -500                         | -55    | 110  | mV   |

| I <sub>REV</sub>                     | reverse current<br>detection level                                       | power FET on (SW or LDO mode)                                                                                                             |     | -120                         | -40    | -1   | mA   |

| $V_{R\_th}$                          | reverse protection voltage threshold                                     | V <sub>(OUTx)</sub> – V <sub>IN</sub>                                                                                                     | [4] | -                            | 200    | -    | mV   |

| V <sub>R_retry</sub>                 | reverse protection auto-retry threshold                                  | $V_{(OUTx)} - V_{IN}$                                                                                                                     | [4] | -                            | -300   | -    | mV   |

| Interface cire                       | cuitry                                                                   |                                                                                                                                           |     |                              |        |      |      |

| V <sub>ERR_L</sub>                   | ERR output low                                                           | I <sub>sink</sub> = 5 mA                                                                                                                  |     | -                            | -      | 0.4  | V    |

| I <sub>ERR(Ikg)</sub>                | ERR open-drain leakage current                                           | ERR high impedance; 5 V external voltage is applied at ERR                                                                                |     | -                            | -      | 1    | μA   |

| R <sub>OUTx_DIS</sub>                | OUT discharge resistor                                                   | ENx = GND                                                                                                                                 | [4] | -                            | 50     | -    | kΩ   |

| $I_{R(lkg)}$                         | reverse leakage<br>current                                               | -40 V < V <sub>IN</sub> < 0 V; reverse current to IN                                                                                      |     | -                            | 0.6    | -    | mA   |

| Symbol               | Parameter Co                                   | Conditions                                              | T <sub>amb</sub> = | Unit   |      |      |

|----------------------|------------------------------------------------|---------------------------------------------------------|--------------------|--------|------|------|

| Syllibol             | raiailletei                                    | Conditions                                              | Min                | Typ[1] | Max  | Unit |

| VCC                  | internal voltage regulator                     | V <sub>IN</sub> = 5.5 V to 40 V; I <sub>CC</sub> = 0 mA | 4.25               | 4.5    | 4.75 | V    |

| I <sub>CC(LIM)</sub> | internal voltage<br>regulator current<br>limit |                                                         | 15                 | -      | 70   | mA   |

| Operating ter        | nperature range                                |                                                         |                    |        |      |      |

| T <sub>SD</sub>      | junction thermal<br>shutdown<br>temperature    | rising junction temperature                             | -                  | 175    | -    | °C   |

| T <sub>HYST</sub>    | thermal shutdown<br>hysteresis                 |                                                         | -                  | 15     | -    | °C   |

- [1] All typical values are measured at T<sub>amb</sub> = 25 °C.

- [2] External feedback resistor is not considered.

- [3] Guaranteed by bench test, not fully tested in production.

- [4] Guaranteed by bench test and design, not fully tested in production.

# 12. Switching characteristics

**Table 9. Switching characteristics**

| Cumbal                       | Parameter                                                         | Conditions                                                                                                                                               |     | T <sub>amb</sub> = -40 °C to 125 °C |     | Unit |       |

|------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------|-----|------|-------|

| Symbol                       | rarameter                                                         |                                                                                                                                                          |     | Min                                 | Тур | Max  | Oilit |

| Current sensi                | ing and current limit                                             |                                                                                                                                                          |     |                                     |     |      |       |

| t <sub>d</sub> (SENSE_SEL_r) | current-sense delay<br>time from the rising<br>edge of SENSE_SEL  | V <sub>ENx</sub> ≥ 1.3 V; SENSE_EN = GND;<br>SENSE_SEL rise from 0 V to 5 V                                                                              | [1] | -                                   | 10  | -    | μs    |

| t <sub>d</sub> (SENSE_SEL_f) | current-sense delay<br>time from the falling<br>edge of SENSE_SEL | V <sub>ENx</sub> ≥ 1.3 V; <u>SENSE_EN</u> = GND;<br>SENSE_SEL fall from 5 V to 0 V                                                                       | [1] | -                                   | 10  | -    | μs    |

| t <sub>d(SENSE_EN_r)</sub>   | current-sense delay<br>time from rising edge of<br>SENSE_EN       | V <sub>ENx</sub> ≥ 1.3 V;<br>SENSE_EN rise from 0 V to 5 V                                                                                               | [1] | -                                   | 10  | -    | μs    |

| t <sub>d(SENSE_EN_f)</sub>   | current-sense delay<br>time from falling edge<br>of SENSE_EN      | V <sub>ENx</sub> ≥ 1.3 V;<br>SENSE_EN fall from 5 V to 0 V                                                                                               | [1] | -                                   | 10  | -    | μs    |

| Fault detection              |                                                                   |                                                                                                                                                          |     |                                     |     |      |       |

| t <sub>PD_RC</sub>           | reverse current (short-<br>to-battery) shutdown<br>deglitch time  | delay to shut down the switch or LDO after a drop over r <sub>on</sub> becomes negative; I <sub>OUTx</sub> = -200 mA (typical); T <sub>amb</sub> = 25 °C |     | -                                   | 5   | 20   | μs    |

| t <sub>BLK_RC</sub>          | reverse current<br>blanking time                                  | $V_{IN} = V_{OUT} + 1.5 \text{ V to } 40 \text{ V; and } V_{IN} \ge 4 \text{ V}$<br>$I_{OUT} = 10 \text{ mA; voltage variation on FB pin}$               |     | -                                   | 16  | -    | ms    |

<sup>[1]</sup> Design information, specified by design, not production tested.

# 13. Typical characteristics

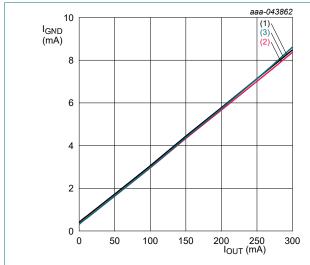

At recommended operating conditions, voltages are referenced to GND (ground = 0 V); typical values are at 25 °C (unless otherwise noted).

$V_{IN}$  = 13.5 V;  $V_{EN} \ge$  1.3 V;  $C_{OUT}$  = 2.2  $\mu$ F;  $V_{OUT}$  = 5 V;  $T_{amb}$  = -40 °C to 125 °C, unless otherwise specified.

(2)

$$T_{amb}$$

= 25 °C

(3)  $T_{amb} = 125 \, ^{\circ}C$

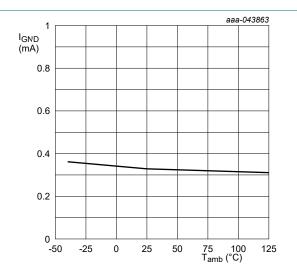

Fig. 3. Ground current vs output current

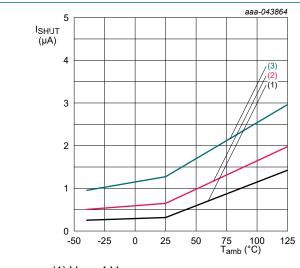

$$(2) V_{IN} = 13.5 V$$

(3)  $V_{IN} = 40 \text{ V}$

Fig. 5. Shutdown current vs ambient temperature

$I_{OUT1} = I_{OUT2} = 0.2 \text{ mA}$

Fig. 4. Ground current vs ambient temperature

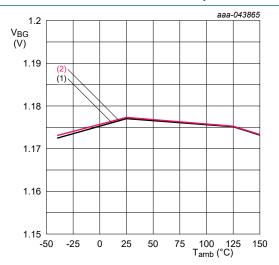

$I_{OUT1} = I_{OUT2} = 10 \text{ mA}$

- (1) Channel 1

- (2) Channel 2

Fig. 6. Bandgap voltage (FB) vs ambient temperature

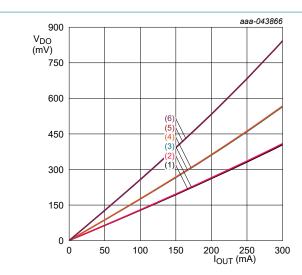

$V_{OUT1} = V_{OUT2} = 5 V$

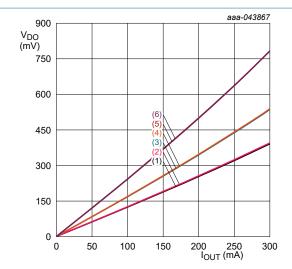

(1)  $T_{amb} = -40$  °C; channel 1

(2) T<sub>amb</sub> = -40 °C; channel 2

(3)  $T_{amb} = 25$  °C; channel 1

(4)  $T_{amb}$  = 25 °C; channel 2

(5) T<sub>amb</sub> = 125 °C; channel 1

(6) T<sub>amb</sub> = 125 °C; channel 2

#### Fig. 7. Dropout voltage vs output current

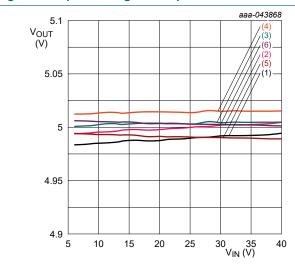

$V_{OUT} = 5 V$ ;  $I_{OUT} = 10 mA$

(1)  $T_{amb} = -40 \, ^{\circ}C; V_{OUT1}$

(2)  $T_{amb} = -40 \, ^{\circ}C; V_{OUT2}$

(3)  $T_{amb} = 25 \, ^{\circ}C; V_{OUT1}$

(4)  $T_{amb}$  = 25 °C;  $V_{OUT2}$

(5)  $T_{amb} = 125 \, ^{\circ}C; V_{OUT1}$

(6)  $T_{amb} = 125 \, ^{\circ}C; \, V_{OUT2}$

Fig. 9. Line regulation vs input voltage

$V_{OUT1} = V_{OUT2} = 8.5 \text{ V}$

(1)  $T_{amb} = -40$  °C; channel 1

(2)  $T_{amb} = -40$  °C; channel 2

(3) T<sub>amb</sub> = 25 °C; channel 1

(4)  $T_{amb} = 25$  °C; channel 2

(5) T<sub>amb</sub> = 125 °C; channel 1

(6) T<sub>amb</sub> = 125 °C; channel 2

# Fig. 8. Dropout voltage vs output current

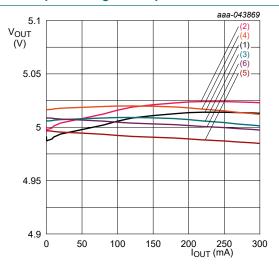

$V_{OUT} = 5 \text{ V}, V_{IN} = 13.5 \text{ V}$

(1)  $T_{amb} = -40 \, ^{\circ}C; V_{OUT1}$

(2)  $T_{amb} = -40 \, ^{\circ}C; V_{OUT2}$

(3)  $T_{amb} = 25 \, ^{\circ}C; V_{OUT1}$

(4)  $T_{amb} = 25 \,^{\circ}\text{C}; V_{OUT2}$

(5)  $T_{amb}$  = 125 °C;  $V_{OUT1}$

(6)  $T_{amb} = 125 \, ^{\circ}C; V_{OUT2}$

Fig. 10. Load regulation vs output current

$V_{IN}$  = 13.5 V;  $C_{OUT}$  = 10  $\mu F$

(1)  $V_{OUT2} = 5 \text{ V}$ ;  $I_{OUT} = 10 \text{ mA}$

(2)  $V_{OUT2} = 5 V$ ;  $I_{OUT} = 100 \text{ mA}$

(3)  $V_{OUT1} = 8.5 \text{ V}$ ;  $I_{OUT} = 10 \text{ mA}$

(4)  $V_{OUT1} = 8.5 \text{ V}$ ;  $I_{OUT} = 100 \text{ mA}$

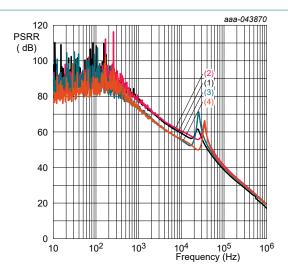

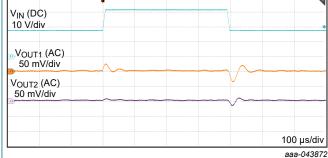

#### Fig. 11. PSRR vs frequency

$V_{IN}$  = 9 V to 16 V; slew rate = 1 V/ $\mu$ s;  $V_{OUT1}$  = 8.5 V;  $V_{OUT2}$  = 5 V;  $I_{OUT}$  = 50 mA;  $C_{OUT}$  = 10  $\mu$ F

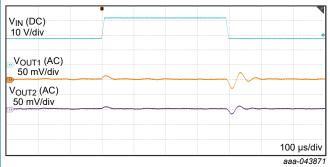

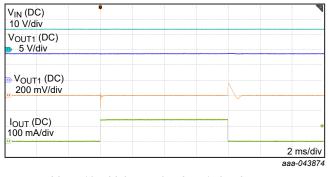

#### Fig. 12. Line transient

$V_{IN}$  = 13.5 V;  $I_{OUT}$  = 0 mA to 150 mA; slew rate = 1 A/µs;  $V_{OUT1}$  = 8.5 V;  $C_{OUT}$  = 10 µF

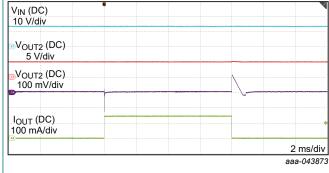

Fig. 14. Load transient

$V_{IN}$  = 9 V to 16 V; slew rate = 1 V/ $\mu$ s;  $V_{OUT1}$  = 8.5 V;  $V_{OUT2}$  = 5 V;  $I_{OUT}$  = 100 mA;  $C_{OUT}$  = 10  $\mu$ F

#### Fig. 13. Line transient

$V_{IN}$  = 13.5 V;  $I_{OUT}$  = 0 mA to 150 mA; slew rate = 1 A/µs;  $V_{OUT2}$  = 5 V;  $C_{OUT}$  = 10 µF

Fig. 15. Load transient

# 14. Detailed description

#### 14.1. Overview

The NEX92x30-Q100 devices feature a dual-channel, high-voltage LDO with the current sensing function. The devices operate with a wide input voltage range of 4 V to 40 V (45 V load dump protection). They also offer protection of antenna lines against electrostatic discharge (ESD) and prevention from short-to-ground, short-to-battery, and thermal over-stress. Device output voltage is adjustable from 1.5 V to 20 V through an external resistor divider.

Alternatively, each channel can be configured as a switch. These devices monitor the load current. Accurate current sensing allows for detection of open, normal, and short to ground conditions without the need of further calibration. Current sensing can also be multiplexed between channels and devices to save ADC resources. Each channel also provides an adjustable current limit with an external resistor.

# 14.2. Functional block diagram

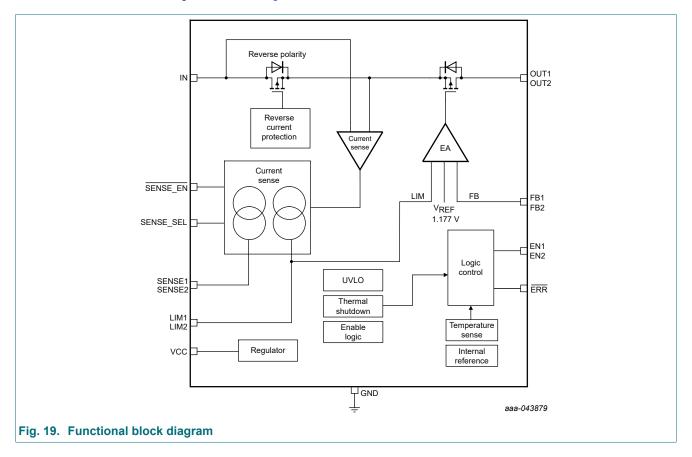

The NEX92x30-Q100 block diagram as below Fig. 19 shown.

### 14.3. Feature description

# 14.3.1. Fault detection and protection

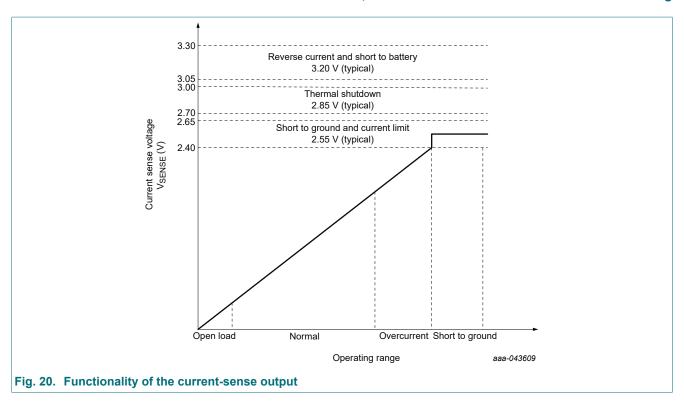

The device includes both analog current sensing and digital fault pins for full diagnostics of different fault conditions. The current sensing voltage scale is selected based on the output current range of requirements. Fig. 20 shows a recommended setting that allows for full diagnostics of each fault.

Before the device goes into current-limit mode, the output current sensing voltage is linearly proportional to the actual load current. During a thermal shutdown and short-to-battery condition, the current sensing voltage is set to the fault voltage level that is specified in <u>Table 8</u>.

# 14.3.2. Short-circuit and current-limit protection

The current limit on each channel is programmed by selecting the external resistor. The voltage on LIMx pin is compared with an internal voltage reference. When the threshold is exceeded, the current limit is triggered. The output of the current-limited channel continues to remain on, and the current is limited.

Under current-limit status, the ERR pin asserts low, and the SENSE voltage of the fault channel is internally pulled up to a voltage rail between 2.4 V and 2.65 V as shown in Fig. 20. At this moment, the output voltage is not disabled. The Microcontroller Unit (MCU) should monitor the voltage at the SENSEx pin or ERR pin (ERR pin does not only indicate current-limit fault, refer to Table 10) to disable the faulted channel by pulling the ENx pin low. If a current-limit condition exists for a long period, thermal shutdown can be triggered and the output is shut down.

#### 14.3.3. Short-to-battery and reverse current detection

Shorting the OUT pin to the battery due to a fault in the vehicle system is possible. Each channel detects this failure by comparing the voltage at the OUT and IN pins before the switch turns on. Each time the LDO switch is enabled on the rising edge of the EN pin or during the exiting of the thermal shutdown, the short-to-battery detection occurs. At this moment, if the device detects the short-to-battery fault, the LDO switch is latched off, the  $\overline{\text{ERR}}$  pin is asserted low, and the fault-channel SENSE voltage is pulled up internally to a voltage rail between 3.05 V and 3.3 V.

During normal operation, if a short-to-battery fault results in reverse current for 5  $\mu$ s (typical), the device is latched off and  $\overline{\text{ERR}}$  pin is asserted low. The device works normally when the short-to-battery is removed and the EN pin must be toggled. Or with the auto-retry version, the device keeps monitoring the input and output voltage. Once input voltage is higher than the output voltage, the device resumes normal operation. It is not necessary to toggle the EN pin.

Series inductance and the output capacitor can produce ringing during power-up or recovery from current-limit, resulting in an output voltage that temporarily exceeds the input voltage. The 16 ms (typical) reverse-current blanking can help filter this ringing.

For the dual-channel antenna LDO application, if both channels are enabled and one channel is shorted to ground after power-up, the current drawn from the input capacitor can result in a temporary dip in the input voltage, which can trigger the reverse-current detection fault. To prevent this false trigger event, care must be taken when selecting the input capacitor. An increase of the input capacitor value is recommended.

#### 14.3.4. Current-limit operation

The device features an internal current-limit circuit that protects the regulator during transient high-load current faults or shorting events.

When the device is in current limit mode, the output voltage is not regulated. During a current-limit event, the device heats up due to increased power dissipation. When the device reaches the current limit ( $I_{CL}$ ), the pass transistor dissipates power according to the formula  $[(V_{IN} - V_{OUT}) \times I_{CL}]$ .

If thermal shutdown is triggered, the device will turn off. Once it cools down, the internal thermal shutdown circuit will turn the device back on. If the output current fault condition persists, the device will cycle between current-limit and thermal shutdown.

#### 14.3.5. Thermal shutdown

The NEX92x30-Q100 integrates an internal temperature sensor to monitor the junction temperature ( $T_j$ ). If  $T_j$  exceeds the thermal shutdown temperature ( $T_{SD}$ ) of 175 °C, the device ceases operation. The device will resume functioning when  $T_j$  drops below the hysteresis threshold of approximately 15 °C.

Thermal shutdown may be triggered during start-up due to large inrush currents charging substantial output capacitance, or under heavy loads where high  $(V_{IN} - V_{OUT})$  regulations result in significant power dissipation across the die. Proper heat sinking should be considered in these high power dissipation scenarios.

Continuously running the device into thermal shutdown or above the maximum recommended junction temperature reduces long-term reliability and device lifetime. The SENSE voltage is internally pulled up to a voltage rail between 2.7 V and 3 V during  $T_{SD}$  status.

### 14.3.6. Integrated reverse-polarity protection

The device integrates a reverse-connected PMOS to block the reverse current during reverse polarity at the input and output short-to-battery condition. A special ESD structure at the input is specified to withstand -42 V. <u>Table 10</u> shows the fault table to indicate which failure occurs.

Table 10. Fault fable

| Failure mode                            | V <sub>SENSE</sub>                           | ERR  | LDO switch output | Latched        |                 |  |

|-----------------------------------------|----------------------------------------------|------|-------------------|----------------|-----------------|--|

| railure illoue                          |                                              |      |                   | NEX92730D-Q100 | NEX92830D-Q100  |  |

| Open load                               |                                              | High | Enable            | No             | No              |  |

| Normal                                  | I <sub>OUT</sub> x R <sub>(SENSE)</sub> /198 | High | Enable            | No             | No              |  |

| Over-current                            |                                              | High | Enable            | No             | No              |  |

| Short-circuit or current-limit          | 2.4 V to 2.65 V                              | Low  | Enable            | No             | No              |  |

| Thermal shutdown                        | 2.7 V to 3 V                                 | Low  | Disable           | No             | No              |  |

| Output short-to battery 3.05 V to 3.3 V |                                              | Low  | Disable           | Yes            | No (auto-retry) |  |

| Reverse current                         | 3.05 V to 3.3 V                              | Low  | Disable           | Yes            | No (auto-retry) |  |

### 14.3.7. Integrated inductive clamp

During output turnoff, the cable inductance continues to source the current from the output of the device. The device integrates an inductive clamp to help dissipate the inductive energy stored in the cable. An internal diode is connected between OUT and GND pins with a DC-current capability of 300 mA for inductive clamp protection.

### 14.3.8. Undervoltage lockout (UVLO)

The device includes an undervoltage lockout (UVLO) threshold that is internally fixed. The undervoltage lockout activates when the input voltage on the IN pin drops below  $V_{IN(UVLO)}$ . The UVLO makes sure that the regulator is not latched into an unknown state during low input supply voltage.

If the input voltage has a negative transient that drops below the UVLO threshold and then recovers, the regulator shuts down and powers up with a normal power-up sequence when the input voltage is above the required levels.

#### 14.3.9. Enable (EN1 and EN2)

The NEX92x30-Q100 devices feature two active-high enable inputs, EN1 and EN2. The EN1 pin controls output voltage 1 (OUT1), and the EN2 pin controls output voltage 2 (OUT2).

The devices consume a maximum of shutdown current at 5  $\mu$ A when the ENx pins are low. Both the EN1 and EN2 pins have a maximum internal pulldown of 5  $\mu$ A.

In addition, the enable logic can support 3.3 V and 1.8 V IO level, and it is well compatible with 5 V/3.3 V and 1.8 V MCU/ SoC.

### 14.3.10. Internal voltage regulator (VCC)

The devices feature an internal regulator that regulates the input voltage to 4.5 V to power all internal circuitry. It bypasses a 1  $\mu$ F ceramic capacitor from the VCC pin to the GND pin for frequency compensation. The VCC pin can be used as a power supply for external circuitry with up to 15 mA current capability.

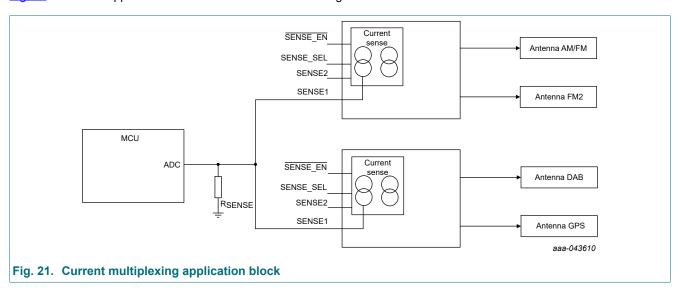

### 14.3.11. Current sensing multiplexing

The two independent current sensing pins (one for each channel) provide flexibility in the system design. When the ADC resource is limited, the device allows the multiplexing of the current sensing pins by only using one current sensing pin and one ADC to monitor all the antenna outputs.

The SENSE\_SEL pin selects the channels to monitor the current. The SENSE\_EN pin enables and disables the SENSE pin, allowing multiplexing between chips. Therefore, only one ADC and one resistor is needed for current sensing diagnostics of multiple outputs. When the SENSE1 pin is connected to an ADC, the current flows through both channels can be sensed by changing the electrical level at the SENSE\_SEL pin.

Table 11 lists the selection logic for the current sensing.

#### Table 11. SENSE\_EN and SEN\_SEL logic table

| SENSE_EN | SENSE_SEL | SENSE 1 status | SENSE 2 status |

|----------|-----------|----------------|----------------|

| Low      | Low       | CH1 current    | CH2 current    |

| Low      | High      | CH2 current    | High impedance |

| High     | -         | High impedance | High impedance |

Fig. 21 shows the application of four antenna channels sharing one ADC resource.

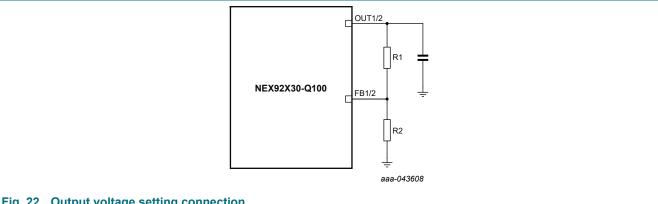

# 14.3.12. Adjustable output voltage (FB1 and FB2)

Use an external resistor divider and select an output voltage between 1.5 V and 20 V. The recommended value for both R1 and R2 is less than 100 k $\Omega$ .

$$V_{OUT} = \frac{V_{FB} \times (R1 + R2)}{R2} \tag{1}$$

Where  $V_{FB} = 1.177 \text{ V (typical)}$ .

The devices can also be configured as a current-limited switch by connecting the FBx pin to the GND pin.

Fig. 22. Output voltage setting connection

# 15. Application implementation

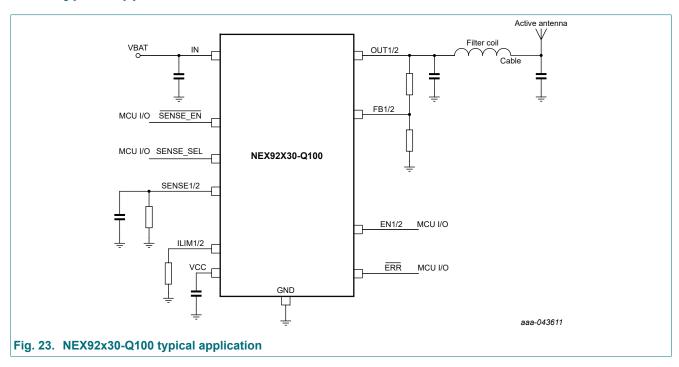

# 15.1. Application information

The following section is a reference to simplify the system design with the NEX92x30-Q100 typical application for external components calculation and selection.

# 15.2. Typical application

### 15.2.1. Design requirements

A typical application is applied in automotive and power supply for AM/FM antenna, which normally requires 8.5 V or 5 V output. The design parameters are listed in <u>Table 12</u>.

Table 12. Design parameters

| Parameters                 | Values                    |  |  |  |

|----------------------------|---------------------------|--|--|--|

| Input voltage              | 4 V to 40 V               |  |  |  |

| Output voltage             | 1.5 V to 20 V             |  |  |  |

| Output capacitor range     | 2.2 μF to 220 μF          |  |  |  |

| Output capacitor ESR range | 0.001 Ω to 5 Ω            |  |  |  |

| SENSE resistor             | Refer to Section 15.2.2.3 |  |  |  |

| Programmable current limit | 50 mA to 300 mA           |  |  |  |

| Auto-retry required        | Yes                       |  |  |  |

#### 15.2.2. Detailed design procedure

#### 15.2.2.1. Input capacitor

The device requires an input decoupling capacitor, the value of which depends on the application. The typical recommended value for the decoupling capacitor is 2.2 µF. The voltage rating must be greater than the maximum input voltage.

#### 15.2.2.2. Output capacitor

To ensure the stability of the NEX92x30-Q100, the device requires an output capacitor with a value of 2.2  $\mu$ F to 220  $\mu$ F from OUT to GND and ESR range between 0.001  $\Omega$  and 5  $\Omega$ . It is recommended to select a ceramic capacitor with low ESR to improve the load transient response and ripple performance.

#### 15.2.2.3. Current sensing resistor selection

The current-sense outputs, SENSEx (SENSE1 and SENSE2), are proportional to the output current at the OUT1 and OUT2 pins with a factor of 1/198. An output resistor,  $R_{SENSEx}$ , must be connected between the SENSEx pin and ground to generate a current sensing voltage to be sampled by ADC. Use equation (2) to calculate the voltage at SENSEx pin  $(V_{SENSEx})$ .

$$V_{SFNSFy} = I_{SFNSFy} \times R_{SFNSFy}$$

(2)

Where

$$I_{SENSEx} = \frac{I_{OUTx}}{198}$$

For this example, 1.5 k $\Omega$  selected as a value for R<sub>SENSEx</sub>. Ignore the resistor and current sensing accuracy. If the load current equals to 198 mA, use equation (3) to get V<sub>SENSEx</sub> voltage.

$$I_{SENSEX} = \frac{I_{OUTX}}{198} = 1 \quad mA \tag{3}$$

Then  $V_{SENSEx}$  can be calculated as 1 mA x 1.5 k $\Omega$  = 1.5 V.

To prevent any overlap between normal operation and current-limit or short-to-ground phase, it is recommended to use equation (4) to select the value of the SENSE resistor.

$$R_{SENSEx} \le \frac{198 \times 24 \, V}{I_{OUT(max)}} \tag{4}$$

#### Where:

- 198 is the output current to current-sense ratio.

- 2.4 V is the minimum possible voltage at the SENSEx pin under a short-circuit fault case.

- I<sub>OUT(max)</sub> is the maximum possible output current under normal operation.

To stabilize the current-sense loop, connecting a 1 µF ceramic capacitor at the SENSE1, or SENSE2 pin is required. <u>Table</u> 13 lists the current sensing accuracy across temperature.

#### Table 13. Current sensing accuracy

| Output current   | Current sensing accuracy |

|------------------|--------------------------|

| 10 mA to 50 mA   | 20%                      |

| 50 mA to 100 mA  | 6%                       |

| 100 mA to 300 mA | 3%                       |

#### 15.2.2.4. Current-limit resistor selection

The current at the LIMx pins (LIM1 and LIM2) is proportional to the load current at the OUTx (OUT1 and OUT2) pins and is internally connected to a current-limit comparator referenced to 1.177 V.

The current limit is programmable through the external resistor connected at LIMx pin. Use equation (5) to calculate the value of the external resistor,  $R_{LIMx}$ . The programmable current-limit accuracy is 8% maximum across all conditions. The internal current limit of the device is set by shorting the LIM pin to ground.

NEX92X30-Q100

All information provided in this document is subject to legal disclaimers

Nexperia B.V. 2025. All rights reserved

Since the current limit varies by 8%, equations (7) and (8) show how to calculate the minimum and maximum current-limit value.

$$R_{LIMx} = \frac{1.177 \, V}{I_{LIMx}} \times 198 \tag{5}$$

Where:

$$I_{LIMx(typ)} = \frac{1177 V}{R_{LIMx}} \times 198 \tag{6}$$

$$I_{LIMx(min)} = I_{LIMx(typ)} \times (1-8\%)$$

(7)

$$I_{LIMx(max)} = I_{LIMx(typ)} \times (1 + 8\%)$$

(8)

Note that this result does not include resistor tolerance in the calculation. To make sure that the current does not exceed the set amount, resistor tolerance must also be included in the equation.

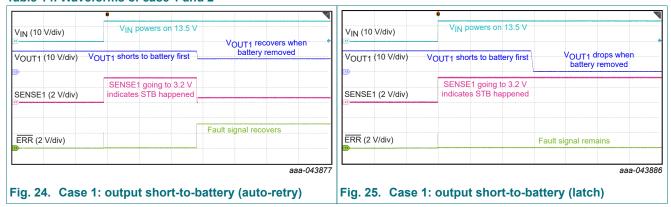

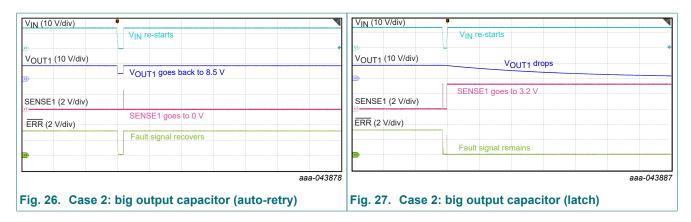

#### 15.2.2.5. Auto-retry and latch behavior

The NEX92x30-Q100 devices include latch and auto-retry versions to provide tailored solutions based on application requirements.

- Auto-retry version (NEX92830-Q100): automatically resumes operation when V<sub>IN</sub> > V<sub>OUT</sub> + 300 mV (typical)

- Latch version (NEX92730-Q100): requires toggling EN or V<sub>IN</sub> to restart

The following examples illustrate the behavioral differences in practical applications: short-to-battery and reverse current.

# Case 1: Short-to-batty event, the device starts with output shorted to battery, battery is subsequently removed

- Auto-retry behavior: The output recovers automatically without toggling V<sub>IN</sub> or EN. When enabled after an initial output short-to-battery condition, the device recovers normally after battery removal. SENSEx and ERR signals return to normal indication. Refer to Fig. 24 for more information.

- Latch behavior: The device disables the output upon detecting a short-to-battery fault and remains latched off. SENSEx and ERR retain fault indications until EN or V<sub>IN</sub> is toggled. Refer to Fig. 25 for more information.

# Case 2: Reverse current event, $V_{\text{IN}}$ or EN is rapidly cycled while output capacitance remains charged

- Auto-retry behavior: Output recovers normally even when voltage does not fully discharge between cycles. SENSEx and

ERR signals return to normal indication. Refer to Fig. 26 for more information.

- Latch behavior: The device detects reverse current, disables the output, and latches off. SENSEx and ERR maintain

fault indications until EN or V<sub>IN</sub> is toggled. Refer to Fig. 27 for more information.

Table 14. Waveforms of case 1 and 2

# 16. Layout

# 16.1. Layout guidelines

For optimal overall performance, the following guidelines are recommended for an LDO layout:

- Place all circuit components on the same side of the circuit board and as near as practical to the respective LDO pin connections.

- Ensure ground return connections for the input and output capacitors, as well as the LDO ground pin, are as close to each other as possible, connected by a wide copper surface on the component side.

- Avoid using vias and long traces to connect the input and output capacitors, as this can negatively impact system

performance.

- In most applications, a ground plane is essential to meet thermal requirements.

A ground reference plane should be either embedded in the PCB or located on the bottom side opposite the components. This reference plane helps ensure output voltage accuracy, shields against noise, and acts as a thermal plane to dissipate heat from the LDO device when connected to the thermal pad.

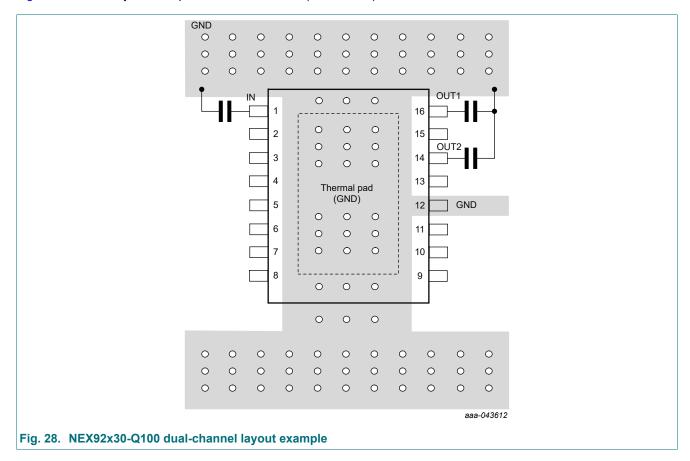

# 16.2. Layout examples

Fig. 28 shows the layout example of NEX92x30-Q100 (HTSSOP16) dual-channel devices.

# 17. Package outline

Fig. 29. Package outline SOT8108-1 (HTSSOP16)

# 18. Abbreviations

#### **Table 15. Abbreviations**

| - Abbieviatio |                                           |

|---------------|-------------------------------------------|

| Acronym       | Description                               |

| ADC           | Analog-to-Digital Converter               |

| AEC           | Automotive Electronics Council            |

| AM            | Amplitude Modulation                      |

| ANSI          | American National Standards Institute     |

| BCM           | Body Control Module                       |

| CDM           | Charge Device Model                       |

| ESD           | ElectroStatic Discharge                   |

| ESDA          | ElectroStatic Discharge Association       |

| EV            | Electric Vehicle                          |

| FM            | Frequency Modulation                      |

| НВМ           | Human Body Model                          |

| HEV           | Hybrid Electric Vehicle                   |

| JEDEC         | Joint Electron Device Engineering Council |

| LDO           | Low-Dropout                               |

| MCU           | Microcontroller Unit                      |

| MIC           | Mechanical Instrument Cluster             |

| PSRR          | Power Supply Ripple Rejection             |

| SoC           | System-on-a-Chip                          |

| UVLO          | Undervoltage Lockout                      |

|               |                                           |

# 19. Revision history

# Table 16. Revision history

| Document ID        | Release date | Data sheet status  | Change notice | Supersedes |

|--------------------|--------------|--------------------|---------------|------------|

| NEX92x30_Q100 v. 1 | 20250801     | Product data sheet | -             | -          |

# 20. Legal information

#### **Data sheet status**

| Document status [1][2]         | Product<br>status [3] | Definition                                                                            |

|--------------------------------|-----------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development           | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification         | This document contains data from the preliminary specification.                       |

| Product [short]<br>data sheet  | Production            | This document contains the product specification.                                     |

- Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions".

- The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the internet at <a href="https://www.nexperia.com">https://www.nexperia.com</a>.

#### **Definitions**

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local Nexperia sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between Nexperia and its customer, unless Nexperia and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the Nexperia product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia.

In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.

Right to make changes — Nexperia reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use in automotive applications — This Nexperia product has been qualified for use in automotive applications. Unless otherwise agreed in writing, the product is not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or

equipment, nor in applications where failure or malfunction of an Nexperia product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer's own triple.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the Nexperia product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). Nexperia does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — Nexperia products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nexperia.com/profile/terms">http://www.nexperia.com/profile/terms</a>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Nexperia hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of Nexperia products by customer.

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### **Trademarks**

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

# **Contents**

| 1. General description                                 | 1   |

|--------------------------------------------------------|-----|

| 2. Features and benefits                               | . 1 |

| 3. Applications                                        | . 1 |

| 4. Ordering information                                | 2   |

| 5. Marking                                             | 2   |

| 6. Pin configuration and description                   | . 3 |

| 6.1. Pin configuration                                 | 3   |

| 6.2. Pin description                                   | 3   |

| 7. Limiting values                                     | . 4 |

| 8. ESD ratings                                         | . 4 |

| 9. Thermal information                                 | 5   |

| 10. Recommended operating conditions                   | 5   |

| 11. Electrical characteristics                         | 6   |

| 12. Switching characteristics                          | . 8 |

| 13. Typical characteristics                            | . 9 |

| 14. Detailed description                               | 12  |

| 14.1. Overview                                         | 12  |

| 14.2. Functional block diagram                         | 13  |

| 14.3. Feature description                              | 13  |

| 14.3.1. Fault detection and protection                 | 13  |

| 14.3.2. Short-circuit and current-limit protection     | 14  |

| 14.3.3. Short-to-battery and reverse current detection | 14  |

| 14.3.4. Current-limit operation                        | 15  |

| 14.3.5. Thermal shutdown                               | 15  |

| 14.3.6. Integrated reverse-polarity protection         | 15  |

| 14.3.7. Integrated inductive clamp                     | 15  |

| 14.3.8. Undervoltage lockout (UVLO)                    | 15  |

| 14.3.9. Enable (EN1 and EN2)                           | 16  |

| 14.3.10. Internal voltage regulator (VCC)              | 16  |

| 14.3.11. Current sensing multiplexing                  | 16  |

| 14.3.12. Adjustable output voltage (FB1 and FB2)       | 17  |

| 15. Application implementation                         | 18  |

| 15.1. Application information                          | 18  |

| 15.2. Typical application                              | 18  |

| 15.2.1. Design requirements                            | 18  |

| 15.2.2. Detailed design procedure                      | 19  |

| 16. Layout                                             | 22  |

| 16.1. Layout guidelines                                | 22  |

| 16.2. Layout examples                                  | 22  |

| 17. Package outline                                    | 23  |

| 18. Abbreviations                                      | 24  |

| 19. Revision history                                   | 24  |

| 20. Legal information                                  | 25  |

### <sup>©</sup> Nexperia B.V. 2025. All rights reserved

For more information, please visit: http://www.nexperia.com For sales office addresses, please send an email to: salesaddresses@nexperia.com Date of release: 1 August 2025