## 1. General description

The NGD4300-Q100 is a high-performance gate driver designed to drive both high-side and low-side N-channel MOSFETs in a synchronous buck or a halfbridge configuration. The floating high-side driver can work with rail voltages up to 120 V and uses a bootstrap supply with an integrated diode. Both lowside and high-side output drivers have an independent undervoltage lockout (UVLO) circuit which disables the output driver when the driver supply is below its threshold level. The NGD4300-Q100 accepts input control signals complying with both TTL and CMOS signaling as low as 2.5 V (±10%). The low voltage, provided by an internal voltage regulator, is used to supply circuitry in signal paths controlling the lowside and high-side power switches. This enables a low-power operation and a better controlled driver performance irrespective of the IC supply voltage.

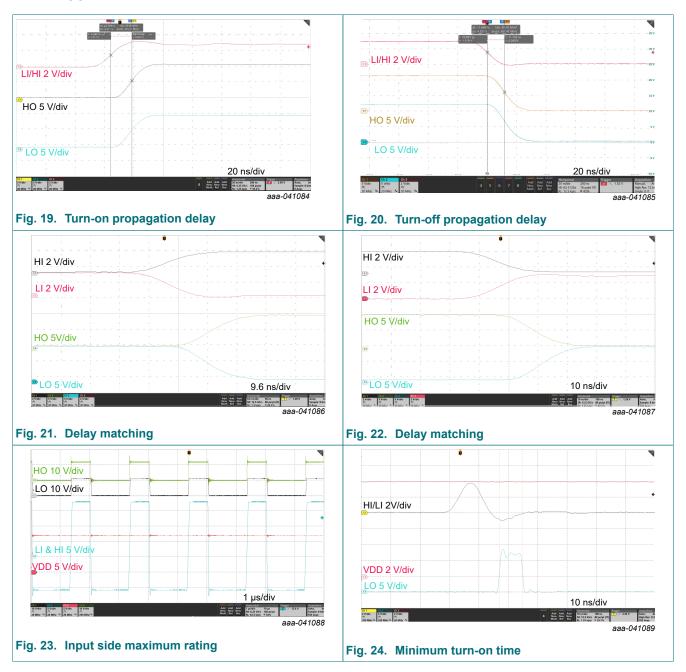

Excellent delay matching of 1 ns typical is achieved for the low-side and high-side signal paths. The 4 A peak source and sink current capability of the driver's output stage guarantees short rise- and fall-times even at high loads.

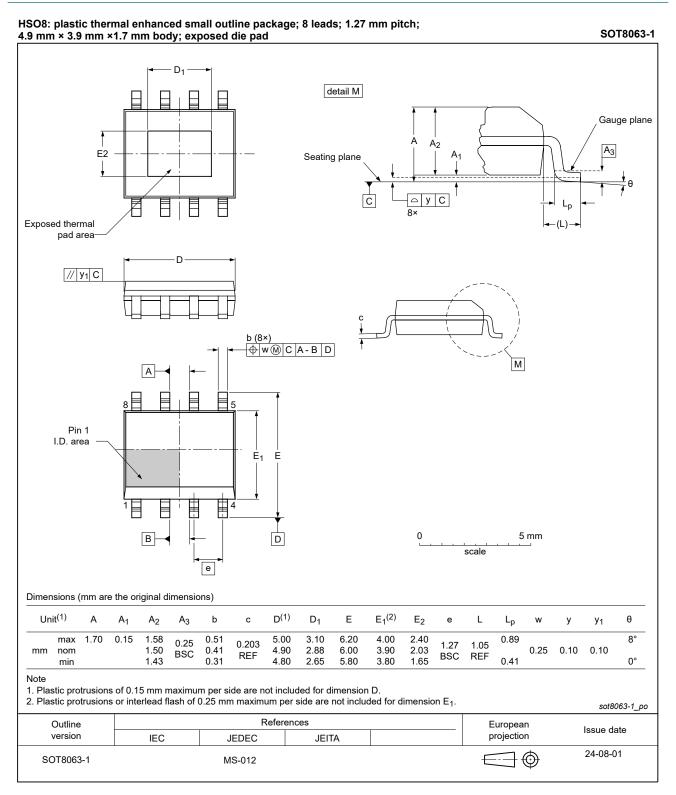

The NGD4300-Q100 is offered in the HSO8 package, and operates over an extended -40 °C to +125 °C temperature range.

This product has been qualified to the Automotive Electronics Council (AEC) standard Q100 (Grade 1) and is suitable for use in automotive applications.

## V<sub>DD(PWM)</sub> НВ н HO NGD4300 PWM HS Vout controller LI LO Vss aaa-041062

### 2. Features and benefits

- Automotive product qualification in accordance with AEC-Q100 (Grade 1)

- Specified from -40 °C to +125 °C

- Input signals complying with both TTL and CMOS signaling of 2.5 V, 3.3 V, and 5 V

- Output signals with 1 ns propagation delay matching (typical)

- Propagation times of 13 ns (typical)

- Switching frequency up to 1 MHz

- 4 A peak source and 5 A sink current capability of the gate driver output stage

- 4 ns rise and 3.5 ns fall times with 1000 pF loads

- Bootstrap supply voltage up to 120 V using an integrated bootstrap diode

- 8 V to 17 V V<sub>DD</sub> operation range

- Undervoltage protection for both low-side and highside supplies

- Low-power consumption (I<sub>DDO</sub>) of 0.6 mA (typical)

- 8 pin HSO8 package

- ESD protection:

- HBM: ANSI/ESDA/JEDEC JS-001 class 2 exceeds 2000 V

- CDM: ANSI/ESDA/JEDEC JS-002 class C3 exceeds 1000 V

## 3. Applications

- Current-fed, push-pull converters

- Two-switch forward power converters

- Class-D audio amplifiers

- Solid-state motor drives

# 4. Ordering information

**Table 1. Ordering information**

| Type number    | Package           | ackage |                                                                                                                        |           |  |  |

|----------------|-------------------|--------|------------------------------------------------------------------------------------------------------------------------|-----------|--|--|

|                | Temperature range | Name   | Description                                                                                                            | Version   |  |  |

| NGD4300DD-Q100 | -40 °C to +125 °C | HSO8   | plastic thermal enhanced small outline package; 8 leads; 1.27 mm pitch; 4.9 mm × 3.9 mm × 1.7 mm body; exposed die pad | SOT8063-1 |  |  |

## 5. Marking

### Table 2. Marking codes

| Type number    | Marking code[1] |

|----------------|-----------------|

| NGD4300DD-Q100 | NGD4300         |

[1] The pin 1 indicator is located on the lower left corner of the device, below the marking code.

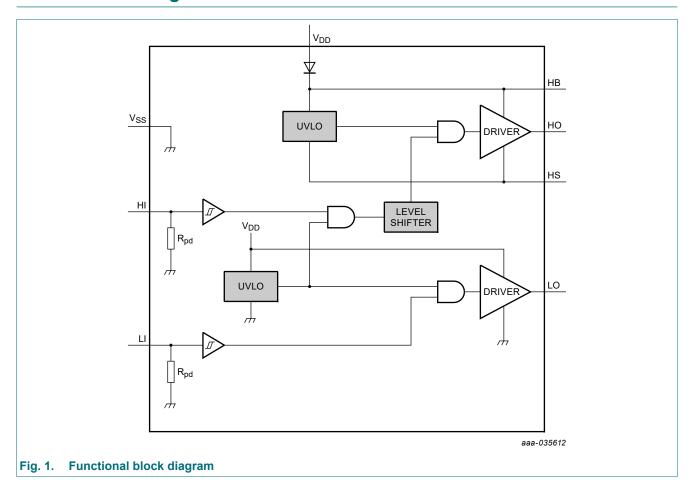

## 6. Functional diagram

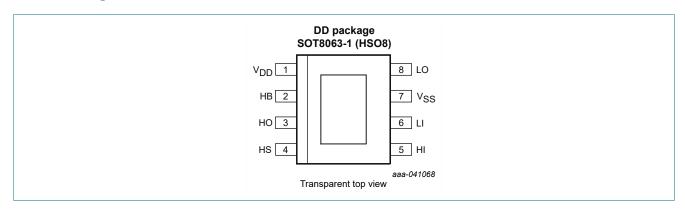

# 7. Pinning information

## 7.1. Pinning

## 7.2. Pin description

Table 3. Pin description

| Symbol          | Pin | Description                                                                                                                                                         |  |

|-----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $V_{DD}$        | 1   | gate drive supply voltage                                                                                                                                           |  |

| НВ              | 2   | h-side gate driver supply voltage; connected to a positive terminal of the bootstrap capacitor and the hode of the internal bootstrap diode                         |  |

| НО              | 3   | driver output signal for controlling the high-side N-channel MOSFET; output is referenced to HS                                                                     |  |

| HS              | 4   | high-side source connection; reference level for the driver high-side; connected to the source of the high-side MOSFET and negative terminal of bootstrap capacitor |  |

| HI              | 5   | h-side control input signal compatible with both TTL and CMOS signaling                                                                                             |  |

| LI              | 6   | low-side control input signal compatible with both TTL and CMOS signaling                                                                                           |  |

| V <sub>SS</sub> | 7   | ground (0 V)                                                                                                                                                        |  |

| LO              | 8   | driver output signal for controlling the low-side N-channel MOSFET; output is referenced to V <sub>SS</sub>                                                         |  |

# 8. Limiting values

### **Table 4. Limiting values**

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to  $V_{\rm SS}$  (ground = 0 V) unless otherwise specified.

| Symbol           | Parameter                             | Conditions                           | Min                      | Max                  | Unit |

|------------------|---------------------------------------|--------------------------------------|--------------------------|----------------------|------|

| Voltages         | and currents                          |                                      | -1                       | ı                    |      |

| $V_{DD}$         | supply voltage on V <sub>DD</sub> pin |                                      | -0.3                     | +20                  | V    |

| $V_{LI}, V_{HI}$ | voltage on LI or HI pins              |                                      | -10                      | +20                  | V    |

| $V_{LO}$         | voltage on LO pin                     | DC                                   | -0.3                     | V <sub>DD</sub> +0.3 | V    |

|                  |                                       | repetitive pulse <100 ns             | -2                       | V <sub>DD</sub> +0.3 | V    |

| V <sub>HO</sub>  | voltage on HO pin                     | DC                                   | V <sub>HS</sub> -0.3     | V <sub>HB</sub> +0.3 | V    |

|                  |                                       | repetitive pulse <100 ns             | V <sub>HS</sub> -2       | V <sub>DD</sub> +0.3 | V    |

| V <sub>HS</sub>  | voltage on HS pin                     | DC                                   | -5                       | +115                 | V    |

|                  |                                       | repetitive pulse <100 ns [1          | ] -(24-V <sub>DD</sub> ) | +115                 | V    |

| $V_{HB}$         | voltage on HB pin                     | referenced to V <sub>HS</sub>        | -0.3                     | +20                  | V    |

|                  |                                       | referenced to V <sub>SS</sub>        | -                        | 120                  | V    |

| T <sub>stg</sub> | storage temperature                   |                                      | -55                      | +150                 | °C   |

| Tj               | junction temperature                  |                                      | -40                      | +150                 | °C   |

| Electrost        | atic discharge                        |                                      | •                        |                      | •    |

| V <sub>ESD</sub> | electrostatic discharge voltage       | HBM: ANSI/ESDA/JEDEC JS-001 class 2  | -2000                    | +2000                | V    |

|                  |                                       | CDM: ANSI/ESDA/JEDEC JS-002 class C3 | -1000                    | +1000                | V    |

<sup>[1]</sup> Verified at bench characterization.

## 9. Recommended operating conditions

#### Table 5. Recommended operating conditions

Voltages are referenced to  $V_{SS}$  (ground = 0 V) unless otherwise specified.

| Symbol           | Parameter                             | Conditions | Min  | Тур | Max   | Unit |

|------------------|---------------------------------------|------------|------|-----|-------|------|

| $V_{DD}$         | supply voltage on V <sub>DD</sub> pin |            | 8.0  | -   | 17.0  | V    |

| V <sub>HS</sub>  | voltage on pin HS                     |            | -0.3 | -   | 110.0 | V    |

| $V_{HB}$         | voltage on pin HB                     |            | -0.3 | -   | 110.0 | V    |

| SR <sub>HS</sub> | slew rate of voltage on pin HS        |            | -    | -   | 50.0  | V/ns |

| T <sub>amb</sub> | ambient temperature                   |            | -40  | -   | +125  | °C   |

## 10. Thermal characteristics

### **Table 6. Thermal characteristics**

| Symbol                 | Parameter                                                          | Condition                     | SOT8063-1 | Unit |

|------------------------|--------------------------------------------------------------------|-------------------------------|-----------|------|

| R <sub>th(j-a)</sub>   | thermal resistance from junction to ambient                        | in free air; JEDEC test board | 38.9      | °C/W |

| R <sub>th(j-c)</sub>   | thermal resistance from case (top) of package                      | in free air; JEDEC test board | 29.5      | °C/W |

| · ) F                  | thermal characterization parameter from junction to top of package | in free air; JEDEC test board | 4.5       | °C/W |

| R <sub>th(j-bop)</sub> | thermal resistance from junction to bottom of package              | in free air; JEDEC test board | 13.1      | °C/W |

## 11. Electrical characteristics

#### **Table 7. Electrical characteristics**

At recommended operating conditions. Voltages are referenced to  $V_{SS}$  (ground = 0 V) unless otherwise specified.  $V_{DD} = V_{HB} = 12 \text{ V}$ ;  $V_{SS} = V_{HS} = 0 \text{ V}$ ; no load on pins LO and HO;  $T_j = T_{amb}$ .

| Supplies (V <sub>DD</sub> and HB pins)  I <sub>DD</sub> quiescent current  I <sub>DDO</sub> operating current  I <sub>HB</sub> total HB quiescen  I <sub>HBO</sub> total HB operating  I <sub>HBSO</sub> total HB to V <sub>SS</sub> qu  I <sub>HBSO</sub> total HB to V <sub>SS</sub> op  V <sub>start(V<sub>DD</sub>)</sub> start voltage on pi  V <sub>start(HB)</sub> start voltage on pi  V <sub>start(HB)</sub> start voltage on pi  V <sub>start(HB)</sub> start voltage hyste |                               |                                                                                    | Min         | Typ[1]       | Max  |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------|-------------|--------------|------|----|

| $\begin{array}{c} I_{DD} & \text{quiescent current} \\ I_{DDO} & \text{operating current} \\ I_{HB} & \text{total HB quiescen} \\ I_{HBO} & \text{total HB operating} \\ I_{HBS} & \text{total HB to V}_{SS} \text{ qu} \\ I_{HBSO} & \text{total HB to V}_{SS} \text{ op} \\ V_{start(V_{DD})} & \text{start voltage on pi} \\ V_{start(hys)V_{DD}} & \text{start voltage on pi} \\ V_{start(HB)} & \text{start voltage on pi} \\ \end{array}$                                       |                               |                                                                                    |             |              | (    |    |

| I <sub>DDO</sub> operating current  I <sub>HB</sub> total HB quiescen  I <sub>HBO</sub> total HB operating  I <sub>HBS</sub> total HB to V <sub>SS</sub> qu  I <sub>HBSO</sub> total HB to V <sub>SS</sub> op  V <sub>start(V<sub>DD</sub>)</sub> start voltage on pi  V <sub>start(HB)</sub> start voltage on pi                                                                                                                                                                     |                               |                                                                                    |             |              |      |    |

| $\begin{array}{c} I_{HB} & \text{total HB quiescen} \\ I_{HBO} & \text{total HB operating} \\ I_{HBS} & \text{total HB to V}_{SS} \text{ qu} \\ I_{HBSO} & \text{total HB to V}_{SS} \text{ op} \\ V_{start(V_{DD})} & \text{start voltage on pi} \\ V_{start(hys)V_{DD}} & \text{start voltage hyste} \\ V_{start(HB)} & \text{start voltage on pi} \end{array}$                                                                                                                     | on pin V <sub>DD</sub>        | V <sub>LI</sub> = V <sub>HI</sub> = 0 V                                            | 0.03        | 0.06         | 0.17 | mA |

| I <sub>HBO</sub> total HB operating I <sub>HBS</sub> total HB to V <sub>SS</sub> qu I <sub>HBSO</sub> total HB to V <sub>SS</sub> op V <sub>start(V<sub>DD</sub>)</sub> start voltage on pi V <sub>start(HB)</sub> start voltage on pi                                                                                                                                                                                                                                                | on pin V <sub>DD</sub>        | f = 500 kHz                                                                        | 0.3         | 0.6          | 2    | mA |

| $\begin{array}{lll} I_{HBS} & \text{total HB to V}_{SS} \text{ qu} \\ I_{HBSO} & \text{total HB to V}_{SS} \text{ op} \\ V_{\text{start(V}_{DD})} & \text{start voltage on pi} \\ V_{\text{start(hys)V}_{DD}} & \text{start voltage hyster} \\ V_{\text{start(HB)}} & \text{start voltage on pi} \end{array}$                                                                                                                                                                         | t current                     | V <sub>LI</sub> = V <sub>HI</sub> = 0 V                                            | 0.01        | 0.04         | 0.1  | mA |

| $I_{HBSO}$ total HB to $V_{SS}$ op<br>$V_{start(V_{DD})}$ start voltage on pi<br>$V_{start(HB)}$ start voltage on pi                                                                                                                                                                                                                                                                                                                                                                  | current                       | f = 500 kHz                                                                        | 0.3         | 0.6          | 2    | mA |

| $V_{start(V_{DD})}$ start voltage on pi<br>$V_{start(hys)V_{DD}}$ start voltage hyster<br>$V_{start(HB)}$ start voltage on pi                                                                                                                                                                                                                                                                                                                                                         | iescent current               | V <sub>HS</sub> = V <sub>HB</sub> = 115 V                                          | 0.0001      | 0.1          | 2    | uA |

| $V_{\text{start(HB)}}$ start voltage hyster $V_{\text{start(HB)}}$ start voltage on pi                                                                                                                                                                                                                                                                                                                                                                                                | erating current               | f = 500 kHz                                                                        | 0.001       | 0.05         | 1.2  | mA |

| $V_{\text{start(Hys)}V_{\text{DD}}}$ start voltage hyster $V_{\text{start(HB)}}$ start voltage on pi                                                                                                                                                                                                                                                                                                                                                                                  | n V <sub>DD</sub>             | $V_{\text{start}(V_{DD})} = V_{DD} - V_{SS}$                                       | 6.1         | 7.11         | 7.85 | V  |

| (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | eresis on pin V <sub>DD</sub> |                                                                                    | 0.4         | 0.63         | 0.8  | V  |

| V <sub>start(hys)HB</sub> start voltage hyste                                                                                                                                                                                                                                                                                                                                                                                                                                         | n HB                          | V <sub>start(HB)</sub> = V <sub>HB</sub> - V <sub>HS</sub>                         | 5.8         | 6.5          | 7.5  | V  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | eresis on pin HB              |                                                                                    | 0.8         | 1            | 1.4  | V  |

| Input stage (LI and HI pins)                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                               |                                                                                    |             |              |      |    |

| V <sub>T-</sub> negative-going thi                                                                                                                                                                                                                                                                                                                                                                                                                                                    | eshold voltage                |                                                                                    | 1           | 1.37         | 1.7  | V  |

| V <sub>T+</sub> positive-going three                                                                                                                                                                                                                                                                                                                                                                                                                                                  | eshold voltage                |                                                                                    | 1.8         | 2.15         | 2.7  | V  |

| R <sub>pd</sub> input pull-down re                                                                                                                                                                                                                                                                                                                                                                                                                                                    | sistance                      |                                                                                    | 20          | 68           | 200  | kΩ |

| Low-side output driver (LO pi                                                                                                                                                                                                                                                                                                                                                                                                                                                         | n)                            |                                                                                    |             |              |      | 1  |

| V <sub>OL(Is)</sub> low-side low-level                                                                                                                                                                                                                                                                                                                                                                                                                                                | output voltage                | I <sub>LO</sub> = 100 mA, V <sub>OL(Is)</sub> = V <sub>LO</sub> - V <sub>SS</sub>  | 0.025       | 0.06         | 0.12 | V  |

| V <sub>OH(Is)</sub> low-side high-leve                                                                                                                                                                                                                                                                                                                                                                                                                                                | el output voltage             | I <sub>LO</sub> = -100 mA, V <sub>OH(hs)</sub> = V <sub>DD</sub> - V <sub>LO</sub> | 0.05        | 0.09         | 0.18 | V  |

| I <sub>OH(Is)</sub> low-side peak pull                                                                                                                                                                                                                                                                                                                                                                                                                                                | -up current                   | V <sub>LO</sub> = 0 V                                                              | -           | 4            | -    | Α  |

| I <sub>OL(Is)</sub> low-side peak pull                                                                                                                                                                                                                                                                                                                                                                                                                                                | -down current                 | V <sub>LO</sub> = 12 V                                                             | -           | 5            | -    | Α  |

| High-side output driver (HO p                                                                                                                                                                                                                                                                                                                                                                                                                                                         | in)                           |                                                                                    |             |              |      | '  |

| V <sub>OL(hs)</sub> high-side low-leve                                                                                                                                                                                                                                                                                                                                                                                                                                                | el output voltage             | I <sub>HO</sub> = 100 mA, V <sub>OL(hs)</sub> = V <sub>HO</sub> - V <sub>HS</sub>  | 0.025       | 0.06         | 0.12 | V  |

| V <sub>OH(hs)</sub> high-side high-lev                                                                                                                                                                                                                                                                                                                                                                                                                                                | el output voltage             | $I_{HO}$ = -100 mA, $V_{OH(hs)}$ = $V_{HB}$ - $V_{HO}$                             | 0.05        | 0.09         | 0.18 | V  |

| I <sub>OH(hs)</sub> high-side peak pu                                                                                                                                                                                                                                                                                                                                                                                                                                                 | II-up current                 | V <sub>HO</sub> = 0 V                                                              | -           | 4            | -    | Α  |

| I <sub>OL(hs)</sub> high-side peak pu                                                                                                                                                                                                                                                                                                                                                                                                                                                 | II-down current               | V <sub>HO</sub> = 12 V                                                             | -           | 5            | -    | Α  |

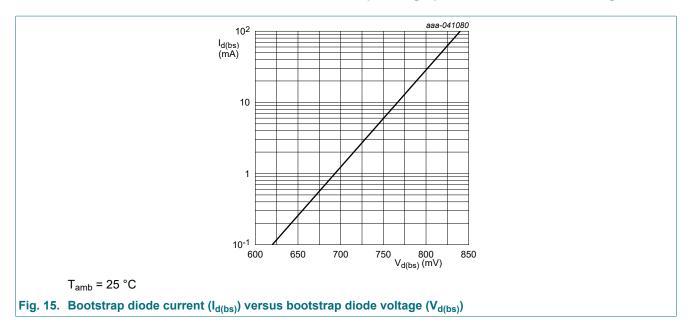

| Bootstrap diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                               |                                                                                    |             |              |      |    |

| V <sub>F</sub> bootstrap diode fo                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               |                                                                                    |             |              |      | _  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | orward voltage                | I <sub>F</sub> = 100 μA                                                            | 0.1         | 0.65         | 0.8  | V  |

| R <sub>dyn(bootd)</sub> bootstrap diode d                                                                                                                                                                                                                                                                                                                                                                                                                                             | orward voltage                | I <sub>F</sub> = 100 μA<br>I <sub>F</sub> = 100 mA                                 | 0.1<br>0.15 | 0.65<br>0.85 | 0.8  | V  |

<sup>[1]</sup> All typical values are measured at  $T_{amb}$  = 25 °C.

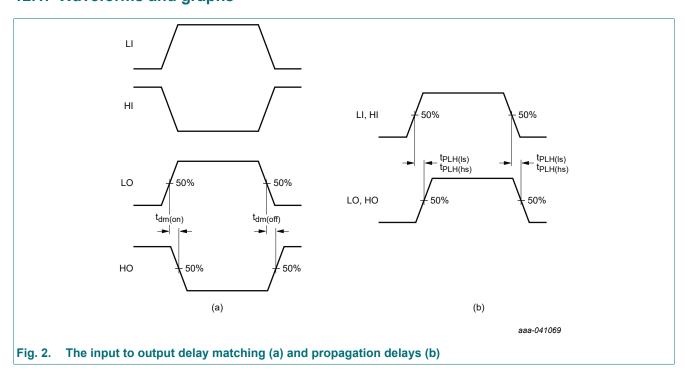

## 12. Dynamic characteristics

#### **Table 8. Dynamic characteristics**

Voltages are referenced to  $V_{SS}$  (ground = 0 V) unless otherwise specified.

For parameters definition see Fig. 2.

$V_{DD} = V_{HB} = 12 \text{ V; } V_{SS} = V_{HS} = 0 \text{ V; no load on pins LO and HO; } T_j = T_{amb}.$

| Symbol                   | Parameter                               | Conditions                                                 | T <sub>amb</sub> = | -40 °C to | +125 °C | Unit |

|--------------------------|-----------------------------------------|------------------------------------------------------------|--------------------|-----------|---------|------|

|                          |                                         |                                                            | Min                | Typ[1]    | Max     |      |

| t <sub>PHL(Is)</sub>     | low-side HIGH to LOW propagation delay  | low-side turn off (LI falling to LO falling)               | 3                  | 13        | 30      | ns   |

| t <sub>PHL(hs)</sub>     | high-side HIGH to LOW propagation delay | high-side turn off (HI falling to HO falling)              | 3                  | 13        | 30      | ns   |

| t <sub>PLH(Is)</sub>     | low-side LOW to HIGH propagation delay  | low-side turn on (LI rising to LO rising)                  | 3                  | 13        | 30      | ns   |

| t <sub>PLH(hs)</sub>     | high-side LOW to HIGH propagation delay | high-side turn on (LI rising to LO rising)                 | 3                  | 13        | 30      | ns   |

| t <sub>dm(on)</sub>      | turn-on delay matching                  | low-side turn on and high-side turn off                    | 0                  | 1         | 7       | ns   |

| t <sub>dm(off)</sub>     | turn-off delay matching                 | low-side turn off and high-side turn on                    | 0                  | 1         | 7       | ns   |

| t <sub>r</sub>           | output rise time                        | LO and HO outputs; C <sub>L</sub> = 1000 pF; 10% to 90%    | 1.5                | 4         | 14      | ns   |

| t <sub>f</sub>           | output fall time                        | LO and HO outputs; C <sub>L</sub> = 1000 pF;<br>90% to 10% | 1.5                | 3.5       | 12      | ns   |

| t <sub>pw(inp),min</sub> | minimum input pulse width               |                                                            | -                  | -         | 20      | ns   |

| t <sub>off(bootd)</sub>  | bootstrap diode turn off time           | I <sub>F</sub> = 100 mA, I <sub>rev</sub> = 0.5 A          | -                  | 10        | 40      | ns   |

<sup>[1]</sup> All typical values are measured at  $T_{amb}$  = 25 °C.

## 12.1. Waveforms and graphs

aaa-041073

(1)

140

80 110 T<sub>amb</sub> (°C)

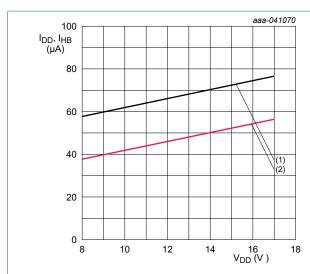

### 4 A peak high-performance dual MOSFET gate driver

$T_{amb}$  = 25 °C;  $V_{DD}$  =  $V_{HB}$

$(1) I_{DD}$

(2) I<sub>HB</sub>

Fig. 3. Quiescent current ( $I_{DD}$ ,  $I_{HB}$ ) versus supply voltage ( $V_{DD}$ )

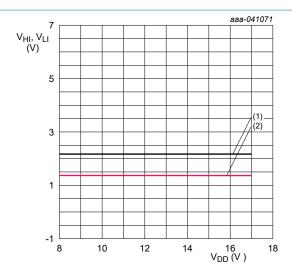

T<sub>amb</sub> = 25 °C

(1) Rising

(2) Falling

Fig. 4. Input  $(V_{HI}, V_{LI})$  threshold voltage versus supply voltage  $(V_{DD})$

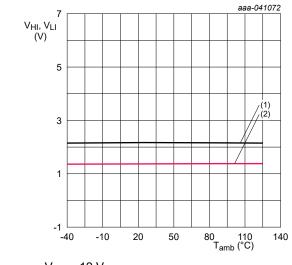

$V_{DD}$  = 12 V

(1) Rising

(2) Falling

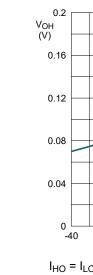

$I_{HO} = I_{LO} = 100 \text{ mA}$

-10

20

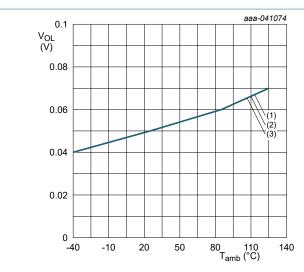

(1)  $V_{DD} = V_{HB} = 8 V$

(2)  $V_{DD} = V_{HB} = 12 V$

(3)  $V_{DD} = V_{HB} = 17 V$

Fig. 5. Input  $(V_{HI}, V_{LI})$  threshold voltage versus ambient temperature  $(T_{amb})$

50

$$I_{HO} = I_{LO} = 100 \text{ mA}$$

(1)

$$V_{DD} = V_{HB} = 8 V$$

(2)

$$V_{DD} = V_{HB} = 12 V$$

(3)

$$V_{DD} = V_{HB} = 17 \text{ V}$$

Fig. 7. Low level output voltage ( $V_{OL(LO)}$ ,  $V_{OL(HO)}$ ) versus ambient temperature ( $T_{amb}$ )

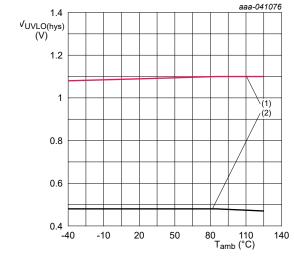

- (1) V<sub>HB</sub> UVLO hysteresis

- (2) V<sub>DD</sub> UVLO hysteresis

Fig. 9. Undervoltage lockout voltage hysteresis  $(V_{UVLO(hys)})$  versus ambient temperature  $(T_{amb})$

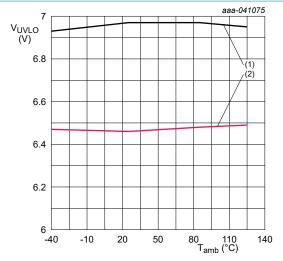

- (1) V<sub>DD</sub> rising

- (2) V<sub>HB</sub> rising

Fig. 8. Undervoltage lockout voltage ( $V_{UVLO}$ ) versus ambient temperature ( $T_{amb}$ )

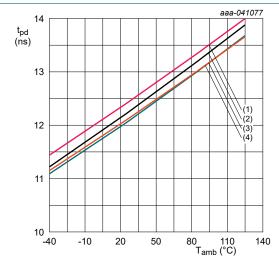

- $V_{DD} = V_{HB} = 12 V$

- (1) t<sub>PHL(Is)</sub>

- (2) t<sub>PLH(Is)</sub>

- (3) t<sub>PHL(hs)</sub>

- (4) t<sub>PLH(hs)</sub>

Fig. 10. Propagation delay  $(T_{pd})$  versus ambient temperature  $(T_{amb})$

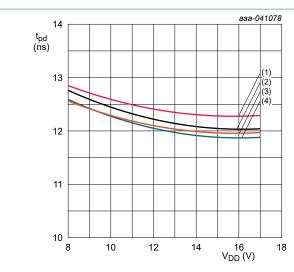

$$T_{amb}$$

= 25 °C;  $V_{DD}$  =  $V_{HB}$

- (1) t<sub>PHL(Is)</sub>

- (2) t<sub>PLH(Is)</sub>

- (3) t<sub>PHL(hs)</sub>

- (4) t<sub>PLH(hs)</sub>

Fig. 11. Propagation delay (T<sub>pd</sub>) versus supply voltage  $(V_{DD})$

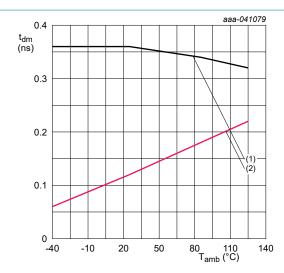

$$V_{DD} = V_{HB} = 12 \text{ V}$$

- (1)  $t_{dm(on)}$

- (2) t<sub>dm(off)</sub>

Fig. 12. Delay matching (T<sub>dm</sub>) versus ambient temperature (T<sub>amb</sub>)

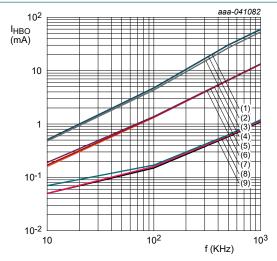

(1)

$$C_L = 0 pF; T_{amb} = -40 °C$$

(2)

$$C_L = 0 \text{ pF}$$

;  $T_{amb} = 25 \text{ °C}$

(3)

$$C_L = 0 pF$$

;  $T_{amb} = 125 °C$

(4)

$$C_L = 1 \text{ nF}$$

;  $T_{amb} = -40 \, ^{\circ}\text{C}$

(5)

$$C_L = 1 \text{ nF}$$

;  $T_{amb} = 25 \text{ °C}$

(7)

$$C_L = 4.7 \text{ nF}$$

;  $T_{amb} = -40 ^{\circ}\text{C}$

(8)

$$C_L = 4.7 \text{ nF}$$

;  $T_{amb} = 25 \text{ °C}$

(9)

$$C_L = 4.7 \text{ nF}$$

;  $T_{amb} = 125 \text{ °C}$

Fig. 13. Operating current (I<sub>HBO</sub>) versus frequency

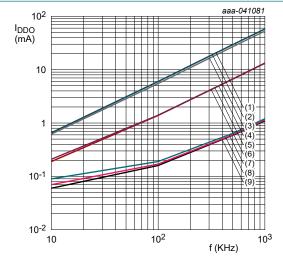

(1)

$$C_L = 0 pF; T_{amb} = -40 °C$$

(2)

$$C_L = 0 \text{ pF}$$

;  $T_{amb} = 25 \text{ °C}$

(3)

$$C_L = 0 pF; T_{amb} = 125 °C$$

(4)

$$C_L = 1 \text{ nF}$$

;  $T_{amb} = -40 \, ^{\circ}\text{C}$

(5)

$$C_L = 1 \text{ nF}; T_{amb} = 25 ^{\circ}C$$

(6)

$$C_L$$

= 1 nF;  $T_{amb}$  = 125 °C

(7)

$$C_L = 4.7 \text{ nF}$$

;  $T_{amb} = -40 \text{ °C}$

(8)  $C_L = 4.7 \text{ nF}$ ;  $T_{amb} = 25 \text{ °C}$

(9)

$$C_L = 4.7 \text{ nF}$$

;  $T_{amb} = 125 \text{ °C}$

Fig. 14. Operating current (I<sub>DDO</sub>) versus frequency

Nexperia NGD4300-Q100

### 4 A peak high-performance dual MOSFET gate driver

## 13. Detailed description

#### 13.1. Overview

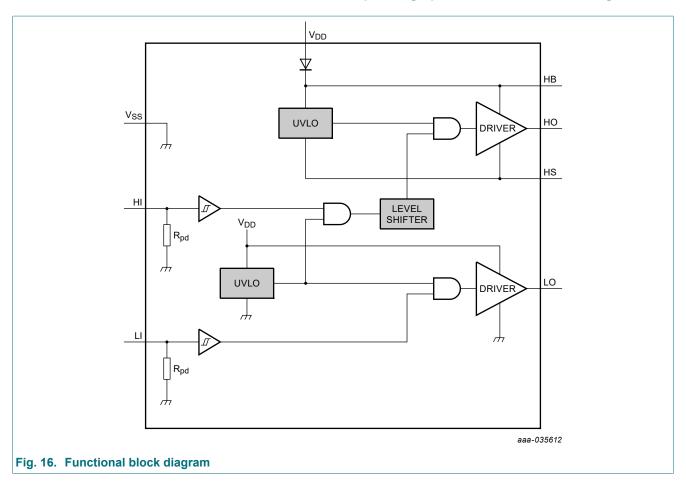

The NGD4300-Q100 is a high-performance cost-effective gate driver meant for driving both high-side and low-side N-channel MOSFETs in a synchronous buck or a half-bridge configuration. The IC can be directly connected to a low-voltage PWM controller providing TTL- or CMOS-compatible signals to control independently external power MOSFETs. The low-side and high-side signal paths up to the output stage driving external power transistor are supplied from an internal low-voltage supply. This reduces the overall power consumption and makes the propagation delay independent of the IC supply voltage V<sub>DD</sub>. Excellent matching of propagation delays of low-side and high-side signal paths is guaranteed.

The NGD4300-Q100 internally generates a floating supply for a high-side MOSFET using an on-chip bootstrap diode and an external capacitor. Maximum allowed voltage on the HB pin is 120 V. The sink and source current capability of the IC output drivers, with a peak current of 4 A, results in fast turn-on and turn-off of external power MOSFETs.

The undervoltage protection circuit available for both low-side and high-side supplies ensures the reliable operation of the IC. NGD4300-Q100 show very low operation current (0.6 mA typical) and strong noise immunity for input (-10, 20 V) and HS (-5V<sub>DC</sub>) pin. NGD4300-Q100 is very suitable for high power module with high frequency operation.

## 13.2. Block diagrams

The NGD4300-Q100 function block diagrams is shown in Fig. 16.

## 13.3. Feature description

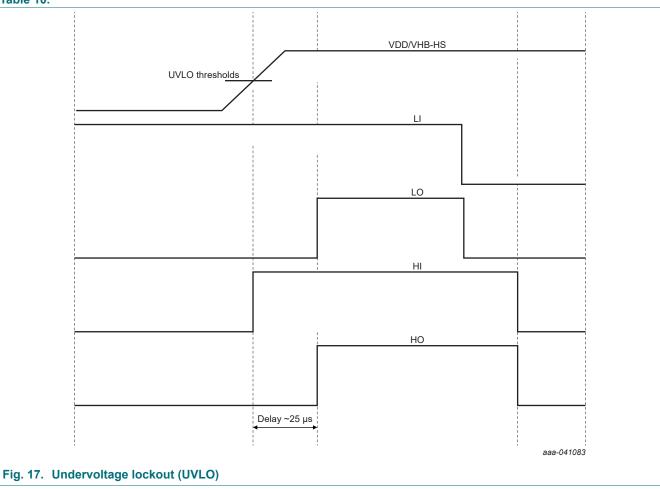

### 13.3.1. Undervoltage lockout (UVLO)

For the IC to work in the normal operating mode, both main supply ( $V_{DD}$  pin) and the bootstrap supply (HB-HS pin) have to be above their start levels ( $V_{start(VDD)}$  and  $V_{start(HB)}$ , respectively). The HS and LS channels are enabled then, and the state of the IC outputs (LO and HO) depends on the state of the inputs LI and HI, respectively. The NGD4300-Q100 works as a non-inverting gate driver which means that the inputs directly influence the state of the gate driver outputs. shows the state of the outputs for different input pin state combinations. When the inputs are not driven, the internal pull-down resistors at these pins define the IC output state.

There are about 25  $\mu$ s output delay during NGD4300-Q100  $V_{DD}$  and  $V_{HB-HS}$  startup. Fig. 17 show the device startup behavior. shows the device startup behavior

### Table 9. Truth table

Truth table describing the NGD4300 outputs for different input state combinations in the IC operating mode.

| HI       | LI       | НО | LO |

|----------|----------|----|----|

| L        | L        | L  | L  |

| L        | Н        | L  | Н  |

| Н        | L        | Н  | L  |

| Н        | Н        | Н  | Н  |

| floating | floating | L  | L  |

Table 10.

### 13.3.2. Input stages

The input stage of the NGD4300-Q100 is COMS and TTL compatible. The logic rising threshold level is 2.2 V and the logic falling is 1.35 V. The input pin of NGD4300-Q100 can withstand voltage from -10 V to 20 V and build in hysteresis for robust noise immunity.

### 13.3.3. Output stages

The low-side and high-side output are independently controlled by HI and LI pin. NGD4300-Q100 provide 4 A peak source current and -5 A peak sink current for both low-side and high-side output when  $V_{DD}$  at 12 V. NGD4300-Q100 high-side and low-side output provide about 4 A output peak current even the  $V_{DD}$  voltage drop to 8 V.

### 13.3.4. Timing

The NGD4300-Q100 LO and HO pin both can drive a 1 nF cap load with 4 ns rise and 3.5 ns fall times. The high-side and low-side channel output delay matching achieve 1ns. The device showing very good timing performance in switching performance. Thanks to NGD4300-Q100 fast timing performance, it can help to reduce system switching loss and shorter the deadtime setting to achieve higher power system efficiency.

## 14. Application information

In power applications gate drivers are used to interface between PWM controllers and power switches such as power MOSFETs. A typical PWM controller has low-power CMOS outputs that are not capable of supplying the current necessary to charge/discharge the relatively high input capacitance of power switches. PWM controllers do not include level shifting to generate the voltage levels required to drive high-side power switches.

The gate driver implements level shifting between the signal levels of the PWM controller and the gate voltages required by power MOSFETs. This is especially required in high-power applications using digital controllers, where low-voltage PWM signaling (typically 3.3 V) is used to drive power MOSFETs working with gate-source ( $V_{GS}$ ) voltages as high 8 V to 20 V. The use of a dedicated gate driver in such cases not only boosts the PWM signals to the required gate-drive levels, including the generation of floating supplies if needed, but also reduces conduction losses. The integration of a bootstrap diode in the NGD4300 as part of the floating supply reduces the number of external components.

Gate drivers such as the NGD4300-Q100 combine a high-impedance low capacitance input stage with high output-current drive. The high-impedance low capacitance input stage can be driven at high frequency by a PWM controller. The high current capability of the output driver in the NGD4300-Q100 allows rapid charge and discharge of power switch capacitances and consequently faster power switching at reduced power losses. Power conversion at higher switching frequencies is especially advantageous in DC/DC converters. It enables the use of smaller-value capacitors and inductors in the converter circuit, and this means a much smaller footprint of the overall power solution.

Gate drivers also shield the power stage from switching noise and thermal stress. This improves the power efficiency and reliability of the application.

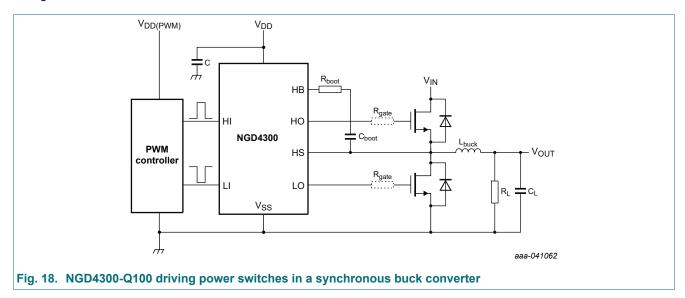

The NGD4300-Q100 gate driver switches two N-channel power MOSFETs, one high- side and one low-side. The power MOSFETs can be configured in half-bridge, full-bridge or synchronous buck converter topologies. Both power MOSFETs are controlled by independent input signals (LI and HI), which offers full flexibility in setting their on- and off-times. Since the NGD4300-Q100 inputs can be driven by low-voltage domain signals, the switching losses of the gate driver can be reduced. The output signals driving the high-side power MOSFET are level-shifted using a floating supply that comprises an integrated boost diode and an external boost capacitor. The maximum input voltage of the power stage, which is connected to the drain voltage of the external high-side N-channel MOSFET, is 120 V.

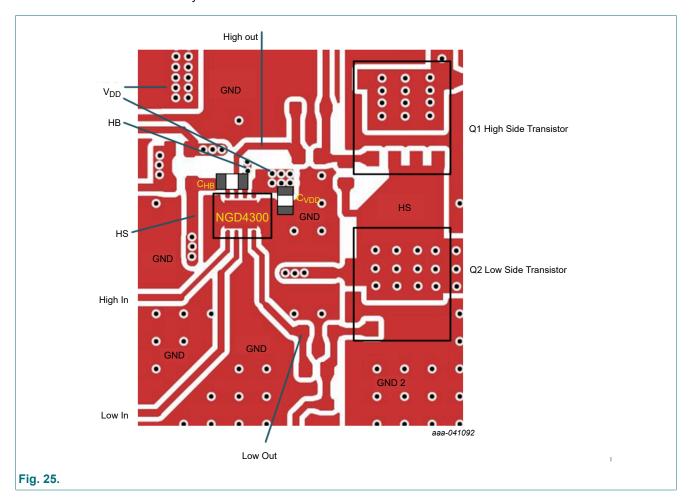

## 14.1. Typical application circuit

Fig. 18 shows a typical application of the NGD4300-Q100 driving power MOSFETs in a synchronous DC/DC buck converter. Unlike common gate drivers with similar functionality, the NGD4300-Q100 can be connected directly to a low-voltage PWM controller, such as the 3.3 V controller shown in the figure. The low-voltage PWM controller and the NGD4300-Q100 internally generated low-voltage supply reduce the power dissipation of the application. Only the output drivers of the NGD4300-Q100 are supplied directly from the  $V_{DD}$  supply. To ensure a stable supply, a bypass capacitor is required between  $V_{DD}$  and  $V_{SS}$  pins. The input voltage ( $V_{IN}$ ) of the buck converter in the figure is 120 V.

Bootstrap resistor ( $R_{boot}$ ) in series with the bootstrap capacitor ( $C_{boot}$ ) reduces the inrush current through the integrated bootstrap diode during the gate driver high-side supply start-up. This resistor also limits the ramp up slew rate of the high-side voltage ( $V_{HS}$  -  $V_{HS}$ ). Additional resistors ( $R_{gate}$ ) can be placed between the outputs (LO, HO) and the gates of the power MOSFETs to adjust the power MOSFETs' switching times. They also help to reduce ringing caused by parasitic inductance in the system and to adjust the dynamic power losses in the IC itself. In applications requiring very fast turn-off times, anti-parallel diodes (not shown) can be placed in parallel with the gate resistors. These diodes will bypass the gate resistors during turn-off and reduce the turn-off transition time.

## 14.2. Application curves

## 15. Power supply recommendations

The NGD4300-Q100 works with the main and bootstrap supplies, both requiring proper decoupling/filter capacitors.

For the main supply, a decoupling capacitor needs to be placed between the  $V_{DD}$  and  $V_{SS}$  pins of the IC, preferably as close to those pins as possible. A low-ESR, ceramic surface mount capacitor is recommended. For more optimized performance, Nexperia recommends the use of two capacitors at this supply:

- 100 nF, ceramic surface-mount capacitor for high-frequency filtering

- 220 nF to 10 μF, for IC bias requirements

The NGD4300-Q100 bootstrap supply provides the current pulses to the high-side (HO) output pin. Therefore, similarly to the main supply, a smaller 22 nF to 220 nF local decoupling capacitor is recommended between the HB and HS pins on the IC.

NGD4300\_Q100

All information provided in this document is subject to legal disclaimers.

© Nexperia B.V. 2025. All rights reserved

## 16. Layout guidelines

The NGD4300-Q100, as any typical gate driver IC, will experience high di/dt during the switching transitions. Therefore any parasitic inductance in the system should be minimized to avoid excessive ringing and undesired voltage drop. PCB traces should be kept as short and wide (>20 mil) as practical. The input and bootstrap capacitors should be placed as close as possible to the IC pins. The current loops in the PCB design should be minimized. The V<sub>SS</sub> pin of the NGD4300-Q100 should be placed as close as possible to the source of the low-side MOSFET. The number of vias should be maximized to ease the thermal conduction away from the driver.

# 17. Package outline

Fig. 26. Package outline SOT8063-1 (HSO8)

## 18. Abbreviations

#### **Table 11. Abbreviations**

| Acronym | Description                                       |  |  |

|---------|---------------------------------------------------|--|--|

| ANSI    | American National Standards Institute             |  |  |

| CDM     | Charged Device Model                              |  |  |

| CMOS    | Complementary Metal Oxide Semiconductor           |  |  |

| DUT     | Device Under Test                                 |  |  |

| ESD     | ElectroStatic Discharge                           |  |  |

| ESR     | Equivalent Series Resistance                      |  |  |

| ESDA    | ElectroStatic Discharge Association               |  |  |

| НВМ     | Human Body Model                                  |  |  |

| IC      | ntegrated Circuit                                 |  |  |

| JEDEC   | Joint Electron Device Engineering Council         |  |  |

| MOSFET  | Metal Oxide Semiconductor Field-Effect Transistor |  |  |

| PCB     | Printed Circuit Board                             |  |  |

| PWM     | ulse Width Modulation                             |  |  |

| TTL     | Transistor-Transistor Logic                       |  |  |

| UVLO    | UnderVoltage LockOut                              |  |  |

## 19. Revision history

#### Table 12. Revision history

| Table 121 Herrician Inclary |                                                                                                         |                                                                                                 |               |                  |  |

|-----------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------|------------------|--|

| Document ID                 | Release date                                                                                            | Data sheet status                                                                               | Change notice | Supersedes       |  |

| NGD4300_Q100 v.2.1          | 20250718                                                                                                | Product data sheet                                                                              | -             | NGD4300_Q100 v.2 |  |

| Modifications:              | • <u>Table 7</u> : The                                                                                  | • <u>Table 7</u> : The typical values of low-side and high-side peak pull-down current updated. |               |                  |  |

| NGD4300_Q100 v.2            | 20241111                                                                                                | Product data sheet                                                                              | -             | NGD4300_Q100 v.1 |  |

| Modifications:              | <u>Section 14.2</u> : Figure titles added for better readability and <u>Fig. 20</u> corrected (errata). |                                                                                                 |               |                  |  |

| NGD4300_Q100 v.1            | 20240927                                                                                                | Product data sheet                                                                              | -             | -                |  |

## 20. Legal information

#### **Data sheet status**

| Document status [1][2]         | Product<br>status [3] | Definition                                                                            |

|--------------------------------|-----------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development           | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification         | This document contains data from the preliminary specification.                       |

| Product [short]<br>data sheet  | Production            | This document contains the product specification.                                     |

- Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions".

- The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the internet at <a href="https://www.nexperia.com">https://www.nexperia.com</a>.

#### **Definitions**

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local Nexperia sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between Nexperia and its customer, unless Nexperia and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the Nexperia product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia.

In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.

Right to make changes — Nexperia reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use in automotive applications — This Nexperia product has been qualified for use in automotive applications. Unless otherwise agreed in writing, the product is not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or

### 4 A peak high-performance dual MOSFET gate driver

equipment, nor in applications where failure or malfunction of an Nexperia product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer's own rick.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the Nexperia product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). Nexperia does not accept any liability in this respect

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — Nexperia products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nexperia.com/profile/terms">http://www.nexperia.com/profile/terms</a>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Nexperia hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of Nexperia products by customer.

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### **Trademarks**

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

## **Contents**

| 1. General description              | 1  |

|-------------------------------------|----|

| 2. Features and benefits            | 1  |

| 3. Applications                     | 1  |

| 4. Ordering information             | 2  |

| 5. Marking                          | 2  |

| 6. Functional diagram               | 2  |

| 7. Pinning information              | 3  |

| 7.1. Pinning                        | 3  |

| 7.2. Pin description                | 3  |

| 8. Limiting values                  | 4  |

| 9. Recommended operating conditions | 5  |

| 10. Thermal characteristics         | 5  |

| 11. Electrical characteristics      | 6  |

| 12. Dynamic characteristics         | 7  |

| 12.1. Waveforms and graphs          | 7  |

| 13. Detailed description            | 11 |

| 13.1. Overview                      | 11 |

| 13.2. Block diagrams                | 11 |

| 13.3. Feature description           | 12 |

| 13.3.1. Undervoltage lockout (UVLO) | 12 |

| 13.3.2. Input stages                | 13 |

| 13.3.3. Output stages               | 13 |

| 13.3.4. Timing                      | 13 |

| 14. Application information         | 13 |

| 14.1. Typical application circuit   | 14 |

| 14.2. Application curves            | 15 |

| 15. Power supply recommendations    | 15 |

| 16. Layout guidelines               | 16 |

| 17. Package outline                 | 17 |

| 18. Abbreviations                   | 18 |

| 19. Revision history                | 18 |

| 20. Legal information               |    |

|                                     |    |

For more information, please visit: http://www.nexperia.com For sales office addresses, please send an email to: salesaddresses@nexperia.com Date of release: 18 July 2025

<sup>&</sup>lt;sup>©</sup> Nexperia B.V. 2025. All rights reserved