# NATIONAL HYBRID, Inc.

# Multi Protocol Data Bus Interface

# **NHi-ET Enhanced Terminals Bus Controller, Remote Terminal, Bus Monitor**

# User's Manual

# Version 2003.07.14 **July 2003**

3thU.com The information provided in this document is believed to be accurate; however, no responsibility is assumed by NATIONAL HYBRID, INC. for its use, and no license or rights are granted by implication or otherwise in connection therewith. Specifications are subject to change without notice.

2200 Smithtown Avenue, Ronkonkoma, NY 11779 Data Bus Fax (631) 981- 2445 Telephone (631) 981- 2400

Website http://www.nationalhybrid.com

www.Datas Email: databus@nationalhybrid.com

# TABLE OF CONTENTS

|                | 22225                                 |          |   |   | •        |

|----------------|---------------------------------------|----------|---|---|----------|

| 1.0.0          | SCOPE.                                | •        | • | • | 6        |

| 2.0.0          | NHI-ET PROTOCOL COMPLIANCE .          | •        | • | • | 6        |

| 3.0.0          | INTRODUCTION                          | •        | • | • | 6        |

| 3.1.0          | FEATURES                              | •        | • | • | 6        |

| 3.1.1          | GENERAL FEATURES                      |          | • | • | 6        |

| 3.1.2          | BUS CONTROLLER HIGHLIGHTS             | •        | • | • | 7        |

| 3.1.3          | REMOTE TERMINAL HIGHLIGHTS .          | •        | • | • | 7        |

| 3.14           | BUS MONITOR HIGHLIGHTS                |          | • |   | 8        |

| 3.2.0          | BLOCK DIAGRAM                         | •        | • | • | 9        |

| 3.3.0          | PROTOCOL CHIP DESCRIPTION             |          | • |   | 10       |

| 3.3.1          | HOST BUS INTERFACE UNIT               |          |   |   | 10       |

| 3.3.2          | I/O BUS INTERFACE UNIT                |          |   |   | 10       |

| 3.3.3          | INTERRUPT CONTROL UNIT                |          |   |   | 10       |

| 3.3.3.1        | ICU REGISTERS                         |          |   |   | 10       |

| 3.3.3.1.1      | INTERRUPT DEFINITION TABLE            |          |   |   | 11       |

| 3.3.3.2        | ICU FIFO                              |          |   |   | 11       |

| 3.3.4          | DUAL REDUNDANT FRONT END              |          |   |   | 12       |

| 3.3.4.1        | MANCHESTER DECODER                    |          |   |   | 12       |

| 3.3.4.2        | MANCHESTER ENCODER                    |          |   |   | 12       |

| 3.3.4.3        | GAP COUNTER                           |          |   |   | 12       |

| 3.3.4.4        | RT - RT NO RESPONSE COUNTER .         |          | - | _ | 12       |

| 3.3.4.5        | MINIMUM RESPONSE TIME COUNTER         | -        | - | - | 12       |

| 3.3.4.6        | FAIL -SAFE TIMEOUT COUNTER .          | •        | • | • | 12       |

| 3.3.5          | MESSAGE PROCESSOR UNIT                | •        | • | • | 12       |

| 3.4.0          | RT HARDWIRE TERMINAL ADDRESS.         | •        | • | • | 13       |

| 4.0.0          | DATA STRUCTURE                        | •        | • | • | 13       |

| 4.1.0          | ADDRESS MAP                           | •        | • | • | 13       |

| 4.1.0          | INTERNAL REGISTERS                    | •        | • | • | 14       |

| 4.2.1          | CONTROL                               | •        | • | • | 15       |

| 4.2.1          |                                       | •        | • | • |          |

| 4.2.2          | POINTER TABLE ADDRESS<br>BASIC STATUS | •        | • | • | 16<br>17 |

|                |                                       | •        | • | • |          |

| 4.2.4<br>4.2.5 |                                       | •        | • | • | 18<br>10 |

|                |                                       | •        | • | • | 18       |

| 4.2.6          | INTERRUPT VECTOR                      | •        | • | • | 18       |

| 4.2.7          | CONFIGURATION REGISTER 2              | •        | • | • | 19       |

| 4.2.8          | AUXILIARY VECTOR REGISTER             | •        | • | • | 20       |

| 4.2.9          | REAL- TIME CLOCK                      | •        | • | • | 20       |

| 4.2.10         | RTC CONTROL REGISTER                  | •        | • | • | 21       |

| 4.2.11         | FIFO READ                             | •        | • | • | 22       |

| 4.2.12         | FIFO RESET                            | •        | • | • | 22       |

| 4.2.13         | LAST COMMAND REGISTER                 | •        | • | • | 22       |

| 4.2.14         | LAST STATUS REGISTER                  |          |   |   | 23       |

| 4.2.15         | RESET REMOTE TERMINAL .               |          |   |   | 23       |

| 4.2.16         | ENCODER STATUS                        |          |   |   | 23       |

| 4.2.17         | CONDITION REGISTER                    |          |   |   | 23       |

| 4.2.18         | ENCODER DATA REGISTER                 |          |   |   | 24       |

| 4.2.19         | ENCODER DATA TRANSMIT RQST .          |          |   |   | 24       |

| 4.2.20         | ENCODER COMMAND TRANSMIT REQUE        | ST       |   |   | 24       |

| 4.2.21         | EXTERNAL TERMINAL ADDRESS REGIS       |          |   |   | 25       |

| 4.2.22         | COMMAND OUTPUT PINS                   | <u> </u> |   |   | 25       |

| 4.2.23         | I/ O TAG WORD REGISTER                |          |   | _ | 25       |

| 4.2.24         | CONFIGURATION REGISTER 1              |          |   |   | 26       |

| 4.2.25  | FRAME "A" POINTER; BLOCK "A" START .                 |  | 27 |

|---------|------------------------------------------------------|--|----|

| 4.2.26  | FRAME "A" LENGTH; BLOCK "A" END .                    |  | 27 |

| 4.2.27  | FRAME "B" POINTER; BLOCK "B" START .                 |  | 28 |

| 4.2.28  | FRAME "B" LENGTH; BLOCK "B" END .                    |  | 28 |

| 4.2.29  | <b><u>BC FRAME GAP;</u></b> WORD MONITOR EOF OPTIONS |  | 29 |

| 4.2.30  | CONFIGURATION REGISTER 3                             |  | 30 |

| 4.2.31  | MT ADDRESS FILTER (RT15- RT0)                        |  | 31 |

| 4.2.32  | MT ADDRESS FILTER (RT31- RT16) .                     |  | 31 |

| 4.2.33  | BLOCK "A" LAST ADDRESS .                             |  | 31 |

| 4.2.34  | BLOCK "B" LAST ADDRESS                               |  | 32 |

| 4.3.0   | RT DATA TABLES                                       |  | 32 |

| 4.3.1   | MESSAGE ILLEGALITY                                   |  | 33 |

| 4.3.2   | DATA TABLE TAG WORD                                  |  | 33 |

| 4.3.3   | DATA TABLE POINTER                                   |  | 34 |

| 4.3.4   | RT DATA TABLE BUFFERING SCHEME                       |  | 35 |

| 4.3.4.1 | RT RAM ACCESS                                        |  | 35 |

| 4.3.4.2 | HOST RAM ACCESS                                      |  | 35 |

| 4.3.4.3 | READ- MODIFY- WRITE                                  |  | 36 |

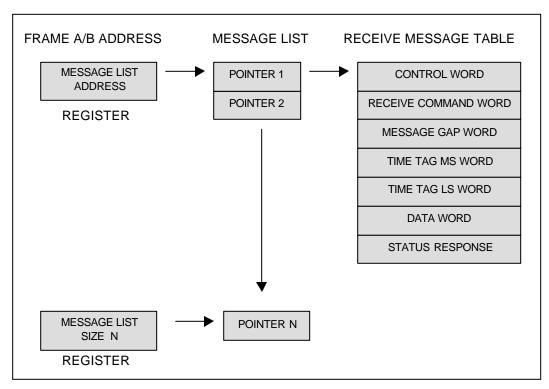

| 4.4.4.0 | BC MESSAGE LISTS AND DATA TABLES                     |  | 36 |

| 4.4.1   | BC CONTROL WORD                                      |  | 37 |

| 4.4.2   | BC COMMAND WORD                                      |  | 39 |

| 4.4.3   | BC MESSAGE GAP WORD                                  |  | 39 |

| 4.4.4   | BC TIME TAG MS WORD                                  |  | 40 |

| 4.4.5   | BC TIME TAG LS WORD                                  |  | 40 |

| 4.4.6   | BC DATA WORD                                         |  | 40 |

| 4.4.7   | BC STATUS RESPONSE                                   |  | 40 |

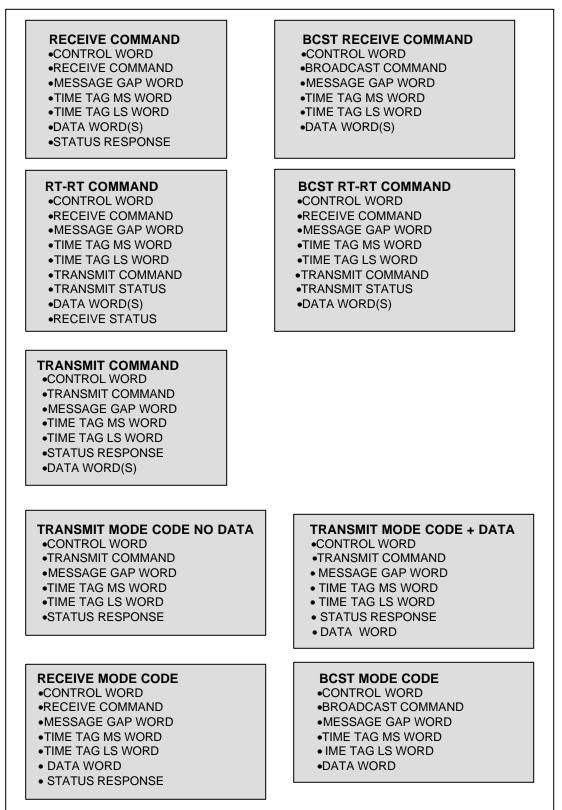

| 4.4.8   | BC MESSAGES                                          |  | 40 |

| 4.5.0   | MESSAGE MONITOR MESSAGE LISTS AND DATA               |  | 42 |

|         | TABLES                                               |  |    |

| 4.5.1   | MESSAGE MONITOR TAG WORD                             |  | 42 |

| 4.5.2   | MESSAGE MONITOR COMMAND/STATUS WORD                  |  | 43 |

| 4.5.3   | MESSAGE MONITOR TIME TAG MS WORD .                   |  | 43 |

| 4.5.4   | MESSAGE MONITOR TIME TAG LS WORD .                   |  | 43 |

| 4.5.5   | MESSAGE MONITOR DATA WORDS .                         |  | 43 |

| 4.5.6   | MESSAGE MONITOR MESSAGE TABLE FORMATS                |  | 44 |

| 4.6.0   | WORD MONITOR DATA TABLES                             |  | 44 |

| 4.6.1   | WORD MONITOR TAG WORD                                |  | 45 |

| 4.6.2   | WORD MONITOR COMMAND / STATUS - DATA                 |  | 46 |

| 4.6.3   | WORD MONITOR TIME TAG MS WORD .                      |  | 46 |

| 4.6.4   | WORD MONITOR TIME TAG LS WORD .                      |  | 46 |

| 5.0.0   | RT MODE CODE OPERATION                               |  | 46 |

| 5.1.0   | GENERAL                                              |  | 46 |

| 5.2.0   | TABLE OF RT MODE CODE RESPONSES                      |  | 47 |

| 5.2.1   | DYNAMIC BUS CONTROL (00000; T/R=1)                   |  | 47 |

| 5.2.2   | SYNCHRONIZE WITHOUT DATA (00001; T/R=1)              |  | 47 |

| 5.2.3   | TRANSMIT LAST STATUS WORD (00010; T/R=1)             |  | 48 |

| 5.2.4   | INITIATE SELF TEST (00011; T/R=1) .                  |  | 48 |

| 5.2.5   | TRANSMITTER SHUTDOWN (00100; T/R=1)                  |  | 48 |

|         |                                                      |  |    |

| 5.2.6   | OVERRIDE TRANSMITTER SHUTDOWN                 | _ |   | 49 |

|---------|-----------------------------------------------|---|---|----|

| 0.2.0   | (00101; T/R=1)                                | • | • |    |

| 5.2.7   | INHIBIT TERMINAL FLAG (00110; T/R=1)          | _ |   | 49 |

| 5.2.8   | OVERRIDE INHIBIT TERMINAL FLAG (00110; T/R=1) |   |   | 49 |

| 5.2.9   | RESET REMOTE TERMINAL (01000; T/ R= 1).       |   |   | 50 |

| 5.2.10  | RESERVED MODE CODES (01001- 01111; T/ R= 1)   |   |   | 50 |

| 5.2.11  | TRANSMIT VECTOR WORD (10000; T/ R= 1) .       |   |   | 50 |

| 5.2.12  | SYNCHRONIZE WITH DATA WORD (10001; T/ R= 0)   |   |   | 51 |

| 5.2.13  | TRANSMIT LAST COMMAND (10010; T/ R= 1).       |   |   | 51 |

| 5.2.14  | TRANSMIT BIT WORD (10011; T/ R= 1)            |   |   | 52 |

| 5.2.15  | SELECTED TRANSMITTER SHUTDOWN                 |   |   | 52 |

|         | (10100; T/ R= 0)                              |   |   |    |

| 5.2.16  | <b>OVERRIDE SELECTED TRANSMITTER SHUTDOWN</b> |   |   | 53 |

|         | (10101; T/ R= 0)                              |   |   |    |

| 5.2.17  | RESERVED MODE CODES (10110- 11111; T/ R= 1)   |   |   | 53 |

| 5.2.18  | RESERVED MODE CODES (10110- 11111; T/ R= 0)   |   |   | 53 |

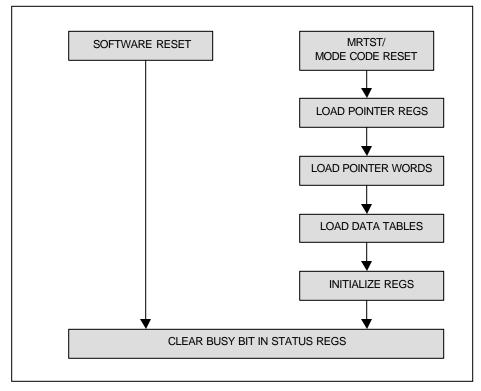

| 6.0.0   | INITIALIZATION                                |   |   | 54 |

| 6.1.0   | INTERNAL INITIALIZATION                       |   |   | 54 |

| 6.2.0   | HOST INITIALIZATION OF NHI-ET                 |   |   | 55 |

| 7.0.0   | INTERRUPT HANDLING                            |   |   | 56 |

| 7.1.0   | HARDWARE INTERRUPT ACKNOWLEDGE .              |   |   | 56 |

| 7.2.0   | SOFTWARE INTERRUPT ACKNOWLEDGE                |   |   | 57 |

| 8.0.0   | TIPS - HINTS 'N TRICKS                        |   |   | 57 |

| 8.1.0   | BUS CONTROLLER APPLICATIONS                   |   |   | 57 |

| 8.1.1   | BC REGISTERS                                  |   |   | 57 |

| 8.1.1.1 | CONFIGURATION REG 2                           |   |   | 57 |

| 8.1.1.2 | CONFIGURATION REG 1                           |   |   | 58 |

| 8.1.1.3 | FRAME "A" POINTER                             | • | • | 58 |

| 8.1.1.4 | FRAME "A" LENGTH                              |   |   | 58 |

| 8.1.1.5 | FRAME "B" POINTER                             | • | • | 58 |

| 8.1.1.6 | FRAME "B" LENGTH                              | • | • | 58 |

| 8.1.1.7 | CONDITION REGISTER                            | • | • | 58 |

| 8.1.1.8 | END OF FRAME GAP                              | • | • | 58 |

| 8.1.1.9 | CONFIGURATION REG 3                           | • | • | 58 |

| 8.1.2   | BCRAM                                         | • | • | 58 |

| 8.1.3   | BC MESSAGE TABLE.                             | • | • | 59 |

| 8.1.4   | BC CONTROL WORD                               | • | • | 59 |

| 8.1.5   | BC COMMAND WORD                               | • | • | 59 |

| 8.1.6   | MESSAGE GAP WORD                              | • | • | 59 |

| 8.1.7   | <u>32 BIT TIME TAG</u> ( 2 WORDS)             | • | • | 60 |

| 8.1.8   | BC INTERRUPTS                                 | • | • | 60 |

| 8.1.9   | BUS CONTROLLER EXAMPLES                       | • | • | 60 |

| 8.1.10  | SAMPLE BUS CONTROLLER MEMORY MAP              | • | • | 61 |

| 8.2.0   | MESSAGE MONITOR APPLICATIONS                  | • | • | 63 |

| 8.2.1   | MESSAGE MONITOR REGISTERS                     | • | • | 63 |

| 8.2.1.1 | CONFIGURATION REG 2                           | • | • | 63 |

| 8.2.1.2 | CONFIGURATION REG 1                           | • | • | 63 |

| 8.2.1.3 | FRAME "A" POINTER.                            | • | • | 64 |

| 8.2.1.4 | FRAME "A" LENGTH                              | • | • | 64 |

| 8.2.1.5 | FRAME "B" POINTER                             | • | • | 64 |

| 8.2.1.6 | FRAME "B" LENGTH                              | • | • | 64 |

| 8.2.1.7 | CONDITION REGISTER                            | • | • | 64 |

| 8.2.1.8 | CONFIGURATION REGISTER 3                      |   | • | 64 |

| 8.2.1.9  | ADDRESS FILTER (15:0)                       |   |   | 64       |

|----------|---------------------------------------------|---|---|----------|

| 8.2.1.10 | ADDRESS FILTER (31:16)                      |   |   | 64       |

| 8.2.2    | MESSAGE MONITOR RAM                         |   |   | 64       |

| 8.2.3    | MESSAGE MONITOR MESSAGE TABLE .             |   |   | 64       |

| 8.2.4    | MESSAGE MONITOR TAG WORD                    |   |   | 65       |

| 8.2.5    | COMMAND WORD OR STATUS WORD                 |   |   | 65       |

| 8.2.6    | DATA WORD(S)                                |   |   | 65       |

| 8.2.7    | MESSAGE MONITOR EXAMPLE                     |   |   | 65       |

| 8.3.0    | WORD MONITOR APPLICATIONS                   |   |   | 65       |

| 8.3.1    | WORD MONITOR REGISTERS                      | • | • | 66       |

| 8.3.1.1  | CONFIGURATION REG 2                         | • | • | 66       |

| 8.3.1.2  | CONFIGURATION REG 1                         | • | • | 66       |

| 8.3.1.3  | BLOCK "A" START                             | • | • | 66       |

| 8.3.1.4  | BLOCK "A" END                               | • | • | 66       |

| 8.3.1.5  | BLOCK "B" START                             | • | • | 66       |

|          | BLOCK "B" END                               | • | • |          |

| 8.3.1.6  |                                             | • | • | 66<br>66 |

| 8.3.1.7  | CONDITION REGISTER                          | • | • | 66       |

| 8.3.1.8  | WORD MONITOR END OF BLOCK OPTIONS .         | • | • | 67       |

| 8.3.1.9  | CONFIGURATION REGISTER 3                    | • | • | 67       |

| 8.3.2    | WORD MONITOR EXAMPLE                        | • | • | 67       |

| 8.4.0    | SIMULTANEOUS MONITOR AND REMOTE TERMINA     | L | • | 67       |

| 8.4.1    | SIMULTANEOUS MODE INTERRUPT HANDLING        |   |   | 67       |

| 8.5.0    | PC BOARD CONSIDERATIONS AND GUIDE LINES     |   |   | 68       |

| 9.0.0    | PIN FUNCTIONAL DESCRIPTION                  |   |   | 68       |

| 9.1.0    | GENERAL PURPOSE SIGNALS                     |   |   | 69       |

| 9.2.0    | HOST INTERFACE SIGNALS                      |   |   | 69       |

| 9.3.0    | DISCRETE I/ O BUS INTERFACE SIGNALS         |   |   | 70       |

| 9.4.0    | MIL BUS INTERFACE SIGNALS                   |   |   | 71       |

| 10.0.0   | ELECTRICAL CHARACTERISTICS                  |   |   | 71       |

| 10.1.0   | ABSOLUTE MAXIMUM RATINGS                    |   |   | 71       |

| 10.2.0   | OPERATING CONDITIONS                        |   |   | 71       |

| 10.3.0   | I/O TYPES & DESCRIPTIONS                    | - | • | 72       |

| 10.4.0   | I/O ELECTRICAL CHARACTERISTICS              | • | • | 72       |

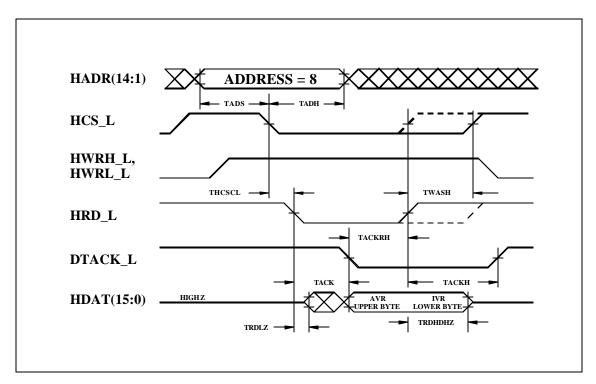

| 11.0.0   | TIMING DIAGRAMS                             | • | • | 73       |

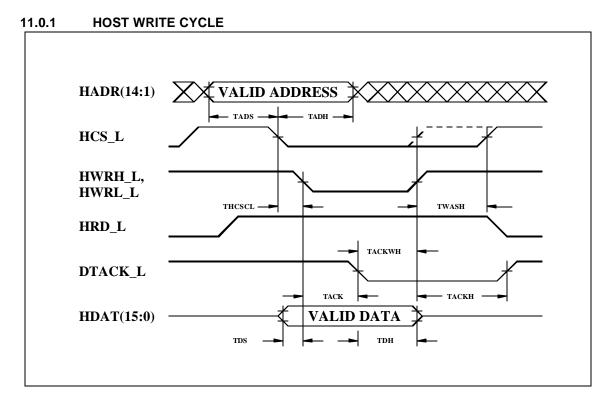

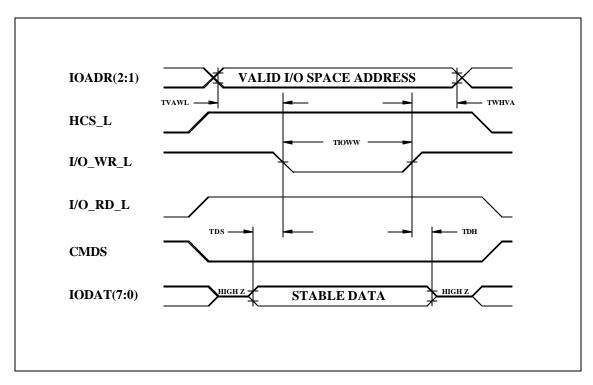

| 11.0.1   | HOST WRITE CYCLE                            | • | • | 73       |

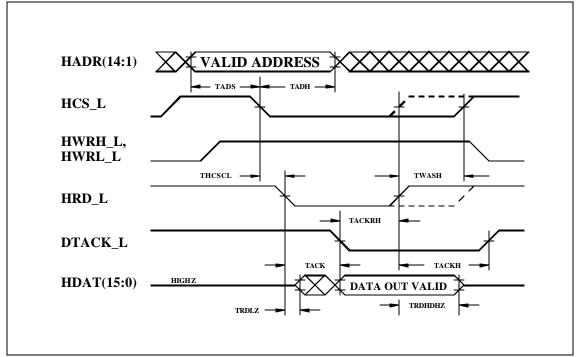

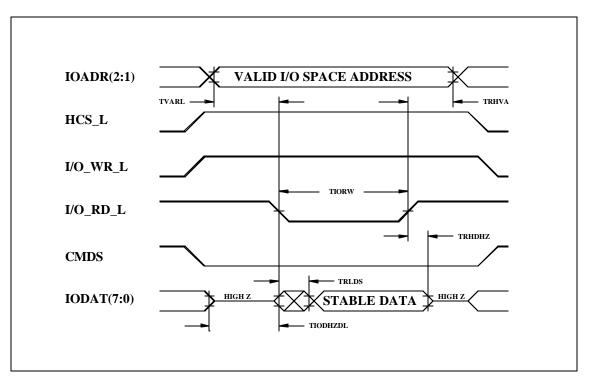

| 11.0.2   | HOST READ CYCLE                             | • | • | 73       |

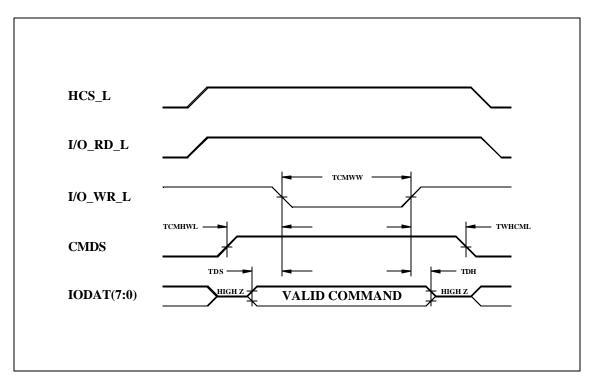

| 11.0.2   |                                             | • | • | 73<br>74 |

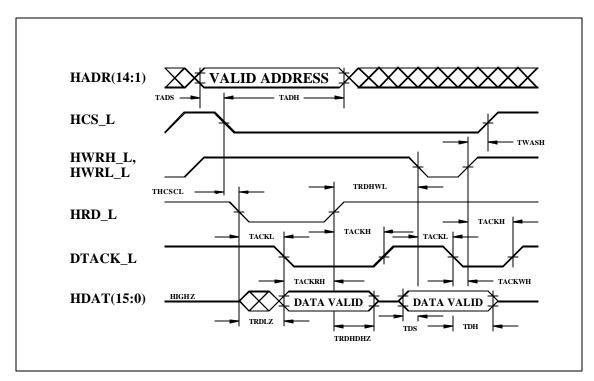

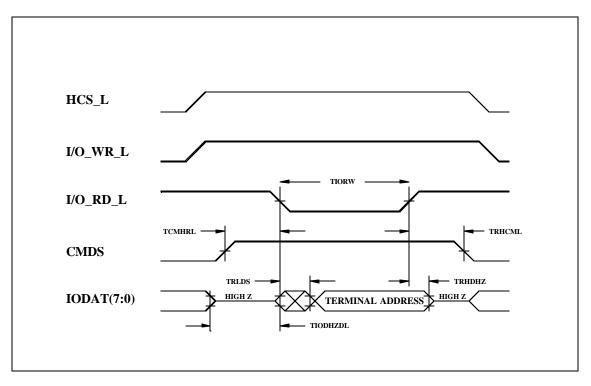

|          | HOST READ- MODIFY- WRITE CYCLE              | - | • |          |

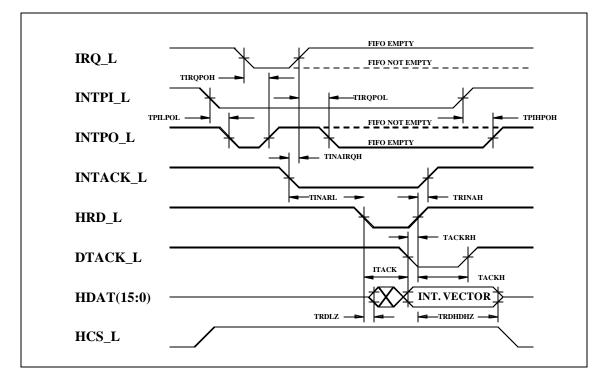

| 11.0.4   | RT HARDWARE INTERRUPT ACKNOWLEDGE CYCL      | E | • | 74       |

| 11.0.5   | <u>I/O WRITE CYCLE</u>                      | • | • | 75       |

| 11.0.6   | I/O READ CYCLE                              | • | • | 75       |

| 11.0.7   | COMMAND WRITE CYCLE                         | • | • | 76       |

| 11.0.8   | TERMINAL ADDRESS READ CYCLE                 | • | • | 76       |

| 11.0.9   | SOFTWARE INTERRUPT ACKNOWLEDGE CYCLE        | • | • | 77       |

| 11.0.10  | TIMING DIAGRAM NOTES                        | • | • | 77       |

| 11.1.0   | TIMING PARAMETER TABLES                     |   |   | 78       |

| 11.1.1   | HOST READ, WRITE; READ- MODIFY- WRITE TABLE | Ξ |   | 78       |

|          | SOFTWARE INTERRUPT ACKNOWLEDGE              |   |   |          |

| 11.1.2   | I/O READ and TERMINAL ADDRESS READ TABLE    |   |   | 78       |

| 11.1.3   | I/O WRITE and COMMAND WRITE TABLE .         |   |   | 78       |

| 11.1.4   | HARDWARE INTERRUPT ACKNOWLEDGE TABLE        |   |   | 79       |

| 12.0.0 | PIN FUNCTIONS                        |  | 80 |

|--------|--------------------------------------|--|----|

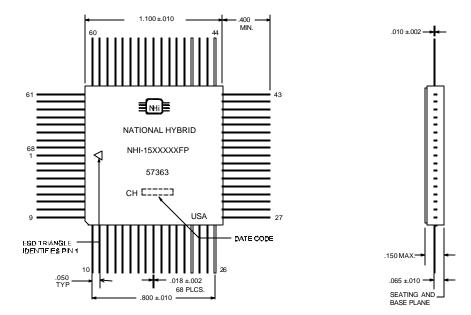

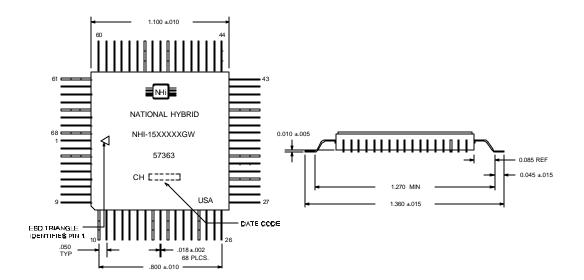

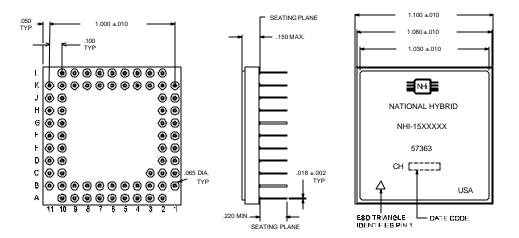

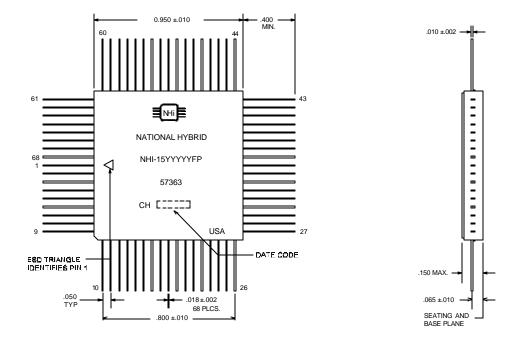

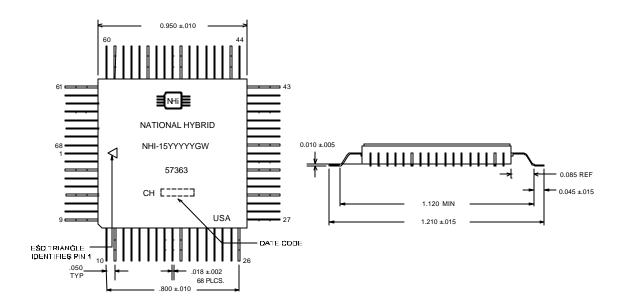

| 12.1.0 | GENERIC PACKAGE OUTLINE DRAWINGS     |  | 81 |

| 12.1.1 | QUAD FLAT PACK UNFORMED LEADS .      |  | 81 |

| 12.1.2 | QUAD FLAT PACK GULL WING LEADS .     |  | 81 |

| 12.1.3 | PIN GRID ARRAY                       |  | 82 |

| 12.1.4 | MICRO QUAD FLAT PACK UNFORMED LEADS  |  | 83 |

| 12.1.5 | MICRO QUAD FLAT PACK GULL WING LEADS |  | 83 |

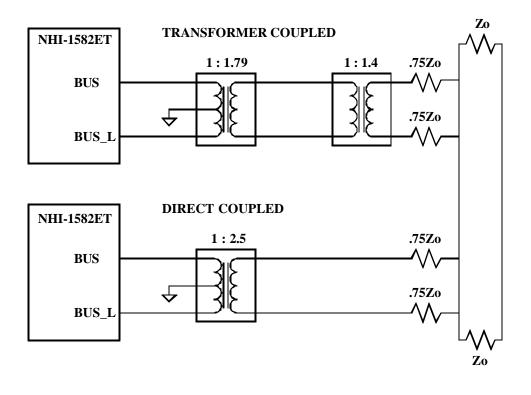

| 13.0.0 | MATING TRANSFORMER REFERENCE         |  | 84 |

| 14.0.0 | ORDERING INFORMATION                 |  | 85 |

#### 1.0.0 <u>SCOPE</u>

This document defines the functional and electrical specification for National Hybrid's series of MIL- STD- Data Bus Enhanced Terminals (NHi- ET).

#### 2.0.0 NHI-ET PROTOCOL COMPLIANCE

MIL- STD- 1553A MIL- STD- 1553B Notices I and II MIL- STD- 1760B MCAIR MDC A3818, A5690, A4905, A5332 EFA/ STANAG- 3838 requirements for Eurofighter Aircraft

#### 3.0.0 INTRODUCTION

The NHi- ET is a low cost complete **Multi-Protocol** Mil- Std- Data Bus Interface between a dual redundant bus and a host processor. The device functions as a programmable Bus Controller, Remote Terminal, and Bus Monitor containing a protocol chip, two +5V monolithic transceivers and 16K or 64K word SRAM. The unit is available packaged in a 1.1" x 1.1" 69 pin ceramic PGA, or 1.1" x 1.1" 68 pin ceramic quad flatpack. The only external components required are two coupling transformers.

The NHi- ET appears to the host computer as 16K or 64K words of 16 bit wide memory controlled by standard RAM signals. The device can thus be easily interfaced with all popular processors and buses. The built in interrupt controller supports an internal FIFO which retains header information for queuing up to 6 pending interrupt requests plus an overflow interrupt.

All modes of operation access data tables via pointers residing in RAM which facilitates multiple buffering. This allows buffers to change without moving data and promotes efficient use of RAM space. The data tables have programmable sizes and locations.

The NHi-ET is plug in compatible with the popular NHi-RT family of remote terminal with no changes to hardware or software required. The NHi-ET defaults to the NHi-RT remote terminal operation on power up.

#### 3.1.0 FEATURES

The NHi- ET is form, fit, and function compatible to the NHi- RT series of parts. This interchange ability gives the user a high degree of flexibility when configuring a system around the NHi family of parts.

#### 3.1.1 GENERAL FEATURES

- Mulit-Protocol Interface

- •Single +5 volt supply.

- •Operates from 10 Mhz clock.

- •Contains two monolithic +5V transceivers

- •Appears to host as a Dual Port Double Buffered 16K or 64K x 16 SRAM

- •Footprint less than 1.25 square inches

- •Ensures integrity of all shared data and control structures

- •Built- in interrupt controller

- •Internal FIFO is configurable to retain header information for queuing up to 6 pending interrupt requests plus an overflow interrupt, or as a 7 interrupt revolving FIFO

- •Provides interrupt priority input and output pins for daisy- chaining interrupt requests

- •Contains a Timer Unit which provides 32 bit RTC (Real- Time- Clock) with 1, 2, 4, 8, 16, 32 and 64 uS internal, or user provided external clock resolution for data and event time tagging.

- •Interfaces with an 8 bit discrete I/ O bus

- •Selectable 768/ 672 us Failsafe Timer with complete Testability

- •Low power CMOS technology

## 3.1.2 Bus Controller Highlights:

- •Implements all Message Formats and Error Checking

- •Simple setup and operation. Preset multiple pointer tables and message blocks. Only two Frame Pointer and Frame Length Registers are required to control unlimited number of message blocks

- •BC initialized by writing to three Configuration Registers and the Interrupt Mask Register

- •Executes lists of messages via Message Frame

- •Configurable Local Retry and Interrupt Requests Enabled on Message by Message Basis

- •Configurable Global Retry and Local Retry

- •Programmable retries per message:

None Retry Current Bus Retry Alternate Bus

Retry Alternate Bus then Current Bus.

- •Programmable response timeout of 14, 18, 26, or 42 microseconds.

- •Programmable Intermessage Gap Time up to 4 mS with 1 uS resolution.

- •Extended Intermessage Gap using NO- OP Feature.

- •Programmable Frame Gap with 64 uS resolution.

- Programmable Interrupts for:

- End of Message End of Frame Response Time Out, Message Error Message Retry RT Status Bit Set FIFO Overflow.

- •Non- Maskable Bus Jam Interrupt.

- •Host controlled commands:

- Start BC Continuous Mode Stop at End of Message Stop at End of Frame Abort, GOTO Alternate Frame.

•Dynamic Bus Switch Upon Successful Retry.

#### 3.1.3 Remote Terminal Highlights:

- •Dynamic Bus Control Acceptance

- •DBCA\_ L bit is set in configuration register.

- •Message Illegality is internally programmable. DOES NOT require external PROMS or glue logic.

- •Employs data tables with individual tag words which indicate whether or not the data is valid, updated since last read, in the process of being updated, was received via broadcast command, or has been lost (i. e. updated more than once by a receive message before being read).

- •Optionally sets the subsystem flag bit whenever stale data is transmitted or received data is overwritten.

- •Issues interrupts on any subset of T/ R bit, subaddresses, mode commands, broadcast messages and errors.

- •Provides interrupt priority input and output pins for daisy- chaining interrupt requests. messages.

- •Optionally resets the real- time clock in response to a "Synchronize" mode command.

- •Optionally updates the lower 16 bits of the real- time clock in response to a "Synchronize WithData" command.

- •Indicates the reception of specific commands by outputting pulses on any one of 8 pins.

- •Internally loops- back messages under host control for test purposes.

- •Employs a decoder algorithm which ensures high noise immunity and a low error rate.

- •Software RT Address Lockout.

- •MDC3818 Status Response, Error Handling, Status Bit Definition, Mode Code Operation.

- Separate Broadcast Interrupts.

# 3.1.4 Bus Monitor Highlights:

- •Simple setup and operation

- •Preset multiple data blocks.

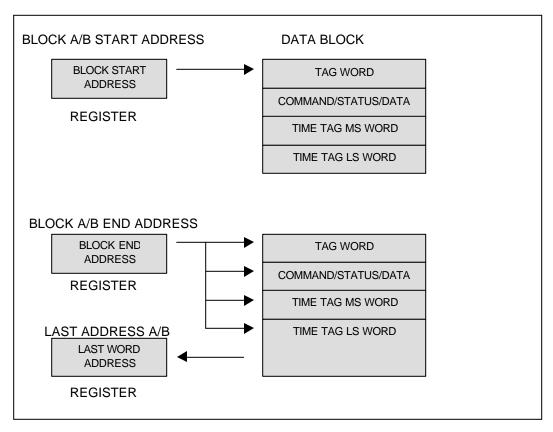

- •Only two MT Data Start Address and MT Data End Address Registers are required to control unlimited number of message blocks. The data block sizes and locations are totally Programmable.

•MT initialized by writing to three MT Configuration Registers and the MT Interrupt Mask Register.

- •Error detection and reporting

- •All encoding, timing and protocol errors defined by the Protocols are detected.

- •Programmable Monitor Modes:

- Word Monitor, transfers all data with/ without ID and Time Tag words.

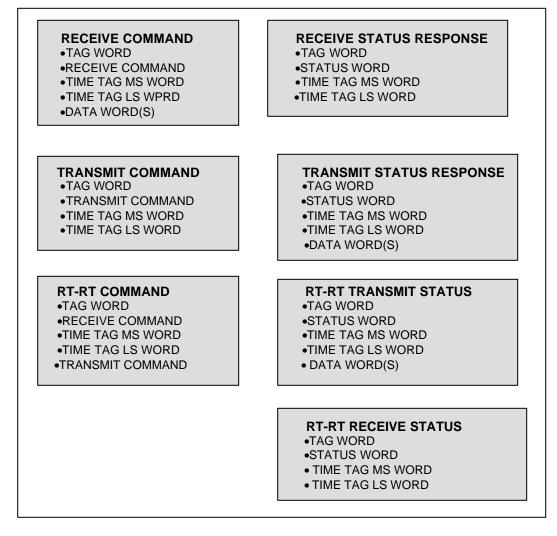

- Message Monitor, transfers all Command and Status words with/ without ID and Time Tag, while data words are transferred directly to conserve memory space.

- •Concurrent Bus Monitor and Remote Terminal operation.

- •Selective Message Monitor, based on RT Address.

- •Programmable Interrupt for End of Block and End of Frame.

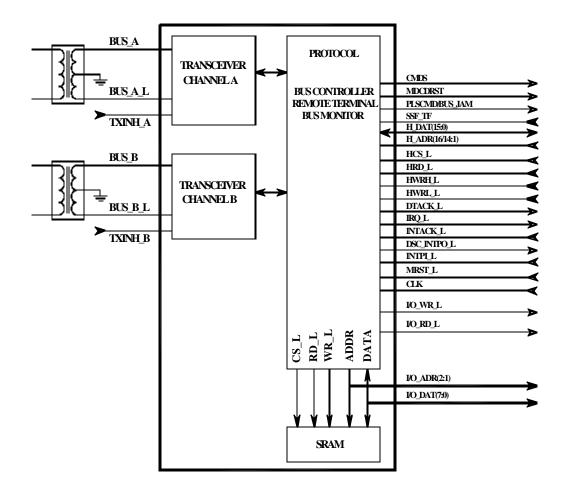

#### 3.2.0 BLOCK DIAGRAM

The NHi- ETs contains two +5 volt transceivers, an ASIC, and an SRAM. The ASIC performs all multi protocol functions; BUS CONTROLLER, BUS MONITOR and REMOTE TERMINAL. It controls accesses to the RAM such that it appears to the host CPU 16bit wide dual port memory.

Since the NHi- ET appears to its host as RAM, no external logic is required when interfacing to the device. It is simply connected to the CPU's address bus, Mil Bus, and control lines. There are NO EPROMS required to illegalize commands in the RT mode. Illegalization is performed internal to the protocol chip in the NHi- ET.The user sets up command illegalization when the NHi- ET is initialized. See sections on Message Illegalization and Host Initialization.

#### NHI-ET ENHANCED TERMINAL FUNCTIONAL BLOCK DIAGRAM

The NHi- ET can be interfaced to an 8 bit CPU Bus by folding the upper and lower bytes on top of each other and performing byte wide data transfers.

By default, the host has priority in accessing the I/ O bus. When the host requests access to a device already in use by the protocol chip, the host \*DTACK signal is delayed by the NHi- ET. If either side (protocol chip or host) waits for access during the current cycle, it is automatically granted priority for the next cycle. The host can retain priority for successive cycles accessing the same address (this is required to guarantee the proper operation of host read- modify- write instructions - see pin \*HCS for details) by keeping \*HCS low.

#### 3.3.0 PROTOCOL CHIP DESCRIPTION

The protocol chip contains the following modules:

| Host Bus Interface Unit                 | (HBIU) |

|-----------------------------------------|--------|

| I/ O Bus Interface Unit                 | (IBIU) |

| Interrupt Controller Unit               | (ICU)  |

| Dual Redundant multi protocol Front End | (DRFE) |

| Message Processor Unit                  | (MPU)  |

#### 3.3.1 HOST BUS INTERFACE UNIT

The HBIU provides a standard RAM interface to the host bus. The module performs the following functions:

Provides NHi- ET device select and decodes host address to select registers. Transfers data between the NHi-ET and the host (word and byte mode as well as readmodify- write are supported).

Provides priority input and output for daisy chaining host interrupts. Outputs \*DTACK signal indicating end of bus cycle.

#### 3.3.2 I/O BUS INTERFACE UNIT

The IBIU controls the RAM and I/ O residing on the I/ O bus so that it appears to the host as a pseudo dual port RAM (i. e., shared memory). The unit implements the following functions:

Arbitrates between host and protocol chip initiated accesses to the RAM and host data bus.

Decodes address lines to select device (e. g. RAM, external byte- wide I/ O, external terminal address buffer, command output register). Generates control signals to access the selected device.

#### 3.3.3 INTERRUPT CONTROL UNIT

The ICU is an 8 input vectored interrupt controller. It contains eight registers as well as a FIFO for storing pending interrupt vectors.

#### 3.3.3.1 ICU REGISTERS

The ICU contains the following registers

| INTERRUPT REQUEST register | (IRR) |

|----------------------------|-------|

| INTERRUPT MASK register    | (IMR) |

| INTERRUPT VECTOR register  | (IVR) |

| AUXILIARY VECTOR register  | (AVR) |

The INTERRUPT REQUEST register samples 8 inputs originating from internal modules. Since the host can write to this register, all interrupt sequences can be software driven for program debugging. The inputs and their priorities (level 7 has highest priority) are described in the following table.

#### 3.3.3.1.1 INTERRUPT DEFINITION TABLE

| PRIORITY | RTU INTERRUPT     | BCU INTERRUPT    | MTU INTERRUPT |

|----------|-------------------|------------------|---------------|

| 0        | VALID TX/RX EOM   | END OF MESSAGE   | N/A           |

| 1        | INVALID TX/RX EOM | END OF FRAME     | N/A           |

| 2        | VALID MODE CODE   | ERROR            | N/A           |

| 3        | INVALID MODE CODE | RETRY            | N/A           |

| 4        | FIFO OVERFLOW     | FIFO OVERFLOW    | FIFO OVERFLOW |

| 5        | VALID BROADCAST   | STATUS SET       | END OF FRAME  |

| 6        | INVALID BROADCAST | NO RESPONSE      | N/A           |

| 7        | FAILSAFE TIMEOUT  | FAILSAFE TIMEOUT | N/A           |

#### Note: RT Interrupts 5 & 6 are enabled only when separate Broadcast Tables are used. Masking interrupt 4 creates a revolving Fifo.

As soon as an interrupt is requested, its vector is pushed onto the FIFO - so the chronological order of the requests normally determines the order in which they will be serviced. Simultaneous requests, however, are pushed onto the FIFO according to the priority of the pending interrupts.

The INTERRUPT MASK register masks the corresponding inputs to the INTERRUPT REQUEST register. The INTERRUPT VECTOR register holds the 3 bit interrupt priority level and an additional 5 bit field (see paragraph on INTERRUPT VECTOR register for details).

The AUXILIARY VECTOR register contains an additional byte of information related to the interrupt request (see paragraph on AUXILIARY VECTOR register for details).

#### 3.3.3.2 ICU FIFO

The ICU FIFO is 16 bits wide and 7 words deep. Whenever an unmasked interrupt request is issued by the message processor, a word is pushed onto the FIFO. When an interrupt is acknowledged by the host, a word is popped from the FIFO and used to update the IVR and the AVR.

The host can read the FIFO by simply popping its contents. This is done by reading the FIFO located at address 8 (refer to address map). The interrupt request output, \*IRQ, will go inactive after the FIFO is emptied in this way.

The host can mask the \*IRQ output by resetting the INTERRUPT REQUEST ENABLE bit in the CONTROL register; however this does not prevent the device from pushing interrupt requests onto the FIFO.

If an interrupt request occurs when the FIFO is full, a vector indicating FIFO overflow is first pushed onto the FIFO and then the vector which caused the overflow is pushed onto the FIFO. As a result, the 2 oldest vectors are lost. All further pushes are then inhibited until the host pops the vector indicating the overflow.

The above mechanism ensures that the host will always be notified of FIFO overflows and will always obtain the 2 interrupt vectors immediately preceding the overflow condition.

If interrupt 4 is masked, the FIFO operates in the revolving mode; vectors are continuously pushed onto the FIFO. After the 7th vector is pushed without any pops, each additional vector pushed causes the oldest vector to be lost.

The FIFO can be emptied by writing (any value) to address 8 (in words).

# 3.3.4 DUAL REDUNDANT FRONT END

The DRFE performs serial to parallel and parallel to serial conversion as well as basic format and timing validation. The unit contains the following:

Manchester encoders/ decoders Gap counter No response counter Minimum response time counter Timeout counter

# 3.3.4.1 MANCHESTER DECODER

The decoder translates serial Manchester bi- phase signals to 16- bit words and outputs the following signals:

Valid command word received

Valid data word received

Invalid word received (parity, incorrect bit count, invalid Manchester encoding, gap) Broadcast command received

Begin new message (i. e., end of a valid legal command for this Remote Terminal)

# 3.3.4.2 MANCHESTER ENCODER

The encoder receives 16 bit words and transmits them with the appropriate sync and parity as a serial Manchester bi- phase signal. The outputs of the encoder can be loop- backed into either decoder for test purposes.

#### 3.3.4.3 GAP COUNTER

The gap counter checks contiguity of successive words. If the time between "contiguous" words (measured from zero- cross of parity to zero- cross of sync) exceeds 3.5 - 3.7 microseconds, the message is invalidated.

# 3.3.4.4 RT - RT NO RESPONSE COUNTER

The no response counter checks the response time of the transmitting RT in a RT to RT transfer. If the response time is exceeded, the message is invalidated. The response time is software programmable (14, 18, 26, 42 microseconds) to accommodate systems with long cables and/ or slow terminals.

#### 3.3.4.5 MINIMUM RESPONSE TIME COUNTER

The minimum response time counter ensures that the response will be no sooner than 4 microseconds

(measured from zero- cross of parity to zero- cross of sync).

#### 3.3.4.6 FAIL -SAFE TIMEOUT COUNTER

This counter inhibits the encoder outputs and issues a TIMEOUT interrupt whenever continuous transmission exceeds 768/ 672 microseconds. Transmission will remain inhibited until a command is received on the same bus or the part is reset.

#### 3.3.5 MESSAGE PROCESSOR UNIT

The MPU forms the heart of the protocol chip and controls the operation of the Decoders, Encoders, and Interrupt Controller. This unit is activated by the reception of a valid legal command addressed to the RT in the RT mode and the START bit in CONFIGURATION 1 in both the BC and MT modes. The MPU performs the following functions:

Recognizes the various message types (for BC, MT, and RT) and responds with the appropriate sequence of control signals. Validates format and timing of received data words. Checks command legality. Responds with status/ data. Calculates all addresses for accessing the RAM and discrete I/ O. Updates RAM data table contents, including tag words. Optionally time tags data tables. Issues interrupt requests to the ICU. The maximum response time of the NHi- ET in the RT mode is less than 6.0 microseconds (measured from zero- cross to zero- cross).

# 3.4.0 <u>RT HARDWIRE TERMINAL ADDRESS</u>

The terminal address of the NHi- ET can be hardwired using I/ O DAT( 5: 0). I/ O DAT( 4: 0) are used for the terminal address, I/ O DAT0 being the LSB, and I/ O DAT5 is used to set odd parity in the address. These pins CANNOT be directly connected to +5 or ground since the I/ O data bus drives the NHi- ET's internal RAM.

The address must be wired using pull- up and pull- down resistors. There are 64K internal pull- up resistors in the protocol chip, so only external pull- down resistors of 4.7K are required. The Hardwire Address is read and loaded into the terminal at Power- On Reset, Hardware Reset, and Software Reset.

The terminal address can be changed at any time through software by writing a new address to the Basic Status Register, however, if any of the above resets occur, the Hardwire Address will be re- loaded into the terminal. The software address can be locked out by setting Bit2 in Configuration Register 1.

## 4.0.0 DATA STRUCTURE

#### 4.1.0 ADDRESS MAP

The NHi- ET appears to the host as 16K or 64K words of memory divided into the following blocks:

| ADDRESS RANGE  | DESCRIPTION        |

|----------------|--------------------|

| 0 30           | INTERNAL REGISTERS |

| 31             | I/O TAG WORD       |

| 32 35          | I/O SPACE          |

| 64 16383/65535 | SHARED RAM         |

# INTERNAL REGISTER MAP

| ADDRESS | REGISTER DEFINITION                         | ACCESS |

|---------|---------------------------------------------|--------|

| 0       | CONTROL                                     | R/W    |

| 1       | POINTER TABLE ADDRESS                       |        |

| 2       | BASIC STATUS                                | R/W    |

| 3       | INTERRUPT MASK(lower byte)                  | R/W    |

| 3       | INTERRUPT VECTOR(upper byte)                | R      |

| 3       | INTERRUPT REQUEST(upper byte)               | W      |

| 4       | INTERRUPT VECTOR(lower byte)                | R/W    |

| 4       | AUXILLARY VECTOR(upper byte)                | R      |

| 4       | CONFIGURATION 2(upper byte, BCU/MTU only)   | W      |

| 5       | REAL TIME CLOCK HIGH WORD                   | R      |

| 6       | REAL TIME CLOCK LOW WORD                    | R      |

| 7       | REAL TIME CLOCK CONTROL                     | R/W    |

| 8       | READ FIFO                                   | R      |

| 8       | RESET FIFO                                  | W      |

| 9       | CONFIGURATION 1                             | R/W    |

| 10      | RESERVED                                    |        |

| 11      | LAST COMMAND                                | R      |

| 12      | LAST STATUS                                 | R      |

| 13      | FRAME "A" LOCATION/BLOCK "A" START          | R/W    |

| 14      | FRAME "A" LENGTH/BLOCK :A" END              | R/W    |

| 15      | RESET TERMINAL(both bytes)                  | W      |

| 16      | FRAME "B" LOCATION/BLOCK "B" START          | R/W    |

| 17      | FRAME "B" LENGTH/BLOCK "B" END              | R/W    |

| 18      | ENCODER STATUS                              | R      |

| 19      | CONDITION                                   | R      |

| 20      | BCU FRAME GAP/WORD MTU END OF FRAME OPTIONS | R/W    |

| 21      | CONFIGURATION 3                             | R/W    |

| 22      | MESSAGE MONITOR ADDRESS FILTER(0 15)        | R/W    |

| 23      | ENCODER DATA*                               | R/W    |

| 24      | ENCODER DATA TX REQUEST*                    | W      |

| 25      | ENCODER COMMAND TX REQUEST*                 | W      |

| 26      | MESSAGE MONITOR ADDRESS FILTER(16 31)       | R/W    |

| 27      | WORD MONITOR BLOCK "A" LAST ADDRESS         | R      |

| 28      | WORD MONITOR BLOCK "B" LAST ADDRESS         | R      |

| 29      | RESERVED                                    |        |

| 30      | EXTERNAL RTU ADDRESS BUFFER(lowre byte)     | R      |

| 30      | COMMAND OUTPUT PINS                         | W      |

| 31      | I/O TAG WORD                                | R/W    |

\*In order to write to addresses 23, 24, or 25, the ET must be in loop- back in the RT mode (see CONTROL register for details).

#### 4.2.0 INTERNAL REGISTERS

#### 4.2.1 CONTROL Address: 0 R/W BC/MT/RT

This register controls the general operation of the NHi- ET.

| 15  | 14   | 13   | 12     | 11    | 10    | 9     | 8     |

|-----|------|------|--------|-------|-------|-------|-------|

| HWD | RSP1 | RSP0 | TSTFST | NBCST | TXINH | LOOPB | LOOPA |

| 7   | 6    | 5    | 4      | 3     | 2     | 1     | 0     |

|     |      |      |        |       |       |       |       |

#### HWD

D Bits: 15

1 = Enables high word detection.

This option allows extra words in a message to be detected, as required by some protocols. 0= Tterminal does not detect high word errors.

RSP1, RSP0

Bits: 14,13

BC/ RT

RT

BC/RT

These bits define the response timeout for RT- RT messages in the RT mode and terminal response timeout in the BC mode as follows:

| RSP1 | RSP0 | TIMEOUT(us) |

|------|------|-------------|

| 0    | 0    | 14          |

| 0    | 1    | 18          |

| 1    | 0    | 26          |

| 1    | 1    | 42          |

#### TSTFST

1= Enables testing of the FAIL SAFE time out.

When this feature is enabled, the RT will transmit continuously once it is enabled by a valid message. The encoder will be inhibited after 768/ 672us. It will be enabled by a reset or the reception of another valid message. If this bit is set to 0 during an RT transmission, before the required number of words have been transmitted, the encoder will return to normal operation and stop at the proper message length.. If it is set to 0 after the message length has been exceeded, the current word will be completed and normal operation resumed. This feature can be used in the LOOPBACK mode to automatically transmit data words. The RT encoder will remain in the tester mode until the CPU sets this bit to 0.

Bits: 12

#### The TSTFST Bit Must Always Be Set to Zero During Normal Operation!!!

| <b>NBCST</b><br>1= Specifies that broadcast commands WILL be                                             | Bits: 11<br>ignored by the RT.          | RT                           |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------|

| <b>TXINH</b><br>1= Inhibits transmission by forcing TXA= TXAN=                                           | <b>Bits: 10</b><br>0 and TXB= TXBN= 0.  | BC/ RT                       |

| LOOPA( B)<br>1= Defines that decoder A (B) inputs shall be co<br>than the transceiver for test purposes. | Bits: 9, 8<br>nnected internally to the | RT<br>encoder outputs rather |

| <b>IRE</b><br>1= Globally enables the interrupt request output,                                          | <b>Bits: 7</b><br>*IRQ.                 | BC/ MT/ RT                   |

0= Disables all interrupt requests; however, interrupt vectors are still pushed onto the FIFO.

#### MIO

RT

1= Defines that certain reserved mode commands with data shall be legal and access the I/ O bus without dependence on host initialization or the BUSY bit in the BASIC STATUS register. This feature can be used, for example, to set a watchdog timer or read a hardware status register via the Mil Bus even though the host's state may be undefined.

The I/ O operations are restricted to the data word's lower byte. The mode commands and their corresponding I/ O addresses in decimal are as follows:

| T/R | MODE CODE | I/O ADR(2,1) | I/O WR_L | I/O RD_L |

|-----|-----------|--------------|----------|----------|

| Т   | 24        | 00           | 1        | 0        |

| Т   | 25        | 10           | 1        | 0        |

| R   | 27        | 10           | 0        | 1        |

| R   | 28        | 00           | 0        | 1        |

#### CMD0

0= Specifies that after a legal valid command is received, a pulse shall be outputted on a pin specified by the PULSE field in the corresponding data table tag word. The pulse is activated together with 2 I/ O control signals (CMDS= 1 and \*I/ O WR = 0).

Bits: 5

1= Specifies that after a valid legal command is received, the word count/ mode code field (together with CMDS= 1 and \*I/ O WR = 0) shall be outputted on the 5 least significant bits of the discrete I/ O bus. (Although the protocol chip outputs the entire command, only 5 bits are outputted by the NHi- RT due to pin- out restrictions).

#### SRQRST

#### Bits: 4

1= Specifies that the service request bit in the STATUS word will be reset upon reception of a valid "Transmit Vector Word" mode command.

#### SSF\_TF

#### Bits: 3

RT

RT

RT

- 0= Specifies that the Sub- System Flag in the Status Word will be determined by the value of the SSF\_ TF pin.

- 1= Specifies that the Terminal Flag in the Status Word will be determined by the value of the SSF\_ TF pin.

# NTAG Bits: 2 RT 1= Specifies that all the data tables shall be without tag words. This mode of operation can be used to store received data from several subaddresses into a contiguous block without interspersed tag words. This feature can facilitate, for example, software upload.

| <b>BINH</b><br>1= Disables reception on bus B. | Bits: 1 | BC/ RT |

|------------------------------------------------|---------|--------|

| <b>AINH</b><br>1= Disables reception on bus A. | Bits: 0 | BC/ RT |

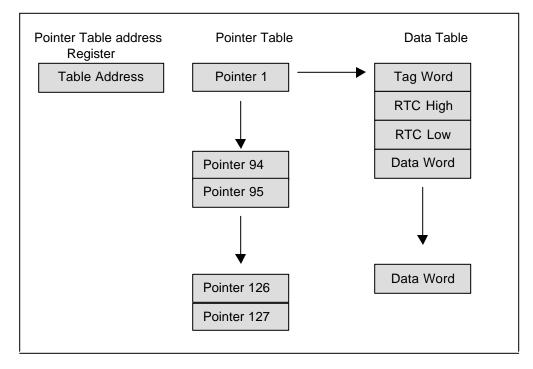

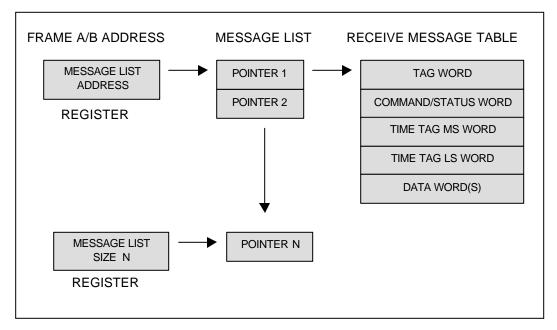

**4.2.2 POINTER TABLE ADDRESS** Address: 1 R/W RT This register holds the address of the table of pointers used in the RT mode when accessing data tables. The address is specified as a word address in the lower 4K of the memory space. After POR the register is initialized to 1000 (hex), with D1 as the LSB of the word address. D0 is a DON'T CARE and should be set to 0.

**Note:** The RT pointer table must always be located in the lower 4K words of memory.

# 4.2.3 BASIC STATUS Address: 2 R/W RT

This register defines the terminal address as well as default values for all status bits. The Status Word is OR'ed with this register before transmission. The bits in the BASIC STATUS register correspond to the bits in the STATUS register and their function is defined in MIL- STD- 1553B. They can be redefined for other protocols.

| 15    | 14       | 13    | 12    | 11    | 10    | 9     | 8    |

|-------|----------|-------|-------|-------|-------|-------|------|

| TADR4 | TADR3    | TADR2 | TADR1 | TADR0 | M_ERR | INSTR | SREQ |

| 7     | <u>^</u> | E     | 4     | 2     | 0     | 4     | 0    |

| 1     | 6        | ວ     | 4     | 3     | 2     |       | U    |

The mechanism employed by the protocol chip for initializing the terminal address is designed to avoid dedicated pins. Upon POR the terminal address and its parity are automatically read from address 30 on the I/ O bus. The value can be supplied in 2 ways: by enabling the output of an external terminal address buffer or by employing pull- up/ down resistors to define a default value for the 6 least significant bits of the I/ O data bus. Odd parity is used to define a valid terminal address; even parity will inhibit reception on both buses. After POR, the host can change the terminal address through software by writing to the TADR field with any desired value. In addition, this operation will enable reception. Providing Bit 2 of Configuration Register is set to "0".

The host can check the validity of the parity bit obtained from the I/ O bus by reading address 30; if the most significant bit in the lower byte equals 1, the parity is invalid.

If the TADR is not defined externally (by pull- down resistors or a buffer), there is no danger of a false response before host initialization because internal pull- up resistors on the I/ O bus guarantee an incorrect terminal address parity.

When BUSY= 1, 1553 message accesses to the RAM are inhibited, however the RT will respond with status as required by MIL- STD- 1553B. The mode commands "Transmit Status Word", "Transmit Last Command Word", "Reset Remote Terminal", "Transmitter Shutdown", "Override Transmitter Shutdown" and the reserved mode commands legalized by MIO (see the CONTROL register for details) are not affected by BUSY. In addition, all output pulses issued after valid command reception are inhibited when BUSY= 1 (except for the signal MDCDRST which is pulsed after receiving the mode command "Reset").

After POR(MRST), BUSY is set to "1"; this prevents the RT from using undefined pointers before the host has had a chance to initialize the POINTER TABLE. The default value for all other status bits is "0" and the TADR field is loaded with the hardwired address.

The BUSY Bit in the LAST STATUS REGISTER is cleared on receipt of the first command after a RESET, except if that command is TRANSMIT LAST STATUS or TRANSMIT LAST COMMAND mode command.

The BUSY Bit in the LAST STATUS REGISTER can be cleared by bit using BIT 5 in the RTC CONTROL REGISTER. See RTC CONTROL REGISTER for details.

# 4.2.4INTERRUPT REQUESTAddress: 3(Ubyte)WBC/ MT/ RTThe INTERRUPT REQUEST register holds 8 types of interrupt requests (see section on

INTERRUPT CONTROL UNIT for details). Interrupt requests are active high and upon POR the register is cleared (see initialization section).

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |

|------|------|------|------|------|------|------|------|

| IRQ7 | IRQ6 | IRQ5 | IRQ4 | IRQ3 | IRQ2 | IRQ1 | IRQ0 |

# **4.2.5 INTERRUPT MASK Address: 3 Lbyte R/W BC/MT/RT** The INTERRUPT MASK register masks the corresponding interrupts. Upon POR, all interrupts are masked (see initialization section).

| [ | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

|   | IMSK7 | IMSK6 | IMSK5 | IMSK4 | IMSK3 | IMSK2 | IMSK1 | IMSK0 |

#### 4.2.6 INTERRUPT VECTOR INTERRUPT VECTOR

Address: 3(Ubyte) R BC/ MT/ RT Address: 4(Lbyte) R/ W BC/ MT/ RT

The IVR is read only in the upper byte at address 3 and is read/ write in the lower byte at address 4. It contains interrupt header information which is popped off the FIFO.

| ADD | R3(4) | 15(7)  | 14(6)  | 13(5)  | 12(4)  | 11(3)  | 9(2) | 10(1) | 8(0) |

|-----|-------|--------|--------|--------|--------|--------|------|-------|------|

|     | RT    | D4     | D3     | D2     | D1     | D0     | L2   | L1    | L0   |

| (B0 | C/MT) | (CNT4) | (CNT3) | (CNT2) | (CNT1) | (CNT0) | L2   | L1    | LO   |

The Interrupt Vector register is loaded with LLL and CNT data from the fifo when it is popped. The fifo is popped by a hardware interrupt acknowledge or a read to address 8. This register in undefined at POR.

#### L(2: 0)

This is the interrupt priority determined by the message processor which is a function of the BC, MT and RT modes of operation.

# D(4: 0)

In the RT mode the DDDDD field is inputted by the CPU. This is used as an offset for the interrupt vector. During a hardware interrupt acknowledge, this register is outputted on the upper and lower bytes of the CPU data bus. This output vector only occurs when the terminal is functioning as an RT.

# CNT(4: 0)

In the BC and MESSAGE MONITOR modes the CNT field is the lower five bits of the number of the message in the frame which caused the interrupt.

#### 4.2.7 **CONFIGURATION REGISTER 2** Address: 4(Ubyte) W BC/MT/RT

This register is used for operational control of the part.

| 15              | 14    | 13             | 12             | 11          | 10              | 9          | 8               |

|-----------------|-------|----------------|----------------|-------------|-----------------|------------|-----------------|

| GO DEF<br>FRAME | ABORT | STOP AT<br>EOF | STOP AT<br>EOM | CLR<br>DISC | GO EOF<br>CNTNU | GO<br>NEXT | DO EOM<br>CNTNU |

Bits: 15

Bits: 14

Bits: 13

**NOTE:** Bits 8 -10 are only used in the BC mode during a BUS JAM condition.

#### GO DEF FRAME

When a "1" is written to this bit, the DEFAULT FRAME, defined by bit 12 in CONFIGURATION REGISTER 1, is made the active frame.

#### ABORT

When a "1" is written to this bit, all BC and MT processing is terminated and the NHi- ET goes off- line. The BC or the MT must be re- started to again become active.

#### STOP END OF FRAME

When a "1" is written to this bit, the BC or the MT will go off- line after the last message in the frame or block has been processed. The BC or the MT must be re- started to again become active.

#### STOP END OF MESSAGE Bits: 12 When a "1" is written to this bit, the BC or the MT will go off- line after the current message in

the frame or block has been processed. The BC or the MT must be re- started to again become active.

CLR DISC FLAG Bits: 11 RT When a "1" is written to this bit, the 1760 DISCONNECT FLAG is cleared. This flag indicates that a store has been released and all the address bits and the parity bit on the hardwire address are "1's". The flag is read on the IPO\_ DSC pin and bit 6 of the EXTERNAL TERMINAL ADDRESS REGISTER.

#### **GO EOF & CONTINUE** Bits: 10 BC.

When a "1" is written to this bit after a BUS JAM condition has halted the BC operation, the BC will ignore all further messages in the current frame, proceed to the end of the frame and perform the programmed EOF operations.

#### GO NEXT MESSAGE Bits: 9 BC

When a "1" is written to this bit after a BUS JAM condition has halted the BC operation, the BC will abort the current message and NOT perform the programmed EOM operations; instead, the next message in the frame will be activated. If there are no more messages in the frame, the programmed EOF operations will be performed.

#### **DO EOM & CONTINUE** BC Bits: 8 When a "1" is written to this bit after a BUS JAM condition has halted the BC operation. the BC will perform the programmed EOM operations, then the next message in the frame will be activated. If there are no more messages in the frame, the programmed EOF operations will be performed.

The contents of CONFIGURATION REGISTER 2 are not affected by these operations and all the bits are always read by the host as "0" after the indicated action has been completed.

BC/MT

BC/MT

BC/MT

BC/MT

| from t               | This register contains additional information related to the interrupt request. The data is popped from the FIFO and latched into the AVR during the interrupt acknowledge cycle or whenever the FIFO is popped by a host read instruction to address 8. Upon POR, this register is undefined. |         |         |       |                |                |                |                |                |   |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|-------|----------------|----------------|----------------|----------------|----------------|---|

|                      | MODE                                                                                                                                                                                                                                                                                           | 15      | 14      | 13    | 12             | 11             | 9              | 10             | 8              |   |

|                      | RTU                                                                                                                                                                                                                                                                                            | EMP     | BUS     | T/R   | SADR4<br>MODE4 | SADR3<br>MODE3 | SADR2<br>MODE2 | SADR1<br>MODE1 | SADR0<br>MODE0 |   |

|                      | BCU                                                                                                                                                                                                                                                                                            | EMP     | BUS     | FRAME | CNT9           | CNT8           | CNT7           | CNT6           | CNT5           |   |

|                      | MTU                                                                                                                                                                                                                                                                                            | EMP     | BUS     | FRAME | CNT9           | CNT8           | CNT7           | CNT6           | CNT5           |   |

|                      | fo empty.<br>fo data va                                                                                                                                                                                                                                                                        | •       |         |       | Bits: 1        | 5              |                | B              | C/MT/RT        | T |

|                      | dicates th<br>dicates th                                                                                                                                                                                                                                                                       |         |         |       |                | 4              |                | ļ              | BC/MT/RT       |   |

| <b>T/ R</b><br>0= In | dicates a                                                                                                                                                                                                                                                                                      | receive | message |       | Bits: 1        | 3              |                |                | RT             |   |

1= Indicates a transmit message.

#### RT SADR / MODE Bits: (12-8) This field defines the sub- address or mode code. Note: the interrupt level distinguishes between regular transmit/ receive commands and mode commands.

#### CNT Bits: (12-8) BC/MT The CNT field is the upper five bits of the number of the message in the frame which caused the interrupt.

| FRAME                            | Bits: 13 | BC/MT |

|----------------------------------|----------|-------|

| 0= Indicates message in frame A. |          |       |

| 1= Indicates message in frame B. |          |       |

| 4.2.9   | REAL- TIMI     | E CLOCK       |                      |            |        |           |

|---------|----------------|---------------|----------------------|------------|--------|-----------|

|         | RTC HIGH       | WORD          | Address:             | 5          | R      | BC/MT/RT  |

|         | RTC LOW V      | NORD          | Address              | 6          | R      | BC/MT/RT  |

| The DTC | ic a 22 hit up | oountor which | oon he used for time | togging in | the DC | MT and DT |

The RTC is a 32 bit up- counter which can be used for time- tagging in the BC, MT and RT modes. If the time- tagging option is in effect, the RTC is sampled and stored in 2 words in the data table The most significant word is stored first.

When messages are time- tagged in the RT mode, the host should not write data to the first 2 locations following the data table tag word since they will be overwritten with the value of the message time tag.

In the RT mode, the RTC can be reset by the mode command "Synchronize Without Data" and the least significant 16 bits can be updated by "Synchronize With Data". The full 32 bits can be updated using the first two data words in a receive command. See RTC CONTROL REGISTER for details.

The RTC can be read and reset by the host at any time. Since the RTC consists of 32 bits, at least 2 memory cycles are required to read all of its value. As a result, a carry- out from the lower word can occur between the read cycles. A mechanism is therefore provided to solve this potential difficulty.

If the host reads the RTC as two 16 bit words, \*LOCK should be initialized to 1 in the RTC CONTROL register. In this case, when the host reads the upper word, all 32 bits are latched into the host output register. The value in the output register remains unchanged until the host finishes reading the lower word of the RTC.

If the host reads the RTC in bytes, \*LOCK should be initialized to 0. In this case, when the host reads any of the bytes of the RTC, all 32 bits are latched into the host output register and its value remains unchanged until updating is re- enabled by reading the RTC CONTROL register. The RTC resolution can be programmed equal to 1, 2, 4, 8, 16, 32, or 64 microseconds.

4.2.10 RTC CONTROL REGISTER Address: 7 R/W BC/MT/RT The RTC CONTROL register controls the RTC as well as having other functions.

| 15                | 14            | 13         | 12          | 11          | 10          | 9           | 8           |

|-------------------|---------------|------------|-------------|-------------|-------------|-------------|-------------|

| RTC<br>RESET      | RESET<br>LAST | RES2       | SYNUPD      | *LOCK       | SYNRST      | RES1        | RES0        |

|                   |               |            |             |             |             |             |             |

| 7                 | 6             | 5          | 4           | 3           | 2           | 1           | 0           |

| <b>7</b><br>M1760 | 6<br>BUSY     | 5<br>RESET | 4<br>PRESET | 3<br>PRESET | 2<br>PRESET | 1<br>PRESET | 0<br>PRESET |

#### RTC RESET

When a "1" is written to RTC RESET, a reset pulse is issued to the RTC. The contents of the register are not affected by this operation and RTC RESET is always read by the host as "0".

Bits: 15

Bits: 14

Bits: 12

BC/MT/RT

BC/MT/RT

RT

RT

#### **RESET LAST**

When a "1" is written to RESET LAST, all the bits in the LAST STATUS REGISTER except the ADDRESS field and the BUSY bit are set to a "0". The contents of the register are not affected by this operation and RESET LAST is always read by the host as "0".

#### SYNUPD

1= Specifies that the lower 16 bits of the RTC will be updated whenever a valid mode command "Synchronize With Data" is received by the ET.

#### \*LOCK

- Bits: 11 BC/MT/RT 0 = Enables updating of the host output register after the RTC CONTROL register is read (this feature is needed to support byte wide read cycles).

- 1 = Enables updating of the host output register after the lower RTC word is read.

#### SYNRST

- Bits: 10

- 1= Specifies that the RTC shall be reset whenever a valid mode command "Synchronize Without Data" is received by the ET.

#### RES

#### Bits: 13, 9, 8 BC/ MT/ RT

This field defines the resolution of the RTC in microseconds as follows:

| RESOLUTION(us) | 13 | 9 | 8 |

|----------------|----|---|---|

| 1              | 0  | 0 | 0 |

| 2              | 0  | 0 | 1 |

| 4              | 0  | 1 | 0 |

| 8              | 0  | 1 | 1 |

| 16             | 1  | 0 | 0 |

| 32             | 1  | 0 | 1 |

| 64             | 1  | 1 | 0 |

| OFF/EXT        | 1  | 1 | 1 |

#### Note: Some NHi- ET device types have an external TIME TAG CLOCK input.

#### M1760

Bits: 7

RT

- 1= Specifies that the RT shall comply with MIL- STD- 1760A. This mode of operation has two consequences: first, the mode command "Synchronize With Data" updates the lower 16 bits of the RTC only if the least significant data bit is "0" and second, the IPO\_ DSC pin serves as a store disconnect signal rather than an interrupt priority output.

- 0= Specifies that the RT shall comply with MIL-STD-1553B.

# BUSY\_OPT Bits: 6 RT

- 0= MRST, Software Reset and MODE CODE\_ 08 RESET will set the BUSY bit in the LAST STATUS REGISTER and the BASIC STATUS REGISTER to a "1".

- 1= Only MRST will set the BUSY bit in the LAST STATUS REGISTER and the BASIC STATUS REGISTER to a "1".

RESET BUSYBits: 5RTWhen a "1" is written to RESET BUSY,<br/>a "0". The contents of the register are not affected by this operation and RESET BUSY is always<br/>read by the host as "0".REGISTER is set to<br/>a always<br/>read by the host as "0".

PRESETBits: (4: 0)RTThese bits provide a method to perform a double word( 32 bit) preset to the RTC. When this bitfield is set to any number from 1 to 30( bit 0 = LSB), the first two words of a receive messagewhose subaddress is equal to this value will be used to preset the internal RTC. The mostsignificant word is received first. If this field is equal to a "0" or "31", the RTC will not be preset.All bits in this register are cleared during initialization of the ET.

4.2.11FIFO READAddress: 8RBC/ MT/ RTThis address is used to read the contents of the interrupt FIFO. Reading this address pops theFIFO, updates the IVR and the AVR; then outputs the AVR(upper byte) and IVR(lower byte).

**4.2.12 FIFO RESET Address: 8 W BC/ MT/ RT** Writing any value to this address empties the FIFO.

**4.2.13** LAST COMMAND REGISTER Address: 11 R RT This register holds the last command word as defined by the MIL-BUS. The contents are not defined after initialization of the RT.

#### LAST STATUS REGISTER 4.2.14 Address: 12 R RT

This register holds the Status Word assosciated with the last message. After initialization of the RT, the BUSY bit= 1, the TADR field contains the hardwire address, and all other bits are set to 0. See RTC CONTROL REGISTER for special options.

#### 4.2.15 RESET REMOTE TERMINAL Address: 15 w BC/MT/RT

Writing a word to address 15 resets the RT and causes it to perform its initialization (see initialization section).

4.2.16 ENCODER STATUS Address: 18 R BC/RT This register contains flags indicating the status of the encoder. These flags are intended to facilitate transmission of messages in loop- back mode during self- test.

| 15      | 7      | 0          |

|---------|--------|------------|

| TXREQ_L | EOTX_L | FAILSAFE_L |

#### TXREQ L

Bits: 15 0= Indicates that the encoder is ready to accept the next word for transmission. This bit should equal "0" before loading the Encoder Data register with the next word. In order to transmit contiguous words, the next word should be loaded within 18 microseconds after \*TXREQ transitions to "0".

Bits: 7

Bits: 0

## EOTX L

0= Indicates that the encoder has completed transmission and that there are no pending requests.

#### FAILSAFE L

0= FAILSAFE TIME OUT has occurred. This bit will be set to a "1" when a new message is received or during a reset.

#### 4.2.17 CONDITION REGISTER Address: 19 R BC/MT/RT

This register contains information about the command being processed by the NHi- ET. and the operational condition.of the NHi-ET.

| 15 | 14    | 13    | 12    | 11  | 10  | 9      | 8      |

|----|-------|-------|-------|-----|-----|--------|--------|

| Х  | Х     | AXEN  | BXEN  | TFE | Х   | MDCD_L | Х      |

| 7  | 6     | 5     | 4     | 3   | 2   | 1      | 0      |

| Х  | CUFRM | EOF B | EOF A | CUR | CUR | BUSJAM | BUSJAM |

|    | BUSY  |       |       | FRM | BUS | В      | А      |

#### AXEN

# Bits: 13

BC/RT

BC/RT

1= Indicates that transmitter A is enabled. This bit is set to a "1": at POWER UP, if the NHi- ET is RESET, after receipt of a "Reset" mode code, or after receipt of an OVERRIDE TRANSMITTER SHUTDOWN mode code on the B bus.

0= Indicates that transmitter A is inhibited. This bit is set to a "0" after receipt of TRANSMITTER SHUTDOWN mode code on the B bus.

#### BXEN

#### Bits: 12

1= Indicates that transmitter B is enabled. This bit is set to a "1": at POWER UP, if the NHi- ET is RESET, after receipt of a "Reset" mode code, or after receipt of an OVERRIDE TRANSMITTER SHUTDOWN mode code on the A bus.

0= Indicates that transmitter B is inhibited. This bit is set to a "0" after receipt of a TRANSMITTER SHUTDOWN mode code on the A bus.

BC/RT

RT

RT

| <ul> <li>TFE</li> <li>1= Indicates that the TERMINAL FLAG bit in the done in the BASIC STATUS REGISTER or I bit is set to a "1" at POWER UP, if the NHi-I CODE, or after receipt of an OVERRIDE INH</li> <li>0= Indicates that the TERMINAL FLAG bit in the set to a "0" after receipt of an INHIBIT TER</li> </ul> | by the TERMINAL FLAG<br>ET is RESET, after recei<br>HIBIT TERMINAL FLAG<br>e status word CANNOT b | pin on the NHi-ET. This<br>pt of a RESET MODE<br>mode code.<br>be set to a "1". This bit is |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| <ul> <li>MDCD_L</li> <li>1= Indicates that the last command received was</li> <li>0= This bit is set to a "0" when a mode code is respectively.</li> </ul>                                                                                                                                                          |                                                                                                   | RT                                                                                          |

| CUFRM BUSY<br>1= The current frame of data block is busy. It i<br>data.                                                                                                                                                                                                                                             | Bits: 6<br>s active and could be re                                                               | BC/ MT<br>ceiving or transmitting                                                           |

| <b>EOF B</b><br>1= Frame "B" or data block "B" has finished proc                                                                                                                                                                                                                                                    | Bits: 5<br>cessing data and in now                                                                | BC/ MT<br>inactive.                                                                         |

| <b>EOF A</b><br>1= Frame "A" or data block "A" has finished proc                                                                                                                                                                                                                                                    | Bits: 4<br>cessing data and in now                                                                | BC/ MT<br>inactive.                                                                         |

| <b>CUR FRM</b><br>0= Frame "A" or block "A" is the current active fr<br>1= Frame "B" or block "B" is the current active fr                                                                                                                                                                                          |                                                                                                   | BC/ MT                                                                                      |

| CUR_BUS<br>0= Bus "A" is the current bus.<br>1= Bus "B". is the current bus.                                                                                                                                                                                                                                        | Bits: 2                                                                                           | BC/ MT                                                                                      |

| BUSJAM B<br>1 = Bus "B" has been jammed by continuous tra<br>indicated when an RT transmits more extra<br>REGISTER 3 (See CONFIG REG 3 for deta                                                                                                                                                                     | a words then the value so                                                                         |                                                                                             |

| <b>BUSJAM A</b><br>1 = Bus "A" has been jammed by continuous tra<br>indicated when an RT transmits more extra<br>REGISTER 3 (See CONFIG REG 3 for deta                                                                                                                                                              | words then the value se                                                                           |                                                                                             |

| <b>4.2.18</b> ENCODER DATA REGISTER<br>This register contains data to be transmitted whe                                                                                                                                                                                                                            | Address: 23 R/A<br>n performing a loop bac                                                        |                                                                                             |

| <b>4.2.19 ENCODER DATA TRANSMIT RQST</b><br>Writing (any value) to this address causes the co<br>sent as a data word. This instruction together with<br>REQUEST can be used to loop- back entire me<br>can be read from the data table associated with                                                              | ntents of the ENCODER<br>th the ENCODER COMI<br>essages for self- test pur                        | MAND TRANSMIT                                                                               |

| <b>4.2.20 ENCODER COMMAND TRANSMIT</b><br>Writing (any value) to this address causes the co<br>sent as a command word. This instruction is use<br>in loop- back mode. The command can then be                                                                                                                       | ntents of the ENCODER                                                                             | R DATA REGISTER to be ds to the decoder while                                               |

#### RT 4.2.21 EXTERNAL TERMINAL ADDRESS REGISTER Address: 30 R

This register contains information about the hardwire terminal address.

| 7      | 6      | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|--------|-------|-------|-------|-------|-------|-------|

| INVALP | DISCON | TADRP | TADR4 | TADR3 | TADR2 | TADR1 | TADR0 |

The terminal address may be hardwired using I/ O DAT( 5: 0). External pull- down resistors of 4.7K are used to set a low, 64K internal pull- ups set a high. I/ O DAT5 is wired for odd parity in the address. The hardwire terminal address and its parity can be obtained by reading I/ O address 30. This address is unique since a read operation activates both the I/ O bus command strobe and the I/ O bus read signal (i. e., CMDS= 1 and \*I/ O RD= 0). As a result, a buffer containing the terminal address can be selected without decoding address lines. If an external buffer is not desired, pull- up/ down resistors on the I/ O data bus can be used instead (see BASIC STATUS register for details). The protocol chip also calculates the terminal address's parity and compares it to the value obtained from the I/ O bus.

#### **INVALP**

#### Bits: 7

1= Specifies that the terminal address which was read automatically by the protocol chip following reset (from I/ O address 30) had invalid parity.

#### DISCON

#### Bits: 6

- 0= Specifies that the store is disconnected because a terminal address of 31 was detected on the I/ O bus for at least 800 nanoseconds.

- 1= Specifies that the store is connected.

This bit indicates the "disconnected store" condition defined by MIL- STD- 1760A, provided that the store contains the pull- down resistors used for defining the terminal address (see BASIC STATUS register for details). After the store is disconnected, the standby state of all I/ O lines will be high and will therefore define an illegal terminal address of 31.

#### TADRP

Bits: 5

TADRP equals the value of the terminal address parity read from I/ O address 30.

#### TADR

## Bits: (4:0)

TADR equals the value of the terminal address read from I/ O address 30.

#### COMMAND OUTPUT PINS 4.2.22

Writing a word to the COMMAND OUTPUT PINS (address 30 in the I/ O space) can be used to simulate the option which outputs 5 bits onto the I/ O bus following valid command reception (see CMDO bit in the CONTROL register for details). This address is unique since a write operation activates both the I/ O bus, COMMAND STROBE and the I/ O bus write signal (i. e., CMDS= 1 and \*I/ O WR= 0). As a result, the bits can be latched without decoding address lines.

#### 4.2.23 I/ O TAG WORD REGISTER Address: 31

When a data table is mapped to address 32 in the I/ O space, its tag word is contained in this register. This tag word can be used, for example, to specify an output pulse whenever the data table is accessed. All other I/ O space data tables are without internal tag words and have no pulses associated with them.

R/W RT

w

RT

Address: 30

#### 4.2.24 **CONFIGURATION REGISTER 1** R/W BC/MT/RT Address: 9

This register is used to configure the functionality of the part.