Package

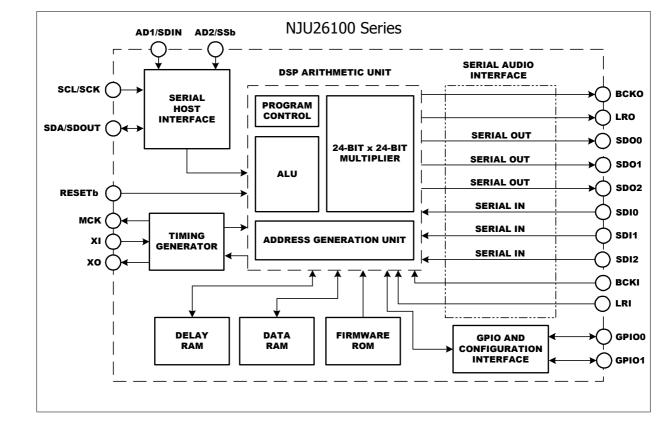

# NJU26100 Series Hardware Specification

This document describes the NJU26100 Series common hardware specifications. This document is applied to the NJU26101 up to the NJU26199. The individual function is described in the each data sheet. Please refer to the each data sheet to find the detail functions. The firmware commands are described in the each firmware document.

## Hardware Specification

- 24bit Fixed-point Digital Signal Processing

- Maximum System Clock Frequency : 38MHz

: 3 Input ports / 3 Output ports

- Digital Audio Interface

Master / Slave Mode

- Master Mode MCK

:1/2 fclk, 1/3 fclk ex. MCK = 384Fs(1/2) or MCK = 256Fs(1/3) at fclk=768Fs

- Two kinds of micro computer interface

I<sup>2</sup>C bus (standard-mode/100kbps)

Serial interface (4 lines: clock, enable, input data, output data)

- Power SupplyPackage

: 2.5V ( 3.3V Input tolerant ) : QFP32-R1

Series

NJU26100

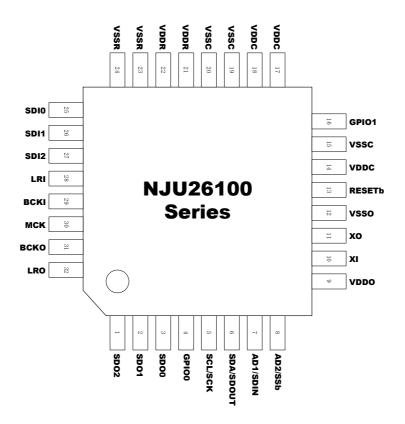

# Pin Configuration

W

# Pin Description

#### **Pin Description**

|     | escription |     |                                          |     |        |     |                         |

|-----|------------|-----|------------------------------------------|-----|--------|-----|-------------------------|

| No. | Symbol     | I/O | Description                              | No. | Symbol | I/O | Description             |

| 1   | SDO2       | 0   | Audio Data Output CH2                    | 17  | VDDC   |     | Core Power Supply +2.5V |

| 2   | SDO1       | 0   | Audio Data Output CH1                    | 18  | VDDC   |     | Core Power Supply +2.5V |

| 3   | SDO0       | 0   | Audio Data Output CH0                    | 19  | VSSC   |     | Core GND                |

| 4   | GPIO0      | I/O | General Purpose IO                       | 20  | VSSC   |     | Core GND                |

| 5   | SCL/SCK    |     | I <sup>2</sup> C Clock / Serial Clock    | 21  | VDDR   | -   | I/O Power Supply +2.5V  |

| 6   | SDA/SDOUT  | I/O | I <sup>2</sup> C I/O / Serial Output     | 22  | VDDR   | -   | I/O Power Supply +2.5V  |

| 7   | AD1/SDIN   |     | I <sup>2</sup> C Address / Serial Input  | 23  | VSSR   |     | I/O GND                 |

| 8   | AD2/SSb    | 1   | I <sup>2</sup> C Address / Serial Enable | 24  | VSSR   |     | I/O GND                 |

| 9   | VDDO       |     | OSC Power Supply +2.5V                   | 25  | SDI0   | Ι   | Audio Data Input CH0    |

| 10  | XI         | 1   | X'tal Clock Input                        | 26  | SDI1   | Ι   | Audio Data Input CH1    |

| 11  | XO         | 0   | OSC Output                               | 27  | SDI2   | Ι   | Audio Data Input CH2    |

| 12  | VSSO       |     | OSC GND                                  | 28  | LRI    | Ι   | LR Clock Input          |

| 13  | RESETb     | 1   | RESET (active Low)                       | 29  | BCKI   | Ι   | Bit Clock Input         |

| 14  | VDDC       |     | Core Power Supply +2.5V                  | 30  | MCK    | 0   | Master Clock Output     |

| 15  | VSSC       |     | Core GND                                 | 31  | BCKO   | 0   | Bit Clock Output        |

| 16  | GPIO1      | I/O | General Purpose IO                       | 32  | LRO    | 0   | LR Clock Output         |

\*1 I : Input, O : Output, I/O : Bi-directional

\*2 SDI0, SDI1, SDI2, SDO0, SDO1, SDO2, GPIO0, GPIO1 are different by any function. Refer to each datasheet.

New Japan Radio Co., Ltd.

# 1. Electric Characteristics

WW

### 1.1 Absolute Maximum Ratings

### Table1-1 Absolute Maximum Ratings (V<sub>sso</sub>=V<sub>ssc</sub>=V<sub>ssc</sub>=0V, Ta=25°C)

| Parameter           | Symbol              | Rating                  | Units |

|---------------------|---------------------|-------------------------|-------|

| Supply Voltage      | V <sub>DD</sub>     | 0 to 3.05               | V     |

| XI Input Voltage    | V <sub>x(OSC)</sub> | -0.3 to $V_{\text{DD}}$ | V     |

| Input Pin Voltage   | V <sub>x(IN)</sub>  | -0.3 to 3.6             | V     |

| Power Dissipation   | PD                  | 0.3                     | W     |

| Storage Temperature | T <sub>stg</sub>    | -40 to +125             | °C    |

\*<sup>1</sup> They apply SCL/SCK, AD1/SDIN, AD2/SSb, RESETb, SDI0, SDI1, SDI2, LRI, and BCKI pin. It applies to GPIO0 (SEL1) pin of NJU26100 series except NJU26150. However, it applies to SDA/SDOUT pin at the time of I<sup>2</sup>C mode operation.

## 1.2 Electric Characteristics

#### Table1-2 Electric Characteristics (V<sub>DDO</sub>=V<sub>DDC</sub>=V<sub>DDR</sub>=2.5V, V<sub>SSO</sub>=V<sub>SSC</sub>=V<sub>SSR</sub>=0V, Ta=25°C)

| Parameter                            | Symbol               | Test Condition                                                               | Min.                                         | Тур. | Max.            | Units |

|--------------------------------------|----------------------|------------------------------------------------------------------------------|----------------------------------------------|------|-----------------|-------|

| Operating V <sub>DD</sub> Voltage    | V <sub>DD</sub>      | $V_{DDO}, V_{DDC}, V_{DDR}$ pin                                              | 2.25                                         | 2.5  | 2.75            | V     |

| Operating Current                    | I <sub>DD</sub>      | f <sub>OSC</sub> =36.864MHz                                                  | -                                            | 40   | -               | mA    |

| Operating Temperature                | T <sub>OPR</sub>     |                                                                              | -40                                          | 25   | 85              | °C    |

| Recommended Operating<br>Temperature | T <sub>OPRR</sub>    | V <sub>DDO</sub> =V <sub>DDC</sub> =V <sub>DDR</sub> =2.5V                   | -10                                          | 25   | 70              | °C    |

| High Level Input<br>Voltage (XI)     | V <sub>IH(OSC)</sub> | XI pin                                                                       | 2.0                                          | -    | V <sub>DD</sub> | V     |

| High Level Input Voltage             | V <sub>IH</sub>      |                                                                              | 2.0                                          | I    | 3.3             | V     |

| Low Level Input Voltage              | VL                   | V <sub>SS</sub> =V <sub>SSO</sub> =V <sub>SSC</sub> =V <sub>SSR</sub>        | V <sub>SS</sub>                              | -    | 0.5             | V     |

| High Level Input Current             | I <sub>H</sub>       | V <sub>IN</sub> =3.3V<br>expect for GPIO pin                                 | -10                                          | -    | +10             | μA    |

| High Level Input Current             | I <sub>IH(pd)</sub>  | V <sub>IN</sub> =3.3V<br>GPIO pin Only                                       | 100                                          | -    | 300             | μA    |

| Low Level Input Current              | IL                   | V <sub>IN</sub> =V <sub>SSO</sub> =V <sub>SSC</sub> =V <sub>SSR</sub>        | -10                                          | -    | +10             | μA    |

| High Level Output Voltage            | V <sub>OH</sub>      | I <sub>OH</sub> =-2mA<br>I <sub>OH</sub> =-100µA                             | V <sub>DD</sub> -0.4<br>V <sub>DD</sub> -0.1 | -    | -               | V     |

| Low Level Output Voltage             | V <sub>OL</sub>      | I <sub>o∟</sub> =2mA                                                         | -                                            | -    | 0.4             | V     |

| Input Capacitance                    | CIN                  |                                                                              | -                                            | 5    | -               | pF    |

| Input Rise/Fall transition Time      | t, / t,              | except for SCL/SCK,<br>SDA/SDOUT,<br>AD1/SDIN, AD2/SS b<br>pin* <sup>1</sup> | -                                            | -    | 100             | ns    |

| Clock Frequency                      | f <sub>OSC</sub>     | XI pin                                                                       | -                                            | -    | 38.0            | MHz   |

| Ext.System Clock Duty Cycle          | r <sub>EC</sub>      | XI pin                                                                       | 47.5                                         | 50   | 52.5            | %     |

\*1 The tr / tf of these pins are specified separately.

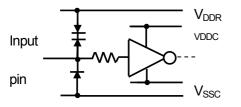

\*<sup>2</sup> All input / input-and-output pins serve as the Schmidt trigger input except for XI pin.

Input pin (GPIO0, SCL/SCK, SDA/SDOUT, AD1/SDIN, AD2/SSb, RESETb, GPIO1, SDI0, SDI1, SDI2, LRI, BCKI pin)

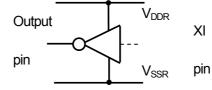

(XI, XO)

Output pin (SDO0, SDO1, SDO2, GPIO0, \*<sup>3</sup>SDA/SDOUT, GPIO1, MCK, BCKO, LRO pin)

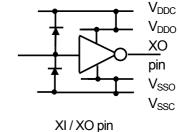

## Fig.1-1 I/O Equivalent Circuits

New Japan Radio Co., Ltd.

$*^3$  SDA becomes Open-Drain at the time of the output of I<sup>2</sup>C.

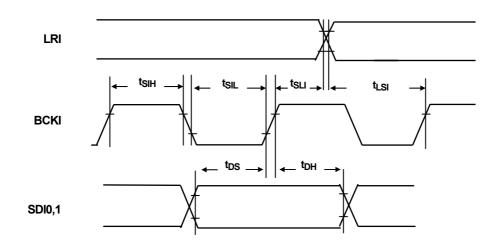

# 2. Clock and Reset

The NJU26100 Series XI pin requires the system clock that should be related to the sample frequency Fs. The XI/XO pins can generate the system clock by connecting the crystal oscillator or the ceramic resonator.

When the external oscillator is connected to XI/XO pins, check the voltage level of the pins. Because the maximum input voltage level of XI pin is deferent from the other input or bi-directional pins. The maximum voltage-level of XI pin equals to  $V_{DD}$ .

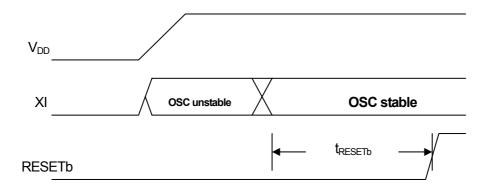

To initialize the NJU26100 Series, RESETb pin should be set Low level during some period. After some period of Low level, RESETb pin should be High level. This procedure starts the initialization of the NJU26100 Series.

To select I<sup>2</sup>C bus or 4-Wire serial bus, some level should be supplied to GPIO0 pin (SEL1 pin). When GPIO0 pin (SEL1 pin)="Low", I<sup>2</sup>C bus is selected. When GPIO0 pin (SEL1 pin)="High", 4-Wire serial bus is selected. The level of GPIO0 pin (SEL1 pin) is checked by the NJU26100 Series in 1 m sec after RESETb pin level goes to "High". After the power supply and the oscillation of the NJU26100 Series becomes stable, RESETb pin should be kept Low-level more than  $t_{RESETb}$  period.

## Fig. 2-1 Reset Timing

| Tahl  | <b>2_1</b> | Reset | Timo |

|-------|------------|-------|------|

| Idule | 2 Z- I     | Resei | Time |

| Symbol              | Time |

|---------------------|------|

| t <sub>RESETb</sub> | ≥1µs |

Notice :

Please consult with manufacture of crystal oscillator / ceramic resonator enough in use of these parts. NJRC would not take the responsibility on the external parts of clock generating.

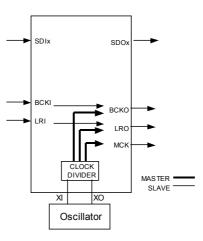

# 3. Audio Clock

Audio data samples must be transferred in synchronism between all components of the digital audio system. That is, for each audio sample originated by an audio source there must be one and only one audio sample processed by the NJU26100 Series and delivered to the D/A converters. To accomplish this, one device in the system is selected to generate the audio sample rate; the remaining devices are designated to follow this sample rate. The device that generates the audio sample rate is called the MASTER device; all devices following this sample rate are called SLAVE(s).

LR, BCK and MCK should be synchronized. This is described in next section. When the NJU26100 Series is in MASTER mode, the NJU26100 Series system clock should be 768 multiples of the sampling frequency (Table3-1). When the NJU26100 Series is in SLAVE mode, NJU26100 Series system clock should be from 768 multiples of the sampling frequency up to the maximum operating frequency.

#### 3.1 System Clock

Three types of clock signals are included in the serial audio interface. Two of the clock signals LR (LRI and LRO) and BCK (BCKI and BCKO) establish data transfer on the serial data lines. The third clock, MCK, is not associated with serial data transfer but is required by delta-sigma A/D and D/A converters.

The frequency of the LR clock is, by definition, equal to the digital audio sample rate, Fs. BCK and MCK operate at multiples of the LR clock rate. Therefore the signals LR, BCK and MCK must be locked, that is, they must be generated or derived from a single frequency reference. In SLAVE mode, the NJU26100 Series dose not generate MCK clock.

| Clock Signal | Multiple Frequency | 32kHz     | 44.1kHz    | 48kHz     |

|--------------|--------------------|-----------|------------|-----------|

| LR           | 1Fs                | 32kHz     | 44.1kHz    | 48kHz     |

| BCK(32Fs)    | 32Fs               | 1.024MHz  | 1.4112MHz  | 1.536MHz  |

| BCK(64Fs)    | 64Fs               | 2.048MHz  | 2.822MHz   | 3.072MHz  |

| MCK(256Fs)   | 256Fs              | 8.192MHz  | 11.289MHz  | 12.288MHz |

| MCK(384Fs)   | 384Fs              | 12.288MHz | 16.934MHz  | 18.432MHz |

| XI           | 768Fs              | 24.576MHz | 33.8688MHz | 36.864MHz |

#### Table 3-1 Sampling Frequency and BCK, MCK, XI

www.DataSheet42.26m

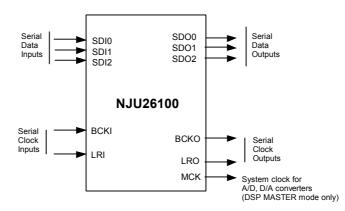

# 4. Audio Interface

WW

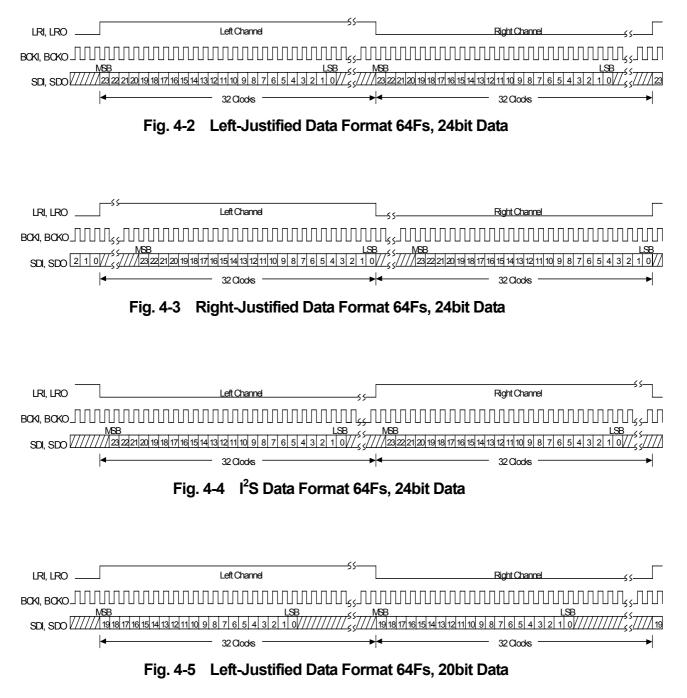

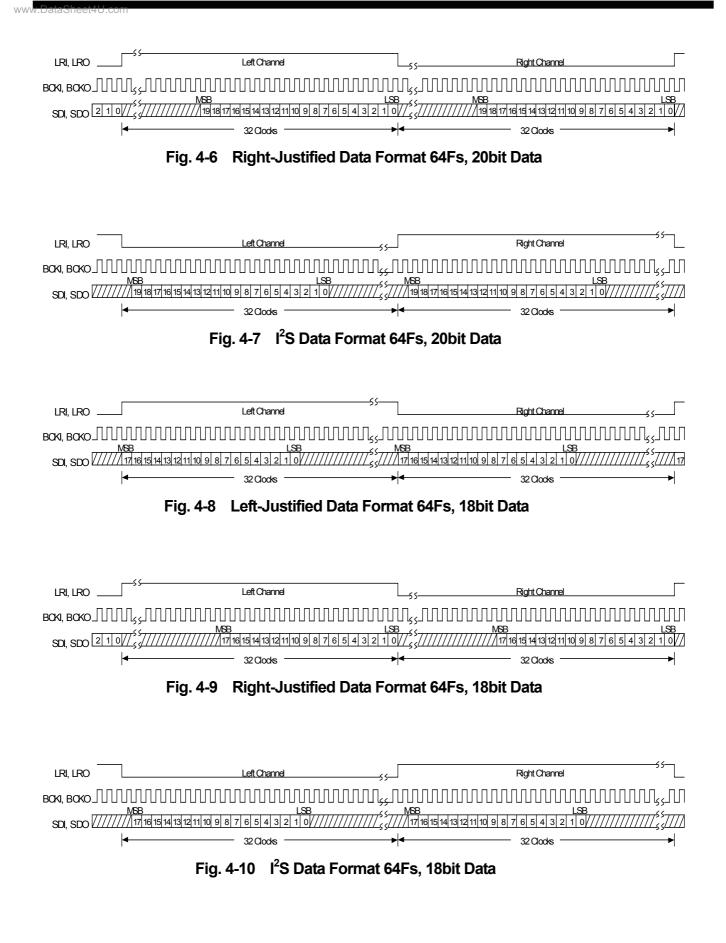

The serial audio interface carries audio data to and from the NJU26100 Series. Industry standard serial data formats of I<sup>2</sup>S, MSB-first left-justified or MSB-first right-justified are supported. These serial audio formats define a pair of digital audio signals (stereo audio) on each data line. Two clock lines, BCK (bit clock) and LR (left/right word clock) establish timing for serial data transfers.

The NJU26100 Series serial audio interface includes three data input lines, SDI0, SDI1 and SDI2, and three data output lines, SDO0, SDO1 and SDO2, as shown in the figure below. The input serial data is selected by the firmaware command. The number of these serial audio interfaces depends on the DSP function. Check the each data sheet.

The NJU26100 Series has a pair of left/right clock lines (LRI and LRO) and a pair of bit clock lines (BCKI and BCKO). Clock inputs BCKI and LRI are used to accept timing signals from an external device when the NJU26100 Series is operating in SLAVE clock mode.

The BCKO, LRO and MCK, system clock output, are provided for delta-sigma A/D and D/A converters when the NJU26100 Series operates in MASTER mode. In SLAVE mode, the output of BCKO and LRO are the buffered output of BCKI and LRI. The output of MCK is fixed to Low level in SLAVE mode.

Fig. 4-1 Serial Audio Interface

#### 4.1 Audio Data Format

The NJU26100 Series can exchange data using any of three industry-standard digital audio data formats: I<sup>2</sup>S, MSB-first Left-justified, or MSB-first Right-justified.

The three serial formats differ primarily in the placement of the audio data word relative to the LR clock. Left-justified format places the most-significant data bit (MSB) as the first bit after an LR transition. I<sup>2</sup>S format places the most-significant data bit (MSB) as the second bit after an LR transition (one bit delay relative to left-justified format). Right-justified format places the least-significant data bit (LSB) as the last bit before an LR transition.

Clock LR (LRI, LRO) marks data word boundaries and clock BCK (BCKI, BCKO) clocks the transfer of serial data bits. One period of LR defines a complete stereo audio sample and thus the rate of LR equals the audio sample rate (Fs). All formats transmit the stereo sample left channel first. Note that polarity of LR is opposite in I<sup>2</sup>S format (LR:LOW = Left channel data) compared to Left-Justified or Right-Justified formats.

# NJU26100 Series

The number of BCK clock must follow the serial data format. If the BCK clock is not enough, the right sound are not produced. Set serial data format for the adequate mode that A/Ds, D/As or Codecs reqire.

The NJU26100 Series supports serial data format which includes 32(32Fs) or 64(64Fs) BCK clocks. This serial data format is applied to both MASTER and SLAVE mode.

## 4.2 Serial Audio Data Transmitting Diagram

\* The 24bit data is always outputted to a SDO0 pin in the format of figure 4-5 to figure 4-10.

# NJU26100 Series

Fig. 4-13 I<sup>2</sup>S Data Format 32Fs, 16bit Data

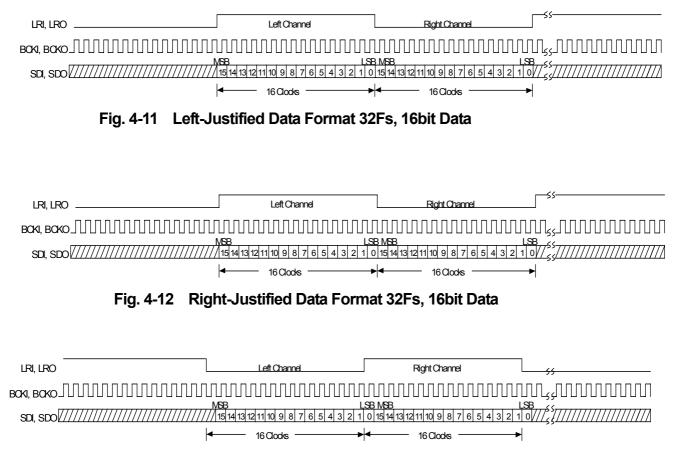

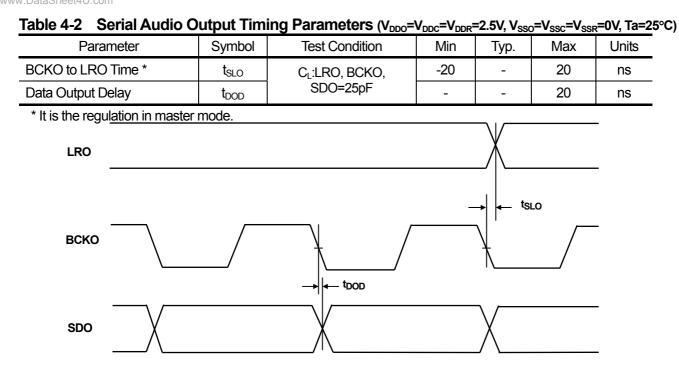

## 4.3 Serial Audio Timing

ww

|                     |                   |                | DC DDK - |      | -33C -33N |       |

|---------------------|-------------------|----------------|----------|------|-----------|-------|

| Parameter           | Symbol            | Test Condition | Min      | Тур. | Max       | Units |

| BCKI Frequency **   | f <sub>BCKI</sub> |                | 0.9      | -    | 4.0       | MHz   |

| BCKI Period **      |                   |                |          |      |           |       |

| Low Pulse Width     | t <sub>SIL</sub>  |                | 85       | -    | -         | ns    |

| High Pulse Width    | t <sub>SIH</sub>  |                | 85       |      |           |       |

| BCKI to LRI Time ** | T <sub>SLI</sub>  |                | 40       | -    | -         | ns    |

| LRI to BCKI Time ** | t <sub>LSI</sub>  |                | 40       | -    | -         | ns    |

| Data Setup Time *   | t <sub>DS</sub>   |                | 40       | -    | -         | ns    |

| Data Hold Time *    | t <sub>DH</sub>   |                | 40       | -    | -         | ns    |

#### Table 4-1 Serial Audio Input Timing Parameters (V<sub>DDO</sub>=V<sub>DDC</sub>=V<sub>DDR</sub>=2.5V, V<sub>SSO</sub>=V<sub>SSC</sub>=V<sub>SSR</sub>=0V, Ta=25°C)

\* It is the regulation to BCKI in slave mode and to BCKO in master mode.

\*\* It is the regulation in slave mode.

Fig. 4-14 Serial Audio Input Timing

Fig. 4-15 Serial Audio Output Timing

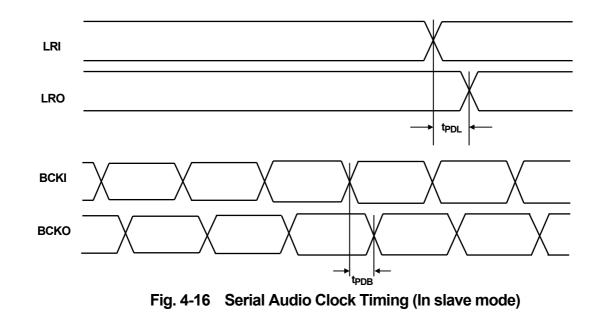

## Table 4-3 Serial Audio Clock Timing Parameters (In slave mode)

| $(V_{DDO}=V_{DDC}=V_{DDR}=2.5V, V_{SSO}=V_{SSC}=V_{SSR}=0V, Ta=25V$ | °C) |

|---------------------------------------------------------------------|-----|

|---------------------------------------------------------------------|-----|

| Parameter                          | Symbol           | Test Condition            | Min | Тур. | Max | Units |

|------------------------------------|------------------|---------------------------|-----|------|-----|-------|

| Clock Output Delay<br>(LRI> LRO)   | t <sub>PDL</sub> | C <sub>L</sub> :LRO,BCKO, | -   | -    | 20  | ns    |

| Clock Output Delay<br>(BCKI> BCKO) | t <sub>PDB</sub> | SDO=25pF                  | -   | -    | 20  | ns    |

www.Da**VaSAQ**942.240m

# 5. Host Interface

The NJU26100 Series can be controlled via Serial Host Interface (SHI) using either of two serial bus formats: 4-Wire serial bus or I<sup>2</sup>C bus. Data transfers are in 8 bit packets (1 byte) when using either format. The SHI operates only in a SLAVE fashion. A host controller connected to the interface always drives the clock (SCL / SCK) line and initiates data transfers, regardless of the chosen communication protocol.

| Pin No. | Symbol<br>(I <sup>2</sup> C / Serial) | 4-Wire Serial bus Format | I <sup>2</sup> C bus Format       |

|---------|---------------------------------------|--------------------------|-----------------------------------|

| 5       | SCL/SCK                               | Serial Clock             | Serial Clock                      |

| 6       | SDA/SDOUT                             | Serial Data Output       | Serial Data<br>(Bi-directional)   |

| 7       | AD1/SDIN                              | Serial Data Input        | I <sup>2</sup> C bus address Bit1 |

| 8       | AD2/SSb                               | SLAVE Select             | I <sup>2</sup> C bus address Bit2 |

| Table 5-1 Serial H | st Interface Pin Description |

|--------------------|------------------------------|

|--------------------|------------------------------|

Note : SDA /SDOUT pin is a bi-directional open drain.

SDA /SDOUT output is normal CMOS output in case of 4-Wire Serial bus mode and SSb="Low". SDA /SDOUT output is Hi-Z state in case of 4-Wire Serial bus mode and SSb="High". This pin requires a 4.7k pull-up resister in both 4-Wire serial and I<sup>2</sup>C bus mode.

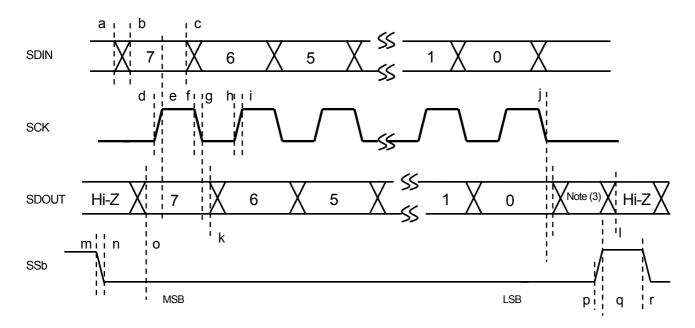

### 5.1 4-Wire Serial Interface

The serial host interface can be configured for 4-Wire Serial bus communication by setting GPIO0 pin (\*SEL1 pin)="High" during the Reset initialization sequence. SHI bus communication is full-duplex; a write byte is shifted into the SDIN pin at the same time that a read byte is shifted out of the SDOUT pin. Data transfers are MSB first and are enabled by setting the Slave Select pin Low (SSb = 0). Data is clocked into SDIN on rising transitions of SCK. Data is latched at SDOUT on falling transitions of SCK except for the first byte (MSB) which is latched on the falling transitions of SSb. SDOUT is Hi-Z in case of SSb = "High". SDOUT is CMOS output in case of SSb = "Low". SDOUT needs a pull-up resistor when SDOUT is Hi-Z.

\* It excepts NJU26150. Refer to each data sheet.

| Table 5-2 4-Wire Serial Interface | Timing Para        | ameters (V <sub>DDO</sub> =V <sub>I</sub> | DDC=VDDR=2 | 2.5V, V <sub>SSO</sub> = | =V <sub>SSC</sub> =V <sub>SS</sub> | <sub>R</sub> =0V, Ta=25 |

|-----------------------------------|--------------------|-------------------------------------------|------------|--------------------------|------------------------------------|-------------------------|

| Parameter                         | Symbol             | Timelines                                 | Min.       | Тур.                     | Max.                               | Units                   |

| Input Data Rising Time            | t <sub>MSDr</sub>  | a-b                                       | -          | -                        | 100                                | ns                      |

| Input Data Falling Time           | t <sub>MSDf</sub>  | a-b                                       | -          | -                        | 100                                | ns                      |

| Serial Clock Rising Time          | t <sub>MSCr</sub>  | d-e                                       | -          | -                        | 100                                | ns                      |

| Serial Clock Falling Time         | t <sub>MSCf</sub>  | f-g                                       | -          | -                        | 100                                | ns                      |

| Serial Strobe Rising Time         | t <sub>MSSr</sub>  | p-q                                       | -          | -                        | 100                                | ns                      |

| Serial Strobe Falling Time        | t <sub>MSSf</sub>  | m-n                                       | -          | -                        | 100                                | ns                      |

| Serial Clock High Duration        | t <sub>MSCa</sub>  | e-f                                       | 50         | -                        | -                                  | ns                      |

| Serial Clock Low Duration         | t <sub>MSCn</sub>  | g-h                                       | 50         | -                        | -                                  | ns                      |

| Serial Clock Period               | t <sub>MSCc</sub>  | e-i                                       | 250        |                          | -                                  | ns                      |

| Serial Strobe Setup Time          | t <sub>MSSs</sub>  | n-e                                       | 100        |                          | -                                  | ns                      |

| Serial Strobe Hold Time           | t <sub>MSSh</sub>  | j-q                                       | 30         |                          | -                                  | ns                      |

| Serial Strobe Low Duration        | t <sub>MSSa</sub>  | n-p                                       | -          | 1.0                      | -                                  | μS                      |

| Serial Strobe High Duration       | t <sub>MSSn</sub>  | q-r                                       | 40         |                          | -                                  | ns                      |

| Input Data Setup Time             | t <sub>MSDis</sub> | b-e                                       | 20         |                          | -                                  | ns                      |

| Input Data Hold Time              | t <sub>MSDih</sub> | e-c                                       | 20         |                          | -                                  | ns                      |

| Output Data Delay                 | ture               | n-o,CL=25pF                               |            | _                        | 50                                 | ns                      |

| (From SSb)                        | t <sub>MSDos</sub> | 11-0,0L=20pi                              | -          | -                        | 50                                 | 115                     |

| Output Data Delay                 | t <sub>MSDo</sub>  | g-k(data-6),                              | _          | _                        | 50                                 | ns                      |

| (From SCK)                        | 401500             | CL=25pF                                   |            |                          |                                    | 115                     |

| Output Data Hold Time             | t <sub>MSDoh</sub> | g-k(data-7)                               | 0          | -                        | -                                  | ns                      |

| Output Data Turn off Time (Hi-Z)  | t <sub>MSDov</sub> | q-l                                       | -          | -                        | 40                                 | ns                      |

#### Table 5-2 4-Wire Serial Interface Timing Parameters (VDDO=VDDC=VDDR=2.5V, VSDO=VSC=VSSC=VSSC=0V, Ta=25°C)

## Fig. 5-1 4-Wire Serial Interface Timing

- Note: \*1 When the data-clock is less than 8 clocks, the input data is shifted to LSB side and is sent to the DSP core at the transition of SSb="High".

- \*2 When the data-clock is more than 8 clocks, the last 8 bit data becomes valid.

- \*3 After sending LSB data, SDOUT transmits the MSB data which is received via SDIN until SSb becomes "High".

- \*4 SDOUT is Hi-Z in case of SSb = "High". SDOUT is CMOS output in case of SSb = "Low".

New Japan Radio Co., Ltd.

SDOUT needs a pull-up resistor to prevent SDOUT from becoming floating level.

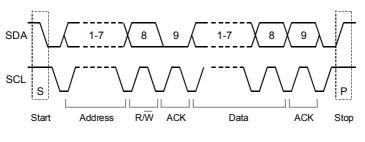

## 5.2 I<sup>2</sup>C Bus

When the NJU26100 Series is configured for I<sup>2</sup>C bus communication in GPIO0 pin (\*SEL1 pin)="Low", the serial host interface transfers data to the SDA pin and clocks data to the SCL pin. SDA is an open drain pin requiring an external 4.7k pull-up resistor. AD1 and AD2 pins are used to configure the seven-bit SLAVE address of the serial host interface. This offers additional flexibility to a system design by four different SLAVE addresses of the NJU26100 Series. An address can be arbitrarily set up by the AD1, 2 pins. The I<sup>2</sup>C address of AD1, 2 is decided by connection of AD1, 2 pins. The I<sup>2</sup>C address should be the same level of AD1, 2 pins. The real I<sup>2</sup>C address is described in the each data sheet. Refer to the each data sheet.

\* It excepts NJU26150. Refer to each data sheet.

| Table 5-3         I <sup>+</sup> C Bus SLAVE Address |      |      |      |      |       |                   |      |  |  |

|------------------------------------------------------|------|------|------|------|-------|-------------------|------|--|--|

| bit7                                                 | bit6 | bit5 | bit4 | bit3 | bit2  | bit1              | bit0 |  |  |

| 0                                                    | 0    | 1    | 1    | 1    | AD2*1 | AD1* <sup>1</sup> | R/W  |  |  |

2

\*1 The SLAVE address bit is 0 when ADx-pin is low level. The SLAVE address bit is 1 when ADx-pin is high level.

The figure on the following page shows the basic timing relationships for transfers. A transfer is initiated with a START condition, followed by the SLAVE address byte. The SLAVE address consists of the seven-bit SLAVE address followed by a read/write (R/W) bit. When an address with an effective serial host interface is detected, the acknowledgement bit which sets a SDA line to Low in the ninth bit clock cycle is returned.

The R/W bit in the SLAVE address byte sets the direction of data transmission until a STOP condition terminates the transfer. R/W = 0 indicates the host will send to the NJU26100 Series while R/W = 1 indicates the host will receive data from the NJU26100 Series.

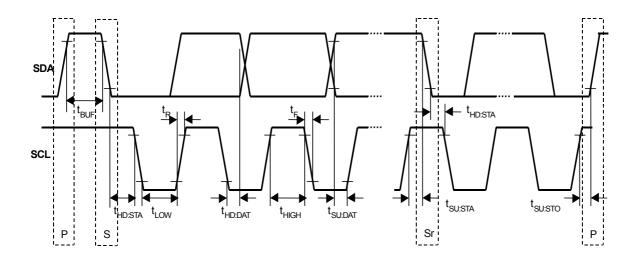

Fig. 5-2 I<sup>2</sup>C Bus Format

In case of the NJU26100 Series, only single-byte transmission is available. The serial host interface supports "Standard-Mode (100kbps)" I<sup>2</sup>C bus data transfer.

| Table 5-4 I <sup>2</sup> C Bus Interface Timing Parameters (V <sub>DDO</sub> =V <sub>DDC</sub> =V <sub>DDR</sub> =2.5V, V <sub>SSO</sub> =V <sub>SSC</sub> =V <sub>SSR</sub> =0V, Ta=25°C) |                     |               |      |        |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------|------|--------|--|--|--|--|--|--|

| Parameter                                                                                                                                                                                  | Symbol              | Standard Mode |      | Units  |  |  |  |  |  |  |

| Falditielei                                                                                                                                                                                | Symbol              | Min           | Max  | UTIIIS |  |  |  |  |  |  |

| SCL Clock Frequency                                                                                                                                                                        | f <sub>SCL</sub>    | 0             | 100  | kHz    |  |  |  |  |  |  |

| Start Condition Hold Time                                                                                                                                                                  | t <sub>HD:STA</sub> | 4.0           | -    | μS     |  |  |  |  |  |  |

| SCL "Low" Duration                                                                                                                                                                         | t <sub>LOW</sub>    | 4.7           | -    | μS     |  |  |  |  |  |  |

| SCL "High" Duration                                                                                                                                                                        | t <sub>HIGH</sub>   | 4.0           | -    | μS     |  |  |  |  |  |  |

| Start Condition Setup Time                                                                                                                                                                 | t <sub>SU:STA</sub> | 4.7           | -    | μS     |  |  |  |  |  |  |

| Data Hole Time                                                                                                                                                                             | t <sub>HD:DAT</sub> | 0             | 3.45 | μS     |  |  |  |  |  |  |

| Data Setup Time                                                                                                                                                                            | t <sub>SU:DAT</sub> | 250           | -    | ns     |  |  |  |  |  |  |

| Rising Time                                                                                                                                                                                | t <sub>R</sub>      | -             | 1000 | ns     |  |  |  |  |  |  |

| Falling Time                                                                                                                                                                               | t⊨                  | -             | 300  | ns     |  |  |  |  |  |  |

| Stop Condition Setup Time                                                                                                                                                                  | t <sub>SU:STO</sub> | 4.0           | -    | μS     |  |  |  |  |  |  |

| Bus Release Time                                                                                                                                                                           | t <sub>BUF</sub>    | 4.7           | -    | μS     |  |  |  |  |  |  |

# ■ I<sup>2</sup>C License

Purchase of  $I^2C$  components of New Japan Radio Co. ,Ltd or one of sublicensed Associated Companies conveys a license under the Philips  $I^2C$  Patent Rights to use these components in an  $I^2C$  system, provided that the system conforms to the  $I^2C$  Standard specification as defined by Philips.

New Japan Radio Co., Ltd.

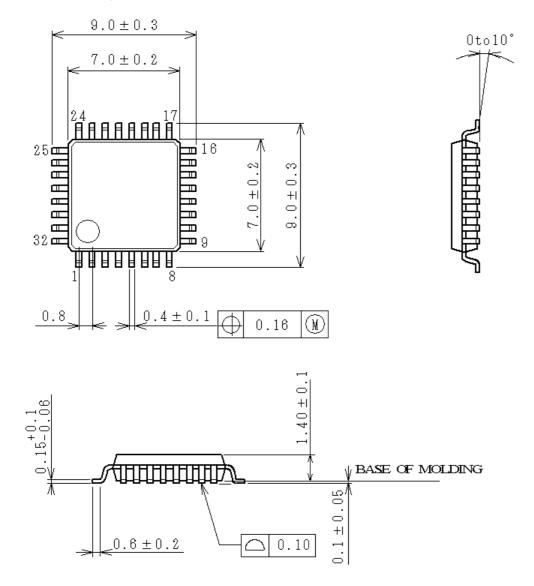

6. Package Dimensions (EIAJ : QFP032-P-0707-1)

UNIT : mm

LEADS MATERIAL : 42ALLOY LEADS FINISH : SOLDER PLATING MOLD MATERIAL : EPOXY RESIN

> [CAUTION] The specifications on this databook are only given for information, without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.

Weight 0.2g (TYP)

Ver. 1.14

WW