## **PRELIMINARY**

## BIT MAP LCD DRIVER

#### **■** GENERAL DESCRIPTION

The NJU6578 is a bit map LCD driver to display graphics or characters.

It contains 3,366 bits display data RAM, microprocessor interface circuits, instruction decoder, 102-segment and 33-common (1 out of 33-driver is prepared for icon display) drivers.

The bit image display data is transferred to the display data RAM by serial or 8-bit parallel interface.

$33 \times 102$  dots graphics or 6-character 2-line by  $16 \times 16$  dot character with icon are displayed by NJU6578 itself.

The wide operating voltage from 2.4V to 5.5V and low operating current are useful for small size battery operating items.

The build-in Electrical Variable Resistance is very precision, furthermore the rectangle outlook is very applicable to COG or Slim TCP.

#### PACKAGE OUTLINE

NJU6578CH

#### **■ FEATURES**

- Direct Correspondence between Display Data RAM and LCD Pixel

- Display Data RAM 3,366 bits

- 135 LCD Drivers 33-common and 102-segment

- Direct Microprocessor for Interface both of 68 and 80 type MPU

- Serial Interface

- Programmable Duty Ratio : 1/32 or 1/33 Duty

- Useful Instruction Set

Display Data Read/Write, Display ON/OFF Cont, Inverse Display, Page Address Set, Column Address Set, Status Read, All On/Off, Icon Display, Read Modify Write, Common Driver order Assignment and Power Saving.

- Power Supply Circuits for LCD Incorporated

Step up Circuits, Regulator, Voltage Follower x 4

- Precision Electrical Variable Resistance

- Low Power Consumption

- Operating Voltage --- 2.4V to 5.5V

- LCD Driving Voltage --- 6.0V to 10V

- Package Outline --- TCP / Bumped Chip

- C-MOS Technology

Feb. 1999 Ver. 1

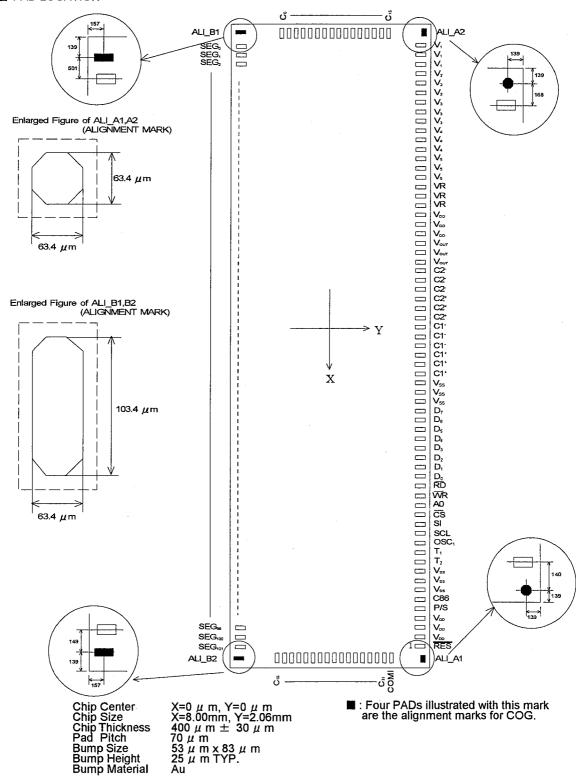

## **■ PAD LOCATION**

#### **■ PAD COORDINATES**

Chip Size 8.00mm x 2.06mm(Chip Center X=0  $\mu$  m,Y=0  $\mu$  m)

| PAD COC | PRDINATES       |       | Chip   |

|---------|-----------------|-------|--------|

| PAD No. | Terminal        | X= μm | Y= μ m |

| 1       | RES             | 3721  | 891    |

| 2       | VDD             | 3651  | 891    |

| 3       | VDD             | 3581  | 891    |

| 4       | <b>V</b> DD     | 3511  | 891    |

| 5       | P/S             | 3431  | 891    |

| 6       | C86             | 3361  | 891    |

| 7       | Vss             | 3281  | 891    |

| 8       | Vss             | 3211  | 891    |

| 9       | Vss             | 3141  | 891    |

| 10      | T <sub>2</sub>  | 3061  | 891    |

| 11      | T1              | 2991  | 891    |

| 12      | OSC1            | 2921  | 891    |

| 13      | SCL             | 2850  | 891    |

| 14      | SI              | 2780  | 891    |

| 15      | ĊŚ              | 2710  | 891    |

| 16      | A0              | 2640  | 891    |

| 17      | WR              | 2570  | 891    |

| 18      | RD              | 2500  | 891    |

| 19      | Do              | 2247  | 891    |

| 20      | D1              | 1865  | 891    |

| 21      | D2              | 1483  | 891    |

| 22      | Дз              | 1101  | 891    |

| 23      | D4              | 719   | 891    |

| 24      | D5              | 338   | 891    |

| 25      | D6              | -45   | 891    |

| 26      | D7              | -426  | 891    |

| 27      | Vss             | -745  | 891    |

| 28      | Vss             | -815  | 891    |

| 29      | Vss             | -885  | 891    |

| 30      | C1 <sup>+</sup> | -991  | 891    |

| 31      | C1 <sup>+</sup> | -1061 | 891    |

| 32      | C1+             | -1131 | 891    |

| 33      | C1-             | -1237 | 891    |

| 34      | C1-             | -1307 | 891    |

| 35      | C1-             | -1377 | 891    |

| 36      | C2+             | -1447 | 891    |

| 37      | C2+             | -1517 | 891    |

| 38      | C2+             | -1587 | 891    |

| 39      | C2 <sup>-</sup> | -1710 | 891    |

| 40      | C2 <sup>-</sup> | -1780 | 891    |

| 41      | C2-             | -1850 | 891    |

| 42      | Vout            | -1972 | 891    |

| 43      | Vout            | -2042 | 891    |

| 44      | Vout            | -2112 | 891    |

| 45      | <b>V</b> DD     | -2235 | 891    |

| 46      | VDD             | -2305 | 891    |

| 47      | VDD             | -2375 | 891    |

| 48      | VR              | -2455 | 891    |

| 49      | VR              | -2525 | 891    |

| 50      | VR VR           | -2595 | 891    |

|         |                 |       | L      |

| PAD No.  | Terminal          | X= μ m         | Y= μ m       |

|----------|-------------------|----------------|--------------|

| 51       | <b>V</b> 5        | -2675          | 891          |

| 52       | <b>V</b> 5        | -2745          | 891          |

| 53       | <b>V</b> 5        | -2815          | 891          |

| 54       | V4                | -2894          | 891          |

| 55       | V4                | -2964          | 891          |

| 56       | V4                | -3034          | 891          |

| 57       | <b>V</b> 3        | -3114          | 891          |

| 58       | <b>V</b> 3        | -3184          | 891          |

| 59       | <b>V</b> 3        | -3254          | 891          |

| 60       | V2                | -3333          | 891          |

| 61       | <b>V</b> 2        | -3403          | 891          |

| 62       | V2                | -3473          | 891          |

| 63       | V1                | -3553          | 891          |

| 64       | V1                | -3623          | 891          |

| 65       | V1                | -3693          | 891          |

| 66       | C15               | -3861          | 573          |

| 67       | C14               | -3861          | 503          |

| 68       | C13               | -3861          | 433          |

| 69       | C12               | -3861          | 363          |

| 70       | C11               | -3861          | 293          |

| 71       | C10               | -3861          | 223          |

| 72       | C9                | -3861          | 153          |

| 73       | C8                | -3861          | 83           |

| 74       | C7                | -3861          | 13           |

| 75       | C6                | -3861          | -57          |

| 76       | C5                | -3861          | -127         |

| 77       | C4                | -3861          | -197         |

| 78       | C3                | -3861          | -267         |

| 79       | C2                | -3861          | -337         |

| 80       | C1                | -3861          | -407         |

| 81       | C <sub>0</sub>    | -3861          | -477         |

| 82       | SEG <sub>0</sub>  | -3360          | -891         |

| 83       | SEG <sub>1</sub>  | -3290          | -891         |

| 84       | SEG2              | -3220          | -891         |

| 85<br>86 | SEG3              | -3150<br>-3080 | -891<br>-891 |

| 87       | SEG4<br>SEG5      | -3080          | -891         |

| 88       | SEG6              | -2940          | -891         |

| 89       | SEG <sub>7</sub>  | -2870          | -891         |

| 90       | SEG#              | -2800          | -891         |

| 91       | SEG <sub>9</sub>  | -2730          | -891         |

| 92       | SEG <sub>10</sub> | -2660          | -891         |

| 93       | SEG11             | -2590          | -891         |

| 94       | SEG12             | -2520          | -891         |

| 95       | SEG13             | -2450          | -891         |

| 96       | SEG14             | -2380          | -891         |

| 97       | SEG <sub>15</sub> | -2310          | -891         |

| 98       | SEG16             | -2240          | -891         |

| 99       | SEG17             | -2170          | -891         |

| 100      | SEG18             | -2100          | -891         |

| L        |                   |                | <u> </u>     |

| PAD No. | Terminal       | X= μ m | Y= μ m       |

|---------|----------------|--------|--------------|

| 101     | SEG19          | -2030  | -891         |

| 102     | SEG20          | -1960  | -891         |

| 103     | SEG21          | -1890  | -891         |

| 104     | SEG22          | -1820  | -891         |

| 105     | SEG23          | -1750  | -891         |

| 106     | SEG24          | -1679  | -891         |

| 107     | SEG25          | -1609  | -891         |

| 108     | SEG26          | -1539  | -891         |

| 109     | SEG27          | -1469  | -891         |

| 110     | SEG28          | -1399  | -891         |

| 111     | SEG29          | -1329  | -891         |

| 112     | SEG30          | -1259  | -891         |

| 113     | SEG31          | -1189  | -891         |

| 114     | SEG32          | -1119  | -891         |

| 115     | SEG33          | -1049  | -891         |

| 116     | SEG34          | -979   | -891         |

| 117     | SEG35          | -909   | -891         |

| 118     | SEG36          | -839   | -891         |

| 119     | SEG37          | -769   | -891         |

| 120     | SEG38          | -699   | -891         |

| 121     | SEG39          | -629   | -891         |

| 122     | SEG40          | -559   | -891         |

| 123     | SEG41          | -489   | -891         |

| 124     | SEG42          | -419   | -891         |

| 125     | SEG43          | -349   | -891         |

| 126     | SEG44          | -279   | -891         |

| 127     | SEG45          | -209   | -891         |

| 128     | SEG46          | -139   | -891         |

| 129     | SEG47          | -69    | -891         |

| 130     | SEG48          | 1      | -891         |

| 131     | SEG49          | 71     | -891         |

| 132     | SEG50          | 141    | -891         |

| 133     | SEG51          | 211    | -891         |

| 134     | SEG52          | 281    | -891         |

| 135     | SEG53          | 351    | -891         |

| 136     | SEG54          | 421    | -891         |

| 137     | SEG55          | 491    | -891         |

| 137     | SEG56          | 561    | -891         |

| 139     | SEG57          | 631    | -891         |

| 140     | SEG57          | 701    | -891         |

| 141     | SEG59          | 771    | -891         |

| 142     | SEG59<br>SEG60 | 841    | -891         |

| 142     | SEG60<br>SEG61 | 911    | -891         |

| 144     | SEG61<br>SEG62 |        | -891         |

|         | <del></del>    | 981    |              |

| 145     | SEG63          | 1051   | -891         |

| 146     | SEG64          | 1121   | -891<br>-801 |

| 147     | SEG65          | 1191   | -891         |

| 148     | SEG66          | 1261   | -891         |

| 149     | SEG67          | 1331   | -891         |

| 150     | SEG68          | 1401   | -891         |

| 151     | SEG69          | 1471   | -891         |

| 152     | SEG70          | 1541   | -891         |

| PAD No.   | Terminal | X= μ m        | Y= μm        |

|-----------|----------|---------------|--------------|

| 153       | SEG71    | 1611          | -891         |

| 154       | SEG72    | 1681          | -891         |

| 155       | SEG73    | 1751          | -891         |

| 156       | SEG74    | 1822          | -891         |

| 157       | SEG75    | 1892          | -891         |

| 158       | SEG76    | 1962          | -891         |

| 159       | SEG77    | 2032          | -891         |

| 160       | SEG78    | 2102          | -891         |

| 161       | SEG79    | 2172          | -891         |

| 162       | SEG/9    | 2242          | -891         |

| 163       | SEG81    | 2312          | -891         |

| 164       | SEG82    | 2382          | -891         |

| 165       | SEG83    | 2452          | -891         |

| 166       | SEG83    | 2522          | -891         |

| -         |          |               |              |

| 167       | SEG85    | 2592          | -891<br>801  |

| 168       | SEG86    | 2662          | -891         |

| 169       | SEG87    | 2732          | -891         |

| 170       | SEG88    | 2802          | -891         |

| 171       | SEG89    | 2872          | -891         |

| 172       | SEG90    | 2942          | -891         |

| 173       | SEG91    | 3012          | -891         |

| 174       | SEG92    | 3082          | -891         |

| 175       | SEG93    | 3152          | -891         |

| 176       | SEG94    | 3222          | -891         |

| 177       | SEG95    | 3292          | -891         |

| 178       | SEG96    | 3362          | -891         |

| 179       | SEG97    | 3432          | -891         |

| 180       | SEG98    | 3502          | -891         |

| 181       | SEG99    | 3572          | -891         |

| 182       | SEG100   | 3642<br>3712  | -891         |

| 183       | SEG101   | 3861          | -891<br>-342 |

| 185       | C16      | 3861          | ·            |

| 186       | C17      | 3861          | -272         |

| 187       | C18      |               | -202         |

| 188       | C19      | 3861<br>3861  | -132<br>-62  |

| 189       | C20      | 3861          | 8            |

| 190       | C21      | 3861          | 78           |

| 190       | C22      | 3861          | 148          |

|           | C23      |               |              |

| 192       | C24      | 3861          | 218<br>288   |

| 193       | C25      | 3861<br>3861  | 358          |

| 194       | C26      |               | 428          |

| 195       | C27      | 3861          | 428          |

| 196       | C28      | 3861          |              |

| 197       | C29      | 3861          | 568          |

| 198       | C30      | 3861          | 638          |

| 199       | C31      | 3861          | 708          |

| 200       | COMI     | 3861          | 778          |

| ALIGNMENT | ALI_A1   | 3861          | 891          |

|           | ALI_A2   | -3861<br>3861 | 891          |

| ALIGNMENT | ALL B2   | -3861         | -873         |

| ALIGNMENT | ALI_B2   | 3861          | -873         |

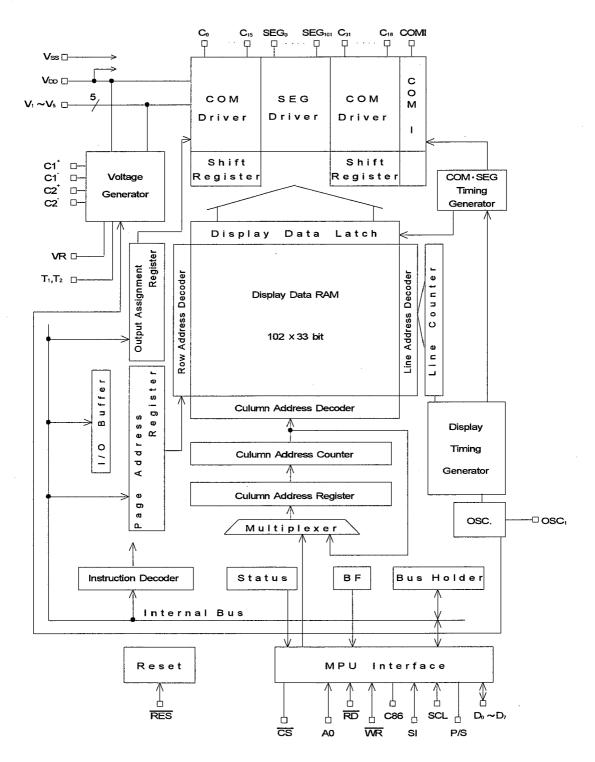

#### **■ BLOCK DIAGRAM**

New Japan Radio Co., Ltd.

## **■ TERMINAL DESCRIPTION**

| No                                                       | Symbol                                                                   | 1/0   |                                                                                                                                                                                                                                                                              |                                       |                           | Func                                  | tion                                              |                   |                                         |

|----------------------------------------------------------|--------------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------|---------------------------------------|---------------------------------------------------|-------------------|-----------------------------------------|

| 2,3,4,<br>45,46,47                                       | VDD                                                                      | Power | VDD=+3V<br>VDD=+5V. (Less                                                                                                                                                                                                                                                    | than 3.3                              | V shou                    | ld apply wh                           | en voltage triple                                 | er using.)        |                                         |

| 7,8,9,<br>27,28,29                                       | Vss                                                                      | GND   | Vss=0V                                                                                                                                                                                                                                                                       | · · · · · · · · · · · · · · · · · · · |                           |                                       |                                                   |                   |                                         |

| 63,64,65<br>60,61,62<br>57,58,59<br>54,55,56<br>51,52,53 | V1<br>V2<br>V3<br>V4<br>V5                                               | Power | LCD Driving Volume Supply each lev VDD VDD When the intern LCDbias voltage                                                                                                                                                                                                   | el of LCD<br>11≧V2≧V<br>al power      | driving<br>3≧V4<br>supply | y voltage fro<br>≧V5<br>is on, the ir | m outside with                                    | following relati  | on.                                     |

|                                                          |                                                                          |       | Terminal                                                                                                                                                                                                                                                                     | V                                     | 1                         | V2                                    | V3                                                | V4                | 7                                       |

|                                                          |                                                                          |       | Voltage                                                                                                                                                                                                                                                                      | V5+6/7                                | <b>V</b> LCD              | V5+5/7VLC                             | D V5+2/7VLCD                                      | V5+1/7VLCD        |                                         |

|                                                          |                                                                          |       |                                                                                                                                                                                                                                                                              |                                       |                           |                                       |                                                   | (VLCD=VD          | D-V5)                                   |

| 30,31,32<br>33,34,35<br>36,37,38<br>39,40,41             | C1 <sup>+</sup><br>C1 <sup>-</sup><br>C2 <sup>+</sup><br>C2 <sup>-</sup> | 0     | Step up capacit<br>In case of triple<br>In case of doub<br>C2 <sup>+</sup> to C1 <sup>+</sup> , and                                                                                                                                                                          | r operatio<br>Ier operat              | n, conr<br>ion, co        | nect the cap                          |                                                   |                   |                                         |

| 42,43,44                                                 | Vout                                                                     | 0     | Step up voltage and Vss.                                                                                                                                                                                                                                                     | output te                             | rminal.                   | Connect th                            | e set up capaci                                   | tor between th    | is terminal                             |

| 48,49,50                                                 | VR                                                                       | ı     | Voltage adjust t<br>between VDD ar                                                                                                                                                                                                                                           |                                       |                           | is adjusted                           | by external ble                                   | eder resistanc    | e connect                               |

| 11                                                       | T1                                                                       | 1     | LCD bias voltag                                                                                                                                                                                                                                                              | e control                             | termina                   | als. (※Don'                           | : Care)                                           |                   | _                                       |

| 10                                                       | T2                                                                       |       | T1                                                                                                                                                                                                                                                                           | T2                                    | Step                      | up Cir.                               | Voltage Adj.                                      | V/F Cir.          | _j'                                     |

|                                                          |                                                                          |       | L                                                                                                                                                                                                                                                                            | *                                     | Ava                       | ailable                               | Available                                         | Available         |                                         |

|                                                          |                                                                          |       | Н                                                                                                                                                                                                                                                                            | · L                                   | Not                       | Avail.                                | Available                                         | Available         |                                         |

|                                                          |                                                                          |       | Н                                                                                                                                                                                                                                                                            | Н                                     | Not                       | Avail.                                | Not Avail.                                        | Available         |                                         |

| 19 to 26                                                 | D0 to D7                                                                 | 1/0   | Tri-state bi-dired                                                                                                                                                                                                                                                           | tional Da                             | ta I/O t                  | erminal in 8                          | -bit parallel ope                                 | ration.           |                                         |

| 16                                                       | A0                                                                       | ı     | Connect to the between Display  A0  Distin                                                                                                                                                                                                                                   |                                       | d Instru                  |                                       | tus of A0.                                        | o D7 is distingu  | iished                                  |

| 1                                                        | RES                                                                      | ī     | Reset terminal.<br>Reset operation                                                                                                                                                                                                                                           |                                       |                           |                                       |                                                   | tialization is pe | erformed.                               |

| 15                                                       | cs                                                                       | ı     | Chip select term                                                                                                                                                                                                                                                             | ninal. Data                           | input/                    | Output are                            | available during                                  | CS ="L".          | * * * * * * * * * * * * * * * * * * * * |

| 18                                                       | RD<br>(E)                                                                |       | <li>In case of 80 RD signal of 80 During this signal case of 68 Enable signal</li>                                                                                                                                                                                           | 80 type M<br>gnal is "L"<br>Type MPU  | PU inp<br>', D0 to<br>l>  | D7 termina                            | Active "L".<br>ils are output.<br>nal. Active "H" |                   |                                         |

| 17                                                       | WR<br>(R/W)                                                              |       | <in 68="" case="" co<="" of="" read="" td="" write=""><td>e 80 type<br/>he data b<br/>Type MPL</td><td>MPU ī<br/>us inpl<br/>I&gt;</td><td>ıt synchroni<br/>3 type MPU</td><td>Active "L".  zing the rise ed  input terminal.</td><td>lge of this sign</td><td>al.</td></in> | e 80 type<br>he data b<br>Type MPL    | MPU ī<br>us inpl<br>I>    | ıt synchroni<br>3 type MPU            | Active "L".  zing the rise ed  input terminal.    | lge of this sign  | al.                                     |

|                                                          |                                                                          |       | R/W                                                                                                                                                                                                                                                                          | Н                                     |                           | L                                     | _                                                 |                   |                                         |

| 1                                                        |                                                                          | ı     | State                                                                                                                                                                                                                                                                        | Re                                    |                           | Write                                 | 1                                                 |                   |                                         |

| No             | Symbol    | 1/0 |      |                           |                             | Fu                                               | nction                            |               |                |            |

|----------------|-----------|-----|------|---------------------------|-----------------------------|--------------------------------------------------|-----------------------------------|---------------|----------------|------------|

| 6              | C86       | ı   | MP   | U interface               | type select                 | ion terminal.                                    |                                   |               |                | 700        |

|                |           |     |      | C86                       | Н                           | 1 [                                              |                                   |               |                |            |

|                |           | 1   |      | Status                    |                             |                                                  | ype                               |               |                |            |

|                |           |     |      |                           |                             |                                                  |                                   |               |                |            |

| 14             | SI        | 1   | Ser  | ial data inp              | out terminal.               |                                                  |                                   |               |                |            |

| 13             | SCL       | l   | SId  | lata input a              |                             | put terminal.<br>dge of SCL in<br>rise edge.     | successive                        | ely. It conve | ert to SCL th  | e parallei |

| 5              | P/S       | 1   | Ser  | ial or paral              | lel interface               | selection term                                   | ninal.                            |               |                |            |

|                |           |     |      | P/S                       | Chip Select                 | Data/Command                                     | Data                              | Read/Write    | Serial CLK     |            |

|                |           |     | l    | "H"                       | ĊS                          | A0                                               | D0 to D7                          | RD,WR         | -              |            |

|                |           |     | İ    | "L"                       | cs                          | A0                                               | SI                                | Write only    | SCL            |            |

|                |           |     |      | interface.                |                             | read operation                                   |                                   |               |                |            |

|                |           |     | · In | case of th                | e serial inte               | terface (P/S='<br>rface (P/S="L'<br>high impedar | '), RD and                        | WR must b     | e fix "H" or " | L", and    |

| 12             | OSC1      | ١   |      |                           | nput termina<br>should be o | al for Maker te<br>pen.)                         | esting.                           |               |                |            |

| 66~81          | C15~C0    | 0   | Se   | gment out                 |                             | terminals.<br>s : SEG0 to S<br>s : C0 to C31     | EG101                             |               |                |            |

|                |           |     | T    | he followin               |                             | tages are sele                                   |                                   |               |                |            |

|                |           |     |      | RAM<br>Data               | FR -                        | <del></del>                                      | t Voltage                         |               |                |            |

| 82~183         | SEG₀<br>~ | 0   |      | Data                      | н                           | Normal<br>VDD                                    | Reve<br>V2                        |               |                |            |

|                | SEG101    |     |      | Н                         | i i                         | V5                                               | V2                                |               |                |            |

|                |           |     |      |                           | Н                           | V2                                               | VDI                               | D             |                |            |

|                |           |     |      | L                         | L                           | V3                                               | V <sub>5</sub>                    |               |                |            |

|                |           |     |      |                           | put Termina<br>g output vol | l<br>tages are sele                              | ected by                          |               |                |            |

| 184~199        | C31       | 0   |      | e combina                 | tion of FR a                | nd status of c                                   |                                   |               |                |            |

| 184~199        |           | 0   |      | e combina<br>Scan<br>Data | tion of FR a                | nd status of c                                   |                                   |               |                |            |

| 184~199        | ~         | 0   |      | Scan<br>Data              | FR<br>H                     | nd status of c                                   | ommon.<br>ut Voltage<br>Vs        |               |                |            |

| 184~199        | ~         | 0   |      | Scan                      | FR<br>H<br>L                | nd status of c                                   | ommon.<br>ut Voltage<br>Vs<br>VDD |               |                |            |

| 184~199        | ~         | 0   |      | Scan<br>Data              | FR<br>H                     | nd status of c                                   | ommon.<br>ut Voltage<br>Vs        |               |                |            |

| 184~199<br>200 | ~         | 0   | lcor | Scan<br>Data<br>H<br>L    | FR H L H L                  | nd status of c                                   | ommon. ut Voltage V5 VDD V1 V4    | execution.    |                | 1400-00    |

|                | ~<br>C16  |     | lcor | Scan<br>Data<br>H<br>L    | FR H L H L                  | Outpu<br>Outpu<br>nal.<br>Icon Display           | ommon. ut Voltage V5 VDD V1 V4    |               |                | 1444       |

#### Functional Description

#### (1) Description for each blocks

#### (1-1) Busy Flag (BF)

While the internal circuits are operating, the busy flag (BF) is "1", and any instruction excepting for the status read are inhibited .

The busy flag goes to "1" from D7 terminal when status read instruction is executed.

When enough cycle time over than toyo indicated in "BUS TIMING CHARACTERISTICS" is ensured, no need to check the busy flag for reduction of the MPU loads.

#### (1-2) Line Counter

The Line Counter generates the line address of display data RAM by the count up operation synchronizing the common cycle after the reset operation at the status change of internal FR signal.

## (1-3) Column Address Counter

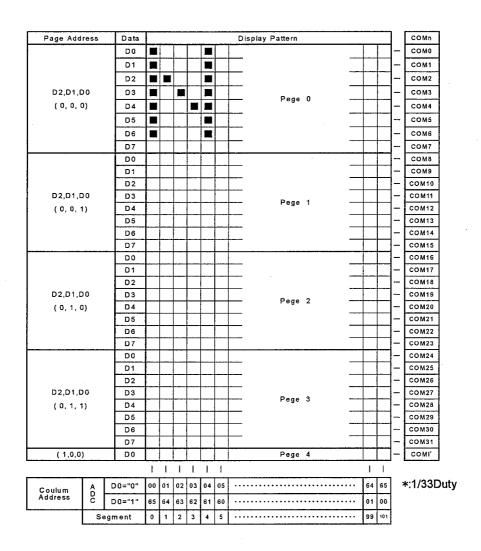

The column address counter is 8-bit pre-settable counter addressing the column address of display data RAM as shown in Fig. 1. It is incremented (+1) up to (66)H by the Display Data Read/Write instruction execution. It stops the count up operation at (66)H, and it does not count up non existing address area over than (66)H by the count lock function. This count lock is released by new column address set.

The column address counter is independent of the Page Register.

By the Address Inverse Instruction, the column address decoder inverse the column address of Display Data RAM corresponding to the Segment Driver.

## (1-4) Page Register

The page register gives a page address of Display Data RAM as shown in Fig. 1. When the MPU accesses the data with the page change, the page address set instruction is required. Page address "4"(D2="H" and D1=D0="L") is Icon RAM area, the data only for the Do is valid.

#### (1-5) Display Data RAM

Display Data RAM is the bit map RAM consisting of 3,366 bits to memorize the display data corresponding to each pixel of LCD panel. The each bit in the Display Data RAM corresponds to the each pixel of the LCD panel and controls the display by following bit data.

When Normal Display: On="1", Off="0" When Inverse Display: On="0", Off="1"

The Display Data RAM outputs 102-bit parallel data in the area addressed by the line counter, and these data are set into the Display Data Latch.

The access operation from MPU to the display data RAM and the data output from the display data RAM are so controlled to operate independently that the data rewriting does not influence with any malfunctions to the display. The relation between column address and segment output can inverse by the Address Inverse Instruction ADC as shown in Fig. 1.

Fig.1 Correspondence with Display Data RAM and Address (COMI can be used in case of 1/33 duty set.)

## (1-6) Common Driver Assignment

The scanning order can be assigned by setting A3 of the Output Assignment Register as shown Table 1.

| Register | ]          |       | COM Output     | ts Terminals      |                |

|----------|------------|-------|----------------|-------------------|----------------|

| A3       | PAD No.    | 66    | 81             | 184               | 199            |

| A3       | Pin name   | C15   | Co             | C16               | C31            |

| 0        | ] <b>→</b> | COM15 | COMo           | COM <sub>16</sub> | <b>→</b> COM31 |

| 1        | ] <b>→</b> | COM16 | <b>→</b> СОМ31 | COM15€            | COMo           |

The lcon display is regardless with this function, therefore the lcon Display instruction must be executed when the lcon display is needed. In this time, the lcon display driver COMI is fixed to COM32 timing regardless the other Common Driver assignment.

### (1-7) Reset Circuit

Reset circuit operates the following initializations when the condition of RES terminal goes to "L" level.

#### Initialization

- Display Off

- ② Normal Display (Non-inverse display)

- 3 Icon Display Reset

- 4 ADC Select : Normal (ADC Instruction Do="0")

- ⑤ Read Modify Write Mode Off

- 6 Internal Power supply (Step up) circuits Off .

- Olear the serial interface register

- Set the address (00)H to the Column Address Counter

- Set the page "0" to the Page Address Register

- Select the D3 of the Output Assignment Register to "0"

- Set the EVR register to (00)H

The RES terminal should be connected to the Reset terminal of MPU for the initialization at the <u>mean</u> time with MPU as shown "MPU Interface Example". The period of reset signal requires over than  $10 \,\mu$  s RES="L" level input as shown in "Electrical Characteristics". After  $1 \,\mu$  s from the rise edge of RES signal, the operation goes to normal. When the internal LCD power supply is not used, the <u>external LCD power supply into the NJU6578 must be turned on during RES = "L". Although the condition of RES="L" clear each registers and initialize as above, the oscillation circuit and the output terminal conditions (Do to D7) are not influenced. The initialization must be performed using RES terminal at the power on, to prevent hung up or any incorrect operations. The reset Instruction performs the initialization procedures from No.8 to No.11 as shown in above.</u>

NOTE) The noise into the RES terminal should be eliminated to avoid error on the application with the careful design.

## (1-8) LCD Driving

#### (a) LCD Driving Circuits

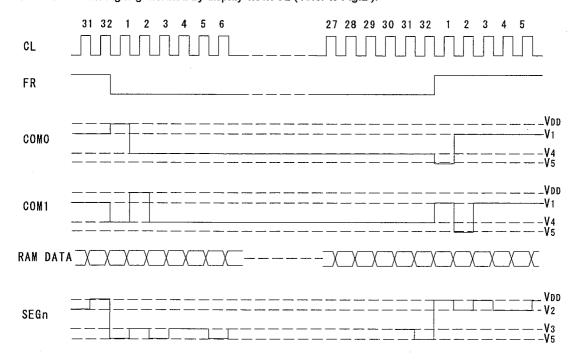

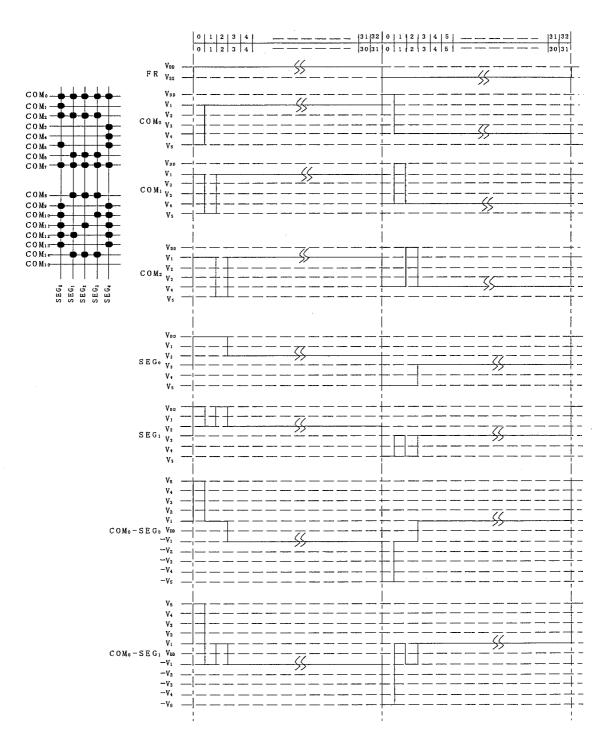

LCD driving circuits are consisted of 135 multiplexers which operate as 102 Segment drivers, 32 Common drivers and 1 Icon common driver. 33 Common drivers with the shift register scan the common display signal. The combination of the Display data, COM scan signal and FR signal forms the LCD driving output voltage. The output wave form is shown in the Fig. 7.

#### (b) Display Data Latch Circuits

Display Data Latch stores 102-bit display data temporarily which is output to LCD driver circuits at a common cycle from Display Data RAM addressed by Line Counter. The instructions of Display On/Off, Display inverse On/Off and Static drive On/Off control only the data in Display Data Latch, therefore, the data in the Display Data RAM is not changed.

## (c) Line Counter and Latch signal of Latch Circuits

The clock to Line Counter and latch signal to the Latch Circuits are generated from the internal display clock (CL). The line address of Display Data RAM is renewed synchronizing with display clock(CL). 102 bits display data are latched in display latch circuits synchronizing with display clock, and then output to the LCD driving circuits. The display data transfer to the LCD driving circuits is executed independently with RAM access by the MPU.

#### (d) Display Timing Generator

Display Timing Generator generates the timing signal for the display system by combination of the master clock CL and Driving Signal FR (refer to Fig.2). The Frame Signal FR and LCD alternative signal generate LCD driving waveform of the two frame alternative driving method.

#### (e) Common Timing Generation

The common timing is generated by display clock CL (refer to Fig.2).

Fig.2 Waveform of Display Timing

## (f) Oscillation Circuit

The Oscillation Circuit is a low power CR oscillator incorporating with a Resistor and a Capacitor. It generates clocks for display timing signal source and the clock for step up circuits for LCD driving. The oscillation circuit output frequency is divided by 4 which is used as display clock CL.

#### (g) Power Supply Circuit

Internal Power Supply Circuit generate the High voltage and Bias voltage for the LCD. The power Supply Circuits consists of Step up (Tripler or Doubler) Circuits, Regulator Circuits, and Voltage Followers. The internal Power Supply is designed for small size LCD panel, therefore it is not suitable for the large size LCD panel application. If the contrast is not good in the large size LCD panel application, please supply the external.

The suitable values of the capacitors connecting to the V1 to V5 terminals and the step up circuit, and the feed-back resistors for V5 operational amplifier depend on the LCD panel. And the power consumption with the LCD panel is depending on the display pattern. Please evaluate with actuale LCD module.

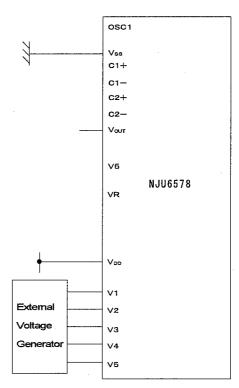

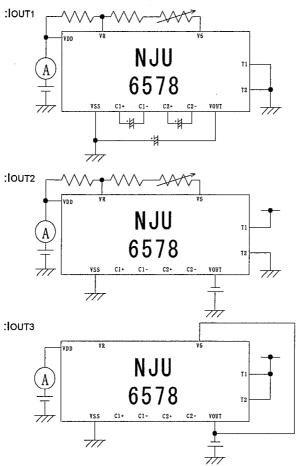

The operation of internal Power Supply Circuits is controlled by the Internal Power Supply On/Off Instruction. When the Internal Power Supply Off Instruction is executed, all of the step up circuits, regulator circuits, voltage follower circuits are turned off. In this time, the bias voltage of V1, V2, V3, V4, and V5 for the LCD should be supplied from outside, terminals C1<sup>+</sup>, C1<sup>-</sup>, C2<sup>+</sup>, C2<sup>-</sup>, and VR should be open. The status of internal power supply is selected by T1 and T2 terminal. Furthermore the external power supply operates with some of internal power supply function.

Table.3

(X: Don't Care)

| T1 | <b>T</b> 2 | Step up | Voltage Adj. | Buffer (V/F) | Ext. Power Supply | C1*,C1*,C2*,C2* | VR Term. |

|----|------------|---------|--------------|--------------|-------------------|-----------------|----------|

| L  | *          | 0       | 0            | 0            | -                 |                 |          |

| Н  | L          | Х       | 0            | 0            | Vout              | OPEN            |          |

| Н  | Н          | X       | Х            | 0            | V5, Vout          | OPEN            | OPEN     |

When (T<sub>1</sub>, T<sub>2</sub>)=(H, L), C1<sup>+</sup>, C1<sup>-</sup>, C2<sup>+</sup>, C2<sup>-</sup> terminals for voltage booster circuits are open because the step up circuits doesn't operate. Therefore the LCD driving voltage to the Vout terminal should be supplied from outside. When (T<sub>1</sub>, T<sub>2</sub>)=(H, H), terminals for step up circuits and VR are open, because the Step up circuits and Voltage adjust circuits do not operate.

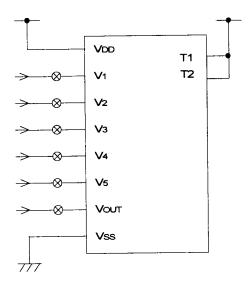

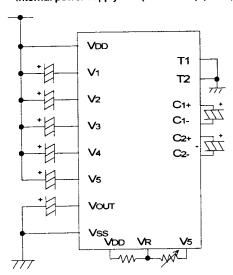

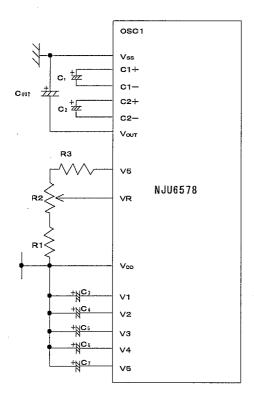

## O Power Supply applications

(1) External power supply operation.

(2)Internal power supply operation.

(Voltage Booster, Voltage Adj., Buffer(V/F))

Internal power supply ON (instruction) (T1,T2)=(L,L)

(3)External power supply operation with Voltage Adjustment, Buffer(V/F)

Internal power supply ON (Instruction)  $(T_1,T_2) = (H,L)$

(4)External power supply operation adjusted

Voltage to V5.

Internal power supply ON (Instruction) (T1,T2) =(H,H)

**V**DD VDD T1 T1 V1 T2 T2 **V**2 777 **V**2 **V**3 **V**4 **V**5 **V**5 **V**OUT -⊗-**V**OUT Vss

\*  $\otimes$  : These switches should be open during the power save mode.

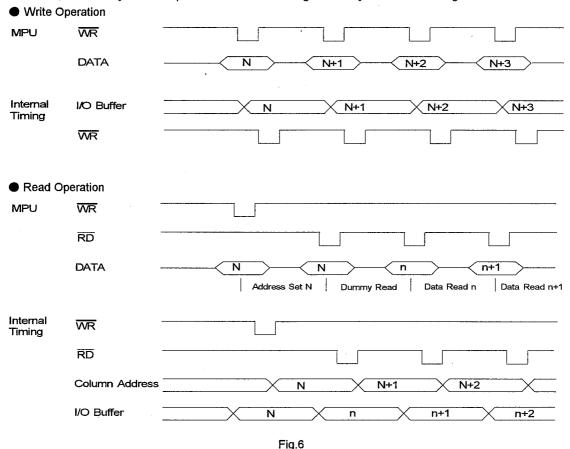

## (2) Instruction

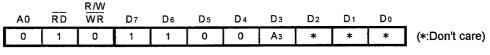

The NJU6578 distinguishes the signal on the data bus by combination of A0,  $\overline{RD}$  and  $\overline{WR}$ . The decode of the instruction and execution are performs only depend on the internal timing only neither the external clock. In case of serial interface, the data input as MSB first serially. The Table. 4 shows the instruction codes of the NJU6578.

Table 4. Instruction Code

|      | l.,                                     |    |    |        |    |     | Code | ,                |        |        | •            |        | Di                                                                                  |

|------|-----------------------------------------|----|----|--------|----|-----|------|------------------|--------|--------|--------------|--------|-------------------------------------------------------------------------------------|

|      | Instruction                             | A0 | RD | WR     | D7 | D6  | D5   | D <sub>.</sub> 4 | Dз     | D2     | D1           | Do     | Description                                                                         |

| (1)  | Display ON/OFF                          | 0  | 1  | 0      | 1  | 0   | 1    | 0                | 1      | 1      | 1            | 0      | LCD Display ON/OFF<br>0:OFF 1:ON                                                    |

| (2)  | Page Address Set                        | 0  | 1  | 0      | 1  | 0   | 1    | 1                | *      |        | Page<br>ddre |        | Set the page of DD RAM to the<br>Page Address Register                              |

| (3)  | Column Address Set<br>High Order 3bits  | 0  | 1  | 0      | 0  | 0   | 0    | 1                | 0      |        | jh Or<br>umn |        | Set the Higher order 3 bits<br>Column Address to the Reg.                           |

| (4)  | Column Address Set<br>Lower Order 4bits | 0  | 1  | 0      | 0  | 0   | 0    | 0                | _      |        | Ordo<br>n Ad |        | Set the Lower order 4 bits<br>Column Address to the Reg.                            |

| (5)  | Status Read                             | 0  | 0  | 1      |    | Sta | tus  |                  | 0      | 0      | 0            | 0      | Read out the internal Status                                                        |

| (6)  | Write Display Data                      | 1  | 1  | 0      |    |     | ١    | ∕Vrite           | Data   | 1      |              |        | Write the data into the Display<br>Data RAM                                         |

| (7)  | Read Display Data                       | 1  | 0  | 1      |    |     | F    | Read             | Data   | a      |              |        | Read the data from the Display<br>Data RAM                                          |

| (8)  | ADC Select                              | 0  | 1  | 0      | 1  | 0   | 1    | 0                | 0      | 0      | 0            | 0<br>1 | Set the DD RAM vs Segment<br>0:Normal 1:Inverse                                     |

| (9)  | Normal or Inverse of ON/OFF Set         | 0  | 1  | 0      | 1  | 0   | 1    | 0                | 0      | 1      | 1            | 0      | Inverse the ON and OFF Display<br>0:Normal 1:Inverse                                |

| (10) | Whole Display ON<br>/Normal Display     | 0  | 1  | 0      | 1  | 0   | 1    | 0                | 0      | 1      | 0            | 0      | Whole Display Turns ON<br>0:Normal 1:Whole Disp. ON                                 |

| (11) | Icon Display                            | 0  | 1  | 0      | 1  | 0   | 1    | 0                | 1      | 0      | 1            | 0      | Set the Duty Ratio<br>0:No Icon 1:With Icon                                         |

| (12) | Read Modify Write                       | 0  | 1  | 0      | 1  | 1   | 1    | 0                | 0      | 0      | 0            | 0      | Increment the Column Address<br>Register when writing but<br>no-change when reading |

| (13) | End                                     | 0  | 1  | 0      | 1  | 1   | 1    | . 0              | 1      | 1      | 1            | 0      | Release from the Read Modify write Mode                                             |

| (14) | Reset                                   | 0  | 1  | 0      | 1  | 1   | 1    | 0                | 0      | 0      | 1            | 0      | Initialize the internal Circuits                                                    |

| (15) | Output Assignment<br>Register Set       | 0  | 1  | 0      | 1  | 1   | 0    | 0                | А3     | *      | *            | *      | Set the scanning order of common drivers to the Register                            |

| (16) | Internal Power Supply<br>ON/OFF         | 0  | 1  | 0      | 0  | 0   | 1    | 0                | 0      | 1      | 0            | 0<br>1 | 0:Int. Power Supply OFF<br>1:Int. Power Supply ON                                   |

| (17) | LCD Driving Voltage Set                 | 0  | 1  | 0      | 1  | 1   | 1    | 0                | 1      | 1      | 0            | 1      | Set LCD Driving Voltage after the internal (external) power supply is turned on     |

| (18) | EVR Register Set                        | 0  | 1  | 0      | 1  | 0   | 0    | 0                | S      | etting | g Dat        | ta     | Set the V5 output level to the EVR register                                         |

| (19) | Power Save<br>(Dual Command)            | 0  | 1  | 0<br>0 | 1  | 0   | 1    | 0                | 1<br>0 | 1<br>1 | 1<br>0       | 0<br>1 | Set the Power Save Mode                                                             |

(\*:Don't Care)

## (3) Explanation of Instruction Code

#### (a) Display On/Off

This instruction executes whole display On/Off no relation with the data in the Display Data RAM and internal conditions.

| A0 | RD  | WR       | D7  | D6 | <b>D</b> 5 | D4 | Dз | D2 | D1 | Dο |

|----|-----|----------|-----|----|------------|----|----|----|----|----|

| 0  | 1   | 0        | 1   | 0  | 1          | 0  | 1  | 1  | 1  | D  |

|    | חיט | isplay C | )ff |    |            |    |    |    |    |    |

D 0:Display Off 1:Display On

#### (b) Page Address Set

When MPU accesses the Display Data RAM, the page address must be selected before the data writing. The access to the Display Data RAM is available by the page and column address set (Refer the Fig. 1.). The page address change does not influence with the display. Page 4 is a lcon display data area which available only for the Do.

|   | Α0  | RD | R/W<br>WR | <b>D</b> 7 | D6 | D5       | D4 | Dз | D <sub>2</sub> | D1                  | Do | _              |

|---|-----|----|-----------|------------|----|----------|----|----|----------------|---------------------|----|----------------|

|   | 0   | 1  | 0         | 1          | 0  | 1        | 1  | *  | A <sub>2</sub> | A1                  | Αo | (*:Don't care) |

|   |     |    |           |            |    |          |    |    |                |                     |    | _              |

| - |     |    |           |            |    |          |    |    |                |                     |    |                |

| L | Α   | .2 | F         | À 1        |    | Αo       |    |    |                | Page                |    |                |

| ŀ | Α ( |    |           | \ 1<br>0   |    | A 0<br>0 |    |    |                | Page<br>0           |    |                |

| ŀ |     | )  |           |            |    |          |    |    |                | Page<br>0<br>1      |    |                |

| ŀ |     | )  |           | 0          |    |          |    |    |                | Page<br>0<br>1<br>2 |    |                |

#### (c) Column Address

When MPU accesses the Display Data RAM, the page address set(refer(b)) and column address set are required before the data writing. The column address set requires twice address set which are higher order 3 bits address set and lower order 4 bits. When the MPU accesses the Display Data RAM sequentially, the column address is increase one by one automatically, therefore, the MPU can access only the data sequentially without address set.

After writing 1page data page address setting is required due to page address doesn't increase automatically. The increment of the column address is stopped at the address of (66)H automatically, and the page address is no changed even if the column address increase to (66)H and stop. In this time the page address is not changed.

|   | Α0             | RD | WR         | D7         | D6         | D5      | D4             | Dз | D2  | D1         | Do     |              |

|---|----------------|----|------------|------------|------------|---------|----------------|----|-----|------------|--------|--------------|

|   | 0              | 1  | 0          | 0          | 0          | 0       | 1              | 0  | A6  | <b>A</b> 5 | A4     | Higher Order |

|   | 0              | 1  | 0          | 0          | 0          | 0       | 0              | Аз | A2  | <b>A</b> 1 | Ao     | Lower Order  |

|   |                |    |            |            |            |         |                |    |     |            |        |              |

| I | A <sub>6</sub> | A5 | <b>A</b> 4 | Аз         | <b>A</b> 2 | A1      | Αo             |    | Col | umn Ac     | dress  |              |

|   | A6             | A5 | A4<br>0    | <b>А</b> з | A2<br>0    | A1<br>0 | A <sub>0</sub> |    | Col | umn Ac     | dress  |              |

|   |                |    |            |            |            |         | _              |    | Col |            | Idress |              |

|   | 0              | 0  | 0          | 0          | 0          | 0       | 0              |    | Col |            | Idress |              |

|   | 0              | 0  | 0          | 0          | 0          | 0       | 0              |    | Col |            | Idress |              |

#### (d) Status Read

This instruction reads out the internal status of "BUSY", "ADC", "ON/OFF" and "RESET".

| Α0 | RD | R/W<br>WR | <b>D</b> 7 | D6  | D5     | D4    | Dз | D2 | D1 | Do |

|----|----|-----------|------------|-----|--------|-------|----|----|----|----|

| 0  | 0  | 1         | BUSY       | ADC | ON/OFF | RESET | 0  | 0  | 0  | 0  |

BUSY: BUSY=1 indicate the operating or the Reset cycle.

The instruction can be input after the BUSY status change to "0".

ADC : Indicate the output correspondence of column (segment) address and segment driver.

0 :Counterclockwise Output (Inverse) Column Address 101-n  $\longleftrightarrow$  Segment Driver n

1 :Clockwise Output (Normal) Column Address n  $\longleftrightarrow$  Segment Driver n

(Note) The data "0=Inverse" and "1=Normal" of ADC is inverted with the ADC select Instruction of "1=Inverse" and "0=Normal".

ON/OFF: Indicate the whole display On/Off status.

0: Whole Display "On

1: Whole Display "Off"

(Note) The data "0=On" and "1=Off" of Display On/Off status read out is inverted with the Display On/Off instruction data of "1=On" and "0=Off".

RESET: Indicate the initializing by RES signal or reset instruction.

0:

1: Initialization Period

#### (e) Write Display Data

This instruction writes the 8-bit data on the data bus into the Display Data RAM. The column address increases "1" automatically after data writing, therefore, the MPU can write the 8-bit data into the Display Data RAM continuously without any address setting after the start address setting.

|     |    | <u>R/W</u> |    |    |    |       |      |    |    |    |

|-----|----|------------|----|----|----|-------|------|----|----|----|

| -A0 | RD | WR         | D7 | D6 | D5 | D4    | Dз   | D2 | D1 | D٥ |

| 1   | 1  | 0          |    |    |    | WRITE | DATA |    |    |    |

#### (f) Read Display Data

This instruction reads out the 8-bit data from Display Data RAM addressed by the column and page address. The column address increase "1" automatically after data reading out, therefore, the MPU can read out the 8-bit data from the Display Data RAM without any address setting after the start address setting. One time of dummy read must operate after column address set as the explanation in "(5-5) Access to the Display Data RAM and Internal Register". In the serial interface mode, the display data is not read out.

|   | Α0 | RD | R/W<br>WR | <b>D</b> 7 | D6 | D5 | D4   | Dз   | D2 | D1 | Do |

|---|----|----|-----------|------------|----|----|------|------|----|----|----|

| L | 1  | 0  | 1         |            |    |    | READ | DATA |    |    |    |

#### (g) ADC Select

This instruction set the correspondence of column address in the Display Data RAM and segment driver output. (See Fig. 1.) By this instruction, the order of segment output can be changed by the software, and no restriction of the LSI placement against the LCD panel.

| 0  | 1  | 0         | 1  | 0  | 1  | 0  | 0  | 0  | 0  | D  |

|----|----|-----------|----|----|----|----|----|----|----|----|

| Α0 | RD | R/W<br>WR | D7 | D6 | D5 | D4 | Dз | D2 | D1 | Do |

D 0 : Clockwise Output (Normal)

1: Counterclockwise Output (Inverse)

#### (h) Normal or Inverse On/Off Set

This instruction changes the condition of display turn on and off as normal or inverse. The contents of Display Data RAM is not changed by this instruction execution.

| Α0 | RD | R/W<br>WR | D7 | D6 | D5 | D 4 | Dз | D2 | D1 | D٥ |

|----|----|-----------|----|----|----|-----|----|----|----|----|

| 0  | 1  | 0         | 1  | 0  | 1  | 0   | 0  | 1  | 1  | D  |

D 0 : Normal RAM data "1" correspond to "On"

1 : Inverse RAM data "0" correspond to "On"

## (i) Whole Display On

This instruction turns on the all pixel independent of the contents of the Display Data RAM. In this time, the contents of Display Data RAM is not change and kept. This instruction takes precedence over the "Normal or Inverse On/Off Set Instruction".

| Α0 | RD | WR | D7 | D6 | D5 | D4 | Dз | D2 | D1 | D٥ |

|----|----|----|----|----|----|----|----|----|----|----|

| 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | D  |

D 0 : Normal Display

1: Whole Display turn on

When Whole Display On Instruction is executed in the Display Off status, the internal circuits go to the power save mode (refer to the (s) Power Save).

## (j) Icon Display

This instruction set the 1/33 duty for the Icon Display. The COMI terminal operate as COM32 and output the icon display data stored in Do of Display Data RAM page 4 (refer to the Fig. 1).

| Γ | 0  | 1               | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | D  |

|---|----|-----------------|----|----|----|----|----|----|----|----|----|

|   | Α0 | $\overline{RD}$ | WR | D7 | D6 | D5 | D4 | Dз | D2 | D1 | Do |

D 0 : 1/32 Duty 1 : 1/33 Duty

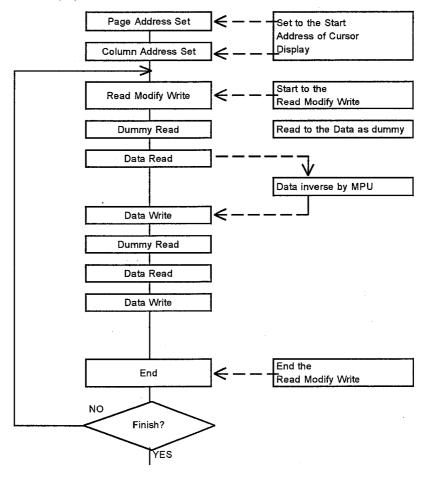

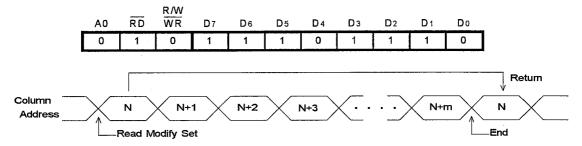

#### (k) Read Modify Write

This instruction sets the Read Modify Write Mode for the column address increment control. In mode of the Read Modify Mode Write, the column address increases "1" automatically when the Display Data Write Instruction is executed, but the address does not change when the Display Data Read Instruction is executed. This status is continued until End instruction execution. When the End instruction is input., the column address goes back to the start address before the Read Modify Write instruction input. This function reduces the load of MPU for repeating the display data change in the fixed area (ex. cursor blink).

| ľ | 0  | 1  | 0  | 1  | 1  | 1  | 0  | 0  | 0              | 0  | 0  |

|---|----|----|----|----|----|----|----|----|----------------|----|----|

|   | ΑO | RD | WR | D7 | D6 | D5 | D4 | Dз | D <sub>2</sub> | D1 | Do |

Note) In mode of the Read Modify Write, any instructions except for Column Address Set can execute.

## (I) Sequence of cursor blink display

New Japan Radio Co., Ltd.

#### (m) End

This instruction release the Read Modify Write mode and the column address back to the address where the read modify write mode setting.

#### (n) Reset

This instruction executes the following initialization.

#### Initialization

- 1 Set the Address (00)H into the Column Address Counter.

- 2 Set the page "0" into the Page Address Register.

- 3 Select the D3 of the Output Assignment Register to "0".

- 4 Set 0 to the EVR Register to (00)H.

In this time, the Display Data RAM is not influenced.

| Α0 | RD | WR | D7 | D6 | D5 | D 4 | Dз | D <sub>2</sub> | D1 | Do |

|----|----|----|----|----|----|-----|----|----------------|----|----|

| 0  | 1  | 0  | 1  | 1  | 1  | 0   | 0  | 0              | 1  | 0  |

The reset signal input to the RES terminal (hardware reset) must be input for the power on initialization. Reset Instruction does not perform completely in stead of hardware reset using the RES terminal.

#### (o) Output Assignment Register

This instruction sets the common driver scanning order.

A3: Set the scanning order. (Refer to 1-6)

#### (p) Internal Power Supply

This instruction set the condition of the internal Power Supply On/Off. Step up circuits, Voltage Regulator and Voltage Follower are operate at On. To operate the step up circuits, the oscillation circuits must be operating.

| A0 | RD | R/W<br>WR | <b>D</b> 7 | D6 | D5 | D 4 | Dз | D2 | D1 | Do |

|----|----|-----------|------------|----|----|-----|----|----|----|----|

| 0  | 1  | 0         | 0          | 0  | 1  | 0   | 0  | 1  | 0  | D  |

D 0 : Internal Power Supply Off

1: Internal Power Supply On

The internal Power Supply must be Off when external power supply using.

#### (q) LCD Driving Voltage Set

This instruction controls LCD driving waveform output through the COM/SEG terminals.

|   | Α0 | RD | R/W<br>WR | D7 | D6 | D5 | D4 | Dз | D2 | D1 | Do |

|---|----|----|-----------|----|----|----|----|----|----|----|----|

| I | 0  | 1  | 0         | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 1  |

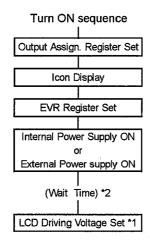

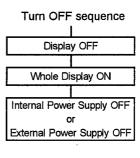

The NJU6578 contains low power LCD driving voltage generator circuit reducing own operation current. Therefore, it requires the following sequence procedures at power on for power source stabilized operation.

#### LCD driving power supply ON/OFF sequences

The following sequences are required when the power supply is turned On/Off.

When the power supply is turned on again after the turn off (by the power save instruction), the power save release sequence ((s)Power Save) is required.

- \*1 This instruction is required in both cases of the internal and external power supply.

Until "LCD driving voltage Set" execution, NJU6578 operating current is higher than usual state and all COM/SEG terminals output VDD level continuously.

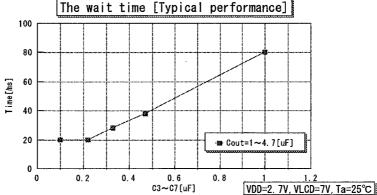

- \*2 The wait time depends on the C3 to C7, Cour capacitors (refer (4) (d)Fig.4), VDD and VLcD voltage.

Therefore it requires the actual evaluation using the LCD module to get the correct time. (Refer to the following graph.)

#### (r) EVR Register Set

This instruction controls voltage adjustment circuits of internal LCD power supply and changes LCD driving voltage "V5". Finally, it adjusts the contrast of LCD display. By setting a data into EVR register. V5 output voltage selects one condition out of 16-voltage conditions. The range of V5 voltage is adjusted by setting external resistors as mentioned in "(4)(b) Voltage Adjust Circuits".

| A0 | RD<br>1 4 | WR | D7 | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D3 | D <sub>2</sub> | D1 | D <sub>0</sub> |

|----|-----------|----|----|----------------|----------------|----------------|----|----------------|----|----------------|

| U  | 1         |    | 3  | כ              | U              | U              | A3 | A2             | A1 | A0             |

| Аз | <b>A</b> 2 | A1 _ | Ao | VLCD |

|----|------------|------|----|------|

| 0  | 0          | 0    | 0  | Low  |

|    |            | :    |    | :    |

|    |            | :    |    | :    |

| 1  | 1          | 1    | 1  | High |

VLCD=VDD-V5 When EVR doesn't use, set the EVR register to (0,0,0,0).

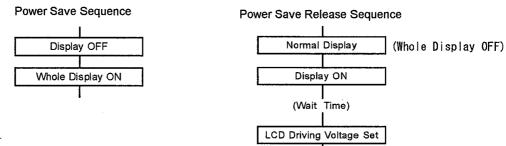

#### (s) Power Save(Dual Command)

When both of Display Off and Whole Display On are executed, the internal circuits go to the power save mode and the operating current is reduced as same as the stand by current.

The internal status in the Power Save Mode is shown in follows;

- ① Stop the Oscillation Circuits and Internal Power Supply Circuits operation.

- ② Stop the LCD driving. Segment and Common drivers output VDD level.

- ③ Keep the display data and operating mode just before the power save mode.

- 4 All of LCD driving bias voltage fix to the VDD level.

The power save and its release perform according to the following sequences.

- \*1 In the power save sequence, the power save mode is started after the second instruction "whole Display ON".

- \*2 In the power save release sequence, the power save mode is released after the Normal Display instruction (Whole display OFF).

- The instruction of display ON is input at any timing after the instruction of normal display in power save release sequence.

- \*3 Until "LCD driving voltage set to ON" execution, NJU6578 operating current is higher than usual state and all COM/SEG terminals output VDD level continuously.

- \*4 In case of the external power supply for LCD driving, it should be turned off and made condition like as disconnection or connection to VDD before the power save mode or at the same time. In this time, Vout terminal should be made condition like as disconnection or connection to the lowest voltage of the system. (V5 level from the external power supply.)

#### (4) Internal Power Supply

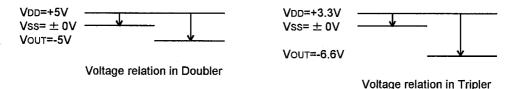

#### (a) Voltage tripler

Three times negative voltage (VDD common) of the voltage VDD-Vss is output from VouT terminal when connecting three capacitor between C1+ and C1-, C2+ and C2-, Vss and VouT. In case of the voltage doubler operation, connect the two capacitor between C2+ and C2-, Vss and VouT, then connect the C1+ and C2+ terminals. Step up circuits like as Voltage Tripler or Doubler using a oscillation circuits output as its clock signal, therefore, the oscillation circuits operation is required when step up operation. The voltage relation regarding the step up circuits is shown in below. When voltage tripler operation, the operation voltage of VDD should be less than 3.3V.

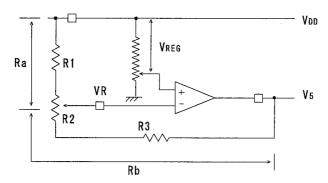

## (b) Voltage Adjust Circuits

The step up voltage of Vout output from V5 through the voltage adjust circuits for LCD driving. The output voltage of V5 is adjusted by changing the Ra and Rb within the range of | V5 | < | Vout |. The output voltage is calculated by the following formula.

VLCD = VDD-V5 = (1+Rb/Ra)·VREG·····(1)

Fig.3

The voltage of VREG is a standard voltage produced from built-in bleeder resistance. And VREG is possible to be fine-adjusted by EVR functions mentioned in (c).

For fine-adjustment of V5, R2 as variable resistor, R1 and R3 as fixed constant should be connected to VDD terminal, VR and V5, as shown in Fig3.

#### [ Design example for R1, R2 and R3 / Reference ]

- R1+R2+R3=5M Ω (Determined by the current flown between VDD-V5)

- Variable voltage range by the R2. -3V ~ -4.5V (VLCD=VDD-V5 → 6.0V ~ 7.5V) (Determined by the LCD electrical characteristics)

- VREG=3V(In case of EVR=(0F)H)

- R1, R2 and R3 are calculated by above conditions and the formula of 1 to mentioned below: R1=2.0M  $\Omega$  , R2=0.5M  $\Omega$  , R3=2.5M  $\Omega$

- \* If the power supply voltage between VDD and Vss changes, V5 changes too. Therefore the power supply voltage should be stabilized for V5 stable operation.

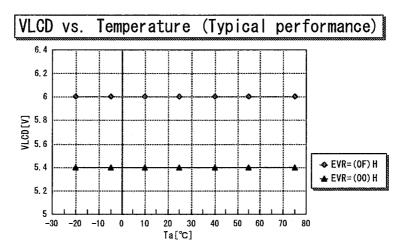

(c) Contrast Adjustment by using the EVR function

The EVR controls voltage of VREG by instruction and changes voltage of V5.

As result, LCD display contrast is adjusted by V5. The EVR selects a voltage of VREG in the following 16 conditions by setting 4bits data in to the EVR register.

In case of EVR operation, T<sub>1</sub> terminal and T<sub>2</sub> require to set couples of value as (L,L), (L,H) and (H,L) excepting for (H,H) and the internal power supply must turn on by instruction.

| E۱             | /R register | VREG [V]              | VLCD |

|----------------|-------------|-----------------------|------|

| (00)н          | (0,0,0,0)   | (135/150) · (VDD-Vss) | Low  |

| (01)H          | (0,0,0,1)   | (136/150) · (VDD-Vss) | :    |

| (02)н          | (0,0,1,0)   | (137/150) · (VDD-Vss) | :    |

| :              | :           | :                     | :    |

| :              | :           | :                     | :    |

| ( <b>0</b> D)н | (1,1,0,1)   | (148/150) • (VDD-Vss) | :    |

| (0Е)н          | (1,1,1,0)   | (149/150) • (VDD-Vss) | :    |

| (0F)н          | (1,1,1,1)   | (150/150) • (VDD-Vss) | High |

Adjustable range of the LCD driving voltage by EVR function using

The adjustable range is decided by the power supply voltage VDD and the ratio of external resistors Ra and Rb. [Design example for the adjustable range / Reference]

- Condition VDD=3.0V, Vss=0V

Ra=1M  $\Omega$ , Rb=1M  $\Omega$  (Ra:Rb=1:1)

The adjustable range and the step voltage are calculated as follows in the above condition.

In case of setting (00)H in the EVR register,

VLCD = ((Ra+Rb)/Ra) · VREG

$= (2/1) \cdot [(135/150) \cdot 3.0]$

= 5.4V

In case of setting (0F)H in the EVR register,

$V_{LCD} = ((Ra+Rb)/Ra) \cdot V_{REG}$

$= (2/1) \cdot [(150/150) \cdot 3.0]$

= 6.0V

|                  | Min.(00)н Ма | х.(0F)н |

|------------------|--------------|---------|

| Adjustable Range | 5.4******6.0 | [V]     |

| Step Voltage     | 40           | [mV]    |

\*) The VLCD operating temperature. Please refer to the following graphs.

(conditions) VDD = 3V

$${\rm Ra=1M~\Omega} \; , \; {\rm Rb=1M~\Omega} \; (\; {\rm Ra:Rb=1:1} \; )$$

Voltage tripler

#### (d) LCD Driving Voltage Generation Circuits

The LCD driving bias voltage of V1,V2,V3,V4 are generated internally by dividing the V5 voltage with the internal bleeder resistance. And it is supplied to the LCD driving circuits after the impedance conversion with voltage follower circuit.

As shown in Fig. 4, Five capacitors are required to connect to each LCD driving voltage terminal for voltage stabilizing. And the value of capacitors C3, C4, C5, C6 and C7 are determined depending on the actual LCD panel display evaluation.

#### Using the internal Power Supply

#### Using the external Power Supply

Reference set up value

VLCD = VDD - V5 ≒6.0 ~7.5V

| item     | Value         |

|----------|---------------|

| Cour     | 4.7 ~ 10 μF   |

| C1,C2    | 4.7 ~ 10 μF   |

| C3 to C7 | 0.1 ~ 0.47 μF |

| R1       | 2.0M Ω        |

| R2       | 0.5M Ω        |

| R3       | 2.5M Ω        |

Fig. 4

When Vss > V5 --- VouT=V5 When Vss  $\leq$  V5 --- VouT=Vss

<sup>\*1</sup> Short wiring or sealed wiring to the VR terminal is required due to the high impedance of VR terminal.

<sup>\*2</sup> Following connection of VouT is required when external power supply using.

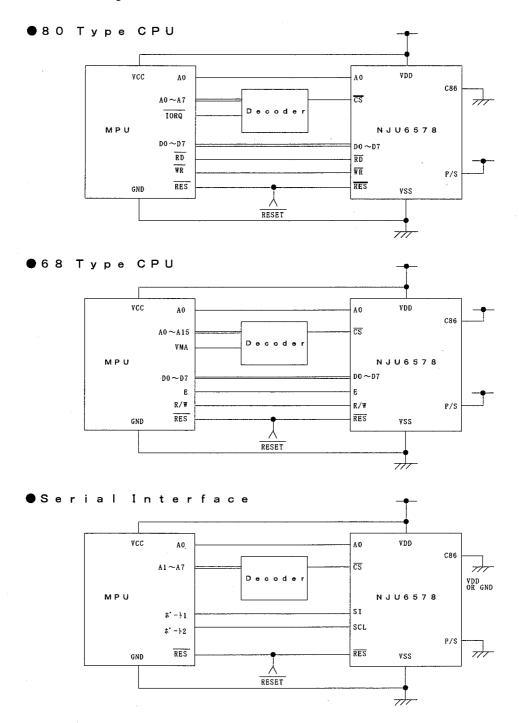

#### (5) MPU Interface

#### (5-1) Interface type selection

NJU6578 interfaces with MPU by 8-bit bi-directional data bus (D7 to D0) or serial interface (SI). The 8 bit parallel or serial interface is determined by a condition of the P/S terminal connecting to "H" or "L" level as shown in Table 5. In case of the serial interface, status and RAM data read out operation is impossible.

| -   |   |   |   | - |

|-----|---|---|---|---|

| - T | ~ | n | 0 |   |

|     |   |   |   |   |

| P/S | Туре     | ĊŚ | A0 | RD | WR | C86 | SI | SCL | D0~D7 |

|-----|----------|----|----|----|----|-----|----|-----|-------|

| Н   | Parallel | CS | A0 | ŔĎ | WR | C86 | -  | -   | D0~D7 |

| L   | Serial   | ĊŚ | Α0 | -  | -  | -   | SI | SCL | -     |

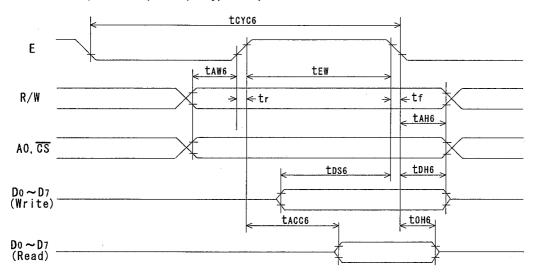

#### (5-2) Parallel Interface

The NJU6578 interfaces to 68 or 80 type MPU directly when the parallel interface (P/S="H") is selected. 68 type MPU or 80 is determined by the condition of C86 terminal connecting to "H" or "L" as shown in table 6.

Table 6

| C86 | Туре        | ĊS | A0 | RD | WR  | D0~D7 |

|-----|-------------|----|----|----|-----|-------|

| Н   | 68 type MPU | CS | A0 | E  | R/W | D0~D7 |

| L   | 80 type MPU | ĊŚ | A0 | RD | WR  | D0~D7 |

## (5-3) Discrimination of Data Bus Signal

The NJU6578 discriminates the mean of signal on the data bus by the combination of A0, E, R/W, and  $(\overline{RD}, \overline{WR})$  signals as shown in Table 7.

Table 7

| Common | 68 type | 80 | type | Cupation                             |  |

|--------|---------|----|------|--------------------------------------|--|

| A0     | R/W     | RD | WR   | Function                             |  |

| 1      | 1       | 0  | 1    | Read Display Data                    |  |

| 1      | 0       | 1  | 0    | Write Display Data                   |  |

| 0      | 1       | 0  | 1    | Status Read                          |  |

| 0      | 0       | 1  | 0    | Write into the Register(Instruction) |  |

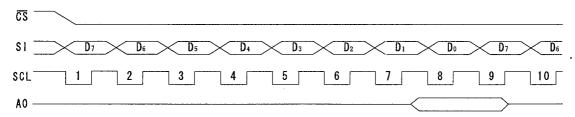

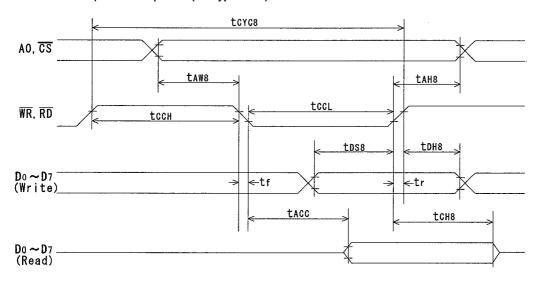

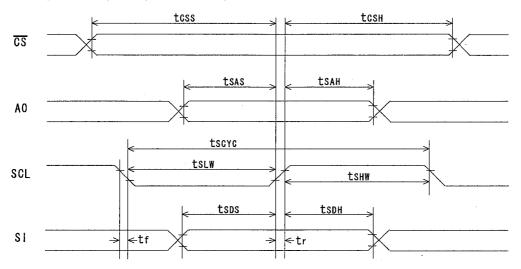

### (5-4) Serial Interface.(P/S="L")

Serial interface circuits <u>consist</u> of 8 bits shift register and 3 bits counter. SI and SCL input are activated when the chip select terminal CS set to "L" and P/S terminal set to "L". The 8 bits shift register and 3 bits counter are reset to the initial condition when chip is not selected. The data input from SI terminal is MSB first like as the order of D7,D6,····D0, and the data are entered into the shift register synchronizing with the rise edge of the serial clock SCL. The data in the shift register are converted to parallel data at the 8th serial clock rise edge input. Discrimination of the display data or instruction of the serial input data is executed by the condition of A0 at the 8th serial clock rise edge. A0="H" is display data and A0="L" is instruction. When RES terminal becomes "L" or CS terminal becomes "H" before 8th serial clock rise edge, NJU6578 recognizes them as a instruction data incorrectly. Therefore a unit of serial data must be structured by 8-bits. The time chart for the serial interface is shown in Fig. 5. To avoid the noise trouble, the short wiring is required for the SCL input.

Note) The read out function, such as the status or RAM data read out, is not supported in this serial interface.

Fig.5