# \_\_\_\_\_. Application Engineering Dep.

**NEC Corporation** 1st edition: June 15, 2000

## NP42B1MF01 Data Sheet

106 cm (42 type), Wide screen (853 x 480 Pixels), Digital Module Digital RGB signal, 8bits signal each

#### **DESCRIPTION**

The NP42B1MF01 is a 42-inch wide color plasma display module with a resolution of 853(H)x480(V) pixels. The display offers vibrant colors we reproduced in a thin and low profile package. This device uses AC plasma technology by NEC and includes an 8-bit of digital video signal interface for each RGB color.

#### **FEATURES**

O Applied Capsulated Color Filter (CCF) technology, developed at NEC, which offers a high quality image match for CRT display. To offer remarkably pure colors, the color plasma display panel uses extremely clear, thin capsulated color filters to cut unnecessary light as the plasma discharges.

O Peak luminance of 500cd/m2 (typical value) is achieved through a new driving method, which

offers extremely vivid image with good contrast.

O Applied Peak Luminance Enhancement (PLE) function that enables the display to operate with the ideal contrast. The PLE function makes it possible to adjust the average luminance level of the PDP display automatically in accordance with the average luminance level of an input video signal.

#### **APPLICATIONS**

- O Wide Screen TV (aspect ratio 16:9)

- O Public Information Display

- O Video Conference Systems

- O Retail

- O Education and Training Systems

The information in this document is subject to change without notice.

## STRUCTURE AND PRINCIPLE OPERATION OF PLASMA DISPLAY

In a Plasma Display Panel, Row and Column electrodes are placed between two glass substrates. A rare gas is then filled between each substrate. When a high voltage is applied to these electrodes, the gas is activated resulting in the radiation of ultraviolet light, similar to the operation in fluorescent lamps. These ultraviolet rays then activate phosphor that has been coated on the inside of the glass substrate, and visible light is emitted from the panel.

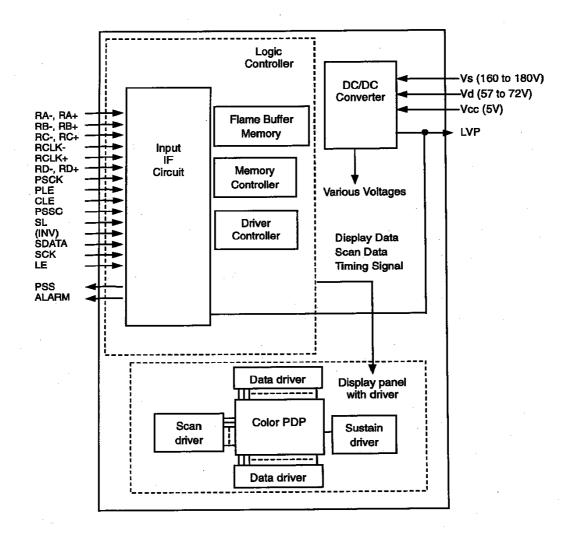

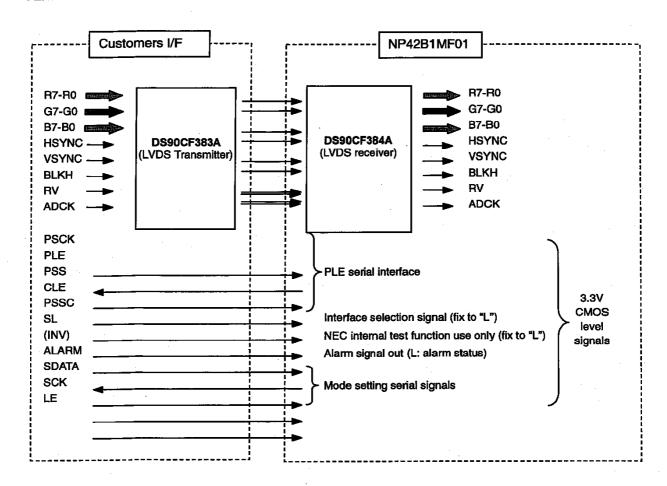

## ELECTRICAL INTERFACE OF PLASMA DISPLAY

NP42B1MF01 requires 8 bits of digital video signals for each RGB color. For the signal inputs, serial interface (LVDS video signal) is prepared in the module. In addition to the video signals, synchronous signals, mode control signals and 3 different DC voltages are required to operate the display.

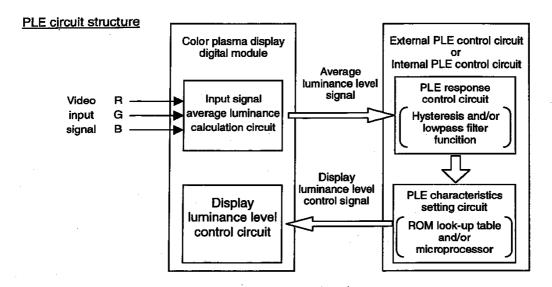

This plasma display module has a "PLE" (Peak Luminance Enhancement) function that adjusts the luminance and contrast to the suitable value in accordance with the input video signal level variance, so that images can be displayed with the ideal luminance and contrast.

#### **BASIC CONFIGURATION**

Technical Document Number: 941-1H0038 3/31

1st edition: June 15, 2000

#### **GENERAL SPECIFICATION**

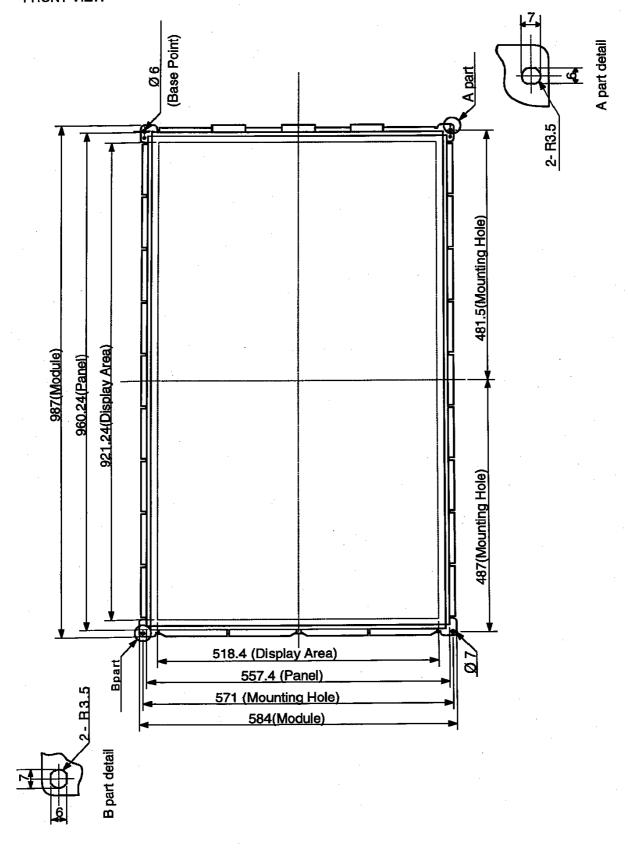

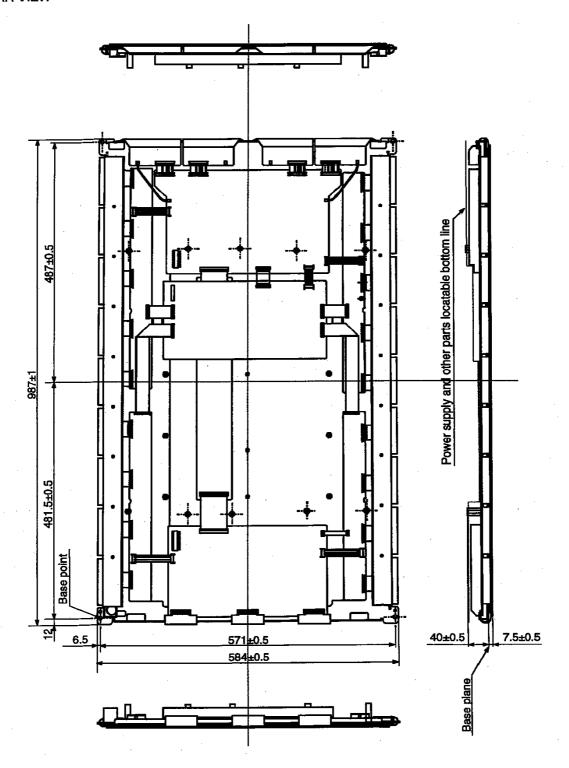

| Display area         | 921(H) x 518(V) mm                                                               |

|----------------------|----------------------------------------------------------------------------------|

| Outline dimensions   | 987(W) x 584(H) x 48(D) mm                                                       |

| Weight               | 15 kg                                                                            |

| Aspect ratio         | 16:9                                                                             |

| Number of pixels     | 853(H) x 480(V) (1pixel = 3 RGB cells)                                           |

| Pixel pitch          | 1.08 (H) x 1.08(V) mm                                                            |

| Color arrangement    | RGB vertical stripes                                                             |

| Number of gradations | 256 steps for each RGB                                                           |

| Peak luminance       | 500cd/m² typical Video signal*, 1/25 white window, PLE** mode set to the maximum |

### **OPERATION ENVIRONMENTAL CONDITIONS**

| Temperature          | 0 to 50 °C (with forced-air cooling) |

|----------------------|--------------------------------------|

| Humidity             | 20 to 80% RH (without condensation)  |

| Atmospheric pressure | 800 to 1100 hPa                      |

## STRAGE ENVIRONMENTAL CONDITIONS

| Temperature          | -20 to 60 °C                        |

|----------------------|-------------------------------------|

| Humidity             | 10 to 90% RH (without condensation) |

| Atmospheric pressure | 700 to 1100 hPa                     |

#### **MECHANICAL TEST CONDITIONS**

| Vibration (operating)     | 4.9m/s <sup>2</sup> (0.5 G), 10 to 100 Hz, 3 directions, 10 minutes each |

|---------------------------|--------------------------------------------------------------------------|

| Vibration (non-operating) | 4.9m/s <sup>2</sup> (0.5 G), 10 to 100 Hz, 3 directions, 2 hours each    |

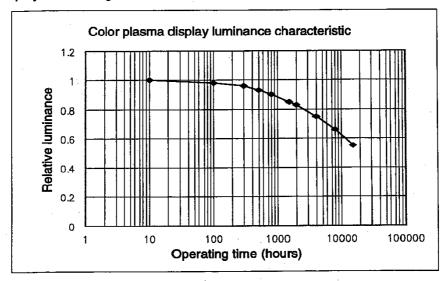

## LIFE EXPECTANCY

More than 10,000 hours of continuous operations (Time when the luminance decreased to half to the initial)

Signal of EUTV, fv = 59.94 Hz and fh = 31.47 kHz

See PLE (Peak Luminance Enhancement) description.

## **POWER INPUT AND OUTPUT**

| 1 | Sustain | <b>Power</b> | Sup | ply |

|---|---------|--------------|-----|-----|

|---|---------|--------------|-----|-----|

| <u> </u>                                            |         | Table 1. Power Output                                |      |      |      |       |

|-----------------------------------------------------|---------|------------------------------------------------------|------|------|------|-------|

| Item                                                | Symbol  | Condition and Remarks                                | Min. | Тур. | Max. | Unit  |

| Absolute Maximum                                    |         |                                                      |      |      | 200  | V     |

| Voltage                                             | Vs      | Dependent on the characteristics of each PDP (Note1) | 160  |      | 180  | V     |

| Voltage Stability                                   |         |                                                      |      |      | ±1.0 | %     |

| Average Current<br>(Note2)                          | ls-a    | Under normal PLE operation                           | 0.1  |      | 2.0  | А     |

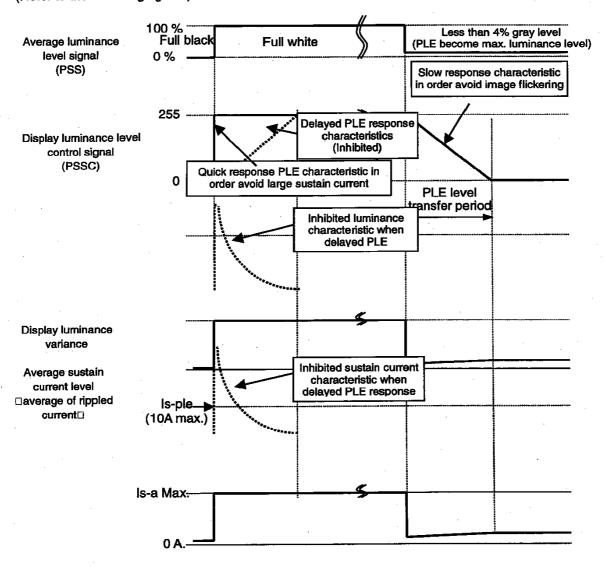

| Average current at inhibited PLE operation (Note 2) | Is-ple  | (Reference value)<br>(Note3)                         |      |      | 10   | A     |

| Peak Current                                        | ls-peak |                                                      |      |      | 15   | Α     |

| Voltage Regulation                                  |         | At peak current                                      |      |      | 5    | V     |

| Ripple and Noise                                    |         | *******                                              |      |      | 500  | mVp-p |

Note1: Voltage should be set to a specified value, which is located on a label attached to the module. Note2: Average of rippled current.

Note3: See PLE (Peak Luminance Enhancement) description.

Current when PLE is set to maximum luminance level with full white image, or when PLE has a delayed response and image is changed from full black to full white.

2) Data Power Supply

|                         |         | Table 2. Data Power Supply                           |       |       |      |      |

|-------------------------|---------|------------------------------------------------------|-------|-------|------|------|

| Item                    | Symbol  | Condition and Remarks                                | Min.  | Тур.  | Max. | Unit |

| Absolute Maximum        |         |                                                      |       | ***** | 90   | V    |

| Voltage                 | Vd      | Dependent on the characteristics of each PDP (Note1) | 57    |       | 72   | V    |

| Voltage Stability       |         |                                                      |       |       | ±1.5 | %    |

| Average Current (Note2) | ld-a    | Varied correspondence to the<br>Image                | 0.005 |       | 2.0  | А    |

| Peak Current            | ld-peak |                                                      |       |       | 5    | A    |

| Ripple and Noise        |         |                                                      |       |       | 300  | mVp- |

Note1: Voltage should be set to a specified value, which is located on a label attached to the module. Note2: Average of rippled current.

3) Logic Power Supply

|                  |          | Table 3. Logic Power Supply | ,    |      |      |       |

|------------------|----------|-----------------------------|------|------|------|-------|

| Item             | Symbol   | Condition and Remarks       | Min. | Тур. | Max. | Unit  |

| Absolute Maximum |          |                             | 4.5  |      | 6.0  | ٧     |

| Voltage Range    | Vcc      |                             | 4.75 | 5.0  | 5.25 | ٧     |

| Current (Note1)  | Icc      |                             | 1.0  | 3.1  | 3.5  | Α     |

| Peak Current     | icc-peak |                             |      | 7.0  | 8.0  | Α     |

| Ripple           |          |                             |      |      | 30   | mVp-p |

| Noise            |          |                             |      |      | 300  | mVp-p |

Note1: Average of rippled current.

This module provides an automatic operation-stop function for internal malfunctions. When the module stops the operation, logic current may reduce to almost zero (0). Even if logic current becomes zero, applied voltage should be kept to less than 6.0 volts.

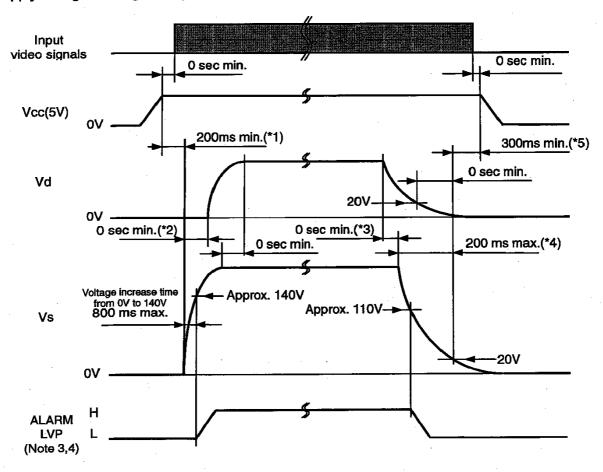

#### Supply Voltage and Signal Sequence

Note 1: Power ON/OFF sequence is as follows (refer to the above sequence diagram):

Power ON sequence:

Vcc ON→ 200ms min.(\*1) → Vs ON → 0sec min.(\*2) → Vd ON Power OFF sequence:

Vd OFF  $\rightarrow$  0sec min. (\*3)  $\rightarrow$  Vs OFF  $\rightarrow$  200ms max.(\*4)  $\rightarrow$  300ms min.(\*5)  $\rightarrow$  Vcc OFF (Caution)

If power sequence does not meet to above sequence diagram, PDP drivers may have a permanent damage.

In order to decrease Vs and Vd voltages quickly to satisfy above sequence diagram, forced discharge circuits are essential in the power supply.

Note 2: The power source for the Input signal circuit and Vcc can be switched on and off at the same time.

Note 3: LVP is the power supply shutdown output signal when the panel is broken and/or failure of internal power source in the PDP module.

Note 4: When the ALARM and LVP signals are "L" High voltage should be shut down. However, when Vcc is applied at first, ALARM and LVP signals are kept "L" until Vs is applied. In order to enable "high voltage power supply" operation, the initial ALARM and LVP signals' status "L" should be disregarded.

#### **INTERFACE SIGNAL**

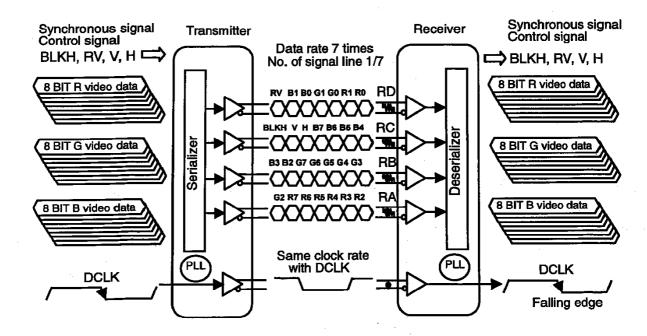

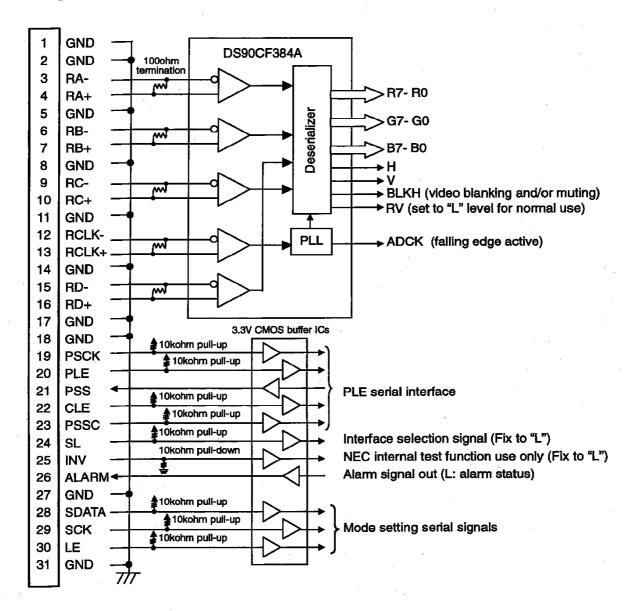

## SERIAL INTERFACE CONFIGURATION

Technical Document Number: 941-1H0038 8/31

1st edition: June 15, 2000

## **ELECTRICAL CHARACTERISTICS**

## 1) Interface Signals; Absolute Ratings

Common conditions: Ta=25°C, Vcc=5V

| · -               | Table 4.                                    | Absolute Ratings |        |             |      |

|-------------------|---------------------------------------------|------------------|--------|-------------|------|

|                   | Item                                        | Parameter        | Symbol | Ratings     | Unit |

| Input             | RA-, RA+, RB-, RB+, RC-, RC+,               | Input Voltage    | Vi     | -0.3 to 3.6 | V    |

|                   | RD-, RD+, RCLK-, RCLK+                      | Input current    | li     |             | mA   |

| Signals           | PSCK, PLE, CLE, PSSC, SL,<br>SDATA, SCK, LE | Input Voltage    | Vi     | -0.5 to 6.0 | V    |

|                   |                                             | Input current    | li .   | ±20         | mA   |

| Output<br>Signals |                                             | Output Voltage   | Vo     | -0.5 to 5.5 | ٧    |

|                   | PSS, ALARM                                  | Output current   | lo     | ±25         | mA   |

## 2) Interface Signals; Electrical Characteristics

Common conditions: Ta=25°C, Vcc=5V

|              | Table                     | 5. Electric     | al Characteristics                     |      |      |      |      |

|--------------|---------------------------|-----------------|----------------------------------------|------|------|------|------|

| Signal       | Signal Item               |                 | Conditions                             | Min. | Тур. | Max. | Unit |

|              | High Level Input Voltage  | V <sub>TH</sub> | V <sub>CM</sub> =1.2V                  |      |      | 100  | mV   |

| LVDS         | Low Level Input Voltage   | V <sub>TL</sub> | V <sub>CM</sub> =1.2V                  | -100 |      |      | mV   |

|              | Input Current             | I <sub>IN</sub> | V <sub>IN</sub> =+2.4/GND              |      |      | ±10  | μΑ   |

|              | High Level Input Voltage  | V <sub>IH</sub> |                                        | 2.0  |      |      | ٧    |

|              | Low Level Input Voltage   | V <sub>IL</sub> |                                        |      |      | 0.8  | ٧    |

| 3.3V<br>CMOS | Input Current             | Ii              | V <sub>i</sub> =V <sub>cc</sub> or GND |      |      | ±5.0 | μΑ   |

|              | High Level Output Voltage | VOH             | l <sub>o</sub> = -1mA                  | 2.2  |      |      | V    |

|              | Low Level Output Voltage  | V <sub>OL</sub> | l <sub>o</sub> =1mA                    |      |      | 0.5  | ٧    |

Technical Document Number: 941-1H0038 9/31

1st edition: June 15, 2000

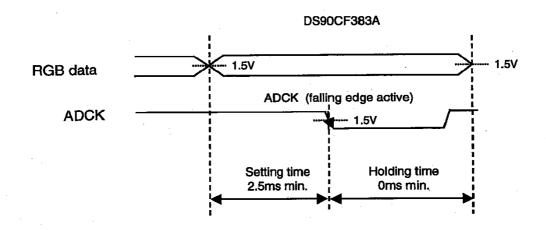

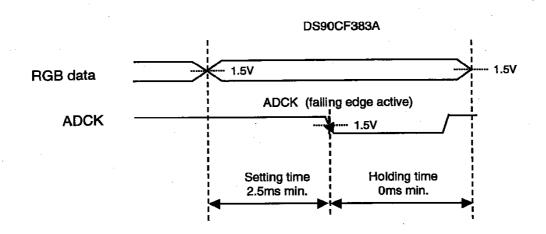

#### INPUT SIGNAL FUNCTION of LVDS transmitter (DS90CF383A)

|          | Table 6. Interface Signal Function           |                                          |  |  |  |  |

|----------|----------------------------------------------|------------------------------------------|--|--|--|--|

| Symbol   | Function                                     | (Remarks)                                |  |  |  |  |

| R7 to R0 | 8 bits red video signal (Note 1)             | (R7:MSB*, R0: LSB**)                     |  |  |  |  |

| G7 to G0 | 8 bits green video signal (Note 1)           | (G7:MSB*, G0:LSB**)                      |  |  |  |  |

| B7 to B0 | 8 bits blue video signal (Note 1)            | (B7:MSB*, B0:LSB**)                      |  |  |  |  |

| ADCK     | Clock for video signal                       | (latch the video signal at falling edge) |  |  |  |  |

| HSYNC    | Horizontal synchronous signal tw=4TADCK min. | (negative pulse)                         |  |  |  |  |

| VSYNC    | Vertical synchronous signal tw=200ns min.    | (negative pulse)                         |  |  |  |  |

| BLKH     | Video blanking and/or muting (Note 2)        | ("H" in blanking, muting)                |  |  |  |  |

| RV       | Reverse the RGB video data polarity          | (Set to "L" level for normal use)        |  |  |  |  |

\* MSB: Most Significant Bit

\*\* LSB: Least Significant Bit

Note 1: The RGB video signal should be compensated with Inverseγcircuit before input to the color plasma display module.

Note 2: While BLKH input is "H" level, all display area image turns to black color display.

INPUT SIGNAL FUNCTION PDP module (NP42B1MF01)

|        |     | Table 7. Interface Signal Function                                           |                          |

|--------|-----|------------------------------------------------------------------------------|--------------------------|

| Symbol | 1/0 | Function                                                                     | (Remarks)                |

| RA-    | 1   | Video signal input A-                                                        | LVDS signal              |

| RA+    | 1   | Video signal input A+                                                        | LVDS signal              |

| RB-    |     | Video signal input B-                                                        | LVDS signal              |

| RB+    | _   | Video signal input B+                                                        | LVDS signal              |

| RC-    | 1   | Video signal input C-                                                        | LVDS signal              |

| RC+    |     | Video signal input C+                                                        | LVDS signal              |

| RD-    | 1   | Video signal input D-                                                        | LVDS signal              |

| RD+    | _   | Video signal input D+                                                        | LVDS signal              |

| RCLK-  |     | Clock signal clock-                                                          | LVDS signal              |

| RCLK+  |     | Clock signal clock+                                                          | LVDS signal              |

| SDATA  |     | Mode setting serial data                                                     | (48-bit)                 |

| SCK    | 1   | Clock signal for SDATA                                                       |                          |

| LE     |     | SDATA write enable                                                           | ("L" in SDATA write)     |

| PSCK   | I   | Clock signal for PSS, PSSC serial data                                       | (latch in positive edge) |

| PLE    |     | PSS data latch enable                                                        | ("L" in PSS data read)   |

| PSS    | 0   | PLE average luminance signal                                                 | (10-bit)                 |

| CLE    | 1   | PSSC data write enable                                                       | ("L" in data write)      |

| PSSC   |     | PLE luminance control data                                                   | (8-bit)                  |

| SL     | I   | Interface selection signal                                                   | (Fix to "L")             |

| INV    |     | NEC internal test function use only                                          | (Fix to "L")             |

| ALARM  | O   | Alarm signal for panel broken and failure of internal power-source. (Note 1) | ("L" in alarmed status)  |

Note 1: When ALARM output turns to "L" level, high voltage power input (Sustain power supply: Vs, and Data power supply: Vd) should be switched off immediately. When glass panel is broken, high voltage may occur at the electrode section and cause electric shock. Failure of internal power-source cause over-power status and gives damage to the display panel and driver-circuits.

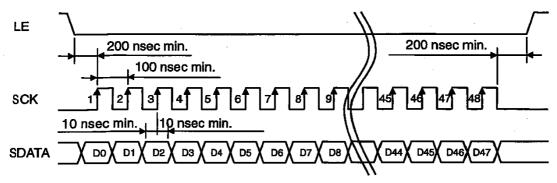

## Set-up of control mode signals and display position

#### Set-up Sequence:

- 1. Set LE to "L" level.

- 2. Enter the 48 bits of SDATA into the module synchronizing to the serial clock signal (SCK)

- 3. Set LE to "H" level.

- Note 1: SCK clock rate: 1MHz max.

- Note 2: Serial input data should be refreshed at least in every 5 or 6 seconds or less.

- Note 3: Serial input data (SDATA) is latched into the module at the falling edge of the VSYNC signal after "LE" signal is returned back to "H" level. When VSYNC is overlapped with the "LE" signal's "L" period, the serial data is latched with the next VSYNC timing.

- Note 4: When only 48 SCK clocks are entered while LE is "L" level period, SDATA become enable, If SCK clocks number is not 48, SDATA is not refreshed.

- Note 5: When powers are supplied to the module, serial data in the module has vague status. Therefore serial data should be refreshed after powered on.

| Mode s | etting signals |                                                 |                                                                                     |  |  |  |  |  |

|--------|----------------|-------------------------------------------------|-------------------------------------------------------------------------------------|--|--|--|--|--|

|        |                | ble8. Contents of SDATA (Mod                    |                                                                                     |  |  |  |  |  |

| SDATA_ | Signal name    | Function                                        | Remarks                                                                             |  |  |  |  |  |

| D0     | Spate bit      | Fix to "L" level                                |                                                                                     |  |  |  |  |  |

| D1     | CODE 2         | _                                               | PC(56 to 75Hz) Video(50Hz) PC, Video(56-64Hz) CODE2 L L L                           |  |  |  |  |  |

| D2     | CODE 1         | Subfield length selection bits                  | CODE1 L L H                                                                         |  |  |  |  |  |

| D3     | CODE 0         |                                                 | CODE0 L H L                                                                         |  |  |  |  |  |

| D4     | PRI M1         | NEC internal use                                | Fix to "H"                                                                          |  |  |  |  |  |

| D5     | PRI MO         | NEC internal use                                | Fix to "H"                                                                          |  |  |  |  |  |

| D6     | SAFEL          | NEC internal use                                | Fix to "L"                                                                          |  |  |  |  |  |

| D7     | LIFEH          | Switch for PLE luminance level                  | L: PLE normal operation H: Fix PLE to low luminance level for longer life operation |  |  |  |  |  |

| D8     | Spare bit      | Fix to "L" level                                |                                                                                     |  |  |  |  |  |

| D9     | SELFPLEH       | Switch for "Internal PLE" and<br>"External PLE" | H: Internal PLE control<br>L: External PLE control                                  |  |  |  |  |  |

| D10    | TSELB          | Switch for ADCK data latch timing               | (11.14.11.19.000 = 11.11.19.19.1                                                    |  |  |  |  |  |

| D11    | FV 2           | ]                                               | (Hz) 50 56-64 66 67-71 72-75<br>FV2 L L L H<br>FV1 L L H H L                        |  |  |  |  |  |

| D12    | FV 1           | Vertical frequency selection bits               | FV1 L H H L<br>FV0 L H L H L                                                        |  |  |  |  |  |

| D13_   | FV 0           |                                                 |                                                                                     |  |  |  |  |  |

| D14    | DISPLINE 2     |                                                 | line 400 480<br>  DL2                                                               |  |  |  |  |  |

| D15    | DISPLINE 1     | Display line number                             | DL1 L L                                                                             |  |  |  |  |  |

| D16_   | DISPLINE 0     |                                                 | DLO L H                                                                             |  |  |  |  |  |

| D17    | DISPDOT 2      |                                                 | Pixels 640 853<br>DD2 L L                                                           |  |  |  |  |  |

| D18    | DISPDOT 1      | Display pixel number/line                       | IDD1 L H                                                                            |  |  |  |  |  |

| D19    | DISPDOT 0      |                                                 | DDO E H                                                                             |  |  |  |  |  |

| D20    | VDELAY 256     | -                                               |                                                                                     |  |  |  |  |  |

| D21    | VDELAY 128     |                                                 |                                                                                     |  |  |  |  |  |

| D22    | VDELAY 64      |                                                 | Set the display start line numbers after the falling ed                             |  |  |  |  |  |

| D23    | VDELAY 32      | Display start vertical position                 | of the VSYNC.                                                                       |  |  |  |  |  |

| D24    | VDELAY 16      | Refer to the "Dv" in the table 9                | Range of setting line numbers: 0 to 511                                             |  |  |  |  |  |

| D25    | VDELAY 8       | Helel for the DA III the (SDIe a                | This number should not exceed the total line numbers                                |  |  |  |  |  |

| D26    | VDELAY 4       |                                                 | in one frame period (1V).                                                           |  |  |  |  |  |

| D27    | VDELAY 2       |                                                 | ·                                                                                   |  |  |  |  |  |

| D28    | VDELAY 1       |                                                 |                                                                                     |  |  |  |  |  |

| D29    | HDELAY 512     |                                                 |                                                                                     |  |  |  |  |  |

| D30    | HDELAY 256     |                                                 |                                                                                     |  |  |  |  |  |

| D31    | HDELAY 128     | -                                               | Set the display start pixel numbers after the falling                               |  |  |  |  |  |

| D32    | HDELAY 64      | ·                                               | edge of the HSYNC.                                                                  |  |  |  |  |  |

| D33_   | HDELAY 32      | Display start horizontal position               | Range of setting line numbers: 0 to 1023                                            |  |  |  |  |  |

| D34    | HDELAY 16      | Refer to the "Dh" in the table 9                | This number should not exceed the total line numbers                                |  |  |  |  |  |

| D35    | HDELAY 8       |                                                 | in one line period (1H).                                                            |  |  |  |  |  |

| D36    | HDELAY 4       |                                                 | In and makening finish                                                              |  |  |  |  |  |

| D37    | HDELAY 2       |                                                 |                                                                                     |  |  |  |  |  |

| D38    | HDELAY 1       |                                                 |                                                                                     |  |  |  |  |  |

| D39_   | HPOS 3         | Setting of horizontal display                   | Position Left Center Right                                                          |  |  |  |  |  |

| D40    | HPOS 2         | position in normal mode (640-                   | POS3 L L LHH H H H POS2 L L LH H H H                                                |  |  |  |  |  |

| D41 _  | HPOS 1         | pixel/line display). Display position           | NPOS1 LLHL.HH                                                                       |  |  |  |  |  |

| D42    | HPOS 0         | is adjustable by 2 pixel. steps.                |                                                                                     |  |  |  |  |  |

| D43    | MASKLEVEL 3    |                                                 | Level(%) 0.7 2.2 4.5 9 14 17.5 22.5 24 0 1.5 3 6 12 16 19 24                        |  |  |  |  |  |

| D44    | MASKLEVEL 2    | Gray level in black area                        | M 2                                                                                 |  |  |  |  |  |

| D45    | MASKLEVEL 1    | (Possible to set 0-24% of white                 | MIT LELLAHANCELIAHAN<br>MLO LEHHELHHELHHELHH                                        |  |  |  |  |  |

| D46    | MASKLEVEL 0    | level)                                          | MICO CEHHLLHHLLHHLLHH<br>MLL LHLHLHLHLHLHLH                                         |  |  |  |  |  |

| D47_   | Spare bit      | Fix to "L" level                                |                                                                                     |  |  |  |  |  |

| U+/    | 1 Opens 201    |                                                 | 4. · · · · · · · · · · · · · · · · · · ·                                            |  |  |  |  |  |

1st edition: June 15, 2000

Example of video signal input and signal timing

|               |    |                | Table 9.                             | Relat                 | ion Be                                | twee                     | n    | In            | pu | t V | /id           | ec   | S   | igı        | nal and M                                                                   | odu                   | le R                                     | G     | В             | Si  | gnal Inpu                                                                   | t   |       |             |        |   |

|---------------|----|----------------|--------------------------------------|-----------------------|---------------------------------------|--------------------------|------|---------------|----|-----|---------------|------|-----|------------|-----------------------------------------------------------------------------|-----------------------|------------------------------------------|-------|---------------|-----|-----------------------------------------------------------------------------|-----|-------|-------------|--------|---|

|               |    |                | Video                                | Signa                 | ı                                     |                          |      | -             |    |     |               |      |     |            | F                                                                           | RGB                   | Sig                                      | ne    | ıl            |     | •                                                                           |     |       |             |        |   |

|               |    |                |                                      |                       |                                       |                          |      |               | М  | ode | sig           | jnal | ı   |            | Norma<br>(Asp                                                               |                       | lay Mo<br>atio 4:                        |       |               |     | Full D<br>(Aspe                                                             |     |       |             |        |   |

|               | No | Signal<br>Name | Display<br>Resolution<br>(dot (line) | Vert<br>Freq.<br>(Hz) | Number<br>of Lines<br>In one<br>Frame | Horiz.<br>Freq.<br>(kHz) |      | ubfie<br>engt |    |     | rtica<br>veno |      | Lin | ne<br>nber | Recommended<br>dot-clock numbers<br>in one horizonial<br>synchronous signal | read<br>timin<br>sync | nei data<br>I start<br>g after<br>signal | 1     | Pixe<br>o./ti |     | Recommended<br>dot-clock numbers<br>in one horizontal<br>synchronous signal |     | start | No.         | Pixe   |   |

|               | ٠  |                |                                      | -                     |                                       |                          | CODE | E             | D  | Vľ  | ۷ľ            | ۷ĮI  | ᄔᆝᄔ |            | period<br>(Horiz. freq.: MHz)                                               | Dv                    | Dh                                       | D D 2 | D<br>D        | D 0 | period<br>(Horlz. freq.: MHz)                                               | Dv. | Dh    | D<br>D<br>2 | D<br>D | D |

|               | 1  | EUTV           | 853 🗆 480                            | 50.0                  | 525                                   | 26.25                    | L    | L             | н  | 4   | ւ             | ιŢι  | L   | Н          | 780 (20.48)                                                                 | 38                    | 128                                      | L     | L             | L   | 1040 (27.3)                                                                 | 38  | 171   | L           | н      | F |

| Video<br>mode | 2  | EDTV           | 853 □480                             | 59.94                 | 525                                   | 31.47                    | L    | н             | 니  | L   | L             | -11  | L l | _ н        | 780 (24.55)                                                                 | 35                    | 116                                      | L     | Ļ             | L   | 1040 (32.73)                                                                | 35  | 154   | L           | н      | Н |

|               | 3  | HDTV           | 853 🗆 480                            | 60                    | 1125/2                                | 33.75                    | L    | Н             | L  | 니   | L             | - 1  | L I | . Н        |                                                                             |                       |                                          |       |               |     | 1054 (35.57)                                                                | 40  | 113   | L           | H      | Н |

|               | 4  | NEC            | 640 □400                             | 56.4                  | 440                                   | 24.83                    | L    | L             | L  | -   | L             | 4    | 1   | . [-       | 848 (21.05)                                                                 | 33                    | 149                                      | L     | L             | L   | 1130 (28.06)                                                                | 33  | 199   | L           | н      | Н |

|               | 5  | NEC            | 640 □400                             | 70                    | 449                                   | 31.47                    | L    | L             | 니  | 니   | ні            | 4    | Ļ   | . [        | 800 (25.18)                                                                 | 36                    | 143                                      | L     | L             | L   | 1066 (33.55)                                                                | 36  | 191   | L           | Н      | ۲ |

|               | 6  | IBM            | 640 □400                             | 70                    | 449                                   | 31.47                    | L    | L             | L  | L   | н             | 4    |     | . .        | 800 (25.18)                                                                 | 36                    | 146                                      | L     | L             | L   | 1066 (33.55)                                                                | 36  | 195   | L           | Ή      | ۲ |

800 (25.18)

800 (25.18)

800 (25.18)

864 (30.24)

832 (31.5)

840 (31.5)

800 (31.5)

35

27 136

39 145

42 | 160

31

19

168

184

1066 (33.55)

1066 (33.55)

1066 (33.55)

1152 (40.32)

1109 (42.00)

1120 (42.00)

1067 (42.00)

35

27

39

42 213

31

19 245

181

224

192

- Note 1: Maximum data clock (ADCK) frequency is 50MHz.

Note 2: Maximum horizontal frequency in Video mode is 47 kHz

- Note 2: Maximum horizontal frequency in Video mode is 47 kHz

Note 3: Maximum horizontal frequency in PC mode is 70 kHz

31.47

35.00

37.86

37.5

39.38

525

525

525

500

Note 4: Vertical frequency range is 50Hz to 75Hz.

59.94

59.94

59.94

66.66

72.8

75

640 □480

640 □480

640 □ 480 640 □ 480

640 🗆 480

640 0480

640 □480

VGA

IBM

MAC

VESA

VESA

IBM

8

9 NEC

10

11

13

PC

- Note 5: D14 to D19 (Display lines number and Display pixel number/line) of serial input data should be set correctly according to the display data. If do not correct, PLE function is not operated correctly.

- Note 6: When one horizontal signal period is divided equally with the value of above "Recommended dot clock numbers in one horizontal period", the effective display width of the video signal becomes equal with the width of the screen width.

- When over-scan is required, this value should be adjusted to smaller value.

- Note 7: When one horizontal signal period is divided equally with the value of above "Recommended dot clock numbers in one horizontal period", Dv and Dh values in the same row gives the display image position at almost the center of the screen.

#### LVDS (FPDLINK) data transfer format

( As for detail of LVDS interface, please refer to www.national.com . )

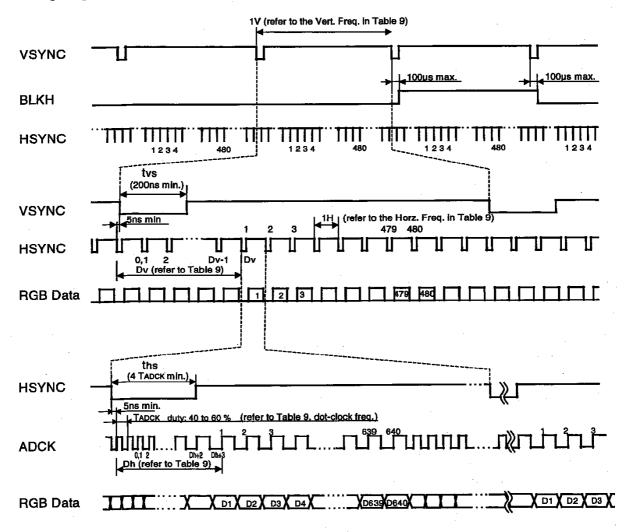

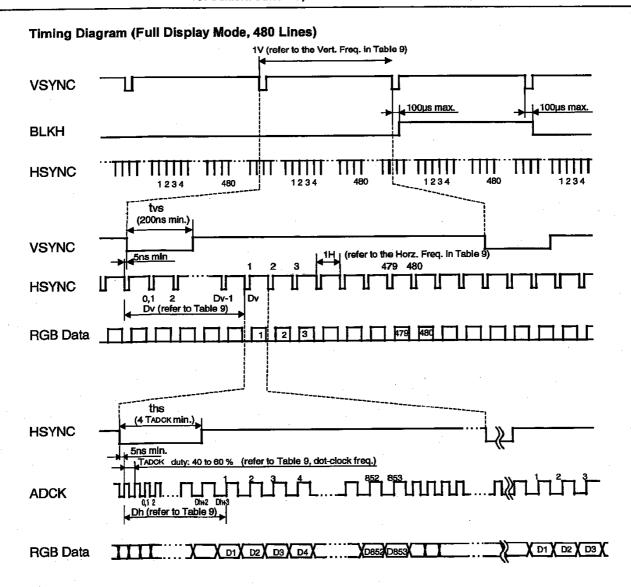

## [SERIAL INTERFACE] SIGNAL TIMING

Refer to the timing diagram on the following pages.

- Input video signal format is determined by Mode signal (refer to Table 9)

- "TADCK" shows 1 cycle period of ADCK.

- "tvs" shows negative pulse width of VSYNC.

- "tvh" shows negative pulse width of HSYNC.

- "1H" shows 1 cycle period of HSYNC (Horizontal Synchronous Signal).

- "1V" shows 1 cycle period of VSYNC (Vertical Synchronous Signal).

- "Dv" is a period between "leading-edge of the vertical synchronous pulses" and "valid RGB lines data read start timing"

- "Dh" is a period between "leading-edge of the horizontal synchronous pulse" and "valid RGB dots data read start timing"

- In case normal mode (640 dot mode) is selected, both sides are masked with gray patterns.

- In case 400 line is selected, upper 40 lines and lower 40 lines are masked with gray patterns.

## Timing Diagram (Normal Display Mode, 480 lines)

#### Interface connector pin assignment and input output circuits

Following shows the interface connector pin assingnment and input output circuits in the PDP module.

Type of serial interface connector

Module side connector: FI-TWE31PB-VF

Mating connector: FI-W31S (plug housing)

FI-C3-A1-15000 (contact)

Connector supplier: Japan Aviation Electronics Industry, Limited (JAE)

Fitting cable: AWG#28 to 32 twlst pair cable (Total cable assembly recommends to be shielded)

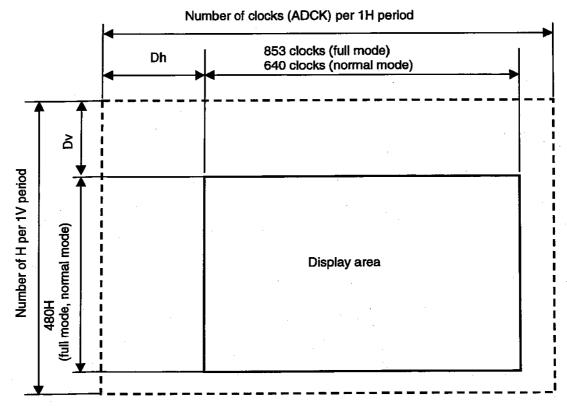

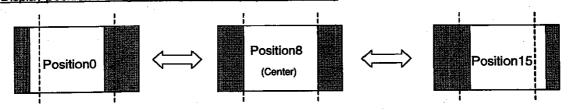

### Display position

The relation among Dv, Dh, and the display position is as shown below.

- 1) Setting range of Dv and Dh Dv: 9bit 0-511 line (HSYNC) Dh: 10bit 0-1023 dot (ADCK)

- 2) Limitation of number of clocks per 1H period normal mode: (Dh)+2+640 Number of clocks per 1H period 11bit+10bit = 3071 full mode: (Dh) +2+853 Number of clocks per 1H period 11bit+10bit = 3071

- 3) Limitation of number of HSYNC pulses per 1V period (Dv) +2+480 Number of HSYNC pulses per 1V period 2047 (HSYNC)

## Display position setting in normal modes (aspect ratio 4:3)

16 positions can be set by 2-pixel pitch through "Mode setting serial data".

### PLE (Peak Luminance Enhancement) FUNCTION

The PLE function makes it possible to increase the luminance level of the PDP display when the average luminance level of the input video signal is low. This PLE function reduces the maximum power by absorbing the luminance when the high-power-load-image is displayed, and results in a higher contrast level.

This plasma display module has following two modes. These two modes can be selected by the mode control signal.

- "Internal PLE" mode ---- Built-in PLE function in the PDP module itself.

This PLE mode realizes one of the best PLE characteristics without any additional circuit.

Therefore this mode is very convenient, and it is recommend to utilize this function actively.

- 2. "External PLE" mode --- Externally controlled PLE function from the customer's interface circuit. External PLE mode enables to make customer's original characteristics within the limitation range. The PLE characteristics is strongly related not only the luminance characteristics of plasma display module but also the power consumption and the generated heat, therefore it is required to obtain the acknowledgement of NEC concerning the external PLE characteristics to be set at the customer.

#### (Caution)

When use the external PLE function, please use within the limitation range. If external PLE characteristic is set outside of the limitation range, plasma display module may have damage. Any trouble caused by this incorrect operation is not included in the warranty

Power consumption and generated heat of plasma display module varies depending on the setting values of PLE characteristic. Therefore the temperature investigation and optimization of cooling design should be done in the state mounted in the plasma display set.

### **Characteristics of internal PLE**

When PDP module displays full white with maximum luminance, or when PLE characteristic has some delayed response and display image is changed from full black to full white, large sustain current (Ispeak: 10A max.) flows, and plasma display becomes over power status.

In the internal PLE function, when the "Average luminance level" increases, in order to avoid large sustain current flow and over power status, the "Display luminance level" is immediately reduced to the setting level with quick response. And when display load decreases, in order to avoid image flickering caused by the short term average luminance level's fluctuations, the "Display luminance level" is gradually move to the setting level with a slow response characteristic. (Refer to the following figures)

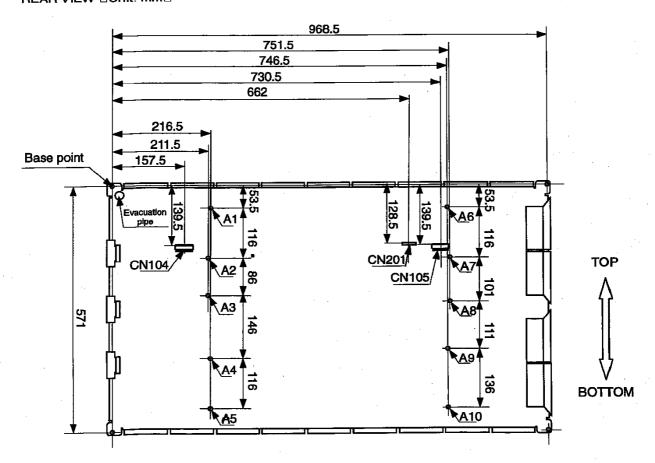

#### **CONNECTORS PIN ASSIGNMENT**

(For the connector position, please refer to the Rear View in the Outline Drawing)

#### 1. POWER !NPUT CONNECTORS

| Tab     | ole 10. Connector | CN104 Pin Assi | gnment |

|---------|-------------------|----------------|--------|

| Pin No. | Symbol            | Pin No.        | Symbol |

| 1       | LVP               | 2              | GND    |

| 3       | GND               | 4              | Vcc    |

| 5       | GND               | 6              | GND    |

| 7       | Vd                | 8              | N.C.   |

| 9       | Vs                | 10             | Vs     |

N.C.: non-connection pin.

Module side connector: B10PS-VH

Mating connector: VHR-10N (housing),

SVH-21T-P1.1(contact)

Connector supplier: J.S.T. TRADING COMPANY., LTD.

Fitting Cable: Equivalent to AWG#20

| Ta      | ble 11. Connector | CN105 Pin As | signment |

|---------|-------------------|--------------|----------|

| Pin No. | Symbol            | Pin No.      | Symbol   |

| 1       | Vs                | 2            | Vs       |

| 3       | N.C.              | 4            | Vd       |

| 5       | GND               | 6            | GND      |

| 7       | Vcc               | 8            | GND      |

| . 9     | GND               |              |          |

N.C.: non-connection pin.

Module side connector: B9PS-VH

Mating connector: VHR-9N (housing),

SVH-21T-P1.1 (contact)

Connector supplier: J.S.T. TRADING COMPANY, LTD.

Fitting Cable: Equivalent to AWG#20

(Note): If using a long cable, applied voltage may be dropped because of its resistance.

Specified voltage should be applied correctly at the input of the module side connector.

1st edition: June 15, 2000

## 2. SIGNAL INTERFACE CONNECTOR

| Ta      | able 12. Connector C | N201 Pin As | signment |

|---------|----------------------|-------------|----------|

| Pin No. | Symbol               | Pin No.     | Symbol   |

| 1       | GND                  | 2           | GND      |

| 3       | RA-                  | 4           | RA+      |

| 5       | GND                  | 6           | RB-      |

| 7       | RB+                  | 8           | GND      |

| 9       | RC-                  | 10          | RC+      |

| 11      | GND                  | 12          | RCLK-    |

| 13      | RCLK+                | 14          | GND      |

| 15      | RD-                  | 16          | RD+      |

| 17      | GND                  | 18          | GND      |

| 19      | PSCK                 | 20          | PLE      |

| 21      | PSS                  | 22          | CLE      |

| 23      | PSSC                 | 24          | SL       |

| 25      | INV                  | 26          | ALARM    |

| 27      | GND                  | 28          | SDATA    |

| 29      | SCK                  | 30          | LE       |

| 31      | GND                  |             |          |

Module side connector:

FI-TWE31PB-VF

Mating connector:

FI-W31S(housing),

Connector supplier:

FI-C3-A1-15000(contact)

pplier: Japan Aviation Electronics Industry, Limited (JAE)

AWG#28 to 32 twist pair cable

Fitting Cable:

(Total cable assembly recommends to be shielded.)

# MECHANICAL DRAWING (Unit: mm) FRONT VIEW

## MECHANICAL DRAWING (Unit: mm) REAR VIEW

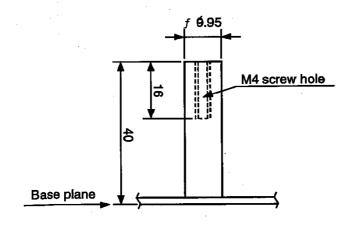

## STUDS AND CONNECTORS POSITION REAR VIEW Unit: mm

## SHAPE OF STUD (Unit: mm)

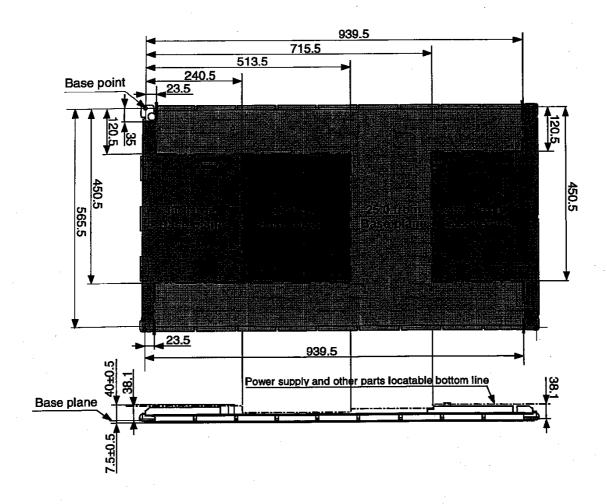

Locatable position of other parts or structures adjacent to the PDP module Rear view (Unit: mm)

1st edition: June 15, 2000

#### IMAGE STICKING CHARACTERISTICS

1) Image sticking

The fluorescent substance used in the plasma module loses its luminance with the lapse of lighting time.

This deterioration in luminance appears to be a difference in luminance in relation to the surroundings, and comes to be recognized as image sticking.

In other words, the image sticking is defined as follows: when the same pattern (of the fixed display) is displayed for a long time, a difference in luminance is caused around the lighting area and non-lighting area due to deterioration in the fluorescent substance.

When the present pattern is changed over to another one, the boundary comes to be seen between the lighting area and non-lighting area due to difference in luminance in the pattern shown shortly before changeover. If this condition is accumulated, the boundary or image sticking comes to be seen with the naked eyes.

2) Secular change in luminance

The life of luminance, defined as the reduction to half the initial level, is more than 10 thousand hours on average.

Conditions: All white (100% white) input at an ambient temperature of 25 °C.

However, this life time is not a guarantee value for life and luminance. It should be recognized simply as the data for reference.

3) Warranty

Image sticking and faults in luminance and picture elements are excluded from the warranty objects.

4) Cause of deterioration in luminance

A major possible cause of deterioration in luminance is damage in the fluorescent substance due to impact caused by ions generated at the time of plasma discharges.

5) Practical value for Image sticking

The relationship between integrated lighting time and luminance in this plasma module is described in the attached material. In particular, the deterioration in luminance tends to be accelerated up to 100 hours in the initial period. In the initial period, the fixed display of patterns particularly tends to cause image sticking.

The practical value for image sticking is difficult to define in concrete numerals. As described below, you are advised to take proper measures to make the occurrence of image sticking as slow as possible.

6) Proposed measures taken to relieve image sticking

So long as there is the reduction of luminance in the fluorescent substance, it is impossible to avoid the occurrence of image sticking. Therefore, to relieve image sticking, we offer you a method of entering an image input that may ensure reluctance to the generation of the difference in luminance reduction among the displayed dots.

The images from TV broadcasting involve a high rate of motion picture displays.

Therefore, there is less chance of being a cause of difference in luminance reduction among the cells.

Even when the fixed patterns are displayed, they generally last for a few minutes.

Since the same pattern is less liable to be displayed, there is almost no influence toward image sticking.

If the fixed patterns tend to be displayed for a long time, however, there occurs a substantial imbalance between the lighting and non-lighting areas, thus causing a difference in luminance as a result. In this document, we offer you some proposals of installation, paying attentions to the two points: the reduction of difference in luminance achieved by integrated lighting time leveling and the method of edge smearing to make image sticking hard to be discerned.

The result from these proposals can, however, greatly depend on the contents of images and the operating environment. Therefore, we consider that it is essential to take the suitable measures in consideration of the customer's operating environment.

Example of Proposal 1: The display position is moved while the fixed display pattern is changed over, or it is scrolled during the display.

Example of Proposal 2: If possible, a pattern of complementary color is incorporated (for integrated time leveling).

Example of Proposal 3: The fixed pattern and the motion picture display are reciprocally exchanged, in order to minimize the display period of the fixed pattern.

Example of Proposal 4: During operation, the luminance of screen is suppressed as low as possible. For the display patterns, characters are indicated not on the black ground (non-picture area) but on the colored ground (mixture of R, G, B recommended).

## 7) Proposed countermeasures for the plasma module

Since the PDP is a display that uses a fluorescent substance like the CRT, it is a fundamental phenomenon that image sticking occurs. Unlike the CRT, the PDP gives rise to deterioration in the fluorescent substance due to impact caused by ions generated during plasma display.

As a result of the above-mentioned improvements, it is possible to extend the PDP lifetime and relieve

the effect of burning, but is impossible to realize the complete elimination of burning so far as a fixed pattern is displayed for a long time.

#### 1. Warning and Cautions

Warning: Indicates a hazard that can lead to death or injury if the warning is ignored and the product

is handled incorrectly.

Caution: Indicates a hazard that can lead to injury or damage to property if the caution is ignored

and the product is handled incorrectly

#### [Warning]

(1) This product uses a high voltage (420V max.). Do not touch the circuitry of this product with your hands when power is supplied to the product or immediately after turning off the power. Be sure to confirm that the voltage has dropped to a sufficiently low level.

(2) Do not supply a voltage higher than that specified to this product. This can damage the product and

may cause a fire.

(3) Do not use this product in locations where the humidity is extremely high, where it may be splashed with water, or where it is surrounded by flammable materials. Do not install or use the product in a location that does not satisfy the specified environmental conditions. This can damage the product and may cause a fire.

(4) If a foreign substance (such as water, metal, or liquid) gets inside the product, immediately turn off the power. Continuing to use the product as it is may cause fire or electric shock.

- (5) If the product emits smoke, an abnormal smell, or makes an abnormal sound, immediately turn off the power. If nothing is displayed or if the display goes out during use, immediately turn off the power. Continuing to use the product as it is may cause fire or electric shock.

- (6) Do not disconnect or connect the connector while power to the product is on. It takes some time for the voltage to drop to a sufficiently low level after the power has been turned off. Confirm that the voltage has dropped to a safe level before disconnecting or connecting the connector. Otherwise, this may cause fire, electric shock, or malfunctioning.

(7) Do not pull out or insert the power cable from/to an outlet with wet hands. Doing so may cause

electric shock.

(8) Do not damage or modify the power cable. Doing so it may cause fire or electric shock.

(9) If the power cable is damaged, or if the connector is loose, do not use the product; otherwise, this can lead to fire or electric shock.

(10) If the power connector or the connector of the power cable becomes dirty or dusty, wipe it with a dry cloth. Otherwise, this can lead to fire.

#### [Caution]

(1) Do not place this product in a location that is subject to heavy vibration, or on an unstable surface such as an inclined surface. The product may fall off or fall over, causing injuries.

(2) When moving the product, be sure to turn off the power and disconnect all the cables. While moving the product, watch your step. The product may be dropped or fall, leading to injuries or electric shock.

(3) Before disconnecting cables from the product, be sure to turn off the power. Be sure to hold the connector when disconnecting cables. Pulling a cable with excessive force may cause the core of the cable to be exposed or break the cable, and this can lead to fire or electric shock.

(4) This product should be moved by two or more persons. If one person attempts to carry this product

alone, he/she may be injured.

- (5) This product contains glass. The glass may break, causing injuries, if shock, vibration, heat, or distortion is applied to the product.

- (6) The temperature of the glass surface of the display may rise to 80°C or more depending on the conditions of use. If you touch the glass inadvertently, you may be burned.

(7) Do not poke or strike the glass surface of the display with a hard object. The glass may break or be scratched. If the glass breaks, you may be injured.

- (8) If the glass surface of the display breaks or is scratched, do not touch the broken pieces or the scratches with bare hands. You may be injured.

- (9) Do not place an object on the glass surface of the display. The glass may break or be scratched.

#### 2. Cautions on Design

(1) This product may be damaged if it is subject to excessive stresses (such as excessive voltage,

current, or temperature). The absolute maximum ratings specify the limits of these stresses, and system design must ensure that none of the absolute maximum ratings are exceeded.

- (2) The recommended operating conditions are conditions in which the normal operation of this product is guaranteed. All the rated values of the electrical specifications are guaranteed within these conditions. Always use the product within the range of the recommended operating conditions. Otherwise, the reliability of the product may be degraded. Use of the product with a combination of parameters, conditions, or logic not specified in the specifications of this product is not guaranteed. If intending to use the product in such a way, be sure to consult NEC in advance.

- (3) This product emits near infrared rays (700 to 1100 nm) that may cause the remote controllers of other electric products to malfunction. To avoid this, use an infrared absorption filter and thoroughly evaluate the system and environment.

- (4) This product uses high-voltage switching and a high-speed clock. A system using this product should be designed so that it does not affect the other systems, and should be thoroughly evaluated.

- (5) This product has a glass display surface. Design your system so that excessive shock and load are not applied to the glass. Exercise care that the vent at the corner of the glass panel is not damaged. If the glass panel or vent is damaged, the product is inoperable.

- (6) There are some exposed components on the rear panel of this product. Touching these components may cause an electric shock.

- (7) This product uses a high voltage. Design your system so that any residual voltage in this product is dissipated quickly when power is turned off, observing the specifications.

- (8) This product uses heat-emitting components. Take the heat emitted by these components into consideration when designing your system. If the product is used outside the specified temperature range, it may malfunction.

- (9) This product uses a high voltage and, because of its compact design, components are densely mounted on the circuit boards. If dust collects on these components, it can cause short-circuiting between the pins of the components and moisture can cause the insulation between the components to break down, causing the product to malfunction.

- (10) Regulations and standards on safety and electromagnetic interference differ depending on the country. Design your system in compliance with the regulations and standards of the country for which your system is intended.

- (11) To obtain approval under certain safety standards (such as UL and EN), a filter that passes a shock test must be fitted over the glass surface of the finished product. In addition, it must be confirmed that the level of UV emissions is within the range specified by such standards.

- (12) If this product is used as a display board to display a static image, "image sticking" occurs. This means that the luminance of areas of the display that remain lit for a long time drops compared with the luminance of areas that are lit for a shorter time, causing uneven luminance across the display. The degree to which this occurs is in proportion to the luminance at which the display is used. To prevent this phenomenon, therefore, avoid static images as much as possible and design your system so that it is used at a low luminance, by setting PLE to the maximum level.

- (13) Within the warranty period, general faults that occur due to defects in components such as ICs will be rectified by NEC without charge. However, IMAGE STICKING is not included in the warranty. Repairs due to the other faults may be charged for depending on responsibility for the faults.

- (14) This product is designed to NEC's "Standard" quality grade. If you wish to use the product for applications outside the scope of the "Standard" grade, be sure to consult NEC in advance to assess the technological feasibility before starting to design your system.

#### 3. Cautions on Use

- (1) Because this product uses a high voltage, connecting or disconnecting the connectors while power is supplied to the product may cause malfunctioning. Never connect or disconnect the connectors while the power is on. Immediately after power has been turned off, a residual voltage remains in the product. Be sure to confirm that the voltage has dropped to a sufficiently low level.

- (2) Watching the display for a long time can tire the eyes. Take a break at appropriate intervals.

- (3) Do not cover or wrap the product with a cloth or other covering while power is supplied to the product.

- (4) Before turning on power to the product, check the wiring of the product and confirm that the supply voltage is within the rated voltage range. If the wiring is wrong or if a voltage outside the rated range is applied, the product may malfunction or be damaged.

## Technical Document Number: 941-1H0038 30/31 1st edition: June 15, 2000

- (5) Do not store this product in a location where temperature and humidity are high. This may cause the product to malfunction. Because this product uses a discharge phenomenon, it may take time to light (operation may be delayed) when the product is used after it has been stored for a long time. In this case, it is recommended to light all cells for about 2 hours (aging).

- (6) If the glass surface of the display becomes dirty, wipe it with a soft cloth moistened with a neutral detergent. Do not use acidic or alkaline liquids, or organic solvents.

- (7) This product is made from various materials such as glass, metal, and plastic. When discarding it, be sure to contact a professional waste disposal operator.

#### 4. REPAIR AND MAINTENANCE

Because this product combines the display panel and driver circuits in a single module, it cannot be repaired or maintained at users' office or plant. Arrangements for maintenance and repair will be determined later.

#### 5. OTHERS

- (1) If your system requires the user to observe any particular precautions, in addition to the above warnings and cautions, include such caution and warning statements in the manual for your system.

- (2) If you have any questions concerning design, such as on housing, storage, or operating environment, consult NEC in advance.

# Technical Document Number: 941-1H0038 31/31 1st edition: June 15, 2000

| Revise history |                   | D       |

|----------------|-------------------|---------|

| Date           | Contents          | Remarks |

| June.15, 2000  | Issue 1st edition |         |

|                |                   |         |

|                |                   |         |

|                |                   | *       |

|                |                   | ·       |

|                |                   |         |

|                |                   |         |

|                |                   |         |

|                |                   | ·       |

|                |                   |         |

|                |                   |         |

|                |                   |         |

| -              | •                 |         |

|                |                   |         |

|                |                   |         |

|                |                   |         |

|                |                   |         |

|                |                   |         |

|                |                   |         |

|                |                   |         |

|                |                   |         |

|                |                   |         |

|                |                   |         |

|                |                   |         |

|                |                   |         |

|                |                   |         |

|                |                   |         |

|                |                   |         |

|                |                   | -       |

|                |                   |         |

|                |                   |         |

| -              |                   |         |

|                |                   |         |

|                |                   | ·       |

|                |                   |         |

|                |                   |         |

|                |                   |         |

|                |                   |         |

|                |                   |         |

|                |                   |         |

| 1   |          | 00000  | <u> </u> | <u>.                                      </u> | 00    |          |

|-----|----------|--------|----------|------------------------------------------------|-------|----------|

|     | 00000000 | 000000 |          | - 0000                                         |       |          |

|     | -        |        |          |                                                | 30000 |          |

| 1   |          |        |          | 0.0                                            |       | . 🗆 🗆    |

|     |          |        |          |                                                |       |          |

|     |          |        |          | 000                                            | 0000  | 00       |

|     |          |        |          |                                                |       |          |

| 1   |          |        | 00       | 0000                                           |       |          |

|     |          |        |          |                                                |       |          |

|     |          |        |          |                                                |       | L        |

|     |          | ·      |          |                                                |       |          |

|     |          |        |          |                                                |       |          |

|     |          |        |          | 000                                            | 0000  | 00       |

|     |          |        | •        |                                                |       |          |

|     |          |        |          |                                                |       | _        |

|     |          |        | -        | 0000                                           |       |          |

|     |          |        |          |                                                |       |          |

|     |          |        | •        |                                                |       |          |

|     |          |        |          |                                                |       |          |

|     |          |        |          | 000                                            | 0000  | 00       |

|     |          |        |          | , LUU                                          |       | "        |

|     |          |        |          |                                                |       |          |

|     |          |        |          | 0000                                           |       | ├        |

|     |          |        |          |                                                |       |          |

|     |          |        |          |                                                |       | T        |

|     |          |        |          |                                                | 00    |          |

|     |          |        |          |                                                |       |          |

|     |          |        |          | 000                                            | 0000  |          |

|     |          |        |          |                                                |       |          |

|     |          |        |          | 0000                                           |       | ļ        |

|     |          |        |          |                                                |       |          |

|     |          |        | <u></u>  | T                                              |       |          |

|     | ·        |        |          |                                                | 00    |          |

|     |          |        |          |                                                |       | <u> </u> |

|     |          |        |          | 000                                            | 0000  |          |

|     |          |        |          |                                                |       |          |

|     |          |        |          | 0000                                           |       | 1        |

| - 1 |          |        | 1.       |                                                |       |          |