# Half-bridge GaN Driver

Datasheet (EN) 1.3

#### **Product Overview**

NSD2621X is an integrated half-bridge gate driver which is designed for GaN HEMT.

The driver operates with a wide supply voltage from 10V to 18V, while internal regulator could offer stable driver voltage to keep GaN FET safe.

The undervoltage lock-out (UVLO) protection feature is provided in low side and high side drivers to prevent the GaN FET from operating in low efficiency or dangerous conditions

The programmable dead-time control function has been provided. The adjustable dead-time range is from 20ns to 100ns.

The device operates in the industrial temperature range, -40°C to 125°C, and is available in a compact 4.0 x 4.0 mm QFN package.

### **Key Features**

- 700V Half-bridge Gate Drivers

- Integrated High-side and Low-side Output Regulators

- · UVLO protection on low side and high side

- Source/Sink Current: 2A/4A

- Propagation Delay: 30ns TYP

- Short switching delay and mismatch

- Independent turn-on and turn-off adjustable

- Programmable Deadtime from 20ns to 100ns

- Allowable SW slew rate: 150V/ns

- Operating Temperature: -40~125°C

- RoHS & REACH Compliance

- Lead-free component, suitable for lead-free soldering profile: 260°C

### **Applications**

- Driving GaN power FET used in Half-bridge, fullbridge, active flyback or forward, LLC DC-DC converter

- PFC and AC-DC converter

- Industrial Inverters and Motor Drives

#### **Device Information**

| Part Number | Output | <b>Body Size</b> |

|-------------|--------|------------------|

| NSD2621A-   | 6V     | 4.0mm x 4.0mm x  |

| DQAGR       | ΟV     | 0.55mm           |

| NSD2621C-   | 5V     | 4.0mm x 4.0mm x  |

| DQAGR       | οv     | 0.55mm           |

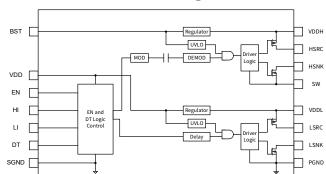

### **Functional Block Diagram**

Figure 0.1 NSD2621X Block Diagram

# **NSD2621X**

### **INDEX**

| 1. PIN CONFIGURATION AND FUNCTIONS  | 3              |

|-------------------------------------|----------------|

| 2. ABSOLUTE MAXIMUM RATINGS         | 4              |

| 3. ESD RATINGS                      | 4              |

| 4. RECOMMENDED OPERATING CONDITIONS | 4              |

| 5. THERMAL INFORMATION              | 4              |

| 6. SPECIFICATIONS                   | 5              |

| 6.1. ELECTRIC CHARACTERISTICS       | 6<br>7         |

| 7. FUNCTION DESCRIPTION             | 10             |

| 7.1. OVERVIEW                       | 10<br>11<br>11 |

| 8. APPLICATION NOTE                 | 13             |

| 8.1. TYPICAL APPLICATION CIRCUIT    |                |

| 9. PACKAGE INFORMATION              | 16             |

| 10. ORDERING INFORMATION            | 17             |

| 11. TAPE AND REEL INFORMATION       | 17             |

| 12. REVISION HISTORY                | 19             |

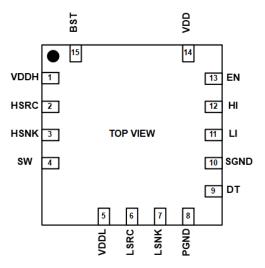

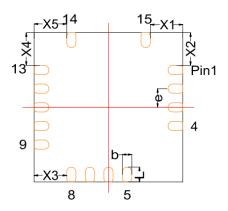

## 1. Pin Configuration and Functions

Figure 1.1 Pin Configuration

Table 1.1 Pin Configuration and Description

| PIN NO. | SYMBOL | FUNCTION                                                                                                               |  |

|---------|--------|------------------------------------------------------------------------------------------------------------------------|--|

| 1       | VDDH   | High-side voltage regulator output. A ceramic capacitor of not less than 100nF must be connected between VDDH and SW.  |  |

| 2       | HSRC   | High-side driver sourcing output                                                                                       |  |

| 3       | HSNK   | High-side driver sinking output                                                                                        |  |

| 4       | SW     | High-side driver reference (Switching node)                                                                            |  |

| 5       | VDDL   | Low-side voltage regulator output. A ceramic capacitor of not less than 100nF must be connected between VDDL and PGND. |  |

| 6       | LSRC   | Low-side driver sourcing output                                                                                        |  |

| 7       | LSNK   | Low-side driver sinking output                                                                                         |  |

| 8       | PGND   | Low-side driver reference (Power ground)                                                                               |  |

| 9       | DT     | Dead-time adjustment                                                                                                   |  |

| 10      | SGND   | Signal ground                                                                                                          |  |

| 11      | LI     | Low-side driver logic input                                                                                            |  |

| 12      | HI     | High-side driver logic input                                                                                           |  |

| 13      | EN     | Dual drivers enabling logic input                                                                                      |  |

| 14      | VDD    | Power supply for logic and low-side regulator                                                                          |  |

| 15      | BST    | Power supply for high-side regulator (Bootstrap voltage)                                                               |  |

2. Absolute Maximum Ratings

| Parameters                    | Symbol                                                    | Min  | Max                                                   | Unit |

|-------------------------------|-----------------------------------------------------------|------|-------------------------------------------------------|------|

| High-side Common Mode Voltage | V <sub>sw</sub>                                           | -700 | 720                                                   | V    |

| Driver Supply Voltage         | VDD to SGND, BST to SW                                    | -0.3 | 24                                                    | V    |

| Regulator Output Voltage      | VDDL to PGND, VDDH to SW                                  | -0.3 | 7                                                     | V    |

| Different Ground Voltage      | SGND to PGND                                              | -5   | 5                                                     | V    |

| land Cina al Maltana          | HI, LI, EN, DT to SGND                                    | -0.3 | V <sub>VDD</sub> +0.3                                 | V    |

| Input Signal Voltage          | HI, LI, EN, DT to SGND, Transient for 50ns                | -5   | V <sub>VDD</sub> +0.3                                 | V    |

| Driver Output Voltage         | LSRC/LSNK to PGND, HSRC/HSNK to SW                        |      | V <sub>VDDL</sub> +0.3<br>,<br>V <sub>VDDH</sub> +0.3 | V    |

|                               | LSRC/LSNK to PGND, HSRC/HSNK to SW,<br>Transient for 50ns | -2   | 7                                                     | V    |

| Junction Temperature          | LT.                                                       | -40  | 150                                                   | °C   |

| Storage Temperature           | T <sub>stg</sub>                                          | -55  | 150                                                   | °C   |

## 3. ESD RATINGS

|                         | Value                                             | Unit  |   |

|-------------------------|---------------------------------------------------|-------|---|

| Electrostatic discharge | Human body model (HBM), per AEC-Q100-002-RevD     | ±3000 | V |

| Electrostatic discharge | Charged device model (CDM), per AEC-Q100-011-RevB | ±1000 | V |

4. Recommended Operating Conditions

| Parameters                    | Symbol                             | Min | Max                                      | Unit |

|-------------------------------|------------------------------------|-----|------------------------------------------|------|

| High-side Common Mode Voltage | V <sub>sw</sub>                    | 0   | 650                                      | V    |

| Driver Supply Voltage         | VDD to SGND, BST to SW             | 10  | 18                                       | V    |

| Driver Output Voltage         | LSRC/LSNK to PGND, HSRC/HSNK to SW | 0   | V <sub>VDDL</sub> ,<br>V <sub>VDDH</sub> | V    |

| Input Signal Voltage          | HI, LI, EN to SGND                 | 0   | $V_{VDD}$                                | V    |

| Ambient Temperature           | Ta                                 | -40 | 125                                      | °C   |

### 5. Thermal Information

| Parameters                                             | Symbol                | Value | Unit |

|--------------------------------------------------------|-----------------------|-------|------|

| Junction-to-ambient thermal resistance <sup>1)</sup>   | θја                   | 81    | °C/W |

| Junction-to-case(top) thermal resistance <sup>1)</sup> | θ <sub>JC</sub> (top) | 24    | °C/W |

| Junction-to-board thermal resistance <sup>1)</sup>     | θЈВ                   | 71    | °C/W |

| Parameters                                                 | Symbol         | Value | Unit |

|------------------------------------------------------------|----------------|-------|------|

| Junction-to-top characterization parameter <sup>1)</sup>   | $\Psi_{ m JT}$ | 61    | °C/W |

| Junction-to-board characterization parameter <sup>1)</sup> | $\Psi_{JB}$    | 55    | °C/W |

<sup>1)</sup> High Effective Thermal Conductivity Test Board (2s2p) in an environment described in JESD51-2a.

## 6. Specifications

### 6.1. Electric Characteristics

VDD = 12V,  $T_a$  = -40°C to 125°C. Unless otherwise noted, Typical values are at  $T_a$ = 25°C.

| Parameter                             | Symbol                                  | Min | Тур  | Max | Unit | Comments                                                          |

|---------------------------------------|-----------------------------------------|-----|------|-----|------|-------------------------------------------------------------------|

| Driver Power Supply                   |                                         |     |      |     |      |                                                                   |

| VDD Quiescent Current                 | $I_{VDDQ}$                              |     | 0.42 |     | mA   | HI = LI = 0V                                                      |

| VDD Operating Current                 | Ivddo                                   |     | 2.6  |     | mA   | HV = SW = 0V, BST = 12V,<br>f = 500kHz, C <sub>load</sub> = 330pF |

| BST Quiescent Current                 | I <sub>BSTQ</sub>                       |     | 0.58 |     | mA   | HI = LI = 0V                                                      |

| BST Operating Current                 | Івѕто                                   |     | 2.7  |     | mA   | HV =SW = 0V, BST = 12V,<br>f = 500kHz, C <sub>load</sub> = 330pF  |

| VDD UVLO Rising Threshold             | $V_{VDD\_ON}$                           | 8.0 | 8.4  | 8.8 | V    |                                                                   |

| VDD UVLO Falling Threshold            | V <sub>VDD_OFF</sub>                    | 7.5 | 7.8  | 8.1 | V    |                                                                   |

| VDD UVLO Hysteresis                   | V <sub>VDD_HYS</sub>                    | 0.4 | 0.6  |     | V    |                                                                   |

| BST UVLO Rising Threshold             | V <sub>BST_ON</sub> -V <sub>SW</sub>    | 8.0 | 8.4  | 8.8 | V    |                                                                   |

| BST UVLO Falling Threshold            | V <sub>BST_OFF</sub> -V <sub>SW</sub>   | 7.5 | 7.8  | 8.1 | V    |                                                                   |

| BST UVLO Hysteresis                   | V <sub>BST_HYS</sub>                    | 0.4 | 0.6  |     | V    |                                                                   |

| Input Logic                           |                                         | •   | •    |     | •    |                                                                   |

| Input Pin Pull-down Resistance        | R <sub>HI_PD</sub> , R <sub>LI_PD</sub> |     | 200  |     | kΩ   | HI = LI = 3V                                                      |

| Enable Pin Pull-down Resistance       | R <sub>EN_PD</sub>                      |     | 200  |     | kΩ   | EN = 3V                                                           |

| Input Pin High Logic Bias Current     | Іні_н, Ісі_н                            |     | 20   |     | μA   | HI = LI = 5V                                                      |

| Enable Pin High Logic Bias<br>Current | len_h                                   |     | 20   |     | μA   | EN = 5V                                                           |

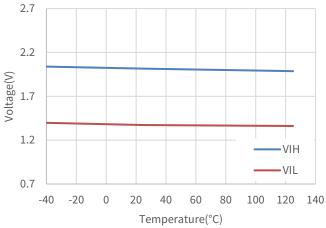

| Logic High Input Threshold            | V <sub>HI_H</sub> , V <sub>LI_H</sub>   | 1.7 | 2.1  | 2.5 | V    |                                                                   |

| Logic Low Input Threshold             | VHI_L, VLI_L                            | 0.9 | 1.2  | 1.5 | V    |                                                                   |

| Input Hysteresis                      | VHI_HYS, VLI_HYS                        | 0.7 | 0.9  |     | V    |                                                                   |

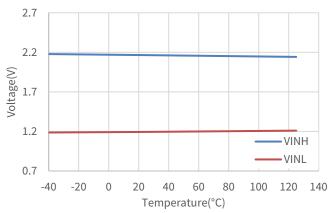

| Logic High Input Threshold            | V <sub>EN_H</sub>                       | 1.7 | 2.1  | 2.5 | V    |                                                                   |

| Parameter                                             | Symbol                                      | Min | Тур | Max | Unit | Comments                                                              |

|-------------------------------------------------------|---------------------------------------------|-----|-----|-----|------|-----------------------------------------------------------------------|

| Logic Low Input Threshold                             | $V_{EN\_L}$                                 | 0.9 | 1.4 | 1.5 | V    |                                                                       |

| Input Hysteresis                                      | V <sub>EN_HYS</sub>                         | 0.5 | 0.7 |     | V    |                                                                       |

| Driver Output Characteristic                          |                                             |     |     |     |      |                                                                       |

| Pagulator Output Valtage                              | VVDDL. VVDDH-VSW                            | 5.6 | 6   | 6.3 | V    | C <sub>VDDL</sub> = 100nF, C <sub>VDDH</sub> -sw<br>= 100nF, NSD2621A |

| Regulator Output Voltage                              | VVDDL, VVDDH-VSW                            | 4.6 | 5   | 5.4 | V    | C <sub>VDDL</sub> = 100nF, C <sub>VDDH</sub> -sw<br>= 100nF, NSD2621C |

| Regulator UVLO Rising Threshold                       | Vvddh_on,<br>Vvddl_on                       | 4.1 | 4.4 | 4.7 | V    |                                                                       |

| Regulator UVLO Falling Threshold                      | Vvddh_off,<br>Vvddl_off                     | 3.8 | 4.1 | 4.4 | V    |                                                                       |

| Regulator UVLO Hysteresis                             | Vvddh_hys,<br>Vvddl_hys                     |     | 0.3 |     | V    |                                                                       |

| High-level output voltage, VVDDH-VHSRC or VVDDL-VLSRC | V <sub>он</sub>                             |     | 16  |     | mV   | I_xSRC = 10 mA                                                        |

| Low-level output voltage, VHSNK-VSW or VLSNK -PGND    | V <sub>OL</sub>                             |     | 8   |     | mV   | I_xSNK = 10 mA                                                        |

| Output Peak Source Current                            | ILSRC_PK, IHSRC_PK                          |     | 2   |     | Α    | _                                                                     |

| Output Peak Sink Current                              | I <sub>LSNK_PK</sub> , I <sub>HSNK_PK</sub> |     | 4   |     | А    |                                                                       |

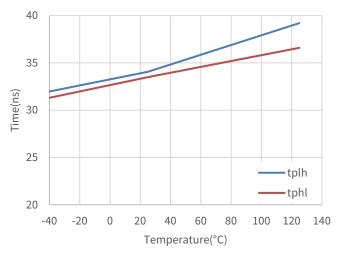

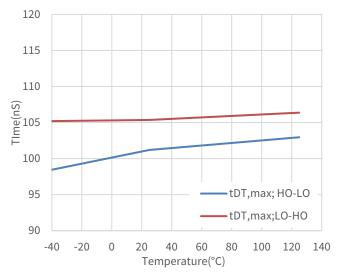

## **6.2. Dynamic Characteristics**

VDD=12V,  $T_a$ =-40°C to 125°C. Unless otherwise noted, Typical values are at  $T_a$ =25°C.

| Parameter                                    | Symbol                                       | Min | Тур | Max | Unit | Comments                                                            |

|----------------------------------------------|----------------------------------------------|-----|-----|-----|------|---------------------------------------------------------------------|

| Minimum Input Pulse Width                    | t <sub>PWmin</sub>                           |     |     | 20  | ns   |                                                                     |

| Output Rising Time                           | t <sub>LSRC</sub> /t <sub>HSRC</sub>         |     | 6   |     | ns   | C <sub>load</sub> = 330pF                                           |

| Output Falling Time                          | t <sub>LSNK</sub> /t <sub>HSNK</sub>         |     | 5   |     | ns   | C <sub>load</sub> = 330pF                                           |

| Turn-on Propagation Delay Time               | t <sub>PD(on)</sub>                          |     | 30  | 60  | ns   |                                                                     |

| Turn-off Propagation Delay Time              | $t_{PD(off)}$                                |     | 30  | 60  | ns   |                                                                     |

| Propagation Delay Match                      | t <sub>PDM</sub>                             |     |     | 10  | ns   |                                                                     |

| Pulse Width Distortion                       | t <sub>PWD</sub>                             |     |     | 10  | ns   |                                                                     |

| VDD or BST Power-up Delay Time <sup>1)</sup> | t <sub>PUD</sub>                             |     | 15  |     | μs   | First time power-up from V <sub>POR</sub>                           |

| VDDL or VDDH Rising Time <sup>1)</sup>       | t <sub>VDDL_R</sub> /<br>t <sub>VDDH_R</sub> |     | 13  |     | μs   | C <sub>VDDL</sub> = 100nF, C <sub>VDDH-SW</sub> = 100nF             |

| Programmed Deadtime                          | t <sub>DT_Min</sub>                          |     | 20  |     | ns   | $R_{DT}$ <=20k $\Omega$ or $R_{DT}$ >620k $\Omega$ , $C_{DT}$ = 1nF |

|                                              | t <sub>DT_Max</sub>                          |     | 100 |     | ns   | 140kΩ<= $R_{DT}$ <=220kΩ, $C_{DT}$ = 1nF                            |

1) See detail in Figure 7.1.

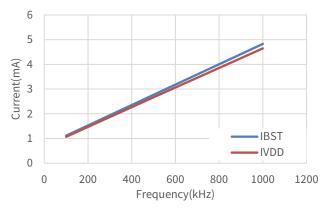

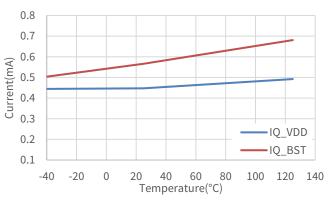

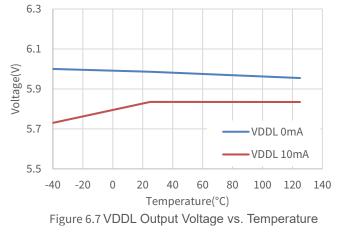

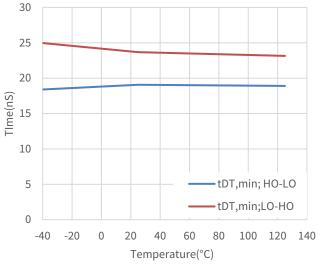

### 6.3. Typical Performance Characteristics

T<sub>a</sub>= 25°C, unless otherwise noted.

Figure 6.1 Operating Current (I\_VDD, I\_BST) vs.

Frequency (VDD = VBST=12 V, SW = PGND, 330pF load)

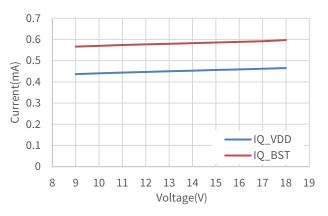

Figure 6.3 Quiescent Current (IQ\_VDD, IQ\_BST) vs.

Temperature

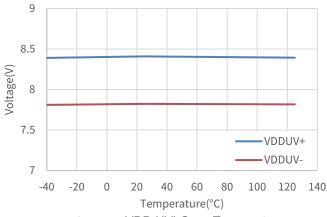

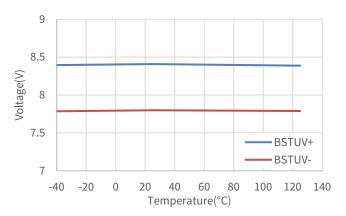

Figure 6.5 VDD UVLO vs. Temperature

Figure 6.2 Quiescent Current (IQ\_VDD, IQ\_BST) vs. Voltage

Figure 6.4 BST UVLO vs. Temperature

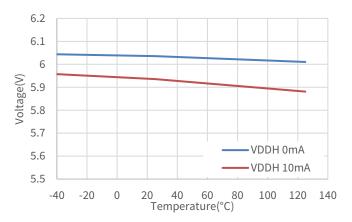

Figure 6.6 VDDH Output Voltage vs. Temperature

Figure 6.9 Input Logic (EN) Threshold vs. Temperature

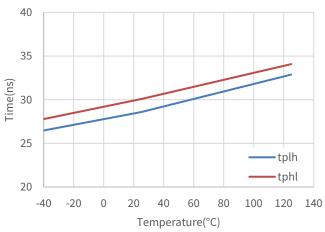

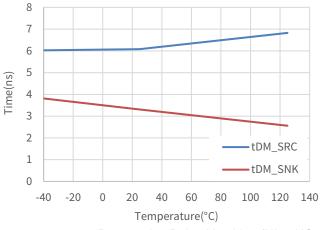

Figure 6.11 HI to HSRC & HSNK Propagation Delay vs. Temperature

Figure 6.8 Input Logic (HI, LI) Threshold vs. Temperature

Figure 6.10 LI to LSRC & LSNK Propagation Delay vs. Temperature

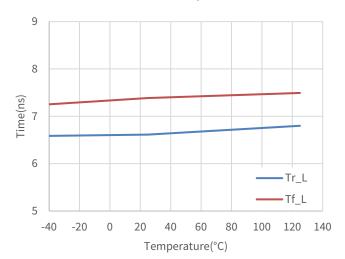

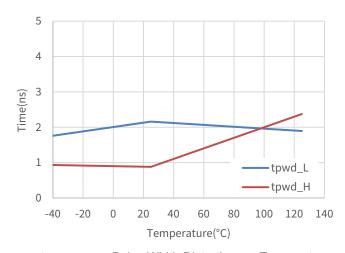

Figure 6.12 LSRC Rise Time and LSNK Fall Time vs. Temperature

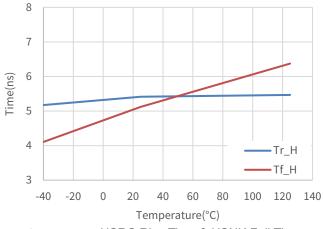

Figure 6.13 HSRC Rise Time & HSNK Fall Time vs. Temperature

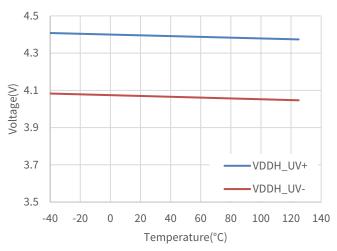

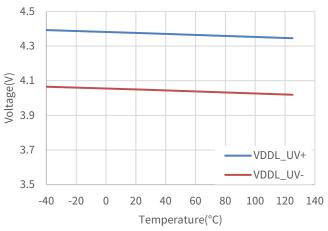

Figure 6.15 VDDH UVLO vs. Temperature

Figure 6.17 Propagation Delay Matching (HI to HO, LI to LO) vs. Temperature

Figure 6.14 VDDL UVLO vs. Temperature

Figure 6.16 Pulse Width Distortion vs. Temperature

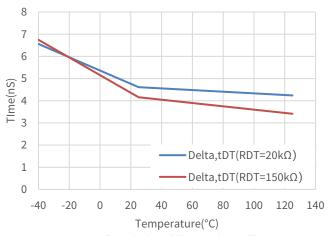

Figure 6.18 Dead-time Mismatch vs. Temperature

Figure 6.19 Minimum Dead-time (RDT =  $20k\Omega$ ) vs. Temperature

Figure 6.20 Maximum Dead-time (RDT =  $150k\Omega$ ) vs. Temperature

#### 6.4. Parameter Measurement Information

Figure 6.21 Switching Time Waveform

### 7. Function Description

#### 7.1. Overview

NSD2621X is an integrated half-bridge gate driver for GaN FET. In order to output stable driver voltage, it integrated the regulator and draws out the output of regulator. The source and sink of gate driver were separated, which is convenient for users to adjust he switching speed of GaN FET. In addition, it also provides the programmable deadtime and under voltage lock out (UVLO) protection.

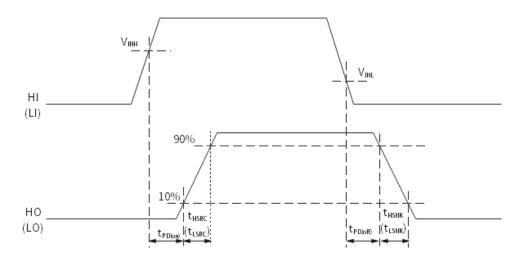

### 7.2. Under Voltage Lock Out (UVLO)

The NSD2621X has internal under voltage lock out (UVLO) protections on low side and high side power supply blocks. The driver output is held low by an active clamp circuit when the supply voltage of VDD or BST is lower than  $V_{VDD\_ON}$  /  $V_{BST\_ON}$  at power-up status or lower than  $V_{VDD\_OFF}$  /  $V_{BST\_OFF}$  after power-up, regardless of the status of the input pins.

The 0.6V hysteresis ( $V_{VDD\_HYS}$ ) on VDD and BST ULVO protections are provided prevent chatter noise from VDD supply and allow small drops in supply power which are usually happened in startup. When VDD voltage or BST voltage is more than  $V_{VDD\_POR} / V_{BST\_POR}$  which is approximate 2V, the internal part circuits will begin to operate. In Figure.6.1,  $t_{PUD}$  is the power up delay time which is about 22us.

Figure 7.1 UVLO Diagram

#### 7.3. Regulator Output (VDDL/VDDH)

The NSD2621X integrated the linear regulator in the low side and high side and VDDL/VDDH is the output of regulator. The VDDL regulator is fed directly from VDD and directedly provide the driver voltage and current for low side GaN FET. The VDDL regulator is referenced to the power ground (PGND) pin. Source current for the low–side GaN FET is provided from the charge stored in the capacitor connected between VDDL and PGND. A not less than 100nF ceramic capacitor must be used on VDDL to normally operate. When the VDDL voltage is higher than 4.4V which is UVLO rising threshold (V<sub>VDDL\_OFF</sub>), the output disables.

The VDDH regulator is fed directly from BST and directedly provide the driver voltage and current for high side GaN FET. The VDDH regulator is referenced to SW. Source current for the how-side GaN FET is provided from the charge stored in the capacitor connected between VDDH and SW. A not less than 100nF ceramic capacitor must be connected between VDDH and SW pins. When the VDDH voltage is higher than 4.4V which is UVLO rising threshold ( $V_{VDDH\_ON}$ ), the output enables; When the VDDH voltage is lower than 4.1V which is UVLO falling threshold ( $V_{VDDH\_OFF}$ ), the output disables.

#### 7.4. Input and Output Logic

The NSD2621X is a half-bridge gate driver with dead-time control. The EN pin should be logic high to keep the driver operating normally.

|        | Input Pins |    | Outp      | ut Pins   | NOTE |

|--------|------------|----|-----------|-----------|------|

| EN     | н          | LI | HSRC/HSNK | LSRC/LSNK |      |

| L or O | Х          | Х  | L         | L         |      |

| Н      | L          | L  | L         | L         |      |

| Н      | L          | Н  | L         | Н         |      |

Table 7.1 Output status vs. Input and Power status

| Input Pins |   | Output Pins |           | NOTE      |                                                      |

|------------|---|-------------|-----------|-----------|------------------------------------------------------|

| EN         | н | LI          | HSRC/HSNK | LSRC/LSNK |                                                      |

| Н          | Н | L           | Н         | L         | Driver's outputs turn on after the deadtime expires. |

| Н          | Н | Н           | L         | L         | The input signal is later than VDD power up.         |

<sup>1)</sup> H= Logic High; L= Logic Low; O= Left Open; X= Irrelevant.

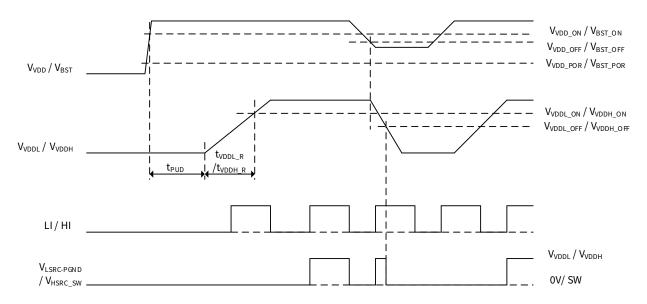

#### 7.5. Programmable Deadtime (DT pin)

The NSD2621X has a programmable deadtime control function by placing a resistor,  $R_{DT}$ , between the DT pin and SGND. The relationship between deadtime and  $R_{DT}$  can refer to the below description.

- 1) While  $R_{DT}$  is lower than  $20k\Omega$  or higher than  $620k\Omega$ , the deadtime duration  $(t_{DT})$  is set to 20ns.

- 2) While  $R_{DT}$  is in range of 140k $\Omega$  to 220k $\Omega$ , the deadtime duration ( $t_{DT}$ ) is set to 100ns.

The recommended value of  $R_{DT}$  is from  $1k\Omega$  to  $14k\Omega$  or from  $140k\Omega$  to  $200k\Omega$ . It is also recommended to parallel a ceramic capacitor, for example 1nF, with  $R_{DT}$  to achieve better noise immunity.

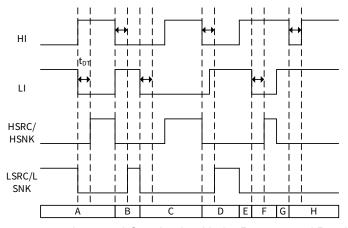

The programmed deadtime is activated by the input signal's falling edge to prevent shoot-through when the device is designed in an application of high side and low side driver. The details of input and output logic with deadtime are shown as Figure 7.2:

Figure 7.2 Input and Gate Logic with the Programmed Deadtime

| Condition                                          | Result                                                                                                                   |  |  |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| A: HI goes high, and LI goes low.                  | LSRC/LSNK goes low immediately, then HSRC/HSNK goes high after the programmed deadtime which is assigned at LI goes low. |  |  |

| B: HI goes low, and LI goes high.                  | HSRC/HSNK goes low immediately, then LSRC/LSNK goes high after the programmed deadtime which is assigned at HI goes low. |  |  |

| C: LI goes low, then HI goes high after deadtime.  | LSRC/LSNK goes low immediately, then HSRC/HSNK goes high immediately when HI goes high.                                  |  |  |

| D: HI goes low, then LI goes high before deadtime. | HSRC/HSNK goes low immediately, then LSRC/LSNK goes high after deadtime                                                  |  |  |

| E: HI goes high, LI is still high.                 | LSRC/LSNK goes low immediately, and HSRC/HSNK keeps low.                                                                 |  |  |

| F: HI is still high, LI goes low.                  | HSRC/HSNK goes high after deadtime while LI is low, and LSRC/LSNK keeps low.                                             |  |  |

| Condition                                                             | Result                                                                |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------|

| G: HI is still high, LI goes high after deadtime                      | HSRC/HSNK goes low immediately, and LSRC/LSNK keeps low.              |

| H: HI goes low then goes high before deadtime while LI is still high. | HSRC/HSNK keeps low and LSRC/LSNK keeps low because deadtime control. |

### 8. Application Note

#### 8.1. Typical Application Circuit

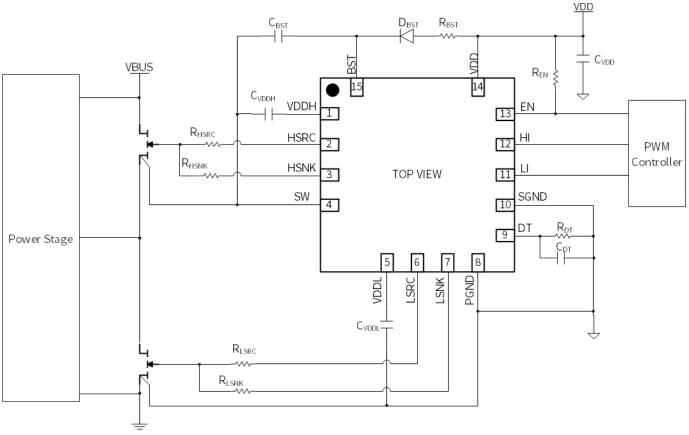

Figure. 8.1 shows a typical half-bridge configuration by using the NSD2621X.

Figure. 8.1 Simplified Half-Bridge Application Schematic

**Supply voltage (VDD):** VDD is the low side power supply of NSD2621X. It provides the power for digital inputs, internal logic functions and the internal low–side regulator (VDDL). A single VDD bypass capacitor,  $C_{VDD}$ , is required and connected directly between the VDD and SGND pins. The  $C_{VDD}$  capacitor should be a ceramic bypass capacitor > 100 nF, located as close as possible to the VDD and SGND pins to properly filter out all glitches while switching.

**High-Side Bootstrap Voltage (BST):** BST is the high side power supply of NSD2621X. The BST voltage is input to an internal regulator which produces the VDDH voltage. The resistor R<sub>BST</sub> is series connected with D<sub>BST</sub> to limit the bootstrap current. The bootstrap capacitor C<sub>BST</sub> connected directly between BST and SW pins. The capacitor C<sub>BST</sub> should be a ceramic capacitor and located as close as possible to the BST and SW pins to properly filter out all glitches while switching. The value of C<sub>BST</sub> should be large to provide fully charge for high side normal operation. No high side pulses are produced when the voltage on BST pin is less than UVLO voltage.

### **NSD2621X**

The bootstrap diode D<sub>BST</sub> should be high-speed, low leakage current and very low junction capacitance. Its rated voltage must be greater than VBUS.

The purpose of the bootstrap resistor  $R_{BST}$  is to limit peak charging current of  $C_{BST}$ , especially during startup. A too small resistor may not limit the peak current enough, resulting in excessive ringing which can cause jitter in the high side gate drive or EMI problems. A large resistor will dissipate more power and create a longer RC time constant causing a longer start up time. A bootstrap resistor in the range of  $1\Omega < R_{BST} < 10\Omega$  is usually sufficient.

**Low Side Regulator (VDDL):** VDDL is the low side regulator output. The VDDL regulator is fed directly from VDD and directedly provide the drive voltage and current for low side GaN FET. The VDDL regulator is referenced to the power ground (PGND) pin. The VDDL output voltage is respectively 6Vand 5V for NSD2621A/ C. Source current for the low–side GaN FET is provided from the charge stored in the capacitor C<sub>VDDL</sub> connected between VDDL and PGND. A not less than 100nF ceramic capacitor C<sub>VDDL</sub> must be connected between VDDL and PGND pins. The VDDL regulator will not output when VDD voltage is less than UVLO voltage. When the VDDL voltage is higher than 4.4V which is UVLO threshold (V<sub>VDDL\_ON</sub>), the output enables; When the VDDL voltage is lower than 4.1V which is UVLO threshold (V<sub>VDDL\_OFF</sub>), the output disables.

High Side Regulator (VDDH): VDDH is the high side regulator output. The VDDH regulator is fed directly from BST and directedly provide the drive voltage and current for high side GaN FET. The VDDH regulator is referenced switching node (SW) pin. The VDDH output voltage is respectively 6V and 5V for NSD2621A/ C. Source current for the high side GaN FET is provided from the charge stored in the capacitor C<sub>VDDH</sub> connected between VDDH and SW. A not less than 100nF ceramic capacitor C<sub>VDDH</sub> must be connected between VDDH and SW pins. The VDDH regulator will not output when BST voltage is lower than UVLO voltage. When the VDDH voltage is higher than 4.4V which is UVLO threshold (V<sub>VDDH\_OFF</sub>), the output disables.

**Signal Ground (SGND) and Power Ground (PGND):** SGND is the PGND for all internal control logic and digital inputs. Internally, the SGND and PGND pins are isolated from each other. PGND is the return reference of the low side gate drive and VDDL. For GaN FETs that include a source Kelvin return, a direct connection should be made from PGND to the GaN FET Kelvin return. C<sub>VDDL</sub> should be referenced to the PGND but separate from the power stage ground as shown in Figure. 8.1

The NSD2621X low side drive circuit is able to withstand −5 V to +5 V of common mode voltage between SGND and PGND. If the common mode voltage is over the range, NSD2621X may be damaged. In practical application, SGND and PGND should be connected together with a low impedance resistor or with a short low impedance trace on the PCB.

**Switch Node (SW):** SW is the return reference of high side gate drive. For GaN FETs included a source Kelvin return, a direct connection should be made from SW to the GaN FET Kelvin return.  $C_{VDDH}$  and  $C_{BST}$  should be referenced to the SW pin but separate from the power stage switch node as shown in Figure. 8.1

**Input (LI, HI):** LI and HI are the PWM signal input pins. Both inputs are independent and internally pulled low to SGND such that each output is defaulted to be low. The input is compatible with Transistor-Transistor Logic (TTL).

**Enable (EN):** Enable (EN) is internally pulled low to SGND so that the driver is defaulted to a disabled output status. EN voltage is above 2.5V maximum, enables the outputs. EN can be controlled by digital signal or connected directly VDD. If EN is pulled low during normal operation, the driver outputs are immediately disabled.

**Deadtime (DT):** A resistor  $R_{DT}$  should be connected between DT and SGND pins in order to configure the deadtime. The recommended value of  $R_{DT}$  is from  $1k\Omega$  to  $14k\Omega$  or from  $140k\Omega$  to  $200k\Omega$ . It is also recommended to parallel a ceramic capacitor, for example 1nF, with  $R_{DT}$  to achieve better noise immunity.

**High Side Output (HSRC and HSNK):** HSRC and HSNK control turn-on and turn-off of high side GaN FET respectively. This allows a single resistor between each pin and the gate of high side GaN FET to independently control gate rising and falling speed.

**Ligh Side Output (LSRC and LSNK):** LSRC and LSNK control turn-on and turn-off of low side GaN FET respectively. This allows a single resistor between each pin and the gate of low side GaN FET to independently control gate rising and falling speed.

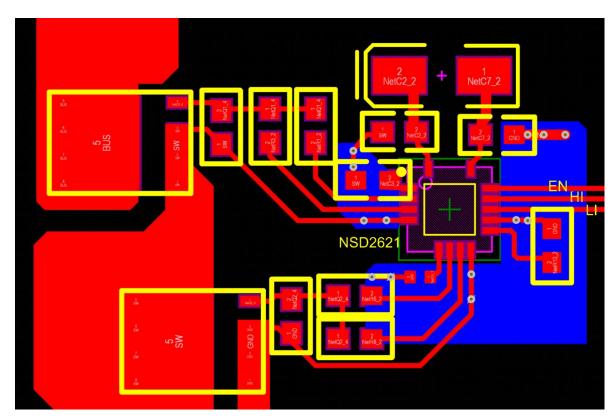

### 8.2. Layout Recommendations

PCB layout is important to get optimal performance. Some of the layout guidelines to be followed are listed below:

- 1) The bypass capacitors connected on VDD, VDDH, VDDL, EN, DT and BST should be placed as close to their respective pins as possible.

- 2) A not less than 100nF MLCC capacitor should be placed between VDDL and PGND. It should be placed as close to VDDL as possible.

- 3) A not less than 100nF MLCC capacitor should be placed between VDDH and SW. It should be placed as close to VDDH as possible.

- 4) High frequency switching current charges and discharges the gate and drain of GaN FETs, which causes EMI and ringing issues. The lengths of gate drive loop should be short to minimum the parasitic inductance and ringing affection.

- 5) The source and sink gate drive resistors should be placed as close to the GaN FETs as possible.

Figure. 8.2 PCB Layout Example

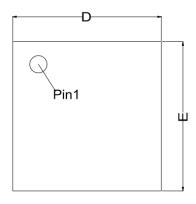

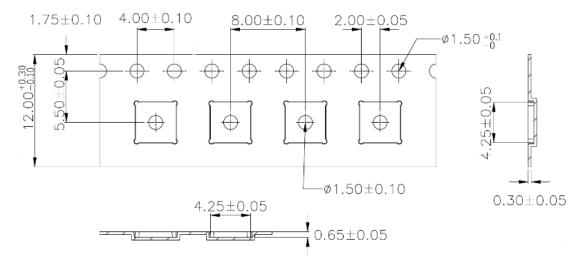

## 9. Package information

Package Top View

Package Bottom View

Package Side View

| SYMBOLS  | DIMENSION IN MM |       |       |  |  |

|----------|-----------------|-------|-------|--|--|

| STWIDOLS | MIN             | NOM   | MAX   |  |  |

| Α        | 0.500           | 0.550 | 0.600 |  |  |

| A1       | 0.007           | 0.012 | 0.017 |  |  |

| D        | 3.900           | 4.000 | 4.100 |  |  |

| Е        | 3.900           | 4.000 | 4.100 |  |  |

| е        | 0.450           | 0.500 | 0.550 |  |  |

| b        | 0.200           | 0.250 | 0.300 |  |  |

| L        | 0.350           | 0.400 | 0.450 |  |  |

| X1       | 0.825           | 0.875 | 0.925 |  |  |

| X2       | 0.825           | 0.875 | 0.925 |  |  |

| Х3       | 0.825           | 0.875 | 0.925 |  |  |

| X4       | 0.825           | 0.875 | 0.925 |  |  |

| X5       | 0.825           | 0.875 | 0.925 |  |  |

Figure. 9.1 Package Shape and Dimension

**10.Ordering Information**

| Part No.       | Temperature  | Auto-motive | Package Type | MSL | SPQ  |

|----------------|--------------|-------------|--------------|-----|------|

| NSD2621A-DQAGR | -40 to 125°C | NO          | QFN          | 3   | 4000 |

| NSD2621C-DQAGR | -40 to 125°C | NO          | QFN          | 3   | 4000 |

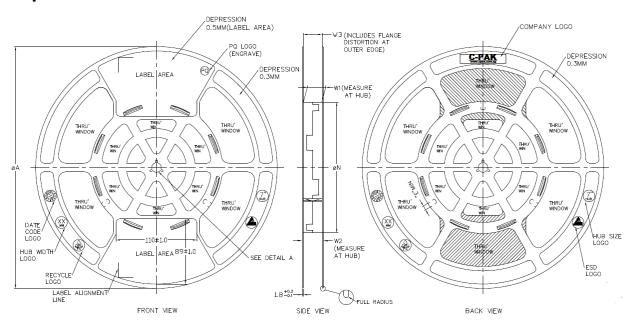

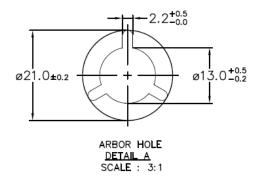

## 11. Tape and Reel Information

| PRODUCT SPECIFICATION |                    |                    |            |             |                      |            |

|-----------------------|--------------------|--------------------|------------|-------------|----------------------|------------|

| TAPE<br>WIDTH         | ØA<br><b>±</b> 2.0 | øN<br><b>±</b> 2.0 | W1         | W2<br>(MAX) | W3                   | E<br>(MIN) |

| 08MM                  | 330                | 178                | 8.4 = 1.5  | 14.4        |                      | 5.5        |

| 12MM                  | 330                | 178                | 12.4 1 2.0 | 18.4        | SHALL<br>ACCOMMODATE | 5.5        |

| 16MM                  | 330                | 178                | 16.4 100   | 22.4        | TAPE WIDTH           | 5.5        |

| 24MM                  | 330                | 178                | 24.4 = 20  | 30.4        | INTERFERENCE         | 5.5        |

| 32MM                  | 330                | 178                | 32.4 10.0  | 38.4        |                      | 5.5        |

| SURFACE RESISTIVITY |                                     |                      |            |  |  |

|---------------------|-------------------------------------|----------------------|------------|--|--|

| LEGEND              | SR RANGE                            | TYPE                 | COLOUR     |  |  |

| Α                   | BELOW 10 <sup>12</sup>              | ANTISTATIC           | ALL TYPES  |  |  |

| В                   | 10 <sup>6</sup> TO 10 <sup>11</sup> | STATIC DISSIPATIVE   | BLACK ONLY |  |  |

| С                   | 105 & BELOW 105                     | CONDUCTIVE (GENERIC) | BLACK ONLY |  |  |

| E                   | 10° TO 10 <sup>11</sup>             | ANTISTATIC (COATED)  | ALL TYPES  |  |  |

Figure. 11.1 Tape Information

Figure. 11.2 Reel Information

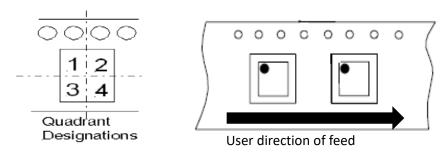

Figure. 11.3 Quadrant Designation for Pin1 Orientation in Tape

# **12.Revision History**

| Revision | Description                                                            | Date       |

|----------|------------------------------------------------------------------------|------------|

| 1.0      | Initial version                                                        | 2023/12/27 |

| 1.1      | Update the deadtime resistor configuration value.                      | 2024/05/13 |

| 1.2      | Update the SPQ from 2500 to 4000                                       | 2024/06/24 |

| 1.3      | Update the description about the recommended value of R <sub>DT.</sub> | 2025/09/02 |

#### IMPORTANT NOTICE

The information given in this document (the "Document") shall in no event be regarded as any warranty or authorization of, express or implied, including but not limited to accuracy, completeness, merchantability, fitness for a particular purpose or infringement of any third party's intellectual property rights.

Users of this Document shall be solely responsible for the use of NOVOSENSE's products and applications, and for the safety thereof. Users shall comply with all laws, regulations and requirements related to NOVOSENSE's products and applications, although information or support related to any application may still be provided by NOVOSENSE.

This Document is provided on an "AS IS" basis, and is intended only for skilled developers designing with NOVOSENSE's products. NOVOSENSE reserves the rights to make corrections, modifications, enhancements, improvements or other changes to the products and services provided without notice. NOVOSENSE authorizes users to use this Document exclusively for the development of relevant applications or systems designed to integrate NOVOSENSE's products. No license to any intellectual property rights of NOVOSENSE is granted by implication or otherwise. Using this Document for any other purpose, or any unauthorized reproduction or display of this Document is strictly prohibited. In no event shall NOVOSENSE be liable for any claims, damages, costs, losses or liabilities arising out of or in connection with this Document or the use of this Document.

For further information on applications, products and technologies, please contact NOVOSENSE (www.novosns.com).

Suzhou NOVOSENSE Microelectronics Co., Ltd