# NT35410

One-chip Driver IC with internal GRAM for 16.77M colors 360 RGB x 640 dot TFT LCD with CPU / RGB / MIPI / MDDI interface

V2.0 2011/10/06

# Index

| REVISION HISTORY                                     | 11         |

|------------------------------------------------------|------------|

| 1 DESCRIPTION                                        | 12         |

| 2 FEATURES                                           | 12         |

| 3 BLOCK DIAGRAM                                      | 14         |

| 4 PIN DESCRIPTION                                    | 15         |

| 4.1 POWER SUPPLY PINS                                | <b>11</b>  |

| 4.2 MODE SELECTION PINS                              | 15         |

| 4.3 INTERFACE LOGIC PINS                             | 16         |

| 4.4 MIPI / MDDI INTERFACE PINS                       |            |

| 4.5 CABC Control Pins                                |            |

| 4.6 Others                                           | 19         |

| 4.7 DRIVER OUTPUT PINS                               | <u></u> 19 |

| 4.8 DC/DC CONVERTER PINS                             | 20         |

| 5 FUNCTIONAL DESCRIPTION                             | 21         |

| 5.1 MPU INTERFACE                                    | 21         |

| 5.1.1 Interface Type Selection                       | 21         |

| 5.1.2 80-series MPU Interface                        | 22         |

| 5.1.2.1 Write cycle sequence                         | 23         |

| 5.1.2.2 Read cycle sequence                          |            |

| 5.1.3 Display Data Format                            | 26         |

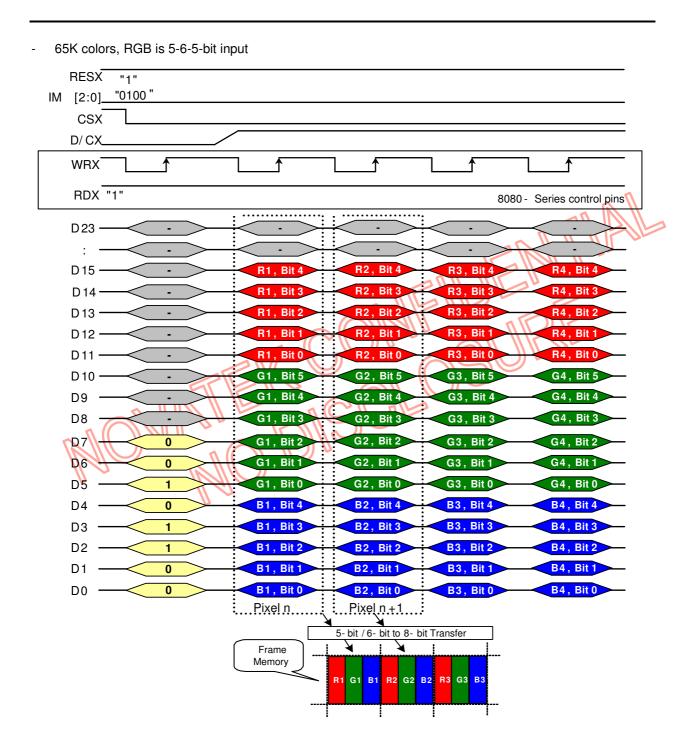

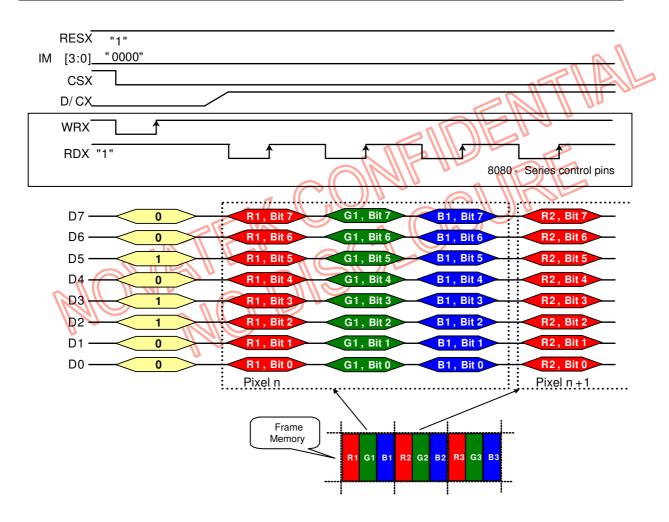

| 5.1.3.1 8-bit parallel interface for data ram write  | 26         |

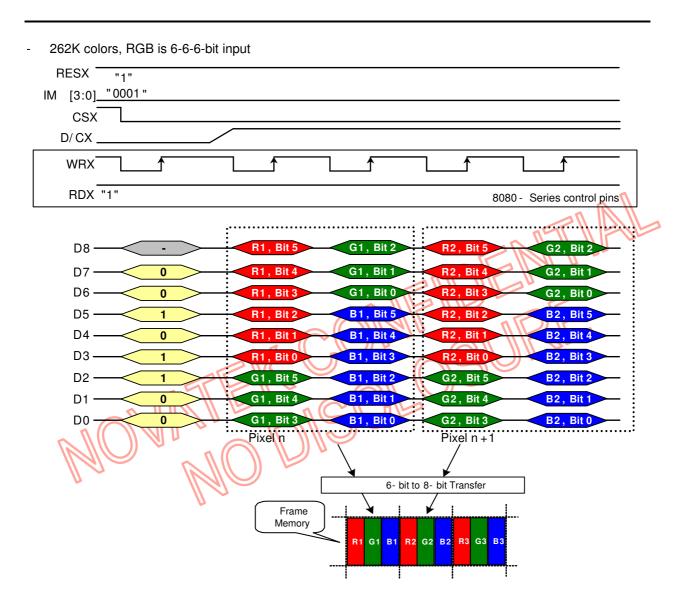

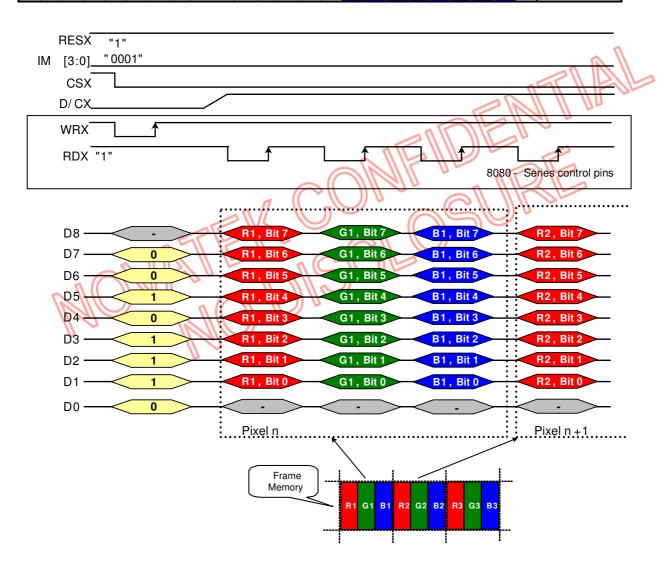

| 5.1.3.2 9-bit parallel interface for data ram write  | 30         |

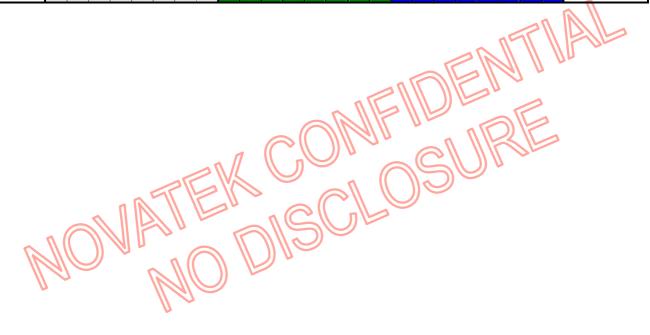

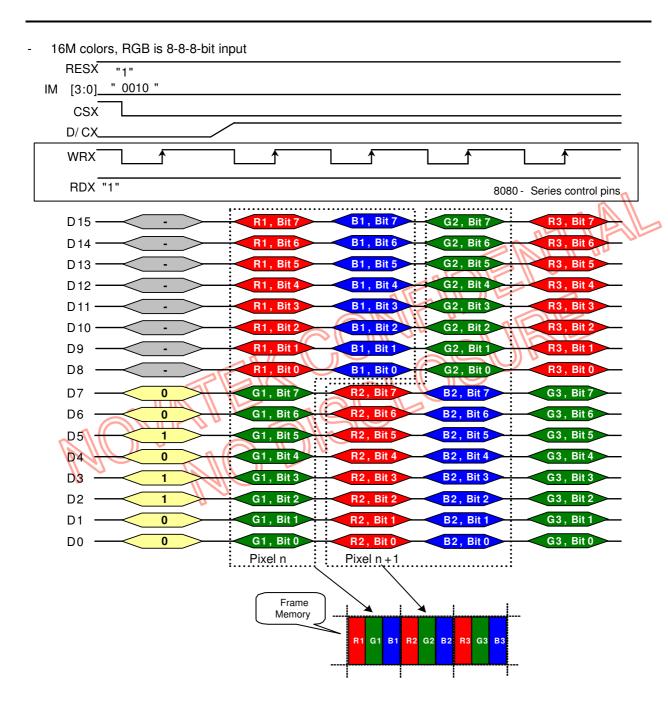

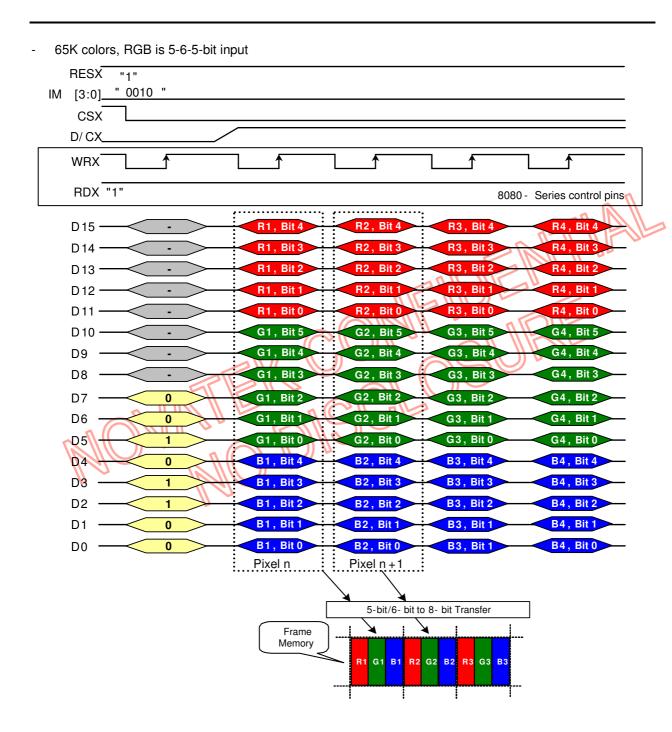

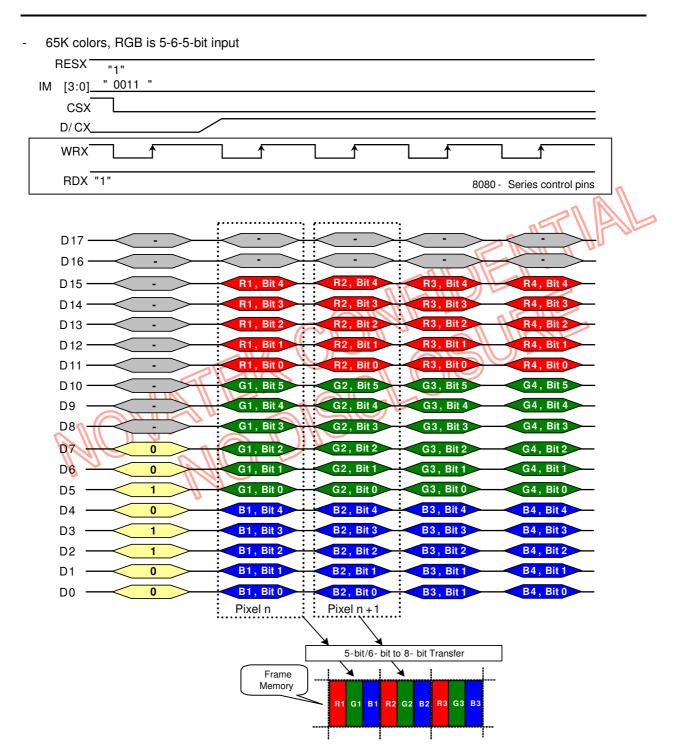

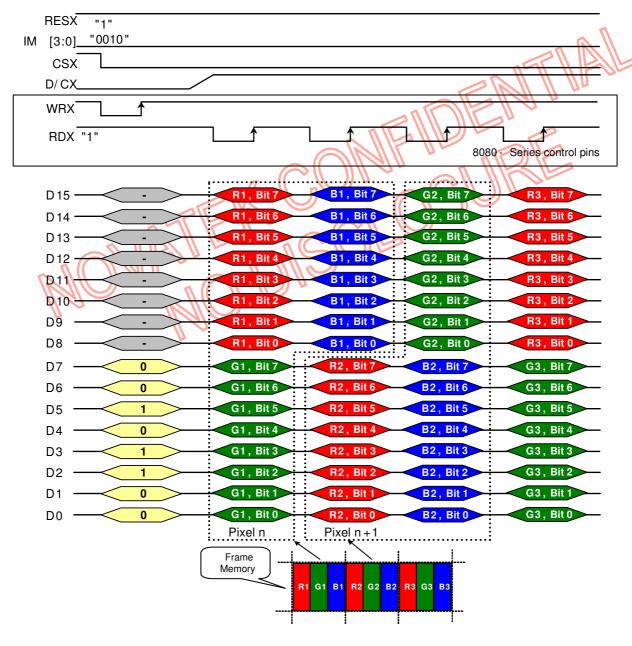

| 5.1.3.3 16-bit parallel interface for data ram write | 33         |

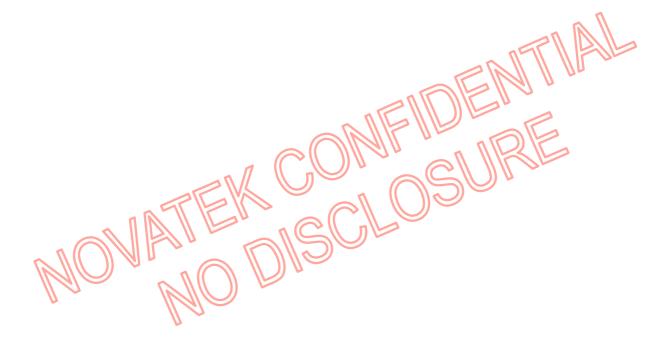

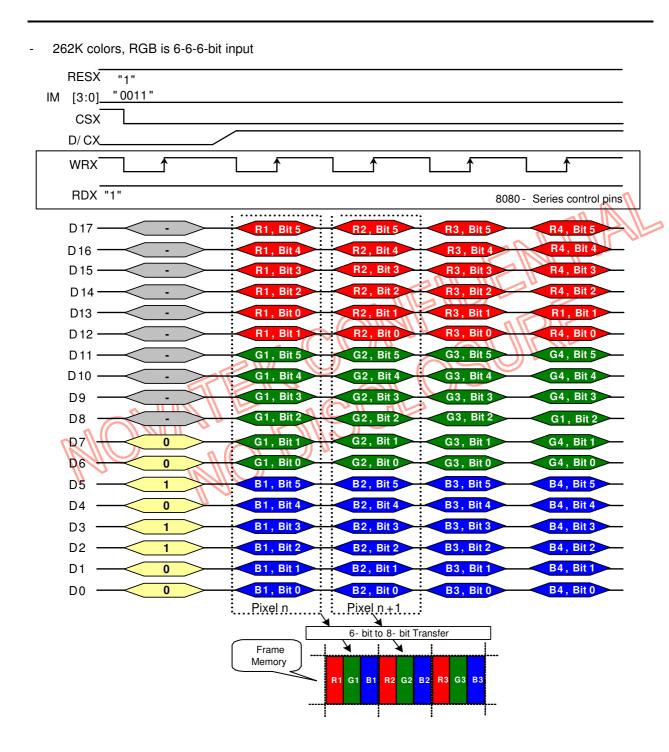

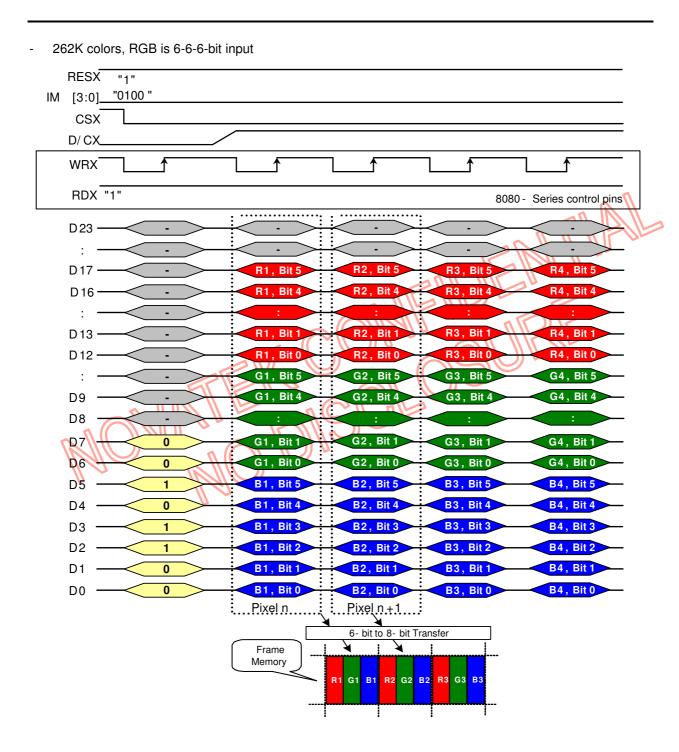

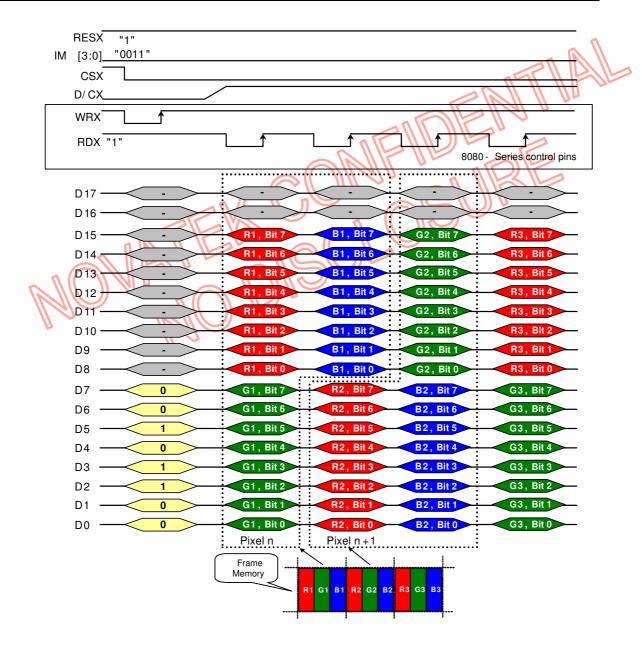

| 5.1.3.4 18-bit parallel interface for data ram write | 37         |

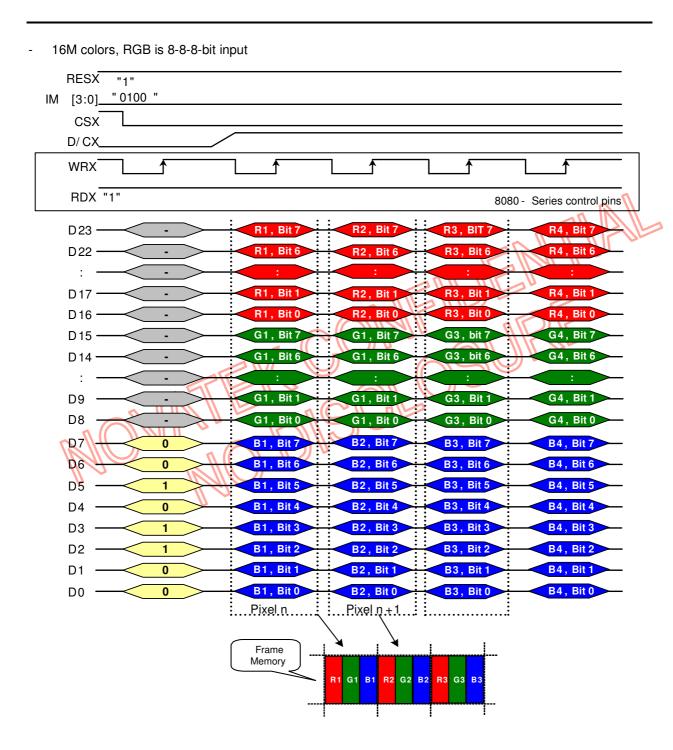

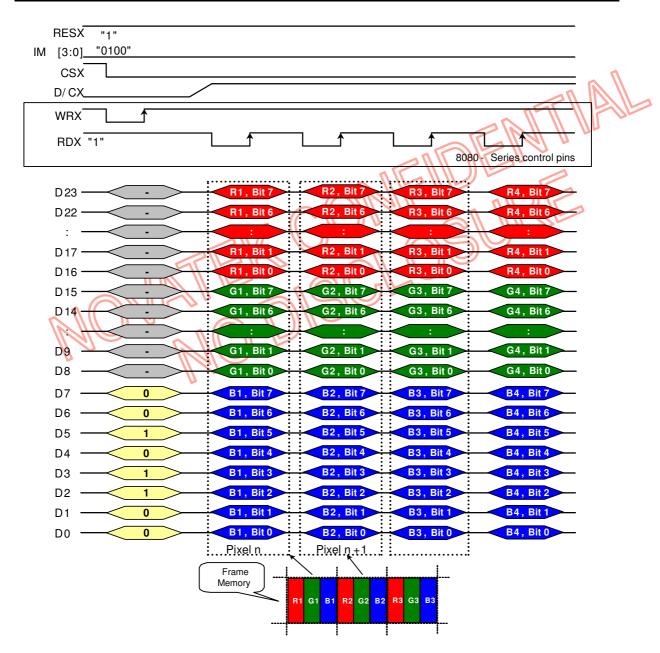

| 5.1.3.5 24-bit parallel interface for data ram write | 41         |

| 5.1.3.6 8-bit parallel interface for data ram read   | 45         |

| 5.1.3.7 9-bit parallel interface for data ram read   | 46         |

| 5.1.3.8 24-bit parallel interface for data ram read  | 49         |

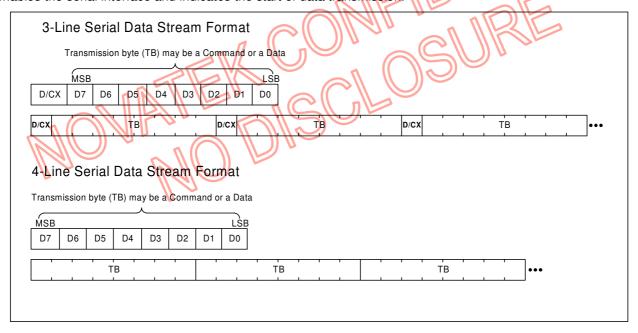

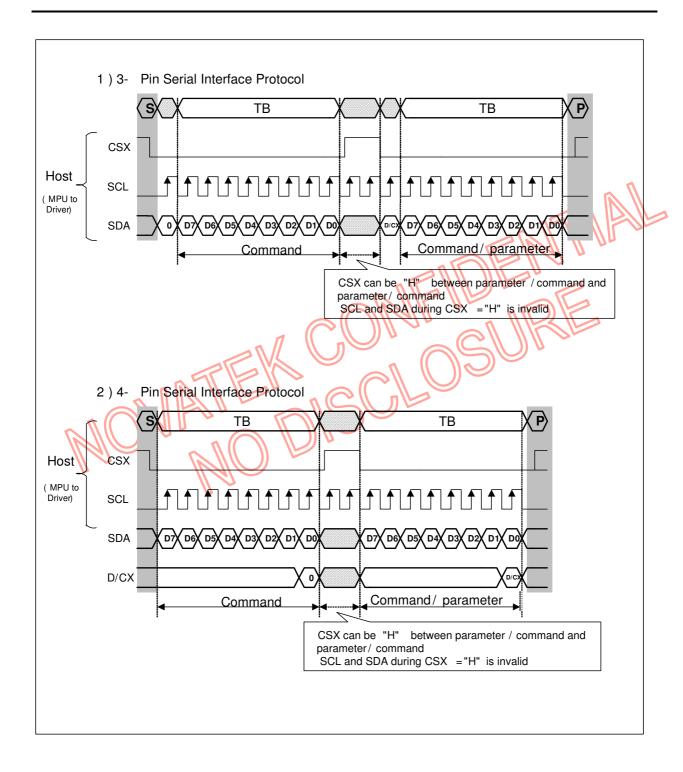

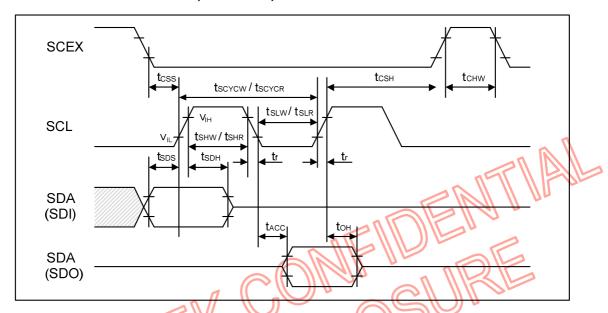

| 5.2 SERIAL INTERFACE                                 | 50         |

| 5.2.1 Interface Type Selection                       | 50         |

| 5.2.2 Serial Interface                               | 51         |

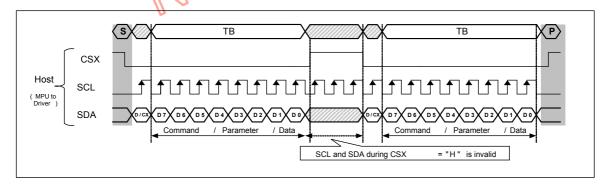

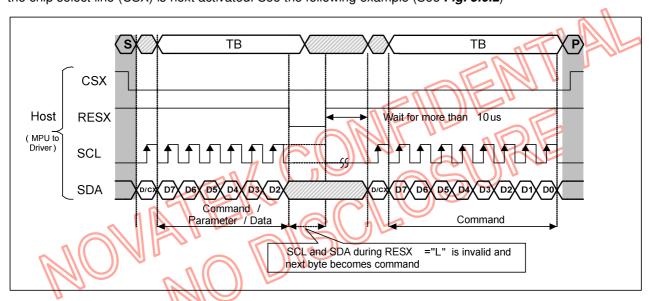

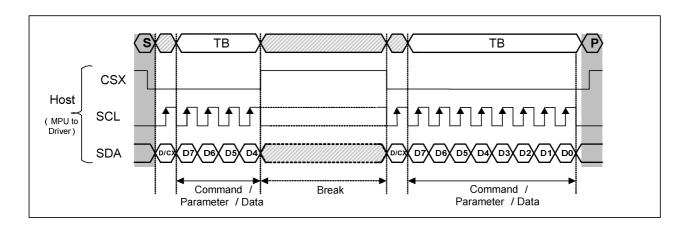

| 5.2.2.1 Write Mode                                   | 51         |

| 2011/10/06 2                                         | V2.0       |

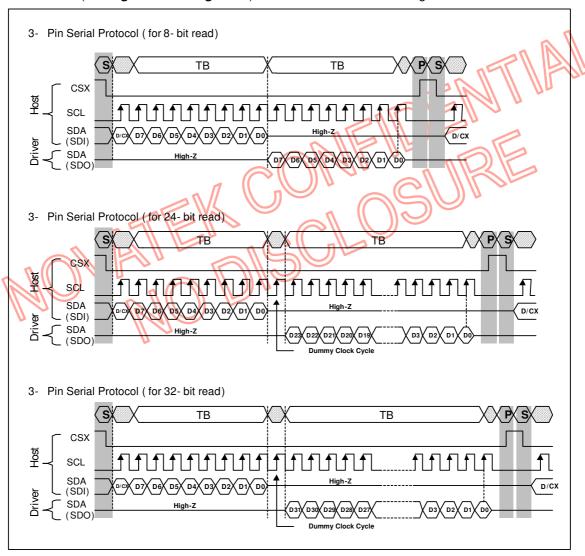

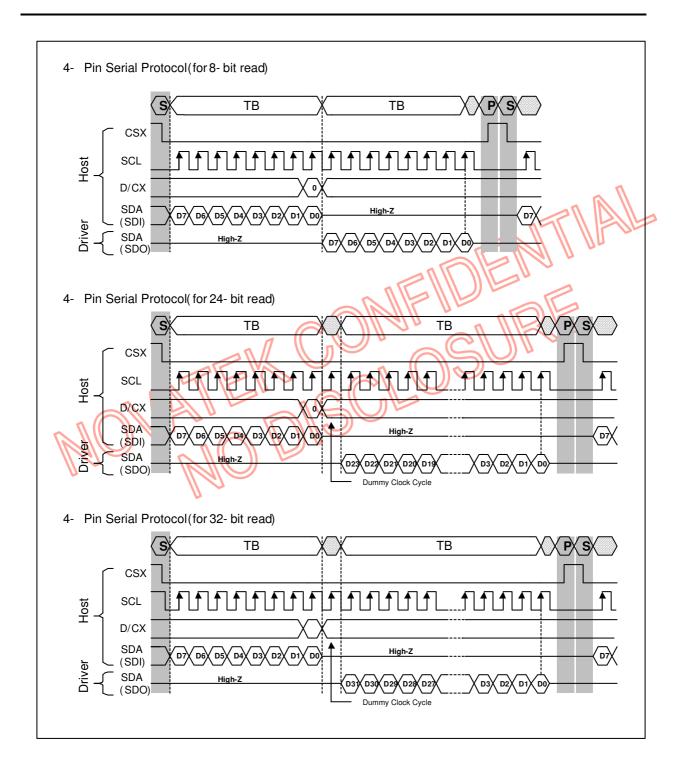

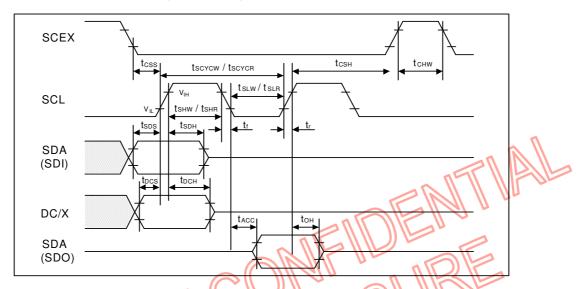

| 5.2.2.2 Read Mode                                                 | 53          |

|-------------------------------------------------------------------|-------------|

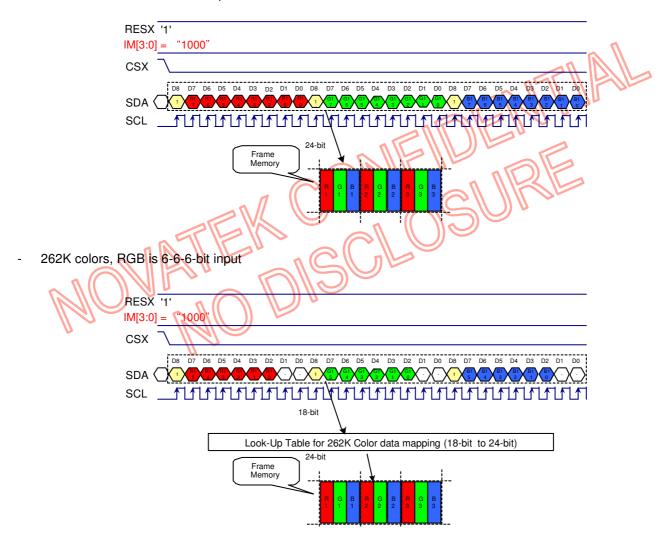

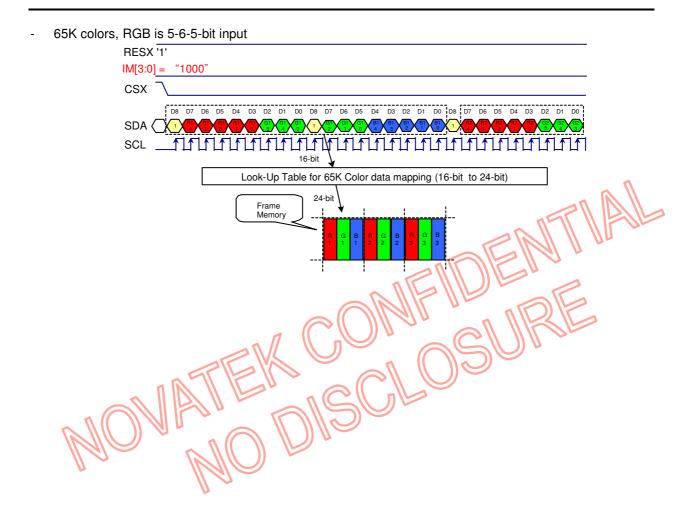

| 5.2.3 Display Data Format                                         | 55          |

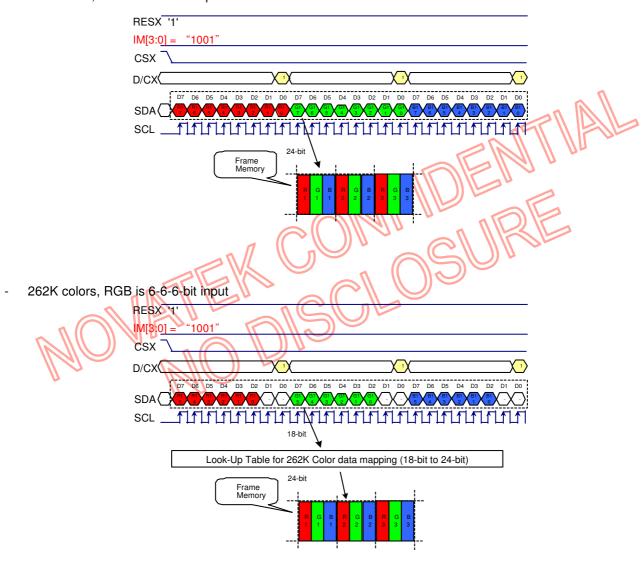

| 5.2.3.1 3-pins Serial Interface for DATA RAM write                | 55          |

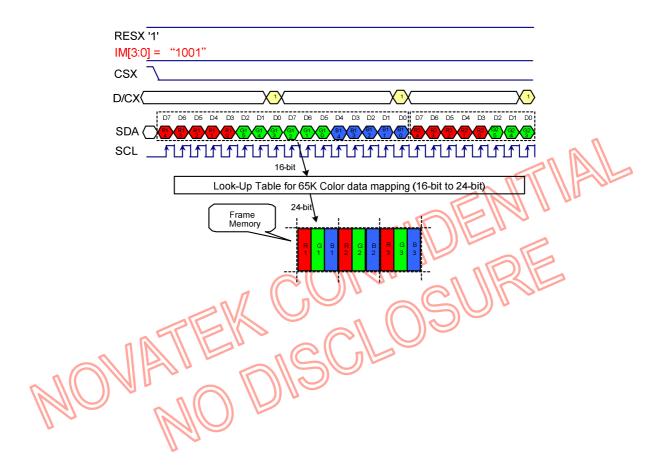

| 5.2.3.2 4-pins Serial Interface for DATA RAM write                | 57          |

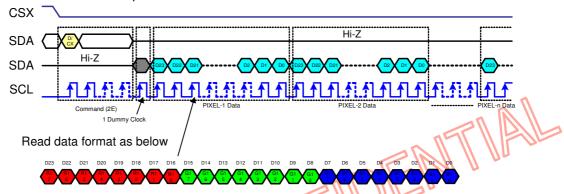

| 5.2.3.3 3-pins Serial Interface for DATA RAM READ                 | 59          |

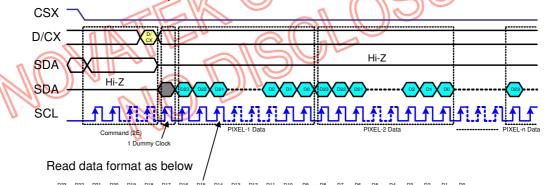

| 5.2.3.4 4-pins Serial Interface for DATA RAM READ                 | 59          |

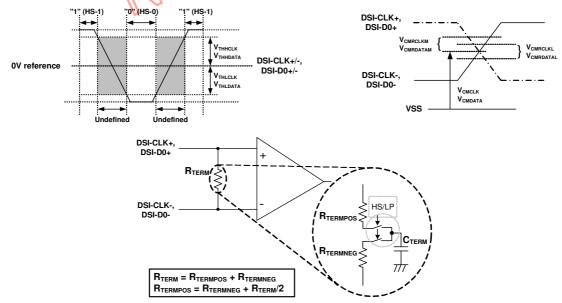

| 5.3 MIPI INTERFACE                                                | 60          |

| 5.3.1 Interface Type Selection                                    |             |

| 5.3.2 MIPI                                                        | 61          |

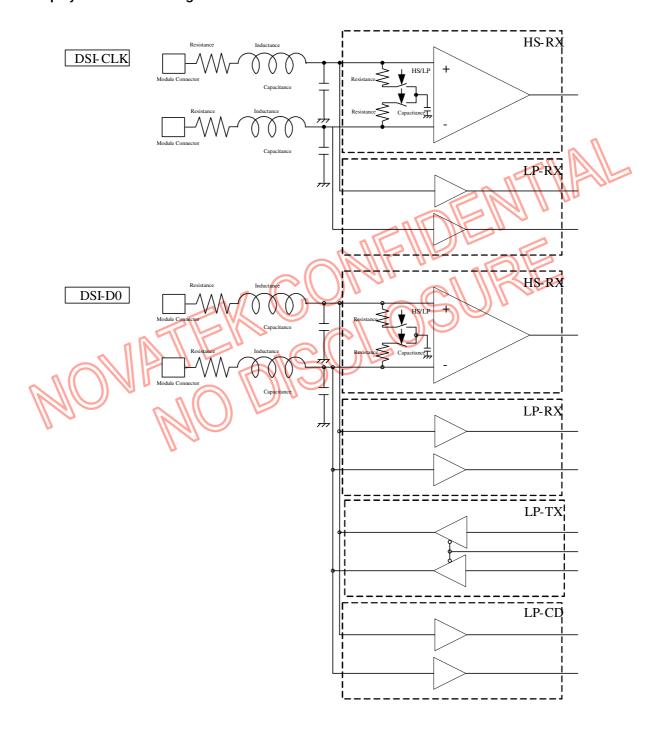

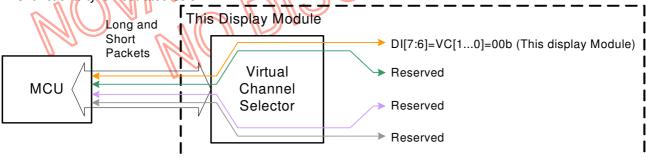

| 5.3.3 Display Module Pin Configuration for DSI                    | <b>1</b> 62 |

| 5.3.4 Display Serial Interface (DSI)                              | 63          |

| 5.3.4.1 General Description                                       |             |

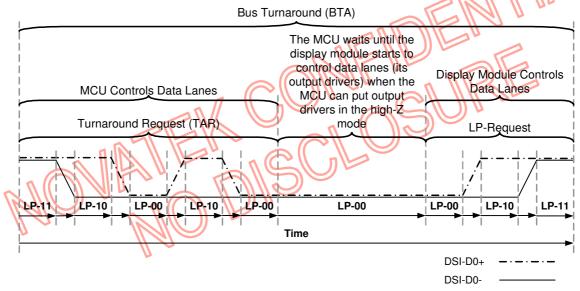

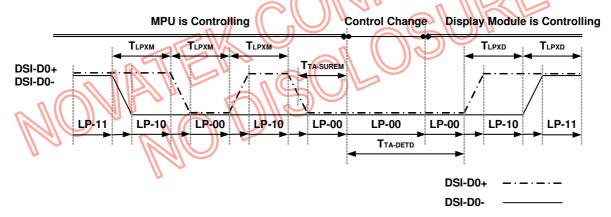

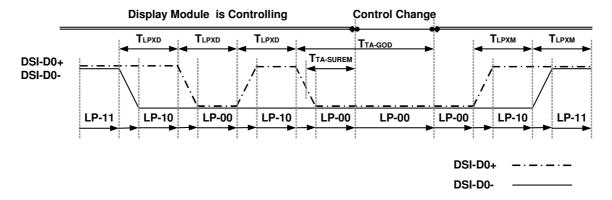

| 5.3.4.2 Interface Level Communication                             | 63          |

| 5.3.4.2.1 General                                                 | 63          |

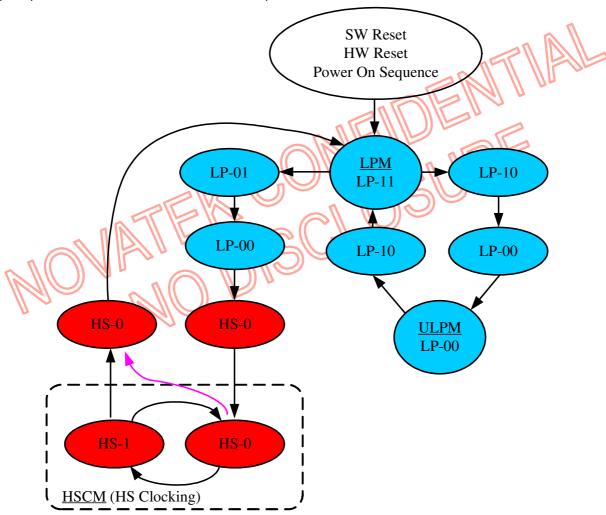

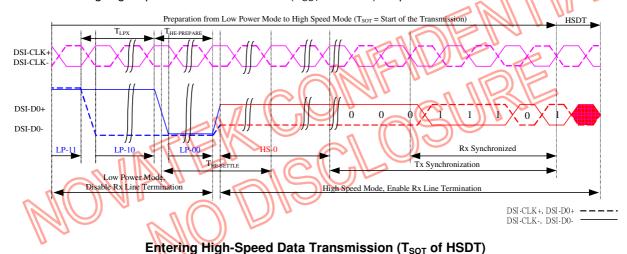

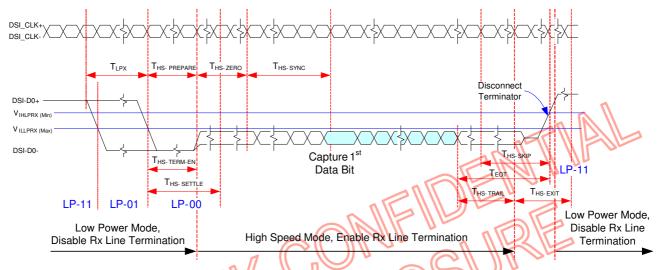

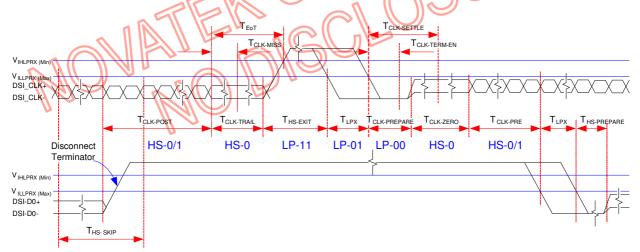

| 5.3.4.2.2 DSI-CLK Lanes                                           |             |

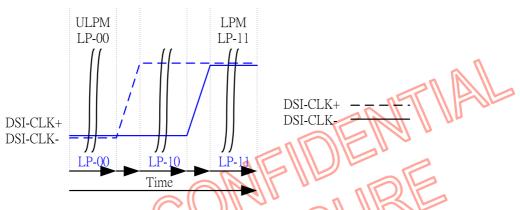

| 5.3.4.2.2.1 Low Power Mode (LPM)                                  | 65          |

| 5.3.4.2.2.2 Ultra Low Power Mode (uLPM)                           | 67          |

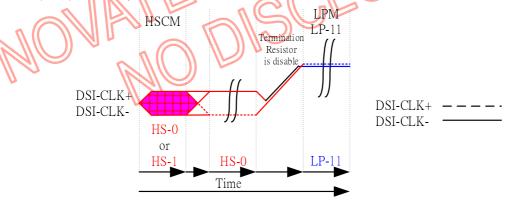

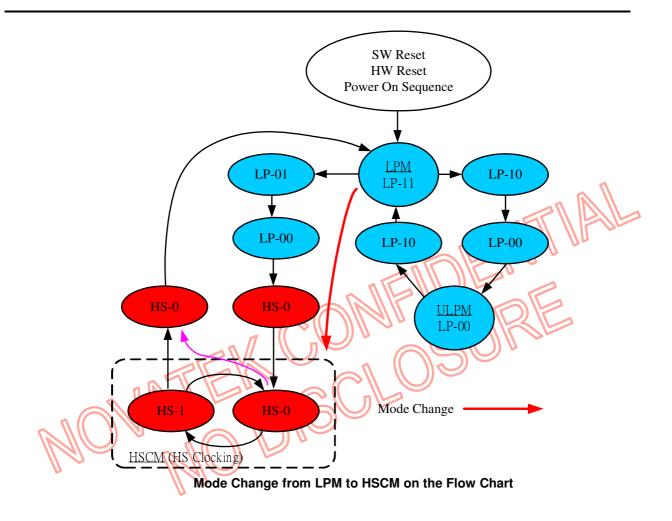

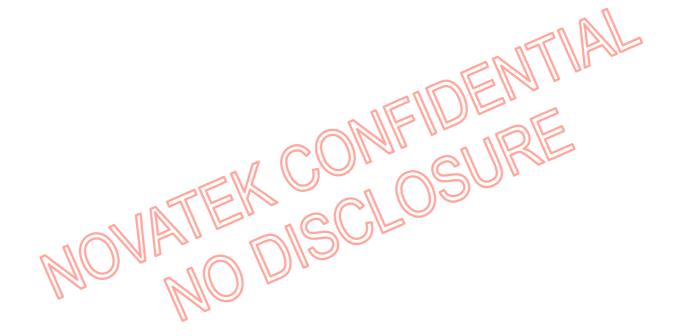

| 5.3.4.2.2.3 High Speed Clock Mode (HSCM)                          | 69          |

| 5.3.4.2.3 DSI-Data Lanes                                          | 73          |

| 5.3.4.2.3.1 General                                               | 73          |

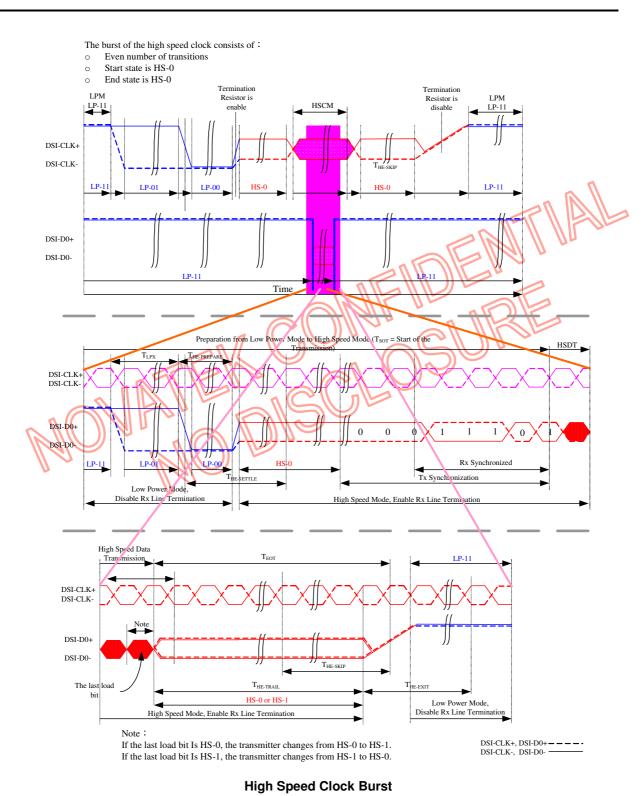

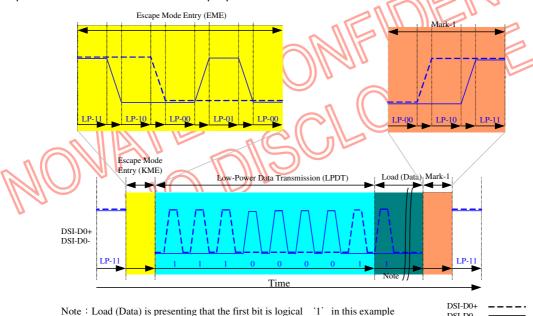

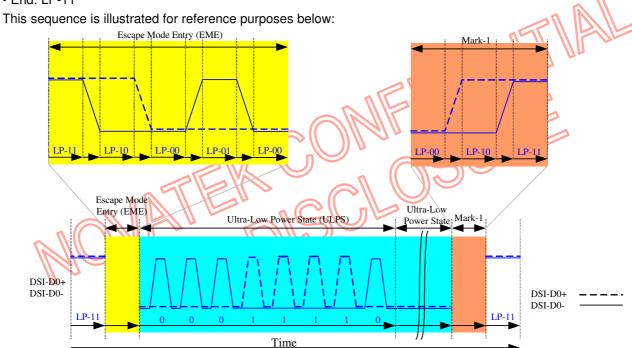

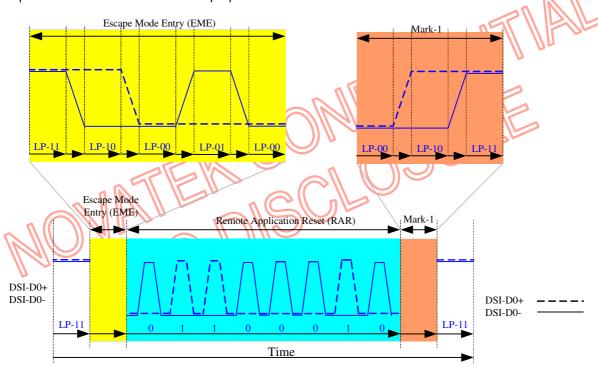

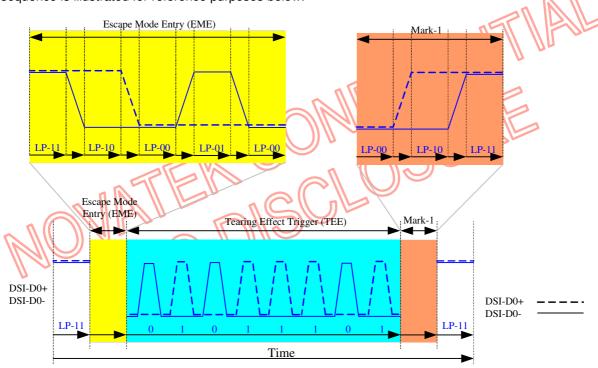

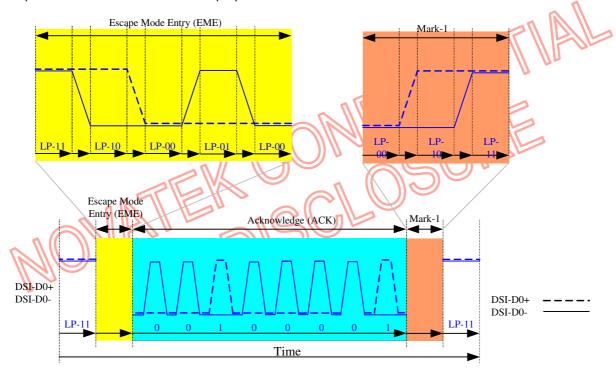

| 5.3.4.2.3.2 Escape Modes                                          | 73          |

| 5.3.4.2.3.3 High Speed Data Transmission (HSDT)                   | 80          |

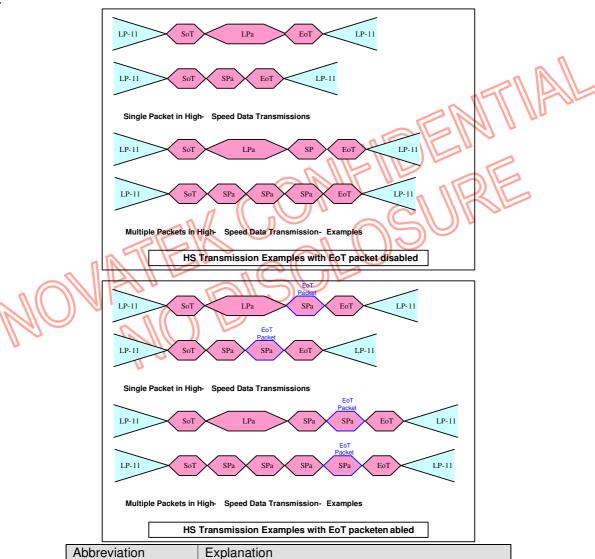

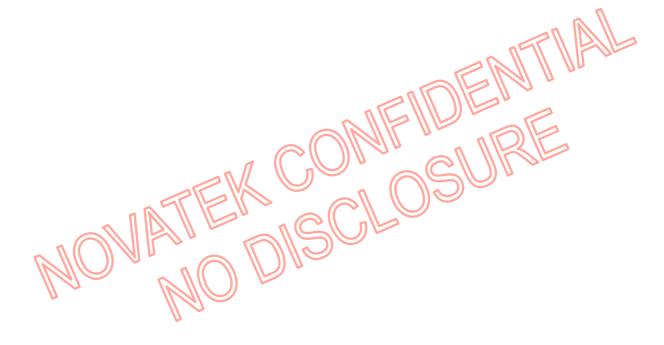

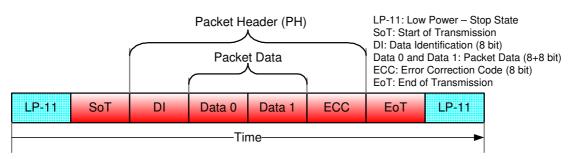

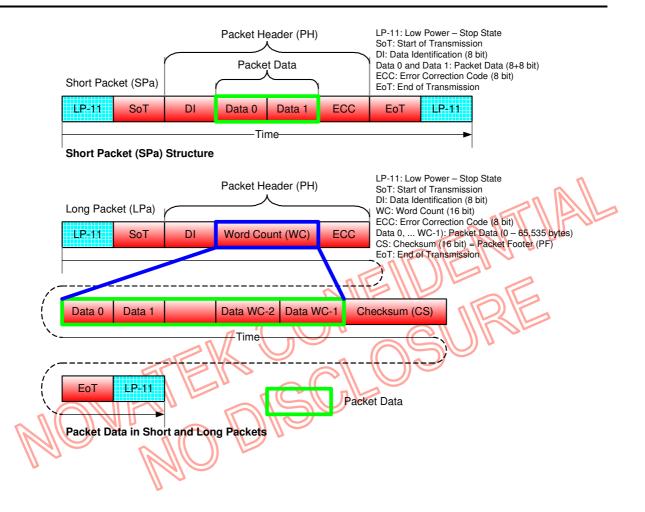

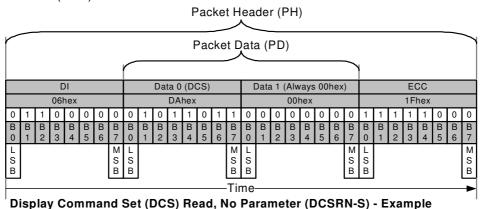

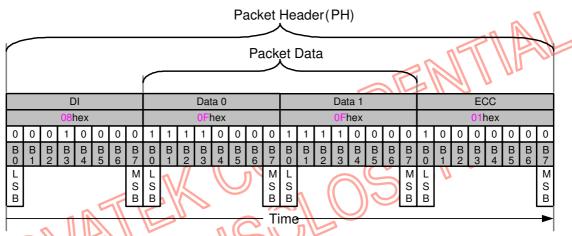

| 5.3.4.3 Packet Level Communication                                | 84          |

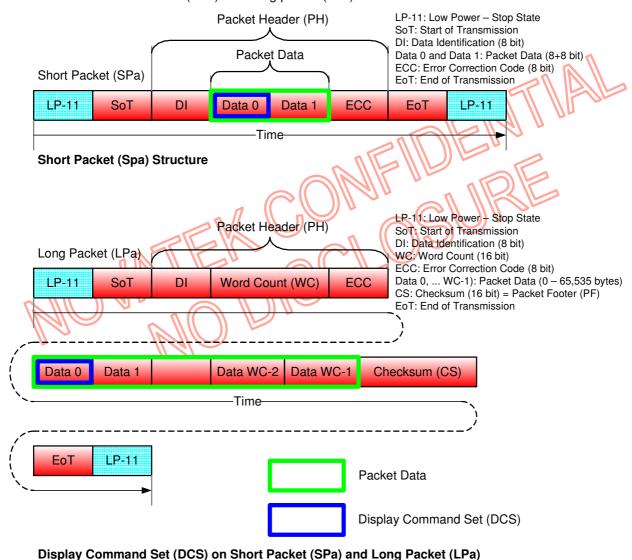

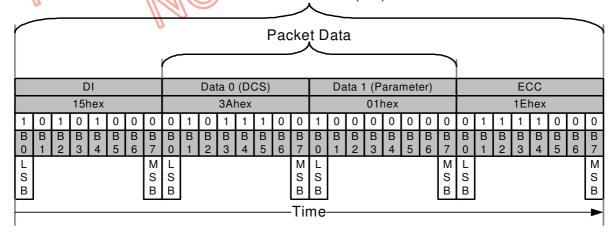

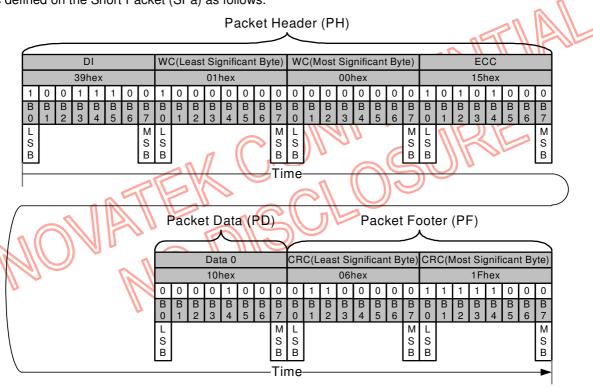

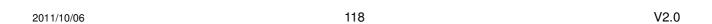

| 5.3.4.3.1 Short Packet (SPa) and Long Packet (IPa) Structure      | 84          |

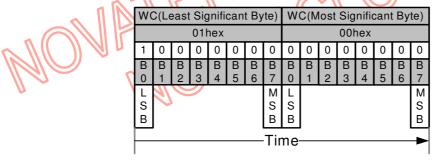

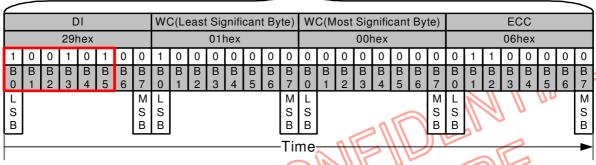

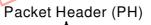

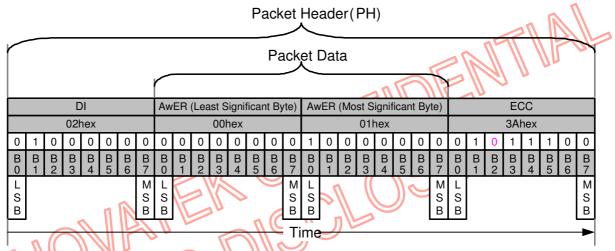

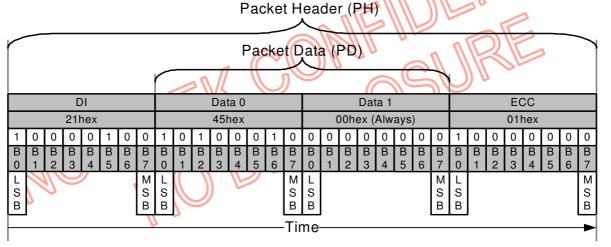

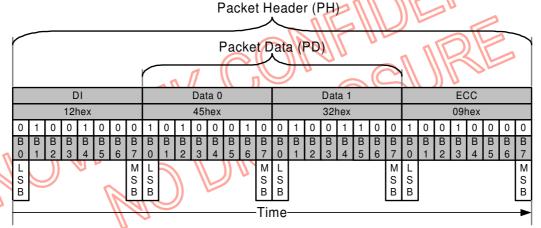

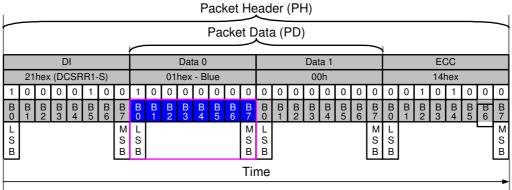

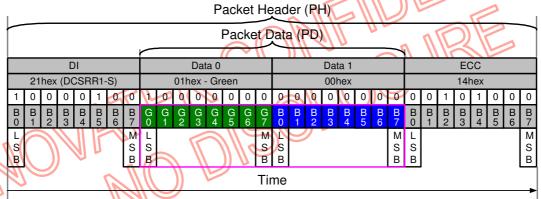

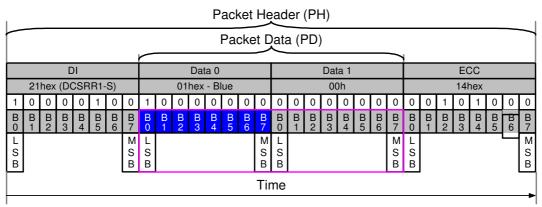

| 5.3.4.3.1.1 Bit Order of the Byte on Packets                      | 86          |

| 5.3.4.3.1.2 Bit Order of the Multiple Byte Information on Packets | 86          |

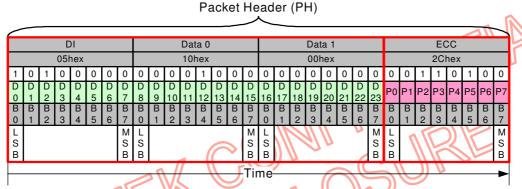

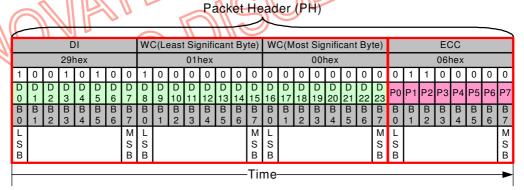

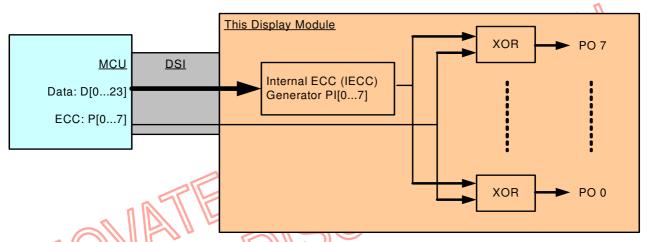

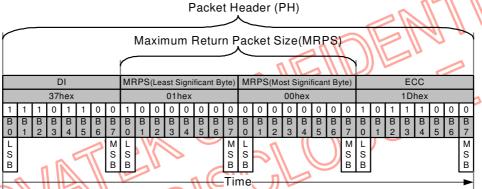

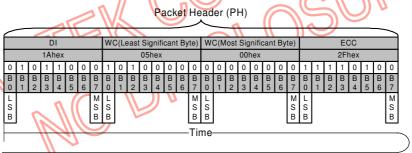

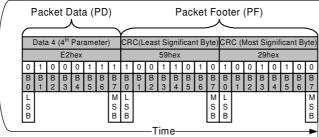

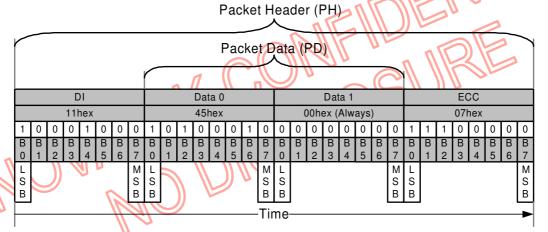

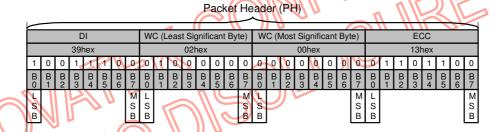

| 5.3.4.3.1.3 Packet Header (PH)                                    | 87          |

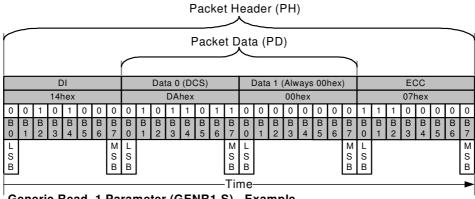

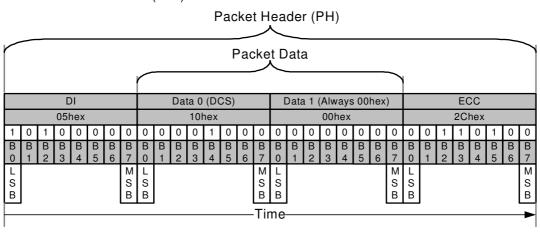

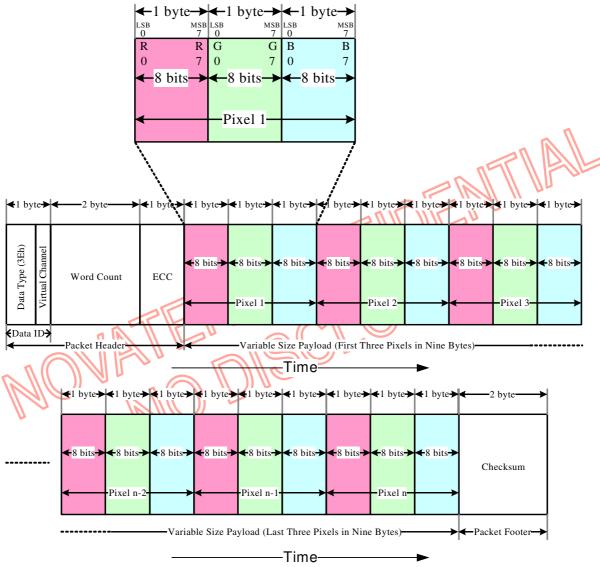

| 5.3.4.3.1.4 Packet Data (PD) on the Long Packet (LPa)             | 101         |

| 5.3.4.3.1.5 Packet Footer (PF) on the Long Packet (LPa)           | 101         |

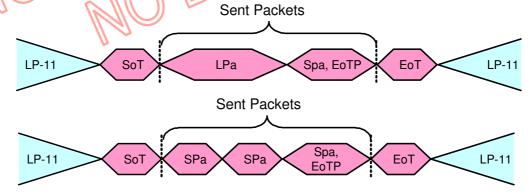

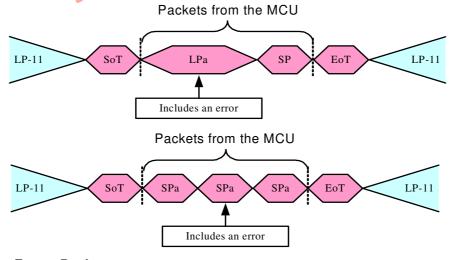

| 5.3.4.3.2 Packet Transmissions                                    | 103         |

| 5.3.4.3.2.1 Packet from the MCU to the Display Module             | 103         |

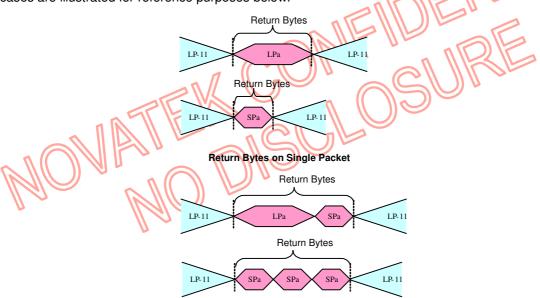

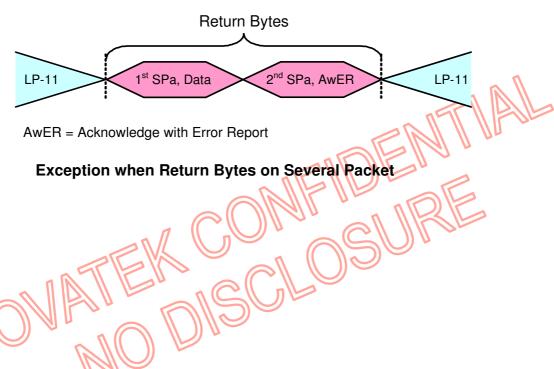

| 5.3.4.3.2.2 Packet from the Display Module to the MCU             | 136         |

| 5.3.4.3.3 Communication Sequences                                 | 147         |

| 2011/10/06 3                                                      | V2.0        |

| 5.3.4.3.3.1 General                                      | 147                                    |

|----------------------------------------------------------|----------------------------------------|

| 5.3.4.3.3.2 Sequences                                    | 148                                    |

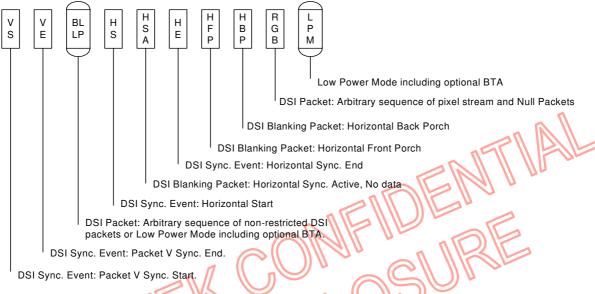

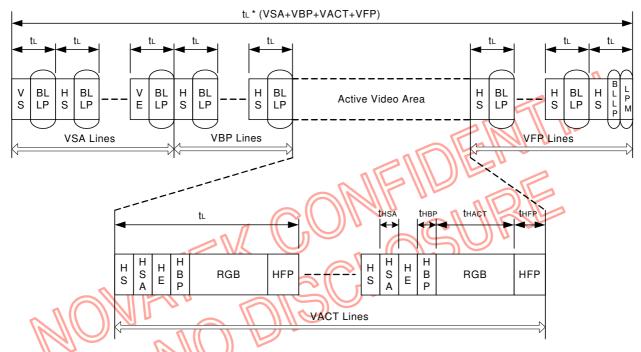

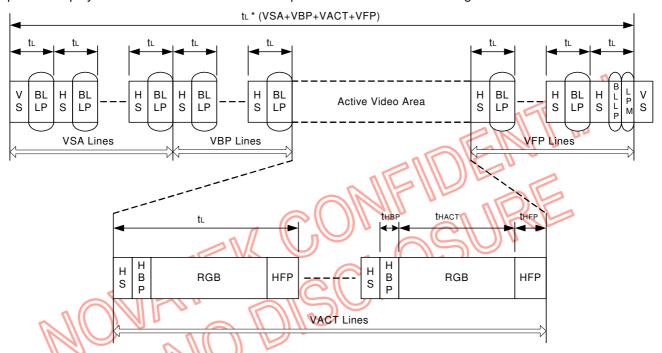

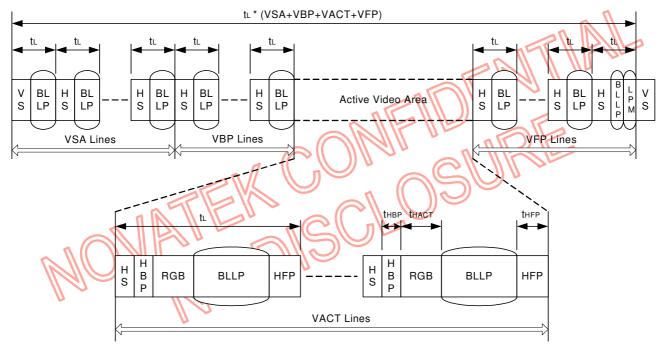

| 5.3.4.4 Video Mode Communication                         | 155                                    |

| 5.3.4.4.1 Transmission Packet Sequences                  | 155                                    |

| 5.3.4.4.2 Non-Burst Mode with Sync Pulses                | 157                                    |

| 5.3.4.4.3 Non-Burst Mode                                 | 158                                    |

| 5.3.4.4.4 Burst Mode                                     |                                        |

| 5.3.4.4.5 Parameters                                     | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |

| 5.3.5 Memory Write/Read Format                           | 161                                    |

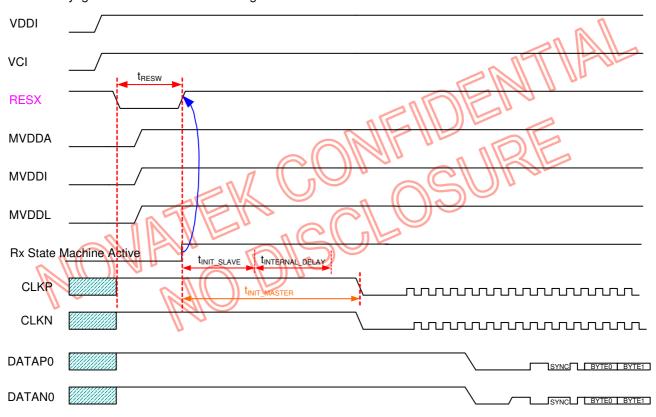

| 5.3.6 System Power-Up and Initialization                 | 168                                    |

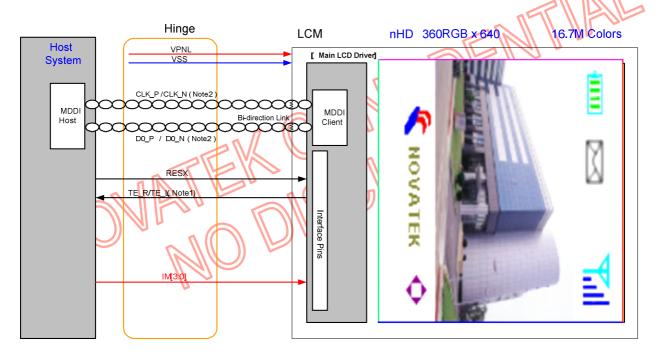

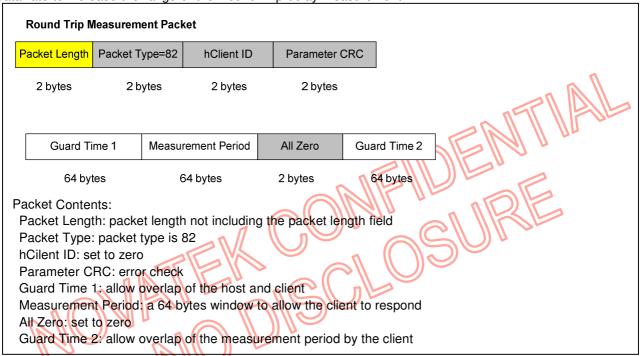

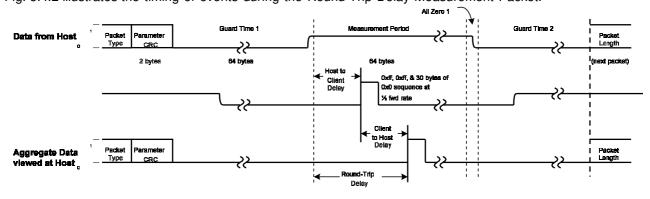

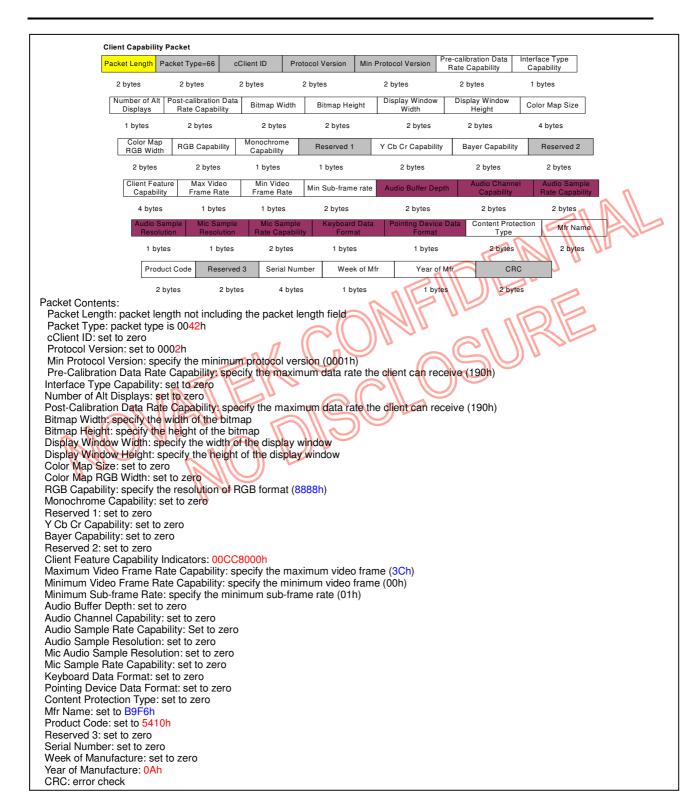

| 5.4 MDDI INTERFACE                                       | 169                                    |

| 5.4.1 MDDI Link Protocol by The NT35410                  | 170                                    |

| 5.4.2 MDDI Link Packet Descriptions by the NT35410       | 171                                    |

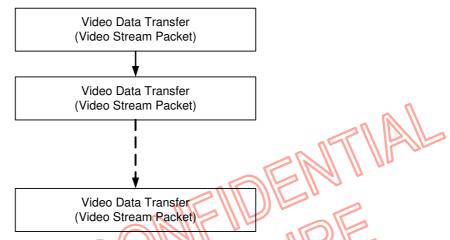

| 5.4.3 Writing Video Data to Memory Sequence              | 184                                    |

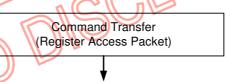

| 5.4.4 Writing Register Sequence                          | 184                                    |

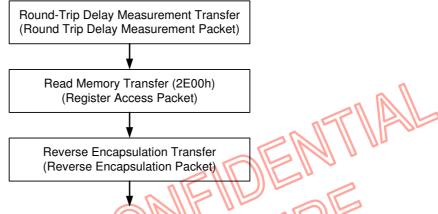

| 5.4.5 Reading Video Data from Memory Sequence            | 185                                    |

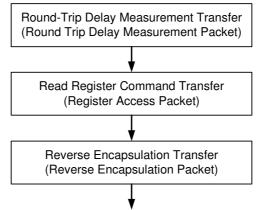

| 5.4.6 Reading Register Sequence                          | 185                                    |

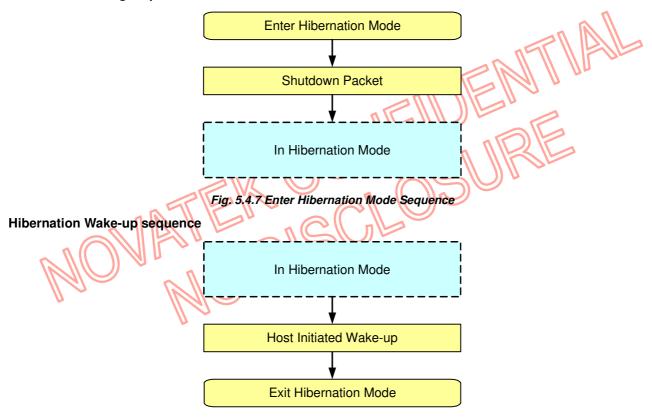

| 5.4.7 Hibernation Setting                                | 186                                    |

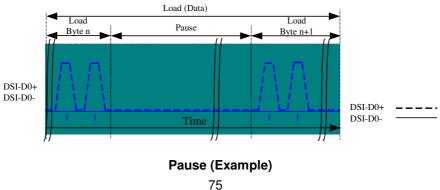

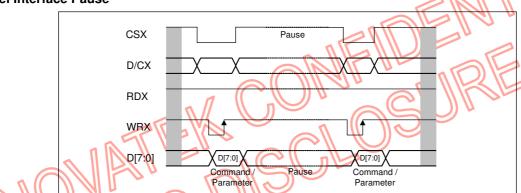

| 5.5 INTERFACE PAUSE.                                     | 187                                    |

| 5.6 DATA TRANSFER RECOVERY                               | 188                                    |

| 5.7 DISPLAY MODULE DATA TRANSFER MODES                   | 191                                    |

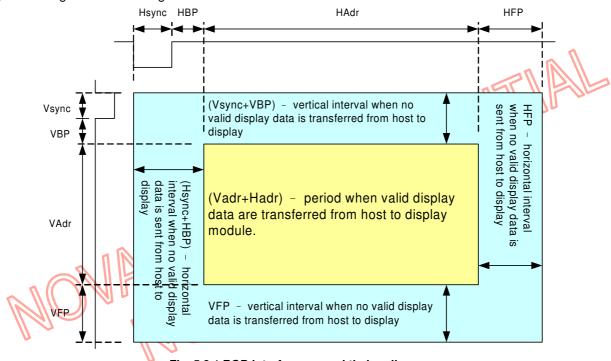

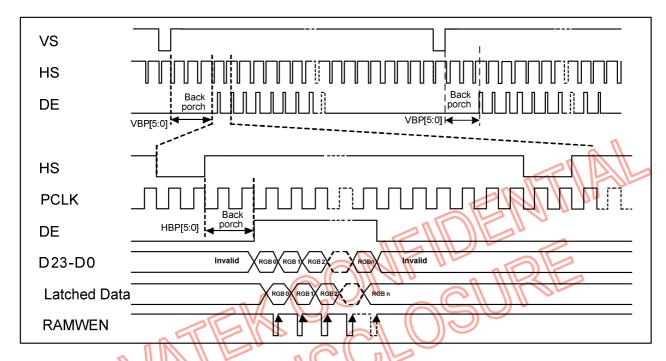

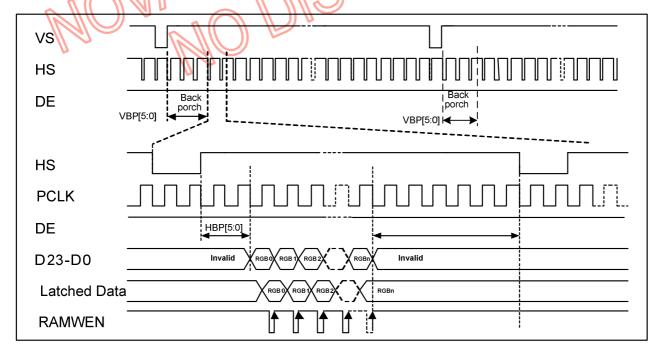

| 5.8 RGB INTERFACE                                        | 192                                    |

| 5.8.1 General Description                                | 192                                    |

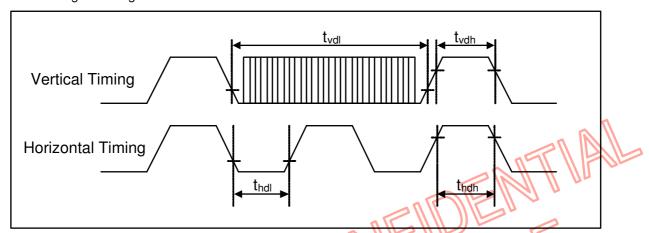

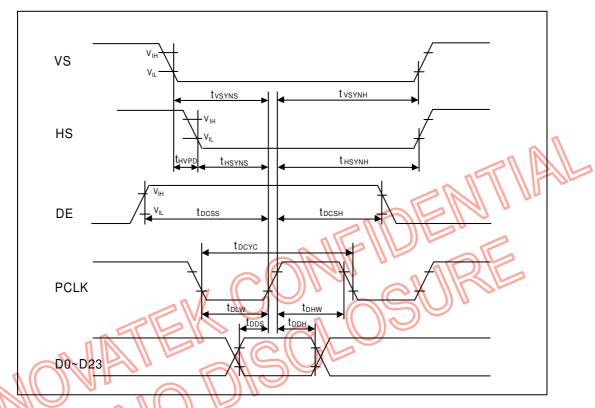

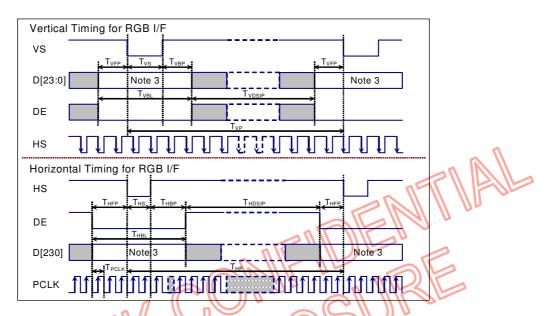

| 5.8.2 RGB Interface Timing Chart                         | 193                                    |

| 5.8.3 RGB Interface Mode Set                             | 195                                    |

| 5.8.3.1 Interface Type Selection                         | 195                                    |

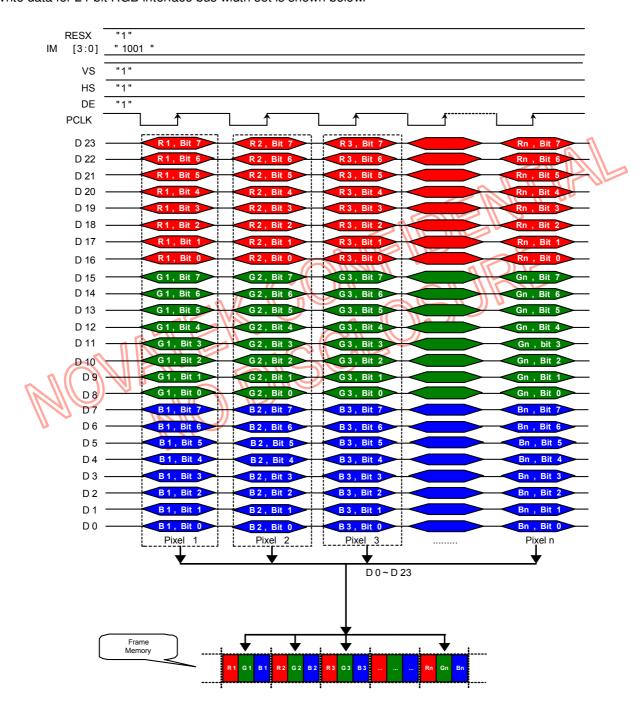

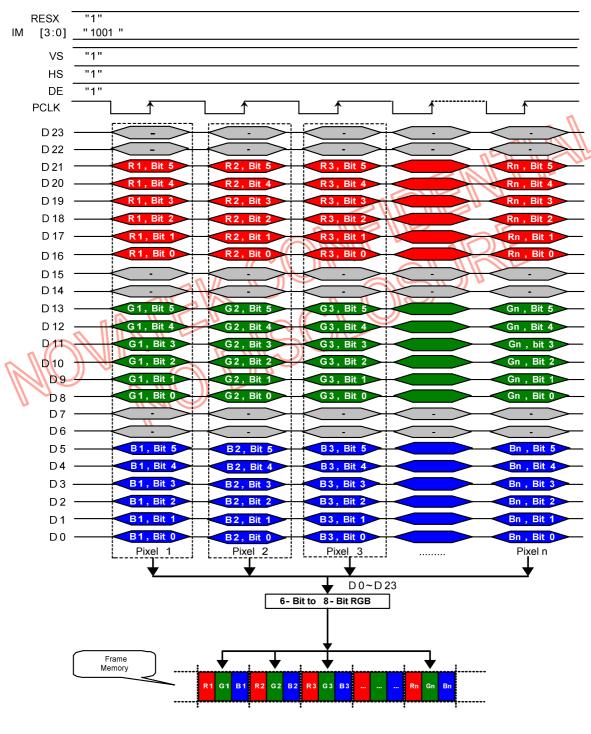

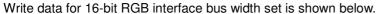

| 5.8.4 RGB Interface Bus Width Set                        | 196                                    |

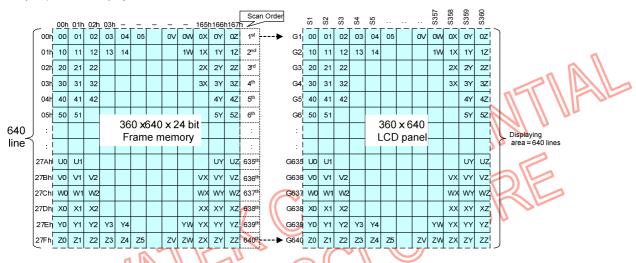

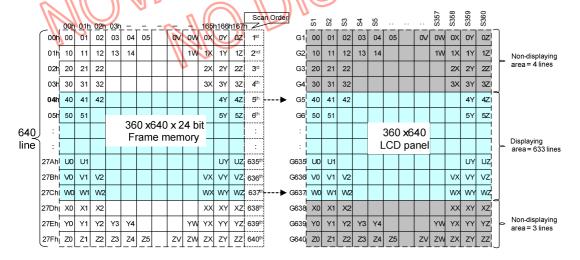

| 5.9 FRAME MRMORY                                         | 200                                    |

| 5.9.1 Address Counter                                    | 200                                    |

| 5.9.3 Interface to Memory Write Direction                |                                        |

| 5.9.4 Frame Memory to Display Address Mapping            |                                        |

| 5.9.4.1 using 360RGB x 640 resolution (SMX=SMY=SRGB='0') |                                        |

| 5.9.5 Normal Display On or Partial Mode On               |                                        |

| 2011/10/06 4                                             | V2.0                                   |

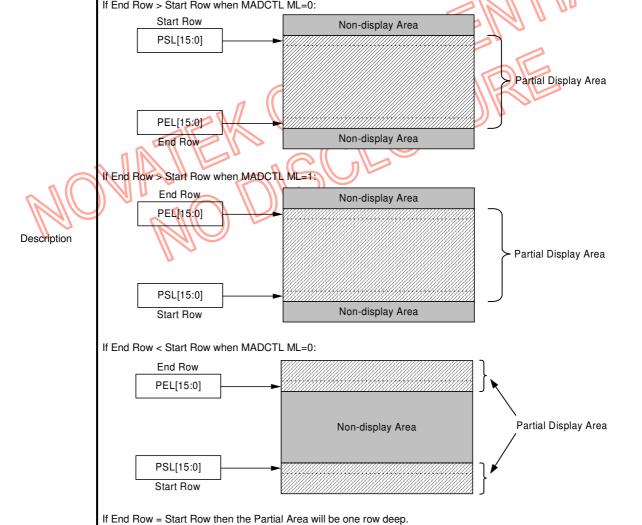

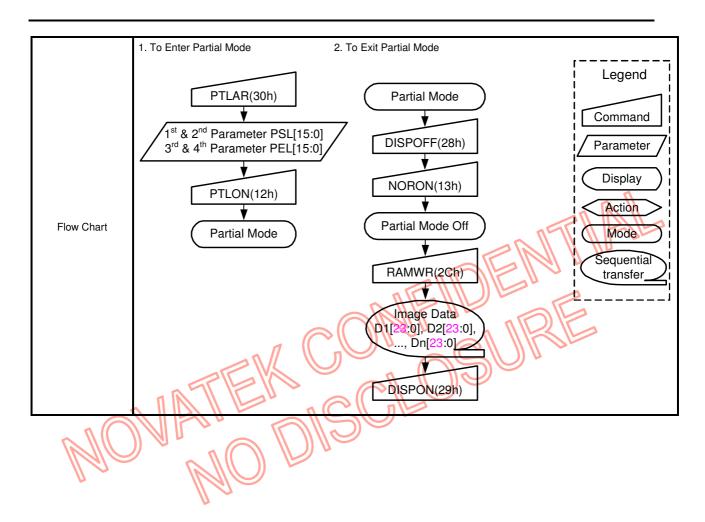

| 5.9.5.1 Partial Mode                                                   | 203  |

|------------------------------------------------------------------------|------|

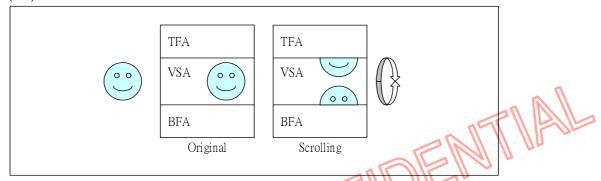

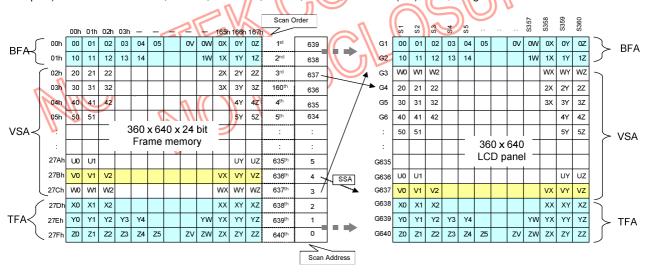

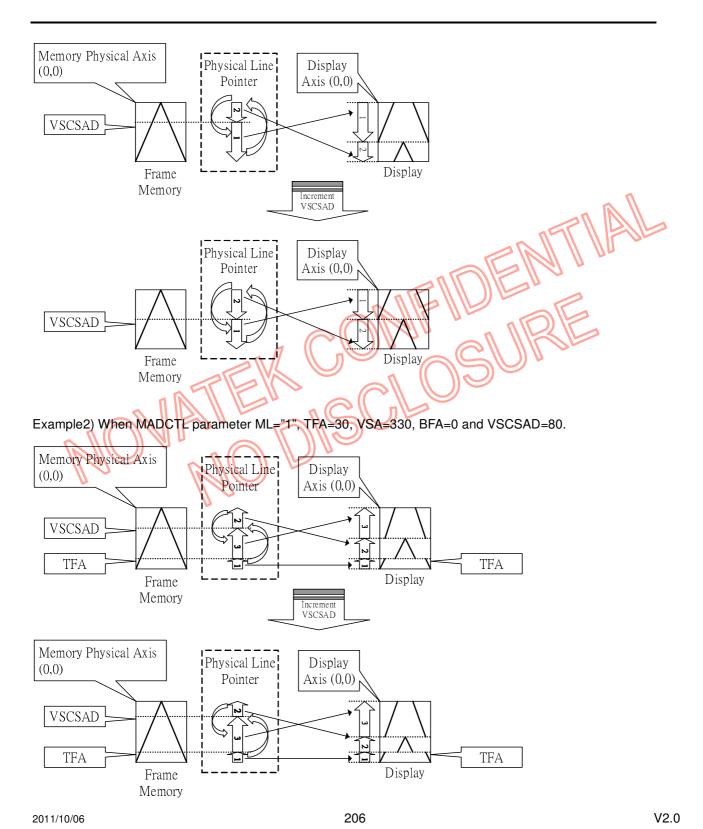

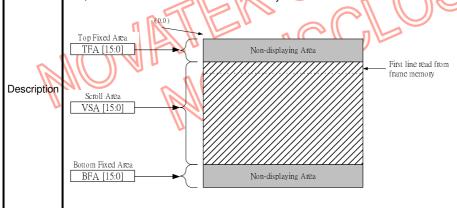

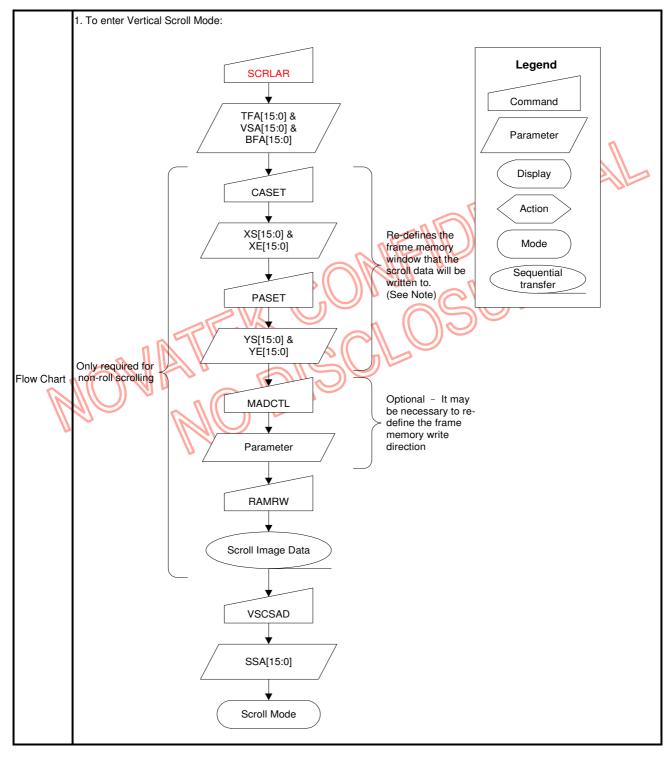

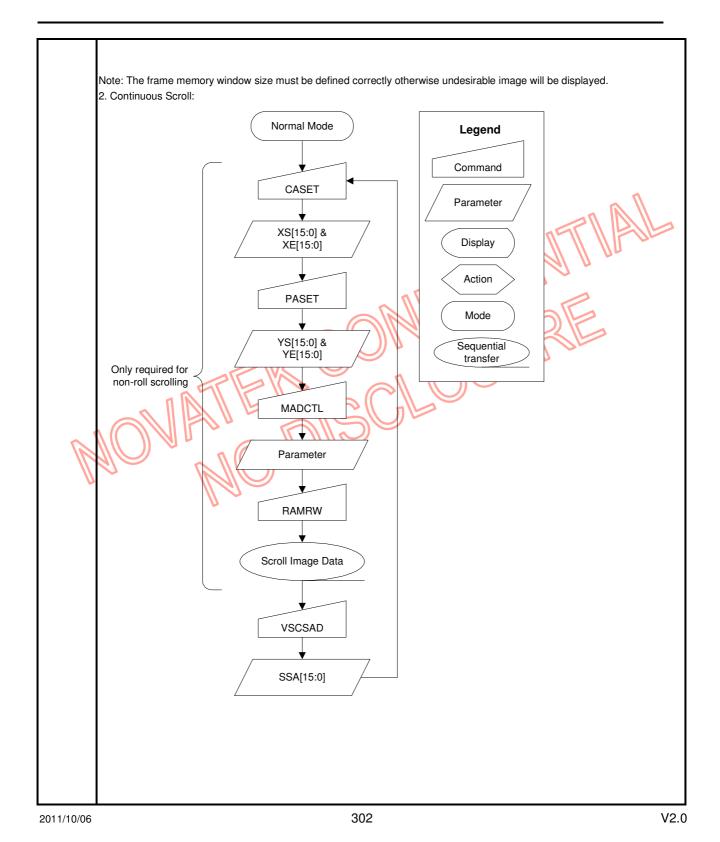

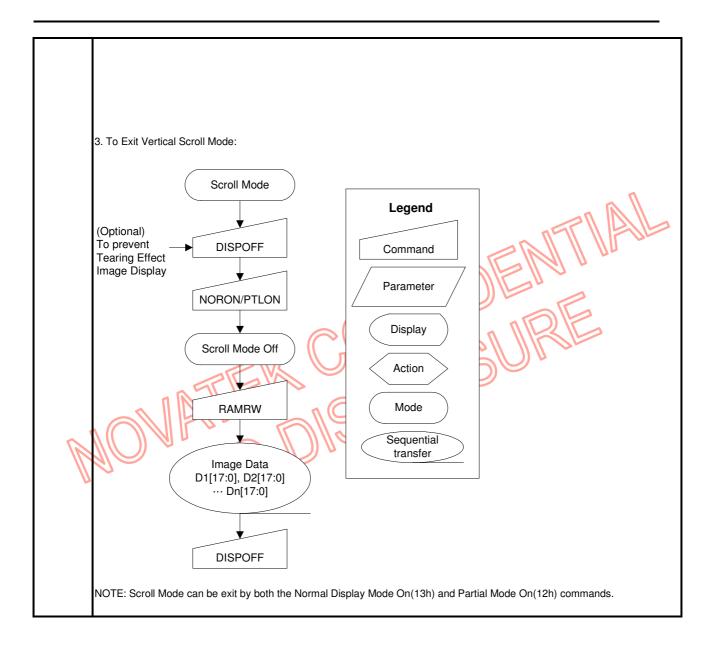

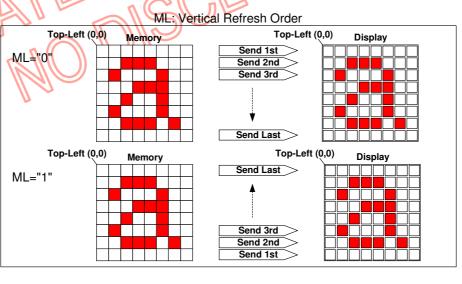

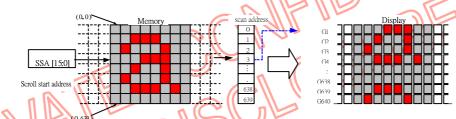

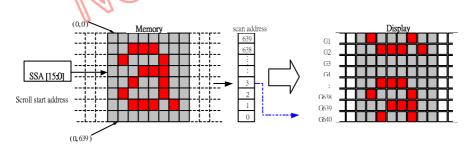

| 5.9.6 Vertical Scrolling                                               | 204  |

| 5.9.6.1 Scrolling                                                      | 204  |

| 5.9.6.2 Vertical Scroll Example                                        | 205  |

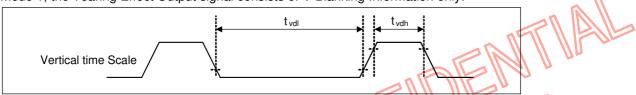

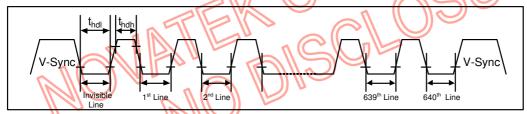

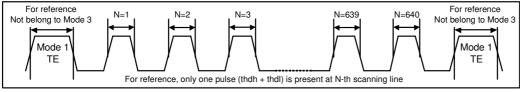

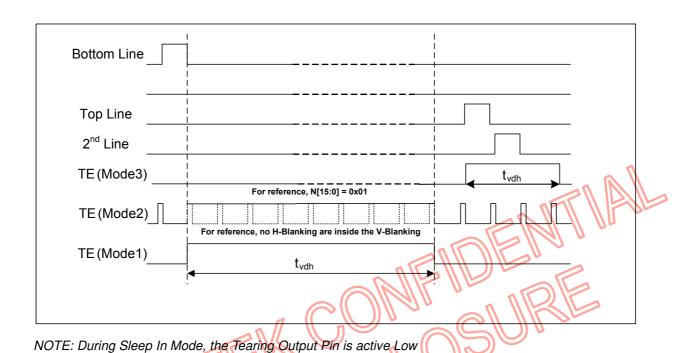

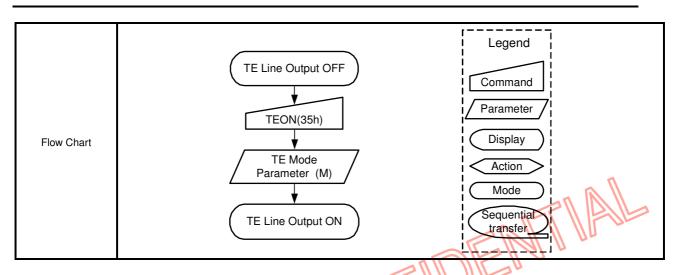

| 5.10 TEARING EFFECT INFORMATION                                        | 207  |

| 5.10.1 Tearing Effect Output Line                                      | 207  |

| 5.10.1.1 Tearing Effect Line Modes                                     | 207  |

| 5.10.1.2 Tearing Effect Line Timing                                    |      |

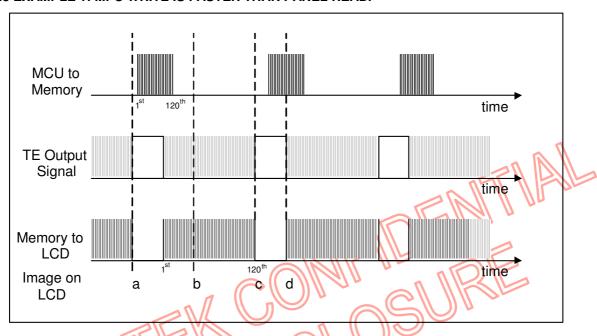

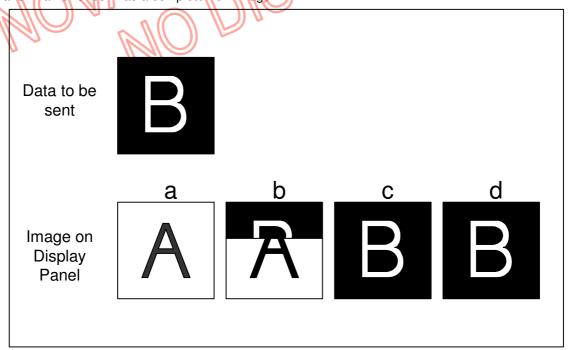

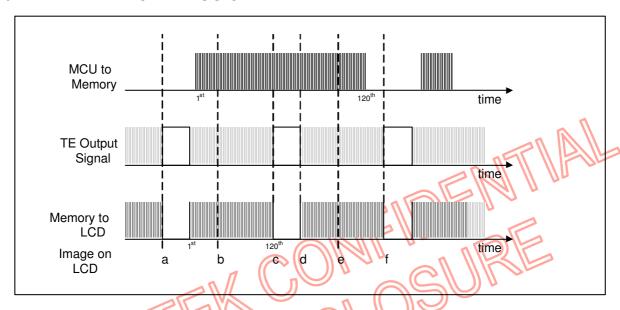

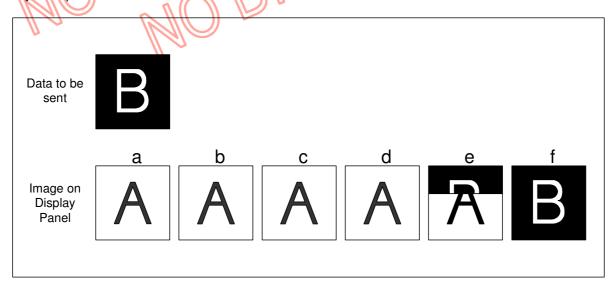

| 5.10.1.3 Example 1: MPU Write is Faster than Panel Read.               |      |

| 5.10.1.4 Example 2: MPU Write is Slower than Panel Read                |      |

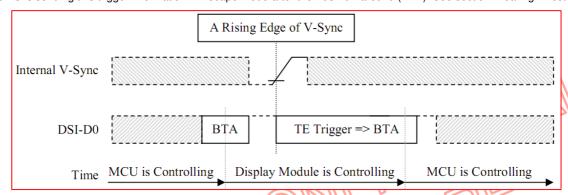

| 5.10.2 Tearing Effect Bus Trigger                                      | 212  |

| 5.10.2.1 Tearing Effect bus trigger enable                             |      |

| 5.10.2.2 Tearing Effect bus trigger disable                            | 214  |

| 5.10.2.3 Tearing Effect bus trigger sequences                          | 215  |

| 5.11 CHECKSUM                                                          | 224  |

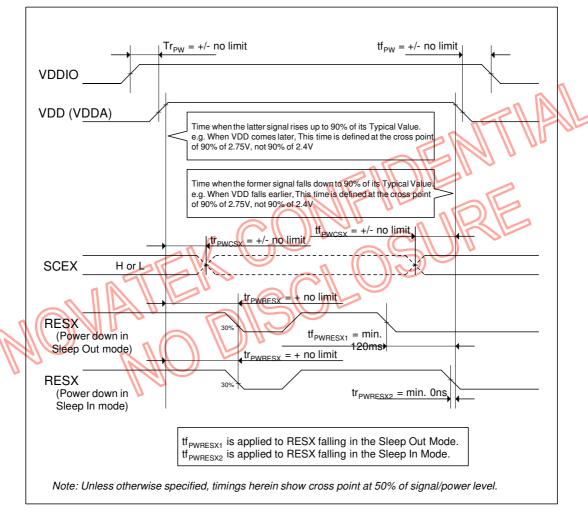

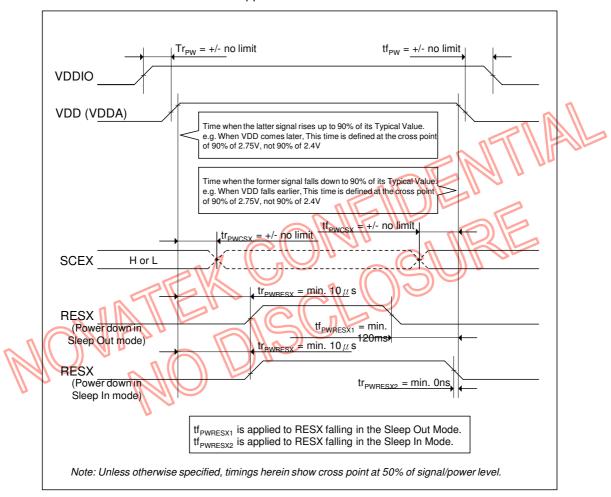

| 5.12 POWER ON/OFF SEQUENCE                                             | 226  |

| 5.12.1 Case 1 - RESX line is held High or Unstable by Host at Power On | 227  |

| 5.12.2 Case 2 – RESX line is held Low by host at Power On              | 228  |

| 5.12.3 Uncontrolled Power Off                                          | 228  |

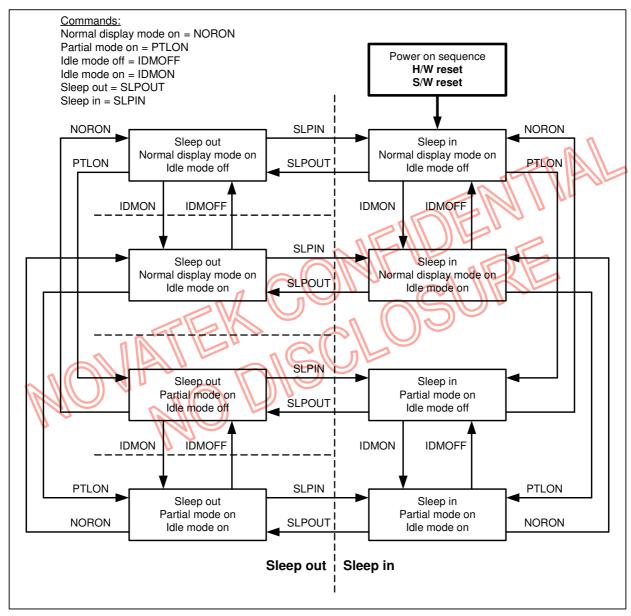

| 5.13 POWER LEVEL MODES                                                 | 229  |

| 5.13.1 Definition                                                      | 229  |

| 5.13.2 Power Level Mode Flow Chart                                     | 230  |

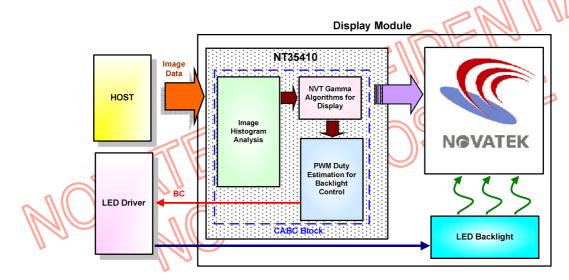

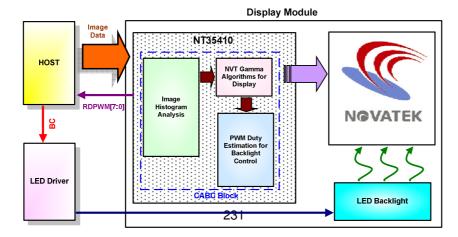

| 5.14 Content Adaptive Brightness Control (CABC) function               | 231  |

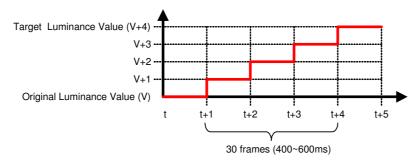

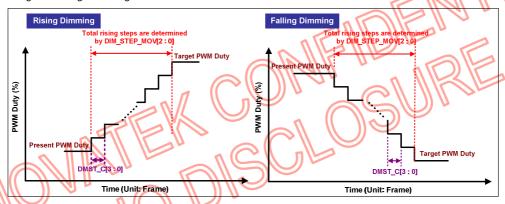

| 5.14.1 Dynamic Backlight Control Function                              | 231  |

| 5.14.1.1 Content Adaptive Brightness Control                           | 232  |

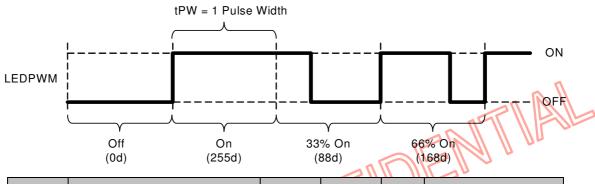

| 5.14.1.2 Display Backlight Dimming Control                             | 232  |

| 5.14.1.3 Brightness Control Line                                       | 233  |

| 5.15 INSTRUCTION DECODER & REGISTER                                    | 234  |

| 5.16 SYSTEM CLOCK GENERATOR                                            | 234  |

| 5.17 OSCILLATOR                                                        | 234  |

| 5.18 SOURCE DRIVER                                                     | 234  |

| 5.19 GATE DRIVER                                                       | 234  |

| 5.20 LCD POWER GENERATION CIRCUIT                                      | 235  |

| 2011/10/06 5                                                           | V2.0 |

| 5.20.1 LCD Power Generation Scheme                          | 235  |

|-------------------------------------------------------------|------|

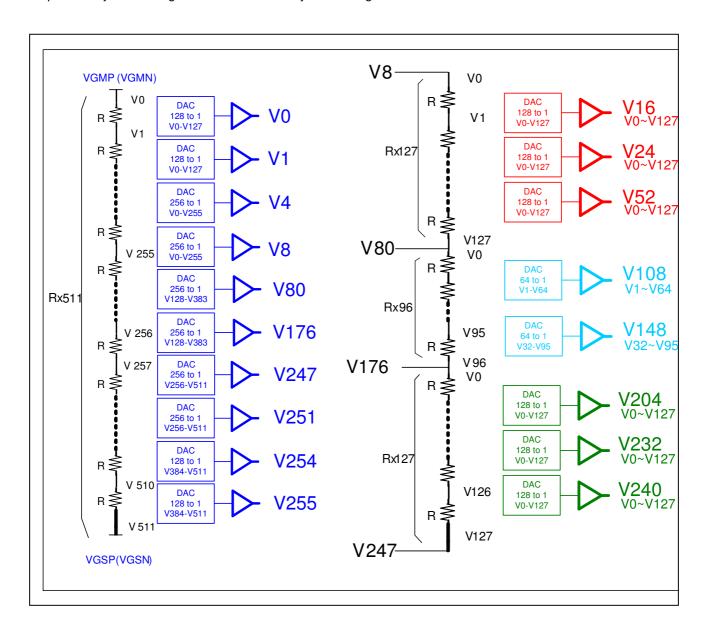

| 5.21 GAMMA CORRECTION FUNCTION                              | 236  |

| 5.22 Zigzag, Column, 1-Dot, 2-Dot Inversion (VCOM DC Drive) | 237  |

| 5.23 DISPLAY PANEL COLOR CHARACTERISTICS                    | 238  |

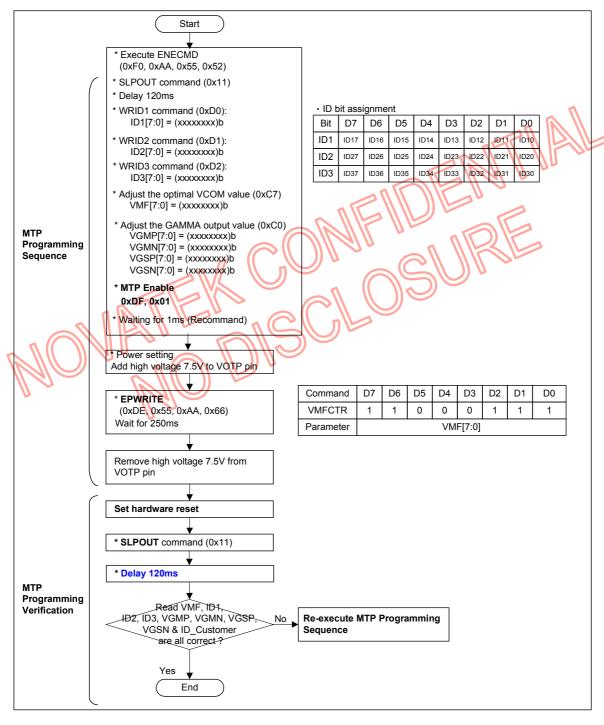

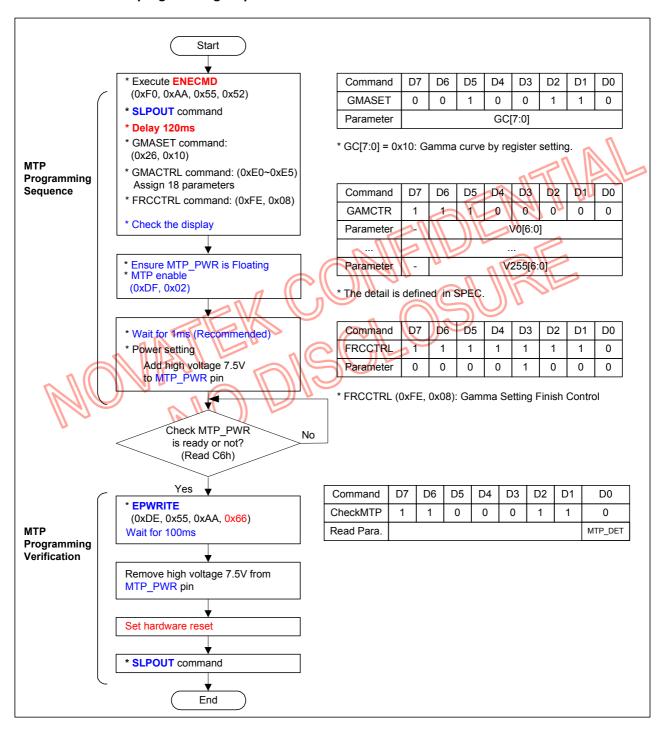

| 5.24 MTP PROGRAMMING SEQUENCE                               | 239  |

| 5.24.1 ID code and VCOM offset programming sequence         | 239  |

| 5.24.2 Gamma code programming sequence                      | 240  |

| 6 INSTRUCTION DESCRIPTION                                   |      |

| 6.1 INSTRUCTION CODE                                        | 241  |

| 6.1.1 NOP (00h)                                             | 245  |

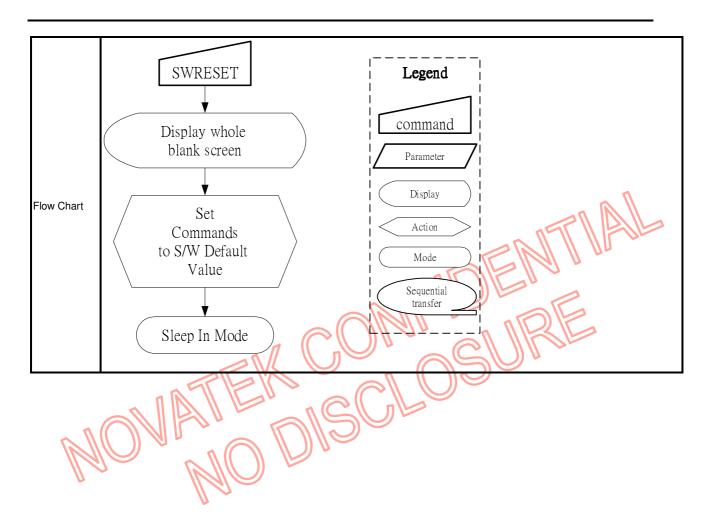

| 6.1.2 SWRESET: Software Reset (01h)                         |      |

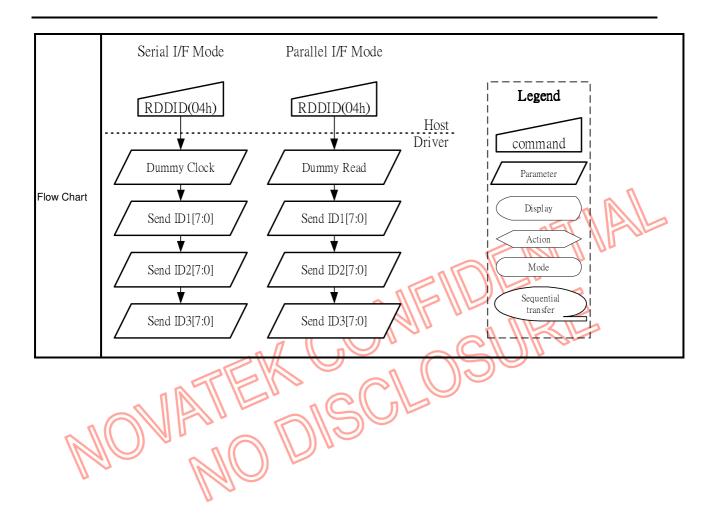

| 6.1.3 RDDID: Read Display ID (04h)                          | 248  |

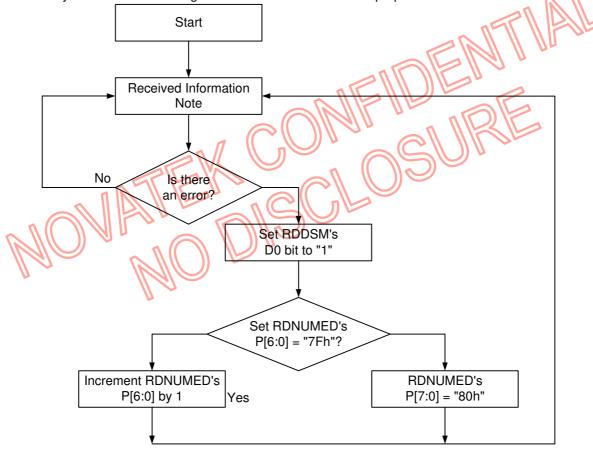

| 6.1.4 RDNUMED: Read Number of Errors on DSI (05h)           | 250  |

| 6.1.5 RDRED: Read Red Color (06h)                           | 251  |

| 6.1.6 RDGREEN: Read Green Color (07h)                       | 252  |

| 6.1.7 RDBLUE: Read Blue Color (08h)                         | 253  |

|                                                             |      |

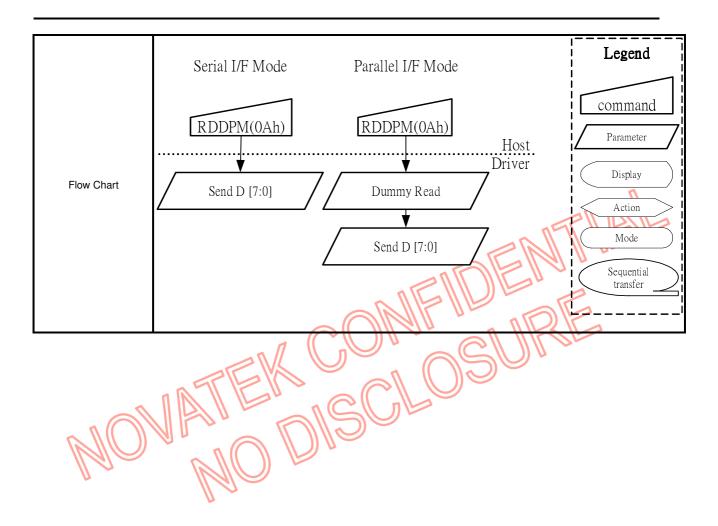

| 6.1.9 RDDPM: Read Display Power Mode (0Ah)                  | 256  |

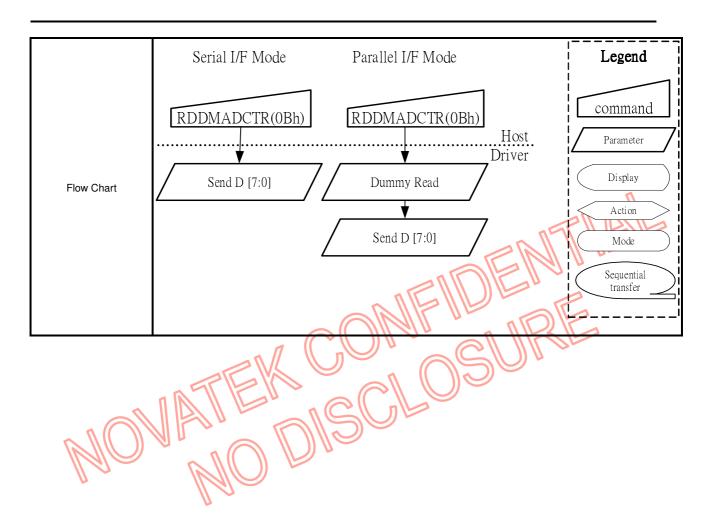

| 6.1.10 RDDMADCTL: Read Display MADCTL (0Bh)                 | 258  |

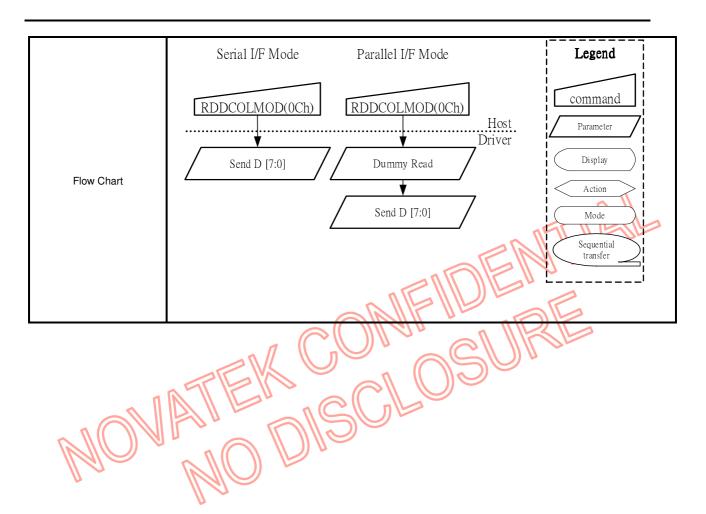

| 6.1.11 RDDCOLMOD: Read Display Pixel Format (0Ch)           | 260  |

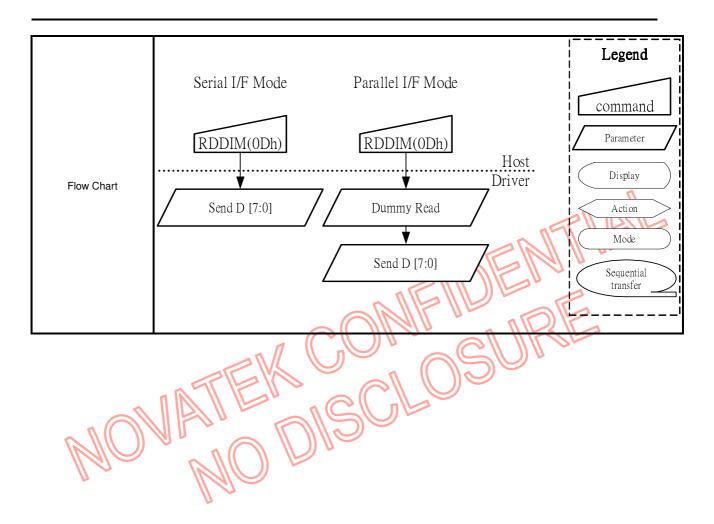

| 6.1.12 RDDIM: Read Display Image Mode (0Dh)                 | 262  |

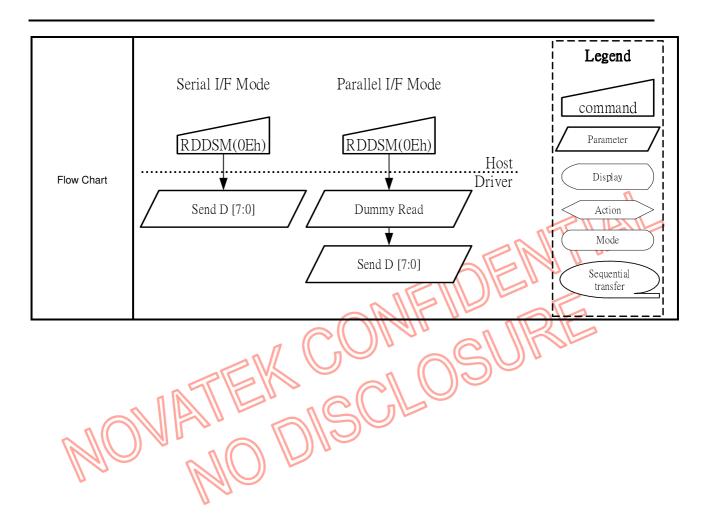

| 6.1.13 RDDSM: Read Display Signal Mode (0Eh)                | 264  |

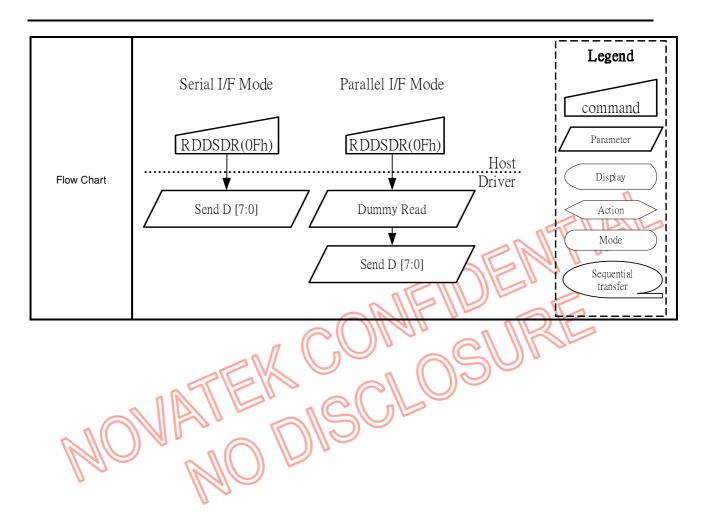

| 6.1.14 RDDSDR: Read Display Self-Diagnostic Result (0Fh)    | 266  |

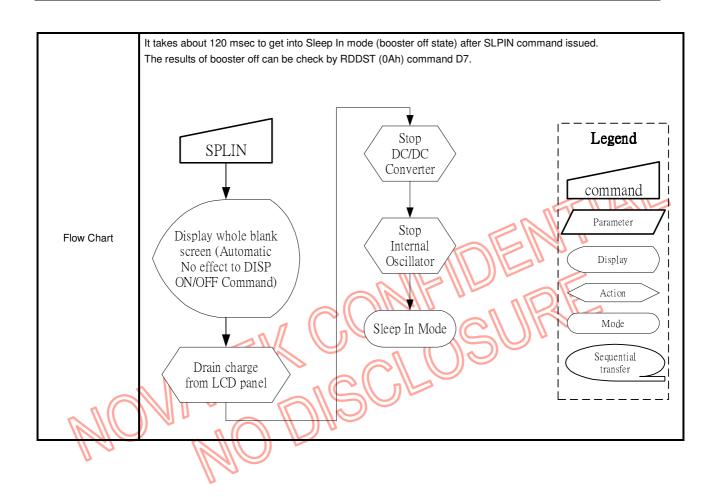

| 6.1.15 SLPIN: Sleep In (10h)                                | 268  |

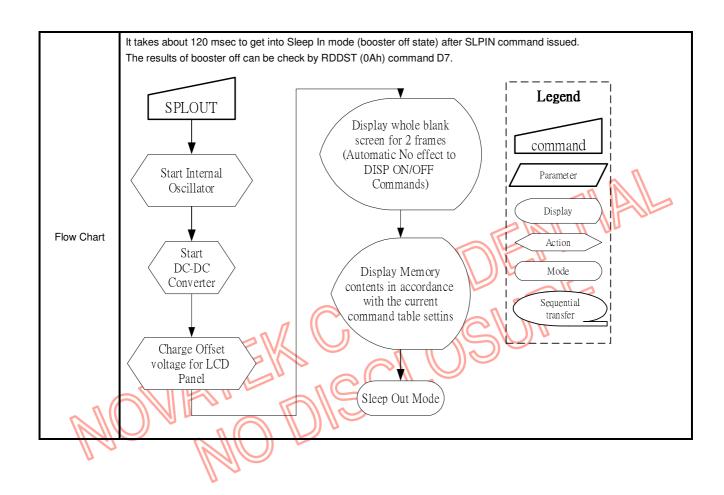

| 6.1.16 SLPOUT: Sleep Out (11h)                              | 270  |

| 6.1.17 PTLON: Partial Display Mode On (12h)                 | 272  |

| 6.1.18 NORON: Normal Display Mode On (13h)                  | 273  |

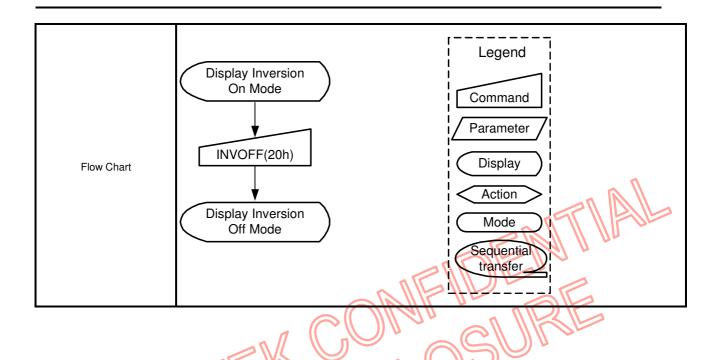

| 6.1.19 INVOFF: Display Inversion Off (20h)                  | 274  |

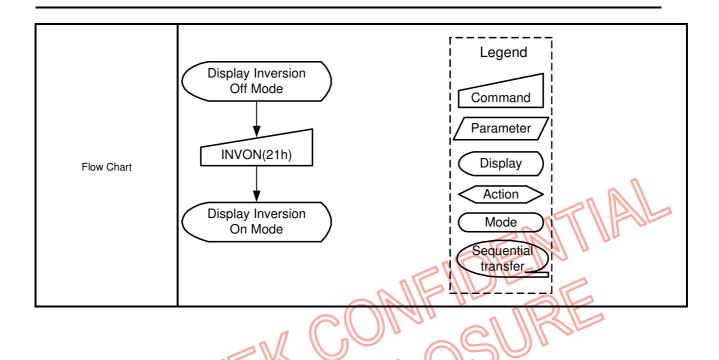

| 6.1.20 INVON: Display Inversion On (21h)                    | 276  |

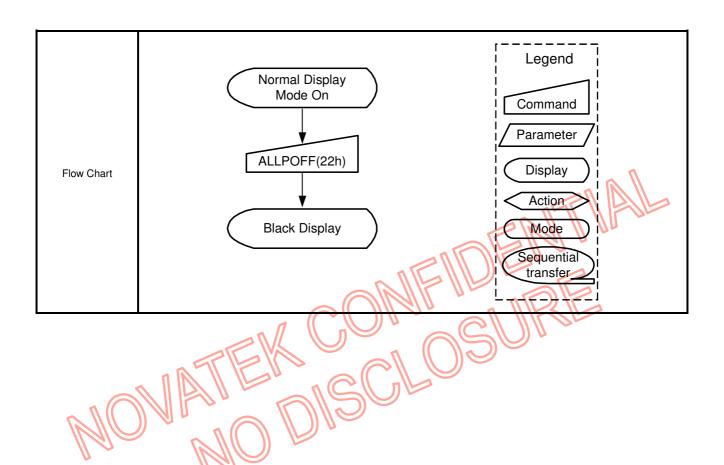

| 6.1.21 ALLPOFF: All Pixel Off (22h)                         | 278  |

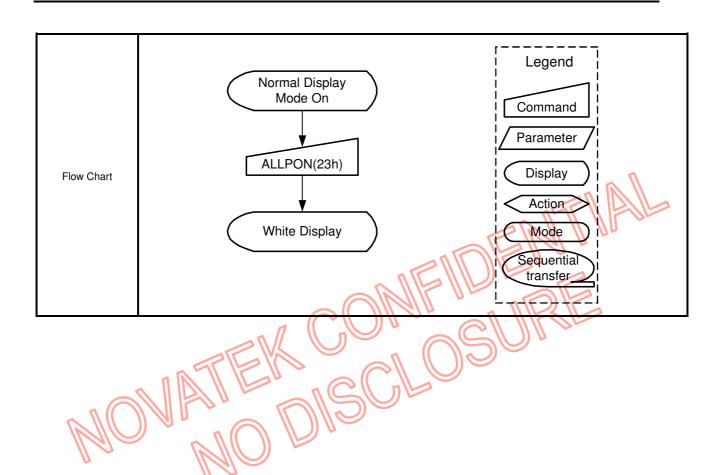

| 6.1.22 ALLPON: All Pixel On (23h)                           | 280  |

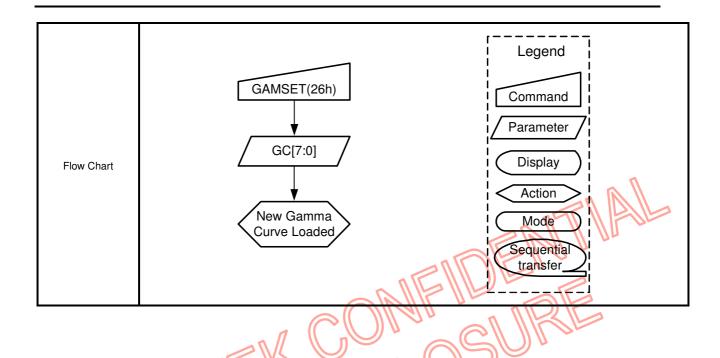

| 6.1.23 GAMSET: Gamma Set (26h)                              | 282  |

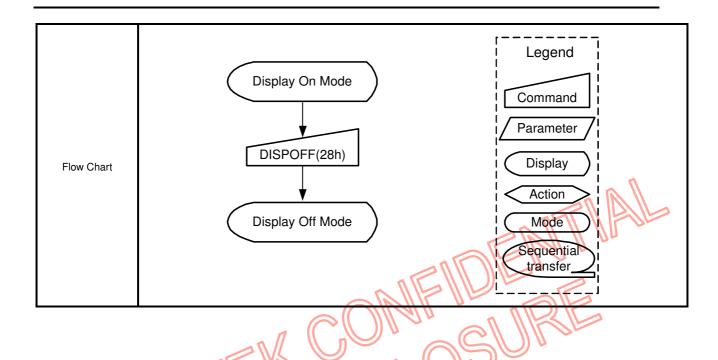

| 6.1.24 DISPOFF: Display Off (28h)                           | 284  |

| 2011/10/06 6                                                | V2.0 |

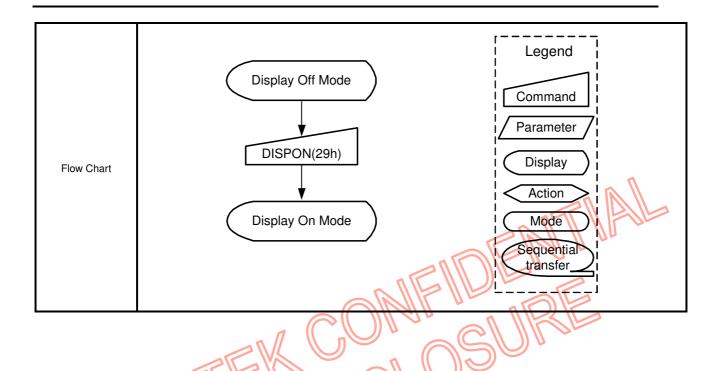

|   | 6.1.25 DISPON: Display On (29h)                                                 | 286  |

|---|---------------------------------------------------------------------------------|------|

|   | 6.1.26 CASET: Column Address Set (2Ah)                                          | 288  |

|   | 6.1.27 RASET: Row Address Set (2Bh)                                             | 290  |

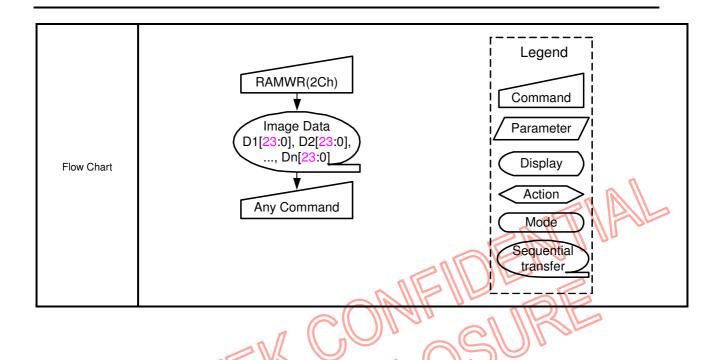

|   | 6.1.28 RAMWR: Memory Write (2Ch)                                                | 292  |

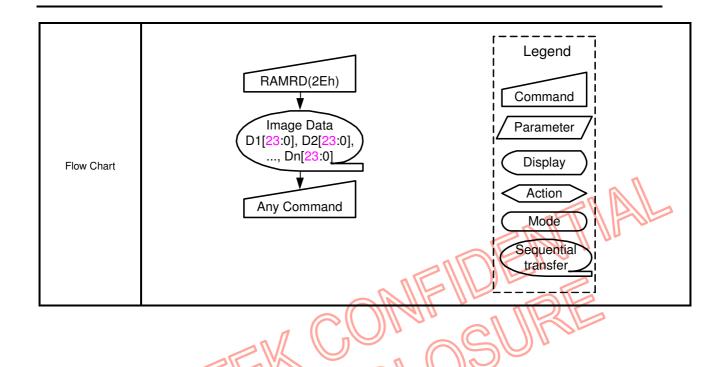

|   | 6.1.29 RAMRD: Memory Read (2Eh)                                                 | 294  |

|   | 6.1.30 PTLAR: Partial Area (30h)                                                | 296  |

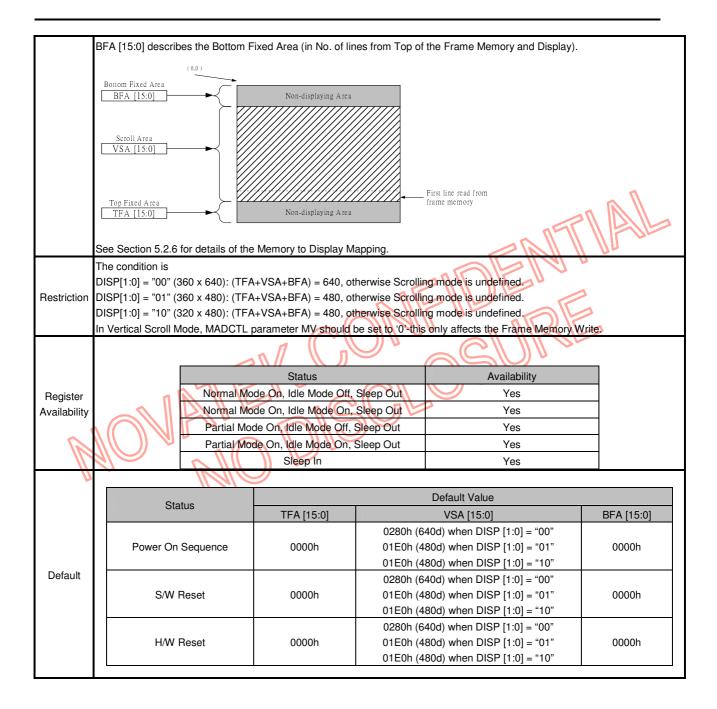

|   | 6.1.31 SCRLAR: Scroll Area (33h)                                                | 299  |

|   | 6.1.32 TEOFF: Tearing Effect Line OFF (34h)                                     | 304  |

|   | 6.1.33 TEON: Tearing Effect Line ON (35h)                                       |      |

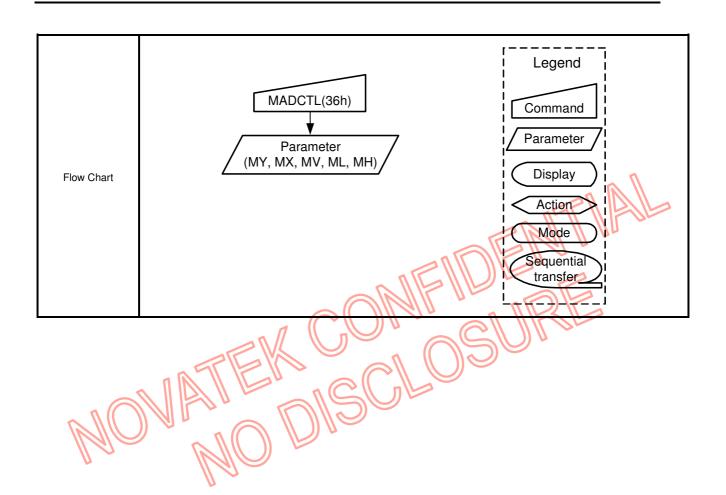

|   | 6.1.34 MADCTL: Memory Data Access Control (36h)                                 |      |

|   | 6.1.35 VSCSAD: Vertical Scroll Start Address SRAM (37h)                         | 310  |

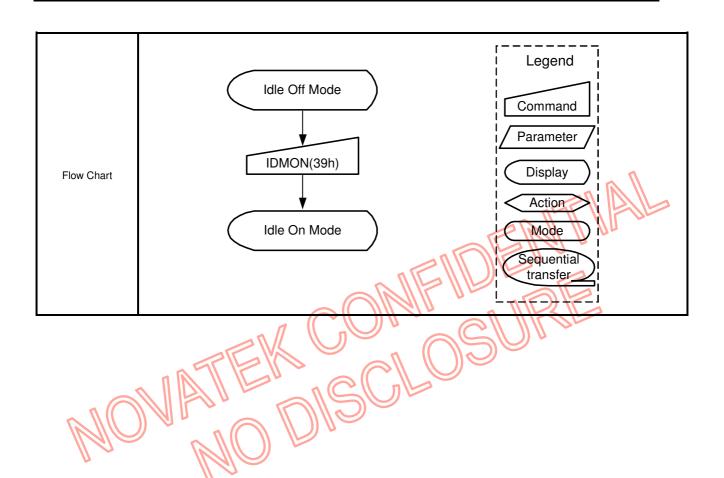

|   | 6.1.36 IDMOFF: Idle Mode Off (38h)                                              | 312  |

|   | 6.1.37 IDMON: Idle Mode On (39h)                                                | 313  |

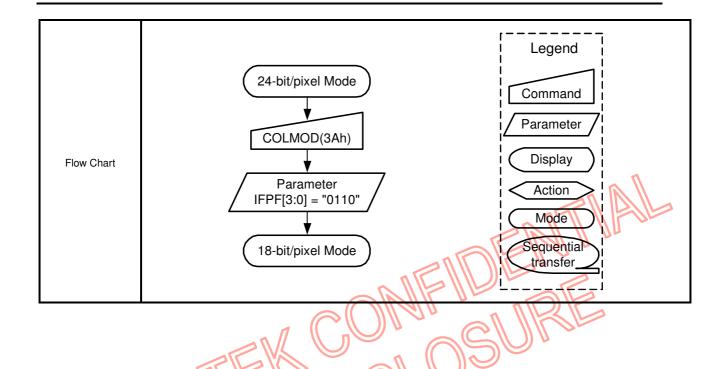

|   | 6.1.38 COLMOD: Interface Pixel Format (3Ah)                                     | 315  |

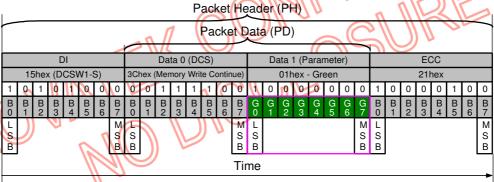

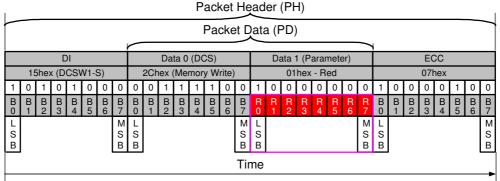

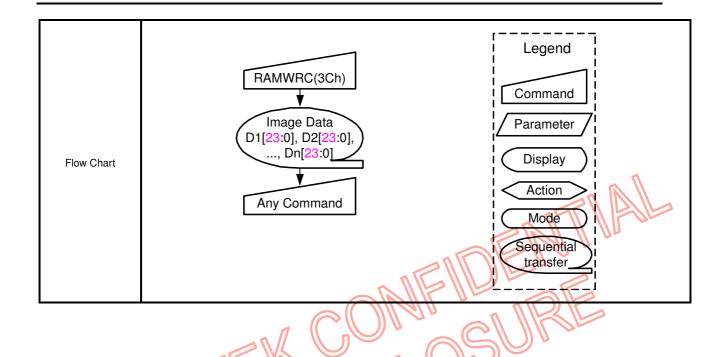

|   | 6.1.39 RAMWRC: Memory Write Continue (3Ch)                                      |      |

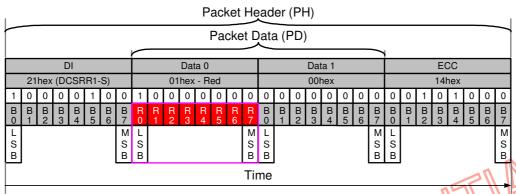

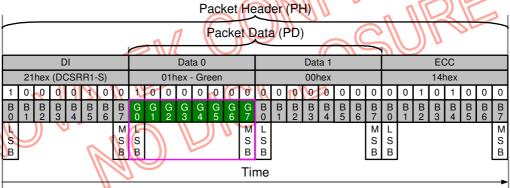

|   | 6.1.40 RAMRDC: Memory Read Continue (3Eh)                                       |      |

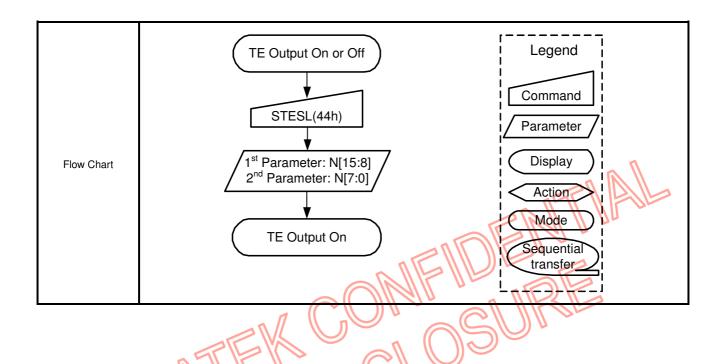

|   | 6.1.41 STESL: Set Tearing Effect Scan Line (44h)                                | 320  |

|   | 6.1.42 GSL: Get Scan Line (45h)                                                 | 322  |

|   | 6.1.43 WRDISBV: Write Display Brightness (51h)                                  | 323  |

|   | 6.1.44 RDDISBV: Read Display Brightness (52h)                                   | 324  |

|   | 6.1.45 WRCTRLD: Write CTRL Display (53h)                                        | 325  |

|   | 6.1.46 RDCTRLD: Read CTRL Display Value (54h)                                   | 326  |

|   | 6.1.47 WRCABC: Write Content Adaptive Brightness Control (55h)                  | 327  |

|   | 6.1.48 RDCABC: Read Content Adaptive Brightness Control (56h)                   | 329  |

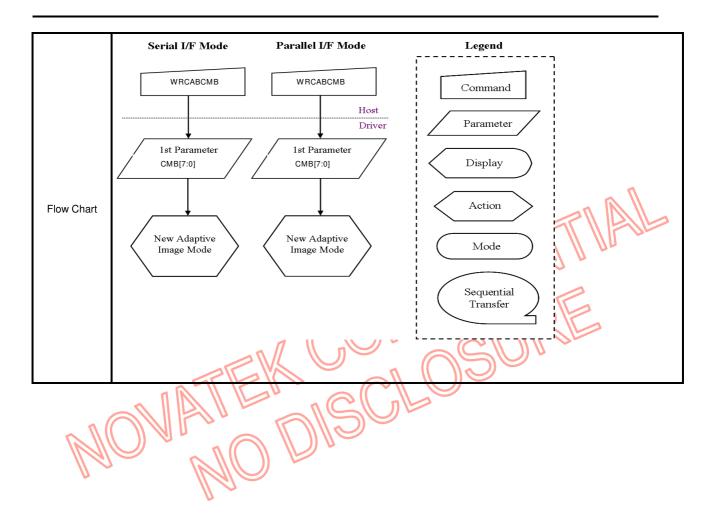

|   | 6.1.49 WRCABCMB: Write CABC minimum brightness (5Eh)                            | 330  |

|   | 6.1.50 RDCABCMB: Read CABC minimum brightness (5Fh)                             | 332  |

|   | 6.1.51 RDABCSDR: Read Automatic Brightness Control Self-Diagnostic Result (68h) | 333  |

|   | 6.1.52 RDBWLB: Read Black/White Low Bits (70h)                                  | 334  |

|   | 6.1.53 RDBkx: Read Bkx (71h)                                                    | 335  |

|   | 6.1.54 RDBky: Read Bky (72h)                                                    | 336  |

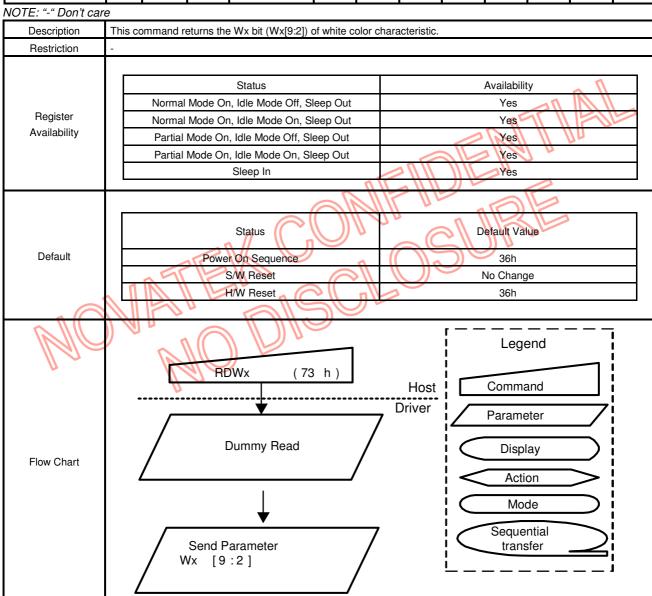

|   | 6.1.55 RDWx: Read Wx (73h)                                                      | 337  |

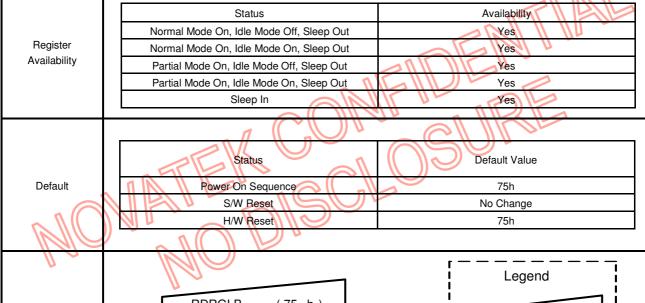

|   | 6.1.56 RDWy: Read Wy (74h)                                                      | 338  |

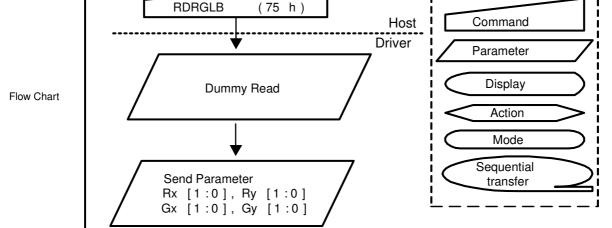

|   | 6.1.57 RDRGLB: Read Red/Green Low Bits (75h)                                    | 339  |

| 2 | 2011/10/06 7                                                                    | V2.0 |

|   | 6.1.58 RDRx: Read Rx (76h)                                                                  | 340  |

|---|---------------------------------------------------------------------------------------------|------|

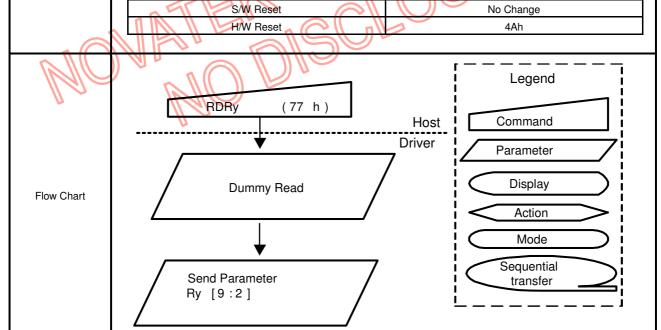

|   | 6.1.59 RDRy: Read Ry (77h)                                                                  | 341  |

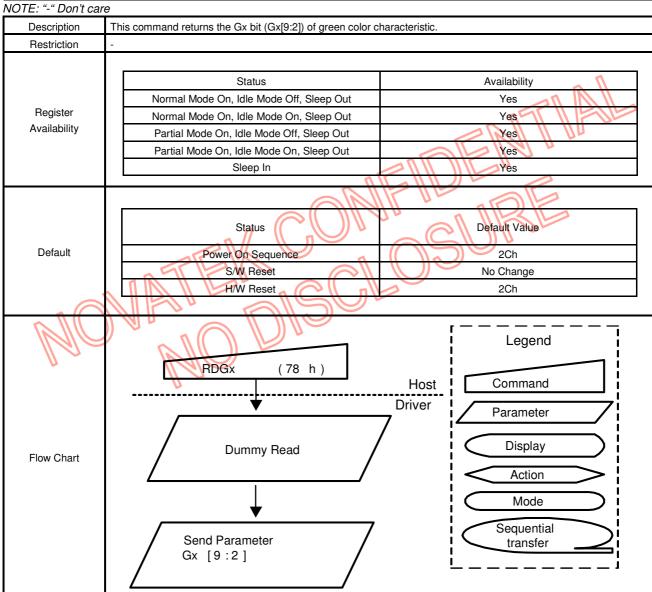

|   | 6.1.60 RDGx: Read Gx (78h)                                                                  | 342  |

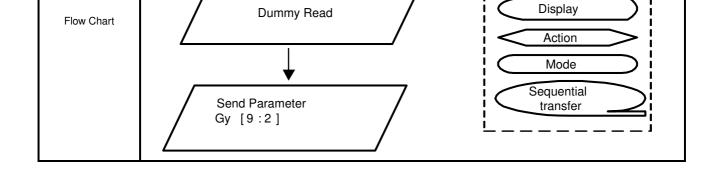

|   | 6.1.61 RDGy: Read Gy (79h)                                                                  | 343  |

|   | 6.1.62 RDBALB: Read Blue/AColor Low Bits (7Ah)                                              | 344  |

|   | 6.1.63 RDBx: Read Bx (7Bh)                                                                  | 345  |

|   | 6.1.64 RDBy: Read By (7Ch)                                                                  | 346  |

|   | 6.1.65 RDAx: Read Ax (7Dh)                                                                  | 347  |

|   | 6.1.66 RDAy: Read Ay (7Eh)                                                                  | 348  |

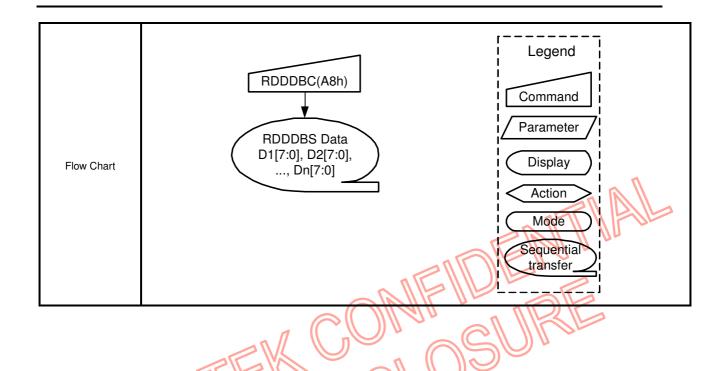

|   | 6.1.67 RDDDBS: Read DDB Start (A1h)                                                         | 349  |

|   | 6.1.68 RDDDBC: Read DDB Continue (A8h)                                                      |      |

|   | 6.1.69 RDFCS: Read First Checksum (AAh)                                                     | 353  |

|   | 6.1.70 RDCCS: Read Continue Checksum (AFh)                                                  | 354  |

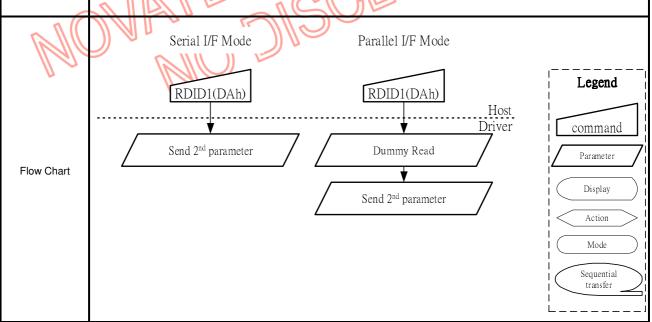

|   | 6.1.71 RDID1: Read ID1 Value (DAh)                                                          | 355  |

|   | 6.1.72 RDID2: Read ID2 Value (DBh)                                                          | 356  |

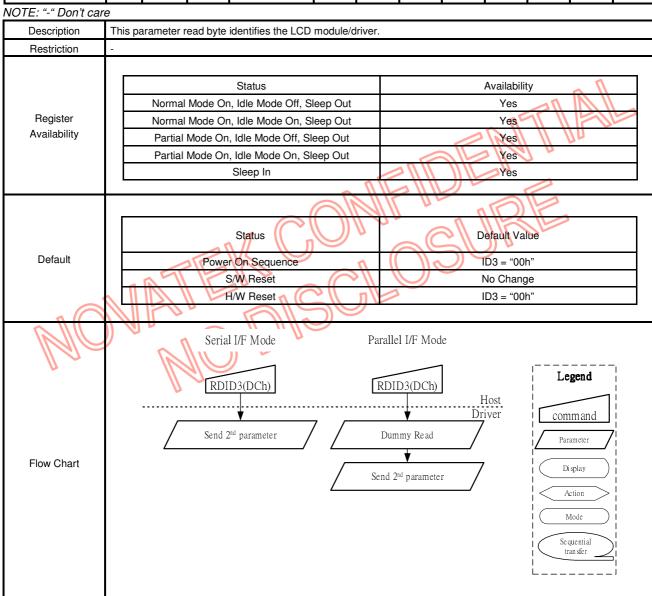

|   | 6.1.73 RDID3: Read ID3 Value (DCh)                                                          | 357  |

|   | 6.2 EXTENDED INSTRUCTION CODE                                                               | 358  |

|   | 6.2.1 IFMODE: Set Display Interface Mode (B0h)                                              | 358  |

|   | 6.2.2 FRMCTR1: Set Division ratio for internal clocks of Normal mode (B1h)                  | 360  |

|   | 6.2.3 FRMCTR2: Set Division ratio for internal clocks of Idle mode (B2h)                    | 362  |

|   | 6.2.4 FRMCTR3: Set Division ratio for internal clocks of Partial mode (Idle mode off) (B3h) | 364  |

|   | 6.2.5 INVCTR: Inversion Control (B4h)                                                       | 366  |

|   | 6.2.6 RGBBPCTR: RGB Interface Blanking Porch Setting (B5h)                                  | 367  |

|   | 6.2.7 DISSET: Display Function set (B6h)                                                    | 368  |

|   | 6.2.8CTRLEDPWM: Set the States for LED Control (B7h)                                        | 372  |

|   | 6.2.9 Display Function Selection(B8h)                                                       | 373  |

|   | 6.2.10 CTRLDMSP: Set the Total Dimming for CABC (B9h)                                       | 375  |

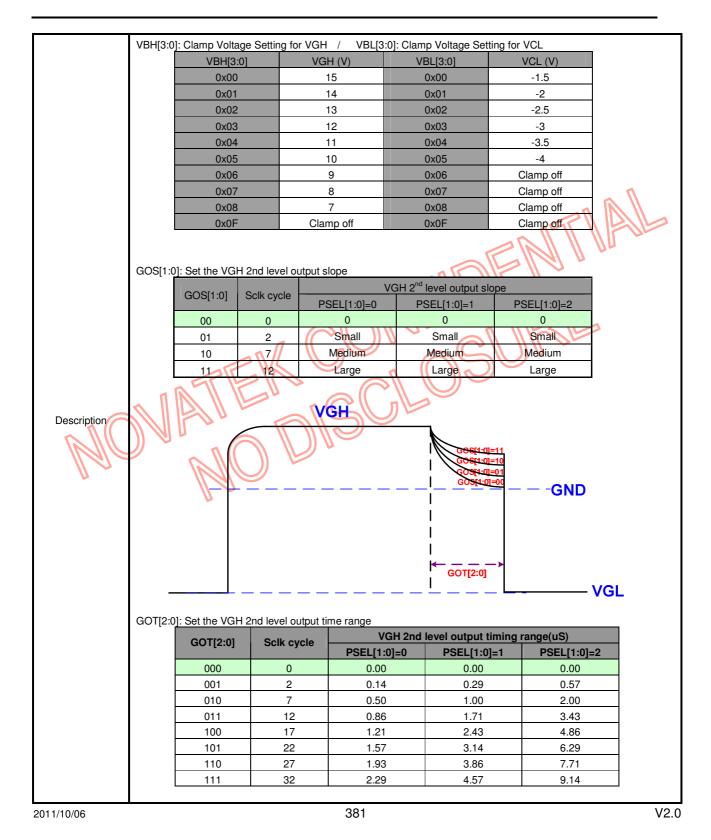

|   | 6.2.12 PWCTR2: Power Control 2 (C1h)                                                        | 380  |

|   | 6.2.13 PWCTR3: Power Control 3 (in Normal mode/ Full colors) (C2h)                          | 384  |

|   | 6.2.14 PWCTR4: Power Control 4 (in Idle mode/ 8-colors) (C3h)                               | 386  |

|   | 6.2.15 PWCTR5: Power Control 5 (in Partial mode/ Full-colors) (C4h)                         | 388  |

|   | 6.2.16 nVM: MTP reload or no-reload selection (C5h)                                         | 390  |

|   | 6.2.16 MTPDET: MTP Power Detect (C6h)                                                       | 391  |

| 2 | 2011/10/06 8                                                                                | V2.0 |

| 6.2.17 VMFCTR: VCOM Offset Control & Gamma Offset Control (C7h)               | 392  |

|-------------------------------------------------------------------------------|------|

| 6.2.18 RDVMF: Read VCOM offset value (C8h)                                    | 395  |

| 6.2.19 RDMTP: Read MTP value (C9h)                                            | 396  |

| 6.2.20 WRID1: Write ID1 for MTP program (D0h)                                 | 398  |

| 6.2.21 WRID2: Write ID2 for MTP program (D1h)                                 | 399  |

| 6.2.22 WRID3: Write ID3 for MTP program (D2h)                                 | 400  |

| 6.2.23 RDID4: Read ID4 for IC Vender Code (D3h)                               | ***  |

| 6.2.24 RDID5: Read ID5 Value (D4h)                                            |      |

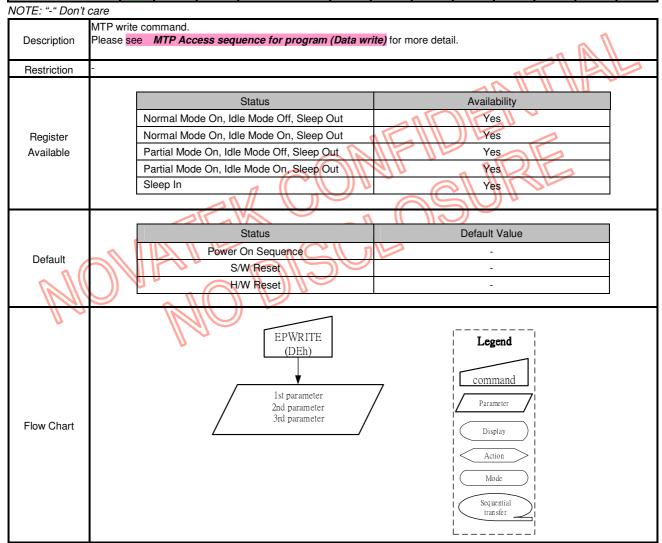

| 6.2.25 EPWRITE: MTP Write Command (DEh)                                       | 403  |

| 6.2.26 EN_MTP: Enable MTP Write Mode (DFh)                                    | 404  |

| 6.2.27 GAMCTRLPR: Set Gamma Correction Characteristics For Positive "R" (E0h) | 405  |

| 6.2.28 GAMCTRLNR: Set Gamma Correction Characteristics For Negative "R" (E1h) |      |

| 6.2.29 GAMCTRLPG: Set Gamma Correction Characteristics For Positive "G" (E2h) |      |

| 6.2.30 GAMCTRLNG: Set Gamma Correction Characteristics For Negative 'G" (E3h) | 408  |

| 6.2.31 GAMCTRLPB: Set Gamma Correction Characteristics For Positive "B" (E4h) | 409  |

| 6.2.32 GAMCTRLNB: Set Gamma Correction Characteristics For Negative "B" (E5h) |      |

| 6.2.33 DSTB: Enter Deep Standby Mode (E8h)                                    |      |

| 6.2.34 ENECMD: Enable Extend Command (F0h)                                    | 412  |

| 6.2.35 GMACMD: GAMMA Write & Read Command (FEh)                               | 413  |

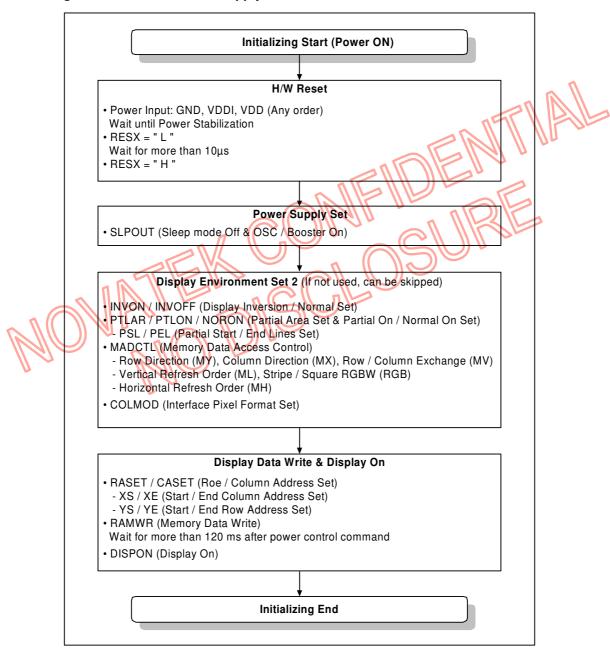

| 6.3 INSTRUCTION SETUP FLOW                                                    | 414  |

| 6.3.1 Initializing with the Built-in Power Supply Circuits                    | 414  |

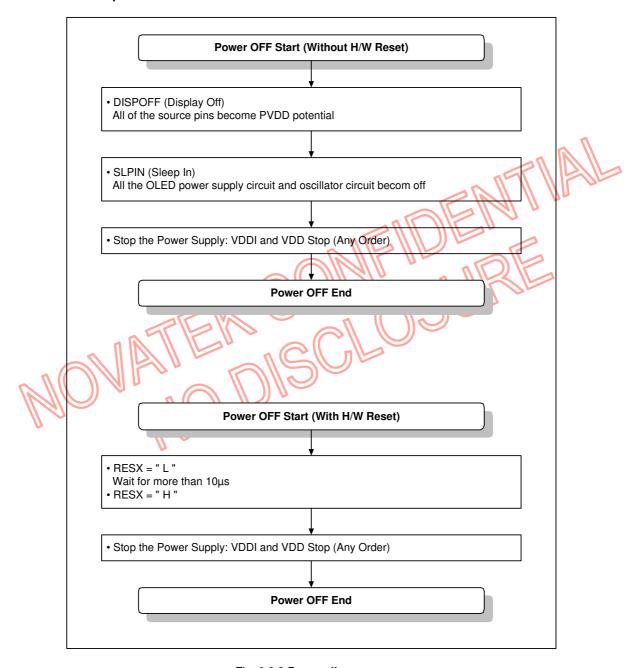

| 6.3.2 Power OFF Sequence                                                      | 415  |

| 7 SPECIFICATIONS                                                              | 416  |

| 7.1 ABSOLUTE MAXIMUM RATINGS                                                  | 416  |

| 7.2 ESD PROTECTION LEVEL                                                      | 416  |

| 7.3 LATCH-UP PROTECTION LEVEL                                                 | 416  |

| 7.4 LIGHT SENSITIVITY                                                         | 416  |

| 7.5 MAXIMUM SERIES RESISTANCE                                                 | 417  |

| 7.6 DC CHARACTERISTICS                                                        | 418  |

| 7.6.1 Basic Characteristics                                                   | 418  |

| 7.6.2 Current Consumption                                                     | 420  |

| 7.6.3 MIPI Characteristics                                                    | 421  |

| 7.6.3.1 DC Characteristics for DSI LP Mode                                    | 421  |

| 2011/10/06 9                                                                  | V2.0 |

| 7.7. AC CHARACTERISTICS                                              | 7.6.4 MDDI Characteristics                                           | 400 |

|----------------------------------------------------------------------|----------------------------------------------------------------------|-----|

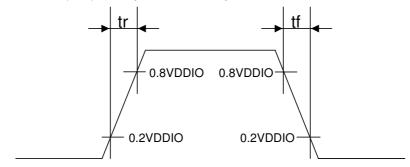

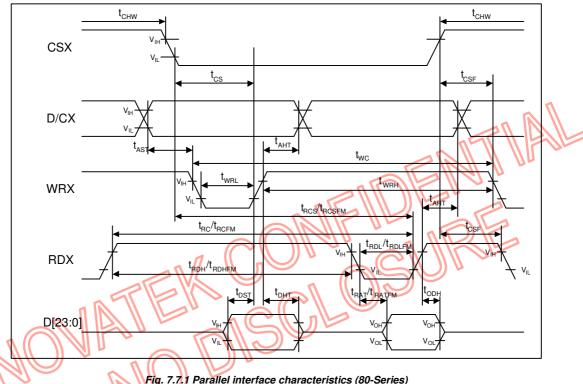

| 7.7.1 Parallel Interface Characteristics (80-Series MCU)             |                                                                      |     |

| 7.7.2 Serial Interface Characteristics (3-Pin Serial)                |                                                                      |     |

| 7.7.3 Serial Interface Characteristics (4-Pin Serial)                | · · · · · · · · · · · · · · · · · · ·                                |     |

| 7.7.4 RGB Interface Characteristics                                  | ·                                                                    |     |

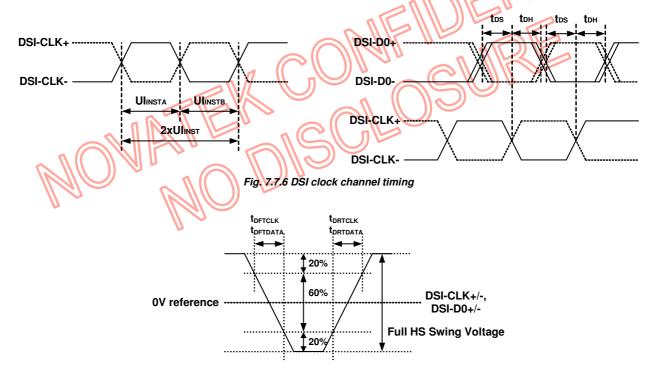

| 7.7.5 MIPI DSI Timing Characteristics                                |                                                                      |     |

| 7.7.5.1 High Speed Mode                                              |                                                                      |     |

| 7.7.5.2 Low Power Mode                                               | - II                                                                 |     |

| 7.7.5.3 DSI Bursts                                                   |                                                                      |     |

| 7.7.6 MDDI Timing Characteristics                                    |                                                                      |     |

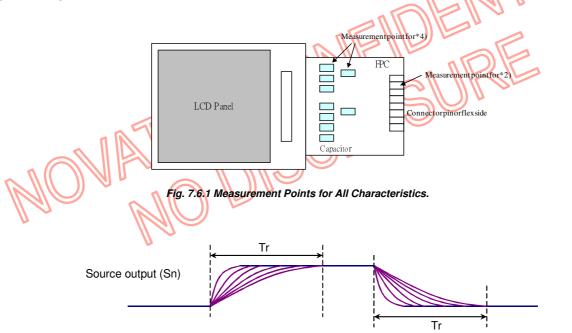

| 7.7.8 Measurement Conditions                                         | 7.7.5.3 DSI Bursts                                                   | 433 |

| 7.7.8 Measurement Conditions                                         | 7.7.6 MDDI Timing Characteristics                                    | 435 |

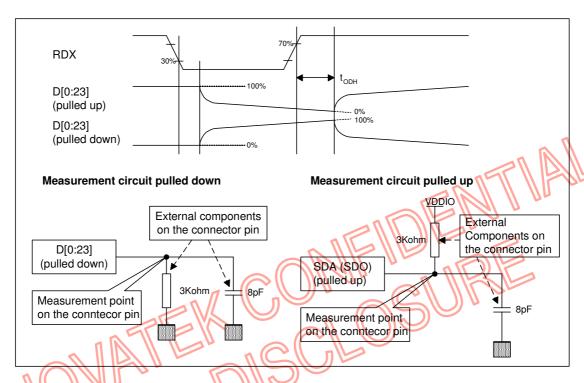

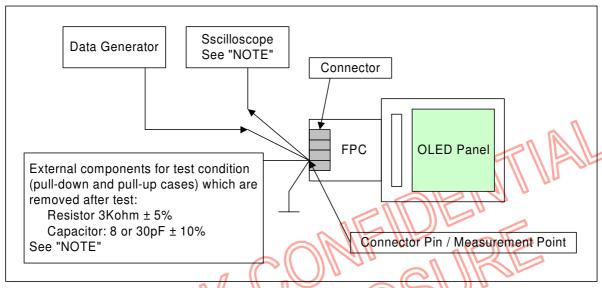

| 7.7.8.1 tRAT, tRATFM, tODH Measurement Condition                     |                                                                      |     |

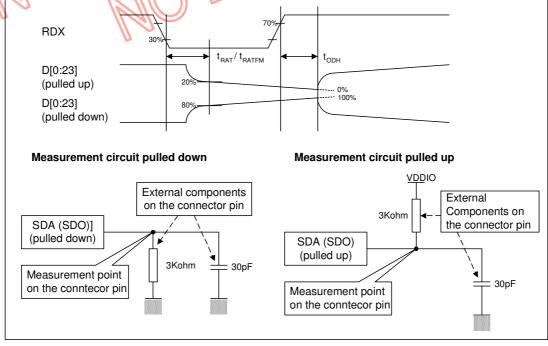

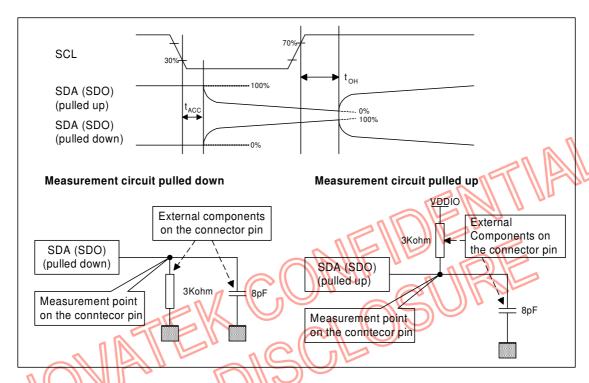

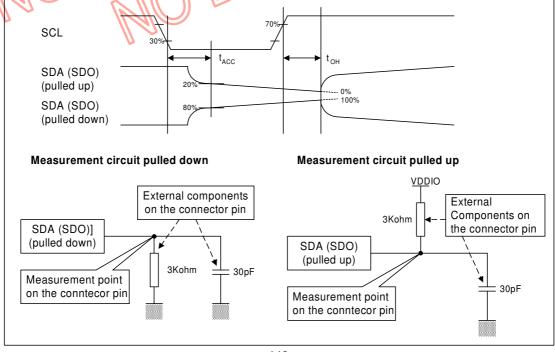

| 7.7.8.2 tACC, tOH Measurement Condition                              |                                                                      |     |

| 8.1 MICROPROCESSOR INTERFACE                                         |                                                                      |     |

| 8.1 MICROPROCESSOR INTERFACE                                         | 7.7.8.2 tACC, tOH Measurement Condition                              | 439 |

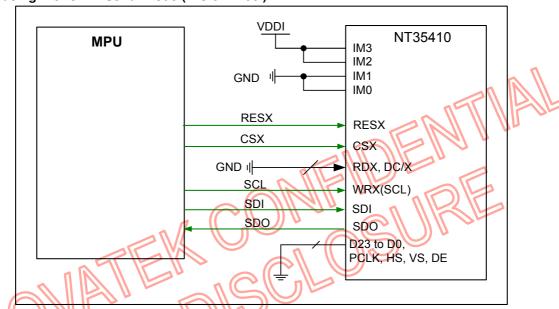

| 8.1.1 Interfacing with 3-Pin Serial Mode (IM3-0='1100')              | REFERENCE APPLICATIONS                                               | 441 |

| 8.1.2 Interfacing with 4-Pin Serial Mode (IM3-0='1101')              |                                                                      |     |

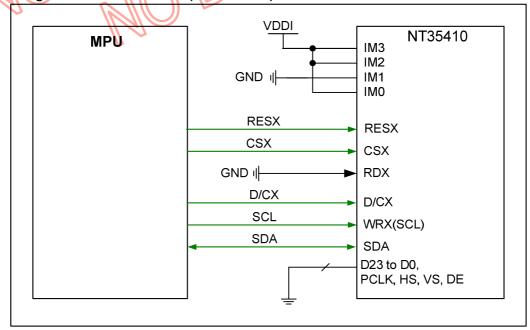

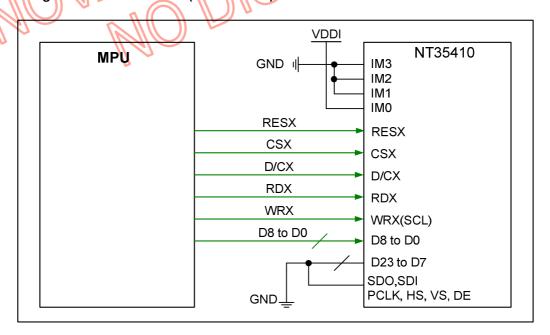

| 8.1.3 Interfacing with 8080- 8 bit Mode (IM3-0='0000')               |                                                                      |     |

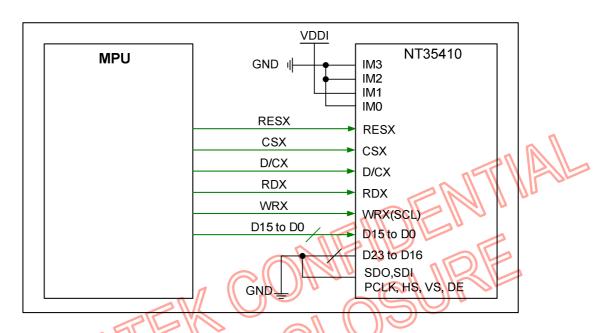

| 8.1.4 Interfacing with 8080- 9 bit Mode (IM3-0='0001')               | 8.1.2 Interfacing with 4-Pin Serial Mode (IM3-0='1101')              | 441 |

| 8.1.5 Interfacing with 8080- 16 bit Mode (IM3-0='0010')              | 8.1.3 Interfacing with 8080- 8 bit Mode (IM3-0='0000')               | 442 |

| 8.1.6 Interfacing with 8080- 18 bit Mode (IM3-0='0011')              | 8.1.4 Interfacing with 8080- 9 bit Mode (IM3-0='0001')               | 442 |

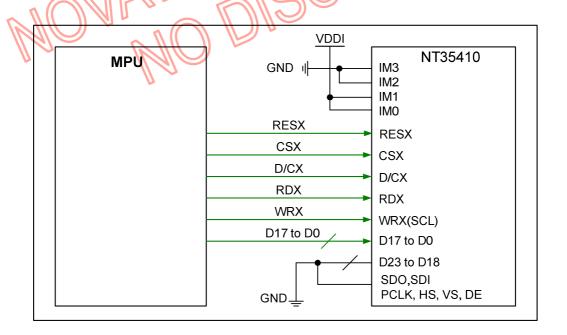

| 8.1.7 Interfacing with 8080- 24 bit Mode (IM3-0='0100')              | 8.1.5 Interfacing with 8080- 16 bit Mode (IM3-0='0010')              | 443 |

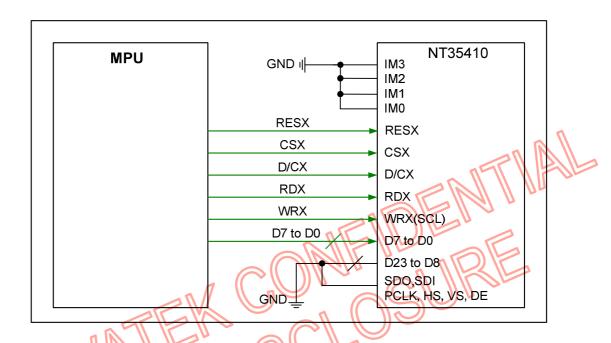

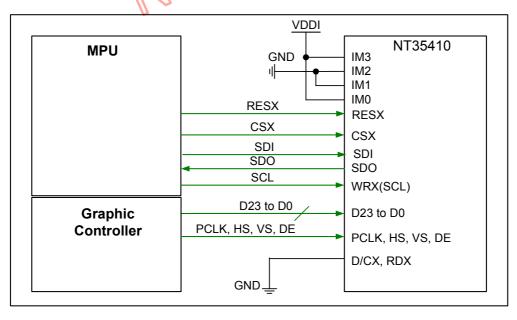

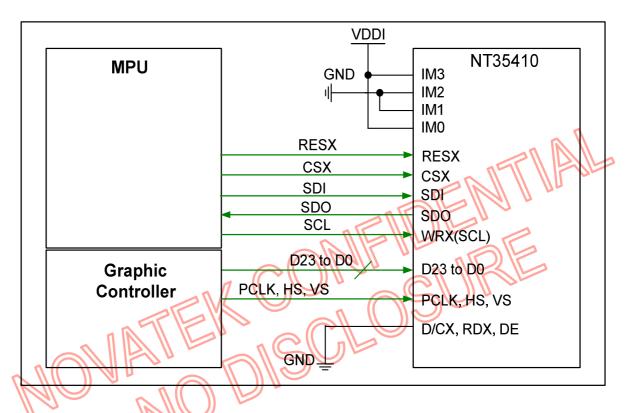

| 8.1.8 Interfacing with RGB Mode 1 with 3-SPI (IM3-0='1001')          | 8.1.6 Interfacing with 8080- 18 bit Mode (IM3-0='0011')              | 443 |

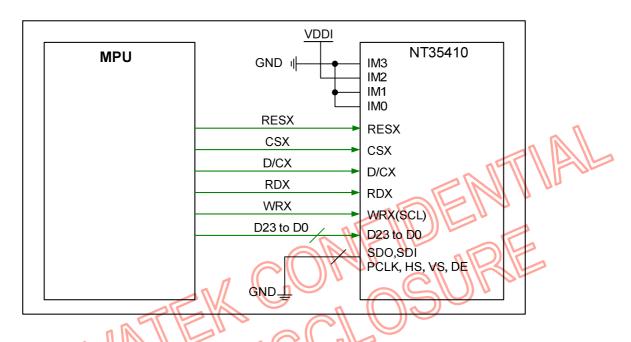

| 8.1.9 Interfacing with RGB Mode 2 with 3-SPI (IM3-0='1001')          | 8.1.7 Interfacing with 8080- 24 bit Mode (IM3-0='0100')              | 444 |

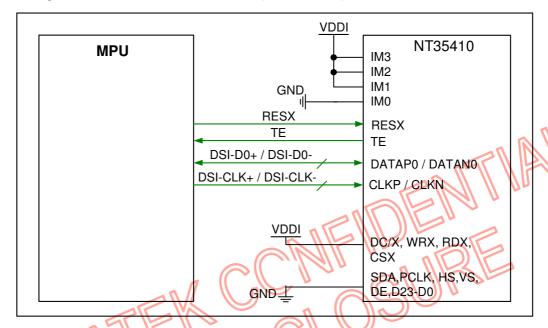

| 8.1.10 Interfacing with MIPI DSI Mode with TE Line (IM3-0='1110')    | 8.1.8 Interfacing with RGB Mode 1 with 3-SPI (IM3-0='1001')          | 444 |

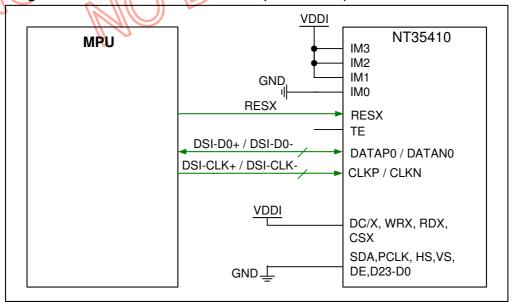

| 8.1.11 Interfacing with MIPI DSI Mode without TE Line (IM3-0='1110') | 8.1.9 Interfacing with RGB Mode 2 with 3-SPI (IM3-0='1001')          | 445 |

| 8.1.12 Interfacing with MDDI Mode with TE Line (IM3-0='1111')        | 8.1.10 Interfacing with MIPI DSI Mode with TE Line (IM3-0='1110')    | 446 |

| 8.2 CONNECTIONS WITH LCD PANEL                                       | 8.1.11 Interfacing with MIPI DSI Mode without TE Line (IM3-0='1110') | 446 |

|                                                                      | 8.1.12 Interfacing with MDDI Mode with TE Line (IM3-0='1111')        | 447 |

| 8.3 EXTERNAL COMPONENTS CONNECTION                                   | 8.2 CONNECTIONS WITH LCD PANEL                                       | 448 |

|                                                                      | 8.3 EXTERNAL COMPONENTS CONNECTION                                   | 449 |

2011/10/06 10 V2.0

## **REVISION HISTORY**

| Version | Contents                                                                                                                      | Prepared<br>by | Checked<br>by | Approved by   | Date       |

|---------|-------------------------------------------------------------------------------------------------------------------------------|----------------|---------------|---------------|------------|

| 1.0     | Original                                                                                                                      | Steven<br>Chen | Eric Tsai     | Dennis<br>Kuo | 2011/09/02 |

| 2.0     | -Add MDDI application reference circuit (page447) -Modify the power on sequence, power up/down can be any order (page226-228) | Steven<br>Chen | Eric Tsai     | Dennis<br>Kuo | 2011/10/6  |

2011/10/06 11 V2.0

SE SE

#### 1 DESCRIPTION

NT35410 is a single chip low power CMOS LCD controller/driver for color TFT-LCD displays of 640 gates and 360xRGB columns. It has a 5.52M-bit (360 x 24bit x 640) display RAM and a full set of control functions. NT35410 offers 16 kinds microprocessor interfaces: 8080-system (8-bit, 9-bit, 16-bit, 18-bit, 24-bit), MIPI interface, MDDI interface, serial (3-pin or 4-pin) and RGB (16-bit, 18-bit, 24-bit) mode1, 2 interface.

#### **2 FEATURES**

- ◆ Single chip AM-TFT-LCD Controller/ driver with Display RAM.

- Display resolution: (programmable and s/w setting)

- 320\*RGB (H) \*480(V)

- 360\*RGB (H) \*480(V)

- 360\*RGB (H) \*640(V)

- Operation Frequency:

- MIPI interface: 500Mbps/Channel

- MDDI interface: 400Mbps/Channel

- 80-series MPU interface (WRX): 27MHz

- RGB interface (PCLK): 30Mhz

- SPI (SCL): 27MHz

- ◆ Display data RAM (frame memory): 360 x 640 x 24-bit = 5,529,600bit

- Output:

- 1080ch source outputs (360xRGB)

- 640 gate outputs

- Common electrode output

- Display mode (Color mode)

- Full color mode (Idle mode off): 16.7M-colors, 262k-colors, 65k-colors

- Reduce color mode (Idle mode on): 8-colors (3-bit binary mode)

- Color modes on the display host interface:

- 16-bit/Pixel: RGB= (565) using the 2488k-bit frame memory

- 18-bit/Pixel: RGB= (666) using the 2488k-bit frame memory

- 24-bit/Pixel: RGB= (888) using the 2488k-bit frame memory

- Interface:

- 3-pin / 4-pin serial interface

- 8-bit, 9-bit, 16-bit, 18-bit, 24-bit interface with 8080-series MCU

- 16-bit, 18-bit, 24-bit RGB interface Mode 1 (DE + SYNC mode) and Mode 2 (SYNC only mode)

- MIPI interface (1 clock and 1 data lane pairs, DSI V1.01 r11 and D-PHY V1.00.00)

- Mobile Display Digital Interface (MDDI 1.2-Type1)

- Display features

- Area scrolling

- Partial display mode

- Software programmable color depth mode

- Content Adaptive Backlight Control (CABC) Function

- Histogram analysis & data process

- Moving picture auto-detect mode.(UI or still picture mode decided by host)

- Dimming control

- 2 level PWM control line for the Display Backlight

- On chip

- DC/DC converter

- DC VCOM voltage generator

2011/10/06 12 V2.0

- Separate RGB gamma control

- Provide 4 times MTP to store VCOM and ID setting

- Oscillator for display clock generation

- NV Memory (4-times on each function)

- 8-bits for User ID1

- 8-bits for User ID2

- 8-bits for User ID3

- 8-bits for VCOM adjustment

- Driving Algorithm

- 2 level gate drive with common electrode modulation drive

- Support 1dot inversion, 2dot inversion, column inversion, zigzag inversion driving

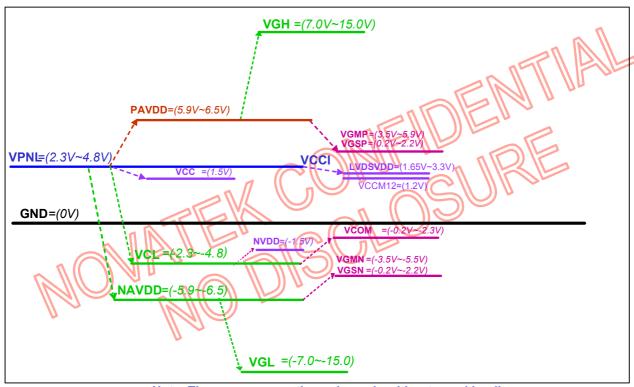

- Supply voltage range

- Analog supply voltage range for VPNL to AVSS: 2.3V to 4.8V

- I/O supply voltage range for VDDI to VSS: 1.65V to 4.8V

- MIPI supply voltage range for VCCI to VSS: 2.3 to 4.8V

- Output voltage levels

- Positive Power supply for driver circuit range(PAVDD): PAVDD-VSS = 5.9V to 6.5V

- Negative Power supply for driver circuit range(NAVDD): NAVDD-VSS = -5.9V to -6.5V

- Positive polarity Source output high voltage level: VGMP = 3.5V to 5.9V (PAVDD-VGMP>0.25)

- Negative polarity Source output high voltage level: VGMN= -3.5V to -5.5V (NAVDD-VGMN<-0.25)

- Positive polarity Source output low voltage level: VGSP = 0.2V to 2.2V (PAVDD-VGSP>0.25)

- Negative polarity Source output low voltage level: VGSN= -0.2V to -2.2V (NAVDD-VGSN<-0.25)

- Common electrode output voltage level: VCOM = -0.2 V to -2.3V (VCL-VCOM<-0.25)

- Positive gate driver output voltage level: VGH-VSS = 7.0V to 15.0V

- Negative gate driver output voltage level: VGL-AVSS = -15.0V to -7.0V

- Lower power consumption, suitable for battery operated systems

- CMOS compatible inputs

- Optimized layout for COG assembly

- ♦ HBM ESD (Handling body mode) > ±3KV, MM (machinery mode) > ±300V

2011/10/06 13 V2.0

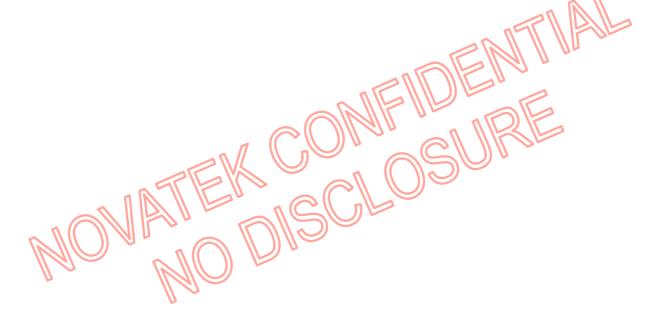

#### **3 BLOCK DIAGRAM**

2011/10/06 14 V2.0

# **4 PIN DESCRIPTION**

# **4.1 POWER SUPPLY PINS**

| Symbol   | Name         | Description                                                                                                   |

|----------|--------------|---------------------------------------------------------------------------------------------------------------|

| VPNL     | Power        | Power supply for Analog block, and booster                                                                    |

| VPNL_DET | Power        | Power supply for Analog block, and booster                                                                    |

| VDDI     | Power        | Power supply for I/O Pad VDDI=1.65V~4.8V or 1.1V~1.3V, depends on VSEL and DSTB_SEL setting                   |

| DIOPWR   | LDO Output   | DIOPWR output is for 1.2V or 1.8V application. DIOPWR is controlled by VSEL.                                  |

| VCC      | LDO Output   | Internal logic regulator output for logic circuit usage.  Connect a capacitor for stabilization.              |

| NVDDI    | LDO Output   | Negative Voltage level generated from VCC Connect a capacitor for stabilization.                              |

| VCCI     | Input        | Using to generate VCC, please connect to VPNL.                                                                |

| LVDSVDD  | MIPI Voltage | Regulator output for internal MIPI / MDDI analog system (1.5V typical) Connect a capacitor for stabilization. |

| VCCM12   | MIPI Voltage | Regulator output for internal MIPI low power system (1.2V typical) Connect a capacitor for stabilization.     |

| VSS      | Digital GND  | System ground for digital system                                                                              |

| cvss     | DC/DC GND    | System ground for booster system                                                                              |

| AVSS     | Analog GND   | System ground for Analog system                                                                               |

| LVDSVSS  | MIPI GND     | System ground for internal MIPI analog system                                                                 |

|          | 11 -         |                                                                                                               |

# **4.2 MODE SELECTION PINS**

| Symbol  | I/O  |               | Description                    |  |

|---------|------|---------------|--------------------------------|--|

|         |      | Interface typ | e selection                    |  |

|         |      | IM[3:0]       | Interface selection            |  |

|         |      | 0000          | 80-series 8-bit MPU interface  |  |

|         |      | 0001          | 80-series 9-bit MPU interface  |  |

|         |      | 0010          | 80-series 16-bit MPU interface |  |

|         |      | 0011          | 80-series 18-bit MPU interface |  |

| IM[3:0] | I    | 0100          | 80-series 24-bit MPU interface |  |

|         |      | 1100          | 3-SPI                          |  |

|         |      | 1101          | 4-SPI                          |  |

|         |      | 1001          | RGB mode + 3-SPI               |  |

|         | 1110 | 1110          | MIPI interface                 |  |

|         |      | 1111          | MDDI interface with 3-SPI      |  |

|         |      |               |                                |  |

NOTE: "1" = VDDI level, "0" = VSS level.

2011/10/06 15 V2.0

# **4.3 INTERFACE LOGIC PINS**

| Symbol     | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESX       | ı   | This signal will reset the device and must be applied to properly initialize the chip. Signal is active low.  The input voltage range for RESX pin is related to DSTB_SEL and VSEL pins.  Input Voltage Level (DSTB_SEL="0")                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CSX        | I   | Chip select input pin ("Low" enable) in 80-series MPU I/F and SPI I/F.  If this pin is not used, please connect to VDDI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| WRX (SCL)  | -   | Writes strobe signal to write data when WRX is "Low" in 80-series MPU I/F. Serial interface clock in SPI I/F. If this pin is not used, please connect to VDDI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RDX        | -   | Reads strobe signal to write data when RDX is "Low" in 80-series MPU interface.  If this pin is not used, please connect to VDDI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DCX        |     | Display data / command selection in 80-series MPU I/F.  DCX = "0" : Command  DCX = "1" : Display data or Parameter  If this pin is not used, please connect to VDDI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SDI        | I   | Serial input signal in SPI I/F. The data is input on the rising edge of the SCL signal. This pin is not used for 80-series MPU I/F and MIPI I/F, please connect to VSS this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SDO        | 0   | Serial output signal in SPI I/F. The data is output on the rising edge of the SCL signal. This pin is not used for 80-series MPU I/F and MIPI I/F, please connect to VSS this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| D[23:0]    | I/O | 24-bit bi-directional data bus for 80-series MPU I/F and RGB I/F. For 8080-series MPU I/F: 8-bit interface: D[7:0] are used, D[23:8] should be connected to VSS 16-bit interface: D[15:0] are used, D[23:16] should be connected to VSS 18-bit interface: D[17:0] are used, D[23:18] should be connected to VSS 24-bit interface: D[23:0] are used For RGB I/F: 16-bit/pixel: D[21:17]=R[4:0], D[13:8]=G[5:0] and D[5:1]=B[4:0], connect unused pins to VSS 18-bit/pixel: D[21:16]=R[5:0], D[13:8]=G[5:0] and D[5:0]=B[5:0], connect unused pins to VSS 24-bit/pixel: D[23:16]=R[7:0], D[15:8]=G[7:0] and D[7:0]=B[7:0] These pins are not used for MIPI I/F, please connect to VSS these pins. |

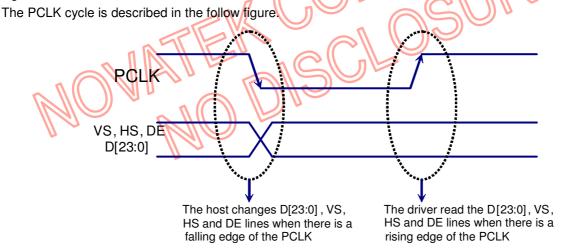

| PCLK       | I   | Pixel clock signal in RGB I/F. This pin is not used for 80-series MPU I/F and MIPI I/F, please connect to VSS this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2011/10/06 |     | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

2011/10/06 16 V2.0

| VS         | ı | Vertical sync. Signal in RGB I/F.                                                                                                                                                                                                                       |

|------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |   | This pin is not used for 80-series MPU I/F and MIPI I/F, please connect to VSS this pin.                                                                                                                                                                |

| HS         | I | Horizontal sync. Signal in RGB I/F. This pin is not used for 80-series MPU I/F and MIPI I/F, please connect to VSS this pin.                                                                                                                            |

| DE         | I | Data enable signal in RGB I/F mode 1. This pin is not used for RGB mode 2, 80-series MPU I/F and MIPI I/F, please connect to VSS this pin.                                                                                                              |

| TE_L(TE_R) | 0 | Tearing effect output pin to synchronize MCU to frame writing, activated by S/W command. When this pin is not activated, this pin is output low. If not used, please open this pin TE_L & TE_R can't connect together, choose one side for application. |

| ERR        | 0 | CRC and ECC error output pin for MIPI interface, activated by S/W command. This pin is output low when it is not activated. When this pin is activated, it output high if CRC/ECC error found. If not used, please open this pin.                       |

NOTE: "1" = VDDI level, "0" = VSS level.

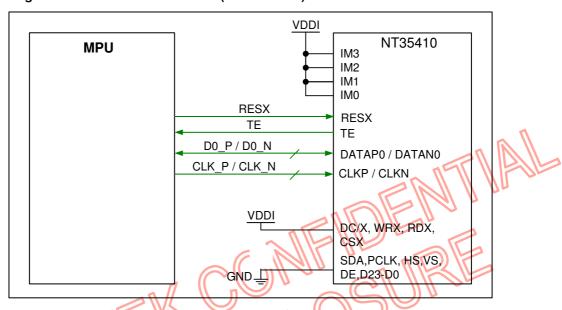

## 4.4 MIPI / MDDI INTERFACE PINS

| Symbol         | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK_P<br>CLK_N |     | -If MIPI interface is selected (IM[3:0] = "1110"), these two pins are positive/negative polarity of MIPI differential clock signalIf MDDI interface is selected (IM[3:0] = "1111"), these two pins are positive/negative polarity of MDDI differential strobe signalThe polarity of these two pins can be changed by command for MIPI / MDDI interface onlyIf not used, please connect these pins to LVDSVSSIf not used, please connect these pins to LVDSVSS. |

| D0_P<br>D0_N   | I/O | -(f MIPI interface is selected (IM[3:0] = "1110"), these two pins are positive/negative polarity of MIPI differential data signalIf MDDI interface is selected (IM[3:0] = "1111"), these two pins are positive/negative polarity of MDDI differential data signalThe polarity of these two pins can be changed by command for MIPI / MDDI interface onlyIf not used, please connect these pins to LVDSVSS.                                                     |

2011/10/06 17 V2.0

# 4.5 CABC Control Pins

| Symbol     | I/O             |                                                                                                                 |                                                                         |                                       | Docorinti                 | on   |                              |                      |  |  |  |  |  |  |  |  |

|------------|-----------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------|---------------------------|------|------------------------------|----------------------|--|--|--|--|--|--|--|--|

| Symbol     | 1/0             | - This pin is connected to the external driver.                                                                 |                                                                         |                                       |                           |      |                              |                      |  |  |  |  |  |  |  |  |

| BC_L(BC_R) | 0               | - Tris pin is connected - PWM type control s - The width of this PV - If not used, please of - BC_L & BC_R can' | ignal for<br>VM sign<br>open thi                                        | r brightnes<br>al is set in<br>s pin. | ss of the LE<br>256 steps | fron | n 0%(Low) to 100%(I          | High).               |  |  |  |  |  |  |  |  |

|            |                 | - This pin is used to se                                                                                        | This pin is used to select the output level of signal for BC, TE, RESX. |                                       |                           |      |                              |                      |  |  |  |  |  |  |  |  |

|            |                 | DSTB_SEL VDDI                                                                                                   | VSEL                                                                    | DIOPWR                                | TE_PWR_<br>(0xC1 CM       |      | Output Voltag<br>TE          | e Level<br>BC        |  |  |  |  |  |  |  |  |

|            |                 | 0 1.65~4.8                                                                                                      | v x                                                                     | Off                                   | Х                         |      | VOH=VDDI<br>VOL=VSSI         | VOH=VDDI<br>VOL=VSSI |  |  |  |  |  |  |  |  |

|            |                 |                                                                                                                 | Low                                                                     | 1.2V                                  | 0                         |      | VOH=VDDI<br>VOL=VSSI         | VOH=VDDI             |  |  |  |  |  |  |  |  |

|            |                 | 1 1.65~1.95                                                                                                     |                                                                         | 1.2 V                                 | nE                        | N    | VOH=1.2V(DIOPWR)<br>VOL=VSSI | VOL=VSSI             |  |  |  |  |  |  |  |  |

|            |                 | 1.00 1.00                                                                                                       | High                                                                    | 1.8V                                  | 1/1/9/                    |      | VOH=VDDI<br>VOL=VSSI         | VOH=VDDI             |  |  |  |  |  |  |  |  |

| VSEL       | ı               |                                                                                                                 |                                                                         |                                       | 1                         | J    | VOH=1.8V(DIOPWR) VOL=VSSI    | VOL=VSSI             |  |  |  |  |  |  |  |  |

| VSEL       | ı<br>n          |                                                                                                                 | Low                                                                     | 1,2V                                  | 10 //                     |      | VOL=VDDI<br>VOL=VSSI         | VOH=VDDI<br>VOL=VSSI |  |  |  |  |  |  |  |  |

|            | $\ f\ _{L^{2}}$ | 1 1.1~1.3\                                                                                                      |                                                                         |                                       |                           |      | VOH=1.2V(DIOPWR)<br>VOL=VSSI | VOL=V331             |  |  |  |  |  |  |  |  |

| ILM        |                 |                                                                                                                 | \(\(\)\\\                                                               |                                       | 0                         |      | VOH=VDDI<br>VOL=VSSI         | VOH=VDDI             |  |  |  |  |  |  |  |  |

| 110        |                 |                                                                                                                 | High                                                                    | 1.8V                                  | 1                         |      | VOH=1.8V(DIOPWR)<br>VOL=VSSI | VOL=VSSI             |  |  |  |  |  |  |  |  |

|            |                 | The input voltage rang                                                                                          | ge for V                                                                | SEL pin:                              |                           |      | _                            |                      |  |  |  |  |  |  |  |  |

|            |                 | Input Voltage L                                                                                                 | evel                                                                    | Min.                                  | Max.                      | Uni  | t                            |                      |  |  |  |  |  |  |  |  |

|            |                 | Logic High level inpu                                                                                           |                                                                         |                                       | VDDI                      | V    |                              |                      |  |  |  |  |  |  |  |  |

|            |                 | Logic Low level inpu                                                                                            |                                                                         |                                       | 0.55                      | V    |                              |                      |  |  |  |  |  |  |  |  |

|            |                 | If not used, please co                                                                                          |                                                                         |                                       |                           |      |                              |                      |  |  |  |  |  |  |  |  |

| DSTB_SEL   | I               | DSTB_SEL is used to<br>DSTB_SEL=1(default<br>DSTB_SEL=0, Dual IO                                                | ), Dual I                                                               | O power o                             | n(DIOPWI                  |      | standby mode.                |                      |  |  |  |  |  |  |  |  |

2011/10/06 18 V2.0

## 4.6 Others

| Symbol                                                                                         | I/O | Description                                                                                                                                                            |

|------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VOTP                                                                                           | I   | <ul><li>MTP programming power pin. Normal Operation: Keep the pin floating or connect to GND.</li><li>MTP Programming: Apply external power 7.5V to this pin</li></ul> |

| TEST1~TEST16                                                                                   | I   | - Internal Test pad. Please open this pin for normal operation.                                                                                                        |

| VDDI_O                                                                                         | 0   | - VDDI voltage output level for control pin used.                                                                                                                      |

| VSS_O                                                                                          | 0   | - VSS voltage output level for control pin used                                                                                                                        |

| DUMMY_GND[0~1] DUMMY_GND[2~3] DUMMY_GND[4~6] DUMMY_GND[7~11] DUMMY_GND[12~14] DUMMY_GND[15~16] | 0   | - These pins are dummy (No function inside), internal pull to ground.                                                                                                  |

# **4.7 DRIVER OUTPUT PINS**

| Symbol      | I/O | Description                                                                                                                                                            |

|-------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

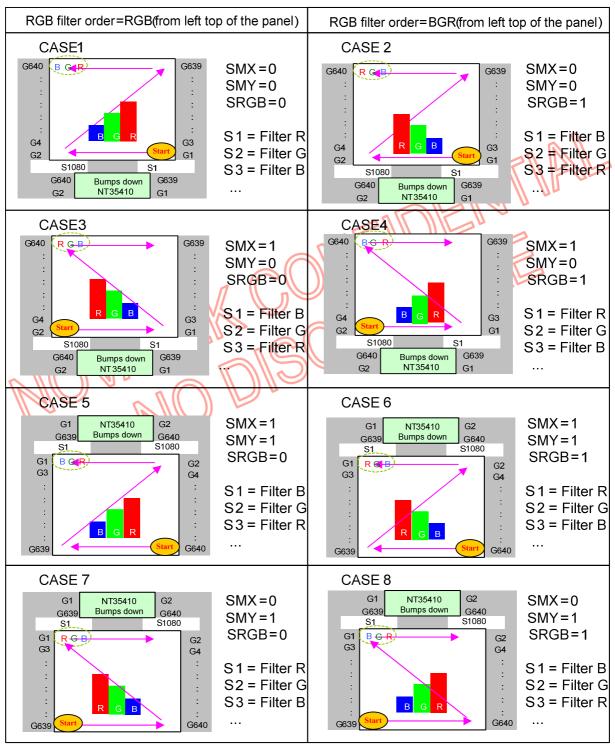

| SDUM0~SDUM3 |     | Liquid crystal application voltage output lines for Zigzag drive method. The shift direction of the segment signal output can be reversed by setting the Register SMX. |

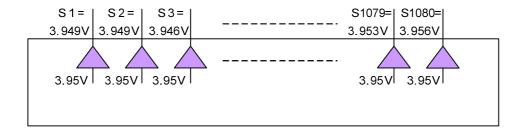

| S1 to S1080 | 0   | - Source driver output pins.                                                                                                                                           |

| G1 to G640  | 0   | - Gate driver output pins.                                                                                                                                             |

2011/10/06 19 V2.0

# 4.8 DC/DC CONVERTER PINS

| Symbol                              | I/O           | Description                                                                                                                                      |

|-------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| VCOM                                | 0             | VCOM output voltage for DC VCOM mode. Connect a capacitor to stabilize output voltage                                                            |

| PAVDD                               | Power output  | Positive Power supply to the source and VCOM drive. Connect a stabilizing capacitor.                                                             |

| NAVDD                               | Power output  | Negative Power supply to the source and VCOM drive.  Connect a stabilizing capacitor.                                                            |

| VGH                                 | Power output  | Output voltage from the step-up circuit, generated from PAVDD.  Connect a capacitor for stabilization.                                           |

| VGL/VGLO                            | Power output  | Output voltage from the step-up circuit, generated from NAVDD.  Connect a capacitor for stabilization.  VGL and VGLO must be connected together. |

| VCL                                 | Power output  | Output voltage from the step-up circuit, generated from VPNL.  Connect a capacitor for stabilization. VCL = - VPNL                               |

| C11P/C11N<br>C12P/C12N<br>C13P/C13N | Power         | Capacitor connection pins for the step-up circuit 1 which generate PAVDD. Connect capacitors as requirement.                                     |

| C21P/C21N<br>C22P/C22N<br>C23P/C23N | Power         | Capacitor connection pins for the step-up circuit 2 which generate NAVDD. Connect capacitors as requirement.                                     |

| C31P/C31N                           | Power         | Capacitor connection pins for the step-up circuit 3 which generate VCL. Connect capacitors as requirement.                                       |

| C41P/C41N                           | Power         | Capacitor connection pins for the step-up 4 circuit which generate VGH. Connect capacitors as requirement.                                       |

| C51P/C51N                           | Power         | Capacitor connection pins for the step-up 5 circuit which generate VGL. Connect capacitors as requirement.                                       |

| VREF                                | LDO<br>Output | Reference voltage output from the internal reference voltage generating circuit. Connect a capacitor for stabilization.                          |

| VGMP                                | LDO<br>Output | Positive voltage level generated from PAVDD. LDO output for gray scale high voltage generator.                                                   |

| VGMN                                | LDO<br>Output | Negative voltage level generated from NAVDD. LDO output for gray scale high voltage generator.                                                   |

| VGSP                                | LDO<br>Output | Positive voltage level generated from PAVDD. LDO output for gray scale low voltage generator.                                                    |

| VGSN                                | LDO<br>Output | Negative voltage level generated from NAVDD. LDO output for gray scale low voltage generator.                                                    |

2011/10/06 20 V2.0

#### **5 FUNCTIONAL DESCRIPTION**

## **5.1 MPU INTERFACE**

NT35410 can interface with MPU at high speed. However, if the interface cycle time is faster than the limit, MPU needs to have dummy wait(s) to meet the cycle time limit.

# 5.1.1 Interface Type Selection

The selection of a given interfaces are done by setting IM3, IM2, IM1 and IM0 pins as show in *Table 5.1.1 and Table 5.1.2*

Table 5.1.1 Interface Type Selection

| IM3 | IM2 | IM1 | IMO | Interface                | Read back selection                                                |

|-----|-----|-----|-----|--------------------------|--------------------------------------------------------------------|

| 0   | 0   | 0   | 0   | 8080 MCU 8-bit Parallel  | RDX strobe (8-bit read data and 8-bit read parameter)              |

| 0   | 0   | 0   | 1   | 8080 MCU 9-bit Parallel  | RDX strobe (9-bit read data and 8-bit read parameter)              |

| 0   | 0   | 1   | 0   | 8080 MCU 16-bit Parallel | RDX strobe (16-bit read data and 8-bit read parameter)             |

| 0   | 0   | 1   | 1   | 8080 MCU 18-bit Parallel | RDX strobe (18-bit read data and 8-bit read parameter)             |

| 0   | 1   | 0   | 0   | 8080 MCU 24-bit Parallel | RDX strobe (24-bit read data and 8-bit read parameter)             |

| 1   | 1   | 0   | 0   | SPI 3-pins serial        | Via the read instruction (8-bit, 24-bit and 32-bit read parameter) |

| 1   | 1   | 0   | 1   | SPI 4-pins serial        | Via the read instruction (8-bit, 24-bit and 32-bit read parameter) |

| 1   | 0   | 0   | 1   | RGB mode 1/2             | Via the read instruction (8-bit, 24-bit and 32-bit read parameter) |

| 1   | 1   | 1   | 0   | MIPI 1                   | Follow MIPI Read Back Sequence                                     |

| 1   | 1   | 1   | 1   | MDDI                     | Follow MDDI Read Back Sequence                                     |

Table 5.1.2 Pin Connection according to the Interface Type

| IM3 | IM2 | IM1 | IMO | Interface                | RDX    | WRX    | DCX    | Read back selection                                                         |

|-----|-----|-----|-----|--------------------------|--------|--------|--------|-----------------------------------------------------------------------------|

| 0   | 0   | 0   | 0   | 8080 MCU 8-bit Parallel  | RDX    | WRX    | DCX    | D[23:8]: Unused, D7-D0: 8-bit Data                                          |

| 0   | 0   | 0   | 1   | 8080 MCU 9-bit Parallel  | RDX    | WRX    | DCX    | D[23:9]: Unused, D8-D0: 9-bit Data                                          |

| 0   | 0   | 1   | 0   | 8080 MCU 16-bit Parallel | RDX    | WRX    | DCX    | D[23:16]: Unused, D15-D0: 16-bit Data                                       |

| 0   | 0   | 1   | 1   | 8080 MCU 18-bit Parallel | RDX    | WRX    | DCX    | D[23:18]: Unused, D17-D0: 18-bit Data                                       |

| 0   | 1   | 0   | 0   | 8080 MCU 24-bit Parallel | RDX    | WRX    | DCX    | D[23:0] : 24-bit Data                                                       |

| 1   | 1   | 0   | 0   | SPI 3-pins serial        | Note 1 | SCL    | Note 1 | D[23:0]: Unused, SDI,SDO,<br>WRX pad: SCL                                   |

| 1   | 1   | 0   | 1   | SPI 4-pins serial        | Note 1 | SCL    | Note 1 | D[23:0]: Unused, SDI, SDO,<br>WRX pad: SCL                                  |

| 1   | 0   | 0   | 1   | RGB mode 1/2             | Note 1 | SCL    | Note 1 | - SDI, SDO, WRX pad: SCL<br>RGB mode 1/2 is selected by command<br>via SPI. |

| 1   | 1   | 1   | 0   | MIPI                     | Note 1 | Note 1 | Note 1 | D[23:0]: Unused,<br>CLK_P/CLK_N, D0_P/D0_N                                  |

| 1   | 1   | 1   | 1   | MDDI                     | Note 1 | Note 1 | Note 1 | D[23:0]: Unused,<br>CLK_P/CLK_N, D0_P/D0_N                                  |

Note1: Unused pins connected to VDDI.

2011/10/06 21 V2.0

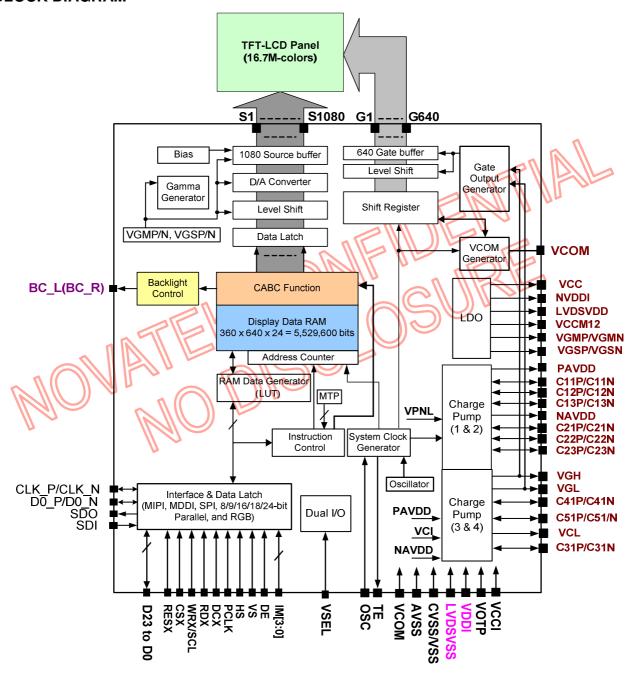

#### 5.1.2 80-series MPU Interface

The MCU uses an 11-wires 8-data or 12-wires 9-data or 19-wires 16-data or 21-wires 18-data or 27-wires 24-data parallel interface.

The chip-select CSX (active low) enables and disables the parallel interface. WRX is the parallel data write, RDX is the parallel data read and D[23:0] is parallel data.

The Graphics Controller Chip reads the data at the rising edge of WRX signal. The DCX is the data/command flag. When DCX='1', D[23:0] bits are display RAM data or command parameters. When DCX='0', D[23:0] bits are commands.

The 8080-series bi-directional interface can be used for communication between the micro controller and LCD driver chip. Interface bus width can be selected with IM3, IM2, IM1 and IM0.

The interface functions of 80-series parallel interface are given in *Table 5.1.3*.

Table 5.1.3 Parallel interface function (80-Series).

| IM3 | IM2 | IM1 | IM0 | Interface       | DCX                       | RDX                 | WRX        | Function                                                          |

|-----|-----|-----|-----|-----------------|---------------------------|---------------------|------------|-------------------------------------------------------------------|

|     |     |     |     |                 | 0                         | 1                   | <b>↑</b>   | Write 8-bit command (D7 to D0)                                    |

| 0   | 0   | 0   | 0   | 8-bit Parallel  | 1                         | 1                   | <b>↑</b>   | Write 8-bit display data or 8-bit parameter (D7 to D0)            |

| 0   | U   | U   | U   | o-bit Faranei   | 1                         | 1                   | 1          | Read 8-bit display data (D7 to D0)                                |

|     |     |     |     |                 | 1                         |                     | 1          | Read 8-bit parameter or status (D7 to D0)                         |

|     |     |     |     |                 | 97                        | ((1                 |            | Write 8-bit command (D7 to D0)                                    |

| 0   | 0   | 0   | 4   | 9-bit Parallel  | $\mathbb{V}_{\mathbb{Z}}$ |                     | <b>)</b> ← | Write 9-bit display data (D8 to D0) or 8-bit parameter (D7 to D0) |

| "   | 0   | U   | '   | 9-DIL Parallel  | 1                         | 1                   | 1          | Read 9-bit display data (D8 to D0)                                |

|     |     |     | . 1 |                 | <b>7</b> 4                | 1                   | シニ         | Read 8-bit parameter or status (D7 to D0)                         |

|     |     |     |     |                 | 0                         | 7116                |            | Write 8-bit command (D7 to D0)                                    |

|     | 0   |     |     |                 | 1                         | \\ <sub>1</sub> \\< |            | Write 16-bit display data (D15 to D0) or 8-bit parameter (D7 to   |

| 0   |     |     | 0   | 16-bit Parallel | 11 11                     | ۳ رر                | '          | D0)                                                               |

|     |     | 7   |     | JIII M          | )) 1                      | 1                   | 1          | Read 16-bit display data (D15 to D0)                              |

|     | U   |     |     |                 | 1                         | 1                   | 1          | Read 8-bit parameter or status (D7 to D0)                         |

|     |     |     |     | 11 -            | 0                         | 1                   | <b>↑</b>   | Write 8-bit command (D7 to D0)                                    |

|     |     |     |     |                 | 4                         | 4                   |            | Write 18-bit display data (D17 to D0) or 8-bit parameter (D7 to   |

| 0   | 0   | 1   | 1   | 18-bit Parallel | 1                         | I                   | T          | D0)                                                               |

|     |     |     |     |                 | 1                         | 1                   | 1          | Read 18-bit display data (D17 to D0)                              |

|     |     |     |     |                 | 1                         | 1                   | 1          | Read 8-bit parameter or status (D7 to D0)                         |

|     |     |     |     |                 | 0                         | 1                   | <b>↑</b>   | Write 8-bit command (D7 to D0)                                    |

|     |     |     |     |                 | 4                         | 4                   |            | Write 24-bit display data (D23 to D0) or 8-bit parameter (D7 to   |

| 0   | 1   | 0   | 0   | 24-bit Parallel | 1                         | I                   | Т          | D0)                                                               |

|     |     |     |     |                 | 1                         | <b>1</b>            | 1          | Read 24-bit display data (D23 to D0)                              |

|     |     |     |     |                 | 1                         | <b>↑</b>            | 1          | Read 8-bit parameter or status (D7 to D0)                         |

Note: applied for command code: DAh, DBh, DCh, 04h, 09h, 0Ah, 0Bh, 0Ch, 0Dh, 0Eh, and 0Fh.

2011/10/06 22 V2.0

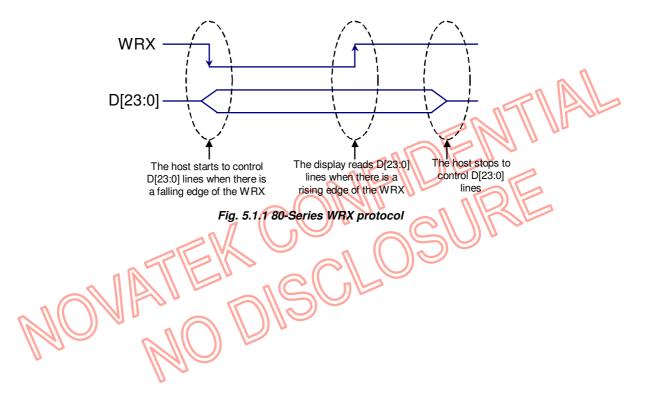

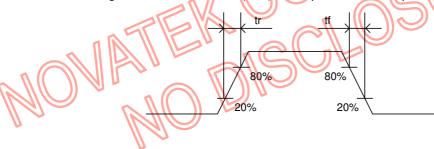

#### **5.1.2.1 WRITE CYCLE SEQUENCE**

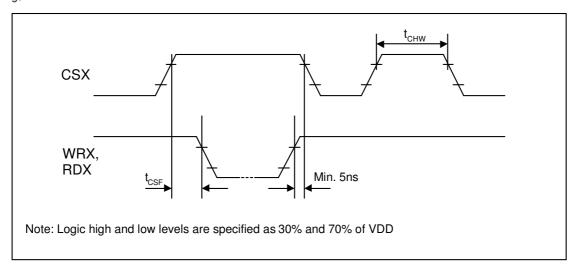

The write cycle means that the host writes information (command or/and data) to the display via the interface. Each write cycle (WRX high-low-high sequence) consists of 3 control (DCX, RDX, WRX) and data signals (D[23:0]). DCX bit is a control signal, which tells if the data is a command or a data. The data signals are the command if the control signal is low (='0') and vice versa it is data (='1').

Fig. 5.1.2 80-Series parallel bus protocol, write to register or display RAM

2011/10/06 24 V2.0

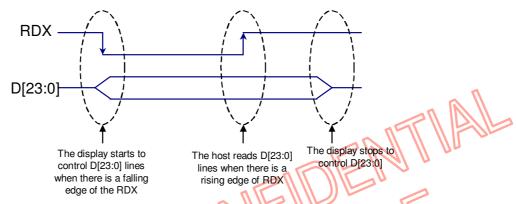

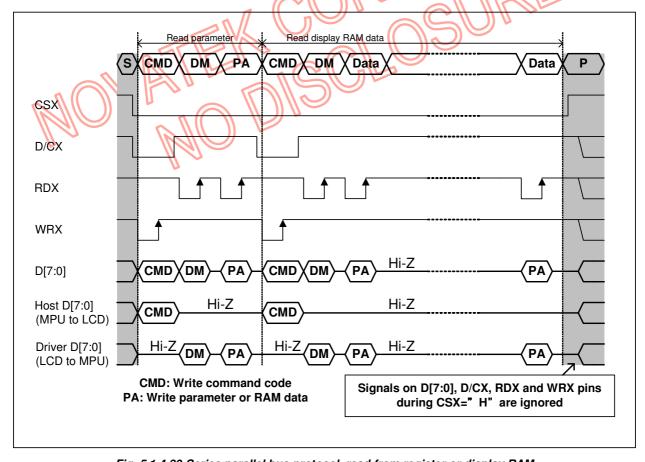

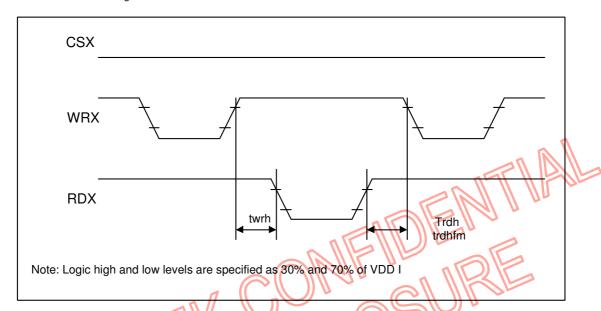

#### 5.1.2.2 Read cycle sequence

The read cycle (RDX high-low-high sequence) means that the host reads information from display via interface. The display sends data (D[23:0]) to the host when there is a falling edge of RDX and the host reads data when there is a rising edge of RDX.

Fig. 5.1.3 80-Series RDX protocol

Fig. 5.1.4 80-Series parallel bus protocol, read from register or display RAM

2011/10/06 25 V2.0

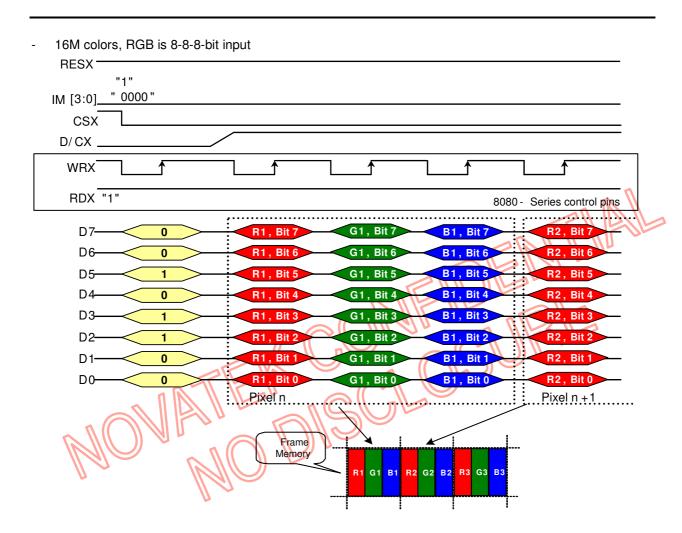

## 5.1.3 Display Data Format

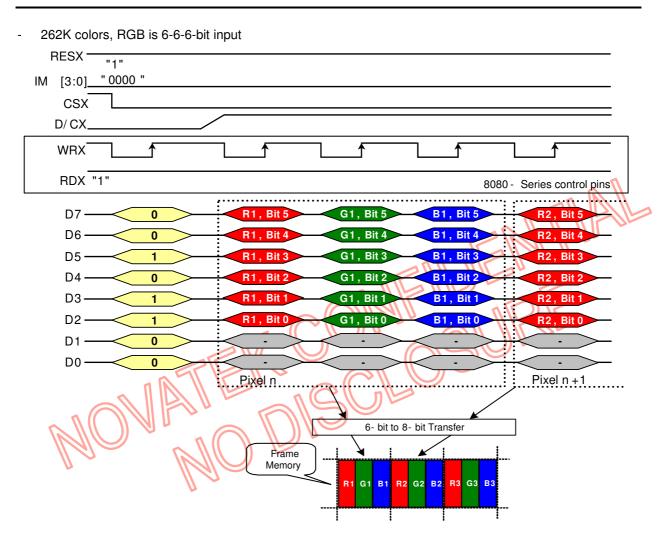

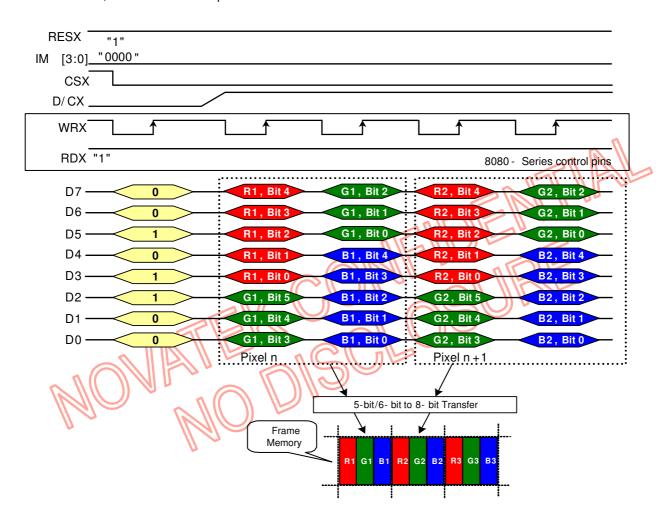

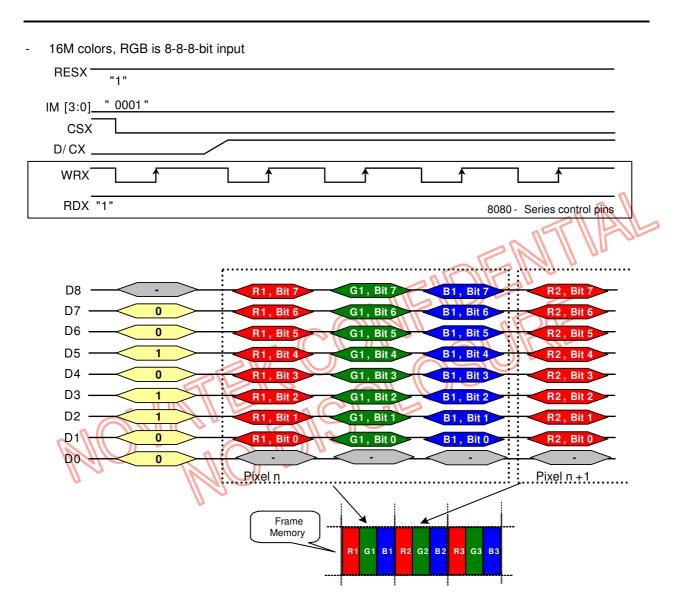

## 5.1.3.1 8-BIT PARALLEL INTERFACE FOR DATA RAM WRITE

Different display data formats are available for three colors depth supported by the LCM listed below.

|          |     |     |     |     |     |     |     |     |     |     |     |     |     |     | _  |    | _  |    |    |    |    |    |    |    |                     |

|----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|---------------------|

| Register | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Register            |

| Command  | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | X   | Х   | Х   | Х   | Х   | X  | Х  | 0  | 0  | 1  | 0  | 1  | 1  | 0  | 0  | 2Ch                 |

| 3Ah      | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Color               |

| 05h      | Х   | х   | Х   | Х   | х   | х   | Х   | х   | х   | Х   | Х   | Х   | х   | х   | Х  | Х  | R4 | R3 | R2 | R1 | R0 | G5 | G4 | G3 | 65K-Color           |

| 0511     | х   | х   | х   | х   | х   | х   | х   | х   | x   | х   | x   | х   | х   | х   | х  | х  | G2 | G1 | G0 | B4 | В3 | B2 | B1 | B0 | (1-pixels/ 2-bytes) |

|          | Х   | х   | Х   | Х   | Х   | х   | х   | х   | х   | Х   | Х   | Х   | Х   | Х   | Х  | Х  | R5 | R4 | R3 | R2 | R1 | R0 | X  | Х  | 262K-Color          |

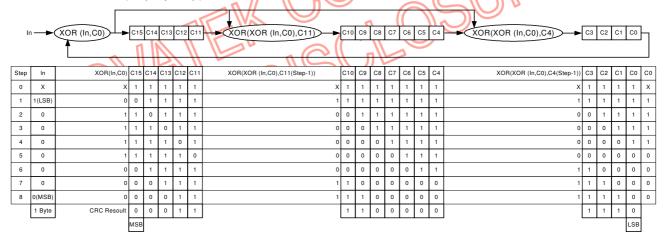

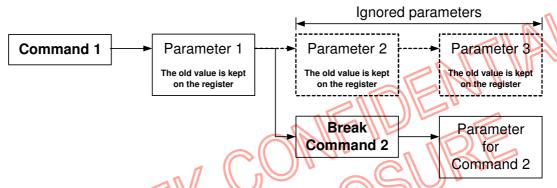

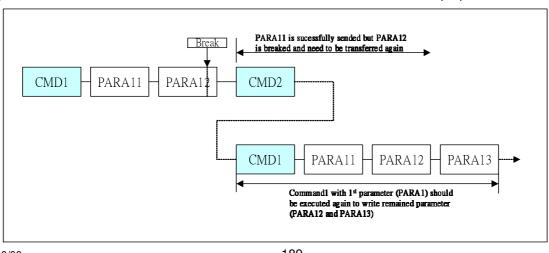

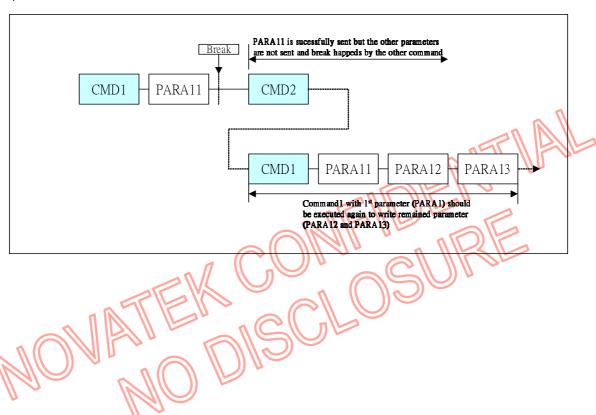

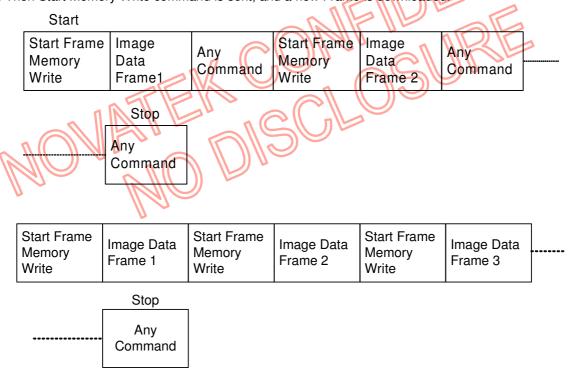

| 06h      | х   | х   | Х   | х   | Х   | х   | х   | х   | х   | х   | Х   | Х   | х   | Х   | X  | Х  | G5 | G4 | G3 | G2 | G1 | G0 | X  | Х  | (1-pixels/ 3bytes)  |