# NT7553E

396 X 162 RAM-Map STN LCD Controller/Driver for 32 Grayscale

V3.0

| Revision History             | 3   |

|------------------------------|-----|

| Features                     | 4   |

| General Description          | 5   |

| Pad Configuration            | 6   |

| Block Diagram                | 7   |

| Pad Descriptions             | 8   |

| Functional Descriptions      | 14  |

| General Commands Description | 62  |

| Absolute Maximum Rating      | 83  |

| Electrical Characteristics   | 83  |

| Bonding Diagram              | 92  |

| Ordering Information         | 103 |

| Cautions                     | 103 |

# **Revision History**

|         | NT7553E Specification Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | n History    |                  |               |           |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------|---------------|-----------|

| Version | Content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Prepared by  | Checked<br>by    | Approved by   | Date      |

| 1.0     | Released                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -            | -                | -             | Sep. 2007 |

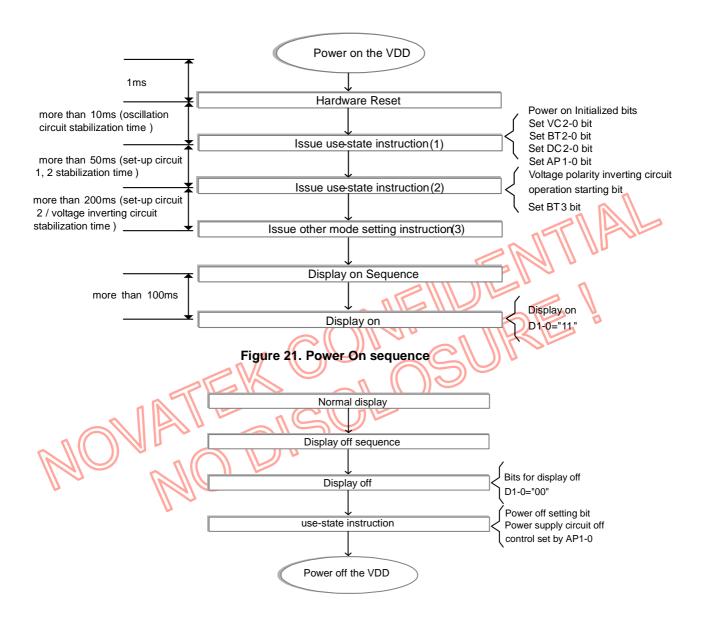

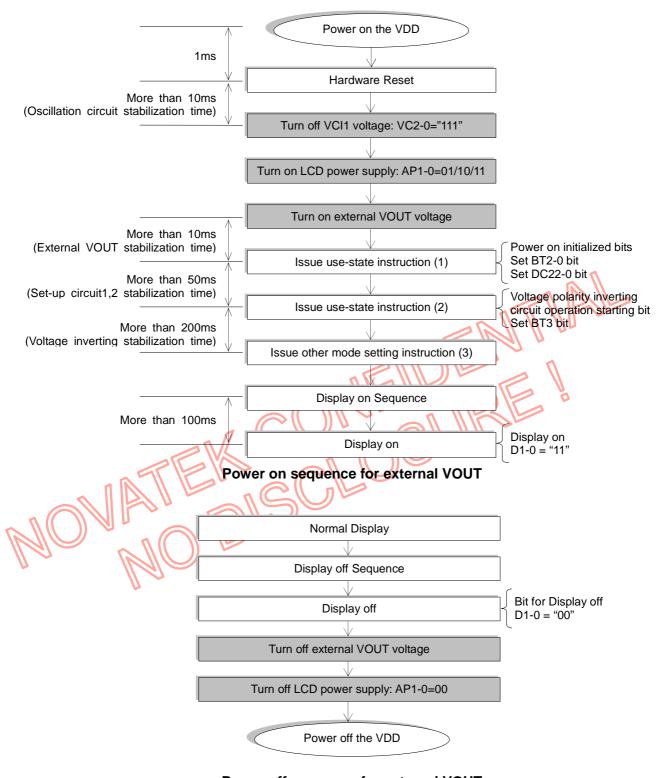

| 2.0     | 1. Correct the stabilization time between instruction (1) to (3) on figure 21.(Page 39) 2. Add ITO Layout Notice for Segment outputs. (Page 57) 3. Add Application Notice for Large Panel Design section. (Page 58) 4. Add Absolute Maximum Rating of VOUT condition. (Page 81)                                                                                                                                                                                                                                                                                        | Mike<br>Chen | Edwards<br>Tseng | Dennis<br>Kuo | Sep. 2008 |

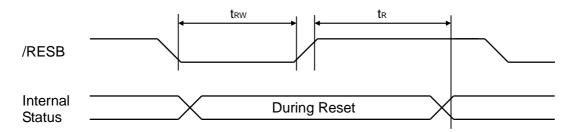

| 3.0     | <ol> <li>Add 100ms delay time between "display on sequence" and "display on" (Page 39)</li> <li>Add specification of Schottky Barrier Didoe.(Page 45)</li> <li>Correct recommend resistance of VDD and VSS from 100Ω to 50Ω.(Page 55)</li> <li>Add recommend external VOUT voltage on/off sequence.(Page 59, 60)</li> <li>Add MTPT description in table32. (Page 74)</li> <li>Add specification of Sleep Mode Current Consumption. (Page 83)</li> <li>Add specification of Reset Timing. (Page 91)</li> <li>Add specification of Chip Thickness. (Page 102)</li> </ol> | Mike<br>Chen | Edwards<br>Tseng | Dennis<br>Kuo | Nov. 2008 |

| M       | ONEX CONTROLLER CLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |                  |               |           |

#### **Features**

- 396 x 162-dot graphics display LCD controller/driver for 32 level grayscale.

- RAM capacity:  $396x 162 \times 5 = 320,760$  bits

- 8-bit and 16-bit parallel bus interface for both 8080 and 6800 series, and 4-wire Serial Peripheral Interface (SPI)

- Various grayscale-display control functions

- 32 grayscale out of 52 possible grayscale can be displayed at the same time (grayscale palette incorporated)

- Vertical scroll display function in raster-row units

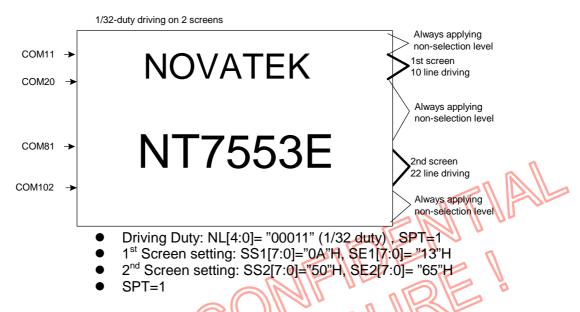

- Partial LCD drive of two screens in any position

- Shift change of segment and common drivers

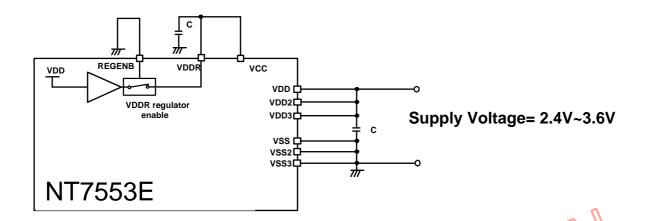

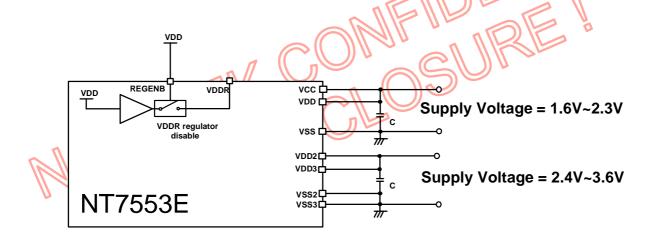

- Power supply voltage:

- VDD = 2.4 ~ 3.6 V (REGENB=L)

- VDD = 1.6 ~ 2.3 V (REGENB=H)

- $-VDD2 = 2.4 \sim 3.6 V$

- $VDD3 = 2.4 \sim 3.6 V$

- VCC = 1.6 ~2.3V

- Common driving voltage = 8 ~ 36 V (power for DC-DC converter)

- Segment driving voltage = 2 ~ 4 V

- VOUT = 4.5 ~ 5.5 V

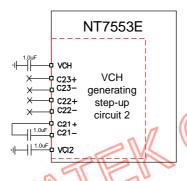

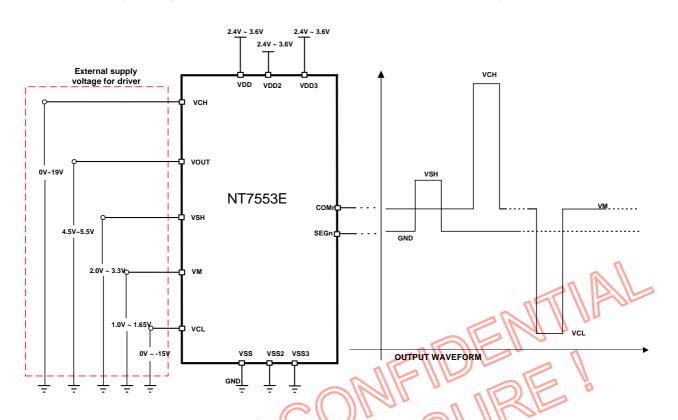

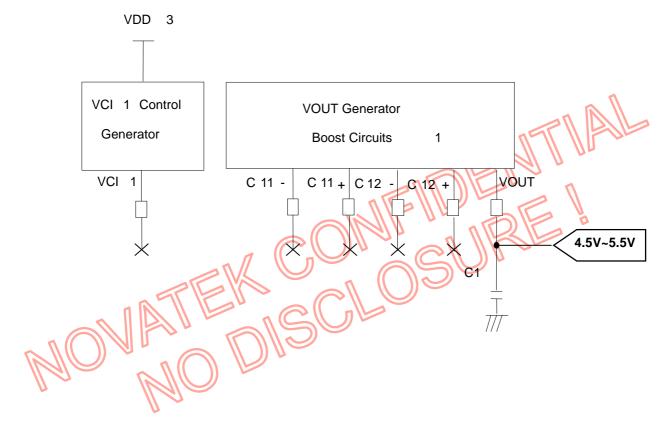

- VCI2 Maximum 4-times step-up circuit for liquid crystal drives voltage and voltage inverting circuit

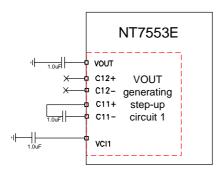

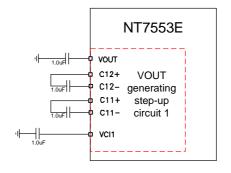

- VCI1 Maximum 3-times step-up circuit for VOUT

- Power save functions such as standby and sleep mode

- On chip LCD driving voltage generator or external power supply selectable

- 128-step contrast adjuster and on chip voltage follower to decrease direct current flow in the LCD drive bleeder-resisters

- Programmable drive duty ratios (1/8~1/162) and bias values (1/2~1/13) displayed on LCD

- Programmable partial display function

- Bit-operation functions for graphics processing:

- Write-data mask function in bit units

- Logical operation in pixel unit and conditional write function

- N-line inversion AC liquid-crystal drive (C-pattern waveform drive)

- On chip oscillation and hardware reset

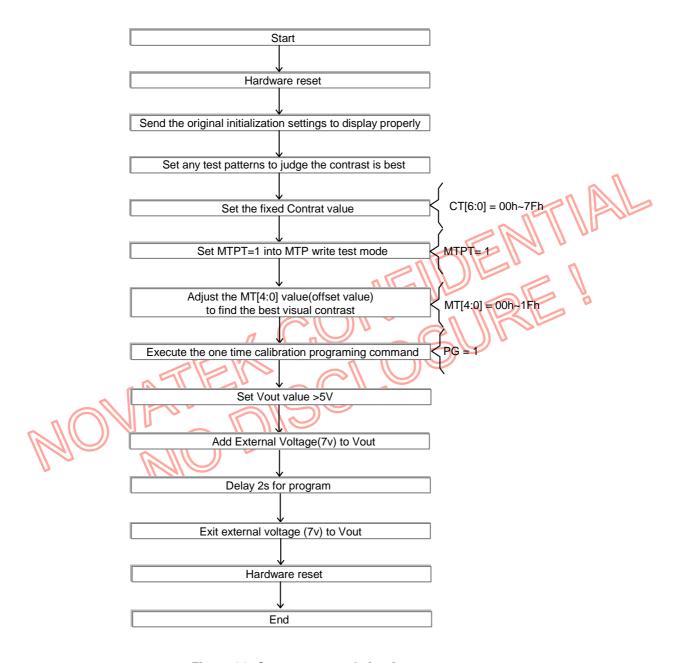

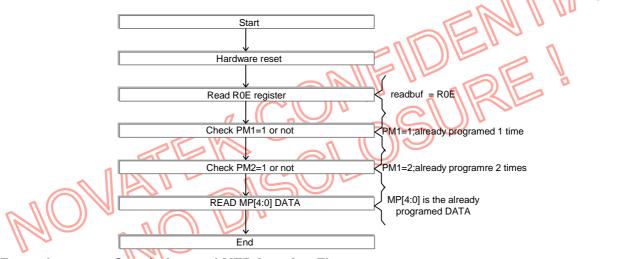

- Multi-Time Programming (2 times) for VSH voltage

- Programmable LCD Driving Voltage Temperature Compensation Coefficients (selected by software command)

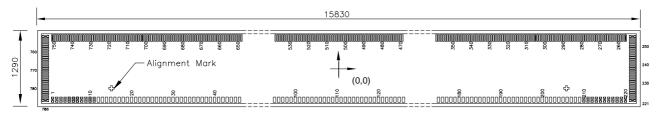

- COM positioned on both sides in one chip for COG form

- CMOS process

## **General Description**

The NT7553E is a single-chip LCD controller/driver LSI for grayscale-graphics, which displays 396 x 162-dot graphics for 32 levels STN grayscale. It accepts display data through 8-bit or 16-bit parallel (8080 or 6800 series) or serial interface directly sent from a microcomputer and stores it in an on-chip display RAM. It generates an LCD drive signal independent of microprocessor clock.

The set of the on-chip display RAM of 396 x 162 x 5 bits and every 5 bits correspondence between LCD panel dots and on-chip RAM bits permits implementation of displays with a high degree of freedom.

The NT7553E contains 162 common output circuits and 396 segment output circuits. It can make 8 to 162 x 396-dot displays with instructions.

The NT7553E has various functions for reducing the power consumption, such as low operation voltage of 2.4/Min., a DC-DC converter to generate a maximum of 12-times the LCD drive voltage from the supplied voltage, voltage follower to decrease the direct current flow in the LCD drive bleeder-resisters, and no external operation clock is required for RAM read/write operations. Accordingly, this driver can be operated with minimum current consumption and its on-board low-current-consumption liquid crystal power supply can implement a high-performance handy display system with minimum current consumption and the smallest LSI configuration.

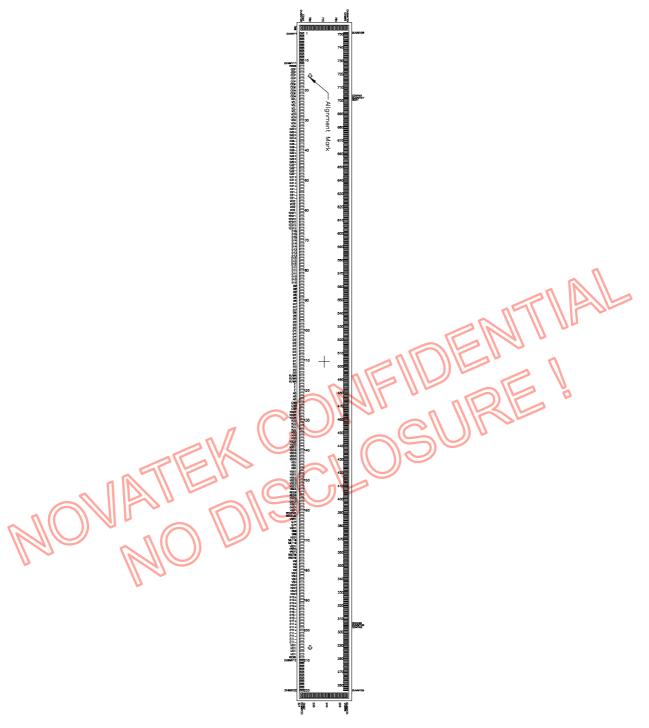

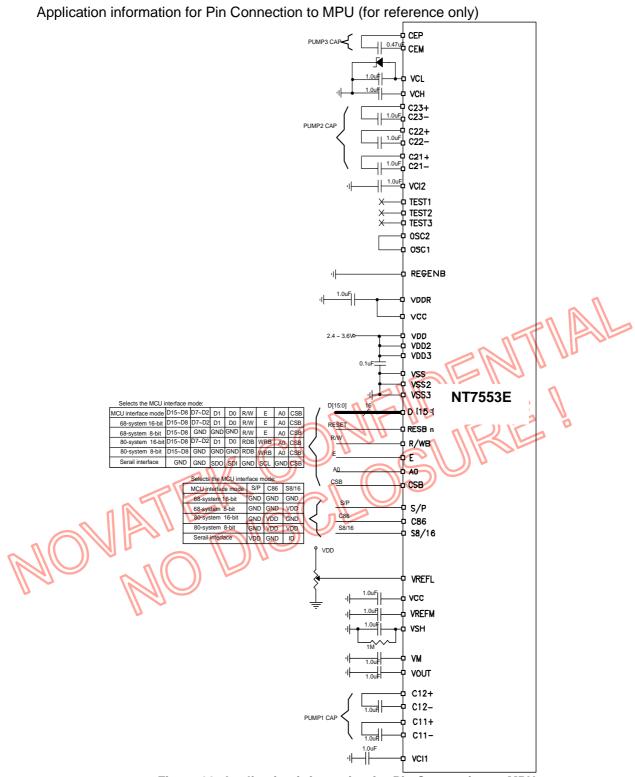

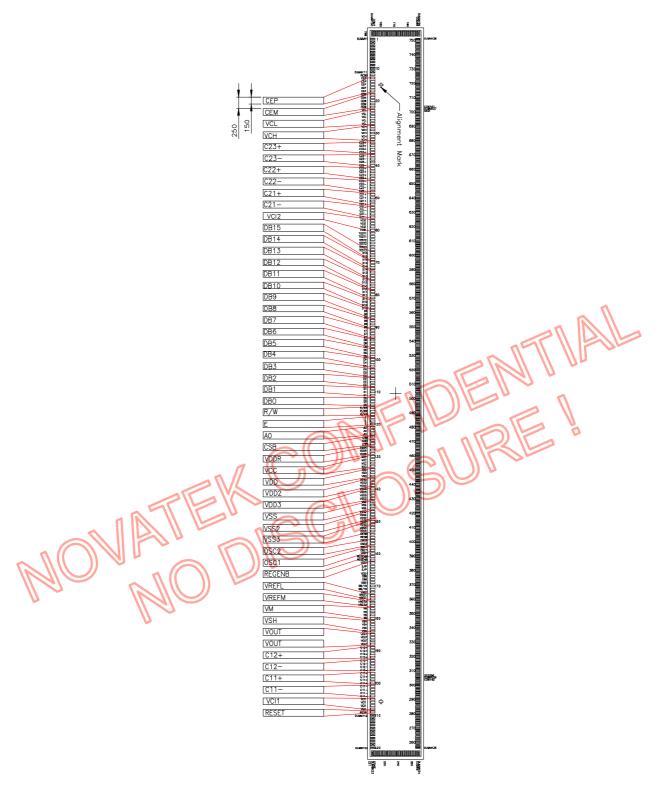

# **Pad Configuration**

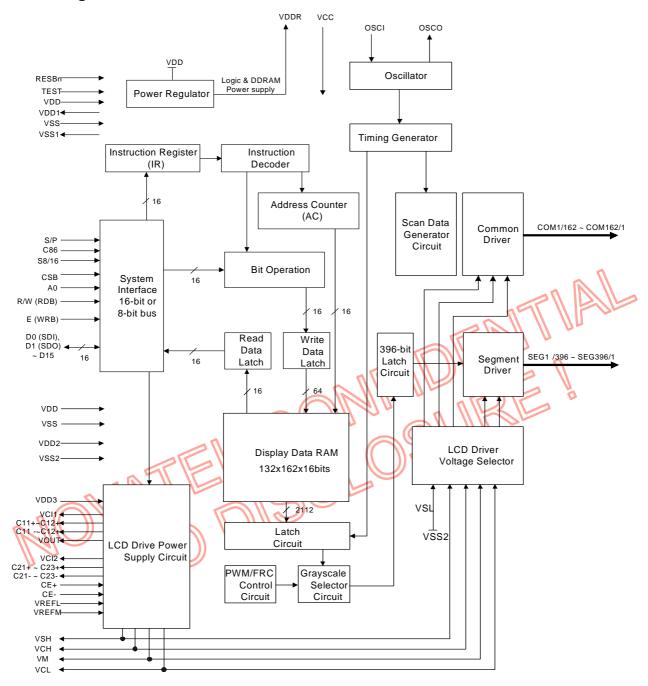

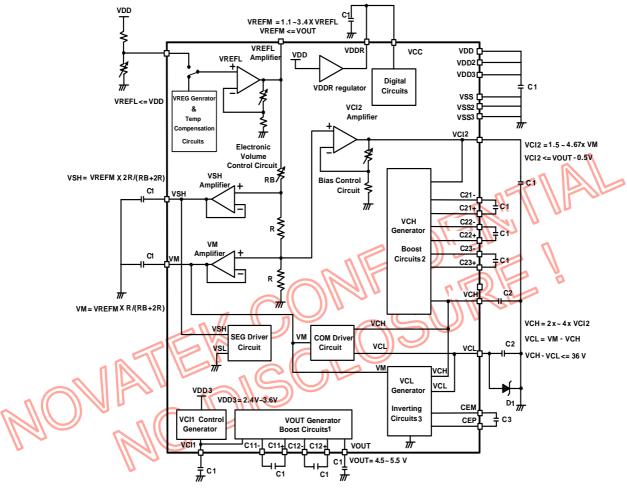

## **Block Diagram**

Figure 1. NT7553E Block Diagram Description

# **Pad Descriptions**

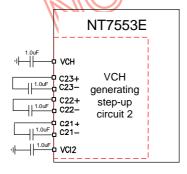

# **Power Supply**

| Pad No.     | Designation | I/O    | Description                                                                                                                                                                                                                                                            |  |  |  |

|-------------|-------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 134~136     | VDD         | Supply | Power supply for logic                                                                                                                                                                                                                                                 |  |  |  |

| 160,166,172 | VDD1        | 0      | Power supply output for pad option                                                                                                                                                                                                                                     |  |  |  |

| 137~139     | VDD2        | Supply | Power supply for analog, input the same level of voltage as VDD                                                                                                                                                                                                        |  |  |  |

| 140~143     | VDD3        | Supply | Voltage-input pin for step-up circuit 1.                                                                                                                                                                                                                               |  |  |  |

| 144~146     | VSS         | Supply | Ground for logic                                                                                                                                                                                                                                                       |  |  |  |

| 163,169     | VSS1        | 0      | Ground output for pad option                                                                                                                                                                                                                                           |  |  |  |

| 147~149     | VSS2        | Supply | Ground for analog                                                                                                                                                                                                                                                      |  |  |  |

| 150~153     | VSS3        | Supply | Ground for VDD3                                                                                                                                                                                                                                                        |  |  |  |

| 173~174     | VREFL       | Supply | Inputs reference voltage for LCD drives power supply.  Inputs a lower level than VDD. Since input current does not run, level input, which is divided by resistors, is also possible.                                                                                  |  |  |  |

| 205~208     | VCI1        | Supply | Voltage-input pin for step-up circuit 1. When the VCI adjuster is used, input the power supply from VCIOUT. When not used, input the external power supply.                                                                                                            |  |  |  |

| 57~60       | VCI2        | Supply | Capacitor for stabilization or open, connect capacitor for stabilization. When the internal power supply circuit is not used, leave this pin open.                                                                                                                     |  |  |  |

| 185~188     | VOUT        | Supply | A voltage that doubles or triples the voltage between VCI1 and VSS is output here. The step-up factor can be set in an internal register. When internal operational amplifier is not used, supply external voltage.                                                    |  |  |  |

| 181-184     | VSH         | Supply | The selection level for the segment signal. When internal operational amplifier is used, it is output from the internal operational amplifier and connects the capacitors for stabilization. When internal operational amplifier is not used, supply external voltage. |  |  |  |

| 28~32       | VCH         | Supply | Selection level for the common signal. When internal power supply is used, connect the capacitors for stabilization to VCH, When internal power supply is not used, supply external voltage.                                                                           |  |  |  |

| 23~27       | VCL         | Supply | Selection level for the common signal. When internal power supply is used, connect the capacitors for stabilization to VCL, and shot key barrier diode to VCL. When internal power supply is not used, supply external voltage.                                        |  |  |  |

# **Power Supply (CONTINUTE)**

| 177~180 | VM    | Supply | Non-selection level for the common signal. When internal operational amplifier is used, it is output from the internal operational amplifier and connects the capacitors for stabilization. When internal operational amplifier is not used, supply external voltage. |

|---------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 175~176 | VREFM | Supply | Capacitor for stabilization or external power supply. Connect capacitor for stabilization for internal power supply. When internal operational amplifier is not used, supply external voltage.                                                                        |

| 130~133 | VCC   | Supply | Capacitor for stabilization or open Connect capacitor for stabilization for internal power supply.                                                                                                                                                                    |

| 127~129 | VDDR  | 0      | Capacitor for stabilization or open Connect capacitor for stabilization for internal power supply.                                                                                                                                                                    |

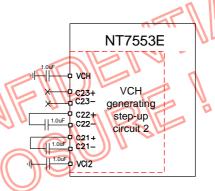

# **STEP-UP Capacitor Pad**

| Pad No. | Designation | I/O | Description                                                                                              |

|---------|-------------|-----|----------------------------------------------------------------------------------------------------------|

| 13~17   | CEP         | 0   | Connect a step-up capacitor to generate VCL level by VCH and VM. When step-up circuit is not used, leave |

| 18~22   | CEM         | 0   | this pin open.                                                                                           |

| 33~36   | C23+        | 0   | When step-up circuit is used, connect a step-up capacitor.                                               |

| 37~40   | C23-        | 0   | When step-up circuit is used, connect a step-up capacitor.                                               |

| 41~44   | C22+        | 0   | When step-up circuit is used, connect a step-up capacitor.                                               |

| 45~48   | C22-        | 0   | When step-up circuit is used, connect a step-up capacitor.                                               |

| 49~52   | C21+        | 0   | When step-up circuit is used, connect a step-up capacitor.                                               |

| 53~56   | C21-        | 10  | When step-up circuit is used, connect a step-up capacitor.                                               |

| 189~192 | C12+        | 0   | When step-up circuit is used, connect a step-up capacitor.                                               |

| 193-196 | C12-        | 0 / | When step-up circuit is used, connect a step-up capacitor.                                               |

| 197~200 | C11+        |     | When step-up circuit is used, connect a step-up capacitor.                                               |

| 201~204 | C11-        | 0   | When step-up circuit is used, connect a step-up capacitor.                                               |

# **Liquid Crystal Drive Pad**

| Pad No.                                     | Designation      | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

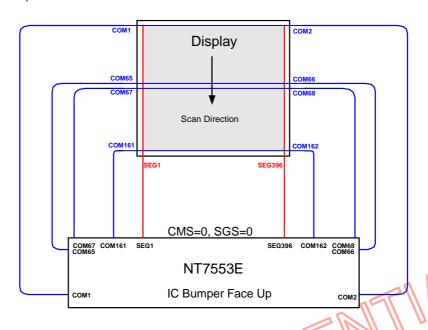

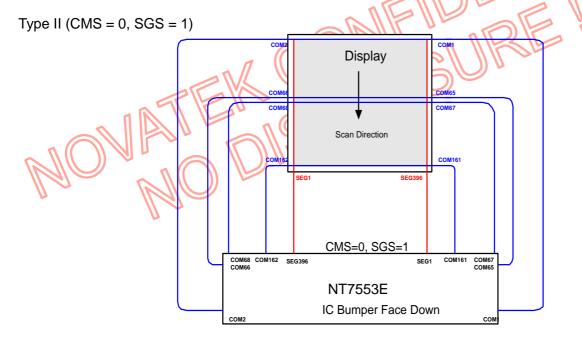

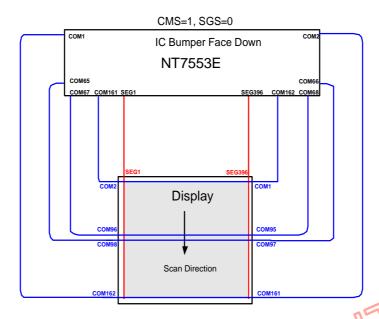

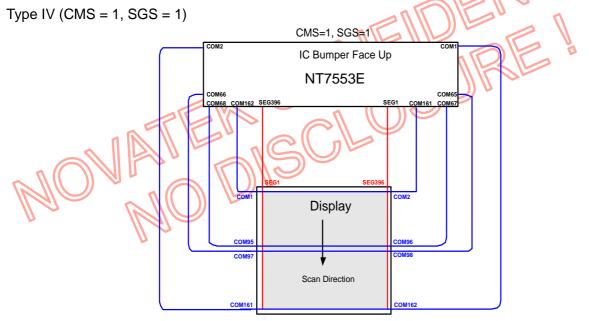

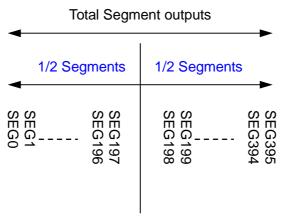

| 306~701                                     | SEG1 ~<br>SEG396 | 0   | Output signals for segment drive. In the display-off period (D1–0 = 00, 01) or standby mode (STB = 1), all pins output VSS level. The SGS bit can change the shift direction of the segment signal. For example, if SGS = 0, RAM address 0000 is output from SEG1 to SEG396. If SGS = 1, it is output from SEG396 to SEG1.                                                                                                              |

| 222~254,<br>257~304,<br>703~750,<br>753~785 | COM1 ~<br>COM162 | 0   | Output signals for common drive. In the display-off period (D1–0 = 00, 01) sleep mode (SLP = 1) or standby mode (STB = 1), all pins output VSS level. The CMS bit can change the shift direction of the common signal. For example, if CMS = 0, driver outputs from COM1 to COM162. If CMS = 1, driver outputs COM162 to COM1.  Note that the start position of the common driver output is changed by screen diving position function. |

# **System Bus Connection Pads**

| Pad No.              | Designation             | I/O | Description                                                                                                                                                                                                                                                                                                                                                              |

|----------------------|-------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 164~165              | S/P                     | I   | Serial/Parallel selection pad:<br>S/P = "L": parallel interface<br>S/P = "H": serial interface                                                                                                                                                                                                                                                                           |

| 167~168              | C86                     | I   | Select MPU parallel interface mode: When S/P = "L": C86 = "L": 6800 series MPU interface C86 = "H": 8080 series MPU interface When S/P = "H": C86 should be connected to VSS.                                                                                                                                                                                            |

| 170~171              | S8/16<br>(SID)          | I   | 8/16-bit parallel interface selection pad: When S/P = "L": S8/16 = "L": 16-bit parallel interface S8/16 = "H": 8-bit parallel interface When S/P = "H": This pad is used as the serial ID (SID) setting for a device code.                                                                                                                                               |

| 124~126              | CSB                     | I   | This is the chip select signal. When CSB = "L", then the chip select becomes active, and data/command I/O is enabled. It must be fixed to VSS when not in use.                                                                                                                                                                                                           |

| 121~123              | A0                      | ı   | A0 = "L": Indicates that D0 to D7 are Index or Status data A0 = "H": Indicates that D0 to D7 are Control data When a register or serial interface is selected, fix this pad to VDD or VSS level.                                                                                                                                                                         |

| 12<br>154~155<br>209 | RESB1<br>RESB2<br>RESB3 |     | Reset pin. Initializes the LSI when low. Must be reset after power-on. Since NT7553E has three RESET pins, use one pin and open two unused pins.                                                                                                                                                                                                                         |

| 115~117              | R/W<br>(RDB)            |     | When connected to a 6800 Series MPU, this is the read/write control signal input terminal. Low: Write, High: Read When connected to an 8080 MPU, this is active LOW. This terminal connects to the 8080 MPU RDB signal and the NT7553E data bus is in an output status when this signal is LOW. When the serial interface is selected, fix this pad to VDD or VSS level. |

| 118~120              | E<br>(WRB)<br>(SCL)     | I   | When connected to a 6800 Series MPU, this is active HIGH. This is used as an enable clock input of the 6800 series MPU. When connected to an 8080 MPU, it is active LOW. This pad is connected to the WRB signal of the 8080 MPU, and writes data at the low level. When the serial interface is selected, it serves as the serial clock input pin (SCL).                |

# **System Bus Connection Pads (continued)**

| 112~114 | D0<br>(SDI) | I/O | When 16-bit parallel interface is selected, it serves as the bi-directional data bus.  When 8-bit parallel interface is selected, data transfer uses D8 ~ D15; fix the unsed pads: D0 ~ D7 to the VDD or VSS level.  When the serial interface is selected, it serves as the serial data input terminal (SDI). The input level is read on the rising edge of SCL signal. |

|---------|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 109~111 | D1<br>(SDO) | I/O | When 16-bit parallel interface is selected, it serves as the bi-directional data bus. When 8-bit parallel interface is selected, data transfer uses D8 ~ D15; fix the unsed pads: D0 ~ D7 to the VDD or VSS level. When the serial interface is selected, it serves as the serial data output terminal (SDO).                                                            |

| 67~108  | D2 ~ D15    | I/O | When 16-bit parallel interface is selected, it serves as the bi-directional data bus.  When 8-bit parallel interface is selected, data transfer uses D8 ~ D15; fix the unsed pads: D0 ~ D7 to the VDD or VSS level.  When the serial interface is selected, fix these pads to VDD or VSS level.                                                                          |

| 161~162 | REGENB      | I   | Input pin for VDDR supply control,  REGENB = "L": VDDR regulator enable  REGENB = "H": VDDR regulator disable                                                                                                                                                                                                                                                            |

## **Oscillation Pads**

| Pad No. | Designation | 1/0 | Description                                            |

|---------|-------------|-----|--------------------------------------------------------|

| 158~159 | osci        | 1/0 | For external clock supply, input clock pulses to OSCI. |

| 156~157 | osco        | 1/0 | For internal clock mode, OSCI must connect to OSCO.    |

## **Dummy Pads**

| Pad No.  | Designation | I/O | Description                         |

|----------|-------------|-----|-------------------------------------|

| 1~11,    |             |     | Dummy pads. No connection for user. |

| 210~221, |             |     |                                     |

| 255~256, | Dummy       |     |                                     |

| 305,702, |             | -   |                                     |

| 751~752, |             |     |                                     |

| 786      |             |     |                                     |

#### **Test Pads**

| Pad No. | Designation | I/O | Description                         |       |  |  |  |  |

|---------|-------------|-----|-------------------------------------|-------|--|--|--|--|

| 61~62   | Test1       | -   | Test pad. Must disconnect this pad. | 2     |  |  |  |  |

| 63~64   | Test2       | -   | Test pad. Must disconnect this pad. |       |  |  |  |  |

| 65~66   | Test3       | -   | Test pad. Must disconnect this pad. | 2 191 |  |  |  |  |

# **Functional Descriptions**

#### **Microprocessor Interface**

The NT7553E can transfer data via 8-bit (D8 ~D15)/16-bit (D0~D15) bi-directional data bus or via serial data input (SDI). When high or low is selected for the S/P, C86, and S8/16 pads, either 8-bit/16-bit parallel data input or serial data input can be selected as shown in Table 1. When serial data input is selected, the RAM data can also be read out via serial data output (SDO).

Table 1. Data Bus Interface Selection Mode

| S/P | C86 | S8/16<br>(SID) | 11/00                           |     | A0 | E<br>(WRB)<br>(SCL) | R/W<br>(RDB) | D0  | D1  | D2~D7 | D8~D15 |

|-----|-----|----------------|---------------------------------|-----|----|---------------------|--------------|-----|-----|-------|--------|

| Н   | L   | L              | Serial interface bus SID = 0    | CSB | A0 | SCL                 | -            | SDI | SDO | -     | -      |

| ''  | L   | Н              | Serial interface bus SID = 1    | CSB | A0 | SCL                 | -            | SDI | SDO | -     | -      |

|     | L   | L              | 6800 series 16-bit parallel bus | CSB | A0 | Е                   | R/W          | D0  | D1  | D2~D7 | D8~D15 |

|     | L   | Н              | 6800 series 8-bit parallel bus  | CSB | A0 | Е                   | R/W          | -   |     |       | D8~D15 |

| -   | Н   | L              | 8080 series 16-bit parallel bus | CSB | A0 | WRB                 | RDB          | PQ  | D1  | D2~D7 | D8~D15 |

|     | Η   | Н              | 8080 series 8-bit parallel bus  | CSB | A0 | WRB                 | RDB          |     | 2   | -     | D8~D15 |

"-" Must always be high or low

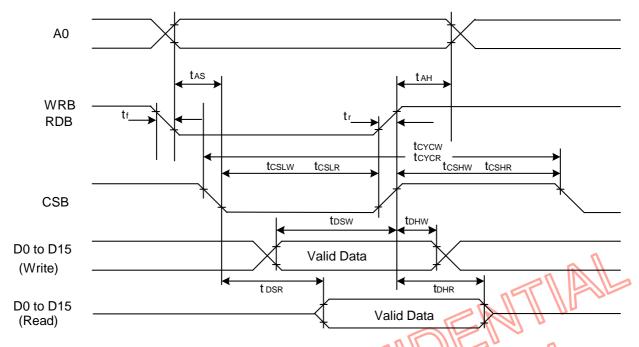

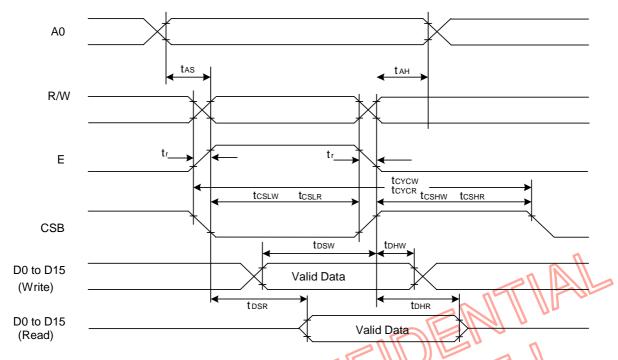

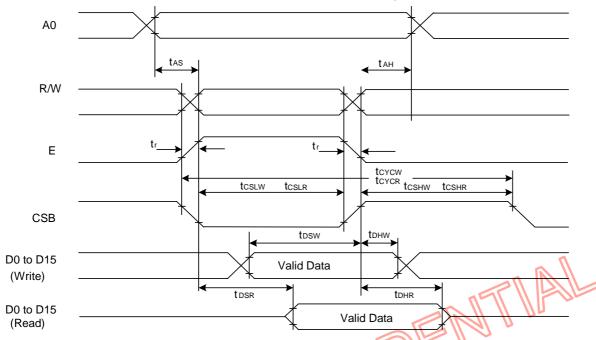

#### **Parallel Interface**

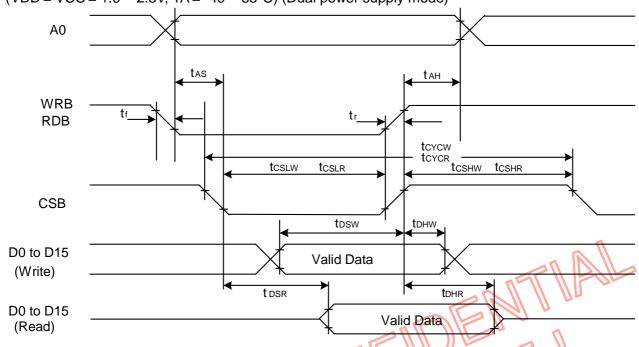

When the NT7553E selects parallel input (S/P = Low), the 8080 series microprocessor or 6800 series microprocessor can be selected by the C86 pad to be connected high or low. The NT7553E identifies the data bus signal according to A0, E (WRB), R/W (RDB) signals as shown in Table 2.

Table 2.Parallel Interface Read/Write Status

| Common | 6800 pr | ocessor | 8080 pr | ocessor | Function                                        |  |  |  |  |  |  |

|--------|---------|---------|---------|---------|-------------------------------------------------|--|--|--|--|--|--|

| A0     | E       | R/W     | RDB     | WRB     | 1 diletion                                      |  |  |  |  |  |  |

| 0      | 1       |         | 0       | 1       | Reads internal status                           |  |  |  |  |  |  |

| 0      | 1       | 0       | 1       | 0       | Writes indexes into IR (index register)         |  |  |  |  |  |  |

| 1      | 1       | 1       | 0       | 1       | Read from RAM data through RDR                  |  |  |  |  |  |  |

| 1      | 1       | 0       | 1       | 0       | Write control registers or RAM data through WDR |  |  |  |  |  |  |

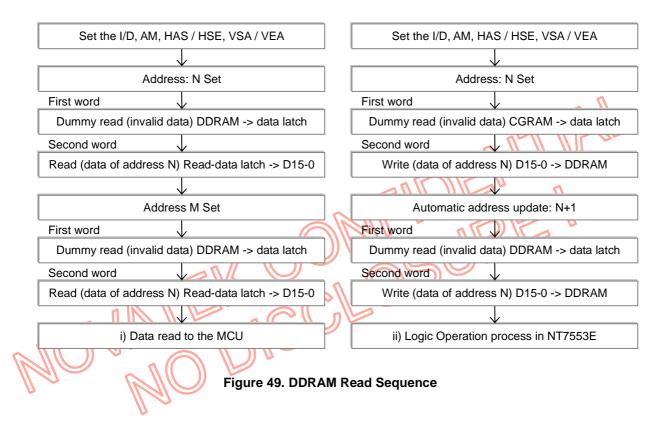

A dummy read is required before the first actual display data is read for parallel interface.

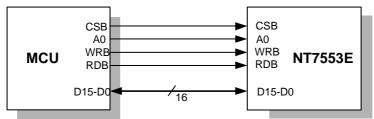

#### 16-bit Bus Interface

Setting the C86 and S8/16 (interface mode) to the VSS/VSS level allows 68-system E-clock-synchronized 16-bit parallel data transfer. Setting the C86 and S8/16 to the VDD/VSS level allows 80-system 16-bit parallel data transfer. When the number of buses or the mounting area is limited, use an 8-bit bus interface.

Interface to 16-bit Microcomputer

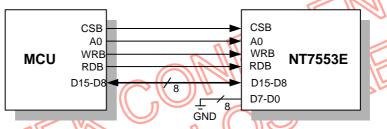

#### 8-bit Bus Interface

Setting the C86 and S8/16 (interface mode) to the VSS/VDD level allows 68-system E-clock-synchronized 8-bit parallel data transfer using pins D15 to D8. Setting the C86 and S8/16 to the VDD/VDD level allows 80-system 8-bit parallel data transfer. The 16-bit instructions and RAM data are divided into eight upper/lower bits and the transfer starts from the upper eight bits. Fix unused pins D7 to D0 to the VDD or VSS level. Note that the upper bytes must also be written when the index register is written.

Interface to 8-bit Microcomputer

Note:

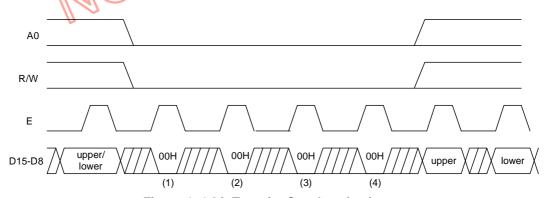

Transfer synchronization function for an 8-bit bus interface

The NT7553E supports the transfer synchronization function, which resets the upper/lower counter to count upper/lower 8-bit data transfer in the 8-bit bus interface. Noise causing transfer mismatch between the eight upper and lower bits can be corrected by a reset triggered by consecutively writing a 00H instruction four times. The next transfer starts from the upper eight bits. Executing synchronization function periodically can recover any runaway in the display system.

Figure 2. 8-bit Transfer Synchronization

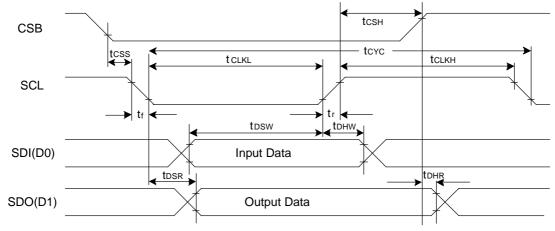

#### **Serial Interface**

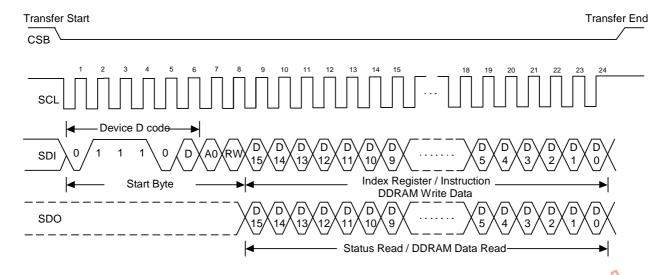

When the serial interface has been selected (S/P = High, C86 = Low), the SID (serial device ID) can be selected by the S8/16 pad to be connected high or low. The unused pads (D2~15) should be connected to VDD or VSS. When the chip is in serial interface, using the chip select input (CSB), serial clock input (SCL), serial data input (SDI) and serial data output (SDO) pins. The NT7553E initiates serial data transfer by transferring the start byte at the falling edge of CSB input. It ends serial data transfer at the rising edge of CSB input.

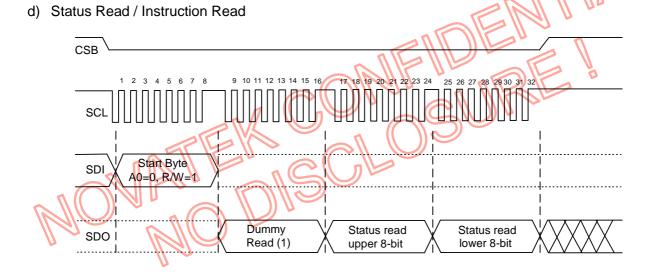

The NT7553E is selected when the 6-bit chip address in the start byte transferred from the transmitting device matches the 6-bit device identification code assigned to the NT7553E. The NT7553E, when selected, receives the subsequent data string. The ID (S8/16) pin can determine the LSB of the identification code. The five upper bits must be "01110". Two different chip addresses must be assigned to a single NT7553E because the seventh bit of the start byte is used as a register select bit (A0): that is, when A0 = "0", data can be written to the index register or status can be read, and when A0 = "1", an instruction can be issued or data can be written to or read from RAM. Read or write is selected according to the eighth bit of the start byte (R/W bit). The data is received when the R/W bit is "0", and is transmitted when the R/W bit is "1".

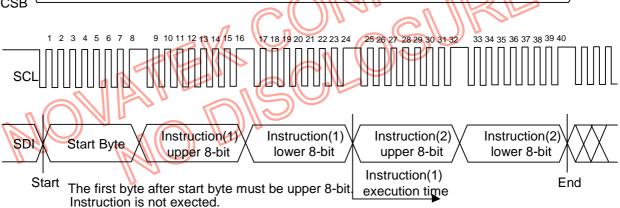

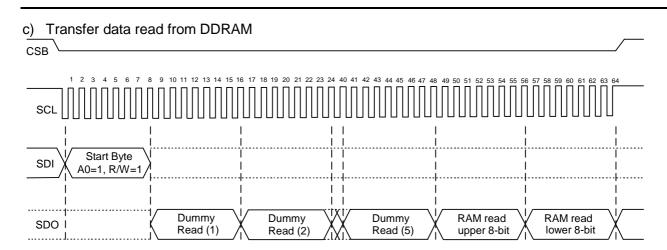

After receiving the start byte, the NT7553E receives or transmits the subsequent data byte-by-byte. The data is transferred with the MSB first. All NT7553E instructions are 16 bits. Two bytes are received with the MSB first (D15 to 0), and then the instructions are internally executed. After the start byte has been received, the first byte is fetched internally as the upper eight bits of the instruction and the second byte is fetched internally as the lower eight bits of the instruction. Five bytes of RAM read data after the start byte are invalid. The NT7553E starts to read correct RAM data from the sixth byte.

Function A0 R/W Reads internal status 0 Writes indexes into IR (index register)

Table 3. Serial Interface Read/Write Status

|   | Read from RAM data through RDR                    |

|---|---------------------------------------------------|

| 0 | Writes control registers and RAM data through WDR |

O

1. When the chip is not active, the shift registers and the counter is reset to their initial states.

2. Caution is required on the SCL signal when it comes to line-end reflections and external noise. We recommend the operation be rechecked on the actual equipment.

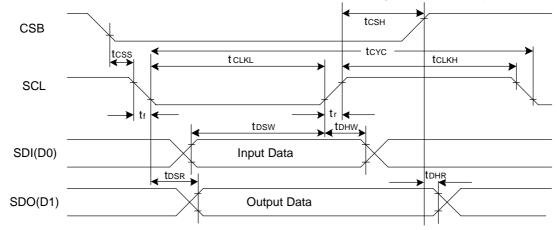

#### Serial Data Transfer

Setting the S/P pin to the "VDD" level and the C86 pin to the "VSS" level allows standard clock-synchronized serial data transfer, using the chip select line (CSB), serial transfer clock line (SCL), serial input data line (SDI), and serial output data line (SDO). For a serial interface, the S8/16/ID pin function uses an ID pin. If the chip is set up for serial interface, the D15-2 pins, which are not used, must be fixed at "VDD" or "VSS".

The NT7553E initiates serial data transfer by transferring the start byte at the falling edge of CSB input. It ends serial data transfer at the rising edge of CSB input.

The NT7553E is selected when the 6-bit chip address in the start byte transferred from the transmitting device matches the 6-bit device identification code assigned to the NT7553E. The NT7553E, when selected, receives the subsequent data string. The LSB of the identification code can be determined by the ID pin. The five upper bits must be "01110". Two different chip addresses must be assigned to a single NT7553E because the seventh bit of the start byte is used as a register select bit (A0): that is, when A0 = "0", data can be written to the index register or status can be read, and when A0 = "1", an instruction can be issued or data can be written to or read from RAM. Read or write is selected according to the eighth bit of the start byte (R/W bit). The data is received when the R/W bit is "0", and is transmitted when the R/W bit is "1". After receiving the start byte, the NT7553E receives or transmits the subsequent data byte-by-byte. The data is transferred with the MSB first. All NT7553E instructions are 16 bits. Two bytes are received with the MSB first (D15 to 0), and then the instructions are internally executed. After the start byte has been received, the first byte is fetched internally as the upper eight bits of the instruction and the second byte is fetched internally as the lower eight bits of the instruction. Five bytes of RAM read data after the start byte are invalid. The NT7553E starts to read correct RAM data from the sixth byte.

Table 4. Start Byte Format

| Start byte format Transfer start 0 1 1 0 ID A0 R/W | Transfer Bit | S              | 1 | 2 3   | (A)       | 5 | 6  | 7  | 8     |

|----------------------------------------------------|--------------|----------------|---|-------|-----------|---|----|----|-------|

| format format 0 1 1 0 ID AO K/W                    | Start byte   | Transfer start |   | Devic | e ID code |   |    | ۸٥ | DAM   |

|                                                    | format       | Transfer start | 0 | 1 0 1 |           | 0 | ID | ζ. | IX/VV |

Note: The S8/16/ID pin selects ID bit.

a) Timing of basic data-transfer through clock synchronized serial interface

Figure 3. Procedure for transfer through the clock synchronized serial interface (a)

b) Timing of consecutive data transfer through clock synchronized serial interface

Figure 4. Procedure for transfer through the clock synchronized serial interface (b)

Five bytes invalid dummy data are read after start byte. 6th data is valid from DDRAM.

Figure 5. Procedure for transfer through the clock synchronized serial interface (c)

One byte invalid dummy data is read after start byte. 2nd data is valid from DDRAM.

Figure 6. Procedure for transfer through the clock synchronized serial interface (d)

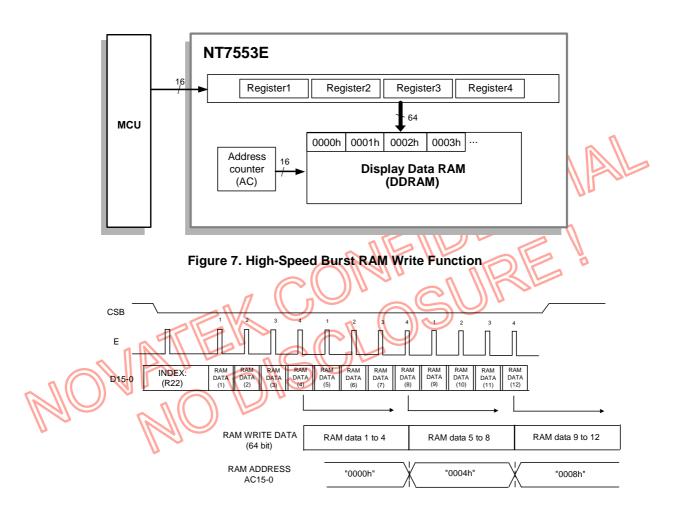

#### **High-Speed Burst RAM Write Function**

The NT7553E has a high-speed burst RAM-write function that can be used to write data to RAM in one-fourth the access time required for an equivalent standard RAM-write operation. This function is especially suitable for applications which require the high-speed rewriting of the display data, for example, display of gray animations, etc.

When the high-speed RAM-write mode (HWM) is selected, data for writing to RAM is stored once to the NT7553E internal register. When data is selected four times per word, all data is written to the on-chip RAM. While this is taking place, the next data can be written to an internal register so that high-speed and consecutive RAM writing can be executed for animated displays, etc.

Figure 8. High-Speed Burst RAM Write timing

Note the following when using high-speed RAM write mode.

- 1. The lower two bits of the address must be set in the following way in high-speed write mode. When D0 becomes 0, the lower two bits of the address must be set to "11". When D1 becomes 1, the lower two bits of the address must be set to "00".

- 2. When a high-speed RAM write is canceled, the next instruction must only be executed after the RAM write execution time has elapsed.

- 3. The logical and compare operation cannot be used.

2008/11/14 20 Ver 3.0

- 4. Data is written to RAM for each four words. When an address is set, the lower two bits in the address must be set to the following values.

- \*When I/D0=0, the lower two bits in the address must be set to "11" and be written to RAM. \*When I/D0=1, the lower two bits in the address must be set to "00" and be written to RAM.

- 5. Data is written to RAM for each four words. If less than four words of data are written to RAM, the last data will not be written to RAM.

- 6. When the index register and RAM data write ("22"h) have been selected, the data is always written first. RAM cannot be written to and read from at the same time. HWM must be set to "0" while RAM is being read.

- 7. High-speed and normal RAM write operations cannot be executed at the same time. The mode must be switched and the address must then be set.

- 8. When high-speed RAM write is used with a window address-range specified, dummy write operation may be required to suit the window address range-specification. Refer to the High-Speed RAM Write in the Window Address

Table 5. Comparisons between Normal and High-Speed RAM Write Operations

|                            | Normal RAM Write<br>(HWM=0) | High-Speed RAM Write<br>(HWM=1)                                                                  |

|----------------------------|-----------------------------|--------------------------------------------------------------------------------------------------|

| Logical operation function | Can be used                 | Can't be used                                                                                    |

| Compare operation function | Can be used                 | Can't be used                                                                                    |

| Write mask function        | Can be used                 | Can be used                                                                                      |

| RAM address set            | Can be specified by word    | ID0 bit=0: Set the lower two bits to 11 ID0 bit=1: Set the lower two bits to 00                  |

| RAM read                   | Can be read by word         | Cannot be used                                                                                   |

| RAM write                  | Can be written by word      | Dummy write operations may have to be inserted according to a window address range specification |

| Window address             | Can be set by word          | Can be set by four words                                                                         |

| MOAL                       |                             |                                                                                                  |

#### **High-Speed RAM Write in the Window Address**

When a window address range is specified, RAM data which is in an optional window area can be rewritten consecutively and quickly by inserting dummy write operations so that RAM access counts become 4N as shown in the tables below.

Dummy write operations may have to be inserted as the first or last operations for a row of data, depending on the horizontal window-address range specification bits (HSA1 to 0, HEA1 to 0). The number of dummy write operations of a row must be 4N.

Table 6. Number of Dummy Write Operations in High-Speed RAM Write (HSA Bits)

| HSA1 | HSA0 | Number of Dummy Write Operations to be<br>Inserted at the Start of a Row |

|------|------|--------------------------------------------------------------------------|

| 0    | 0    | 0                                                                        |

| 0    | 1    | 1                                                                        |

| 1    | 0    | 2                                                                        |

| 1    | 1    | 3                                                                        |

Table 7. Number of Dummy Write Operations in High-Speed RAM Write (HEA Bits)

| HEA1 | HEA0 | Number of Dummy Write Operations to be Inserted at the End of a Row |

|------|------|---------------------------------------------------------------------|

| 0    | 0    | 3                                                                   |

| 0    | 1    | 2                                                                   |

| 1    | 0    |                                                                     |

| 1    | 1    |                                                                     |

Each row of access must consist of 4 x N operations, including the dummy writes. Horizontal access count = first dummy write count + write data count + last dummy write count = 4 x N

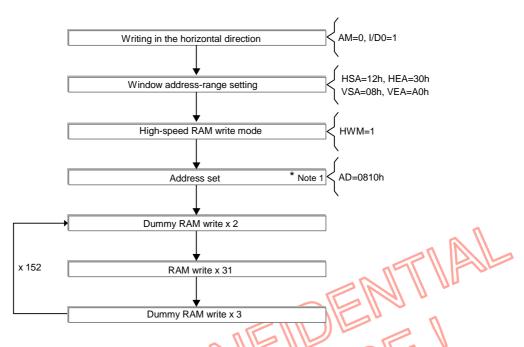

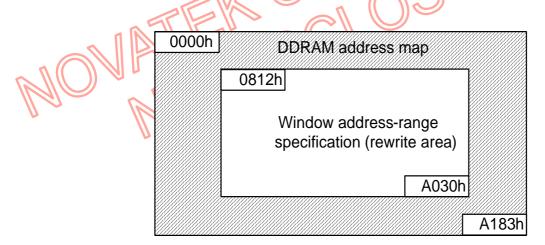

An example of high-speed RAM write with a window address-range specified is shown below. The window address-range can be rewritten consecutively and quickly by inserting two dummy writes at the start of a row and three dummy writes at the end of a row, as determined by using the window address-range specification bits (HSA1 to  $0 = 10^\circ$ , HEA1 to  $0 = 00^\circ$ ).

Figure 9. High-Speed Burst RAM with a window mask write

<sup>\*</sup>Note1The address set for the high-speed RAM write must be 00 or 11 according to the value of I/D0 bit. Only RAM in the specified window address-range will be overwritten.

Window address-range setting HSA=12h, HEA=30h VSA=08h, VEA=A0h

Figure 10. Example of the High-Speed RAM write with a window address-range specification

2008/11/14 23 Ver 3.0

#### **Window Address Function**

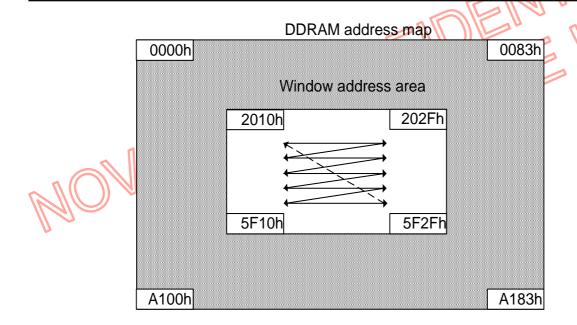

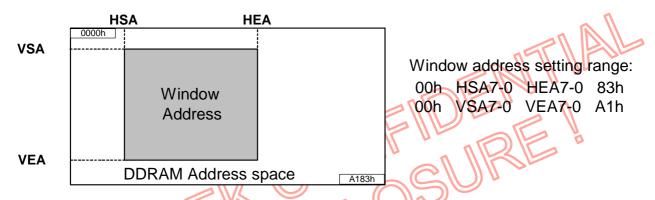

When data is written to the on-chip DDRAM, a window address-range that is specified by the horizontal address register (start: HSA[7:0], end: HEA[7:0]) or the vertical address register (start: VSA[7:0], end: VEA[7:0]) can be written consecutively.

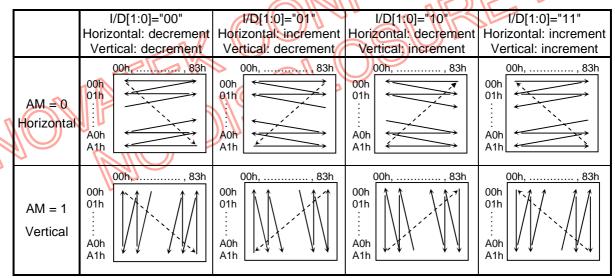

Data is written to addresses in the direction specified by the AM bit (increment/decrement). When image data, etc. is being written, data can be written consecutively without thinking a data wrap by doing this. The window must be specified to be within the DDRAM address area described below. Addresses must be set within the window address.

[Restriction on window address-range settings]

(Horizontal direction)  $00h \le HSA[7:0] \le HEA[7:0] \le 83h$ (Vertical direction)  $00h \le VSA[7:0] \le VEA[7:0] \le A1h$

[Restriction on address settings during the window address]

(RAM address) HSA[7:0] ≤ AD[7:0] ≤ HEA[7:0] VSA[7:0] ≤ AD[15:8] ≤ VEA[7:0]

Note: In high-speed RAM-write mode, the lower two bits of the address must be set as shown below according to the value of the ID0 bit.

ID0 = 0: The lower two bits of the address must be set to "11".

ID0 = 1: The lower two bits of the address must be set to "00".

I/D0=1 (increment)

AM=0 (horizontal writing)

Window address-range specification area

HSA5-0=10h, HSE5-0=2Fh

VSA7-0=20h, VEA7-0=5Fh

Figure 11. Example of Address Operation in the Window Address Specification

## **Display Data RAM (DDRAM)**

The display data RAM stores the segment data for the display. It has 162 x 396 x 5 bit structure for 32 gray scale levels.

## **DDRAM Address Map**

Table 8. Relationship between Display Position and DDRAM Address

|        |        | Horizontal<br>Address |        | 00h    |        |        | 01h    |        | (      | 02h    |        |        | 03h    |        |          |            | 80h      | l        |            | 81h    |          |        | 82h    |        |        | 83l    | า      |

|--------|--------|-----------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|----------|------------|----------|----------|------------|--------|----------|--------|--------|--------|--------|--------|--------|

|        |        | SGS=0                 | SEG1   | SEG2   | SEG3   | SEG4   | SEG5   | SEG6   | SEG7   | SEG8   | 693S   | SEG10  | SEG11  | SEG12  |          | SEG385     | 98E53S   | 28E93S   | 88E93S     | SEG389 | SEG390   | SEG391 | SEG392 | SEG393 | SEG394 | SEG395 | SEG396 |

|        |        | SGS=1                 | SEG396 | SEG395 | SEG394 | SEG393 | SEG392 | SEG391 | SEG390 | SEG389 | SEG387 | SEG386 | SEG385 | SEG384 |          | SEG12      | SEG11    | SEG10    | SEG9       | SEG8   | SEG7     | SEG6   | SEG5   | SEG4   | SEG3   | SEG2   | SEG1   |

| CMS=0  | CMS=1  | Vertical<br>Address   | D1     | 15 ~ I | 00     | D1     | 5 ~ C  | 00     | D1     | 5 ~ [  | 00     | D1     | 5 ~    | D0     |          | D          | 15 ~     | D0       | D1         | 5 ~ E  | 00       | D.     | 15 ~   | D0     | D      | 15 ~   | D0     |

| COM1   | COM162 | 00h                   | 0      | 0000   | h      | 0      | 001h   | ì      | 0      | 002l   | 1      | 0      | 003    | h      |          | (          | 080      | h        | 0          | 081h   | 1        | (      | 082    | h      | ID     | 0083   | 3h     |

| COM2   | COM161 | 01h                   | 0      | 100    | h      | 0      | 101ŀ   | ì      | 0      | 102ŀ   | 1      | 0      | 103    | h      |          | (          | )180     | h        | 0          | 181h   | 1        | (      | 182    | h \\   | Ir     | 0183   | 3h     |

| COM3   | COM160 | 02h                   | 0      | 200    | h      | 0:     | 201h   | 1      | 0:     | 202l   | 1      | 0      | 203    | h      |          | (          | )280     | h        | 0          | 281h   |          |        | 282    | h      |        | 0283   | 3h     |

| COM4   | COM159 | 03h                   | 0      | 300    | h      | 0:     | 301h   | 1      | 0:     | 302l   | 1      | 0      | 303    | h      |          | (          | 380      | Ā        | 0          | 381h   | 1        |        | 382    | h      |        | 0383   | 3h     |

| COM5   | COM158 | 04h                   | 0      | 400    | h      | 0      | 401h   | 1      | 0-     | 402ŀ   | 1      | 0      | 403    | h      |          | 17         | )480     | h        | 0          | 481h   | 10       | (      | )482   | h      |        | 0483   | 3h     |

| COM6   | COM157 | 05h                   | 0      | 500    | h      | 0      | 501h   | ì      | 0      | 502l   | 1      | 0      | 503    | h 🤇    |          |            | 580      | h        | O          | 581h   | ۱ 🍦      | C      | 582    | h 🚺    |        | 0583   | 3h     |

| COM7   | COM156 | 06h                   | 0      | 600    | h      | 0      | 601h   | ì      | 0      | 602l   | 1      | 0      | 603    | h      |          | (          | 0680     | h        | 0          | 681ŀ   | 9        | 0      | 682    | h      | 2      | 0683   | 3h     |

| COM8   | COM155 | 07h                   | 0      | 700    | h      | 0      | 701h   | 1      | 0      | 702l   | 1//    | 0      | 703    | h      | 21 11    | (          | 780      | h        | 70         | 781ŀ   | <u> </u> | //(    | 782    | h      |        | 0783   | 3h     |

|        | COM154 | 08h                   |        | 008    |        |        | 801h   | _      |        | 802l   | -      | )      | 803    |        |          | -//        | 0880     | - 11     | <b>— \</b> | 881h   | _        |        | 882    |        |        | 0883   |        |

| COM10  | COM153 | 09h                   | 0      | 900    | h      | 0      | 901r   | 1      | 0      | 902l   | IJ.    | 0      | 903    | h      |          | 1          | 980      | h        |            | 981h   | 1        | (      | 982    | h      |        | 0983   | 3h     |

| :      |        |                       | 5      | 77     | 1      |        |        |        |        | :      |        | ((     | 1      |        | الألف    | <b>)</b> ) | <u>ر</u> | <b>1</b> |            | ÷      |          |        | ÷      |        |        | ÷      |        |

| COM159 | COM4   | 9Eh                   | 9      | E00    | h      | 91     | E01h   | 1      | 9      | E02l   | ) (    | 9      | E03    | h      | <b>7</b> | ç          | 9E80     | )h       | 9          | E81h   | 1        | 9      | E82    | h      |        | 9E8    | 3h     |

| COM160 |        | 9Fh                   | 9      | F00    | h      | 9      | F01l   |        |        | F02l   |        | 9      | F03    | h      |          | 9          | )F80     | h        | 9          | F81h   | 1        | 9      | F82    | h      |        | 9F83   | 3h     |

| COM161 | COM2   | A0h                   | Α      | 000    | h      | A      | 001ŀ   | 1      | - * *  | 002    |        | Α      | .003   | h      |          | A          | 1080     | )h       | Α          | .081h  | 1        | P      | 082    | h      |        | A08    | 3h     |

| COM162 | COM1   | A1h                   | A      | 100    | h      | Α      | 101H   |        | Α      | 102    | า      | Α      | 103    | h      |          | P          | 180      | )h       | Α          | .181h  | 1        | P      | 182    | h      |        | A18:   | 3h     |

Table 9. Relationship between DDRAM data and Segment output pin

| DDRAM Data       | D15        | D14          | D13 | D12 | D11 | D10          | D9         | D8   | D7   | D6 | D5 | D4 D3 D2 D1 |     |       |       | D0 |

|------------------|------------|--------------|-----|-----|-----|--------------|------------|------|------|----|----|-------------|-----|-------|-------|----|

| Selected Palette | PK palette |              |     |     |     |              | PK         | pale | ette |    | 0  | PK palette  |     |       |       |    |

| Output Pin       | SEG (3n+1) |              |     |     |     |              | SEG (3n+2) |      |      |    |    |             | SEC | 3 (3r | 1+3)  |    |

| Output Pin       |            | SEG (396-3n) |     |     |     | SEG (395-3n) |            |      |      |    | 0  | SEG (394-3n |     |       | 4-3n) |    |

Note: 1. n=Lower 8 bits address (00h ~83h)

<sup>2.</sup> D5 is dummy bit must fixed this bit to "0".

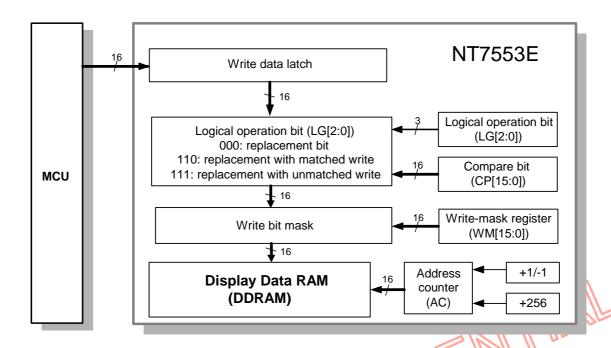

#### **Bit Operation**

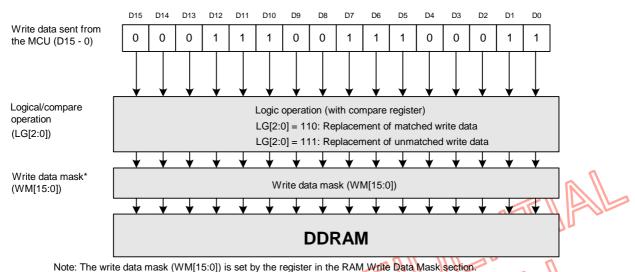

The NT7553E supports the following functions. A write data mask function that selects data into the display data RAM in bit units, and a logic operation function that performs logic operations or conditional determination on the display data set in the RAM and writes into the RAM. With the 16-bit bus interface, these functions can greatly reduce the processing load of the MPU graphics software for the display data in the RAM at high speed. For details, see the Graphics Operation Function section.

#### **Graphic Operation Function**

The NT7553E can greatly reduce the load of the microcomputer graphics software processing through the 16-bit bus architecture and internal graphics-bit operation function. This function supports the following:

- 1. A write data mask function that selectively rewrites some of the bits in the 16-bit write data.

- 2. A conditional write function that compares the write data and compares-bit data and writes the data sent from the microcomputer only when the conditions match. Even if the display size is large, the display data in the display data RAM (DDRAM) can be quickly rewritten. The graphics bit operation can be controlled by combining the entry mode register. The bit set value of the RAM-write-data mask register, and the write from the microcomputer.

**Table 10. Graphics Operation**

| Operation Mode | 1   | Bit Setting   | g       | Operation and Usage                                                |

|----------------|-----|---------------|---------|--------------------------------------------------------------------|

| Operation mode | I/D | AM            | LG[2:0] | Operation and usage                                                |

| Write mode 1   | 0/1 | 0             | 000     | Horizontal data replacement, horizontal-border drawing             |

| Write mode 2   | 0/1 | <b>//1</b> (( | 000     | Vertical data replacement, vertical-border drawing                 |

| Write mode 3   | 0/1 |               | 110,111 | Conditional horizontal data replacement, horizontal-border drawing |

| Write mode 4   | 0/1 | 17            | 110,111 | Conditional vertical data replacement, vertical-border drawing     |

Figure 12. Graphics Operation Flow

#### Write-data Mask Function

The NT7553E has a bit-wise write-data mask function that controls writing the 16-bit data from the microcomputer to the DDRAM. Bits that are "0" in the write-data mask register (WM [15:0]) cause the corresponding D bit to be written to the DDRAM. Bits that are "1" prevent writing to the corresponding DDRAM bit to the DDRAM; the data in the DDRAM is retained. This function can be used when only one dot data is rewritten or the particular display gray level is selectively rewritten.

|                | - // | 12  | iab | ie II. | AAIIIG | -uata | iviask | unc | 1011 0 | perau | OII |     |     |     |     |     |

|----------------|------|-----|-----|--------|--------|-------|--------|-----|--------|-------|-----|-----|-----|-----|-----|-----|

| Interface data | D15  | D14 | D13 | D12    | D11    | D10   | D9     | D8  | D7     | D6    | D5  | D4  | D3  | D2  | D1  | D0  |

| bus            | P04  | P03 | P02 | P01    | P00    | P14   | P13    | P12 | P11    | P10   | 0   | P24 | P23 | P22 | P21 | P20 |

| Write mask     | D15  | D14 | D13 | D12    | D11    | D10   | D9     | D8  | D7     | D6    | D5  | D4  | D3  | D2  | D1  | D0  |

| register       | 1    | 1   | 1   | 1      | 1      | 0     | 0      | 0   | 0      | 0     | 0   | 1   | 1   | 0   | 0   | 0   |

| DDRAM data     | D15  | D14 | D13 | D12    | D11    | D10   | D9     | D8  | D7     | D6    | D5  | D4  | D3  | D2  | D1  | D0  |

| DDINAMI data   | *    | *   | *   | *      | *      | P14   | P13    | P12 | P11    | P10   | 0   | *   | *   | P22 | P21 | P20 |

Table 11. Write-data Mask Function Operation

<sup>\*</sup> **D5** is dummy bit must fixed this bit to "0".

#### **Graphics Operation Processing**

1. Write mode 1: AM = 0, LG [2:0] = "000"

This mode is used when the data is horizontally written at high speed. It can also be used to initialize the graphics RAM (DDRAM) or to draw borders. The write-data mask function (WM [15:0]) is also enabled in these operations. After writing, the address counter (AC) automatically increments by 1 (I/D = 1) or decrements by 1 (I/D = 0), and automatically jumps to the counter edge one-raster below after it has reached the left or right edge of the DDRAM.

Operation Examples:

- 1) I/D =1, AM=0, LG[2:0]=000

- 2) WM[15:0]=07FFH

3) AC=0000H **WM15** WM0 0000011111111111111 Write data mask: D15 D0 100110001010100011 Write data (1): Write data (2): 1100001111000100 Write data (3): 0001H 0000H |0|0|0|1|0|\* Write data (1) Write data (2) Write data (3) **DDRAM**

2008/11/14 28 Ver 3.0

Figure 13. Writing Operation of Write Mode 1

2. Write mode 2: AM = 1, LG [2:0] = "000"

This mode is used when the data is vertically written at high speed. It can also be used to initialize the DDRAM, develop the font pattern in the vertical direction, or draw borders. The write-data mask function (WM [15:0]) is also enabled in these operations. After writing, the address counter (AC) automatically increments by 256, and automatically jumps to the upper-right edge (I/D = 1) or upper left edge (I/D = 0) following the I/D bit after it has reached the lower edge of the DDRAM.

#### Operation Examples:

- 1) I/D =1, AM=0, LG[2:0]=000

- 2) WM[15:0]=07FFH

- 3) AC=0000H

| 3) A | S=0000H          |                                  |                      |      |

|------|------------------|----------------------------------|----------------------|------|

|      | Write data mask: | WM15<br>00000011111111111<br>D15 | WM0<br>1 1 1 1<br>D0 |      |

|      | Write data (1):  | 100110001010100                  | 0111                 |      |

|      | Write data (2):  | 1 1 0 0 0 0 1 1 1 0 0 0 1 0      | polo                 | 1 AL |

|      | Write data (3):  | 00010111110101                   |                      |      |

| 0000 | H 100111***      | * * * * * *  Write data (        | 1)                   |      |

| 0100 | H 110000***      | * * * * * *  Write data (        | 2)                   |      |

| 0200 | H 00010***       | * * * * * * * * Write data (     | 3)                   |      |

|      |                  |                                  |                      |      |

Figure 14. Operation of Write Mode 2

**DDRAM**

## 3. Write mode 3: AM = 0, LG [2:0] = 110/111

This mode is used when the data is horizontally written by comparing the write data and the set value of the compare register (CP [7:0]). When the result of the comparison in a byte unit satisfies the condition write-data mask function (WM [15:0]) is also enabled. After writing, the address counter (AC) automatically increments by 1 (I/D = 1) or decrements by 1 (I/D = 0), and automatically jumps to the counter edge one-raster-raw below after it has reached the left or right edge of the DDRAM.

Operation Examples: 1) I/D =1, AM=0, LG[2:0]=110 (Matched Write) 2) CP[15:0]=2860H 3) WM[15:0]=0000H 3) AC=0000H

WM15 W<sub>M</sub>0 Write data mask: CP0

0010101000011100000 Compare register:

(Matched) D15 D0 Write data (1): 0010100001100000

Compare Operation (Unmatched) Replacement Write data (2):

Conditional

0000H

0010100001100000

Matched replacement of Write data (1)

Write data (2) is not changed

**DDRAM**

Figure 15. Operation of Write Mode 3

# 4. Write mode 4: AM = 1, LG [2:0] = 110/111

Operation Examples:

This mode is used when a vertical comparison is performed between the write data and the set value of the compare register (CP [15:0]) to write the data. When the result by the comparison in a byte unit satisfies the condition, the write data sent from the microcomputer is written to the DDRAM. In this operation, write data mask function (WM [15:0]) is also enabled. After writing, the address counter (AC) automatically increments by 256, and automatically jumps to the upper-right edge (I/D = 1) or upper-left edge (I/D = 0) following the I/D bit after it has reached the lower edge of the DDRAM.

#### 1) I/D =1, AM=1, LG[2:0]=111 (Unmatched Write) 2) CP[15:0]=2860H 3) WM[15:0]=0000H 3) AC=0000H WMO WM15 Write data mask: CP15 CP0 0010100001100000 Compare register: (Unmatched) D15 D0 011101010010010011 Write data (1): (R)- **→**|0|1|1|1|0|1|0|1|0|1|1 Conditional Compare (Matched) Operation Replacement Write data (2): 0010100001100000 (R) \* |\*|\* $\langle \mathcal{O} \rangle$ 0000H 0001H 0000H Unmatched replacement of Write data (1) Write data (2) is not changed 0100H **DDRAM** AF00H

Figure 16. Writing Operation of Write Mode 4

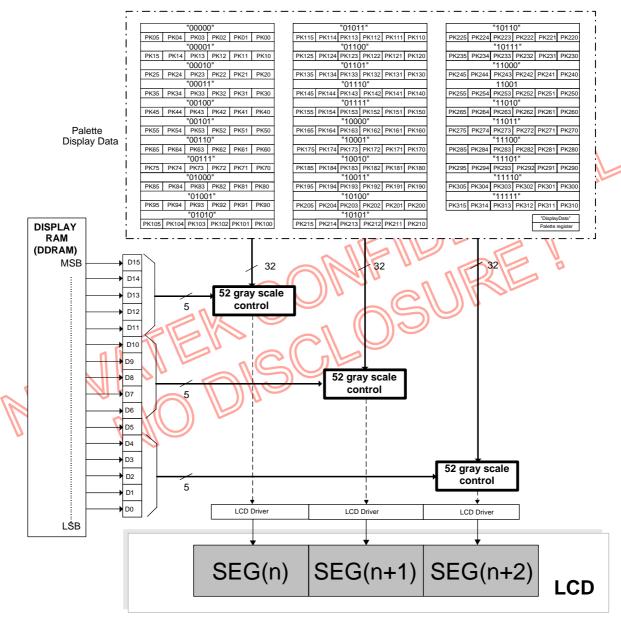

#### **Grayscale Palette**

The NT7553E incorporates a grayscale palette to simultaneously display 32-grayscale of the 52-grayscale possible levels. The grayscales consist of 32 6-bit palettes. The 52-stage grayscale levels can be selected from the 6-bit palette data.

For the display data, the four-bit data in the DDRAM written from the microcomputer is used.

In this palette, a pulse-width control system (PWM) is used to eliminate flickers in the LCD display. The time over which the LCD is switched on is adjusted according to the level and grayscales are displayed so that flicker is reduced and grayscales are clearly displayed.

Figure 17. Grayscale Palette Control

## **Grayscale Palette Table**

The grayscale register that is set for each palette register (PK) can be set to any level. 52-grayscale lighting levels can be set according to palette values ("000000" to "110100").

**Table 12. Grayscale Control Level**

|     |                                        | Palette Regis | ter Value (PK) |       |       | Value | Grayscale<br>Control Level |

|-----|----------------------------------------|---------------|----------------|-------|-------|-------|----------------------------|

| 0   | 0                                      | 0             | 0              | 0     | 0     | 00h   | All off level              |

| 0   | 0                                      | 0             | 0              | 0     | 1     | 01h   | 1/52 level                 |

| 0   | 0                                      | 0             | 0              | 1     | 0     | 02h   | 2/52 level                 |

| 0   | 0                                      | 0             | 0              | 1     | 1     | 03h   | 3/52 level                 |

| 0   | 0                                      | 0             | 1              | 0     | 0     | 04h   | 4/52 level                 |

| 0   | 0                                      | 0             | 1              | 0     | 1     | 05h   | 5/52 level                 |

| 0   | 0                                      | 0             | 1              | 1     | 0     | 06h   | 6/52 level                 |

| 0   | 0                                      | 0             | 1              | 1     | 1     | 07h   | 7/52 level                 |

| 0   | 0                                      | 1             | 0              | 0     | 0     | 08h   | 8/52 level                 |

| 0   | 0                                      | 1             | 0              | 0     | 1     | 09h   | 9/52 level                 |

| 0   | 0                                      | 1             | 0              | 1     | 0     | 0Ah   | 10/52 level                |

| 0   | 0                                      | 1             | 0              | 1     | 1     | 0Bh   | 11/52 level                |

| 0   | 0                                      | 1             | 1              | 0     | 0     | 0Ch   | 12/52 level                |

| 0   | 0                                      | 1             | 1              | 0     | 1     | 0Dh   | 13/52 level                |

| 0   | 0                                      | 1             | 1              | 1     | 0     | 0Eh   | 14/52 level                |

| 0   | 0                                      | 1             | 1              | 1     | 1     | 0Fh   | 15/52 level                |

| 0   | 1                                      | 0             | 0              | 0     | 0     | 10h   | 16/52 level                |

| 0   | 1                                      | 0             | 0              | 0     |       | 11h   | 17/52 level                |

| 0   | 1                                      | 0             | 0              | 1     | 0     | 12h   | 18/52 level                |

| 0   | 1                                      | 0             | 0              |       |       | 13h   | 19/52 level                |

| 0   | 1                                      | 0             | 1              |       | 0 n [ | 14h   | 20/52 level                |

| 0   | 1                                      | 0             |                | 0     |       | 15h   | 21/52 level                |

| 0   | 1                                      | 0 /           |                | 1     | (0)   | 16h   | 22/52 level                |

| 0   | 1                                      | 0 1/1         |                | 10    |       | 17h   | 23/52 level                |

| 0   | 1                                      | 2177          | 0              | ( ( ) | 0     | 18h   | 24/52 level                |

| 0   | 1,5                                    | 171           | 0              | 0     | 1     | 19h   | 25/52 level                |

| 0   | 111                                    | 11 14         | 0              | II P  | 0     | 1Ah   | 26/52 level                |

| 0   |                                        | V 1           |                | 1     | 1     | 1Bh   | 27/52 level                |

| 0   | \ \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | 1 \           |                | 0     | 0     | 1Ch   | 28/52 level                |

| N   | ) 1                                    |               | <i>)</i>       | 0     | 1     | 1Dh   | 29/52 level                |

| 0   | 1, \                                   |               | 1              | 1     | 0     | 1Eh   | 30/52 level                |

| 1 1 | : 16/                                  |               | :              | :     | :     | :     | :                          |

| 1   | 0                                      | 1             | 1              | 1     | 0     | 2Eh   | 46/52 level                |

| 1   | 0                                      | 1             | 1              | 1     | 1     | 2Fh   | 47/52 level                |

| 1   | 1                                      | 0             | 0              | 0     | 0     | 30h   | 48/52 level                |

| 1   | 1                                      | 0             | 0              | 0     | 1     | 31h   | 49/52 level                |

| 1   | 1                                      | 0             | 0              | 1     | 0     | 32h   | 50/52 level                |

| 1   | 1                                      | 0             | 0              | 1     | 1     | 33h   | 51/52 level                |

| 1   | 1                                      | 0             | 1              | 0     | 0     | 34h   | All on level               |

## Display data and Grayscale level

Table 13. Display data and output level

| _           |              | •            | _          |

|-------------|--------------|--------------|------------|

|             | Display data | Output level |            |

|             | 00000        | PK0          |            |

|             | 00001        | PK1          |            |

|             | 00010        | PK2          |            |

|             | 00011        | PK3          |            |

|             | 00100        | PK4          |            |

|             | 00101        | PK5          |            |

|             | 00110        | PK6          |            |

|             | 00111        | PK7          |            |

|             | 01000        | PK8          |            |

|             | 01001        | PK9          |            |

|             | 01010        | PK10         |            |

|             | 01011        | PK11         |            |

|             | 01100        | PK12         |            |

|             | 01101        | PK13         |            |

|             | 01110        | PK14         |            |

|             | 01111        | PK15         |            |

|             | 10000        | PK16         |            |

|             | 10001        | PK17         |            |

|             | 10010        | PK18         |            |

|             | 10011        | PK19         |            |

|             | 10100        | PK20         |            |

|             | 10101        | PK21         |            |

|             | 10110        | PK22         |            |

|             | 10111        | PK23         |            |

|             | 11000        | PK24         |            |

|             | 11001        | PK25         |            |

|             | 11010        | PK26         | <i>y</i> ~ |

|             | 11011        | PK27         |            |

|             | 11100        | PK28         |            |

| n (A) \\ \\ | 11101        | PK29         |            |

|             | 11110        | PK30         |            |

|             | 11111        | PK31         | ı          |

|             |              |              |            |

|             |              |              |            |

|             | <i>y</i>     |              |            |

|             |              |              |            |

| U           |              |              |            |

|             |              |              |            |

#### **Address Counter (AC)**

The address counter (AC) assigns an address to the data display RAM. When an address set instruction is written into the IR, the address information is sent from the IR to the AC. After writing into the RAM, the AC is automatically incremented by 1 (or decremented by 1). After reading from the RAM, the AC is not updated.

### **PWM Control Circuit**

The grayscale palette generates a PWM signal for segment pins, which corresponds to the specified grayscale level. Any 32-grayscale out of the 52-grayscale possible levels can be displayed simultaneously.

## **Display Data Latch**

The display data latch circuit is a latch that temporarily stores the display data that is output to the liquid crystal driver circuit from the display data RAM.

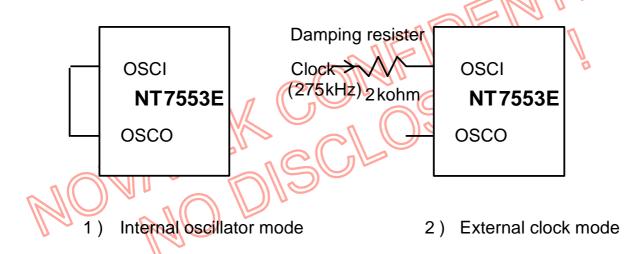

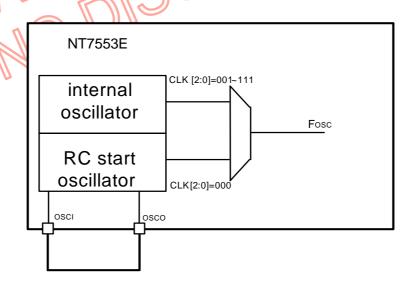

#### **Oscillation Circuit**

The NT7553E can set internal oscillate mode and external clock mode, when use internal oscillate mode, OSCI must connect to OSCO to set R-C start oscillation and select oscillation frequency by R0B command.

Figure 18. Oscillation Circuits

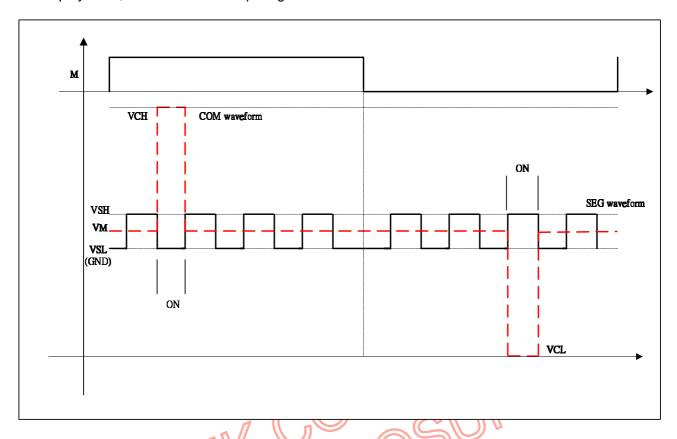

The relationship between the SEG and COM output levels is as shown in the following figure. While the display is off, SEG and COM outputs go to VSS level.

Figure 19. Relationship with SEG/COM output level

### Liquid Crystal Display Driver Circuit

The liquid crystal display driver circuit consists of 162 common signal drivers (COM1 to COM162) and 396 segment signal drivers (SEG1 to SEG396). Display pattern data from display data RAM is latched to the 396-bit latch circuit. The latched data then enables the segment signal drivers to generate drive waveform outputs. The common driver outputs one of the VCH, VM or VCL voltage level. The SGS bit can change the shift direction of 396-bit data for the segment. The CMS bit can also change the shift direction for the common by selecting an appropriate direction for the device-mounting configuration. When display is off, or during the standby or sleep mode, all the above common and segment signal drivers output the VSS level, halting the display.

## LCD drive power supply circuit

LCD drive power supply circuit generates VCH, VSH, VM and VCL voltage level to drive the LCD panel.

## **Display Timing Generator Circuit**

The display timing generator circuit generates the timing signal to the display data latch circuit using the system clock. The display data is latched into the display data latch circuit synchronized with the display clock, and is output to the data driver output terminal. Reading to the display data liquid crystal driver circuits is completely independent of access to the display data RAM by the MPU.

Moreover, the display timing generator circuit generates a drive waveform using an alternating current drive method that is determined by N -Line Inversion command for the liquid crystal drive circuit.

# **Common Output Control Circuit**

This circuit controls the relationship between the number of common output and specified duty ratio. Common output mode select instruction specifies the scanning direction of the common output pads.

## Sleep Mode

Setting the sleep mode bit (SLP) to "1" puts the NT7553E in the sleep mode, where the device stops all internal display operations, thus reducing current consumption. Specifically, LCD operation is completely halted. Here, all the SEG (SEG1 to SEG396) and COM (COM1 to COM162) pins output the "VSS" level, resulting in no display. If the AP [1:0] bits in the power control register are set to "00" in the sleep mode, the LCD drive power supply can be turned off, reducing the total current consumption of the LCD module.

Table 14. Comparisons of Sleep Mode and Standby Mode

| Function            | Sleep Mode (SLP = 1) | Standby Mode (STB = 1) |

|---------------------|----------------------|------------------------|

| LCD control         | Turned off           | Turned off             |

| Oscillation circuit | Operates normally    | Operation stopped      |

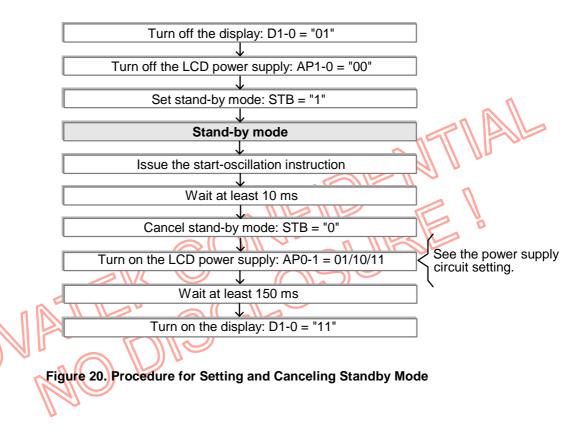

#### **Standby Mode**

Setting the standby mode bit (STB) to "1" puts the NT7553E in the standby mode, where the device stops completely, halting all internal operations including the Oscillation circuit, thus further reducing current consumption compared to that in the sleep mode. Specifically, all the SEG (SEG1 to SEG396) and COM (COM1 to COM162) pins for the time-sharing drive output the VSS level, resulting in no display. If the AP [1:0] bits are set to "00" in the standby mode, the LCD drive power supply can bet turned off. During the standby mode, no instructions can be accepted other than the start-oscillation instruction. To cancel the standby mode, issue the start-oscillation instruction to stabilize oscillation before setting the STB bit to "0".

## **Setting Flows for Power Supply and Display Instruction**

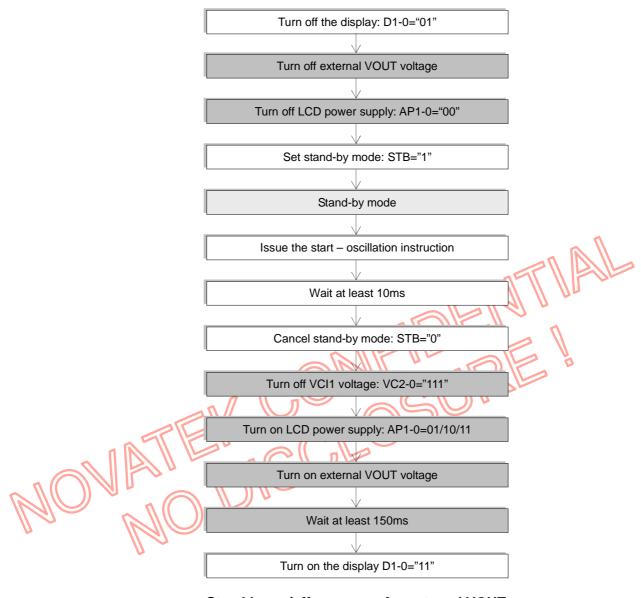

## Power-on / off Sequence

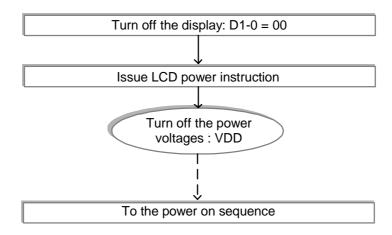

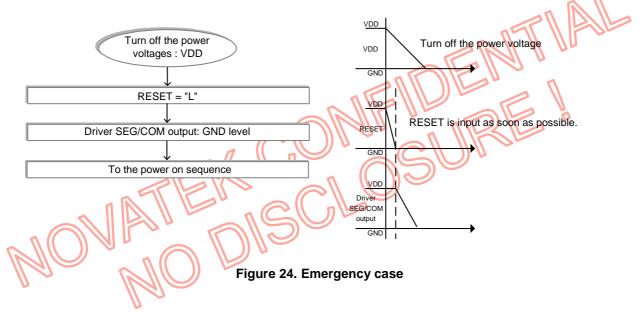

To prevent pulse lighting of LCD screens at power-on/off, the power-on/off sequence is activated as shown below. However, since the sequence depends on LCD materials to be used, confirm the conditions by using your own system.

Figure 22. Power Off sequence

## **Power-off Sequence**

Figure 23. Normal case

Note: When hardware reset is input during the power-off period, the D1-0 bits are cleared to "00" and SEG/COM output is forcibly lowered to the VSS levels.

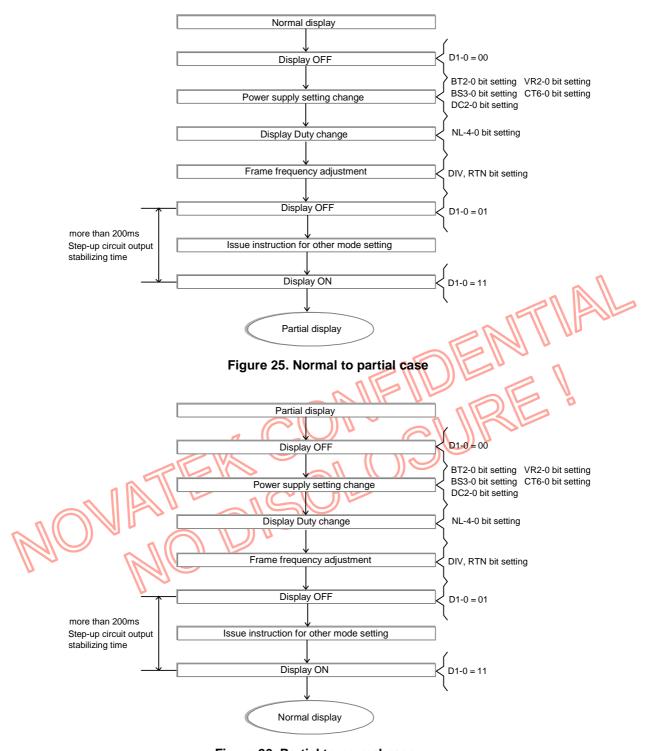

#### **Partial Sequence Setting Flow**

Figure 26. Partial to normal case

## **Frame-Frequency Adjustment Function**

The NT7553E has an on-chip frame-frequency adjustment function. The frame frequency can be adjusted by the instruction setting (DIV, RTN) during the LCD drive, as the oscillation frequency is always the same. When the display duty is changed, the frame frequency can be adjusted to be the same.

If the oscillation frequency is set to high, an animation or a static image can be displayed in suitable ways by changing the frame frequency. When a static image is displayed, the frame frequency can be set low and the low-power consumption mode can be entered. When high-speed screen switching, for an animated display, etc. is required, the frame frequency can be set high.

## Relationship between LCD Drive Duty and Frame Frequency

The relationship between the LCD driver duty and the frame frequency is calculated by the following expression. The frame frequency can be adjusted in the retrace-line period bit (RTN) and in the operation clock division bit (DIV) by the instructions.

(Formula for the frame frequency)

Frame frequency = fosc / (Clock cycles per raster-row  $\times$  division ratio  $\times$  duty cycle) [Hz]

fosc: Oscillation frequency Duty: drive duty (NL bit)

Clock cycles per raster-row: (RTN + 26) clock cycles

Division ratio: DIV bit

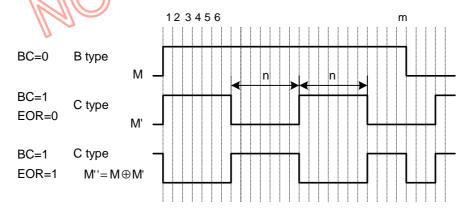

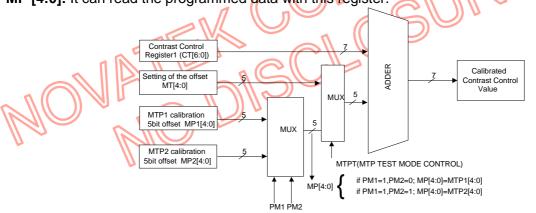

#### n-raster-row Reversed AC Drive