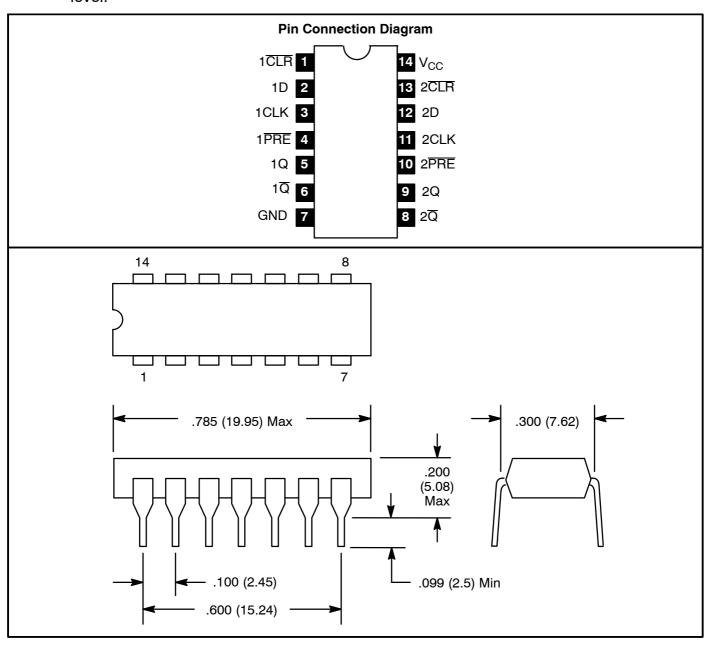

# NTE7474 Integrated Circuit TTL, Dual D-Type Positive-Edge-Triggered Flip-Flop W/Preset and Clear

### **Description:**

The NTE7474 contains two independent D-type positive-edge-triggered flip-flops in a 14-Lead DIP type package characterized for operating from 0° to +70°C. A low level at the preset or clear inputs sets or resets the outputs regardless of the levels of the other inputs. When preset and clear are inactive (high), data at the D input meeting the setup time requirements are transferred to the outputs on the positive-going edge of the clock pulse. Clock triggering occurs at a voltage level and is not directly related to the rise time of the clock pulse. Following the hold time interval, data at the D input may be changed without affecting the levels at the outputs.

| <b>Absolute Maximum Ratings:</b> $(T_A = 0^\circ \text{ to } +70^\circ \text{C unless otherwise specified})$ |                |

|--------------------------------------------------------------------------------------------------------------|----------------|

| Supply Voltage (Note 1), V <sub>CC</sub>                                                                     | 7V             |

| Input Voltage, V <sub>IN</sub>                                                                               | 5.5V           |

| Operating Ambient Temperature Range, T <sub>A</sub>                                                          | 0° to +70°C    |

| Storage Temperature Range, T <sub>stg</sub>                                                                  | −65° to +150°C |

| Note 1. Voltage values are with respect to network GND terminal.                                             |                |

## **Recommended Operating Conditions:**

| Parameter                        | Symbol          | Test Conditions | Min  | Тур | Max  | Unit |

|----------------------------------|-----------------|-----------------|------|-----|------|------|

| Supply Voltage                   | V <sub>CC</sub> |                 | 4.75 | 5.0 | 5.25 | V    |

| High-Level Input Voltage         | V <sub>IH</sub> |                 | 2    | _   | _    | V    |

| Low-Level Input Voltage          | V <sub>IL</sub> |                 | -    | -   | 0.8  | V    |

| High-Level Output Current        | I <sub>OH</sub> |                 | _    | _   | -0.4 | mA   |

| Low-Level Output Current         | l <sub>OL</sub> |                 | _    | _   | 16   | mA   |

| Pulse Duration<br>CLK High       | t <sub>w</sub>  |                 | 30   | _   | _    | ns   |

| CLK Low                          | 1               |                 | 37   | -   | -    | ns   |

| PRE or CLR Low                   | ]               |                 | 30   | _   | _    | ns   |

| Input Setup Time Before CLK ↑    | t <sub>su</sub> |                 | 20   | -   | _    | ns   |

| Input Hold Time-Data After CLK ↑ | t <sub>h</sub>  |                 | 5    | _   | _    | ns   |

| Operating Ambient Temperature    | T <sub>A</sub>  |                 | 0    | _   | 70   | °C   |

# **<u>Electrical Characteristics:</u>** $(T_A = 0^{\circ} \text{ to } +70^{\circ}\text{C}, \text{ Note 2 unless otherwise specified})$

| Parameter                    | Symbol          | Test Conditions                                                       | Min | Тур | Max  | Unit |

|------------------------------|-----------------|-----------------------------------------------------------------------|-----|-----|------|------|

| Input Clamp Diode Voltage    | V <sub>IK</sub> | $V_{CC}$ = Min, $I_{l1}$ = -12mA                                      | _   | _   | -1.5 | V    |

| Output High Voltage          | V <sub>OH</sub> | $V_{CC} = Min$ , $V_{IH} = 2V$ , $V_{IL} = 800mV$ , $I_{OH} = -0.4mA$ | 2.4 | 3.4 | _    | V    |

| Output Low Voltage           | V <sub>OL</sub> | $V_{CC}$ = Min, $V_{IH}$ = 2V, $V_{IL}$ = 800mV, $I_{OL}$ = 16mA      | _   | 0.2 | 0.4  | V    |

| Input Current                | lı              | $V_{CC} = Max, V_I = 5.5V$                                            | _   | _   | 1    | mA   |

| Input High Current<br>D      | I <sub>IH</sub> | $V_{CC} = Max, V_I = 2.4V$                                            | _   | _   | 40   | mA   |

| CLR                          | 1               |                                                                       | _   | _   | 120  | mA   |

| All Others                   |                 |                                                                       | _   | _   | 80   | mA   |

| Input Low Current<br>D       | I <sub>IL</sub> | $V_{CC} = Max, V_I = 0.4V$                                            | _   | _   | -1.6 | mA   |

| PRE (Note 3)                 |                 |                                                                       | _   | _   | -1.6 | mA   |

| CLR (Note 3)                 | 1               |                                                                       | _   | _   | -3.2 | mA   |

| CLK                          | 7               |                                                                       | _   | -   | -3.2 | mA   |

| Output Short Circuit Current | Ios             | V <sub>CC</sub> = Max, Note 4                                         | -18 | -   | -57  | mA   |

| Power Supply Current         | I <sub>CC</sub> | V <sub>CC</sub> = Max, Note 5                                         | _   | 8.5 | 15   | mA   |

- Note 2. All typical values are at  $V_{CC}$  = 5V,  $T_A$  = +25°C. For conditions shown as Min and Max, use the appropriate value specified under recommended operating conditions.

- Note 3. Clear is tested with preset high and preset is tested with clear high.

- Note 4. Not more than one output should be shorted at a time.

- Note 5. With all outputs open,  $I_{CC}$  is measured with the Q and  $\overline{Q}$  outputs high in turn. At the time of measurement, the clock input is grounded.

# <u>Switching Characteristics:</u> $(V_{CC} = 5V, T_A = +25^{\circ}C \text{ unless otherwise specified})$

| Parameter                             | Symbol           | From<br>(Input) | To<br>(Output) | Test<br>Conditions               | Min | Тур | Max | Unit |

|---------------------------------------|------------------|-----------------|----------------|----------------------------------|-----|-----|-----|------|

| Maximum Clock Frequency               | f <sub>max</sub> |                 |                |                                  | 15  | 25  | _   | MHz  |

| Propagation Delay Time<br>Low-to-High | t <sub>PLH</sub> | PRE or          | Q or Q         | D 4000                           | ı   | _   | 25  | ns   |

| High-to-Low                           | t <sub>PHL</sub> | CLR             |                | $R_L = 400\Omega$ , $C_I = 15pF$ | -   | -   | 40  | ns   |

| Propagation Delay Time<br>Low-to-High | t <sub>PLH</sub> | CLK             | Q or Q         |                                  | _   | 14  | 25  | ns   |

| High-to-Low                           | t <sub>PHL</sub> |                 |                |                                  | _   | 20  | 40  | ns   |

### **Function Table:**

|     | Inp | Outputs  |   |            |                  |

|-----|-----|----------|---|------------|------------------|

| PRE | CLR | CLK      | D | Q          | Q                |

| L   | Н   | Х        | Х | Н          | L                |

| Н   | L   | Х        | Х | L          | Н                |

| L   | L   | Х        | Х | H (Note 6) | H (Note 6)       |

| Н   | Н   | <b>↑</b> | Н | Н          | L                |

| Н   | Н   | <b>↑</b> | L | L          | Н                |

| Н   | Н   | L        | Х | $Q_0$      | $\overline{Q}_0$ |

Note 6. The output levels in this configuration are not guaranteed to meet the minimum levels in  $V_{OH}$  if the lows at preset and clear are near  $V_{IL}$  maximum. Furthermore, this configuration is nonstable; that is, it will not presist when either preset or clear returns to its inactive (high) level.