# NTE74LS221 Integrated Circuit TTL – Dual Monostable Multivibrator

#### **Description:**

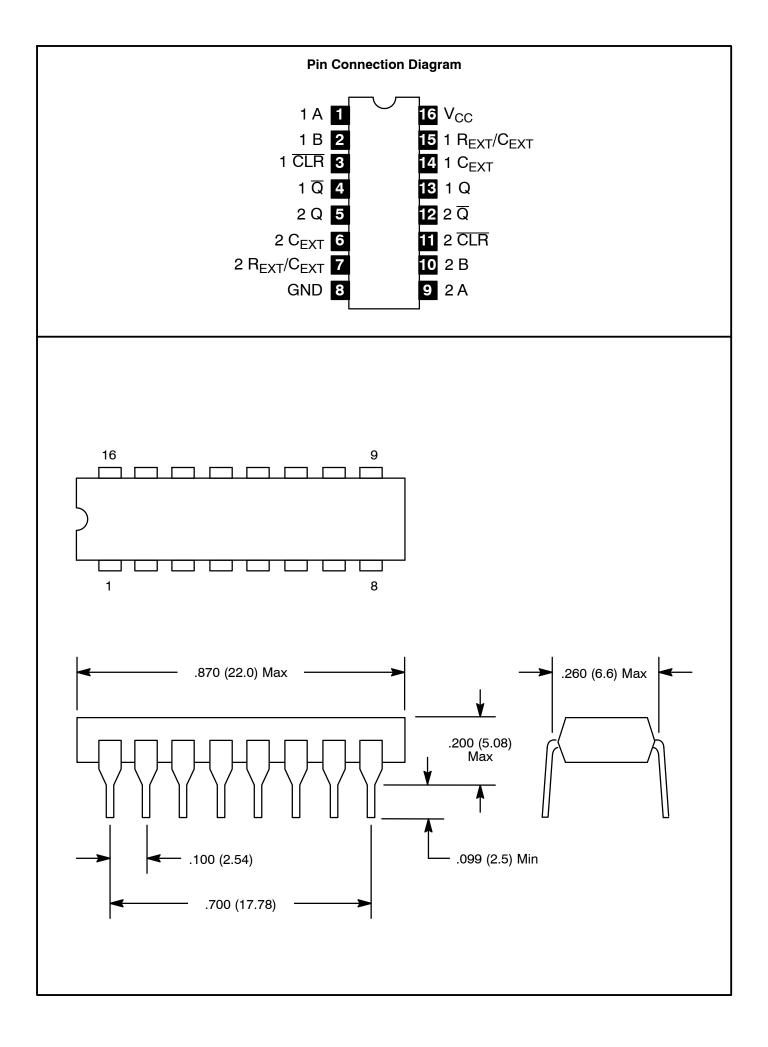

The NTE74LS221 is a monolithic dual multivibrator in a 16–Lead plastic DIP type package with performance characteristics virtually identical to those of the NTE74121. Each multivibrator features a negative-transition-triggered input and a positive-transition-triggered input either of which can be used as an inhibit input.

Pulse triggering occurs at a particular voltage level and is not directly related to the transition time of the input pulse. Schmitt-trigger input circuitry (TTL hysteresis) for B input allows jitter-free triggering from inputs with transition rates as slow as 1 volt/second, providing the circuit with excellent noise immunity of typically 1.2 volts. A high immunity to  $V_{CC}$  noise of typically 1.5V is also provided by internal latching circuitry.

Once fired, the outputs are independent o further transitions of the A an B inputs and are a function of the timing components, or the output pulses can be terminated by the overriding clear. Input pulses may be of any duration relative to the output pulse. Output pulse length may be varied from 35ns to the maximum pulse length of 70 seconds by choosing appropriate timing components. With  $R_{ext} = 2k\Omega$  and  $C_{ext} = 0$ , and output pulse of typically 30ns is achieved which may be used as a DC triggered reset signal. Output rise and fall times are TTL compatible and independent of pulse length.

Pulse width stability is achieved through internal compensation and is virtually independent of  $V_{CC}$  and temperature. In most applications, pulse stability will only be limited by the accuracy of external timing components.

Jitter–free operation is maintained over the full temperature and V<sub>CC</sub> ranges for more than six decades of timing capacitance (10pF to 10µF) and more than one decade of timing resistance (2k $\Omega$  to 100k $\Omega$ ).Throughout these ranges, pulse width is defined by the relationship: t<sub>w</sub>(out) = C<sub>ext</sub>R<sub>ext</sub> In2  $\approx$  0.7 C<sub>ext</sub>R<sub>ext</sub>. In circuits where the pulse cutoff is not critical, timing capacitance up to 1000µF and timing resistance as low as 1.4k $\Omega$  may be used. Also, the range of jitter–free output pulse widths is extended if V<sub>CC</sub> is held to 5V and free–air temperature is +25°C. Duty cycles as high as 90% are achieved when using maximum recommended R<sub>T</sub>. Higher duty cycles are available if a certain amount of pulse–width jitter is allowed.

#### Features:

• Overriding Clear Terminates Output Pulse

### **Recommended Operating Conditions:**

| Parameter                                      |                     |                       | Min  | Тур | Max  | Unit |

|------------------------------------------------|---------------------|-----------------------|------|-----|------|------|

| Supply Voltage                                 |                     |                       | 4.75 | 5.0 | 5.25 | V    |

| High-Level Output Current                      |                     |                       | -    | _   | -400 | μA   |

| Low-Level Output Current                       |                     |                       | -    | -   | 8    | mA   |

| Rate of Rise or Fall of Input Pulse Schmitt, B |                     | dv/dt                 | 1    | -   | -    | V/s  |

|                                                | Logic Input, A      |                       | 1    | _   | -    | V/µs |

| Input Pulse Width                              | A or B              | t <sub>w(in)</sub>    | 50   | _   | -    | ns   |

|                                                | Clear               | t <sub>w(clear)</sub> | 40   | _   | -    | ns   |

| Clear Inactive-State Setup Time                |                     |                       | 15   | _   | -    | ns   |

| External Timing Resistance                     |                     |                       | 1.4  | -   | 100  | kΩ   |

| External Timing Capacitance                    |                     |                       | 0    | _   | 1000 | μF   |

| Output Duty Cycle                              | $R_T = 2k\Omega$    |                       | -    | -   | 50   | %    |

|                                                | $R_T = MAX R_{ext}$ | 1                     | -    | _   | 90   | %    |

| Operating Temperature Range                    |                     |                       | 0    | _   | +70  | °C   |

#### Electrical Characteristics: (Note 1, Note 2)

| Parameter                    | Symbol          | Test Conditions                                      |                       | Min | Тур  | Max  | Unit |

|------------------------------|-----------------|------------------------------------------------------|-----------------------|-----|------|------|------|

| Threshold Voltage at A Input | V <sub>T+</sub> | V <sub>CC</sub> = MIN                                |                       | -   | 1.0  | 2.0  | V    |

|                              | V <sub>T-</sub> |                                                      |                       | 0.8 | 1.0  | -    | V    |

| Threshold Voltage at B Input | V <sub>T+</sub> | V <sub>CC</sub> = MIN                                |                       | -   | 1.0  | 2.0  | V    |

|                              | V <sub>T-</sub> |                                                      |                       | 0.8 | 0.9  | -    | V    |

| Input Clamp Voltage          | V <sub>IK</sub> | $V_{CC} = MIN, I_I = -18mA$                          |                       | -   | -    | -1.5 | V    |

| High Level Output Voltage    | V <sub>OH</sub> | $V_{CC} = MIN, I_{OH} = -400 \mu A$                  |                       | 2.7 | 3.4  | -    | V    |

| Low Level Output Voltage     | V <sub>OL</sub> | V <sub>CC</sub> = MIN                                | I <sub>OL</sub> = 4mA | -   | 0.25 | 0.4  | V    |

|                              |                 |                                                      | I <sub>OL</sub> = 8mA | -   | 0.35 | 0.5  | V    |

| Input Current                | l <sub>l</sub>  | V <sub>CC</sub> = MAX, V <sub>I</sub> = 7V           | •                     | -   | -    | 0.1  | mA   |

| High Level Input Current     | Ι <sub>ΙΗ</sub> | $V_{CC} = MAX, V_I = 2.7V$                           |                       | -   | _    | 20   | μΑ   |

| Low Level Input Current      | ۱ <sub>IL</sub> | V <sub>CC</sub> = MAX, V <sub>I</sub> = 0.4V Input A |                       | -   | -    | -0.4 | mA   |

|                              |                 |                                                      | Input B               | -   | -    | -0.8 | mA   |

|                              |                 |                                                      | Clear                 | -   | _    | -0.8 | mA   |

| Short-Circuit Output Current | I <sub>OS</sub> | V <sub>CC</sub> = MAX, Note 3                        | -                     | -20 | -    | -100 | mA   |

| Supply Current               | I <sub>CC</sub> | V <sub>CC</sub> = MAX                                | Quiescent             | -   | 4.7  | 11   | mA   |

|                              |                 |                                                      | Triggered             | -   | 19   | 27   | mA   |

Note 1. .For conditions shown as MIN or MAX, use the appropriate value specified under "Recommended Operation Conditions".

Note 2. All typical values are at  $V_{CC} = 5V$ ,  $T_A = +25^{\circ}C$ .

Note 3. Not more than one output should be shorted at a time and duration of short-circuit should not exceed one second.

## <u>Switching Characteristics</u>: ( $V_{CC}$ = 5V, $T_A$ = +25°C unless otherwise specified)

| Parameter                                                | Symbol              |                                    | Test Conditions                            | Min | Тур | Max | Unit |

|----------------------------------------------------------|---------------------|------------------------------------|--------------------------------------------|-----|-----|-----|------|

| Propagation Delay Time<br>(From A Input to Q Output)     | t <sub>PLH</sub>    | $C_L = 15 pF,$<br>$R_L = 2k\Omega$ | $C_{ext}$ = 80pF, $R_{ext}$ = 2k $\Omega$  | -   | 45  | 70  | ns   |

| Propagation Delay Time<br>(From B Input to Q Output)     | t <sub>PLH</sub>    | ]                                  |                                            | _   | 35  | 55  | ns   |

| Propagation Delay Time<br>(From A Input to Q Output)     | t <sub>PHL</sub>    | ]                                  |                                            | _   | 50  | 80  | ns   |

| Propagation Delay Time<br>(From B Input to Q Output)     | t <sub>PHL</sub>    | ]                                  |                                            | _   | 40  | 65  | ns   |

| Propagation Delay Time<br>(From Clear Input to Q Output) | t <sub>PHL</sub>    | ]                                  |                                            | _   | 35  | 55  | ns   |

| Propagation Delay Time<br>(From Clear Input to Q Output) | t <sub>PHL</sub>    | ]                                  |                                            | _   | 44  | 65  | ns   |

| Output Pulse Width                                       | t <sub>w(out)</sub> |                                    | $C_{ext}$ = 80pF, $R_{ext}$ = 2k $\Omega$  | 70  | 120 | 150 | ns   |

| (From A or B Input to Q or $\overline{Q}$ Output)        |                     |                                    | $C_{ext}$ = 0pF, $R_{ext}$ = 2k $\Omega$   | 20  | 47  | 70  | ns   |

|                                                          |                     |                                    | $C_{ext} = 100 pF, R_{ext} = 10 k\Omega$   | 670 | 740 | 810 | ns   |

|                                                          |                     |                                    | $C_{ext} = 1\mu F$ , $R_{ext} = 10k\Omega$ | 6.0 | 6.9 | 7.5 | ns   |

#### **Function Table:**

#### Truth Table:

| Inputs |              |   | Outputs |   |  |

|--------|--------------|---|---------|---|--|

| Clear  | Α            | В | Q       | Q |  |

| L      | Х            | Х | L       | Н |  |

| Х      | Н            | Х | L       | Н |  |

| Х      | Х            | L | L       | Н |  |

| Н      | L            | Ť |         |   |  |

| Н      | $\downarrow$ | H |         |   |  |

| ↑ *    | Ĺ            | H |         |   |  |

H = High Level

L = Low Level

X = Irrelavent

↑ = Transition from LOW-to-HIGH

↓ = Transition from HIGH-to-LOW

\_\_\_ = One HIGH Level Pulse

□ = One LOW Level Pulse

\* This condition is true only if the output of the latch formed by the two NAND gates has been conditioned to the logical "1" state prior to CLR going high. This latch is conditioned by taking either A or B low which CLR is in the inactive state.