### Half Bridge GaNFast™ Power IC with GaNSense™ Technology

#### 1. Features

#### GaNFast™ Power IC

- Wide Vcc range (10 to 24 V)

- 3.3, 5, 12 V PWM input compatible

- · Floating high-side with internal level shift

- · Two independent logic inputs with hysteresis

- · 200V/ns common mode transient immunity

- · Integrated high-side bootstrap

- · Shoot-through protection

- Turn-on dV/dt slew rate control (low-side and high-side)

- · 800 V transient voltage rating

- · 650 V continuous voltage rating

- 70 mΩ high-side FET, 70 mΩ low-side FET

- Zero reverse recovery charge

- 2 KV ESD Rating (HBM)

- 2 MHz operation

#### GaNSense™ Technology

- · Integrated loss-less current sensing

- · Over-current protection

- Over-temperature protection

- · Autonomous low-current standby mode

- · Auto-standby enable input

#### Small, low profile SMT QFN

- 8x10 mm footprint, 0.85 mm profile

- · Minimized package inductance

- · Enlarged cooling pads

#### Sustainability

- · RoHS, Pb-free, REACH-compliant

- · Up to 40% energy savings vs Si solutions

- System level 4kg CO<sub>2</sub> Carbon Footprint reduction

#### **Product Reliability**

· 20-year warranty

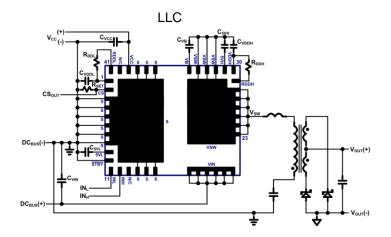

#### 2. Topologies / Applications

- · AC-DC, DC-DC

- · ACF, buck, boost, half bridge, full bridge, LLC, AHB, Class D, PFC, Motor Drive

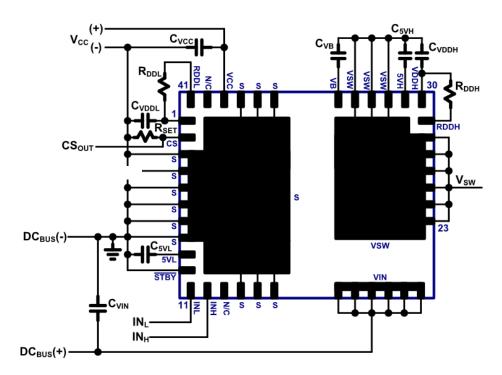

# 4. Typical Application Circuits

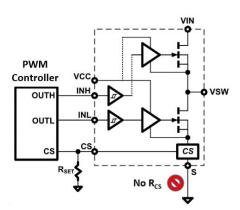

Loss-less Current Sensing

QFN 8 x 10 mm

Simplified schematic

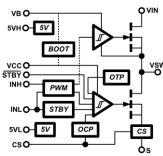

#### 3. Description

This half-bridge GaNFast™ power IC integrates high performance eMode GaN FETs with integrated gate drive, control and protection to achieve unprecedented highfrequency and high efficiency operation. technology is also integrated which enables real-time, accurate sensing of voltage, current and temperature to further improve performance and robustness not achieved by any discrete GaN or discrete silicon device. GaNSense™ enables integrated loss-less current sensing which eliminates external current sensing resistors increases and efficiency. GaNSense™ also enables short circuit and overtemperature protection to increase system robustness, while auto-standby mode increases light, tiny & no-load efficiency. These GaN ICs combine the highest dV/dt immunity, high-speed integrated drive and thermally optimized, lowinductance, QFN packaging to enable designers to achieve simple, quick, and reliable solutions. Navitas' GaN IC technology extends the capabilities of traditional topologies such as active clamp flyback, half-bridge, buck/boost, LLC and other resonant converters to reach MHz+ frequencies with very high efficiencies and low EMI to achieve unprecedented power densities at a very attractive cost structure.

### 5. Table of Contents

| 1. Features                                                        | 1  |

|--------------------------------------------------------------------|----|

| 2. Topologies / Applications                                       | 1  |

| 3. Description                                                     | 1  |

| 4. Typical Application Circuits                                    | 1  |

| 5. Table of Contents                                               | 2  |

| 6. Specifications                                                  | 3  |

| 6.1. Absolute Maximum Ratings (1) (with respect PGND unless noted) |    |

| 6.2. Recommended Operating Conditions <sup>(3)</sup>               | 4  |

| 6.3. ESD Ratings                                                   | 4  |

| 6.4. Thermal Resistance                                            | 4  |

| 6.5. Electrical Characteristics                                    | 5  |

| 6.6. Electrical Characteristics (2, cont.)                         | 6  |

| 6.7. Electrical Characteristics (3, cont.)                         | 7  |

| 6.8. Switching Waveforms                                           | 8  |

| 6.9. Characteristic Graphs                                         | 9  |

| 7. Pin Configurations and Functions                                | 12 |

| 8 Functional Description                                           | 12 |

| 8.1. GaN Power IC Connections and Compone Values 1 |    |

|----------------------------------------------------|----|

| 8.2. UVLO Mode 1                                   | 15 |

| 8.3. Normal Operating Mode1                        | 15 |

| 8.4. Low Power Standby Mode1                       | 16 |

| 8.5. Programmable Turn-on dV/dt Control1           | 17 |

| 8.6. GaNSense™ Technology Loss-Less Curre Sensing1 |    |

| 8.7. Over Current Protection (OCP) 1               | 19 |

| 8.8. Over Temperature Protection (OTP)2            | 20 |

| 9. PCB Layout Guidelines2                          | 21 |

| 10. Recommended PCB Land Pattern 2                 | 22 |

| 11. Package Outline (Power QFN)2                   | 23 |

| 12. Tape and Reel Dimensions2                      | 24 |

| 13. Tape and Reel Dimensions (Cont.) 2             | 25 |

| 14. Ordering Information2                          | 26 |

| 15. 20-Year Limited Warranty2                      | 26 |

| 16. Revision History 2                             | 26 |

### 6. Specifications

#### 6.1. Absolute Maximum Ratings (1) (with respect to PGND unless noted)

| SYMBOL                                       | PARAMETER                                                                  | MAX                            | UNITS |

|----------------------------------------------|----------------------------------------------------------------------------|--------------------------------|-------|

| V <sub>IN</sub>                              | HV input                                                                   | 0 to +650                      | V     |

| V <sub>SW(CONT)</sub>                        | Switch Node Continuous Voltage Rating                                      | -7 to +657                     | V     |

| V <sub>SW(TRAN)</sub> (2)                    | Switch Node Transient Voltage Rating                                       | -10 to +800                    | V     |

| I <sub>DSL</sub> @ T <sub>C</sub> =100°C     | Continuous Output Current (Low-side FET)                                   | 14                             | Α     |

| I <sub>DSL</sub> PULSE@ T <sub>C</sub> =25°C | Pulsed Output Current (Low-side FET)                                       | 28                             | Α     |

| I <sub>DSH</sub> @ T <sub>C</sub> =100°C     | Continuous Output Current (High-side FET)                                  | 14                             | Α     |

| I <sub>DSH</sub> PULSE@ T <sub>C</sub> =25°C | Pulsed Output Current (High-side FET)                                      | 28                             | Α     |

| V <sub>B</sub> (to V <sub>SW</sub> )         | High-side Gate Driver Bootstrap Rail                                       | 30                             | V     |

| V <sub>DDH</sub> (to V <sub>SW</sub> )       | V <sub>DDH</sub> (to V <sub>SW</sub> ) High-side Gate Drive Supply Voltage |                                | V     |

| V <sub>5VH</sub> (to V <sub>SW</sub> )       | High-side 5V Supply Voltage                                                | 6                              | V     |

| V <sub>cc</sub>                              | Supply Voltage                                                             | 30                             | V     |

| $V_{DDL}$                                    | Low-side Drive Supply Voltage                                              | 7                              | V     |

| $R_{DDL}$                                    | Low-side Gate Drive Supply Resistor Setting Input                          | 7                              | V     |

| $V_{5VL}$                                    | Low-side 5V Supply Voltage                                                 | 6                              | V     |

| Vstby                                        | Auto-Standby Mode Pin Voltage                                              | -0.6 to +20 or V <sub>CC</sub> | V     |

| $V_{INH}, V_{INL}$                           | PWM Input Pin Voltages                                                     | -0.6 to +20 or V <sub>CC</sub> | V     |

| V <sub>cs</sub>                              | CS Pin Voltage                                                             | 5.3                            | V     |

| dV/dt (3)                                    | Slew Rate                                                                  | 100                            | V/ns  |

| T <sub>J</sub>                               | Junction Temperature                                                       | -55 to 150                     | °C    |

| T                                            | Storage Temperature                                                        | -55 to 150                     | °C    |

<sup>(1)</sup> Absolute maximum ratings are stress ratings; devices subjected to stresses beyond these ratings may cause permanent damage.

Final Datasheet 3 Rev Sep. 24, 2024

<sup>(2)</sup>  $V_{DS\,(TRAN)}$  rating allows for surge ratings during non-repetitive events that are <100us (for example start-up, line interruption).  $V_{DS\,(TRAN)}$  rating allows for repetitive events that are <300ns, with 80% derating required (for example repetitive leakage inductance spikes).

<sup>(3)</sup> Max dV/dt rating is based on stress ratings and common mode transient immunity

## 6.2. Recommended Operating Conditions(3)

| SYMBOL             | PARAMETER                                         | MIN | TYP | MAX                   | UNITS |

|--------------------|---------------------------------------------------|-----|-----|-----------------------|-------|

| V <sub>cc</sub>    | Supply Voltage                                    | 10  | 15  | 24                    | V     |

| $V_{INH}, V_{INL}$ | PWM Input Pin Voltage                             | 0   | 5   | 15 or V <sub>CC</sub> | V     |

| Vstby              | Auto-Standby Mode Pin Voltage                     | 0   | 5   | 15 or V <sub>CC</sub> | V     |

| R <sub>DDL</sub>   | Low-side gate drive turn-on current set resistor  | 100 |     | 1,000                 | Ω     |

| R <sub>DDH</sub>   | High-side gate drive turn-on current set resistor | 100 |     | 1,000                 | Ω     |

| T <sub>J</sub>     | Operating Junction Temperature                    | -40 |     | 125                   | °C    |

<sup>(3)</sup> Exposure to conditions beyond maximum recommended operating conditions for extended periods of time may affect device reliability.

### 6.3. ESD Ratings

| SYMBOL | PARAMETER                              | MAX   | UNITS |

|--------|----------------------------------------|-------|-------|

| HBM    | Human Body Model (per JS-001-2014)     | 2,000 | V     |

| CDM    | Charged Device Model (per JS-002-2014) | 500   | V     |

#### 6.4. Thermal Resistance

| SYMBOL               | PARAMETER           | TYP  | UNITS |

|----------------------|---------------------|------|-------|

| R <sub>eJC</sub> (4) | Junction-to-Case    | 0.98 | °C/W  |

| R <sub>eJA</sub>     | Junction-to-Ambient | 40   | °C/W  |

<sup>(4)</sup>  $R_{\rm e}$  measured on DUT mounted on 1 square inch 2 oz Cu (FR4 PCB)

Final Datasheet 4 Rev Sep. 24, 2024

#### 6.5. Electrical Characteristics

Typical conditions:  $V_{IN}$ =400V,  $V_{CC}$ =15V,  $F_{SW}$ =1MHz,  $T_{AMB}$ =25°C,  $I_{D}$ =7A (unless otherwise specified)

| SYMBOL                         | PARAMETER                                                                           | MIN       | TYP     | MAX  | UNITS | CONDITIONS                                                                         |

|--------------------------------|-------------------------------------------------------------------------------------|-----------|---------|------|-------|------------------------------------------------------------------------------------|

|                                | V <sub>CC</sub> , V <sub>DDL</sub> , V <sub>B</sub> and V <sub>DDH</sub> Supp       | oly Char  | acteris | tics |       | •                                                                                  |

| V <sub>CCUV+</sub>             | V <sub>CC</sub> UVLO Rising Threshold                                               | 8.0       | 8.6     | 9.3  | V     |                                                                                    |

| V <sub>CCUV</sub> -            | V <sub>CC</sub> UVLO Falling Threshold                                              |           | 7.4     |      | V     |                                                                                    |

| I <sub>QCC-STBY</sub>          | V <sub>CC</sub> Standby Current                                                     | 200       | 400     | 560  | μΑ    | $\overline{STBY} = 0 \text{ V, V}_{SW} >= V_{CC}$                                  |

| I <sub>QCC</sub>               | V <sub>CC</sub> Quiescent Current                                                   |           |         |      | mA    | $V_{INL} = V_{INH} = 0 \text{ V}, \overline{STBY}$<br>= 5 V                        |

| I <sub>QCC-SW</sub>            | I <sub>QCC-SW</sub> V <sub>CC</sub> Operating Current                               |           | 9       |      | mA    | F <sub>SW</sub> = 500 KHz (INL and INH @ 50% Duty cycle), V <sub>SW</sub> = 0 V    |

| $V_{DDL}$                      | V <sub>DD</sub> Supply Voltage                                                      | 5.9       | 6.1     | 6.6  | V     | V <sub>CC</sub> = 15 V, V <sub>INL</sub> = VI <sub>NH</sub> = 0 V                  |

| $V_{DDLUV+}$                   | V <sub>DDL</sub> UVLO Rising Turn-On Threshold                                      |           | 4.9     |      | V     |                                                                                    |

| V <sub>DDLUV-HYS</sub>         | V <sub>DDL</sub> UVLO Hysteresis                                                    |           | 0.6     |      | V     |                                                                                    |

| $V_{\text{BUV+}}$              | $V_B$ UVLO Rising Threshold ( $V_B - V_{SW}$ )                                      | 8.0       | 8.6     | 9.3  | V     |                                                                                    |

| $V_{\text{BUV-}}$              | V <sub>B</sub> UVLO Falling Threshold (V <sub>B</sub> – V <sub>SW</sub> )           |           | 7.8     |      | V     |                                                                                    |

| I <sub>QVB</sub>               | V <sub>B</sub> Quiescent Current                                                    |           | 1.7     |      | mA    | $V_{INH} = V_{INL} = 0 \text{ V},$<br>$V_{SW} = 0 \text{ V}, V_{B} = 15 \text{ V}$ |

| $V_{DDH}$                      | V <sub>DD</sub> Supply Voltage                                                      | 5.9       | 6.1     | 6.6  | V     | V <sub>B</sub> = 15 V                                                              |

|                                | 5V Output (5\                                                                       | / pin)    |         | •    |       |                                                                                    |

| $V_{5VL},V_{5VH}$              | 5V Output Voltage                                                                   | 4.4       | 5.1     | 5.5  | V     |                                                                                    |

|                                | Input Logic Characteristic                                                          | s (INL,I  | NH, ST  | BY)  |       | •                                                                                  |

| $V_{LOGIC-H}$                  | Input Logic High Threshold (rising edge)                                            |           | 2.5     | 2.8  | V     |                                                                                    |

| $V_{LOGIC\text{-L}}$           | Input Logic Low Threshold (falling edge)                                            | 1.1       | 1.2     |      | V     |                                                                                    |

| $V_{LOGIC\text{-HYS}}$         | Input Logic Hysteresis                                                              |           | 1.4     |      | V     |                                                                                    |

|                                | Switching Charac                                                                    | cteristic | s       |      |       |                                                                                    |

| F <sub>SW</sub>                | Switching Frequency                                                                 |           |         | 2    | MHz   | $R_{DDL,H} = 100 \Omega$                                                           |

| t <sub>PW</sub> <sup>(1)</sup> | Pulse width                                                                         | 0.05      |         |      | us    |                                                                                    |

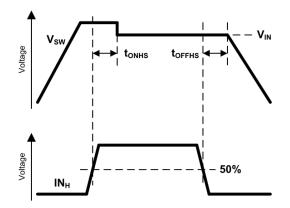

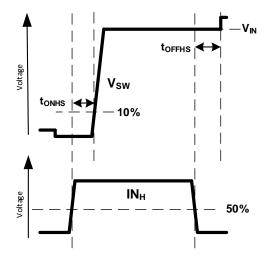

| t <sub>ONHS</sub>              | Prop Delay (IN $_{\rm H}$ from Low to High, V $_{\rm SW}$ pulled to V $_{\rm IN}$ ) |           | 65      |      | ns    | Fig. 3                                                                             |

| t <sub>OFFHS</sub>             | Prop Delay (IN $_{\rm H}$ from High to Low, V $_{\rm SW}$ tri-stated)               |           | 50      |      | ns    | Fig. 3                                                                             |

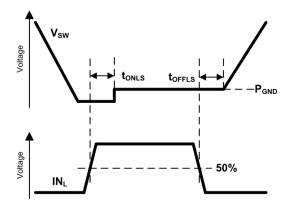

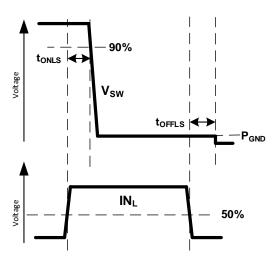

| t <sub>ONLS</sub>              | Prop Delay (IN, from Low to High, V <sub>SW</sub> pulled to                         |           | 42      |      | ns    | Fig. 4                                                                             |

| t <sub>OFFLS</sub>             | Prop Delay (IN <sub>L</sub> from High to Low, V <sub>SW</sub> tri-stated)           |           | 51      |      | ns    | Fig. 4                                                                             |

| High side<br>turn on dvdt      |                                                                                     |           | 16      |      | V/ns  | $R_{DDH} = 100 \Omega$                                                             |

| Low side turn<br>on dvdt       |                                                                                     |           | 14      |      | V/ns  | R <sub>DDL</sub> = 100 Ω                                                           |

<sup>(1)</sup> Min Pulse width limitation is only for the high side FET

Rev Sep. 24, 2024 Final Datasheet 5

## 6.6. Electrical Characteristics (2, cont.)

$\text{Typical conditions: V}_{\text{DS}} \text{=} 400 \text{V, V}_{\text{CC}} \text{=} 15 \text{V, F}_{\text{SW}} \text{=} 1 \text{MHz, T}_{\text{AMB}} \text{=} 25 ^{\circ} \text{C, I}_{\text{D}} \text{=} 7 \text{A (unless otherwise specified)}$

| SYMBOL               | PARAMETER                                                                     | MIN       | TYP         | MAX     | UNITS | CONDITIONS                                                              |  |  |  |  |

|----------------------|-------------------------------------------------------------------------------|-----------|-------------|---------|-------|-------------------------------------------------------------------------|--|--|--|--|

|                      | Current Sense Characteristics (CS pin)                                        |           |             |         |       |                                                                         |  |  |  |  |

| I <sub>CS</sub>      | CS Pin Output Current                                                         | 1.16      | 1.25        | 1.34    | mA    | V <sub>INL</sub> = 5 V, I <sub>DS</sub> = 11 A                          |  |  |  |  |

| Offset               | CS Output Offset                                                              |           | +18         |         | μΑ    | $V_{INL} = 5 \text{ V}, I_{DS} = 0 \text{ A}$                           |  |  |  |  |

| t <sub>CSDLY</sub>   | CS Pin Delay (from I <sub>DS</sub> to V <sub>CS</sub> , at 10% rated current) |           | 55          |         | ns    | di/dt = 40 A/us,<br>R <sub>SET</sub> = 400 Ohm, C <sub>CS</sub> = 25 pF |  |  |  |  |

|                      | Over-Current Protection                                                       |           |             |         |       |                                                                         |  |  |  |  |

| ОСРтн                | OCP Threshold Voltage (V <sub>CS</sub> Pin)                                   |           | 1.9         |         | ٧     |                                                                         |  |  |  |  |

|                      | Star                                                                          | ndby Mod  | e Characte  | ristics |       |                                                                         |  |  |  |  |

| t <sub>TO_STBY</sub> | Time Out Delay Entering Standby Mode                                          |           | 90          |         | μs    | V <sub>INL</sub> = 0 V                                                  |  |  |  |  |

| t <sub>ON_FP</sub>   | First Pulse Propagation Delay                                                 |           | 460         | 650     | ns    | $V_{INL} = 5 \text{ V pulse}, \overline{STBY} = 0 \text{ V}$            |  |  |  |  |

|                      | Ove                                                                           | er-Temper | ature Prote | ection  |       |                                                                         |  |  |  |  |

| T <sub>OTP+</sub>    | OTP Shutdown Threshold                                                        |           | 165         |         | °C    |                                                                         |  |  |  |  |

| T <sub>OTP_HYS</sub> | OTP Restart Hysteresis                                                        |           | 60          |         | °C    |                                                                         |  |  |  |  |

|                      | Bootstrap FET Characteristics                                                 |           |             |         |       |                                                                         |  |  |  |  |

| I <sub>BOOT</sub>    | Bootstrap Charging Current                                                    |           | 2           |         | А     | $V_{CC} = 12 \text{ V}, V_{B} = 0 \text{ V}, V_{SW} = 0 \text{ V}$      |  |  |  |  |

Final Datasheet 6 Rev Sep. 24, 2024

### 6.7. Electrical Characteristics (3, cont.)

$\textit{Typical conditions: V}_{\textit{DS}} = 400 \textit{V}, \textit{V}_{\textit{CC}} = 15 \textit{V}, \textit{F}_{\textit{SW}} = 1 \textit{MHz}, \textit{T}_{\textit{AMB}} = 25 ^{\circ} \textit{C}, \textit{I}_{\textit{D}} = 7 \textit{A} \textit{ (unless otherwise specified)}$

| SYMBOL                 | PARAMETER                                       | MIN    | TYP               | MAX         | UNITS | CONDITIONS                                                              |

|------------------------|-------------------------------------------------|--------|-------------------|-------------|-------|-------------------------------------------------------------------------|

|                        |                                                 | Low s  | ide GaN FET Chara | cteristics  |       |                                                                         |

| I <sub>DSS</sub>       | Drain-Source Leakage Current                    |        | 0.2               | 25          | μΑ    | $V_{DS} = 650 \text{ V}, V_{INL} = 0 \text{ V}$                         |

| I <sub>DSS</sub>       | Drain-Source Leakage Current, TC<br>=150 °C     |        | 10                |             | μΑ    | V <sub>DS</sub> =650V, V <sub>INL</sub> =0V, T <sub>C</sub> =150 °C     |

| R <sub>DS(ON)</sub>    | Low-side FET Drain-Source<br>Resistance         |        | 70                | 98          | mΩ    | $V_{INL} = 5 \text{ V}, I_D = 7 \text{ A}$                              |

| V <sub>SD</sub>        | Source-Drain Reverse Voltage                    |        | 3.2               | 5           | V     | $V_{INL} = 0 \text{ V}, V_{INH} = 0 \text{ V}, I_{SD} = 7 \text{ A}$    |

| Q <sub>oss</sub>       | Output Charge                                   |        | 41.5              |             | nC    | $V_{DS} = 400 \text{ V}, V_{INL} = 0 \text{ V}, V_{INH} = 0 \text{ V}$  |

| $Q_{RR}$               | Reverse Recovery Charge                         |        | 0                 |             | nC    | V <sub>DS</sub> = 400 V                                                 |

| C <sub>oss</sub>       | Output Capacitance                              |        | 59                |             | pF    | $V_{DS} = 400 \text{ V}, V_{INL} = 0 \text{ V}, V_{INH} = 0 \text{ V}$  |

| C <sub>O(er)</sub> (1) | Effective Output Capacitance,<br>Energy Related |        | 75.5              |             | pF    | V <sub>DS</sub> = 400 V, V <sub>INL</sub> = 0 V, V <sub>INH</sub> = 0 V |

| C <sub>O(tr)</sub> (2) | Effective Output Capacitance, Time Related      |        | 103.8             |             | pF    | $V_{DS} = 400 \text{ V}, V_{INL} = 0 \text{ V}, V_{INH} = 0 \text{ V}$  |

|                        |                                                 | High s | ide GaN FET Chara | acteristics |       |                                                                         |

| I <sub>DSS</sub>       | Drain-Source Leakage Current                    |        | 0.2               | 25          | μΑ    | $V_{DS} = 650 \text{ V}, V_{INL} = 0 \text{ V}$                         |

| I <sub>DSS</sub>       | Drain-Source Leakage Current, TC =150 °C        |        | 10                |             | μΑ    | V <sub>DS</sub> =650V, V <sub>INL</sub> =0V, T <sub>C</sub> =150 °C     |

| R <sub>DS(ON)</sub>    | High-side FET Drain-Source<br>Resistance        |        | 70                | 98          | mΩ    | $V_{INL} = 5 \text{ V}, I_D = 7 \text{ A}$                              |

| V <sub>SD</sub>        | Source-Drain Reverse Voltage                    |        | 3.2               | 5           | V     | $V_{INL} = 0 \text{ V}, V_{INH} = 0 \text{ V}, I_{SD} = 7 \text{ A}$    |

| Q <sub>oss</sub>       | Output Charge                                   |        | 37.5              |             | nC    | $V_{DS} = 400 \text{ V}, V_{INL} = 0 \text{ V}, V_{INH} = 0 \text{ V}$  |

| Q <sub>RR</sub>        | Reverse Recovery Charge                         |        | 0                 |             | nC    | V <sub>DS</sub> = 400 V                                                 |

| C <sub>oss</sub>       | Output Capacitance                              |        | 50                |             | pF    | V <sub>DS</sub> = 400 V, V <sub>INL</sub> = 0 V, V <sub>INH</sub> = 0 V |

| C <sub>O(er)</sub> (1) | Effective Output Capacitance,<br>Energy Related |        | 66.6              |             | pF    | V <sub>DS</sub> = 400 V, V <sub>INL</sub> = 0 V, V <sub>INH</sub> = 0 V |

| C <sub>O(tr)</sub> (2) | Effective Output Capacitance, Time Related      |        | 93.8              |             | pF    | $V_{DS} = 400 \text{ V}, V_{INL} = 0 \text{ V}, V_{INH} = 0 \text{ V}$  |

<sup>(1)</sup>  $C_{O(er)}$  is a fixed capacitance that gives the same stored energy as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 400 V

Final Datasheet 7 Rev Sep. 24, 2024

<sup>(2)</sup>  $C_{O(tr)}$  is a fixed capacitance that gives the same charging time as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 400 V

### 6.8. Switching Waveforms

(T<sub>C</sub> = 25 °C unless otherwise specified)

Fig. 1. Propagation Delay ZVS Mode  $t_{\mbox{\scriptsize ONHS/OFFHS}}$

Fig. 2. Propagation Delay ZVS Mode  $t_{\text{ONLS/OFFLS}}$

Fig. 3. Propagation Delay Hard Switching tonhs/offhs

Fig. 4. Propagation Delay Hard Switching tonls/OFFLS

Final Datasheet 8 Rev Sep. 24, 2024

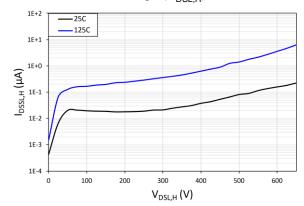

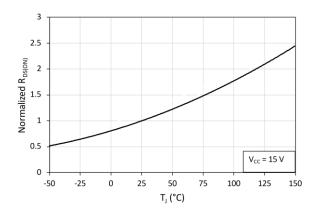

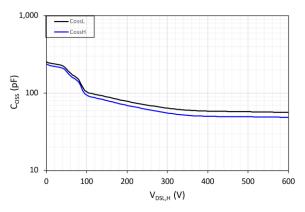

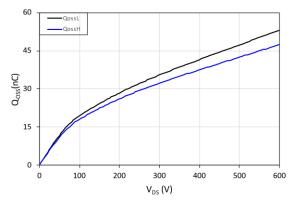

### 6.9. Characteristic Graphs

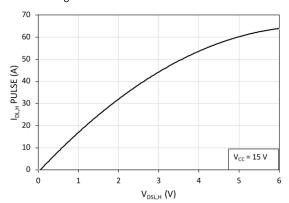

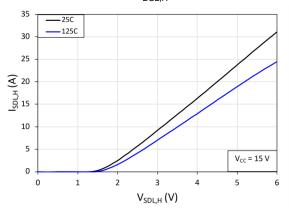

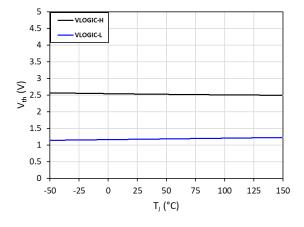

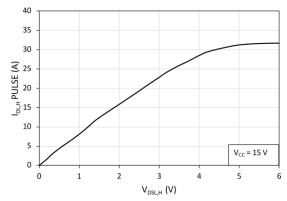

(GaN FET, T<sub>C</sub> = 25 °C unless otherwise specified)

Fig. 5. Pulsed Drain current ( $I_{\mathrm{DSL,H}}$  PULSE) vs. drain-tosource voltage ( $V_{DSL,H}$ ) at T = 25 °C

Fig. 7. Source-to-drain reverse conduction voltage (I<sub>SDL,H</sub>)

Fig. 9. VLOGIC-H and VLOGIC-L vs. junction temperature (T<sub>.</sub>)

Fig. 6. Pulsed Drain current ( $I_{DSL,H}$  PULSE) vs. drain-to-source voltage (V<sub>DSL,H</sub>) at T = 125 °C

Fig. 8. Drain-to-source leakage current (I<sub>DSSL,H</sub>) vs.drain-to-source voltage  $(V_{DSL,H})$

Fig. 10. Normalized on-resistance ( $R_{DSL,H(ON)}$ ) vs. junction temperature (T,)

**Final Datasheet** Rev Sep. 24, 2024

### **Characteristic Graphs (Cont.)**

Fig. 11. Output capacitance ( $C_{\text{OSSL},H}$ ) vs. drain-tosource voltage (V<sub>DSL.H</sub>)

Fig. 13. Charge stored in output capacitance (Q<sub>OSS</sub>) vs. drain-to-source voltage (V<sub>DS</sub>)

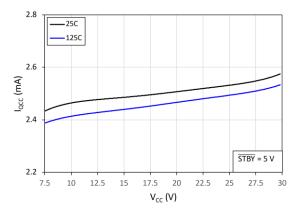

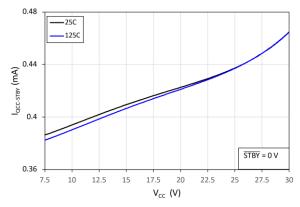

Fig. 15.  $V_{CC}$  quiescent current ( $I_{QCC}$ ) vs. supply voltage (V<sub>CC</sub>)

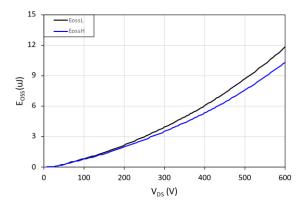

Fig. 12. Energy stored in output capacitance ( $E_{\rm OSSL,H}$ ) vs. drain-to-source voltage  $(V_{DSL,H})$

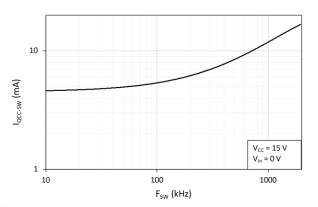

Fig. 14.  $V_{CC}$  operating current ( $I_{QCC-SW}$ ) vs. operating frequency (F<sub>SW</sub>)

Fig. 16. Vcc stand-by quiescent current (Iqcc) vs. supply voltage (V<sub>CC</sub>)

**Final Datasheet** 10 Rev Sep. 24, 2024

# **Characteristic Graphs (Cont.)**

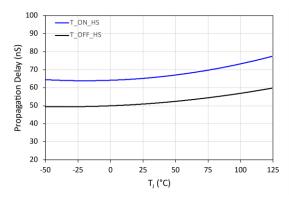

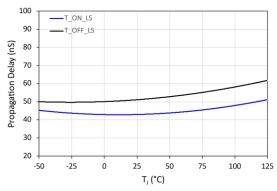

Fig. 17. Propagation delay ( $T_{ON}$  and  $T_{OFF}$ ) vs. junction temperature ( $T_{IJ}$ ) – low side

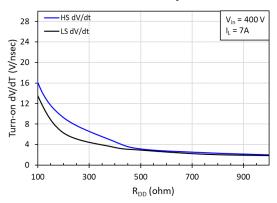

Fig. 19. Slew rate (dV/dt) vs. gate drive turn-on current set resistance ( $R_{DDL}$ ) at T = 25 °C

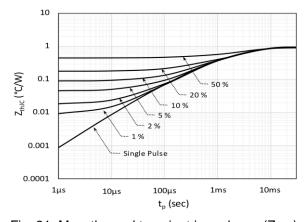

Fig. 21. Max. thermal transient impedance  $(Z_{thJC})$  vs. pulse width  $(t_p)$

Fig. 18. Propagation delay ( $T_{ON}$  and  $T_{OFF}$ ) vs. junction temperature ( $T_{,l}$ ) – high side

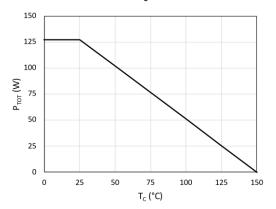

Fig. 20. Power dissipation  $(P_{TOT})$  vs. case temperature  $(T_C)$

Fig. 22. CS Pin Current Output Drift vs. case temperature (Tc)

Final Datasheet 11 Rev Sep. 24, 2024

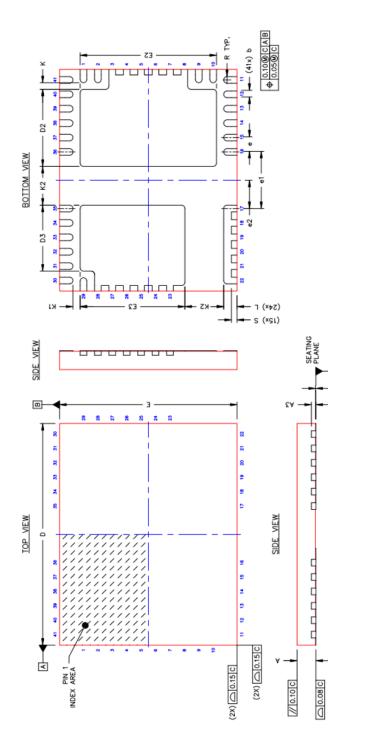

## 7. Pin Configurations and Functions

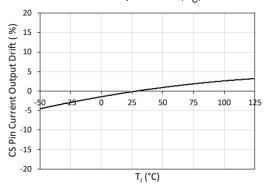

Fig. 23 Package Top View

| Pin                           |                              | I/O <sup>(1)</sup> | Description                                                                                                                                                           |

|-------------------------------|------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number                        | Symbol                       |                    |                                                                                                                                                                       |

| 3-8,14-16,36-38<br>(and PAD1) | $P_{GND}$                    | G                  | Power ground                                                                                                                                                          |

| 1                             | $V_{\scriptscriptstyle DDL}$ | Р                  | Low-side drive supply                                                                                                                                                 |

| 2                             | CS                           | 0                  | GaN FET IDS current sensing set pin. Internal current source and external resistor R <sub>SET</sub> sets current measurement level. Connect resistor from CS to SGND. |

| 9                             | 5V <sub>L</sub>              | Р                  | Low-side 5 V supply                                                                                                                                                   |

| 10                            | STBY                         | I                  | Auto-standby enable input (0=ON)                                                                                                                                      |

| 11                            | IN <sub>L</sub>              | I                  | Low-side drive input                                                                                                                                                  |

| 12                            | IN <sub>H</sub>              | I                  | High-side drive input                                                                                                                                                 |

| 13, 40                        | N/C                          |                    | No connect                                                                                                                                                            |

| 17 – 22                       | V <sub>IN</sub>              | Р                  | HV input                                                                                                                                                              |

| 23-28,32-34<br>(and PAD2)     | V <sub>sw</sub>              | 0                  | Half-bridge switch node                                                                                                                                               |

| 29                            | R <sub>DDH</sub>             | I                  | High-side gate drive turn-on current set resistor (using $R_{DD}$ resistor connected from $R_{DDH}$ pin to $V_{DDH}$ pin)                                             |

| 30                            | V <sub>DDH</sub>             | Р                  | High-side drive supply                                                                                                                                                |

| 31                            | 5V <sub>H</sub>              | Р                  | High-side 5 V supply                                                                                                                                                  |

| 35                            | V <sub>B</sub>               | Р                  | High-side gate driver bootstrap rail                                                                                                                                  |

| 39                            | V <sub>cc</sub>              | Р                  | IC supply voltage                                                                                                                                                     |

| 41                            | R <sub>DDL</sub>             | I                  | Low-side gate drive turn-on current set resistor (using R <sub>DD</sub> resistor connected from R <sub>DDL</sub> pin to V <sub>DDL</sub> pin)                         |

(1) I = Input, O = Output, P = Power, G = Ground, NC = No Connect

Final Datasheet 12 Rev Sep. 24, 2024

#### 8. Functional Description

The functional description contains additional information regarding the IC operating modes and pin functionality.

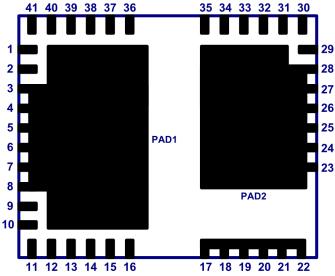

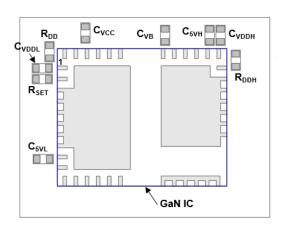

#### 8.1. GaN Power IC Connections and Component Values

The typical connection diagram for this GaN Half-Bridge IC is shown in Fig. 24. The IC pins include the drain of the high-side GaN power FET ( $V_{IN}$ ), the half-bridge mid-point switched node ( $V_{SW}$ ), the source of the low-side GaN power FET and IC GND ( $P_{GND}$ ), low-side IC supply ( $V_{CC}$ ), low-side gate drive supply ( $V_{DDL}$ ), low-side turn-on dV/dt control ( $R_{DDL}$ ), low-side 5V supply ( $5V_L$ ), low-side referenced PWM inputs (INL, INH), low-side current sensing output (CS), auto-standby enable input ( $\overline{STBY}$ ), high-side supply ( $V_B$ ), high-side gate drive supply ( $V_{DDH}$ ), and high-side 5V supply ( $5V_H$ ). The external low-side components around the IC include  $V_{CC}$  supply capacitor ( $C_{VCC}$ ) connected between  $V_{CC}$  pin and  $P_{GND}$ ,  $V_{DDL}$  supply capacitor ( $C_{VDDL}$ ) connected between  $V_{DDL}$  pin and  $P_{GND}$ , turn-on dV/dt set resistor ( $R_{DDL}$ ) connected between  $V_{DDL}$  pin and  $V_{SMD}$ , supply capacitor ( $V_{SMD}$ ) connected between  $V_{SMD}$ , and the auto-standby enable pin ( $\overline{STBY}$ ) connected to  $V_{CMDL}$ ) connected between  $V_{CMDL}$  pin and  $V_{CMDL}$  connected between  $V_{CMDL}$  connected between  $V_{CMDL}$  connected between  $V_{CMDL}$  pin and  $V_{SMD}$ , turn-on dV/dt set resistor ( $V_{CMDL}$ ) connected between  $V_{CMDL}$  pin and  $V_{SMD}$ , turn-on dV/dt set resistor ( $V_{CMDL}$ ) connected between  $V_{CMDL}$  pin and  $V_{CMDL}$  connected between  $V_{CMDL}$  pin and  $V_{CMDL}$  connected between  $V_{CMDL}$  connected between  $V_{CMDL}$  pin and  $V_{CMDL}$  connected between  $V_{CMDL}$  pin and  $V_{$

Fig. 24. IC connection diagram

Final Datasheet 13 Rev Sep. 24, 2024

The following table (Table I) shows the recommended component values (typical only) for the external components connected to the pins of this Half-Bridge GaN power IC. These components should be placed as close as possible to the IC. Please see PCB Layout Guidelines for more information.

| SYM              | DESCRIPTION                                       | ТҮР                          | UNITS |

|------------------|---------------------------------------------------|------------------------------|-------|

| C <sub>VCC</sub> | V <sub>CC</sub> supply capacitor                  | 0.1                          | μF    |

| $C_{VDD}$        | V <sub>DD</sub> supply capacitor                  | 0.01                         | μF    |

| R <sub>DDL</sub> | Low-side gate drive turn-on current set resistor  | 100                          | Ω     |

| R <sub>SET</sub> | Current sense amplitude set resistor              | See Section 8.6 , Equation 1 | Ω     |

| C <sub>5VL</sub> | 5V <sub>∟</sub> supply capacitor                  | 0.022                        | μF    |

| C <sub>VB</sub>  | V <sub>B</sub> supply capacitor                   | 0.01                         | μF    |

| $C_{VDDH}$       | V <sub>DDH</sub> supply capacitor                 | 0.01                         | μF    |

| R <sub>DDH</sub> | High-side gate drive turn-on current set resistor | 100                          | Ω     |

| C <sub>5VH</sub> | 5V <sub>H</sub> supply capacitor                  | 0.01                         | μF    |

Table I. Recommended component values (typical only).

Final Datasheet 14 Rev Sep. 24, 2024

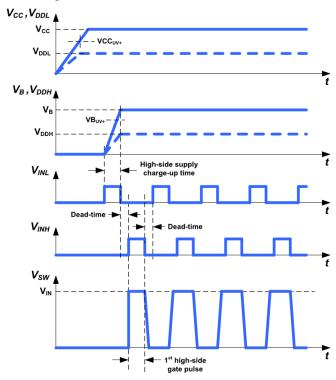

#### 8.2. UVLO Mode

This GaN Power IC includes under-voltage lockout (UVLO) circuits for both the high side and low side power supplies for properly disabling all the internal circuitry while ensuring that the gates of power FETs are kept in their OFF state. While  $V_{CC}$  is below the  $V_{CC}$  in the  $V_{CC}$  is below the  $V_{CC}$  in the  $V_{CC}$  is below the  $V_{CC}$  is below the  $V_{CC}$  in the  $V_{CC}$  in the  $V_{CC}$  in the  $V_{CC}$  is below the  $V_{CC}$  in the  $V_{$

Fig. 25. UVLO Mode timing diagram

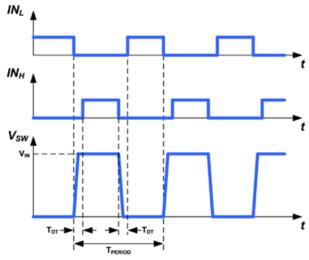

#### 8.3. Normal Operating Mode

During normal operating mode,  $V_{CC}$  is set at a sufficient level (15 V typical) by the auxiliary power supply of the power converter, and  $V_B$  is at a sufficient level (as set by  $V_{CC}$  and the internal bootstrap circuit). The PWM input signals at the  $IN_L$  and  $IN_H$  pins turn the gates of the internal high- and low-side GaN power FETs on and off at the desired duty-cycle, frequency, and dead-time. The input logic signal at the  $IN_L$  pin turns the low-side half-bridge power FET on and off (0=OFF, 1=ON), and the input logic signal at the  $IN_H$  pin turns the high-side half-bridge power FET on and off (0=OFF, 1=ON). As the PWM inputs are turned on and off in a complementary manner each switching cycle, the  $V_{SW}$  pin (half-bridge mid-point) is then switched between  $P_{GND}$  ( $IN_L=1$ ,  $IN_H=0$ ) and  $V_{IN}$  ( $IN_L=0$ ,  $IN_H=1$ ) at the given frequency and duty-cycle (Fig. 26). This GaN Half-Bridge IC includes shoot-through protection circuitry that prevents both power FETs from turning on simultaneously. This IC also includes an internal bootstrap FET for supplying the high-side circuitry. The bootstrap FET is enabled during normal operating mode and is turned on each PWM switching cycle only when the  $IN_L$  pin is 'HIGH' and the low-side power FET is on. This will allow the  $V_B$  capacitor to be charged up each switching cycle for properly maintaining the necessary floating high-side supply voltage. The  $V_B$  capacitor value should be sized correctly such that the  $V_B$  voltage is maintained at a sufficient level above UVLO- during normal operation. Should the  $V_B$ - $V_{SW}$  voltage decrease below the  $V_{BUV}$ - falling UVLO threshold

Final Datasheet 15 Rev Sep. 24, 2024

(7.8 V typical) at any time, then the high-side GaN power FET will turn off and become disabled until V<sub>B</sub>-V<sub>SW</sub> increases again above the VB<sub>UV+</sub> rising threshold (8.6 V typical).

Fig. 26. Normal operating mode timing diagram

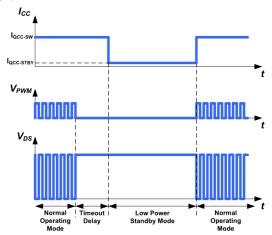

#### 8.4. Low Power Standby Mode

This GaN Half-Bridge IC includes an autonomous low power standby mode for disabling the IC and reducing the  $V_{CC}$  current consumption. During normal operating mode, the PWM input signals at the IN<sub>L</sub> and IN<sub>H</sub> pins turn the gates of the internal high- and low-side GaN power FETs on and off at the desired duty-cycle, frequency, and dead-time. If the input pulses at the IN<sub>L</sub> pin stop and stay below the lower  $V_{INL}$  turn-off threshold (1.1V, typical) for the duration of the internal timeout standby delay ( $t_{TO\_STBY}$ , 90usec, typical), then the IC will automatically enter low power standby mode (Fig. 27). This will disable the gate drive and other internal circuitry and reduce the  $V_{CC}$  supply current to a low level (300uA, typical). When the IN<sub>L</sub> pulses restart, the IC will wake up after a delay (typically around 490ns) at the first rising edge of the IN<sub>L</sub> input and enter normal operating mode again. To enable auto standby mode, the  $\overline{STBY}$  pin should be connected to Source (set low). To disable auto standby mode,  $\overline{STBY}$  pin should be connected to the 5V<sub>L</sub> pin 7 (set high).

Fig. 27. Autonomous Low Power Standby Mode timing diagram

Final Datasheet 16 Rev Sep. 24, 2024

### 8.5. Programmable Turn-on dV/dt Control

Energy • Efficiency • Sustainability

During first start-up pulses or during hard-switching conditions, it is desirable to limit the slew rate (dV/dt) of the drain of the power FET during turn-on. This is necessary to reduce EMI or reduce circuit switching noise. To program the turn-on dV/dt rate of the internal power FET, a resistor ( $R_{DDL,H}$ ) is placed in between the  $V_{DDL,H}$  pin and the  $R_{DDL,H}$  pin. This resistor ( $R_{DDL,H}$ ) sets the turn-on current of the internal gate driver and therefore sets the turn-on falling edge dV/dt rate of the drain of the power FET (Fig. 28). This resistor value should be 100  $\Omega$  minimum (see Table II)

Fig. 28. Turn-on dV/dt slew rate control

| SYM                | DESCRIPTION                 | MIN | TYP | MAX   | UNITS |

|--------------------|-----------------------------|-----|-----|-------|-------|

| R <sub>DDL,H</sub> | R <sub>DDL,H</sub> resistor | 100 |     | 1,000 | Ω     |

Table II. Recommended RDDL, H values

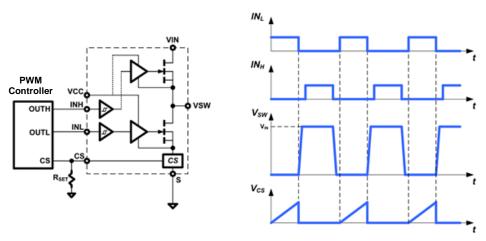

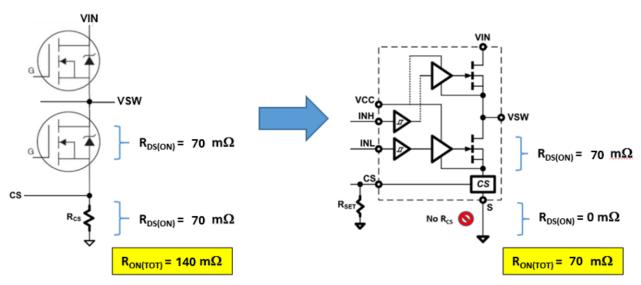

## 8.6. GaNSense<sup>™</sup> Technology Loss-Less Current Sensing

For many applications it is necessary to sense the cycle-by-cycle current flowing through the low-side GaN power FET. Existing current sensing solutions require a current sensing resistor to be placed in between the source of the low-side GaN power FET and P<sub>GND</sub>. This resistor method increases system conduction power losses, creates a hotspot on the PCB, and lowers overall system efficiency. To eliminate this external resistor and hotspot, and increase system efficiency, this GaN Half-Bridge IC includes GaNSense<sup>TM</sup> Technology for integrated and accurate loss-less current sensing. The current flowing through the internal low-side GaN power FET is sensed internally and then converted to a current at the current sensing output pin (CS). An external resistor (R<sub>SET</sub>) is connected from the CS pin to the Source (P<sub>GND</sub>) and is used to set the amplitude of the CS pin voltage signal (Fig. 29). This allows for the amplitude of the CS pin signal to be programmed so it is compatible with different controllers with different current sensing input thresholds.

Final Datasheet 17 Rev Sep. 24, 2024

Fig. 29. External resistor sensing vs. GaNSense™ Technology

To select the correct  $R_{\text{SET}}$  resistor value, the following equation (Equation 1) can be used. This equation uses the equivalent desired external current sensing resistor value ( $R_{\text{CS}}$ ), together with the gain of the internal sensing circuitry, to generate the equivalent  $R_{\text{SET}}$  resistor value. This  $R_{\text{SET}}$  value will give then give the correct voltage level at the CS pin to be compatible with the internal current sensing threshold of the system controller.

$$I_{OUT}\ Ratio = \frac{I_{DS}}{I_{CS}} = \frac{11A}{0.00125A} = 8800$$

$R_{SET} = 8800*R_{CS}$  Equation 1. R<sub>SET</sub> resistor value equation

When comparing GaNSense<sup>TM</sup> Technology versus existing external current sensing resistor method (Fig. 30), the total ON resistance, R<sub>ON(TOT)</sub>, can be substantially reduced. For a 240W high-frequency asymmetrical half-bridge (AHB) circuit, for example, R<sub>ON(TOT)</sub> is reduced from 140m to 70m. The power loss savings by eliminating the external resistor results in a +0.5% efficiency benefit for the overall system.

## **External Current Sensing Resistor Method**

Fig. 30. External current sensing resistor vs. GaNSense<sup>™</sup> Technology

Final Datasheet 18 Rev Sep. 24, 2024

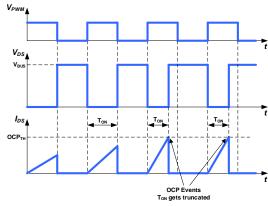

### 8.7. Over Current Protection (OCP)

This GaN Power IC includes cycle-by-cycle over-current detection and protection (OCP) circuitry to protect the GaN power FET against high current levels. During the on-time of each switching cycle, should the peak current exceed the internal OCP threshold (1.9V, typical), the internal gate drive will turn the GaN power FET off quickly and truncate the on-time period to prevent damage occurring to the IC. The IC will then turn on again at the next PWM rising edge at the start of the next on-time period (Fig. 31). This OCP protection feature will self-protect the IC each switching cycle against fast peak over current events and greatly increase the robustness and reliability of the system. The actual peak current threshold can be calculated using Equation 2 and is a function of the internal current-sensing ratio and the external R<sub>SET</sub> resistor. The internal OCP threshold (1.9V, typical) is much higher than the OCP thresholds of many popular QR, ACF and PFC controllers. This ensures good compatibility of this IC with existing controllers without OCP threshold conflicts.

Fig. 31. OCP threshold timing diagram

$$I_{OCP} = \frac{[1.9 \text{ V x } 8800]}{R_{SET}}$$

Equation 2. OCP trip current threshold equation

Final Datasheet 19 Rev Sep. 24, 2024

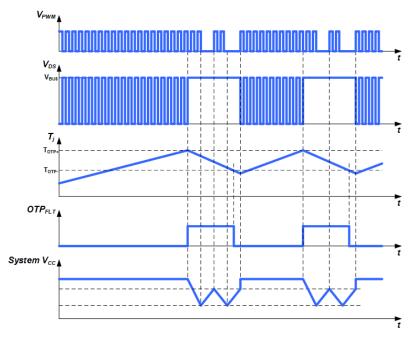

### 8.8. Over Temperature Protection (OTP)

This GaN Power IC includes over-temperature detection and protection (OTP) circuitry to protect the IC against excessively high junction temperatures ( $T_J$ ). High junction temperatures can occur due to overload, high ambient temperatures, and/or poor thermal management. Should  $T_J$  exceed the internal  $T_{OTP+}$  threshold (165C, typical) then the IC will latch off safely. When  $T_J$  decreases again and falls below the internal  $T_{OTP-}$  threshold (105C, typical), then the OTP latch will be reset. Until then, internal OTP latch is guaranteed to remain in the correct state while  $V_{CC}$  is greater than 5V. During an OTP event, this GaN IC will latch off and the system  $V_{CC}$  supply voltage will decrease due to the loss of the aux winding supply. The system  $V_{CC}$  will fall below the lower UV- threshold of the controller and the high-voltage start-up circuit will turn-on and  $V_{CC}$  will increase again (Fig. 32).  $V_{CC}$  will increase above the rising UV+ threshold and the controller will turn on again and deliver PWM pulses again.

Fig. 32. OTP threshold timing diagram

Final Datasheet 20 Rev Sep. 24, 2024

### 9. PCB Layout Guidelines

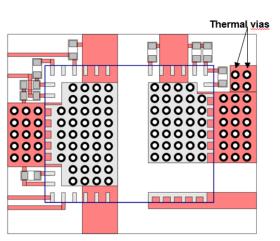

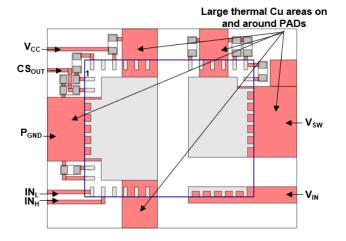

For best electrical and thermal results, these PCB layout guidelines (and 4 steps below) must be followed:

- 1) Place IC components as close as possible to the GaN IC. Place R<sub>SET</sub> resistor directly next to CS pin to minimize high frequency switching noise.

- 2) Connect the ground of IC components to Source to minimize high frequency switching noise. Connect controller ground also to Source (P<sub>GND</sub>).

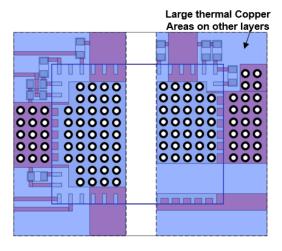

- 3) Route all connections on single layer. This allows for large thermal copper areas on other layers.

- 4) Place large copper areas on and around Pad1 and Pad2.

- 5) Place many thermal vias inside Pad1 and Pad2 and inside Pad1 and Pad2 copper areas.

Place large possible copper areas on all other PCB layers (bottom, top, mid1, mid2).

Do not extend copper planes from the low-side across the components or pads of the high-side; do not extend copper planes from the high-side across the components or pads of the low-side! Keep high and low-side layouts separate. Do not overlap!

Step 1. Place GaN IC and components on PCB. Place components as close as possible to IC

Step 3. Place many thermal vias inside source pad and inside source copper areas. (dia=0.65mm, hole=0.33mm, pitch=0.925mm, via

wall=1mil)

Step 2. Route all connections on single layer. Make large copper areas on and around Source pad

Step 4. Place large copper areas on other layers. Make all thermal copper areas as large as possible!

Final Datasheet 21 Rev Sep. 24, 2024

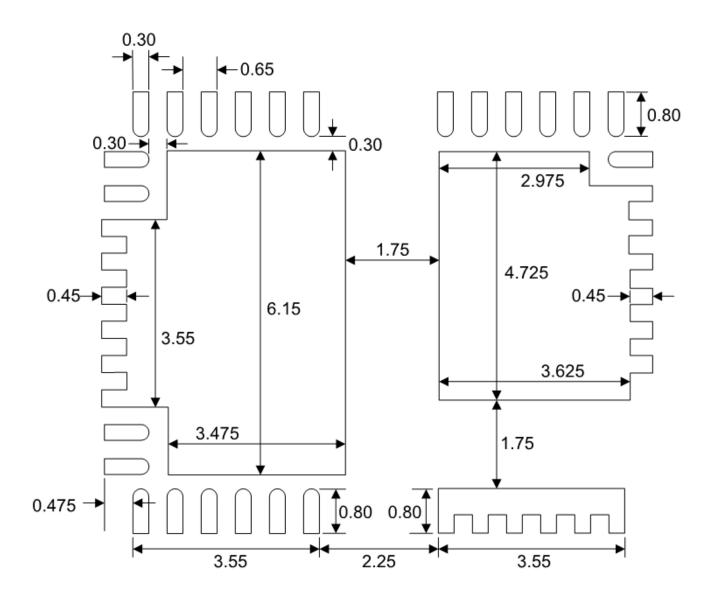

#### 10. Recommended PCB Land Pattern

Top View All dimensions are in mm

Final Datasheet 22 Rev Sep. 24, 2024

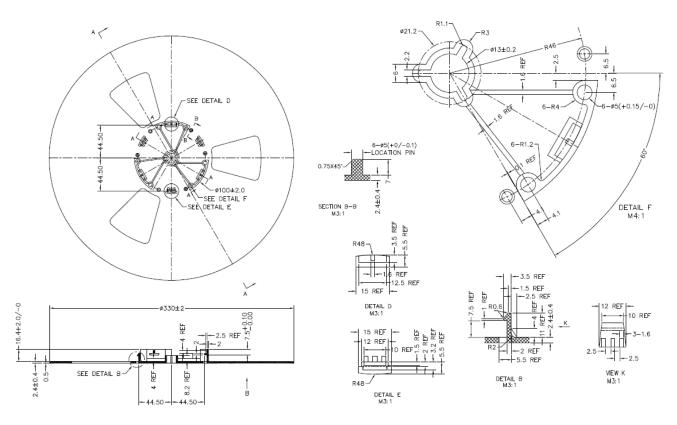

## 11. Package Outline (Power QFN)

|     |      |      |            |      |       |      |       |      |       |       |          |          | NOTES     |           | 1. DIMENSIONING AND TOLERANCING CONFORM TO ASME Y14.5M - 1994. | <ol><li>ALL DIMENSIONS ARE IN MILLIMETERS.</li></ol> | 3. MAXIMUM ALLOWABLE BURRS IS 0,050 MM IN ALL DIRECTIONS. |           |      |

|-----|------|------|------------|------|-------|------|-------|------|-------|-------|----------|----------|-----------|-----------|----------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------|-----------|------|

| MAX | 0.90 | 0.05 |            | 0.35 | 10.10 | 8.10 | 3.525 | 6.20 | 3.025 | 4.775 |          |          |           |           |                                                                |                                                      | 0,65                                                      |           | 0.30 |

| MOM | 0.85 |      | 0.203 REF. | 0.30 | 10.00 | 8.00 | 3.475 | 6,15 | 2.975 | 4,725 | 0.65 BSC | 2.55 BSC | 1.275 BSC | 0.30 REF. | 0.325 REF.                                                     | 1.75 REF.                                            | 09'0                                                      | 0.15 REF. | 0.25 |

| Z   | 0.80 | 0.00 |            | 0.25 | 9.90  | 7.90 | 3.425 | 6.10 | 2.925 | 4.675 |          |          |           | 1         | 1                                                              | 1                                                    | 0.55                                                      |           | 0.20 |

|     | Н    |      |            |      |       |      |       |      |       |       | 0        |          | Г         |           |                                                                | Г                                                    | Г                                                         |           | Г    |

23 Rev Sep. 24, 2024 Final Datasheet

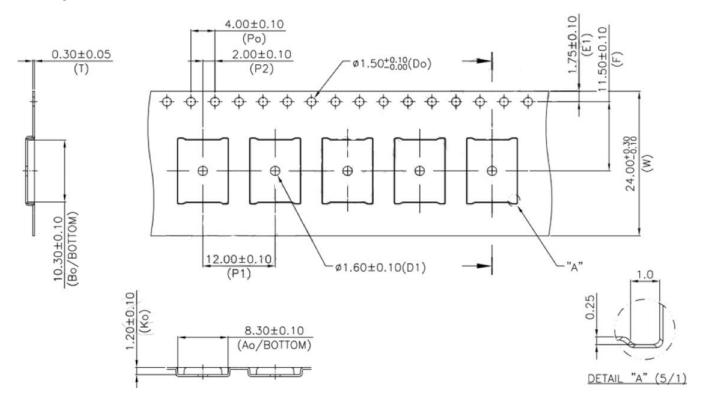

### 12. Tape and Reel Dimensions

Rev Sep. 24, 2024 Final Datasheet 24

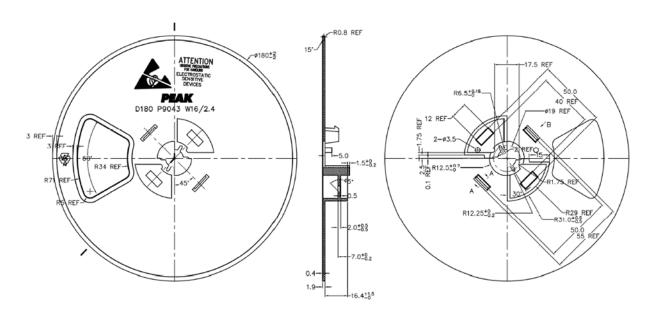

## 13. Tape and Reel Dimensions (Cont.)

#### 7" Reel

13" Reel

### 14. Ordering Information

| Part Number | Operating<br>Temperature Grade       | Storage<br>Temperature<br>Range      | Package           | MSL<br>Rating | Packing<br>(Tape & Reel) |  |

|-------------|--------------------------------------|--------------------------------------|-------------------|---------------|--------------------------|--|

| NV6269C-RA  | -55°C to +150°C<br>T <sub>CASE</sub> | -55°C to +150°C<br>T <sub>CASE</sub> | 8 x 10 mm<br>PQFN | 3             | 1000: 7" Reel            |  |

| NV6269C     | -55°C to +150°C<br>T <sub>CASE</sub> | -55°C to +150°C<br>T <sub>CASE</sub> | 8 x 10 mm<br>PQFN | 3             | 5000: 13" Reel           |  |

#### 15. 20-Year Limited Warranty

The product(s) described in this data sheet **include a** warranty period of twenty (20) years under, and subject to the terms and conditions of, Navitas' express limited product warranty, available at <a href="https://navitassemi.com/terms-conditions">https://navitassemi.com/terms-conditions</a>. The warranted specifications include only the MIN and MAX values only listed in Absolute Maximum Ratings, ESD Ratings and Electrical Characteristics sections of this datasheet. Typical (TYP) values or other specifications are not warranted.

### 16. Revision History

| Date          | Status               | Notes                                              |

|---------------|----------------------|----------------------------------------------------|

| Mar. 21, 2024 | Preliminary Revision | Graphs need to be updated                          |

| May. 13, 2024 | Prelim Update        | All data and graphs added. Theta JA to be updated. |

| Sep. 24, 2024 | Final                | Fix several typos.                                 |

#### **Additional Information**

DISCLAIMER Navitas Semiconductor (Navitas) reserves the right to modify the products and/or specifications described herein at any time and at Navitas' sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied. This document is presented only as a guide and does not convey any license under intellectual property rights of Navitas or any third parties. Navitas' products are not intended for use in applications involving extreme environmental conditions or in life support systems. Terms and Conditions.

Navitas Semiconductor, Navitas, GaNSense and associated logos are registered trademarks of Navitas.

Copyright ©2024 Navitas Semiconductor. All rights reserved

Contact info@navitassemi.com

Final Datasheet 26 Rev Sep. 24, 2024