#### GaNSense™ Power FET

- · Loss-less current sensing

- Low 330 mΩ power FET

- · Zero reverse recovery charge

- · Low output charge

- · 800 V Transient Voltage Rating

- · 700 V Continuous Voltage Rating

## **High Frequency QR Controller**

- Wide VDD range up to 77V

- · QR valley switching and optional CCM operating modes

- · High frequency operation up to 225kHz

- High voltage start-up

- Frequency hopping for low EMI

- · OVP, UVP, OTP, CSSP, SSSP protection functions

- LPS function

- Ultra-low standby current consumption (<20mW)</li>

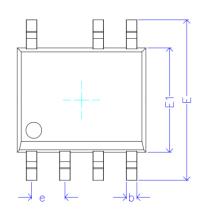

### Small, low-profile SMT ESOP 7

- · ESOP footprint, 1.27 mm profile

- · Minimized package inductance

- · Large cooling pad

#### **High Power Density**

- > 1W/cc achievable power density

- · Small transformer size

- · Low component count

#### Sustainability

- · RoHS, Pb-free, REACH-compliant

- Up to 40% energy savings vs Si solutions

- System level 4kg CO<sub>2</sub> Carbon Footprint reduction

#### **Product Reliability**

· 20-year limited product warranty (see Section 14 for details)

### 2. Topologies / Applications

- · High efficiency AC-DC power adapters

- · USB PD/QC battery charger

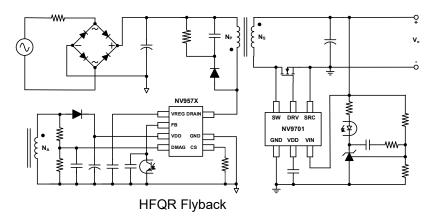

### 4. Typical Application Circuit

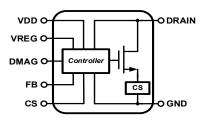

# GaNSense™ HFQR Controller

#### ESOP 7

#### Simplified schematic

· Mobile chargers, adapters, aux power

### 3. Description

This GaNSense™ HFQR/CCM controller integrates a high performance eMode GaNSense Power FET together with a Flyback controller to achieve unprecedented high-frequency and high-efficiency operation for smallest size mobile charger and adapter solutions. The GaNSense Power FET includes loss-less current sensing, ultra-low gate charge, low output charge, 700V continuous and 800V transient voltage ratings to provide excellent performance and robustness. The HFQR Flyback controller enables high frequency operation, wide VDD range, high-voltage start-up, and multi-mode operation. The Flyback controller also includes abnormal component shortcircuit, over-temperature and LPS protection features to increase system robustness, while ultra-low standby current consumption increases light, tiny & no-load efficiency. Lowprofile, low-inductance, and small footprint SMT ESOP 7 packaging enables designers to achieve simple, quick and reliable solutions. Navitas' GaN IC technology enables high frequencies, high efficiencies and low EMI to achieve unprecedented power densities at a very attractive cost structure.

## 5. Table of Contents

| 1. Features1                                           | Electrical Specifications (cont.)         | 10 |

|--------------------------------------------------------|-------------------------------------------|----|

| 2. Topologies / Applications1                          | Electrical Specifications (cont.)         | 11 |

| 3. Description1                                        | 8.4. Characteristic Graphs                | 12 |

| 4. Typical Application Circuit1                        | Characteristic Graphs (cont.)             | 13 |

| 5. Table of Contents2                                  | Characteristic Graphs (cont.)             | 14 |

| 6. Ordering Information3                               | Characteristic Graphs (Cont.)             | 15 |

| 7. Internal Functional Block Diagram4                  | 9. Pin Configurations and Marking Diagram | 16 |

| 8. Specifications5                                     | 10. Functional Description                | 17 |

| 8.1. Absolute Maximum Ratings <sup>(1)</sup> 5         | 11. Package Outline (ESOP 7)              | 25 |

| 8.2. Recommended Operating Conditions <sup>(4)</sup> 6 | 12. Tape and Reel Dimensions              | 26 |

| 8.3. Electrical Specifications7                        | 13. Tape and Reel Dimensions (Cont.)      | 27 |

| Electrical Specifications (cont.)8                     | 14. 20-Year Limited Product Warranty      | 28 |

| Electrical Specifications (cont.)9                     | 15. Revision History                      | 28 |

# 6. Ordering Information

| Part Number | Maximum<br>Frequency | Function          | Protection<br>Mode | R <sub>DS(ON)</sub> | Operating<br>Temperature<br>Range | Package | Packing<br>Method |

|-------------|----------------------|-------------------|--------------------|---------------------|-----------------------------------|---------|-------------------|

| NV9573S1P1  | 129kHz/100kHz        | PL+CC, OLP        | AR                 | 330mΩ               |                                   |         | 4.000             |

| NV9573S2P1  | 225kHz/164kHz        | PL+CC, OLP        | AR                 |                     | -40°C to<br>+125°C                | ESOP 7  | 13" Tape          |

| NV9573S121  | 129kHz/100kHz        | CCM<br>PL+CC, OLP | AR                 |                     | 120 0                             |         | & Reel            |

<sup>\*</sup>PL=Power Limit, CC=Constant Current

<sup>\*</sup>Those protection functions not mentioned in **Protection Mode** column, they are all AR (auto restart) mode.

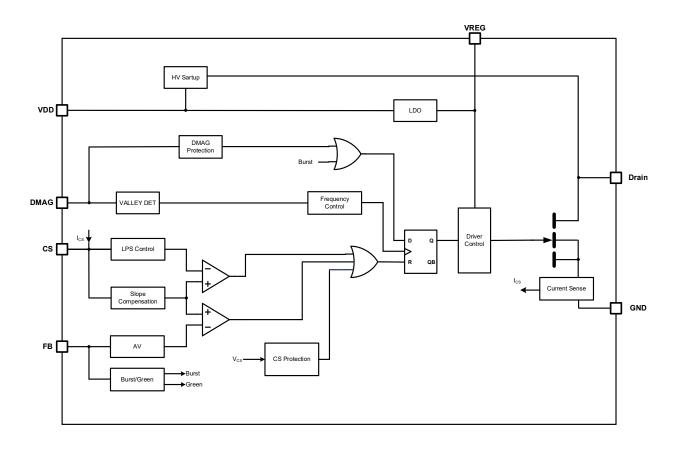

# 7. Internal Functional Block Diagram

# 8. Specifications

### 8.1. Absolute Maximum Ratings(1)

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                | Parameter                                             |                                                    |      | Max.  | Unit |

|-----------------------|-------------------------------------------------------|----------------------------------------------------|------|-------|------|

| V <sub>DS(CONT)</sub> | GaN Power FET Continuous D                            | Prain-to-Source Voltage                            | -7   | 700   | V    |

| V <sub>DS(TRAN)</sub> | GaN Power FET Transient Dra                           | ain-to-Source Voltage <sup>(2)</sup>               | -    | 800   | V    |

| V <sub>VDD</sub>      | VDD DC Supply Voltage                                 |                                                    | -0.3 | 80    | V    |

| V <sub>CS</sub>       | CS Pin Input Voltage                                  |                                                    | -0.3 | 6     | V    |

| V <sub>FB</sub>       | FB Pin Input Voltage                                  |                                                    | -0.3 | 6     | V    |

| $V_{DMAG}$            | DMAG Pin Input Voltage                                |                                                    |      | 6     | V    |

| V <sub>REG</sub>      | VREG Pin Output Voltage                               |                                                    |      | 7.5   | V    |

| I <sub>D</sub>        | GaN Power FET Continuous Drain Current (@ Tc = 100°C) |                                                    |      | 4     | Α    |

| I <sub>D</sub> PULSE  | GaN Power FET Pulsed Drain                            | Current (10 µs @ T <sub>J</sub> = 25°C)            | -    | 8     | Α    |

| θја                   | Thermal Resistance (Junction-                         | to-Ambient) <sup>(3)</sup>                         | -    | 48.29 | °C/W |

| Өлс                   | Thermal Resistance (Junction-                         | to-Case) <sup>(3)</sup>                            | -    | 2.32  | °C/W |

| TJ                    | Operating Junction Temperatu                          | re                                                 | -40  | 150   | °C   |

| T <sub>STG</sub>      | Storage Temperature Range                             |                                                    | -40  | 150   | °C   |

| TL                    | Lead Temperature (Soldering) 10 Seconds               |                                                    | -    | 260   | °C   |

| ESD                   | Electrostatic Discharge                               | Human Body Mode,<br>ANSI/ESDA/JEDEC JS-001-2017    | -    | 2.0   | kV   |

| ESD                   | Capability                                            | Charge Device Mode,<br>ANSI/ESDA/JEDEC JS-001-2018 | -    | 2.0   | kV   |

- Note (1): Absolute maximum ratings are stress ratings; devices subjected to stresses beyond these ratings may cause permanent damage.

- Note (2): V<sub>DS (TRAN)</sub> rating allows for surge ratings during non-repetitive events that are <100us (for example start-up, line interruption). V<sub>DS (TRAN)</sub> rating allows for repetitive events that are <400ns, with 80% derating required (for example repetitive leakage inductance spikes). Refer to Section "GaN Power FET Drain-to-Source Voltage Considerations" for detailed recommended design guidelines.

- Note (3): Measured on DUT mounted on 1 square inch 2 oz Cu (FR4 PCB)

Datasheet 5 Rev Sep. 20, 2024

# 8.2. Recommended Operating Conditions<sup>(4)</sup>

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance. Navitas does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol            | Parameter               | Min. | Тур. | Max. | Unit |

|-------------------|-------------------------|------|------|------|------|

| $V_{VDD}$         | VDD Pin Supply Voltage  | -0.3 |      | 75   | V    |

| Vcs               | CS Pin Supply Voltage   | -0.3 |      | 5.5  | V    |

| V <sub>FB</sub>   | FB Pin Supply Voltage   | -0.3 |      | 5.5  | V    |

| V <sub>DMAG</sub> | DMAG Pin Supply Voltage | -0.3 |      | 5.5  | V    |

| $V_{REG}$         | VREG Pin Output Voltage | -0.3 |      | 7    | V    |

Note (4): Functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied, exposure to absolute maximum rated conditions of extended periods may affect device reliability. All voltage values are with respect to the normal operation ambient temperature range is from -40°C to +125°C unless otherwise noted.

Datasheet 6 Rev Sep. 20, 2024

# 8.3. Electrical Specifications

$V_{DD}$  (Typ.) = 12V,  $T_A$  = -40°C to 125°C, and  $T_A$  (Typ.) = 25°C, unless otherwise specified.

|                                 | Parameter                                                 | Test Conditions                                                         | Min.  | Тур. | Max.  | Unit  |  |  |

|---------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------|-------|------|-------|-------|--|--|

|                                 | HV Startup Section                                        |                                                                         |       |      |       |       |  |  |

| lhv                             | HV Startup Current Drawn from Drain Pin                   | V <sub>DRAIN</sub> =50 V, V <sub>DD</sub> =0 V                          | 2     |      | 20    | mA    |  |  |

| IHV_LC                          | HV Startup Leakage Current Drawn from Drain Pin           | V <sub>DRAIN</sub> =700 V,<br>V <sub>DD</sub> =V <sub>DD_UVLO</sub> +1V |       |      | 3     | μA    |  |  |

|                                 |                                                           | VDD Section                                                             |       |      |       |       |  |  |

| $V_{DD\_ON}$                    | V <sub>DD</sub> Turn-On Threshold Voltage                 | V <sub>DD</sub> Rising                                                  | 12.5  | 13.5 | 14.5  | V     |  |  |

| $V_{DD\_UVLO}$                  | V <sub>DD</sub> UVLO Threshold Voltage                    |                                                                         | 6.2   | 6.5  | 6.8   | V     |  |  |

| V <sub>DD_DLCH</sub> (5)        | V <sub>DD</sub> Threshold for Latch<br>Release            |                                                                         | 1.2   | 1.8  | 2.2   | ٧     |  |  |

| I <sub>DD_ST</sub>              | Startup Current                                           |                                                                         | 0.5   | 2    | 5     | μA    |  |  |

| I <sub>DD_OP</sub>              | Operating Supply Current                                  | No DRV Switching                                                        | 0.60  | 0.75 | 0.90  | mA    |  |  |

| IDD_DPGN                        | Operating Supply Current in Deep Green-Mode               |                                                                         | 300   | 375  | 450   | μA    |  |  |

| t <sub>D_DPGN</sub>             | Debounce Time to Enter Deep Green Mode                    |                                                                         | 380   | 480  | 580   | μs    |  |  |

| $V_{DD\_OVP}$                   | V <sub>DD</sub> Over-Voltage-Protection Threshold         |                                                                         | 77    | 78.5 |       | V     |  |  |

| t <sub>D_UVLO</sub> (5)         | UVLO De-bounce Time                                       |                                                                         |       | 10   |       | μs    |  |  |

| $t_{D\_VDD\_OVP}$ (5)           | V <sub>DD</sub> Over-Voltage-Protection<br>De-bounce Time |                                                                         |       | 15   |       | μs    |  |  |

| t <sub>VDD_LAR</sub>            | Long Auto-Restart Mode Time                               | Trim Option                                                             | 2.08  | 2.64 | 3.20  | S     |  |  |

|                                 |                                                           | VREG Section                                                            |       |      |       | _     |  |  |

| $V_{REG}$                       | VREG output voltage                                       |                                                                         | 6.15  | 6.4  | 6.65  | V     |  |  |

| $V_{REG\_5mA}$                  | VREG with 5mA Load Current                                | I <sub>OUT</sub> = 5mA                                                  | 6.05  | 6.4  | 6.65  | V     |  |  |

|                                 | C                                                         | Scillator Section                                                       |       |      |       |       |  |  |

| fs_bnk_max_ll                   | Maximum Blanking Frequency                                | 129kHz/100kHz                                                           | 121   | 129  | 137   | kHz   |  |  |

|                                 | at Low Line Input Voltage                                 | 225kHz/164kHz                                                           | 202.5 | 225  | 247.5 | kHz   |  |  |

| fs_bnk_max_hl                   | Maximum Blanking Frequency                                | 129kHz/100kHz                                                           | 93    | 100  | 107   | kHz   |  |  |

| TO_BINIT_INIAX_TIE              | at High Line Input Voltage                                | 225kHz/164kHz                                                           | 147.2 | 164  | 180   | kHz   |  |  |

| f <sub>S_BNK_MAX_CCM</sub>      | Maximum Blanking Frequency in CCM                         | 129kHz/100kHz                                                           | 93    | 100  | 107   | kHz   |  |  |

| fs_tmo                          | Minimum Time-Out PWM Frequency                            |                                                                         | 23    | 25   | 27    | kHz   |  |  |

| ton max                         | Maximum PWM ON Time                                       | 129kHz/100kHz                                                           | 16.6  | 18   | 19.4  | μs    |  |  |

|                                 |                                                           | 225kHz/164kHz                                                           | 9.5   | 10.5 | 11.5  | μs    |  |  |

| D <sub>MAX</sub>                | Maximum Duty Cycle                                        |                                                                         | 72    | 75   | 78    | %     |  |  |

| m <sub>slp</sub> <sup>(5)</sup> | Slope Compensation                                        |                                                                         |       | 60   |       | mv/µs |  |  |

| $\Delta V_{JIT}{}^{(5)}$        | Current Sense Jitter Range                                |                                                                         |       | 10   |       | %     |  |  |

| T <sub>JIT</sub> <sup>(5)</sup> | Frequency Jitter Period                                   |                                                                         |       | 0.64 |       | ms    |  |  |

$V_{DD}$  (Typ.) = 12V,  $T_A$  = -40°C to 125°C, and  $T_A$  (Typ.) = 25°C, unless otherwise specified.

|                                         | Parameter                                                  |                                              | Min.  | Тур.  | Max.  | Unit |  |  |

|-----------------------------------------|------------------------------------------------------------|----------------------------------------------|-------|-------|-------|------|--|--|

|                                         | Feedback Section                                           |                                              |       |       |       |      |  |  |

| $V_{FB\_OPEN}$                          | FB Open Voltage                                            |                                              | 4.7   | 5.2   |       | V    |  |  |

| $Z_FB$                                  | FB Pull Up Resistor                                        |                                              | 36    | 42    | 48    | kΩ   |  |  |

| Vfb_olp                                 | FB Threshold for OLP                                       |                                              | 3.4   | 3.5   | 3.6   | V    |  |  |

| TD_OLP <sup>(5)</sup>                   | OLP Protection De-bounce time                              |                                              |       | 36    |       | ms   |  |  |

| A <sub>V_HV</sub> <sup>(5)</sup>        | FB Voltage Attenuation<br>Factor at High Output<br>Voltage | 129kHz/100kHz<br>(V <sub>DMAG</sub> > 1.75V) |       | 0.225 |       | V/V  |  |  |

| A <sub>V_LV</sub> (5)                   | FB Voltage Attenuation<br>Factor at Low Output<br>Voltage  | 129kHz/100kHz<br>(V <sub>DMAG</sub> < 1.6V)  |       | 0.200 |       | V/V  |  |  |

| A <sub>V</sub> <sup>(5)</sup>           | FB Voltage Attenuation Factor                              | 225kHz/164kHz                                |       | 0.175 |       | V/V  |  |  |

| V <sub>FB_BST_ENT</sub>                 | FB Threshold for Burst<br>Mode Entry                       |                                              | 0.50  | 0.55  | 0.60  | V    |  |  |

| V <sub>FB_BST_EXT</sub>                 | FB Threshold for Burst<br>Mode Exit                        |                                              | 0.55  | 0.60  | 0.65  | V    |  |  |

| $V_{FB\_BNK\_STR}$                      | Frequency Foldback Start Point                             | 129kHz/100kHz                                | 2.240 | 2.300 | 2.380 | V    |  |  |

| Vfb_bnk_str_l                           | Frequency Foldback Start Point at Low Line Input Voltage   | 225kHz/164kHz                                | 2.592 | 2.692 | 2.792 | V    |  |  |

| Vfb_bnk_str_h                           | Frequency Foldback Start Point at High Line Input Voltage  | 225kHz/164kHz                                | 3.058 | 3.158 | 3.258 | V    |  |  |

| V ·                                     | Frequency Foldback End Point at Low Line Input             | 129kHz/100kHz                                | 1.340 | 1.394 | 1.480 | V    |  |  |

| Vfb_bnk_end_l                           | Voltage                                                    | 225kHz/164kHz                                | 1.054 | 1.154 | 1.254 | V    |  |  |

| V                                       | Frequency Foldback End<br>Point at High Line Input         | 129kHz/100kHz                                | 1.390 | 1.456 | 1.530 | V    |  |  |

| Vfb_bnk_end_h                           | Voltage                                                    | 225kHz/164kHz                                | 1.051 | 1.151 | 1.251 | V    |  |  |

| V <sub>FB_</sub> CSMIN_H <sup>(5)</sup> | V <sub>CS_MIN</sub> Foldback High<br>Threshold Voltage     | 225kHz/164kHz                                | 1.450 | 1.500 | 1.550 | V    |  |  |

| Vfb_csmin_l <sup>(5)</sup>              | V <sub>CS_MIN</sub> Foldback Low<br>Threshold Voltage      | 225kHz/164kHz                                | 0.725 | 0.750 | 0.775 | V    |  |  |

$V_{DD}$  (Typ.) = 12V,  $T_A$  = -40°C to 125°C, and  $T_A$  (Typ.) = 25°C, unless otherwise specified.

|                              | Parameter                                                 | Test Conditions          | Min.  | Тур.  | Max.  | Unit  |

|------------------------------|-----------------------------------------------------------|--------------------------|-------|-------|-------|-------|

|                              |                                                           | DMAG Section             |       |       |       |       |

| Idmag_max                    | Maximum Guaranteed Operating Current Flow Out of DMAG Pin |                          | 1.94  |       |       | mA    |

| I <sub>DMAG_BRI</sub>        | Current Threshold for Brown-In                            |                          | 0.432 | 0.480 | 0.528 | mA    |

| N <sub>BRI</sub>             | Debounce Cycle for Brown-In                               |                          |       | 4     |       | Cycle |

| I <sub>DMAG_BRO</sub>        | Current Threshold for Brown-Out                           |                          | 0.324 | 0.360 | 0.396 | mA    |

| t <sub>D_BRO</sub>           | Debounce Cycle for Brown-Out                              |                          | 14.5  | 16.5  | 18.5  | ms    |

| I <sub>DMAG_HL</sub>         | Current Threshold for High Line                           |                          | 1.008 | 1.120 | 1.232 | mA    |

| N <sub>HL_ENT</sub>          | Debounce Cycle for High Line Entry                        |                          |       | 4     |       | Cycle |

| I <sub>DMAG_LL</sub>         | Current Threshold for Low Line                            |                          | 0.936 | 1.040 | 1.144 | mA    |

| t <sub>D-LL_ENT</sub>        | Debounce Cycle for Low Line Entry                         |                          | 14.5  | 16.5  | 18.5  | ms    |

| t <sub>DMAG_BNK_L</sub>      | DMAG Sampling Blanking<br>Time                            | (V <sub>FB</sub> < 1.5V) | 0.85  | 1.00  | 1.15  | μs    |

| tdmag_bnk_m                  | DMAG Sampling Blanking<br>Time                            | (V <sub>FB</sub> > 1.6V) | 1.28  | 1.50  | 1.73  | μs    |

| V <sub>DMAG_HV</sub>         | V <sub>DMAG</sub> Threshold for High Output               |                          | 1.65  | 1.75  | 1.85  | V     |

| V <sub>DMAG_LV_HYS</sub> (5) | V <sub>DMAG</sub> Hysteresis<br>Threshold for Low Output  |                          |       | 0.15  |       | V     |

| $V_{DMAG\_UVP}$              | V <sub>DMAG</sub> Under-Voltage-<br>Protection Threshold  |                          | 0.390 | 0.425 | 0.460 | V     |

| N <sub>DMAG_UVP</sub> (5)    | Debounce Cycle for VDMAG_UVP                              | _                        |       | 2     |       | Cycle |

| tvdmag_uvp_bnk               | V <sub>DMAG_UVP</sub> Blanking Time<br>during Start-up    |                          | 25    | 32    | 36    | ms    |

| V <sub>DMAG_OVP</sub>        | V <sub>DMAG</sub> Over-Voltage-<br>Protection Threshold   |                          | 3.45  | 3.55  | 3.65  | V     |

| N <sub>DMAG_OVP</sub> (5)    | Debounce Cycle for V <sub>DMAG_OVP</sub>                  |                          |       | 2     |       | Cycle |

$V_{DD}$  (Typ.) = 12V,  $T_A$  = -40°C to 125°C, and  $T_A$  (Typ.) = 25°C, unless otherwise specified.

| Parameter           |                                                                                           | Test Conditions      | Min.  | Тур.  | Max.  | Unit  |  |  |

|---------------------|-------------------------------------------------------------------------------------------|----------------------|-------|-------|-------|-------|--|--|

|                     | Current Sense Section                                                                     |                      |       |       |       |       |  |  |

| Gaincs              | Current Sense Ratio                                                                       | T <sub>A</sub> =25°C | 1600  | 1725  | 1850  | A/A   |  |  |

| Vcs_LIM             | Maximum Current<br>Sense Limit                                                            |                      | 0.620 | 0.650 | 0.680 | V     |  |  |

| Vcs_min_h           | Minimum Current<br>Sense Limit at High<br>Output Voltage                                  |                      | 0.190 | 0.225 | 0.260 | V     |  |  |

| Vcs_min_l           | Minimum Current Sense Limit at Low Output Voltage                                         |                      | 0.140 | 0.175 | 0.210 | V     |  |  |

| Vcs_min_fb_str_ll_h | Feedback of V <sub>CS_MIN</sub> Foldback Start Point at Low Line and High Output Voltage  | 225kHz/164kHz        | 0.380 | 0.425 | 0.470 | V     |  |  |

| Vcs_min_fb_str_ll_l | Feedback of V <sub>CS_MIN</sub> Foldback Start Point at Low Line and Low Output Voltage   | 225kHz/164kHz        | 0.330 | 0.375 | 0.420 | V     |  |  |

| Vcs_min_fb_str_hl_h | Feedback of V <sub>CS_MIN</sub> Foldback Start Point at High Line and High Output Voltage | 225kHz/164kHz        | 0.480 | 0.525 | 0.570 | V     |  |  |

| Vcs_min_fb_str_hl_l | Feedback of Vcs_min<br>Foldback Start Point<br>at High Line and Low<br>Output Voltage     | 225kHz/164kHz        | 0.430 | 0.475 | 0.510 | V     |  |  |

| t <sub>LEB</sub>    | Leading Edge<br>Blanking Time                                                             |                      | 220   | 295   | 370   | ns    |  |  |

| t <sub>PD</sub>     | Propagation Delay                                                                         |                      |       | 30    | 45    | ns    |  |  |

| V <sub>CSSP</sub>   | CS Threshold for CS<br>Short Circuit<br>Protection                                        |                      | 0.095 | 0.125 | 0.155 | V     |  |  |

| Ncs_cssp (5)        | Debounce Cycle for<br>CSSP Protection<br>Trigger                                          |                      |       | 2     |       | Cycle |  |  |

| Vcs_sssp            | CS Threshold for SSSP                                                                     |                      | 0.95  | 1.00  | 1.05  | V     |  |  |

| Ncs_sssp (5)        | Debounce Cycle for<br>SSSP Protection<br>Trigger                                          |                      |       | 2     |       | Cycle |  |  |

| t <sub>D_SSSP</sub> | Debounce Time for<br>SSSP Protection<br>Trigger                                           |                      | 90    | 125   | 200   | ns    |  |  |

Datasheet 10 Rev Sep. 20, 2024

$V_{DD}$  (Typ.) = 12V,  $T_A$  = -40°C to 125°C, and  $T_A$  (Typ.) = 25°C, unless otherwise specified.

|                                   | Parameter                                                        | Test Conditions                                 | Min.        | Тур.   | Max. | Unit |  |

|-----------------------------------|------------------------------------------------------------------|-------------------------------------------------|-------------|--------|------|------|--|

|                                   | Over-Temperature Protection Section                              |                                                 |             |        |      |      |  |

| T <sub>OTP</sub> <sup>(5)</sup>   | Over-Temperature-<br>Protection Threshold                        |                                                 | 125         | 140    |      | °C   |  |

| ΔT <sub>OTP</sub> <sup>(5)</sup>  | Over-Temperature-<br>Protection Hysteresis                       |                                                 |             | 20     |      | °C   |  |

|                                   |                                                                  | GaN Power FET Section                           |             |        |      |      |  |

| Typical conditions                | : V <sub>DS</sub> = 400V, F <sub>SW</sub> = 1MHz, T <sub>A</sub> | $_{MB}$ = 25°C, $I_{D}$ = 2A, unless other      | erwise spec | cified |      |      |  |

| I <sub>DSS</sub>                  | Drain-Source Leakage<br>Current                                  | V <sub>DS</sub> = 700V, PWM off                 |             | 0.15   | 25   | μA   |  |

| R <sub>DS(ON)</sub>               | Drain-Source Resistance                                          | PWM on, I <sub>D</sub> = 2 A                    |             | 330    | 462  | mΩ   |  |

| V <sub>SD</sub>                   | Source-Drain Reverse<br>Voltage                                  | V <sub>PWM</sub> = 0 V, I <sub>SD</sub> = 2A    |             | 3.5    | 5    | V    |  |

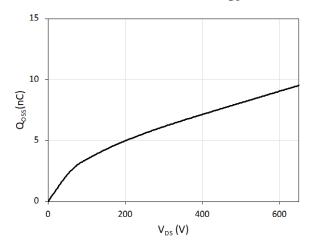

| Qoss                              | Output Charge                                                    |                                                 |             | 7.2    |      | nC   |  |

| Q <sub>RR</sub>                   | Reverse Recovery<br>Charge                                       |                                                 |             | 0      |      | nC   |  |

| Coss                              | Output Capacitance                                               | V <sub>DS</sub> = 400 V, V <sub>PWM</sub> = 0 V |             | 9.7    |      | pF   |  |

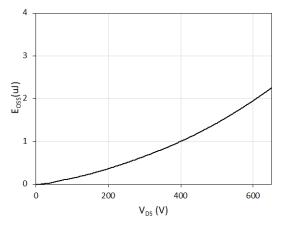

| C <sub>O(er)</sub> <sup>(6)</sup> | Effective Output<br>Capacitance, Energy<br>Related               | V <sub>DS</sub> = 400 V, V <sub>PWM</sub> = 0 V |             | 13     |      | pF   |  |

| C <sub>O(tr)</sub> (6)            | Effective Output Capacitance, Time Related                       | V <sub>DS</sub> = 400 V, V <sub>PWM</sub> = 0 V |             | 18     |      | pF   |  |

Note (5): Guaranteed by design

Note (6):  $C_{O(er)}$  is a fixed capacitance that gives the same stored energy as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 400 V

Note (6):  $C_{O(tr)}$  is a fixed capacitance that gives the same charging time as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 400 V

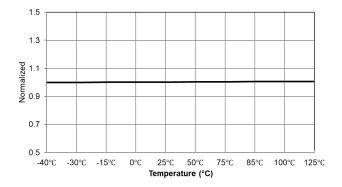

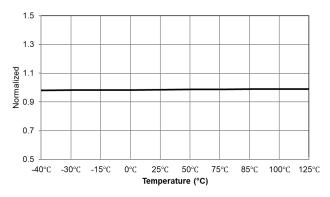

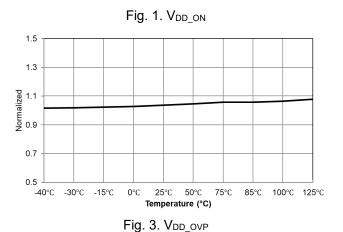

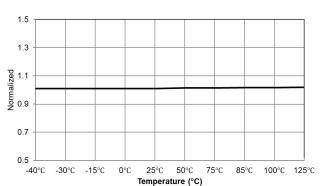

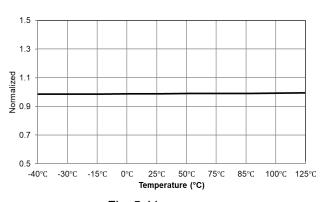

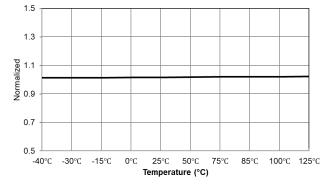

## 8.4. Characteristic Graphs

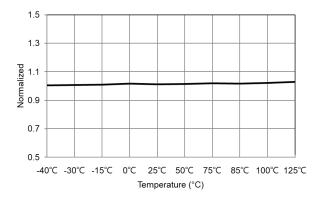

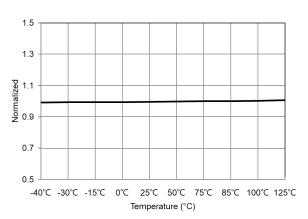

( $T_C$  = -40 to 125 °C unless otherwise specified)

Fig. 2. VDD\_UVLO

Fig. 4. fs\_tmo

Fig. 5. VFB\_BST\_ENT

Fig. 6. V<sub>FB\_BST\_EXT</sub>

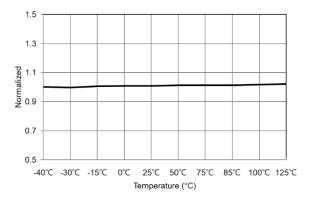

# **Characteristic Graphs (cont.)**

(T<sub>C</sub> = -40 to 125 °C unless otherwise specified)

Fig. 7. IDMAG\_BRI

Fig. 9. VDMAG\_UVP

Fig. 11. V<sub>CS\_LIM\_H</sub>

Fig. 8. IDMAG\_BRO

Fig. 10. VDMAG\_OVP

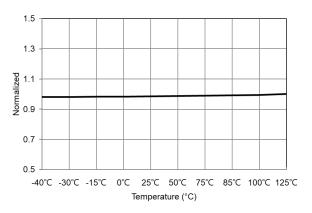

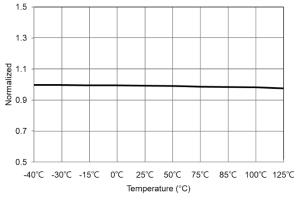

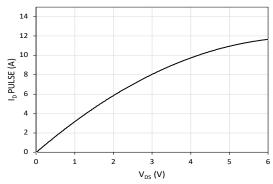

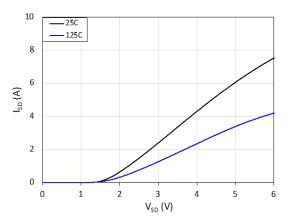

## **Characteristic Graphs (cont.)**

(GaN Power FET, T<sub>C</sub> = 25 °C unless otherwise specified)

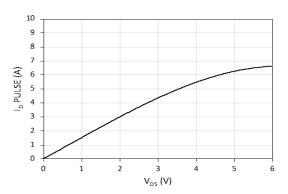

Fig. 12. Pulsed Drain current ( $I_D$  PULSE) vs. drain-to-source voltage ( $V_{DS}$ ) at T = 25 °C

Fig.14. Source-to-drain reverse conduction voltage

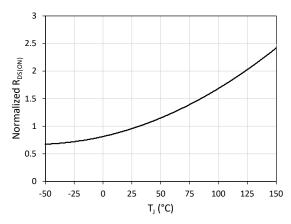

Fig.16. Normalized on-resistance ( $R_{\text{DS(ON)}}$ ) vs. junction temperature (T<sub>i</sub>)

Fig. 13. Pulsed Drain current ( $I_D$  PULSE) vs. drain-to-source voltage ( $V_{DS}$ ) at T = 125 °C

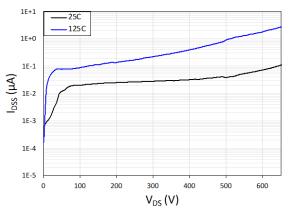

Fig.15. Drain-to-source leakage current ( $I_{DSS}$ ) vs. drain-to-source voltage ( $V_{\rm DS}$ )

# **Characteristic Graphs (Cont.)**

(GaN Power FET,  $T_C$  = 25 °C unless otherwise specified)

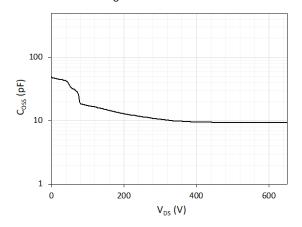

Fig.17. Output capacitance ( $C_{\rm OSS}$ ) vs. drain-to-source voltage  $(V_{DS})$

Fig.19. Charge stored in output capacitance (Q<sub>OSS</sub>) vs. drain-to-source voltage  $(V_{DS})$

Fig.18. Energy stored in output capacitance (E<sub>oss</sub>) vs. drain-to-source voltage  $(V_{DS})$

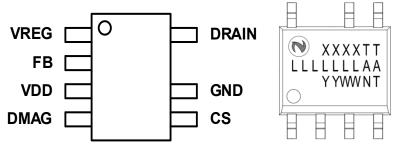

# 9. Pin Configurations and Marking Diagram

Fig. 20. Pin Configuration (Top View)

| Symbol  | Content             |  |  |  |

|---------|---------------------|--|--|--|

| XXXX    | Part Number         |  |  |  |

| TT      | Optional Trim Code  |  |  |  |

| LLLLLLL | Lot Number          |  |  |  |

| AA      | Die Run Code Number |  |  |  |

| YY      | Year Code           |  |  |  |

| WW      | Week Code           |  |  |  |

| N       | Supplier Code       |  |  |  |

| Т       | Optional Trim Code  |  |  |  |

| Pin No. | Name  | Description                                                                                                                                                                                                                                                  |

|---------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VREG  | <b>LDO Output</b> . Typically, this pin is connected to an external capacitor with recommended value = 100nF to 1uF.                                                                                                                                         |

| 2       | FB    | Feedback. Input for the internal PWM comparator.                                                                                                                                                                                                             |

| 3       | VDD   | <b>Power Supply</b> . IC operation current and GaN FET driving current are supplied through this pin. Typically, this pin is connected to external V <sub>DD</sub> capacitor. The device starts to operate when V <sub>DD</sub> exceeds V <sub>DD_ON</sub> . |

| 4       | DMAG  | <b>Demagnetization Sense</b> . This pin is used to detect resonant valleys for QR switching. It also detects the output voltage information, as well as the input voltage information for Brown-in & Brown-out protection.                                   |

| 5       | CS    | <b>Current Sense.</b> This pin detects the integrated GaN sense FET current cycle by cycle when connected to a current-sense resistor. There is a current ratio between Idrain and Ics                                                                       |

| 6       | GND   | <b>Ground.</b> Source of power FET and IC supply ground. Metal pad on bottom of package.                                                                                                                                                                     |

| 8       | Drain | <b>Drain of GaN Power FET.</b> This pin is also connected internally to high-voltage startup circuit.                                                                                                                                                        |

### 10. Functional Description

The following functional description contains additional information regarding the IC operating modes and pin functionality.

NV9573

### **Basic Operation**

NV957x family ICs are offline flyback regulator which operate in frequency limit quasi-resonant (QR) mode to reduce switching losses and EMI (electromagnetic interference). It regulates the output based on the load condition through feedback circuitry.

The QR resonant frequency is determined by the transformer primary inductance ( $L_p$ ) and the primary side GaN FET effective output capacitance ( $C_{oss-eff}$ ).

$$C_{oss-eff} = C_{oss-GaNFET} + C_{parasitic} + C_{transformer}$$

(Equation 1)

$$t_{resonance} = 2\pi \sqrt{L_p \times C_{oss-eff}}$$

(Equation 2)

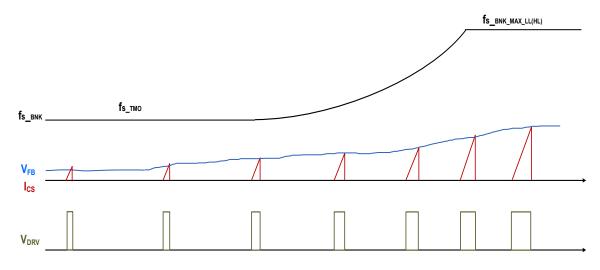

In a general 957x family design, at no load or light load condition, the frequency limit  $f_{S\_BNK}$  for the pulse to pulse operating frequency is  $f_{S\_TMO}$ . So operating frequency is between  $f_{S\_TMO}$  and  $1/(1/f_{S\_TMO} + t_{resonance})$ . At the medium load condition (e.g. 25%~50% of full load), the frequency limit  $f_{S\_BNK}$  is modulated as a function of load current such that it varies between  $f_{S\_TMO}$  and  $f_{S\_BNK\_MAX\_LL(HL)}$  as load varies. At the heavy load condition (e.g. 50%~100% of full load),  $f_{S\_BNK}$  is fixed at  $f_{S\_BNK\_MAX\_LL(HL)}$  such that the switching frequency is not higher than  $f_{S\_BNK\_MAX\_LL(HL)}$  as shown in Figure 21.

NV957x family ICs also have option to operate in CCM at low line. When the device enters CCM, the maximum CCM frequency limit is fs\_BNK\_MAX\_CCM.

Figure 21 Frequency Fold-Back Operation

Datasheet 17 Rev Sep. 20, 2024

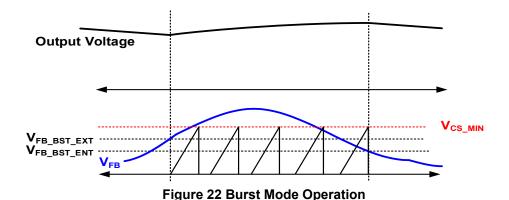

#### **Burst Mode**

As shown in Figure 22, when feedback voltage V<sub>FB</sub> drops below V<sub>FB\_BST\_ENT</sub> at light load, the PWM output shuts off and the output voltage drops at a rate depending on the load current level. Thereafter, feedback voltage V<sub>FB</sub> rises. Once V<sub>FB</sub> exceeds V<sub>FB\_BST\_EXT</sub>, NV957x family products resume switch, and the switch peak currents is limited by V<sub>CS\_MIN</sub>. If more power is delivered to the load than required, V<sub>FB</sub> voltage will decrease. Once V<sub>FB</sub> voltage is pulled below V<sub>FB\_BST\_ENT</sub>, switching stops again. In this manner, the burst mode operation alternately enables and disables switching of the GaN FET to regulate the output and in the meanwhile reduce the switching losses.

#### **Deep Green Mode**

NV957x family ICs enter the deep green mode if  $V_{FB}$  voltage stays below  $V_{FB\_BST\_ENT}$  for more than  $t_{D\_DPGN}$ . In the deep green mode, the IC operating current is reduced to  $I_{DD\_DPGN}$  to minimize power consumption. IC resumes switching with normal operating current  $I_{DD\_OP}$  once  $V_{FB}$  voltage rises above  $V_{FB\_BST\_EXT}$ .

#### **Valley Detection**

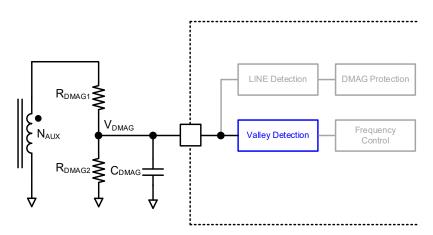

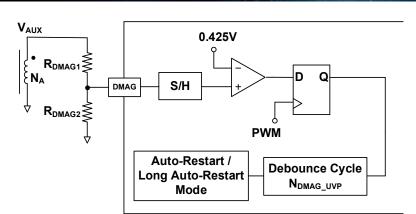

NV957x family valley detection is achieved by monitoring  $V_{DMAG}$  voltage, which is the divided auxiliary winding voltage by  $R_{DMAG1}$  and  $R_{DMAG2}$  as shown in Figure 23. One ceramic capacitor ( $C_{DMAG}$ ) with typical value 10pF (and not bigger than 22pF) is recommended to filter out the noise if there is PCB noise coupling concern.

**Figure 23 Valley Detection Circuit**

Datasheet 18 Rev Sep. 20, 2024

### **Inherent Frequency Jitter**

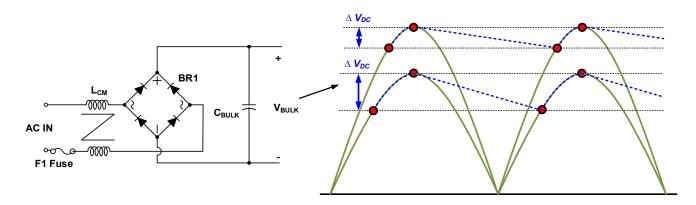

In flyback application, the DC ripple ( $\Delta VDC$ ) of bulk capacitor at the low line application is larger than at the high line application as shown in Figure 24. This large DC ripple will result in switching frequency variation for a valley switched converter. The frequency variation scatters EMI noise over the nearby frequency band, allowing compliance with EMI requirement easily. Therefore, the EMI performance at the low line application is easy to comply with EMI limitation naturally. However, at the high line application, the DC ripple is relatively small and consequently the EMI performance may suffer. To maintain good EMI performance across over the universal input, a frequency jitter is implemented in the NV957x family products.

Figure 24 Inherent Frequency Jitter

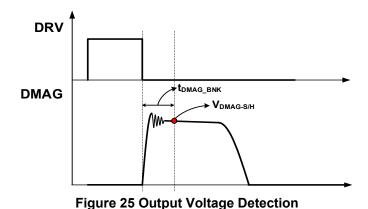

#### **Output Voltage Detection**

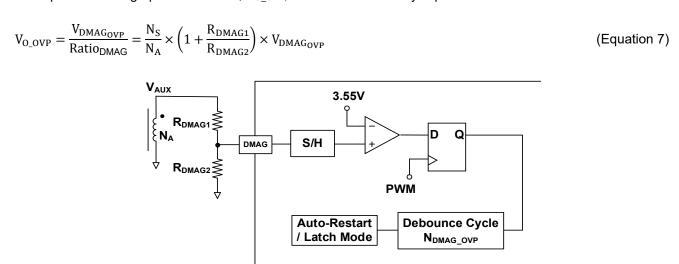

NV957x family products detect output voltage through DMAG voltage. Figure 25 shows the DMAG voltage (VDMAGs/H) is sampled at the end of tomag BNK to avoid sampling error. The DMAG voltage is set based on the transformer turn ratio, the voltage divider resistors RDMAG1 & RDMAG2. The ratio (RatioDMAG) between VDMAG-S/H and Vo can be defined as:

$$Ratio_{DMAG} = \frac{V_{DMAG-S/H}}{V_{O}} = \frac{N_{A}}{N_{S}} \times \frac{R_{DMAG2}}{R_{DMAG1} + R_{DMAG2}} \tag{Equation 3}$$

Ratiodmag is required to be designed to guarantee Vo nominal operation will not hit protections, i.e., VDMAG-S/H will not hit either VDMAG-OVP or VDMAG-UVP described in protection section. For USB-PD/PPS application, a typical recommended Ratiodmag design is 0.16.

**Datasheet** 19 Rev Sep. 20, 2024

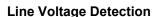

As illustrated in Figure 26, NV957x family products indirectly sense the line voltage through DMAG pin during GaN FET turn-on period. During the GaN FET conduction time, the line voltage detector clamps DMAG pin voltage at 0V. The auxiliary winding voltage, V<sub>AUX</sub>, is proportional to the input bulk capacitor voltage, V<sub>BLK</sub>. So current I<sub>DMAG</sub> flowing out of DMAG pin is expressed as:

$$I_{DMAG} = \frac{V_{BLK}}{R_{DMAG1}} \times \frac{N_A}{N_P}$$

(Equation 4)

I<sub>DMAG</sub> current, reflecting the line voltage information, is used for the brown-in and brown-out protection.

**Figure 26 Line Voltage Detection Circuit**

#### **LPS Function**

The NV957x family products incorporate built-in circuits to limit output power (PL) and limit output current (CC) in the event of the protocol IC becoming malfunction.

### **Cycle by Cycle Current Limit**

Under certain operation condition, such as the startup or the overload condition, the feedback control loop can be saturated and is unable to control the primary peak current. To limit the current under such conditions, NV957x family products incorporate the cycle by cycle current limit function which forces the GaN switch turn off when CS pin voltage reaches the current limit threshold V<sub>CS\_LIM</sub>.

#### Start-up

During startup, the internal HV startup circuit is enabled, and the input voltage supplies the current,  $I_{HV}$ , to charge hold-up capacitor  $C_{VDD}$ . When  $V_{DD}$  voltage reaches  $V_{DD\_ON}$ , the HV startup circuit is disabled. The IC starts PWM switching and senses DMAG signal to check the brown-in condition. If the brown-in is not detected, the IC enters the auto-restart mode. The internal startup circuit is connected to the Drain pin inside.

Datasheet 20 Rev Sep. 20, 2024

### **Protection Description**

NV957x family products protection functions include VDD over-voltage protection (VDD-OVP), Brown-in/out protection, DMAG over-voltage protection (DMAG-OVP), DMAG under-voltage protection (DMAG-UVP), Overload protection (OLP), IC internal over-temperature protection (OTP) etc. All protections have auto-restart mode option. The DMAG-OVP can be configured with auto-restart or latch mode. The DMAG-UVP can be configured with auto-restart or long auto-restart mode. The protection function information is provided on page 3.

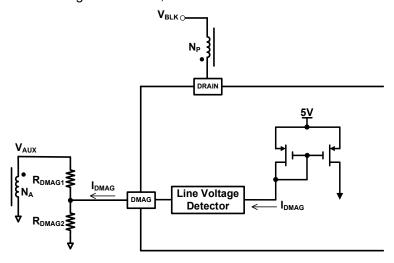

When the long auto-restart mode protection is triggered, the integrated GaN FET is turned off for a period of  $t_{VDD\_LAR}$ . After  $t_{VDD\_LAR}$ , if VDD rises above  $V_{DD\_ON}$ , NV957x family products resume normal operation as shown in Figure 27.

Figure 27 Auto-Restart Long AR Mode

#### **VDD-OVP**

VDD-OVP prevents IC damage from over voltage stress when abnormal system conditions occur. When VDD voltage exceeds V<sub>DD\_OVP</sub> for the debounce time t<sub>D\_VDD\_OVP</sub>, the VDD-OVP protection is triggered, the device enters the auto-restart mode.

### **Brown-in & Brown-out**

The sensed line voltage information is used for the brown-in and brown-out protection. During GaN FET conduction time, when the current, I<sub>DMAG</sub>, flowing out of DMAG pin is higher than I<sub>DMAG\_BRI</sub> for N<sub>BRI</sub> debounce cycles, the brown-in is enabled. The input bulk capacitor voltage level to enable the brown-in is given as

$$V_{\text{BLK\_Brownin}} = I_{\text{DMAG\_BRI}} \times \frac{R_{\text{DMAG1}}}{N_{\text{A}}/N_{\text{P}}} \tag{Equation 5}$$

When  $I_{DMAG}$  is lower than  $I_{DMAG\_BRO}$  for longer than  $t_{D\_BRO}$ , the brown-out is triggered. The input bulk capacitor voltage level to trigger the brown-out protection is given as

$$V_{\text{BLK\_Brownout}} = I_{\text{DMAG\_BRO}} \times \frac{R_{\text{DMAG1}}}{N_{\text{A}}/N_{\text{P}}}$$

(Equation 6)

Datasheet 21 Rev Sep. 20, 2024

### **IC Internal OTP**

The internal temperature-sensing circuit disables the PWM output if the junction temperature exceeds Totp, and the IC enters protection mode.

### **DMAG-OVP**

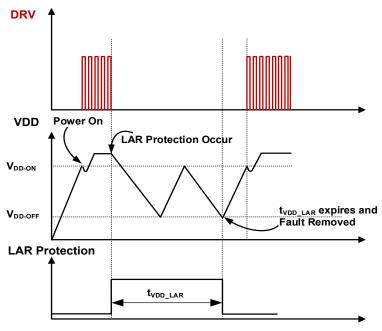

DMAG-OVP prevents server system damage when abnormal system conditions occur and cause DMAG voltage rising abnormally. Usually, DMAG over voltage protection is caused by not working properly feedback network (FB) or a fault condition of the DMAG voltage divider resistors. Figure 28 shows the internal circuit of DMAG-OVP. When abnormal system conditions occur and cause DMAG voltage to exceed V<sub>DMAG\_OVP</sub> for more than N<sub>DMAG\_OVP</sub> consecutive switching cycles, PWM pulses are disabled, and the IC enters the auto-restart mode or the latch mode. For DMAG voltage divider design, R<sub>DMAG1</sub> is obtained from Equation 5, and R<sub>DMAG2</sub> is determined by Equation 3. The output over voltage protection level, V<sub>O\_OVP</sub>, can be determined by Equation 7.

Figure 28 DMAG Over Voltage Protection Circuit

#### **DMAG-UVP**

In the event with shorted output, the output voltage will drop, and the primary peak current will increase. To prevent operation for a long time under this condition, NV957x family products incorporate the under voltage protection through DMAG pin (DMAG-UVP). Figure 29 shows the internal circuit for DMAG-UVP. When DMAG voltage is less than V<sub>DMAG\_UVP</sub> and longer than de-bounce cycles N<sub>DMAG\_UVP</sub>, DMAG UVP is triggered, and the IC enters the autorestart mode or the long auto-restart mode.

The output under voltage protection level, V<sub>O\_UVP</sub>, can be determined by Equation 8.

$$V_{O\_UVP} = \frac{V_{DMAG_{UVP}}}{Ratio_{DMAG}} = \frac{N_S}{N_A} \times (1 + \frac{R_{DMAG1}}{R_{DMAG2}}) \times V_{DMAG\_UVP}$$

(Equation 8)

To avoid DMAG-UVP triggering during the startup sequence, startup blanking time tvDMAG\_UVP\_BNK is incorporated for system power on.

Datasheet 22 Rev Sep. 20, 2024

**Figure 29 DMAG Under Voltage Protection Circuit**

#### **Current Sense Short Protection (CSSP)**

NV957x family has CSSP function. When abnormal system conditions occur, in case after debounce time CS pin voltage is still lower than Vcssp, the GaN switch turn on time will be limited to limit output power. If this status maintains consecutive Ncs\_cssp switching cycles, The IC enters auto-restart mode.

#### **Secondary Side Short Protection (SSSP)**

When the secondary-side rectifier is abnormally shorted, the primary-side switch current will increase dramatically within the leading-edge blanking time. To limit the switch current during such conditions, NV957x family products incorporate SSSP function which forces the GaN Switch to turn off when CS pin voltage reaches V<sub>CS\_SSSP</sub> after blanking time t<sub>D SSSP</sub>. If this status maintains consecutive N<sub>CS SSSP</sub> switching cycle, the IC enters auto-restart mode.

### Over Load Protection (OLP)

NV957x family implements overload protection by limiting the maximum duration for operation of overload conditions. The overload timer starts counting when VFB voltage reaches VFB\_OLP. If this time is over OLP debounce time TD\_OLP, OLP protection will be triggered, and device will shut down and turn to auto restart mode. If VFB voltage drops to below VFB\_OLP before TD\_OLP, the overload timer will be reset.

Datasheet 23 Rev Sep. 20, 2024

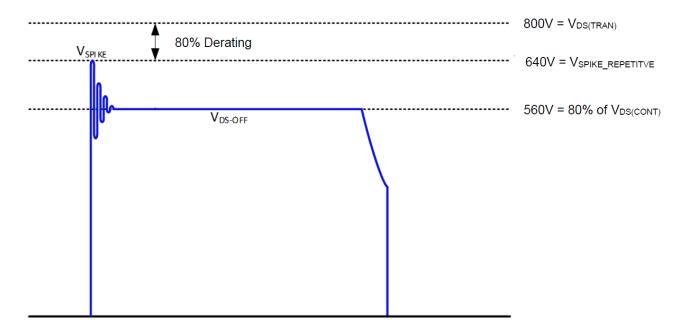

### **GaN Power FET Drain-to-Source Voltage Considerations**

GaN Power ICs have been designed and tested to provide significant design margin to handle transient and continuous voltage conditions that are commonly seen in single-ended topologies, such as quasi-resonant (QR) flyback applications. The different voltage levels and recommended margins in a typical QR flyback can be analyzed using Fig. 30. When the device is switched off, the energy stored in the transformer leakage inductance will cause VDs to overshoot to the level of VSPIKE. The clamp circuit should be designed to control the magnitude of VSPIKE. After dissipation of the leakage energy, the device VDs will settle to the level of the bus voltage plus the reflected output voltage which is defined in Fig. 30 as VDS-OFF.

- For repetitive events, 80% derating should be applied from V<sub>DS (TRAN)</sub> rating (800V) to 640V max under the worst case operating conditions.

- It is recommended to design the system such that V<sub>DS-OFF</sub> is derated 80% from the V<sub>DS(CONT)</sub> (700V) max rating to 560V.

- For half-bridge based topologies, such as LLC, V<sub>DS</sub> voltage is clamped to the bus voltage. V<sub>DS</sub> should be designed such that it meets the V<sub>DS-OFF</sub> derating guideline (560V).

- Non-repetitive events are infrequent, one-time conditions such as line surge, ESD, and lightning. No derating from the V<sub>DS(TRAN)</sub> rating (800V) is needed for non-repetitive V<sub>SPIKE</sub> durations < 100 μs. The V<sub>DS(TRAN)</sub> rating (800V) allows for repetitive events that are <400ns, with 80% derating required (for example repetitive leakage inductance spikes).

Figure 30 QR flyback drain-to-source voltage stress diagram

Datasheet 24 Rev Sep. 20, 2024

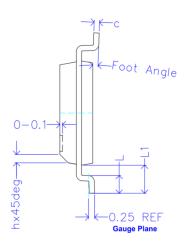

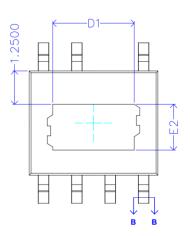

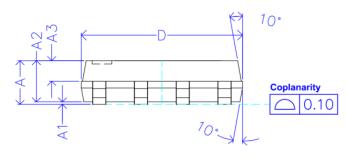

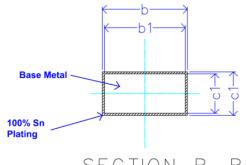

# 11. Package Outline (ESOP 7)

TOP VIEW

SECTION B-B SCALE 1:5

| SYMBOL                  | MIN      | NOM      | MAX  |  |  |

|-------------------------|----------|----------|------|--|--|

| Α                       | -        | -        | 1.65 |  |  |

| A1                      | 0.05     | -        | 0.15 |  |  |

| A2                      | 1.30     | 1.40     | 1.50 |  |  |

| A3                      | 0.60     | 0.65     | 0.70 |  |  |

| b                       | 0.39     |          | 0.47 |  |  |

| b1                      | 0.38     | 0.41     | 0.44 |  |  |

| С                       | 0.20     |          | 0.24 |  |  |

| c1                      | 0.19     | 0.20     | 0.21 |  |  |

| D                       | 4.80     | 4.90     | 5.00 |  |  |

| E                       | 5.80     | 6.00     | 6.20 |  |  |

| E1                      | 3.80     | 3.90     | 4.00 |  |  |

| е                       |          | 1.27 BSC |      |  |  |

| h                       | 0.25     | -        | 0.50 |  |  |

| L                       | 0.50     | 0.60     | 0.80 |  |  |

| L1                      | 1.05 REF |          |      |  |  |

| Foot angle: 0-8 degrees |          |          |      |  |  |

Foot angle: 0-8 degrees **Expossed Pad Dimension:**

D1: 3.10 REF E2: 1.72 REF

Note: Dimensions in mm

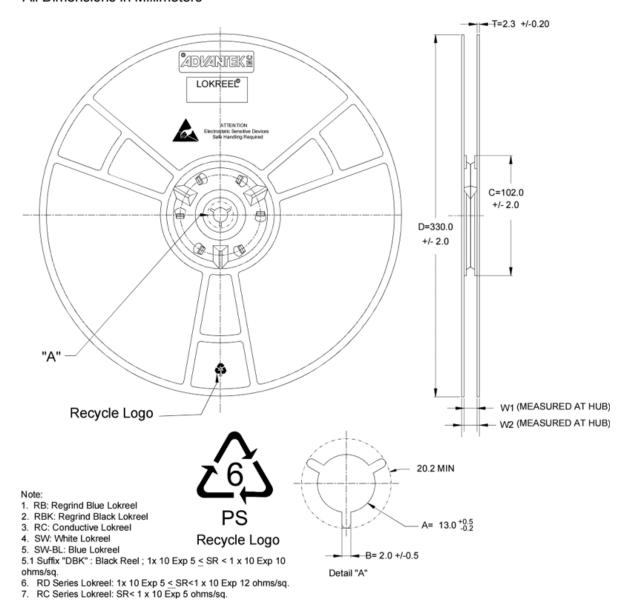

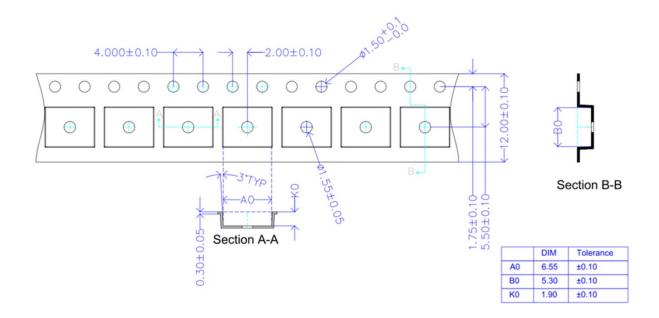

## 12. Tape and Reel Dimensions

-All Dimensions in Millimeters-

| Nominal Hub Width | W1                 | W2 MAX |

|-------------------|--------------------|--------|

| 12mm              | 12.8mm +1.6 / -0.4 | 18.4mm |

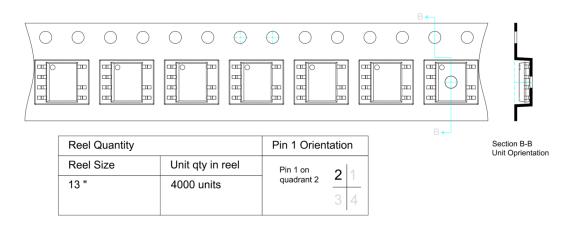

# 13. Tape and Reel Dimensions (Cont.)

## 14. 20-Year Limited Product Warranty

The 20-year limited warranty applies to all packaged Navitas GaNFast Power ICs and GaNSense HFQR Controllers in mass production, subject to the terms and conditions of, Navitas' express limited product warranty, available at <a href="https://navitassemi.com/terms-conditions">https://navitassemi.com/terms-conditions</a>. The warranted specifications include only the MIN and MAX values only listed in Absolute Maximum Ratings and Electrical Characteristics sections of this datasheet. Typical (TYP) values or other specifications are not warranted.

### 15. Revision History

| Date          | Status          | Notes                               |

|---------------|-----------------|-------------------------------------|

| Sep. 20, 2024 | Initial version | Included Sustainability description |

|               |                 |                                     |

|               |                 |                                     |

|               |                 |                                     |

|               |                 |                                     |

|               |                 |                                     |

### **Additional Information**

DISCLAIMER Navitas Semiconductor (Navitas) reserves the right to modify the products and/or specifications described herein at any time and at Navitas' sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied. This document is presented only as a guide and does not convey any license under intellectual property rights of Navitas or any third parties. Navitas' products are not intended for use in applications involving extreme environmental conditions or in life support systems. Terms and Conditions.

Navitas Semiconductor, Navitas, GaNSense and associated logos are registered trademarks of Navitas.

Copyright ©2023 Navitas Semiconductor. All rights reserved

Contact info@navitassemi.com

Datasheet 28 Rev Sep. 20, 2024