# USER MANUAL

# **NY9T Series**

4-bit MCU with LED Controller and Capacitive Touch of Low Stand-by Current

Version 1.3 Aug. 31, 2016

NYQUEST TECHNOLOGY CO. reserves the right to change this document without prior notice. Information provided by NYQUEST is believed to be accurate and reliable. However, NYQUEST makes no warranty for any errors which may appear in this document. Contact NYQUEST to obtain the latest version of device specifications before placing your orders. No responsibility is assumed by NYQUEST for any infringement of patent or other rights of third parties which may result from its use. In addition, NYQUEST products are not authorized for use as critical components in life support devices/systems or aviation devices/systems, where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user, without the express written approval of NYQUEST.

# **Revision History**

| Version# | Date       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Modified Page                                             |

|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 1.0      | 2015/05/29 | Formally release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                                                         |

| 1.1      | 2015/08/20 | Modify PWM-IO description.     Update DC characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7, 17<br>9                                                |

| 1.2      | 2016/02/24 | <ol> <li>Modify NY9T001 I/O function.</li> <li>Modify NY9T008 I/O function.</li> <li>Modify Interrupt description.</li> <li>Modify the recommended R<sub>ADJ</sub> value.</li> </ol>                                                                                                                                                                                                                                                                                                                        | 18<br>20<br>26<br>40                                      |

| 1.3      | 2016/08/31 | <ol> <li>Add CDC, PWM Frame Rate and Hysteresis description.</li> <li>Modify R<sub>ADJ</sub> description and add notice of PCB layout for R<sub>ADJ</sub>.</li> <li>Add CDC parameter to DC Characteristics.</li> <li>Add CDC pin description and the IC body with this function.</li> <li>Add 4KHz and 66KHz of LED PWM Frame Rate.</li> <li>Add Enlarge Scan Time.</li> <li>Modify R<sub>ADJ</sub> description and recommended R<sub>ADJ</sub> value.</li> <li>Add Touch-Key Hysteresis Level.</li> </ol> | 7<br>8<br>9<br>17, 18, 20<br>28, 29<br>34, 35<br>42<br>43 |

# **Table of Contents**

| Cha | apte | r 1. Introduction               |       | 6  |

|-----|------|---------------------------------|-------|----|

|     | 1.1  | General Description             |       | 6  |

|     | 1.2  | Features                        |       | 6  |

|     | 1.3  | Product List                    |       | 7  |

|     | 1.4  | Block Diagram                   |       | 8  |

|     | 1.5  | Pad Description                 |       | 8  |

|     | 1.6  | Electrical Characteristics      |       | 9  |

|     |      | 1.6.1 Absolute Maximum Rating   |       | 9  |

|     |      | 1.6.2 DC Characteristics        |       | 9  |

|     |      | 1.6.3 Touch-Key Scan Current    |       | 10 |

| Cha | apte | r 2. Hardware Architecture      |       | 11 |

|     | 2.1  | Hardware Summary Table          |       | 11 |

|     | 2.2  | Clock Generator                 |       | 11 |

|     | 2.3  | System Reset                    |       | 12 |

|     |      | 2.3.1 Power-On Reset (POR)      |       | 12 |

|     |      | 2.3.2 Low Voltage Reset (LVR).  |       | 12 |

|     |      | 2.3.3 Watch-Dog Timer Reset (V  | VDTR) | 12 |

|     |      | 2.3.4 IO Port External Reset    |       | 12 |

|     | 2.4  | Address Pointer                 |       | 13 |

|     |      | 2.4.1 Program Counter (PC)      |       | 13 |

|     |      | 2.4.2 LED Pointer Register (LPR | ?)    | 13 |

|     | 2.5  | Arithmetic Logic Unit (ALU)     |       | 13 |

|     |      | 2.5.1 ALU Instruction Summary.  |       | 13 |

|     |      | 2.5.2 ALU Related Status Flag   |       | 15 |

|     | 2.6  | Memory Organization             |       | 16 |

|     |      | 2.6.1 ROM                       |       | 16 |

|     |      | 2.6.2 RAM                       |       | 16 |

|     |      | 2.6.3 System Register           |       | 17 |

|     | 2.7  | IO Ports                        |       | 17 |

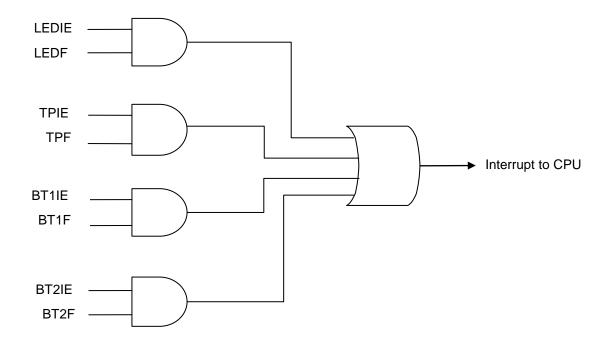

|     | 2.8  | Interrupt Generator             |       | 22 |

| Cha | apte | r 3. System Control             |       | 23 |

|     | 3.1  | Introduction                    |       | 23 |

|     |      | 3.1.1 System Register Address I | Мар   | 23 |

|     | 3.2  | RPT                             |       | 24 |

|     |      |                                 |       |    |

| 3.3    | 3 ROD                                                                          | 25             |

|--------|--------------------------------------------------------------------------------|----------------|

| 3.4    | I I/O Ports Register                                                           | 25             |

| 3.5    | 5 Interrupt                                                                    | 26             |

|        | 3.5.1 LED Interrupt                                                            | 26             |

|        | 3.5.2 Touch-Key Interrupt                                                      | 26             |

|        | 3.5.3 Base Timer (BT)                                                          | 26             |

| 3.6    | Power Saving Mode                                                              | 27             |

|        | 3.6.1 Halt Mode                                                                | 27             |

|        | 3.6.2 RC16K Mode                                                               | 27             |

| Chapte | er 4. LED Control                                                              | 28             |

| _      | LED Control                                                                    |                |

|        | 4.1.1 LED Play                                                                 | 28             |

|        | 4.1.2 LED Section                                                              | 28             |

| 4.2    | 2 LED Control Register                                                         | 29             |

|        | 4.2.1 LED Step                                                                 | 29             |

|        | 4.2.2 Pause/Resume                                                             | 30             |

|        | 4.2.3 Busy Condition                                                           | 30             |

| 4.3    | B LED Channel Output Enable Register                                           | 31             |

| Chapte | er 5. Touch-Key Control                                                        | 32             |

| 5.1    | Touch-Key Control                                                              | 32             |

|        | 5.1.1 Touch-Key Control Register                                               | 32             |

|        | 5.1.2 Sensitivity Control Register                                             | 32             |

|        | 5.1.3 Touch-Key Data Register                                                  | 33             |

| 5.2    | 2 Touch-Key Scan Time                                                          | 33             |

|        | 5.2.1 Sample Time                                                              | 33             |

|        | 5.2.2 Frame Rate                                                               | 33             |

|        | 5.2.3 Debounce Time                                                            | 34             |

|        | 5.2.4 Detect Time                                                              | 34             |

|        | 5.2.5 Enlarge Scan Time                                                        | 34             |

| 5.3    | 3                                                                              |                |

|        | Touch-Key Scan Mode                                                            | 35             |

|        |                                                                                |                |

|        | 3 Touch-Key Scan Mode                                                          | 36             |

|        | Touch-Key Scan Mode                                                            | 36<br>37       |

|        | Touch-Key Scan Mode  5.3.1 Normal Mode  5.3.2 Slow Mode                        | 36<br>37<br>38 |

|        | Touch-Key Scan Mode  5.3.1 Normal Mode  5.3.2 Slow Mode  5.3.3 Slow-Green Mode |                |

|     |      | 5.4.1   | Auto-Judge Calibration      | . 39    |

|-----|------|---------|-----------------------------|---------|

|     |      | 5.4.2   | Enforce Calibration         | . 39    |

|     |      | 5.4.3   | Software Example            | . 40    |

|     | 5.5  | Touch   | n Sensitivity               | .41     |

|     |      | 5.5.1   | Preset Mode                 | . 41    |

|     |      | 5.5.2   | Custom Mode                 | . 41    |

|     |      | 5.5.3   | Sensitivity Level           | . 41    |

|     |      | 5.5.4   | External Adjust             | . 42    |

|     |      | 5.5.5   | Touch-Key Anti-Interference | . 43    |

|     |      | 5.5.6   | Touch-Key Hysteresis Level  | . 43    |

| Cha | apte | r 6. In | struction Set               | 44      |

|     | 6.1  | Instru  | ction Classified Table      | .44     |

|     | 6.2  | Instru  | ction Descriptions          | .46     |

|     |      | 6.2.1   | Arithmetic Instructions     | . 46    |

|     |      | 6.2.2   | Conditional Instructions    | . 52    |

|     |      | 6.2.3   | LED Instructions            | . 54    |

|     |      | 604     | Other Instructions          | <i></i> |

# **Chapter 1. Introduction**

#### 1.1 General Description

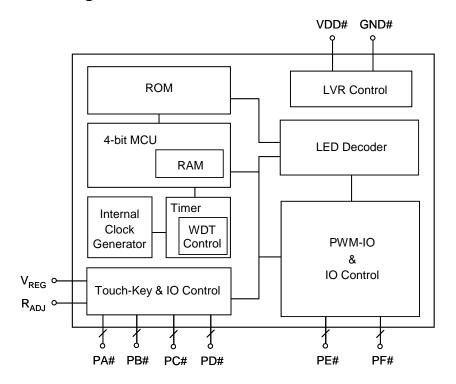

The NY9T series IC is a powerful 4-bit micro-controller based LED control processor with capacitive touch sensing function. The RISC MCU architecture is very easy to program and control, and various applications can be easily implemented. There are total 45 instructions, and most of them are executed in one cycle.

Through the accurate 400kHz internal oscillation of +/- 1% tolerance, an external resister is not required. Furthermore, a RC16K mode is designed to save power consumption and a HALT is to minimize the power.

There are maximum 8 channels of PWM-IO LED output. PWM-IO output can provide 4 kinds of analog output current cooperating with 256-level software digital current control to drive different brightness LED. The optional constant current is provided to protect LED, and it's not necessary to add the external current-limit resistor. The interactive software-developing tool of "*Q-Visio*" is user-friendly and quick for LED pattern programming.

The Touch-Key function replaces the mechanical switch or button. Multiple Touch-Keys is from 1 touch key up to 16 touch keys. A built-in LDO regulator for touch sensor can provide a stable capacitive sensing design for touch application. The auto distinguishing methodology supports the diversity key pattern in a thickness range of non-conductive dielectric material, and time sharing Touch-Key scan also reduces the power consumption. An innovative software tool "*Q-Touch*" is provided to develop the different touch applications.

#### 1.2 Features

- Wide operating voltage range: 2.0V to 6.0V.

- 4-bit RISC type micro-controller with 45 instructions.

- Maximum 16Kx10-bit ROM, program and LED data share the same ROM space.

- Maximum 96x4-bit RAM, divided into 2 pages.

- 400KHz instruction frequency.

- Precisely 400KHz oscillator with built-in resistor Rosc for operating mode. (+/- 1% tolerance)

- RC16K mode to save the power consumption. (+/- 30% tolerance)

- HALT mode to minimize power, less than 1uA standby current.

- Very low standby current for Touch-Key scan to reduce the power consumption.

- Low Voltage Reset (1.8V), Watch-Dog Reset and I/O Port reset are all supported to protect the system.

- Maximum 24 flexible I/Os with optional function: General purpose I/O, PWM-IO output or Touch-Key input.

- General purpose I/O's direction is controlled by registers. For the input option, users can select one of three

kinds of option: input without pull-low resistor, input with weak pull-low resistor or input with strong pull-low

resistor. For the output Port, users can select the CMOS output or Open Drain output with normal sink and

drive output.

- Maximum 8-channel PWM-IO output of PE0~3 and PF0~3 shared with I/Os. Each output has other 3 kinds

of output option: large sink current, constant sink current (CSC) or drive current.

- PE0~3 and PF0~3 output current option: (PE0~3 and PF0~3)

- a. Large sink current: 4 kinds of current, 100%, 83%, 50%, 33%.

- b. Constant sink current: 4 kinds of current, 100%, 83%, 50%, 33%.

- c. Drive current: only 100% current and constant drive current (CDC) only for PE1 and PE2.

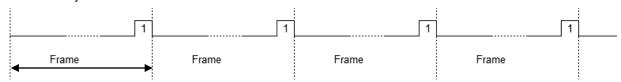

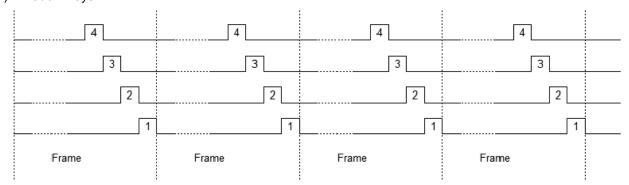

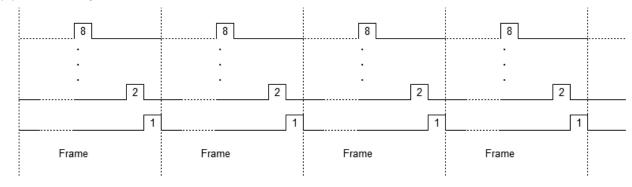

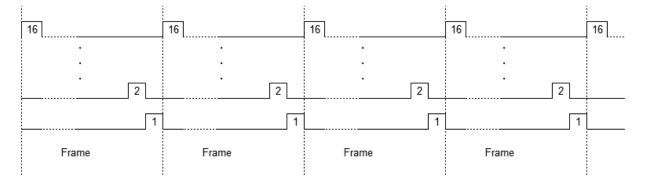

- Programmable PWM-IO has maximum 256 levels LED brightness with software control. The LED frame rate can be selected from 128Hz, 4KHz and 66KHz.

- Maximum 16 Touch-Keys of PA0~3, PB0~3, PC0~3 and PD0~3 shared with I/Os.

- Touch-Key supports simultaneous multi-key or single-key touch function configured by option.

- Hardware Auto-Calibration function of Touch-Key is provided for touch accuracy to prevent the environment change.

- Touch-Key wake-up can be any key or specified key (Key1/PA0) configured by option.

- 2 kinds of scan modes for Touch-Key: normal mode and slow mode, selected by software programming. At normal mode, sequential scan can shorten the touch detecting time but more power consumed. Oppositely, at slow mode, time sharing scan can reduce power consumption but longer wake-up time.

- 4 kinds of debounce time for Touch-Key press/release detection configured by option in order to keep away from the noise interference.

- 2 kinds of hysteresis level: Small Hysteresis Level and Large Hysteresis Level for all Touch-Keys configured by option.

- 2 kinds of sensitivity mode: Preset mode and Custom mode for all Touch-Keys configured by option.

- 8 kinds of sensitivity levels can be selected by software programming or external R<sub>ADJ</sub> resistor.

- Built-in LDO regulator (2.1V) for a stable power that avoids the abnormal sensitivity and false detection.

### 1.3 Product List

| IC Type  | 1/0 | ROM<br>(bits) | RAM<br>(bits) | Touch-Key | PWM-IO | LED Brightness<br>Level |

|----------|-----|---------------|---------------|-----------|--------|-------------------------|

| NY9T001A | 4   | 4K x 10       | 48 x 4        | 1         | 3      | 256                     |

| NY9T004A | 8   | 8K x 10       | 48 x 4        | 4         | 4      | 256                     |

| NY9T008A | 16  | 12K x 10      | 96 x 4        | 8         | 8      | 256                     |

| NY9T016A | 24  | 16K x 10      | 96 x 4        | 16        | 8      | 256                     |

<sup>\*</sup> NY9T001A - Touch-Key: PAO, PWM-IO: PEO~PE2.

<sup>\*</sup> NY9T004A - Touch-Key: PA0~PA3, PWM-IO: PE0~PE3.

<sup>\*</sup> NY9T008A – <u>Touch-Key:</u> PA0~PA3, PB0~PB3, <u>PWM-IO:</u> *PE0~PE3, PF0~PF3*.

<sup>\*</sup> NY9T016A – Touch-Key: PA0~PA3, PB0~PB3, PC0~PC3, PD0~PD3, PWM-IO: PE0~PE3, PF0~PF3.

# 1.4 Block Diagram

# 1.5 Pad Description

| Pad       | ATTR. | Description                                                               |  |

|-----------|-------|---------------------------------------------------------------------------|--|

| VDD#      | Power | Positive power                                                            |  |

| GND#      | Power | Negative power                                                            |  |

| $V_{REG}$ | power | Regulator input. Connect a 1000pF (102) cap to GND or keep floating.      |  |

| PA0~3     | I/O   | Bit 0~3 for Port A                                                        |  |

| PB0~3     | I/O   | Bit 0~3 for Port B                                                        |  |

| PC0~3     | I/O   | Bit 0~3 for Port C                                                        |  |

| PD0~3     | I/O   | Bit 0~3 for Port D                                                        |  |

| PE0~3     | I/O   | Bit 0~3 for Port E                                                        |  |

| PF0~3     | I/O   | Bit 0~3 for Port F                                                        |  |

| $R_{ADJ}$ | I     | Connect an external resistor to adjust the sensitivity, or keep floating. |  |

<sup>\*</sup> PA0~PA3, PB0~PB3, PC0~PC3 and PD0~PD3 shared with Touch-Key1~16.

<sup>\*</sup> PE0~PE3 and PF0~PF3 shared with PWM-IO.

<sup>\*</sup> PE0 is shared with reset pin.

<sup>\*</sup> PCB designer should notice that the length of R<sub>ADJ</sub> trace from IC to resistor must be within 0.5cm, and also avoids any parallel trace, or parallel GND nearby or at different layer.

# 1.6 Electrical Characteristics

The following lists the electrical characteristics of the NY9T EV chip. All the product's properties must refer to each part's datasheet.

# 1.6.1 Absolute Maximum Rating

| Symbol    | Parameter             | Rated Value        | Unit |

|-----------|-----------------------|--------------------|------|

| VDD - VSS | Supply voltage        | -0.5 ~ +6.5        | V    |

| Vin       | Input voltage         | Vss-0.3V ~ VDD+0.3 | V    |

| Тор       | Operating Temperature | 0 ~ +70            | °C   |

| Tst       | Storage Temperature   | -25 ~ +85          | °C   |

#### 1.6.2 DC Characteristics

| Symbol          | Parameter                                          |                               | $V_{DD}$ | Min. | Тур. | Мах. | Unit | Condition                           |  |

|-----------------|----------------------------------------------------|-------------------------------|----------|------|------|------|------|-------------------------------------|--|

| $V_{DD}$        | Operati                                            | ng voltage                    |          | 2.0  | 3    | 6.0  | V    | 400KHz                              |  |

|                 |                                                    | Halt                          | 3        |      | 0.1  | 0.5  | uA   | Sleep, no load                      |  |

| SB              |                                                    | mode                          | 4.5      |      | 0.1  | 0.5  | ūΥ   | LVR disable                         |  |

|                 |                                                    | RC16K                         | 3        |      | 0.7  |      | uA   | 16KHz, no load                      |  |

|                 | Supply                                             | mode                          | 4.5      |      | 2.2  |      | uΛ   | Torki iz, no load                   |  |

| I <sub>OP</sub> | Current                                            | Standby                       | 3        |      | 1.6  |      | uA   | Key1 (PA0) wakeup,                  |  |

| IOP             |                                                    | mode                          | 4.5      |      | 3.3  |      | uA   | 16 samples per frame                |  |

|                 |                                                    | Operating mode                | 3        |      | 350  |      | uA   | 400KHz, no load                     |  |

|                 |                                                    | Operating mode                | 4.5      |      | 500  |      | uA   | 400KHZ, 110 10au                    |  |

|                 |                                                    | Weak                          | 3        |      | 3    |      |      |                                     |  |

| I <sub>IH</sub> | Input current (Internal pull-                      | (1M ohms)                     | 4.5      |      | 8    |      | uA   | V <sub>IH</sub> =V <sub>DD</sub>    |  |

| IН              | low)                                               | Strong                        | 3        |      | 30   |      | uД   | V IH— V DD                          |  |

|                 | ,                                                  | (100k ohms)                   | 4.5      |      | 80   |      |      |                                     |  |

|                 | Output d                                           | rivo current                  | 3        |      | -10  |      | mA   | V <sub>OH</sub> =2.0V               |  |

| I <sub>OH</sub> | Output drive current                               |                               | 4.5<br>3 |      | -16  |      |      | V <sub>OH</sub> =3.5V               |  |

| ·OH             | Output consta                                      | Output constant drive current |          |      | -3.4 |      | mA   | V <sub>OH</sub> =2.0V               |  |

|                 |                                                    |                               | 4.5      |      | -3.8 |      |      | V <sub>OH</sub> =3.5V               |  |

|                 | Output norm                                        | nal sink current              | 3        |      | 20   |      |      |                                     |  |

|                 | - Output Holli                                     | idi sirik sarrent             | 4.5<br>3 |      | 30   |      |      |                                     |  |

| I <sub>oL</sub> | Output larg                                        | Output large sink current     |          |      | 50   |      | mA   | V <sub>01</sub> =1.0V               |  |

| IOL             | (1)                                                | 00%)                          | 4.5      |      | 70   |      | ША   | V <sub>OL</sub> =1.0V               |  |

|                 | Output const                                       | ant sink current              | 3        |      | 19   |      |      |                                     |  |

|                 | (1)                                                | 00%)                          | 4.5      |      | 20   |      |      |                                     |  |

| ∆F/F            | Frequency deviation<br>by voltage drop<br>(400kHz) |                               | 3        |      | -0.5 |      | %    | Fosc(3.0v)-Fosc(2.4v)<br>Fosc(3v)   |  |

| △1 /1           |                                                    |                               | 4.5      |      | 1.0  |      | 70   | Fosc(4.5v)-Fosc(3.0v)<br>Fosc(4.5v) |  |

| ∆F/F            | Frequency lot deviation<br>(400kHz)                |                               | 3        | -1   |      | 1    | %    | Fmax(3.0v)-Fmin(3.0v)<br>Fmax(3.0v) |  |

| Fosc            | Oscillation                                        | n Frequency                   | -        | 370  | 400  | 430  | KHz  | V <sub>DD</sub> =2.0~6.0V           |  |

**1.6.3 Touch-Key Scan Current** (Sample\_Time=1ms, Calibration\_Period=4s, T<sub>A</sub>=25°C, unless otherwise specified)

|              |               |               |      |         | Touch-Key Scan Current |           |                    |        |  |

|--------------|---------------|---------------|------|---------|------------------------|-----------|--------------------|--------|--|

| Body         | Touch<br>Keys | Samples<br>of | VDD  | Normal  | PA0 Wakeup             | Any-Key   | y Wakeup           |        |  |

| (Wakeup Key) | Neys          | Frame         |      | Mode    | Slow Mode              | Slow Mode | Slow-Green<br>Mode |        |  |

|              |               | 8             | 3.0V | 4.1 uA  | 1.6 uA                 |           |                    |        |  |

| NY9T001A     | 1-key         |               | 4.5V | 6.3 uA  | 3.3 uA                 |           |                    |        |  |

| NISIOUIA     | 1-KGy         | 16            | 3.0V | 2.4 uA  | 1.2 uA                 |           |                    |        |  |

|              |               | 10            | 4.5V | 4.3 uA  | 2.8 uA                 |           |                    |        |  |

|              |               | 0             | 3.0V | 10.1 uA | 1.6 uA                 | 2.8 uA    |                    |        |  |

|              | O kay         | 8             | 4.5V | 12.7 uA | 3.3 uA                 | 4.8 uA    |                    |        |  |

|              | 2-key         | 40            | 3.0V | 5.5 uA  | 1.2 uA                 | 2.0 uA    |                    |        |  |

|              |               | 16            | 4.5V | 7.5 uA  | 2.8 uA                 | 3.4 uA    |                    |        |  |

| NY9T004A     |               | 0             | 3.0V | 13.0 uA | 1.6 uA                 | 3.7 uA    |                    |        |  |

|              | 4 1           | 8             | 4.5V | 17.0 uA | 3.3 uA                 | 6.0 uA    |                    |        |  |

|              | 4-key         | 40            | 3.0V | 7.0 uA  | 1.2 uA                 | 2.3 uA    |                    |        |  |

|              |               | 16            | 4.5V | 9.6 uA  | 2.8 uA                 | 4.1 uA    |                    |        |  |

|              |               |               | 3.0V | 21.5 uA | 1.8 uA                 | 6.0 uA    | 4.1 uA             |        |  |

|              | 6-key         | 0.1           | 8    | 4.5V    | 27.0 uA                | 3.5 uA    | 8.8 uA             | 6.4 uA |  |

|              |               | 16            | 3.0V | 11.5 uA | 1.4 uA                 | 3.5 uA    | 2.7 uA             |        |  |

| NY9T008A     |               |               | 4.5V | 15.1 uA | 3.0 uA                 | 5.7 uA    | 4.6 uA             |        |  |

|              | 8-key         |               | 3.0V | 24.8 uA | 1.8 uA                 | 6.9 uA    | 4.1 uA             |        |  |

|              |               | 8             | 4.5V | 31.6 uA | 3.5 uA                 | 9.8 uA    | 6.4 uA             |        |  |

|              |               | 40            | 3.0V | 13.0 uA | 1.4 uA                 | 4.1 uA    | 2.7 uA             |        |  |

|              |               | 16            | 4.5V | 17.2 uA | 3.0 uA                 | 6.2 uA    | 4.6 uA             |        |  |

|              | 10-key        |               | 3.0V |         |                        |           |                    |        |  |

|              |               |               | 4.5V |         |                        |           |                    |        |  |

|              |               | то-кеу        | 40   | 3.0V    | 20.0 uA                | 1.6 uA    | 5.8 uA             | 2.9 uA |  |

|              |               | 16            | 4.5V | 25.0 uA | 3.3 uA                 | 8.5 uA    | 4.9 uA             |        |  |

|              |               |               | 3.0V |         |                        |           |                    |        |  |

|              | 40.1          |               | 4.5V |         |                        |           |                    |        |  |

|              | 12-key        | 10            | 3.0V | 21.7 uA | 1.6 uA                 | 6.3 uA    | 2.9 uA             |        |  |

|              |               | 16            | 4.5V | 27.1 uA | 3.3 uA                 | 9.0 uA    | 4.9 uA             |        |  |

| NY9T016A     |               |               | 3.0V |         |                        |           |                    |        |  |

|              |               |               | 4.5V |         |                        |           |                    |        |  |

|              | 14-key        | 16            | 3.0V | 23.3 uA | 1.6 uA                 | 6.7 uA    | 2.9 uA             |        |  |

|              |               |               | 4.5V | 29.3 uA | 3.3 uA                 | 9.5 uA    | 4.9 uA             |        |  |

|              |               |               | 3.0V |         |                        |           |                    |        |  |

|              |               |               | 4.5V |         |                        |           |                    |        |  |

|              | 16-key        |               | 3.0V | 24.6 uA | 1.6 uA                 | 7.1 uA    | 2.9 uA             |        |  |

|              |               | 16            |      |         |                        |           |                    |        |  |

|              |               |               | 4.5V | 31.8 uA | 3.3 uA                 | 11.8 uA   | 4.9 uA             |        |  |

# **Chapter 2. Hardware Architecture**

# 2.1 Hardware Summary Table

| Name            | Function                            | Address    |

|-----------------|-------------------------------------|------------|

| PC              | Program counter                     |            |

| LPR             | LED pointer register                |            |

| RPT             | Multi-function register pointer     | M[0x0~0x3] |

| RAM             | 96 nibbles RAM                      |            |

| ROM             | Program & data ROM                  |            |

| INT             | Interrupt function register         | M[0x6~0x7] |

| PWM             | PWM-IO LED output                   |            |

| INST            | Instruction registers               |            |

| INST DEC        | Instruction decoder                 |            |

| LED             | LED function register               | M[0x8]     |

| LED DEC         | LED decoder                         |            |

| TOUCH           | Touch-Key function register         | M[0x9~0xF] |

| Clock Generator | Ring oscillator clock generator     |            |

| WDT             | Watch-dog timer and reset generator |            |

| ROD1            | ROM[7:4] data access register       | M[0x4]     |

| ROD2            | ROM[9:8] data access register       | M[0x5]     |

| SYS Reset       | System reset generator              |            |

| POR             | Power reset generator               |            |

| LVR             | Low voltage reset generator         |            |

| ACC             | 4-bit accumulator                   |            |

| ALU             | 4-bit arithmetic logic unit         |            |

| С               | Carry flag for arithmetic           |            |

| Z               | Zero flag for arithmetic            |            |

| I/O Ports       | I/O Port register                   | T[0x0~0xB] |

M[]: Memory register and the hex number 0x? between the brackets is its address.

$T[\ ]$ : System register and the hex number 0x? between the brackets means its address.

#### 2.2 Clock Generator

The clock generator is a built-in Ring oscillator, and users can only select the internal resistor (INT-R). The INT-R oscillator accuracy is up to ±1%. The system clock is 400KHz for instructions running.

In normal operating mode, the system clock is 400kHz. User can implement sorts of application in this mode. On the other hand, users can select RC16K mode or Halt mode to save power consumption.

#### 2.3 System Reset

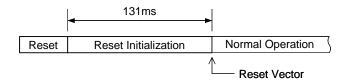

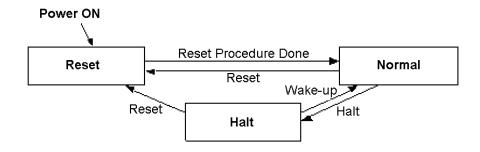

Reset Initialization Procedure

#### 2.3.1 Power-On Reset (POR)

After Power-on, the power-on reset initialization will automatically be set out. After the system leaves the reset initialization procedure, it enters the normal operation and the program counter starts at the reset vector. The power on stable time is about 131ms.

#### 2.3.2 Low Voltage Reset (LVR)

When the system enters the normal operation, the power supply voltage must be kept in an effective working voltage range. When the power supply voltage is lower than the effective working voltage range, the system can't work properly. To prevent the system crash, a low voltage detector is built in NY9T. When the detector detects a harmful low voltage supply, it will cause a low voltage reset. The so-called "low voltage" point is about 1.8V. The NY9T provides mask option to decide LVR global enable or disable. The other mask option decide enable or disable at HALT mode.

#### 2.3.3 Watch-Dog Timer Reset (WDTR)

To recover from program malfunction, the NY9T supports an embedded watch-dog timer reset. The WDTR function always works with the program executing. Users have to clear the WDT periodically to prevent from timing up with a reset generation. Typically, the minimum time-up period of the WDT is about 56ms. Users can use CWDT instruction to clear WDT.

It should be noted that WDT must be cleared carefully. Theoretically, it can't be placed at any loop other than main loop. One thing should be kept in mind, clear the WDT only when you make sure the execution of the MCU is still under the control of the program.

#### 2.3.4 IO Port External Reset

The PE0 pin can be optioned as a reset pin. A reset pin should always be pulled-down in normal operation, whether to use the built-in internal pull-low resister option or to use the external one on PCB with the floating input option. When the reset pin rises to the power level, it generates an external reset.

#### 2.4 Address Pointer

The NY9T micro-controller contains a program counter (PC) and LED pointer (LPR). The length of each address pointer is 14-bit maximum, varies by the product parts. Not like the PC, the initial value of the LPR is unknown.

#### 2.4.1 Program Counter (PC)

As a program instruction is executed, the PC will contain the address of the next program instruction to be executed. The PC starts from the reset vector (address 0x000000) after the system reset, and its value is increased by one every instruction cycle unless changed by a branch instruction.

| Inst./Event                                                                   | Function                                                       |  |  |  |  |

|-------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|

| JMP Changes the LSB 14-bit of PC, and the reminder MSB bits keep their value. |                                                                |  |  |  |  |

| CALL                                                                          | The same functions as JMP. In addition, it pushes PC+2 to RPT. |  |  |  |  |

| LDPC Loads RPT to PC, so users can execute a long jump or jump by table.      |                                                                |  |  |  |  |

| RBPC                                                                          | Reads back PC to RPT.                                          |  |  |  |  |

#### 2.4.2 LED Pointer Register (LPR)

The NY9T is also an 8-channel LED processor, a LED pointer is necessary for playing LED. When PLAY is executed, the system loads RPT to LPR. So users have to move the start address of the LED to RPT first. Besides, users can read LPR back by RBLP instruction.

### 2.5 Arithmetic Logic Unit (ALU)

The NY9T provides a 4-bit arithmetic logic unit with a 4-bit accumulator to perform logic, unsigned arithmetic, data transfer and conditional branch operation. We have two flags (carry and zero) to indicate the result of the operation. One or two operands will be the data sources of the ALU operation. The operands can be ACC, RAM, register, or literal constant data.

13

#### 2.5.1 ALU Instruction Summary

### 2.5.1.1 Logic Instruction

| Instruction | Function                                        | Flag Influenced |

|-------------|-------------------------------------------------|-----------------|

| XORM m      | $A \leftarrow M[m] \oplus A$                    | Z               |

| ANDM m      | $A \leftarrow M[m] \& A$                        | Z               |

| ORM m       | $A \leftarrow M[m] \mid A$                      | Z               |

| XORL L      | $A \leftarrow A \oplus L$                       | Z               |

| ANDL L      | A ← A & L                                       | Z               |

| ORL L       | A ← A   L                                       | Z               |

| ROLA        | $C \leftarrow A[3]; A \leftarrow \{A[2:0], C\}$ | C, Z            |

| RORA        | $C \leftarrow A[0]; A \leftarrow \{C, A[3:1]\}$ | C, Z            |

#### 2.5.1.2 Arithmetic Instruction

| Instruction | Function                    | Flag Influenced |

|-------------|-----------------------------|-----------------|

| INCM m      | A ← M[m] + 1                | C, Z            |

| DECM m      | A ← M[m] - 1                | C, Z            |

| ADDM m      | $A \leftarrow A + M[m] + C$ | C, Z            |

| ADDL L      | $A \leftarrow A + L + C$    | C, Z            |

| INCA        | A ← A + 1                   | C, Z            |

| DECA        | A ← A - 1                   | C, Z            |

#### 2.5.1.3 Data Transfer Instruction

| Instruction | Function               | Flag Influenced |

|-------------|------------------------|-----------------|

| MVAM        | M[m] ← A               |                 |

| MVMA        | $A \leftarrow M[m]$    | Z               |

| MVRM        | $M[m] \leftarrow R[r]$ |                 |

| MVMR        | $R[r] \leftarrow M[m]$ |                 |

| MVLR        | $R[r] \leftarrow L$    |                 |

| MVLA        | A ← L                  |                 |

| MVAT        | T[t] ← A               |                 |

| MVTA        | $A \leftarrow T[t]$    |                 |

| RSTC        | C ← 0                  | С               |

| SETC        | C ← 1                  | С               |

The width of the memory register address 'r' of MVRM, MVMR, and MVLR command is 2-bit and the MSB of the memory register is forced to be 0. So users can only use the three commands to handle RPT0~3. The width of the RAM or memory register address 'm' of MVRM, and MVMR command is 4-bit and the MSB 2-bit of the address is forced to be 0x3. Users can only use the two instructions to handle RAM or memory register of address 0x10~0x3F, but the RAM page is still working. The width of the PORT register address 't' of MVAT, and MVTA command is 4-bit. Users can only use the two instructions to handle PORT register of address 0x0~0xB, but the RAM page is still working.

#### 2.5.1.4 Conditional Branch Instruction

| Instruction | Function            | Flag Influenced |

|-------------|---------------------|-----------------|

| CPAL        | Skip if A = L       |                 |

| CNAL        | Skip if A != L      |                 |

| CPAB        | Skip if (A & L) = 0 |                 |

| CPCZ        | Skip if C = 0       |                 |

| CPZZ        | Skip if $Z = 0$     |                 |

| CNCZ        | Skip if C != 0      | С               |

| CNZZ        | Skip if Z != 0      | С               |

A conditional branch instruction compares two data and skips next instruction if they are equal. The skip operation is making an instruction NOP, not jump across it.

: Exclusive OR bitwise logical operation

& : AND bitwise logical operation

|: OR bitwise logical operation

A: 4-bit Accumulator data

C: 1-bit carry flag data

L: 4-bit immediately literal data

M[m]: 4-bit RAM or memory register data at memory address m

R[r]: 4-bit memory register data at register address r

Z: 1-bit zero flag data

#### 2.5.1.5 Interrupt Instruction

| Instruction | Function                         | Flag Influenced |  |

|-------------|----------------------------------|-----------------|--|

| IRET        | Return from interrupt subroutine | C, Z            |  |

#### 2.5.2 ALU Related Status Flag

| Symbol       | Flag                                                   | Description                                              |  |  |

|--------------|--------------------------------------------------------|----------------------------------------------------------|--|--|

| C Carry flag | C=1 if a carry-out occurs after an addition operation. |                                                          |  |  |

|              | Carry nag                                              | C=0 if a borrow-in occurs after a subtraction operation. |  |  |

| Z            | Zero flag                                              | Z=1 if the result of an ALU operation is zero.           |  |  |

Besides RSTC and SETC commands directly assign the value of the carry flag, C is influenced by the arithmetic result. C means carry and also means the complement of borrow. If the addition operation larger than 0xF, C=1, and C=0 if the result  $\leq$ 15. If the subtraction operation smaller than 0, C=0, and C=1 if the result  $\geq$ 0.

#### 2.6 Memory Organization

There are maximum 16K words ROM, 96 nibbles of RAM and 14 nibbles of dedicated system control register. The RAM page register (PG) is without address allocation, and they can only be accessed by the special instruction MPG.

#### 2.6.1 ROM

A large program/data/LED single ROM is provided and its structure is shown below. The reserved region contains system information and can't be utilized by users. The program page is limited by the unconditional branch instruction: JMP and CALL. Because it can only handle 14-bit length address of ROM, the program page size is 16K words.

| Address  | ROM                  |

|----------|----------------------|

| 0x000000 | Reset Vector         |

| 0x000001 |                      |

| 0x00000F |                      |

| 0x000010 | Interrupt Vector     |

| 0x00001E | ·                    |

| 0x00001F |                      |

|          | Reserved             |

| 0x0001FF |                      |

| 0x000200 | Program & Data Space |

| 0x000FFF | Program Page 0       |

| 0x001000 |                      |

|          | Program & Data Space |

| 0x003FFF |                      |

#### 2.6.2 RAM

Each page of RAM contains 48 nibbles. The NY9T provides maximum 96 nibbles of 2 pages. The page number (PG) register of RAM defined by the MPG instruction, and its initial value is 0. The address for RAM is 0x10~0x3F.

#### 2.6.3 System Register

The system registers are located at the first 16 nibbles of the memory space, and the addresses of them are not affected by the memory page register (PG). By the memory mapping, user can perform any register addressing operations on them.

| Address | Name   | R/W | Description                        |

|---------|--------|-----|------------------------------------|

| 0       | RPT0   | R/W | Register Pointer [3:0]             |

| 1       | RPT1   | R/W | Register Pointer [7:4]             |

| 2       | RPT2   | R/W | Register Pointer [11:8]            |

| 3       | RPT3   | R/W | Register Pointer [14:12]           |

| 4       | ROD1   | R/W | ROM data bit [7:4] access register |

| 5       | ROD2   | R/W | ROM data bit [9:8] access register |

| 6       | INTE   | R/W | Interrupt enable register          |

| 7       | INTF   | R/W | Interrupt flag register            |

| 8       | LEDCTL | R/W | LED control register               |

| 9       | SENS   | R/W | Sensitivity selection register     |

| Α       | TPCTL  | R/W | Touch-Key control register         |

| В       | IPCTL  | R/W | IP control register                |

| С       | KEYD0  | R   | Touch-Key1~4 status register       |

| D       | KEYD1  | R   | Touch-Key 5~8 status register      |

| Е       | KEYD2  | R   | Touch-Key 9~12 status register     |

| F       | KEYD3  | R   | Touch-Key 13~16 status register    |

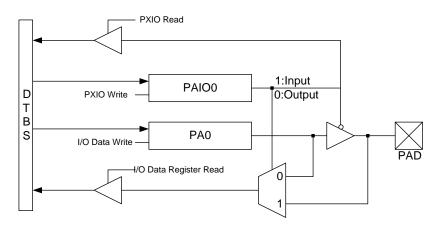

#### 2.7 IO Ports

There are 24 I/O Ports at most, designated as PAx through PFx, and x=0~3. All the I/O Ports can be configured as input or output by registers, i.e. normal I/O. For the input Port, we provide an internal pull-low register option for convenience. For the output port, users can select the normal sink current output or drive current output. When the PE0~3 or PF0~3 pins are optioned as normal I/O, the output sink current can be optioned as normal sink current, large sink current (33%, 50%, 83%, 100%) or constant sink current (33%, 50%, 83%, 100%). The PE1 and PE2 pins can be optioned as constant drive current (CDC) output by body (refer to the following table).

The PA0~3, PB0~3, PC0~3 or PD0~3 pins can be optioned as a Touch-Key individually. The PE0~3 or PF0~3 pins can be optioned as PWM-IO output pin individually, and each output pin can be optioned as large sink current (33%, 50%, 83%, 100%), constant sink current (33%, 50%, 83%, 100%) or drive current output. The PE1 and PE2 pins can be optioned as constant drive current (CDC) output by body (refer to the following table). The PE0 pin can be optioned as an external reset pin, which can possess a pull-low resister.

The pull-low resister of all the I/O Ports has two kinds of option: weak and strong. The weak one is about  $1M\Omega$  @3V for normal application and the strong one is about  $100k\Omega$  @3V usually for key matrix function. Each I/O can be configured as the weak or strong pull-low resister individually.

The following table shows the I/O Port options for MaskROM products.

#### NY9T001A with 4 I/Os

| 1/0     |                 | Option                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|---------|-----------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PA0     | Touch-Key input |                         | Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|         |                 |                         | Floating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|         |                 | Input pull-low resister | Weak                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|         |                 |                         | Strong                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|         |                 | Output two              | CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|         |                 | Output type             | Strong                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|         |                 | Output Drive current    | Constant Drive (PE1, PE2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|         |                 |                         | Strong CMOS Open Drain Constant Drive (PE1, PE2) Normal Sink Large Sink 33% Large Sink 50% Large Sink 83% Large Sink 100% Constant Sink 33% Constant Sink 33% Constant Sink 50% Constant Sink 83% Large Sink 100% Disable Large Sink 33% Large Sink 50% Large Sink 33% Large Sink 50% Large Sink 50% Large Sink 50% Large Sink 83%                                                                                                                                                                                               |  |  |

|         | Normal I/O      |                         | Large Sink 33%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|         |                 |                         | Large Sink 50%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|         |                 |                         | Large Sink 83%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|         |                 | Output sink current     | Large Sink 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|         |                 |                         | Constant Sink 33%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|         |                 |                         | Constant Sink 50%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| PE0~PE2 |                 |                         | Constant Sink 83%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| FEU~FEZ |                 |                         | Constant Sink 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|         |                 |                         | Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|         |                 |                         | Large Sink 33%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|         |                 |                         | Large Sink 50%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|         |                 |                         | Large Sink 83%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|         |                 |                         | Large Sink 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|         | PWM-IO outpu    | ıt                      | Large Sink 33%  Large Sink 50%  Large Sink 83%  Large Sink 100%  Constant Sink 33%  Constant Sink 50%  Constant Sink 100%  Disable  Large Sink 33%  Large Sink 50%  Large Sink 50%                                                                                                                                                                                                                                                                                                                                               |  |  |

|         |                 |                         | Constant Sink 50%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|         |                 |                         | Constant Sink 83%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|         |                 |                         | Constant Sink 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|         |                 |                         | Drive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|         |                 |                         | CMOS Open Drain Constant Drive (PE1, PE2) Normal Sink Large Sink 33% Large Sink 50% Large Sink 83% Large Sink 100% Constant Sink 33% Constant Sink 50% Constant Sink 50% Constant Sink 100% Disable Large Sink 33% Large Sink 50% Large Sink 50% Constant Sink 50% Constant Sink 50% Constant Sink 100% Constant Sink 100% Constant Sink 33% Constant Sink 33% Constant Sink 33% Constant Sink 33% Constant Sink 50% |  |  |

|         | Reset input (P  | EO only)                | Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|         | Neset IIIput (P | LO Offig)               | Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

#### NY9T004A with 8 I/Os

| 1/0       |                | Option                  | Description                                                                                                                                                            |  |  |  |

|-----------|----------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|           |                |                         | Floating                                                                                                                                                               |  |  |  |

|           |                | Input pull-low resister | Weak                                                                                                                                                                   |  |  |  |

|           | Normal I/O     |                         | Strong                                                                                                                                                                 |  |  |  |

| PA0~PA3   |                | Output time             | CMOS                                                                                                                                                                   |  |  |  |

|           |                | Output type             | Open Drain                                                                                                                                                             |  |  |  |

|           | Touch-Key inp  | t                       | Disable                                                                                                                                                                |  |  |  |

|           | Touch-Key inp  | out                     | Enable                                                                                                                                                                 |  |  |  |

|           |                |                         | Disable Enable Floating Weak Strong CMOS Open Drain Normal Sink Large Sink 33% Large Sink 50% Large Sink 83% Trent Large Sink 100% Constant Sink 33% Constant Sink 50% |  |  |  |

|           |                | Input pull-low resister | Weak                                                                                                                                                                   |  |  |  |

|           |                |                         | Strong  CMOS  Open Drain  Normal Sink  Large Sink 33%  Large Sink 50%                                                                                                  |  |  |  |

|           |                | Output type             | CMOS                                                                                                                                                                   |  |  |  |

|           |                | Output type             | Open Drain                                                                                                                                                             |  |  |  |

|           |                |                         | Normal Sink                                                                                                                                                            |  |  |  |

|           | Normal I/O     |                         | Large Sink 33%                                                                                                                                                         |  |  |  |

|           | Normal I/O     | Output sink current     | Large Sink 50%                                                                                                                                                         |  |  |  |

|           |                |                         | Large Sink 83%                                                                                                                                                         |  |  |  |

|           |                |                         | Large Sink 100%                                                                                                                                                        |  |  |  |

|           |                |                         | Constant Sink 33%                                                                                                                                                      |  |  |  |

|           |                |                         | Constant Sink 50%                                                                                                                                                      |  |  |  |

| PE0~PE3   |                |                         | Constant Sink 83%                                                                                                                                                      |  |  |  |

| 1 20~1 23 |                |                         | Constant Sink 100%                                                                                                                                                     |  |  |  |

|           |                |                         | Disable                                                                                                                                                                |  |  |  |

|           |                |                         | Large Sink 33%                                                                                                                                                         |  |  |  |

|           |                |                         | Large Sink 50%                                                                                                                                                         |  |  |  |

|           |                |                         | Large Sink 83%                                                                                                                                                         |  |  |  |

|           | PWM-IO outpu   | ıt                      | Large Sink 100%                                                                                                                                                        |  |  |  |

|           | F WWI-10 outpo | at .                    | Constant Sink 33%                                                                                                                                                      |  |  |  |

|           |                |                         | Constant Sink 50%                                                                                                                                                      |  |  |  |

|           |                |                         | Constant Sink 83%                                                                                                                                                      |  |  |  |

|           |                |                         | Constant Sink 100%                                                                                                                                                     |  |  |  |

|           |                |                         | Drive                                                                                                                                                                  |  |  |  |

|           | Reset input (P | PEO only)               | Disable                                                                                                                                                                |  |  |  |

|           | Neset Input (P |                         | Enable                                                                                                                                                                 |  |  |  |

#### NY9T008A with 16 I/Os

| 1/0                |                        | Option                  | Description          |

|--------------------|------------------------|-------------------------|----------------------|

|                    |                        |                         | Floating             |

|                    |                        | Input pull-low resister | Weak                 |

|                    | Normal I/O             |                         | Strong               |

| PA0~PA3<br>PB0~PB3 |                        | Output type             | CMOS                 |

| 1 00~1 00          |                        | Output type             | Open Drain           |

|                    | Touch-Key inp          | suit.                   | Disable              |

|                    | Touch-Ney Imp          | out                     | Enable               |

|                    |                        |                         | Floating             |

|                    |                        | Input pull-low resister | Weak                 |

|                    |                        |                         | Strong               |

|                    |                        | Output type             | CMOS                 |

|                    |                        | Output type             | Open Drain           |

|                    |                        | Output drive current    | Constant Drive (PE2) |

|                    |                        |                         | Normal Sink          |

|                    | Normal I/O             |                         | Large Sink 33%       |

|                    |                        | Output sink current     | Large Sink 50%       |

|                    |                        |                         | Large Sink 83%       |

|                    |                        |                         | Large Sink 100%      |

|                    |                        |                         | Constant Sink 33%    |

|                    |                        |                         | Constant Sink 50%    |

| PE0~PE3            |                        |                         | Constant Sink 83%    |

| PF0~PF3            |                        |                         | Constant Sink 100%   |

|                    |                        |                         | Disable              |

|                    |                        |                         | Large Sink 33%       |

|                    |                        |                         | Large Sink 50%       |

|                    |                        |                         | Large Sink 83%       |

|                    |                        |                         | Large Sink 100%      |

|                    | PWM-IO outpu           | ut                      | Constant Sink 33%    |

|                    |                        |                         | Constant Sink 50%    |

|                    |                        |                         | Constant Sink 83%    |

|                    |                        |                         | Constant Sink 100%   |

|                    |                        |                         | Drive                |

|                    |                        |                         | Constant Drive (PE2) |

|                    | Reset input /B         |                         | Disable              |

|                    | Reset input (PE0 only) |                         | Enable               |

#### NY9T016A with 24 I/Os

| 1/0                |                | Option                  | Description        |  |

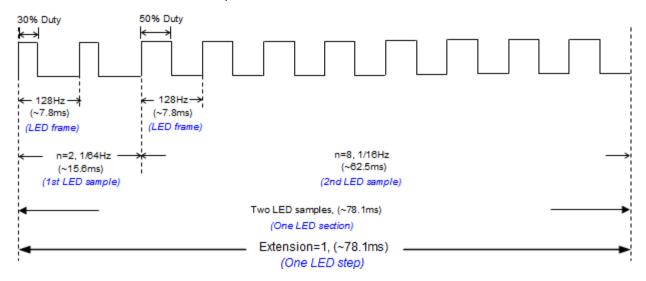

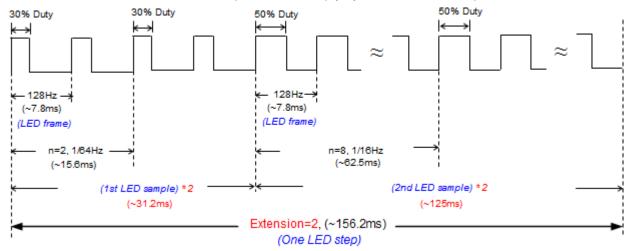

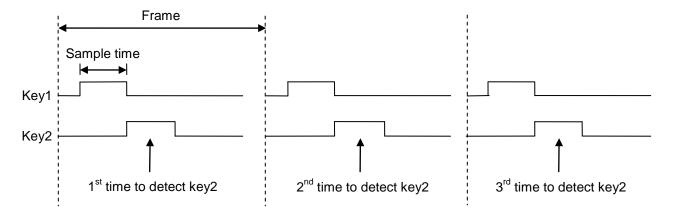

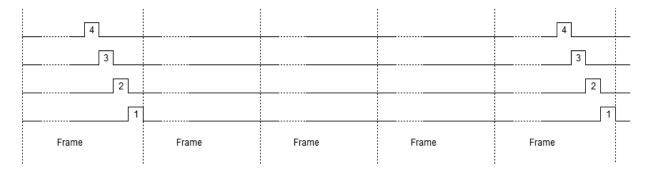

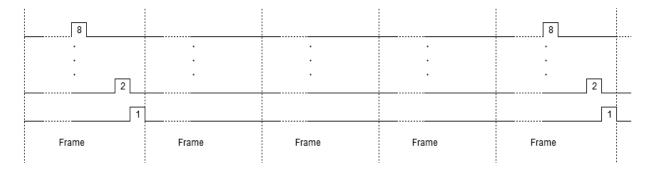

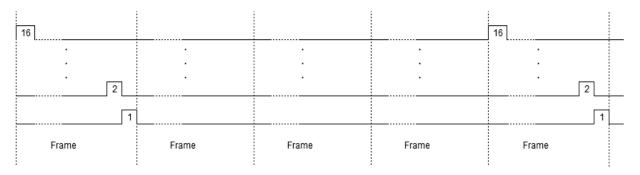

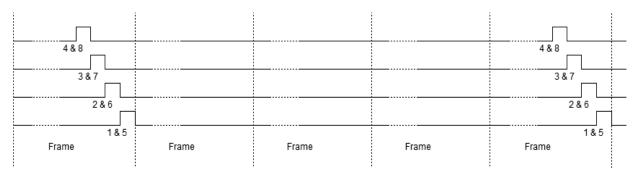

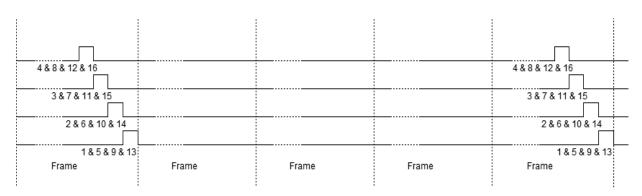

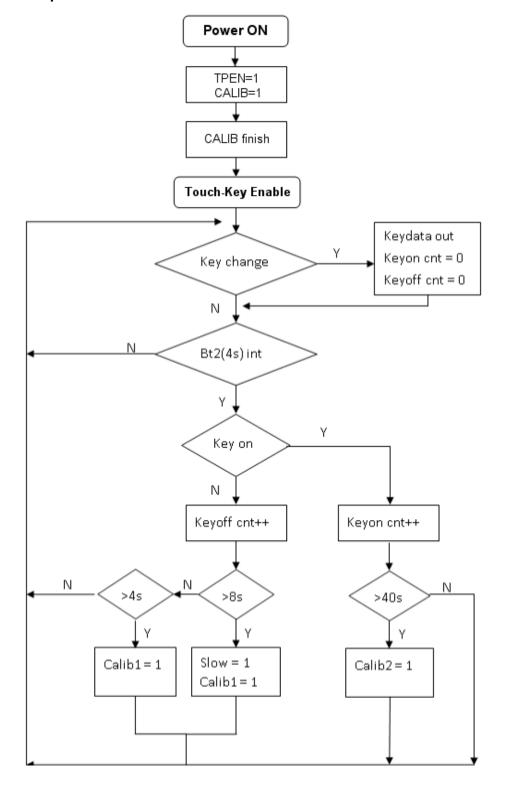

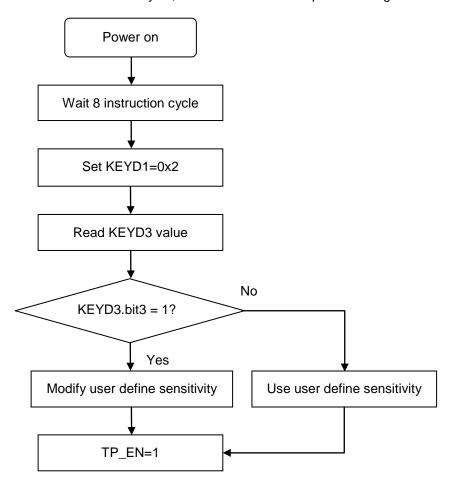

|--------------------|----------------|-------------------------|--------------------|--|