Order

Now

SBOS872A - MAY 2018 - REVISED JUNE 2018

# **OPA521 2.5-A Narrowband Line Driver**

Technical

Documents

## 1 Features

- Supports:

- CENELEC Bands A, B, C, D

- ARIB STD-T84, FCC

- FSK, SFSK, and NB-OFDM

- Conforms To:

- EN50065-1, -2, -3, -7

- FCC, Part 15

- ARIB STD-T84

- Standards:

- G3, PRIME, P1901.2, ITU-G.hnem

- Line Driver With Integrated Thermal and Overcurrent Protection

- Pin-Selectable Quiescent Current Consumption:

- 58 µA in Standby Mode (Typical)

- 51 mA for CENELEC Bands A, B, C, D (Typical)

- 78 mA for FCC, ARIB STD-T84 (Typical)

- Package: 5-mm × 5-mm 20-Pin VQFN

- Operating Junction Temperature Range:  $T_A = -40^{\circ}C$  to +125°C

## 2 Applications

- Power Quality Meter

- Merchant Network and Server PSU

- Lighting

- Solar Arc Protection

- Central Inverters

## 3 Description

Tools &

Software

The OPA521 is a line-driver power amplifier that aligns with the power-line communications (PLC) conducted emissions requirements in CENELEC bands A, B, C, and D and ARIB STD-T84 and FCC Part 15. This device supplies up to 2.5 A on highcurrent, low-impedance lines with reactive loads. With optimized internal protection structure, the OPA521 uses minimal external protection components that enable cost- and space-effective systems.

Support &

Community

20

The OPA521 gives a closed-loop gain of -7 V/V with 3.8-MHz of bandwidth. The monolithic integrated circuit gives high reliability in power-line communication applications.

The OPA521 line driver operates with a single supply from 7 V to 24 V. At a typical load current ( $I_{OUT}$  = 2.5 A, maximum), a wide output swing gives a 10-V<sub>PP</sub> capability with a nominal 24-V supply.

The device has protection against overtemperature and short-circuit conditions. Fault detection flags show current and thermal limits. A shutdown pin is available, which places the device into a low-power state that consumes 58  $\mu$ A (typical).

The OPA521 is available in a surface-mount, 5-mm  $\times$  5-mm, 20-pin VQFN (RGW) package. The device operates over the extended industrial junction temperature range of -40°C to +125°C.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| OPA521      | VQFN (20) | 5.00 mm × 5.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

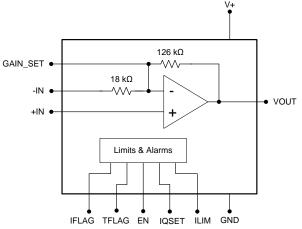

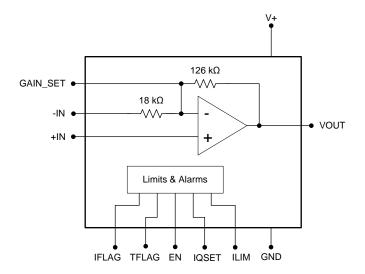

# OPA521 Block Diagram

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

Texas Instruments

www.ti.com

# **Table of Contents**

| 1 | Feat | tures 1                                    |

|---|------|--------------------------------------------|

| 2 | Арр  | lications1                                 |

| 3 | Des  | cription1                                  |

| 4 | Rev  | ision History 2                            |

| 5 | Pin  | Configuration and Functions 3              |

| 6 | Spe  | cifications 4                              |

|   | 6.1  | Absolute Maximum Ratings 4                 |

|   | 6.2  | ESD Ratings 4                              |

|   | 6.3  | Recommended Operating Conditions 4         |

|   | 6.4  | Thermal Information 4                      |

|   | 6.5  | Electrical Characteristics 5               |

|   | 6.6  | Electrical Characteristics: Digital 6      |

|   | 6.7  | Electrical Characteristics: Power Supply 6 |

|   | 6.8  | Typical Characteristics 7                  |

| 7 | Deta | ailed Description 11                       |

|   | 7.1  | Overview 11                                |

|   | 7.2  | Functional Block Diagram 11                |

|   | 7.3  | Feature Description 11                     |

|   |      |                                            |

|    | 7.4  | Device Functional Modes                         | 12 |

|----|------|-------------------------------------------------|----|

| 8  | Арр  | lication and Implementation                     | 13 |

|    | 8.1  | Application Information                         | 13 |

|    | 8.2  | Typical Application                             | 13 |

| 9  | Pow  | er Supply Recommendations                       | 18 |

| 10 | Lay  | out                                             | 21 |

|    | 10.1 | Layout Guidelines                               | 21 |

|    | 10.2 | Layout Example                                  |    |

| 11 | Dev  | ice and Documentation Support                   | 24 |

|    | 11.1 | Device Support                                  | 24 |

|    | 11.2 | Documentation Support                           | 24 |

|    | 11.3 | Receiving Notification of Documentation Updates | 24 |

|    | 11.4 | Community Resources                             | 24 |

|    | 11.5 | Trademarks                                      | 24 |

|    | 11.6 | Electrostatic Discharge Caution                 | 24 |

|    | 11.7 | Glossary                                        | 24 |

| 12 |      | hanical, Packaging, and Orderable mation        | 24 |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Cł | hanges from Original (May 2018) to Revision A | Page |

|----|-----------------------------------------------|------|

| •  | First release of production-data data sheet   | 1    |

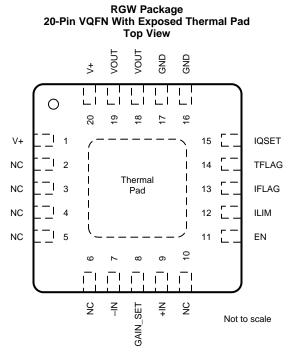

## 5 Pin Configuration and Functions

NC - no internal connection

#### **Pin Functions**

| Р           | IN                   | I/O | DESCRIPTION                                                                                                                                                       |  |  |

|-------------|----------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME        | NO.                  | 1/0 | DESCRIPTION                                                                                                                                                       |  |  |

| EN          | 11                   | I   | Enables the amplifier (active high, high enables the OPA521)                                                                                                      |  |  |

| GAIN_SET    | 8                    | I   | Connect an external resistor to Gain_Set and -IN to increase the gain beyond -7 V/V                                                                               |  |  |

| GND         | 16, 17               | —   | Ground                                                                                                                                                            |  |  |

| IFLAG       | 13                   | 0   | Current limit warning flag (open-drain, active high, high signifies current limit condition)                                                                      |  |  |

| ILIM        | 12                   | I   | Resistor programmable current limit                                                                                                                               |  |  |

| +IN         | 9                    | I   | Non-inverting input (connect to a voltage equal to (V+)/2)                                                                                                        |  |  |

| -IN         | 7                    | I   | Inverting input for closed loop gain = $-7 \text{ V/V}$                                                                                                           |  |  |

| IQSET       | 15                   | I   | Quiescent current select (active high, high configures the OPA521 to operate in FCC/ARIB bands, low configures the OPA521 to operate in CENELEC Bands A, B, C, D) |  |  |

| NC          | 2, 3, 4, 5, 6,<br>10 | _   | No internal connection                                                                                                                                            |  |  |

| TFLAG       | 14                   | 0   | Thermal limit warning flag (open-drain, active high, high signifies thermal limit condition)                                                                      |  |  |

| V+          | 1, 20                | _   | Positive power supply                                                                                                                                             |  |  |

| VOUT        | 18. 19               | 0   | Output                                                                                                                                                            |  |  |

| Thermal pad |                      | _   | Must be soldered to PCB and connected to GND                                                                                                                      |  |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                               |                               |                             | MIN  | MAX        | UNIT |

|-----------------------------------------------|-------------------------------|-----------------------------|------|------------|------|

| Supply voltage, V+                            |                               | Pins 1, 20                  |      | 26         | V    |

|                                               | Voltage <sup>(2)</sup>        | Pins 7, 8, 9, 12            | -0.4 | (V+) + 0.4 | V    |

| Signal input pins                             | vollage ->                    | Pins 11, 15                 | -0.4 | 3.3        | v    |

|                                               | Current <sup>(2)</sup>        | Pins 7, 8, 9, 11, 12,<br>15 |      | ±10        | mA   |

|                                               |                               | Pins 18, 19                 | -0.4 | (V+) + 0.4 |      |

| Signal output terminals                       | Voltage                       | Pins 13, 14                 | -0.4 | 3.3        | V    |

| oignaí output terminais                       | Current; short-circuit to GND | Pins 13, 14, 18, 19         | Con  | tinuous    |      |

| Operating junction temperature <sup>(3)</sup> |                               | -40                         | 125  | °C         |      |

| Storage temperature, T <sub>stg</sub>         |                               |                             | -55  | 150        | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.4 V beyond the supply rails should be current limited to 10 mA or less.

(3) The device automatically goes into shutdown above +140°C junction temperature

## 6.2 ESD Ratings

|                  |                          |                                                                                | VALUE | UNIT |

|------------------|--------------------------|--------------------------------------------------------------------------------|-------|------|

| V                | Electrostatic            | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±1500 | V    |

| V <sub>(ES</sub> | <sup>SD)</sup> discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                   | MIN | NOM MAX | UNIT |

|-----------------------------------|-----|---------|------|

| Supply voltage, V+                | 7   | 24      | V    |

| Output current, DC <sup>(1)</sup> |     | 1.9     | А    |

| Operating junction temperature    | -40 | 125     | °C   |

(1) Under safe operating conditions. See Power Amplifier Stress and Power Handling Limitations safe operating area (SOA) information.

## 6.4 Thermal Information

|                       |                                              | OPA521    |      |

|-----------------------|----------------------------------------------|-----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RGW (QFN) | UNIT |

|                       |                                              | 20 PINS   |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 33.0      | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 24.4      | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 12.7      | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.3       | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 12.7      | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 3.4       | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Electrical Characteristics

| At $T_{CASE} = 25^{\circ}C$ , V | √+ = 15 V, IN+ = ( | $V+) / 2$ , $R_{LOAD} = 50$ | $\Omega \Omega$ unless otherwise noted. |

|---------------------------------|--------------------|-----------------------------|-----------------------------------------|

|---------------------------------|--------------------|-----------------------------|-----------------------------------------|

|                | PARAMET                    | ER                  | TEST CONDITIONS                                                  | MIN           | TYP              | MAX                  | UNIT                    |  |

|----------------|----------------------------|---------------------|------------------------------------------------------------------|---------------|------------------|----------------------|-------------------------|--|

| NOISE          |                            |                     |                                                                  |               |                  |                      |                         |  |

|                |                            | CEN-A               | 35 kHz to 95 kHz                                                 |               | 45               |                      | $\mu V_{RMS}$           |  |

|                |                            | CEN-B               | 95 kHz to 125 kHz                                                |               | 32               |                      | $\mu V_{RMS}$           |  |

|                |                            | CEN-C               | 125 kHz to 140 kHz                                               |               | 23               |                      | μV <sub>RMS</sub>       |  |

|                | Integrated output noise    | CEN-D               | 140 kHz to 148 kHz                                               |               | 16.5             |                      | μV <sub>RMS</sub>       |  |

|                |                            | ARIB STD-T84        | 35 kHz to 420 kHz                                                |               | 114              |                      | μV <sub>RMS</sub>       |  |

|                |                            | FCC-LOW             | 35 kHz to 125 kHz                                                |               | 55               |                      | μV <sub>RMS</sub>       |  |

|                |                            | G3-FCC              | 150 kHz to 490 kHz                                               |               | 107              |                      | $\mu V_{RMS}$           |  |

| INPUT          |                            |                     |                                                                  |               |                  |                      |                         |  |

|                | Input voltage rang         | ie, IN-             | For linear operation, +IN = V+/2                                 | (GND + 0.4)/7 |                  | (V+ –<br>0.4)/7      | V                       |  |

|                | Input impedance            |                     |                                                                  |               | 18               |                      | kΩ                      |  |

| FREQUE         | NCY RESPONSE               |                     |                                                                  |               |                  |                      |                         |  |

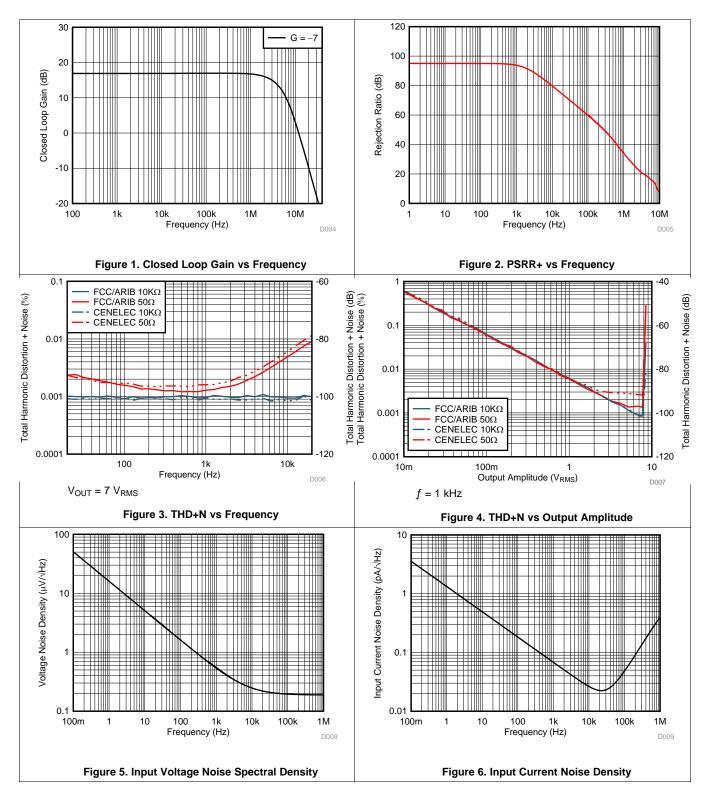

| BW             | Bandwidth                  |                     | I <sub>LOAD</sub> = 0 mA                                         |               | 3.82             |                      | MHz                     |  |

| SR             | Slew rate                  |                     | V+ = 24 V, V <sub>OUT</sub> = 20-V step                          |               | 75               |                      | V/µs                    |  |

|                | Full-power bandw           | idth                | V+ = 24 V, V <sub>OUT</sub> = 15 V <sub>PP</sub>                 |               | 800              |                      | kHz                     |  |

|                |                            |                     | RTI, DC                                                          | 80            | 94               |                      | dB                      |  |

| PSRR           | Power-supply reje          | ction ratio         | RTI, DC to f = 50 kHz                                            |               | See Typical      | Curves               | uв                      |  |

| OUTPUT         | •                          |                     |                                                                  |               |                  |                      |                         |  |

|                |                            | E 1/                | I <sub>O</sub> = 200-mA sourcing, 1-ms pulse                     |               |                  | 0.5                  | V                       |  |

| . /            | Voltage output             | From V+             | I <sub>O</sub> = 1.5-A sourcing, 1-ms pulse                      |               |                  | 2.25                 | V                       |  |

| Vo             | swing                      | From GND            | I <sub>O</sub> = 200 mA sinking, 1-ms pulse                      |               |                  | 0.5                  | V                       |  |

|                |                            |                     | I <sub>O</sub> = 1.5-A sinking, 1-ms pulse                       |               |                  | 1.5                  | V                       |  |

|                | Max continuous current, DC |                     | ILIM (pin 12) connected to ground                                | See Reco      | mmended Oµ<br>Co | oerating<br>nditions | А                       |  |

|                | Output resistance          |                     | I <sub>O</sub> = 1.9 A, f = 500 kHz                              |               | 0.1              |                      | Ω                       |  |

|                | Disabled output in         | npedance            | f = 100 kHz                                                      | 14            | 5    125         |                      | k $\Omega \parallel pl$ |  |

|                | Max output current         | Resistor-selectable | ILIM (pin 12) connected to ground                                |               | 2.5              |                      | А                       |  |

| GAIN           |                            |                     |                                                                  |               |                  |                      |                         |  |

| G              | Nominal gain               |                     | V <sub>OUT</sub> /V <sub>IN</sub>                                |               | -7               |                      | V/V                     |  |

| G <sub>E</sub> | Gain error                 |                     | $T_{\rm J} = -40^{\circ}{\rm C} \text{ to } +125^{\circ}{\rm C}$ | -2%           | 0.1%             | 2%                   |                         |  |

|                | Gain error drift           |                     | $T_{\rm J} = -40^{\circ}{\rm C} \text{ to } +125^{\circ}{\rm C}$ |               | ±5               |                      | ppm/°C                  |  |

| THERMA         | AL SHUTDOWN                |                     |                                                                  |               |                  |                      |                         |  |

|                | Junction temperat          | ure at shutdown     |                                                                  |               | 140              |                      | °C                      |  |

|                | Hysteresis                 |                     |                                                                  |               | 10               |                      | °C                      |  |

|                | Return to normal           | operation           |                                                                  |               | 130              |                      | °C                      |  |

SBOS872A-MAY 2018-REVISED JUNE 2018

www.ti.com

## 6.6 Electrical Characteristics: Digital

At T\_{CASE} = 25°C, V+ = 15 V, IN+ = (V+) / 2, R\_{LOAD} = 50  $\Omega$  unless otherwise noted.

|                           | PARAMETE                 | R              | TEST CONDITIONS                     | MIN                            | TYP          | MAX                        | UNIT          |  |

|---------------------------|--------------------------|----------------|-------------------------------------|--------------------------------|--------------|----------------------------|---------------|--|

| DIGITA                    | L INPUTS (ENABLE, IQSE   | ET)            |                                     | H                              |              |                            |               |  |

|                           | Leakage input current    |                | $GND \le V_{IN} \le 3.3$            | -1                             | 0.01         | 1                          | μA            |  |

| V <sub>IH</sub>           | High-level input voltage | je             |                                     |                                | 2            | 3.3                        | V             |  |

| V <sub>IL</sub>           | Low-level input voltag   | e              |                                     | GND                            |              | 0.8                        | V             |  |

|                           | EN pin function          | EN pin high    | 2 < EN < 3.3                        |                                | Devid        | e in norm                  | al operation  |  |

|                           | (active high)            | EN pin low     | EN < 0.8                            |                                |              | Device i                   | n shutdown    |  |

|                           | IQSET pin function       | IQSET pin high | IQSET > 2                           | Device in F                    | CC/ARIB mo   | ode ( $I_Q = 7$            | '8 mA (typ))  |  |

|                           | (active high)            | IQSET pin low  | IQSET < 0.8                         | Device in 0                    | CENELEC mo   | ode ( $I_Q = 5$            | 1 mA (typ))   |  |

| DIGITA                    | L OUTPUTS (TFLAG, IFLA   | AG)            |                                     |                                |              |                            |               |  |

| I <sub>OH</sub>           | High-level output curre  | ent            | V <sub>OH</sub> = 3.3 V             |                                |              | 1                          | μΑ            |  |

| V <sub>OL</sub>           | Low-level output volta   | ge             | I <sub>OL</sub> = 4 mA              |                                |              | 0.4                        | V             |  |

| I <sub>OL</sub>           | Low-level output curre   | ent            | V <sub>OL</sub> = 400 mV            | 4                              |              |                            | mA            |  |

|                           | TFLAG (active high,      | TFLAG pin high | TFLAG sink high < 1 μA              |                                | Device is    | s in therma                | al shutdown   |  |

|                           | open-drain)              | TFLAG pin low  | TFLAG < 0.4 V                       |                                | Device is no | is not in thermal shutdown |               |  |

|                           | IFLAG (active high,      | IFLAG pin high | IFLAG sink high < 1 μA              |                                | De           | evice is in                | current limit |  |

| open-drain) IFLAG pin low |                          | IFLAG < 0.4 V  |                                     | Device is not in current limit |              |                            |               |  |

| SHUTD                     | OWN MODE TIMING          | ·              |                                     | · · ·                          |              |                            |               |  |

|                           | Enable time              |                | SD pin transitions from low to high |                                | 3            |                            | ms            |  |

|                           | Disable time             |                | SD pin transitions from high to low |                                | 2            |                            | ms            |  |

|                           |                          |                |                                     |                                |              |                            |               |  |

## 6.7 Electrical Characteristics: Power Supply

At  $T_{CASE}$  = 25°C, V+ = 15 V, IN+ = (V+) / 2, R<sub>LOAD</sub> = 50  $\Omega$  unless otherwise noted.

|         | PARAMETER               | TEST CONDITIONS                      | MIN | TYP | MAX | UNIT |

|---------|-------------------------|--------------------------------------|-----|-----|-----|------|

| OPERAT  | ING SUPPLY RANGE        |                                      |     |     |     |      |

| V+      | Power amplifier         |                                      | 7   | 15  | 24  | V    |

| QUIESCE | ENT CURRENT (ENABLE pin | high)                                |     |     |     |      |

|         | FCC/ARIB mode           | I <sub>O</sub> = 0 A, IQSET pin high | 64  | 78  | 88  | mA   |

| IQ      | CENELEC mode            | I <sub>O</sub> = 0 A, IQSET pin low  | 41  | 51  | 61  | mA   |

| SHUTDO  | WN (ENABLE pin low)     |                                      |     |     |     |      |

| EN      | Power amplifier         | EN pin low                           |     | 58  | 130 | μA   |

SBOS872A - MAY 2018 - REVISED JUNE 2018

#### www.ti.com

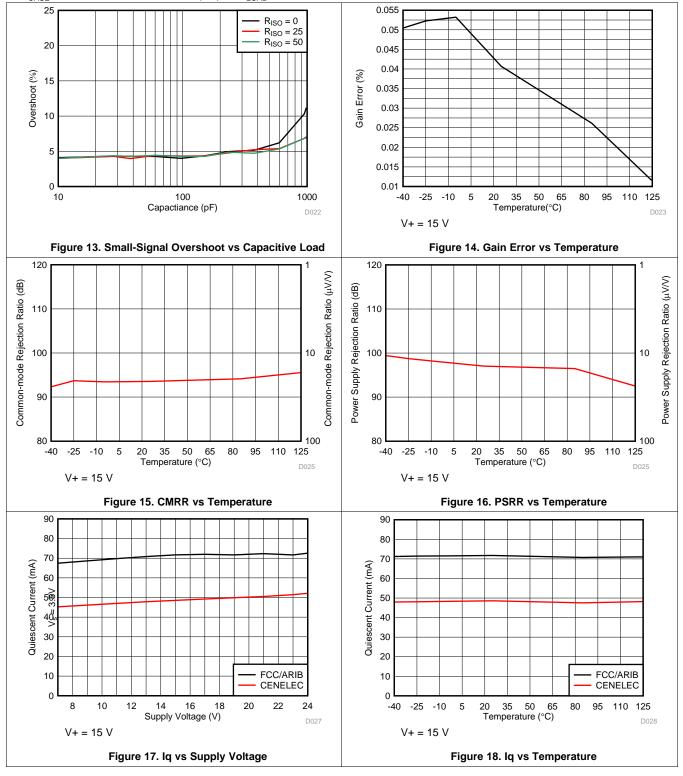

## 6.8 Typical Characteristics

## **Typical Characteristics (continued)**

## **Typical Characteristics (continued)**

SBOS872A-MAY 2018-REVISED JUNE 2018

www.ti.com

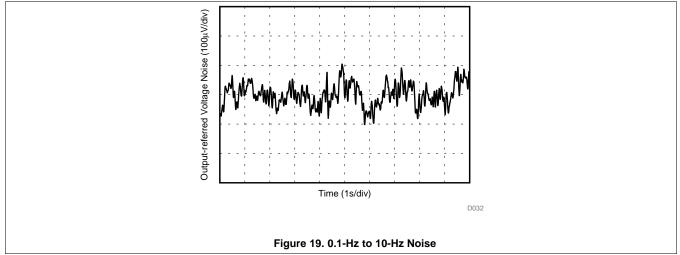

## **Typical Characteristics (continued)**

## 7 Detailed Description

#### 7.1 Overview

The OPA521 is a power amplifier (PA) designed for power-line communication (PLC) applications. The device features a fixed gain of -7 V/V, low-pass filter response, excellent linearity and low distortion through the bandwidth. The amplifier operates with 7-V to 24-V supplies, and can deliver up to ±1.9 A of continuous current from  $-40^{\circ}$ C to +125°C.

## 7.2 Functional Block Diagram

## 7.3 Feature Description

The OPA521 offers an optional output current limit (ILIM), quiescent current (IQSET) selection pins, and a device enable pin. The IFLAG output alarm pin indicates an output current warning and the TFLAG alarm triggers when the internal temperature of the device forces the devices to shut down.

## 7.3.1 IQSET Pin

This pin sets the operating band of the amplifier by adjusting the quiescent current.

- IQSET > 2 V sets the device to operate in the FCC or ARIB bands

- IQSET < 0.8 V sets the device to operate in the CENELEC bands

#### 7.3.2 EN Pin

When the transmitter is not in use, the output is disabled and placed in a high-impedance state when the EN pin decreases. For typical operation, connect the EN pin to 3.3 V. In disabled mode, the entire device draws 58  $\mu$ A (typical) of current.

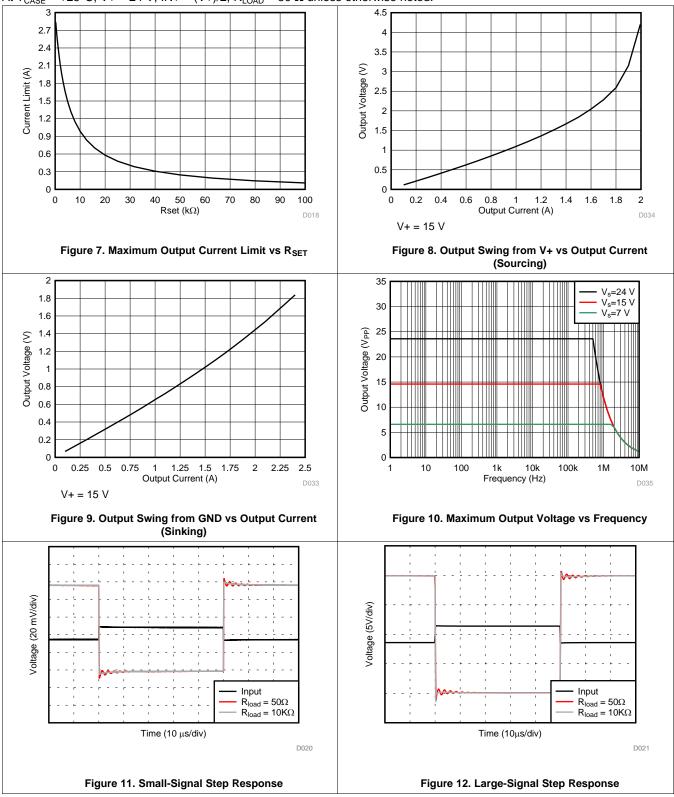

#### 7.3.3 ILIM Pin Current Limiting

The ILIM pin (pin 12) provides a resistor-programmable output current limit. Figure 6 shows the typical current limit for a given external R<sub>SET</sub> resistor attached to this pin.

Several typical target values and the approximate corresponding R<sub>SET</sub> are provided in Table 1.

| CURRENT LIMIT (A) | R <sub>SET</sub> (approximate, kΩ) |

|-------------------|------------------------------------|

| Maximum Output    | Grounded                           |

| 1                 | 10                                 |

| 0.5               | 25                                 |

#### Table 1. Typical Current Limit and R<sub>SET</sub> Values

Copyright © 2018, Texas Instruments Incorporated

### 7.3.4 IFLAG and TFLAG Pins

The IFLAG and TFLAG pins are active-high, open-drain outputs that indicate if the OPA521 is in current or thermal limit. Connect these pins to 3.3 V through pullup resistors (for example 10 k $\Omega$ ).

The maximum output current from the power amplifier is programmed with the external  $I_{LIM}$  resistor that is connected between ILIM (pin 12) and ground. IFLAG is set if the amplifier goes to a current limit state if a fault condition occurs. This causes the power amplifier to source or sink more current than the programmed limit value. IFLAG exhibits transient pulses under typical operation. An IFLAG true state for greater than 100 ms is a definite indication of a fault current condition.

The device contains internal thermal shutdown protection circuitry that automatically disables the output stage if the junction temperature exceeds 140°C. The device thermal shutdown protection circuitry lets the amplifier typical normal operation only when the junction temperature falls below 130°C. The TFLAG is active when the device is in thermal shut down mode.

## 7.4 Device Functional Modes

The OPA521 operates from a single power rail from 7 V to 24 V. The gain is fixed at -7 V/V and can increase with an external resistor that is connected to the GAIN\_SET and -IN pins.

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

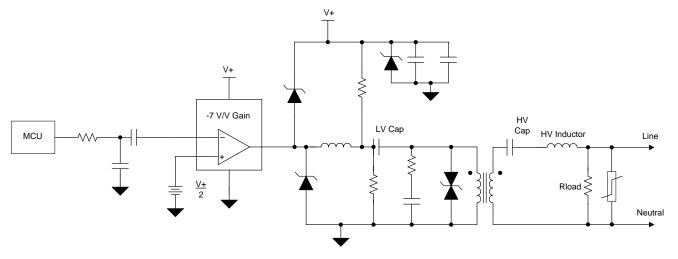

## 8.1 Application Information

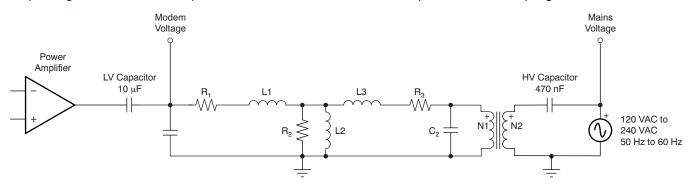

The application circuit shown in Figure 20 is an AC mains-line driver over 40-kHz-to-90-kHz utility band and is based around the European standard (EN56065–1) describing utility and consumer applications. This example shows a possible implementation for differential transmission on the mains line. This applications circuit is designed around the requirements of a domestic electricity meter operating over a utility band of 40 kHz to 90 kHz.

## 8.2 Typical Application

The impedance of the mains network at these signaling frequencies is relatively low (< 1  $\Omega$  to 30  $\Omega$ ). This circuit has been designed to drive a 2- $\Omega$  mains line over the 40-kHz-to-90-kHz bandwidth. The signaling impedance of the mains network fluctuates as different loads are switched on during the day or over a season and it is influenced by many factors such as:

- Localized loading from appliances connected to the mains supply near to the connection of the communication equipment; for example, heavy loads such as cookers and immersion heaters and reactive loads such as EMC filters and power factor corrections.

- Distributed loading from consumers connected to the same mains cable, where their collective loading reduces the mains signaling impedance during times of peak electricity consumption; for example, meal times.

- Network parameters; for example, transmission properties of cables and the impedance characteristics of distribution transformers and other system elements.

With such a diversity of factors, the signaling environment fluctuates enormously, irregularly, and can differ greatly from one installation to another. Design the signaling system for reliable communications over a wide range of mains impedances and signaling conditions. Consequently, the transmitter must be able to drive sufficient signal into the mains network under these loading conditions.

The OPA521 amplifier has 1.9-A output drive capability with short-circuit protection; hence, it adequately copes with the high current demands required for implementing mains signaling systems.

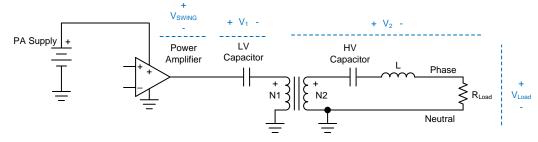

Figure 20. OPA521 Interface to the AC Mains

### Typical Application (continued)

#### 8.2.1 Design Requirements

The primary subsystems of a power-line communication mains-line driver system include the line coupling circuit, circuit protection, and power supply. The following sections detail the design of each.

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Interfacing the OPA521 to the AC Mains

The line coupling circuit is one of the most critical segments of a power-line modem. The line coupling circuit has two primary functions: first, to prevent the high voltage, low frequency of the mains (commonly 50 Hz or 60 Hz) from damaging the low-voltage modem circuitry; and second, as the name implies, to couple the modem signal to and from the ac mains.

#### 8.2.2.1.1 Low-Voltage Capacitor

The low-voltage capacitor (LV Cap) couples the time-varying components of the power amplifier output signal into the line coupling transformer. The LV Cap must have a large enough capacitance to appear as a low impedance throughout the signal band of interest;  $10-\mu$ F is a common value for signals in the range of 35 kHz to 150 kHz. The voltage rating of the LV cap should be sufficient to withstand the clamping voltage of the TVS diode (that is, the transient voltage suppressor (see Circuit Protection more information) operating under surge conditions. Generally, this limit must be equal to the power amplifier supply voltage or slightly higher.

#### 8.2.2.1.2 High-Voltage Capacitor

The high-voltage capacitor (HV Cap) blocks the low-frequency mains voltage by forming a voltage divider with the winding inductance of the line coupling transformer. In many applications, a maximum reactive power (VA limit) on the HV Cap may be required. To meet this requirement, the HV Cap value is calculated by Equation 1.

$$HV_{CAP} = \frac{VA_{\text{LIMIT}}}{V_{AC^2} \times 2 \pi \times f}$$

(1)

For a 240-VAC, 50-Hz application with a 10-VA limit, the maximum value for the HV Cap is shown in Equation 2.

$$HV_{CAP} \le \frac{10}{240^2 \times 2 \pi \times f} = 550 \text{ nF}$$

(2)

A 470-nF capacitor is frequently used in these types of applications. A metallized polypropylene electromagnetic interference and radio frequency interference (EMI/RFI) suppression capacitor is recommended because of the low loss factor associated with the dielectric, which results in minimal internal self-heating. Operating the capacitor at approximately 80% of its ac-rated voltage ensures a long component operating life. See Circuit Protection of this document for additional discussion on selecting the correct HV Cap value to withstand impulses on the mains.

#### 8.2.2.1.3 Inductor

The inductor that is connected in series with the HV Cap is required when driving low line impedances and the HV Cap is restricted to approximately 470 nF for the reasons previously stated. In applications that operate in the CENELEC A band, the impedance of the 470-nF capacitance at 40 kHz is approximately 8.5  $\Omega$ . If the application requires the ability to drive a 2- $\Omega$  load, for example, this series impedance is restrictive. Adding the series inductor can mitigate this effect. To properly select the value of the inductance, the operating frequency range of the system must be known. A common example would be the PRIME frequency band, which is approximately 40 kHz to 90 kHz. Selecting the HV Cap and inductor to have a resonant frequency in the center of the frequency band is recommended, and results in a series inductor value of 12.8  $\mu$ H and HV Cap value of 470 nF. The inductor must be sized to be capable of withstanding the maximum load current without saturation, using this Equation 3 as a guideline.

$$L = \frac{I}{\left(HV_{CAP} \times 2 \pi \times f\right)^2}$$

(3)

**OPA521**

## **Typical Application (continued)**

#### 8.2.2.1.4 Line Coupling Transformer

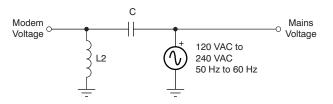

Most power-line communication transformers are compact, with turns ratios between 1:1 and 4:1, low leakage inductance, and approximately 1-mH of winding inductance. It is the voltage divider formed by the HV Cap and winding inductance that divides down the ac mains voltage and reduces it to negligible levels at the modem output. Figure 21 shows the equivalent circuit formed with the HV Cap and the line coupling transformer.

Figure 21. Voltage Divider with HV Cap and Transformer Equivalent Circuit

Where:

- 1. R1 is the series dc resistance of the primary winding

- 2. R2 is the shunt resistance reflecting losses in the core

- 3. R3 is the series dc resistance of the secondary winding, reflected to the primary side

- 4. L1 is the primary leakage inductance

- 5. L2 is the open circuit inductance of the primary winding

- 6. L3 is the secondary leakage inductance reflected to the primary side

- 7. C1 is the self-capacitance of the primary winding

- 8. C2 is the self-capacitance of the secondary winding reflected to the primary side

For the purposes of analysis, this circuit can be simplified as shown in Figure 22.

Figure 22. Simplified AC Mains Voltage Divider

#### Where:

- 1. L2 = OCL of the transformer primary

- 2. C = HV Cap reflected to the primary side

In a typical line coupling circuit the ac mains voltage injected into the modem is approximately 20 mVPP.

Determining the optimal turns ratio (N1/N2) for the power-line communication transformer is simple, and based on the principle of using the maximum output swing capability of the power amplifier together with the maximum output current capability of the power amplifier to achieve maximum power transfer efficiency into the load. Assuming the power-supply voltage and target load impedance are known, the turns ratio is determined as shown in Figure 17, and calculated with Equation 11 and Equation 12.

Copyright © 2018, Texas Instruments Incorporated

## **Typical Application (continued)**

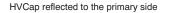

### 8.2.2.2 Circuit Protection

Power-line communications are often located in operating environments that are harsh for electrical components connected to the ac line. Noise or surges from electrical anomalies (such as lightning, capacitor bank switching, inductive switching, or other grid fault conditions) can damage high-performance integrated circuits if proper protection is not provided. The OPA521, however, can survive even the harshest conditions by using a variety of techniques to protect the device. Layout the protection circuitry in order to dissipate as much of the electrical disturbance as possible with a multilayer approach using metal-oxide varistors (MOVs), transient voltage suppression diodes (TVSs), Schottky diodes, and a Zener diode. These components dissipate the electrical disturbance before the anomaly reaches the device. shows the recommended strategy for transient overvoltage protection.

Copyright © 2017, Texas Instruments Incorporated

Figure 23. Transient Overvoltage Protection for OPA521

Note that the high-voltage coupling capacitor must be able to withstand pulses up to the clamping protection provided by the MOV. A metalized polypropylene capacitor, such as the 474MKP275KA from Illinois Capacitor, is rated for 50 Hz to 60 Hz and 250 VAC to 310 VAC, and can withstand 24 impulses of 2.5 kV. Table 2 lists several recommended transient protection components.

| COMPONENT | DESCRIPTION                   | MANUFACTURER            | MFR PART NO (OR EQUIVALENT) |

|-----------|-------------------------------|-------------------------|-----------------------------|

| D1        | Zener diode                   | Diodes, Inc.            | 1SMB59xxB                   |

| D2, D3    | Schottky diode                | Diodes, Inc.            | 1N5819HW                    |

| TVS       | Transient voltage suppressor  | Diodec<br>Semiconductor | P6SMBJxxC                   |

| MOV       | Varistor (for 120 VAC, 60 Hz) | LittleFuse              | TMOV20RP140E                |

| MOV       | Varistor (for 240 VAC, 50 Hz) | LittleFuse              | TMOV20RP300E                |

| HV Cap    | High-voltage capacitor        | Illinois Capacitor, Inc | 474MKP275KA                 |

**OPA521**

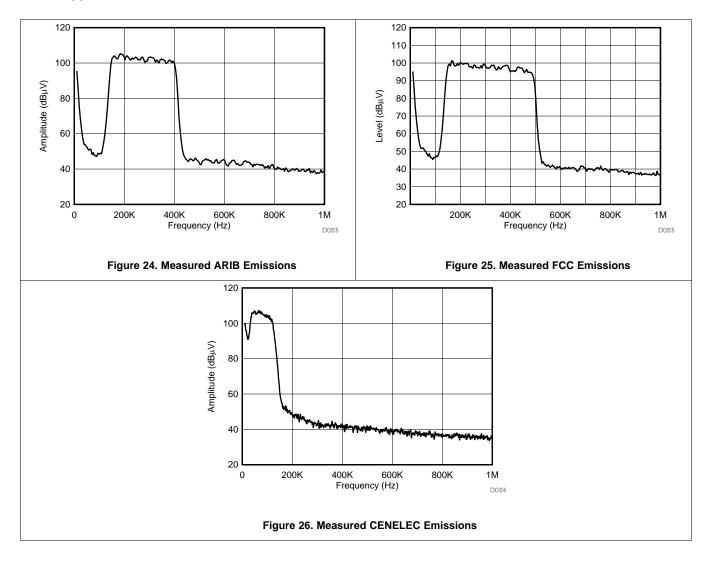

#### 8.2.3 Application Curves

#### SBOS872A - MAY 2018 - REVISED JUNE 2018

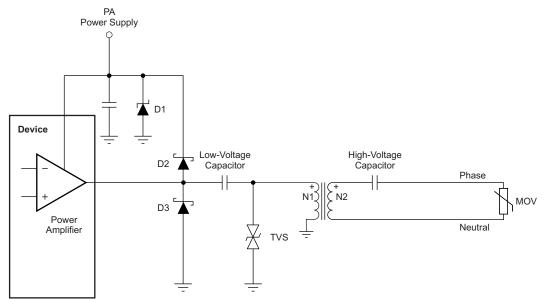

## 9 Power Supply Recommendations

Determining the power-supply requirements requires only a straightforward analysis. The desired load voltage, load impedance, and available power-supply voltage or desired transformer ratio are all the parameters that must be known. In many power-line communication applications, such as PRIME, it is required to drive a 1-V<sub>RMS</sub> signal into a 2- $\Omega$  load. Using Figure 27, calculate the minimum power-supply voltage required by adding the peak-to-peak load voltage; the voltage dropped across the HV Cap and inductor, V2; the voltage dropped across the LV Cap, V1; and twice the output swing to rail limit of the power amplifier, VSWING. For FSK and SFSK systems, the peak to average ratio is  $\sqrt{2}$ , while for OFDM systems this ratio is approximately 3:1.

Figure 27. Typical Line Coupling Circuit

These ratios must be considered when performing calculations that relate the RMS voltages and peak voltages during an analysis. Choosing a large value for the LV Cap results in the voltage drop (V1) becoming negligible in most circumstances. The losses in the transformer are also negligible, even at high load currents, if the proper transformer with a low DCR is used. For FSK and SFSK systems, the voltage drop across the HV Cap and inductor, V2, is also usually negligible; in OFDM systems, because of the wider operating bandwidth, voltage drop V2 can be ignored and accounted for by using a 1.5× multiplier on the load voltage as an approximation.

#### NOTE

This approximation is only valid with a load impedance of 2  $\Omega$  for PRIME and G3. Voltage drop V2 becomes negligible with increasing load impedance. These assumptions greatly simplify the analysis.

| PARAMETER           | FSK OR SFSK | PRIME OR G3 OFDM | UNIT              |  |  |  |  |  |  |

|---------------------|-------------|------------------|-------------------|--|--|--|--|--|--|

| Frequency range     | 63 to 74    | 35 to 95         | kHz               |  |  |  |  |  |  |

| R <sub>LOAD</sub>   | 2           | 2                | Ω                 |  |  |  |  |  |  |

| V <sub>LOAD</sub>   | 1           | 1                | V <sub>RMS</sub>  |  |  |  |  |  |  |

| V <sub>LOAD</sub>   | 1.414       | 3                | V <sub>PEAK</sub> |  |  |  |  |  |  |

| V <sub>LOAD</sub>   | 2.828       | 6                | V <sub>PP</sub>   |  |  |  |  |  |  |

| OFDM multiplier     | —           | 1.5              | —                 |  |  |  |  |  |  |

| V <sub>SWING</sub>  | 2           | 2                | V                 |  |  |  |  |  |  |

| Turns ration, N1/N2 | 1.5         | 1.5              | —                 |  |  |  |  |  |  |

| PA supply           | 8.25        | 17.5             | V                 |  |  |  |  |  |  |

Table 3. Power-Supply Requirements

Table 3 summarizes the power-supply requirements for various power-line communication systems.

Example:

For PRIME or G3 using an OFDM signal with a 2- $\Omega$  load and 1-V<sub>RMS</sub>load voltage:

$PA_{Supply} = V_{LOAD} \times OFDM$  Multiplier × Turns Ration + (2 ×  $V_{SWING}$ )

$$PA_{Supply} = 6 V \times 1.5 \times 1.5 + (2 \times 2 V)$$

$PA_{Supply} = 17.5 V$

Power consumption

(5)

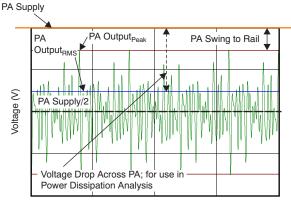

Calculating the power dissipation in the load and in OPA521 also requires some direct calculations. The desired load voltage, load impedance, available power-supply voltage, and the transformer ratio are the only parameters required. In many power-line communication applications, such as PRIME, it is required to drive a 1-VRMS signal into a 2- $\Omega$  load. The power dissipation in the power amplifier is determined by calculating the RMS value of the OPA521's output current, and the voltage difference between the power amplifier supply and RMS value of the output voltage. These two values are multiplied, and the quiescent power of the power amplifier is added.

The power in the load is given as Equation 4 shows.

PA output voltage (RMS) =

$$\frac{PA_{SUPPLY}}{2} + V_{LOAD_RMS} \times \frac{N_1}{N_2}$$

(4)

The power amplifier output current is given as calculated by Equation 5.

PA power dissipation = voltage drop across  $PA \times PA_{IOUT RMS}$

Because the output of the power amplifier is always symmetric around PASupply/2, only the voltage difference between the amplifier supply and the RMS values of the PA output must be considered. Figure 28 illustrates this concept for an OFDM signal. Table 4 shows example power dissipation values.

Time (s)

Figure 28. Typical OFDM Output Waveforms

| PARAMETER              | FSK OR SFSK | PRIME OR G3 OFDM | UNITS            |

|------------------------|-------------|------------------|------------------|

| Turns ration, N1/N2    | 1.5         | 1.5              | -                |

| R <sub>LOAD</sub>      | 2           | 2                | Ω                |

| V <sub>LOAD</sub>      | 1           | 1                | V <sub>RMS</sub> |

| I <sub>LOAD</sub>      | 0.5         | 0.5              | A <sub>RMS</sub> |

| PA output voltage      | 6           | 10.75            | V <sub>RMS</sub> |

| Voltage drop across PA | 3           | 6.25             | V <sub>RMS</sub> |

| PA output current      | 0.333       | 0.333            | A <sub>RMS</sub> |

| PA supply              | 9           | 17               | V                |

| PA power dissipation   | 1           | 2.1              | W                |

| Load power dissipation | 0.5         | 0.5              | W                |

| Total                  | 1.5         | 2.6              | W                |

#### **Table 4. Power Dissipation**

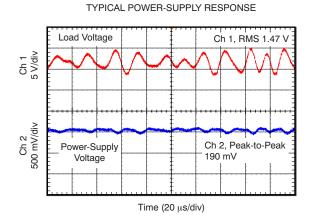

The power supply itself does not need to be designed to supply the peak power amplifier current continuously. The peak demand for current is supplied by the power-supply bypass capacitance. The power-supply voltage is shown in Figure 29 on channel 2, along with the signal voltage at the  $2-\Omega$  load on channel 1.

Figure 29. Typical Power-Supply AC Response

Two power-supply pins and two ground pins are available to provide a path for the high currents associated with driving the low impedance of the ac mains. Connecting the two supply pins together is recommended. Placing a 47- $\mu$ F to 100- $\mu$ F bypass capacitor in parallel with a 100-nF capacitor as close as possible to the device is also recommended. Care must be taken when routing the high-current ground lines on the PCB to avoid creating voltage drops in the PCB ground that may vary with changes in load current. /

## 10 Layout

### **10.1 Layout Guidelines**

#### **10.1.1** Thermal Considerations

In a typical power line communications application, the device dissipates 2 W of power when transmitting to the low-impedance AC line. This amount of power dissipation can increase the junction temperature, which can lead to a thermal overload that results in signal transmission interruptions if the PCB thermal design is not implemented properly. Proper management of heat flow from the device and good PCB design and construction are required to ensure proper device temperature, maximize performance, and extend the operating life of the device.

The device is assembled in a 5-mm × 5-mm, QFN-20 package. This QFN package has a large exposed thermal pad on the underside that conducts heat away from the device and to the underlying PCB.

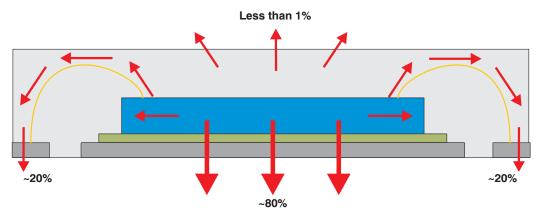

Some heat is conducted from the silicon die surface through the plastic packaging material and is transferred to the ambient environment. However, this route is not the primary thermal path for heat flow because plastic is a relatively poor conductor of heat. Heat flows across the silicon die surface to the bond pads through the wire bonds to the package leads, to the top layer of the PCB. While these paths for heat flow are important, the majority (nearly 80%) of the heat flows downward through the silicon die to the thermally-conductive die-attach epoxy and to the exposed thermal pad on the underside of the package (as shown in Figure 30). Minimizing the thermal resistance of this downward path to the ambient environment maximizes the life and performance of the device.

Figure 30. Heat Flow in the QFN Package

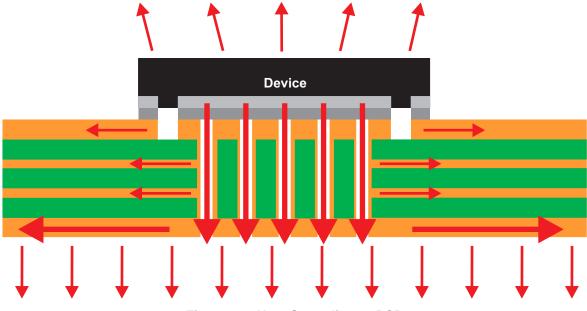

The exposed thermal pad must be soldered to the PCB thermal pad. The thermal pad on the PCB must be the same size as the exposed thermal pad on the underside of the QFN package. See *QFN/SON PCB Attachment* for recommendations on attaching the thermal pad to the PCB. Figure 31 shows the direction of heat spreading to the PCB from the device.

## Layout Guidelines (continued)

Figure 31. Heat Spreading to PCB

The heat spreading to the PCB is maximized if the thermal path is uninterrupted. Best results are achieved if the heat-spreading surfaces are filled with copper to the greatest extent possible, which maximizes the percentage of area covered on each layer. As an example, a thermally robust, multilayer PCB design consists of four layers with copper (Cu) coverage of 60% in the top layer, 85% and 90% in the inner layers (respectively), and 95% on the bottom layer.

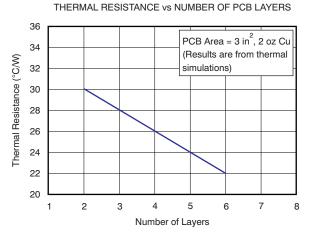

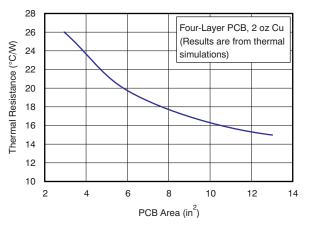

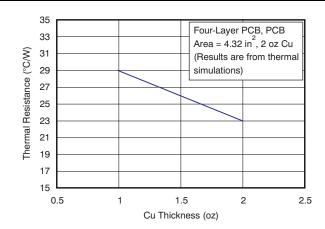

Increasing the number of layers in the PCB, using thicker copper, and increasing the PCB area are all factors that improve the spread of heat. Figure 32 through Figure 34 show thermal resistance performance as a function of each of these factors.

Figure 33. Thermal Resistance as a Function of PCB Area

SBOS872A - MAY 2018 - REVISED JUNE 2018

Figure 34. Thermal Resistance as a Function of Copper Thickness

For additional information on thermal PCB design using exposed thermal pad packages, see *PowerPAD<sup>TM</sup> Thermally-Enhanced Package* (available for download at www.ti.com).

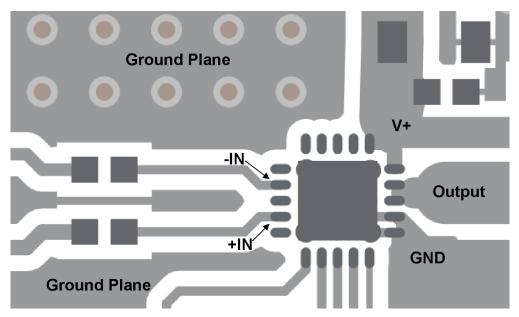

## 10.2 Layout Example

Figure 35. Recommended Layout for Typical Transformer Coupling Application

## **11** Device and Documentation Support

## **11.1 Device Support**

#### 11.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

## **11.2 Documentation Support**

#### 11.2.1 Related Documentation

For related documentation see the following:

- Texas Instruments, *PowerPAD™ Thermally Enhanced Package*

- Texas Instruments, QFN/SON PCB Attachment

## **11.3 Receiving Notification of Documentation Updates**

To receive notification of documentation updates, find the device product folder on ti.com. In the upper right corner, see *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, read the revision history included in any revised document.

### **11.4 Community Resources**

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 11.5 Trademarks

PowerPAD, E2E are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

#### **11.6 Electrostatic Discharge Caution**

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## 11.7 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 Mechanical, Packaging, and Orderable Information

The following pages show mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, see the the left-hand navigation.

10-Dec-2020

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|----------------------|--------------|-------------------------|---------|

| OPA521IRGWR      | ACTIVE        | VQFN         | RGW                | 20   | 3000           | RoHS & Green    | (6)<br>NIPDAU                 | Level-2-260C-1 YEAR  | -40 to 125   | OPA<br>521              | Samples |

| OPA521IRGWT      | ACTIVE        | VQFN         | RGW                | 20   | 250            | RoHS & Green    | NIPDAU                        | Level-2-260C-1 YEAR  | -40 to 125   | OPA<br>521              | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE OPTION ADDENDUM

10-Dec-2020

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

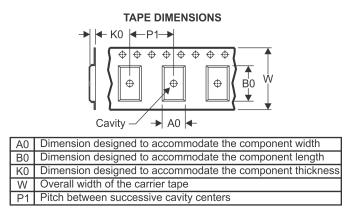

## TAPE AND REEL INFORMATION

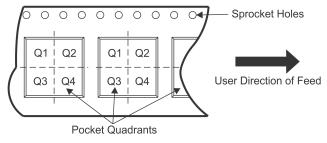

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| OPA521IRGWR                 | VQFN            | RGW                | 20 | 3000 | 330.0                    | 12.4                     | 5.3        | 5.3        | 1.1        | 8.0        | 12.0      | Q2               |

| OPA521IRGWT                 | VQFN            | RGW                | 20 | 250  | 180.0                    | 12.4                     | 5.3        | 5.3        | 1.1        | 8.0        | 12.0      | Q2               |

TEXAS INSTRUMENTS

www.ti.com

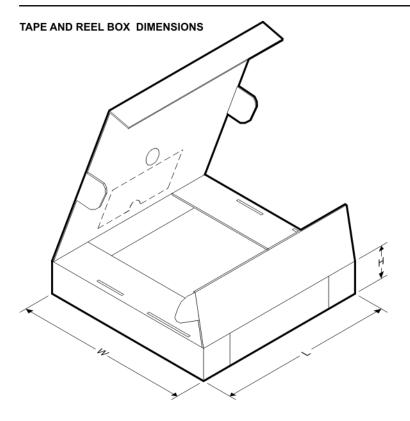

# PACKAGE MATERIALS INFORMATION

1-Jul-2018

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| OPA521IRGWR | VQFN         | RGW             | 20   | 3000 | 367.0       | 367.0      | 35.0        |

| OPA521IRGWT | VQFN         | RGW             | 20   | 250  | 210.0       | 185.0      | 35.0        |

# **RGW 20**

5 x 5, 0.65 mm pitch

# **GENERIC PACKAGE VIEW**

## VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

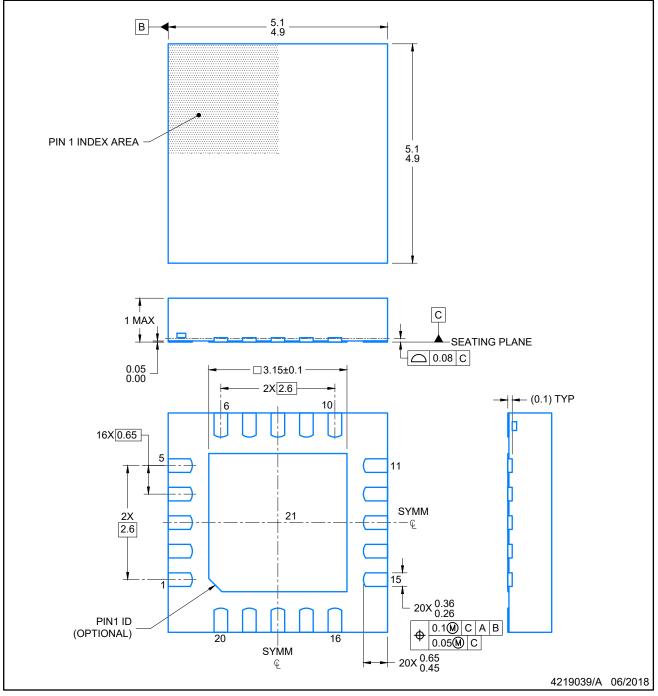

# **RGW0020A**

# **PACKAGE OUTLINE**

## VQFN - 1 mm max height

PLASTIC QUAD FLATPACK-NO LEAD

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

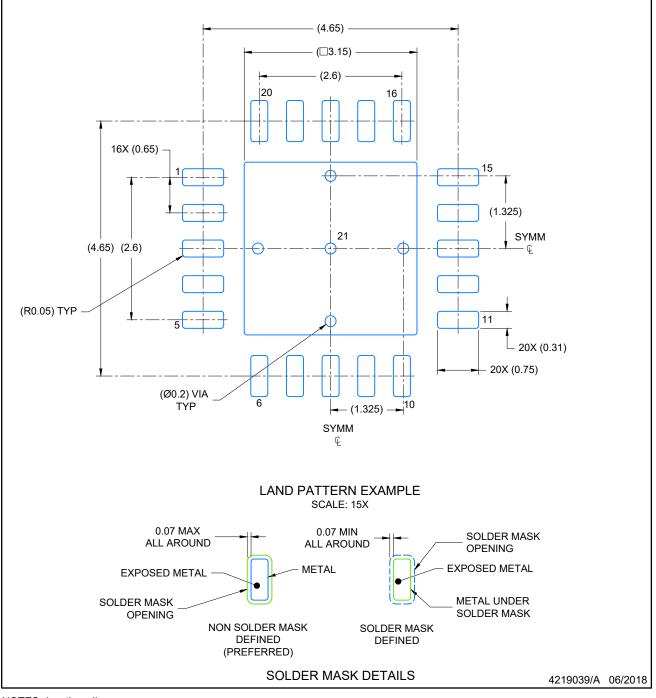

# **RGW0020A**

# **EXAMPLE BOARD LAYOUT**

## VQFN - 1 mm max height

PLASTIC QUAD FLATPACK-NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

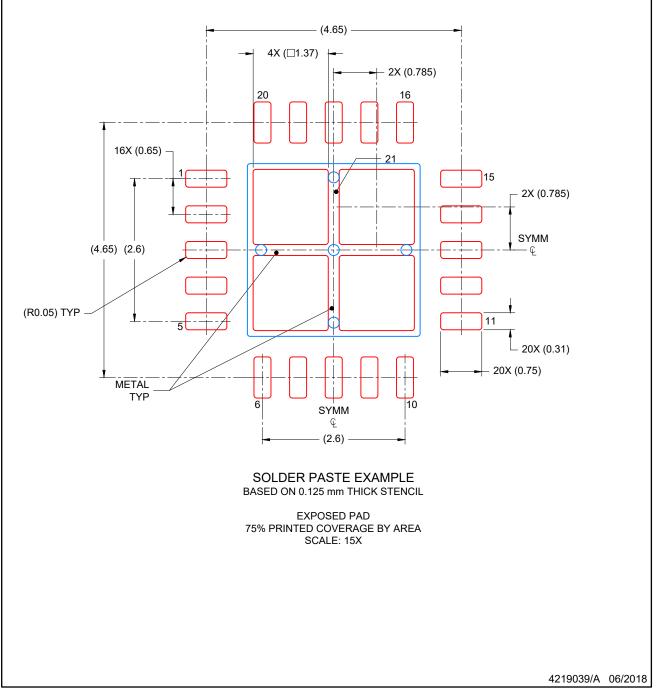

# **RGW0020A**

# **EXAMPLE STENCIL DESIGN**

# VQFN - 1 mm max height

PLASTIC QUAD FLATPACK-NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated