### **MOST System On Chip**

Final Product Data Sheet

DS8805FP5

Apr. 2003

Media Oriented Systems Transport

Multimedia and Control Networking Technology

© Copyright 2001-2003 Oasis SiliconSystems

**RESTRICTED ACCESS**

Valid Part Numbers:

| Order Number | Grade                           |            | Package                      |

|--------------|---------------------------------|------------|------------------------------|

|              | Temperature                     | Supply     | Fackaye                      |

| OS8805AQ     | T <sub>J</sub> = -40 to +150 °C | 3.3 V ±5 % | 128-pin MQFP                 |

| OS8805AQR    | T <sub>J</sub> = -40 to +150 °C | 3.3 V ±5 % | 128-pin MQFP, Tape and Reel  |

| OS8805AH     | T <sub>J</sub> = -40 to +150 °C | 3.3 V ±5 % | 128-pin ETQFP                |

| OS8805AHR    | T <sub>J</sub> = -40 to +150 °C | 3.3 V ±5 % | 128-pin ETQFP, Tape and Reel |

This table represents valid part numbers at the time of printing and may not represent parts that are currently available. For the latest list of valid ordering numbers for this product, please contact the nearest sales office (as listed on back page).

### **Intellectual Property**

© Copyright 2001-2003 Oasis SiliconSystems. The information within this document is Oasis SiliconSystems intellectual property. Duplication of this document without the expressed written permission from Oasis SiliconSystems is prohibited. The information in this document is considered "Restricted Access", and must not be sent to third parties without written permission from Oasis SiliconSystems.

### Trademarks

MOST is a registered trademark of Oasis SiliconSystems. All other trademarks used in this document are proprietary of their respective owners.

### Patents

There are a number of patents and patents pending on the MOST technology. The rights to these patents are not granted without any specific Agreement between the users and the patent owners.

#### Conventions

Within this manual, the following abbreviations and symbols are used to improve readability.

| Example         | Description                                                                                                                                                                       |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT             | Name of a single bit within a register                                                                                                                                            |

| REG.BIT         | Name of a single bit (BIT) in register REG                                                                                                                                        |

| ху              | Range from x to y, inclusive                                                                                                                                                      |

| BITS[m:n]       | Groups of bits (or pins) from m to n, inclusive                                                                                                                                   |

| PIN             | Pin Name                                                                                                                                                                          |

| 0xzzz           | Hexadecimal number (value zzz)                                                                                                                                                    |

| zzh             | Hexadecimal number (value zz)                                                                                                                                                     |

| rsvd            | Reserved memory location. Must write 0, read value indeterminate                                                                                                                  |

| code            | Instruciton code                                                                                                                                                                  |

| Multi Word Name | Used for multiple words that are considered a single unit, such as: <i>Resource Allocate</i> message, or <i>Connection Label</i> , or <i>Decrement Stack Pointer</i> instruction. |

| Section Name    | Section or Document name.                                                                                                                                                         |

| VAL             | Over-bar indicates active low pin or register bit                                                                                                                                 |

| bREG            | Single byte MOST register                                                                                                                                                         |

| mBUF            | Multi-byte MOST buffer                                                                                                                                                            |

| х               | Don't care                                                                                                                                                                        |

#### **Data Sheet Versions**

| Doc. Number | Date      | Description                    |

|-------------|-----------|--------------------------------|

| DS8805AP2   | Aug. 2001 | First released Data Sheet      |

| DS8805AP3   | Mar. 2002 | Second released Data Sheet     |

| DS8805AP4   | July 2002 | Third released Data Sheet      |

| DS8805FP5   | Apr. 2003 | First Final Product Data Sheet |

### MOST System On Chip TABLE OF CONTENTS

| LIST OF FIGURES                                                     | 8  |

|---------------------------------------------------------------------|----|

| LIST OF TABLES                                                      |    |

| 1 OVERVIEW                                                          | 15 |

|                                                                     |    |

| 1.1 Host Controller                                                 |    |

| 1.2 Control Bus and Peripherals                                     |    |

| 1.3 MOST Processor and the Routing Bus                              |    |

| 1.3.1 Source Data Ports                                             |    |

| 1.3.2 Source Data Converters                                        |    |

| 1.4 DSP Processors                                                  |    |

| 1.5 MOST NetServices API                                            |    |

| 2 HOST CONTROLLER AND CONTROL BUS PERIPHERALS                       | 25 |

| 2.1 Architecture                                                    | 25 |

| 2.1.1 Program Memory                                                | 27 |

| 2.1.1.1 Flash Memory                                                | 29 |

| 2.1.2 Data Memory                                                   | 32 |

| 2.1.3 Program and Interrupt Controller                              | 32 |

| 2.1.4 Execution Unit                                                |    |

| 2.1.5 Address Generation Unit                                       |    |

| 2.1.5.1 Immediate Data                                              |    |

| 2.1.5.2 Inherent                                                    |    |

| 2.1.5.3 Register Addressing                                         |    |

| 2.1.5.4 Direct Addressing                                           |    |

| 2.1.5.5 Indirect Addressing                                         |    |

| 2.1.5.6 Program Memory Indirect Addressing Mode                     |    |

| 2.1.6 Instruction Summary                                           |    |

| 2.2 Inter-Processor Communications                                  |    |

| 2.2.1 MOST Processor COM Port                                       |    |

| 2.2.2 DSP0 COM Port                                                 |    |

| 2.2.3 DSP1 COM Port                                                 |    |

| 2.2.4 DSP Debug Interface                                           |    |

| 2.3 Control Bus Peripherals                                         |    |

| 2.3.1 Clock Manager                                                 |    |

| 2.3.1.1 Crystal Pins                                                |    |

| 2.3.2 Global Timer<br>2.3.3 Control Port                            |    |

| 2.3.3 Control Port                                                  |    |

| 2.3.3.1 I2C Slave Format<br>2.3.3.2 Oasis-Specific Slave SPI Format |    |

| 2.3.3.3 Generic Slave SPI Format                                    |    |

| 2.3.4 Debug Port                                                    |    |

| 2.3.5 USARTs                                                        |    |

| 2.3.6 GPIO Pins and GP Timer                                        |    |

| 2.3.7 Global Control                                                |    |

| 2.3.8 EGPIO                                                         |    |

| 2.3.9 DC Measurement ADC                                            |    |

| 2.3.10 Source Converter Control                                     |    |

| 2.3.10.1 MPX ADC                                                    |    |

| 2.3.10.2 Microphone ADC                                             |    |

| 2.3.10.3 Stereo Audio ADCs                                          |    |

| 2.3.10.4 Quad Audio DACs                                            |    |

|                                                                     | -  |

### **MOST System On Chip**

| 2.3.11 DSP Program Control                                 | 91  |

|------------------------------------------------------------|-----|

| 2.3.12 DSP0 External Memory Configuration                  |     |

| 2.3.13 Watchdog Timer                                      |     |

| 2.3.13.1 Reset Generator                                   |     |

| 2.3.14 Power Supply Monitor                                |     |

| 2.4 Control Bus I/O Register Summary                       |     |

| 3 MOST INTERFACE AND ROUTING BUS                           | 103 |

| 3.1 Host Controller COM Port                               |     |

| 3.2 MOST Transceiver                                       |     |

|                                                            |     |

| 3.2.1 MOST Routing Table (MRT) and Routing Ports           |     |

| 3.2.2 SPDIF Mode (SR0/SX0)                                 |     |

| 3.2.3 MOST Configuration Registers                         |     |

| 3.2.4 MOST Control Message Registers                       |     |

| 3.2.4.1 System Control Messages                            |     |

| 3.2.5 Packet Data Transfer                                 |     |

| 3.2.5.1 Packet Data Handling                               |     |

| 3.2.6 Configurable Routing Registers                       |     |

| 3.3 Source Ports                                           |     |

| 3.4 MOST Register Summary                                  |     |

| 4 DIGITAL SIGNAL PROCESSORS                                |     |

| 4.1 Architecture                                           |     |

| 4.1.1 Program Memory                                       |     |

| 4.1.2 Vector Memory                                        |     |

| 4.1.3 Pointer Memory                                       |     |

| 4.1.4 Program Controller                                   |     |

| 4.1.5 Interrupt Controller                                 |     |

| 4.1.6 Execution Unit                                       |     |

| 4.1.7 Address Generation Unit                              | 152 |

| 4.1.7.1 Register Addressing Mode                           |     |

| 4.1.7.2 Direct Addressing Mode                             |     |

| 4.1.7.3 Indirect Addressing Mode                           |     |

| 4.1.8 Instruction Summary                                  |     |

| 4.2 Global Timer Peripheral                                |     |

| 4.3 Inter-Processor Communications                         |     |

| 4.3.1 MOST Routing Port                                    |     |

| 4.3.2 Host Controller COM Port                             |     |

| 4.3.3 Host Controller Debug COM Port                       |     |

| 4.3.4 Inter-DSP FIFO Port<br>4.4 Asynchronous Source Ports |     |

| 4.4.1 Async. Source Port Timer                             |     |

| 4.4.1 Async. Source Port Timer                             |     |

| 4.4.2.1 S/PDIF Format                                      |     |

| 4.5 Source Converter Volume Control                        |     |

| 4.6 Unique DSP Peripherals                                 |     |

| 4.6.1 DSP0 External Data Memory Interface                  |     |

| 4.6.1.1 External Memory Addressing                         |     |

| 4.6.1.2 DSP0 External Memory Register Description          |     |

| 4.6.1.3 Write Operation                                    |     |

| 4.6.1.4 Read Operation                                     |     |

| 4.6.1.5 Programming Examples                               | 182 |

|                                                            |     |

### **MOST System On Chip**

| -                             |                                            |           |

|-------------------------------|--------------------------------------------|-----------|

|                               | 3                                          |           |

|                               |                                            |           |

| 5.2 Microphone ADC            |                                            |           |

|                               |                                            |           |

| 5.4 Stereo Audio ADCs         |                                            |           |

| 6 ELECTRICAL CHARAC           | TERISTICS                                  | 199       |

| 6.1 Absolute Maximum Ratin    | gs                                         |           |

|                               | Conditions                                 |           |

|                               | ,                                          |           |

|                               |                                            |           |

| 6.5 Switching Characteristics |                                            |           |

| -                             | y Interface                                |           |

| <b>-</b>                      | erface                                     |           |

| 6.8 Source Data Ports         |                                            |           |

| 6.9 DSP Async. Source Ports   | 5                                          | 210       |

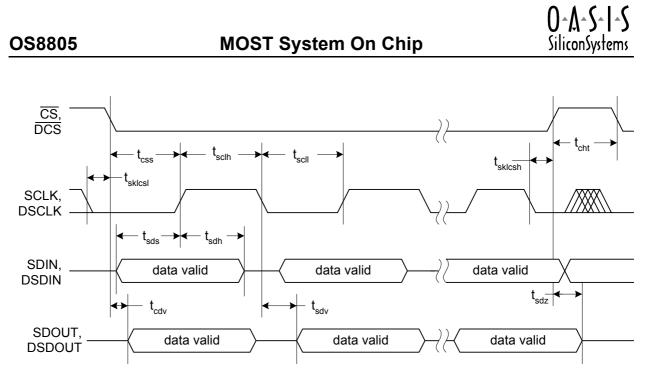

| 6.10 Control and Debug Ports  | s - SPI Mode                               | 211       |

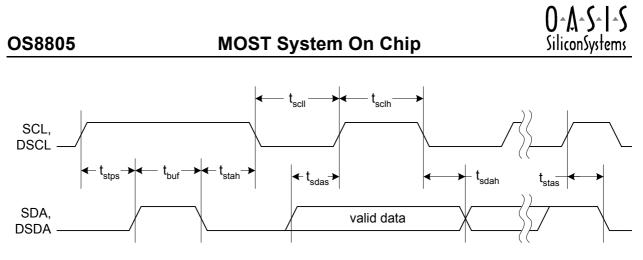

| 6.11 Control and Debug Ports  | s - I2C Mode                               | 213       |

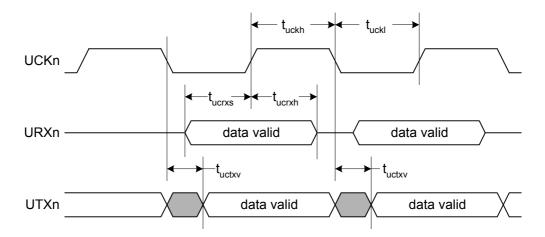

| 6.12 Control and Debug Ports  | s - USART mode                             | 215       |

| 6.13 Analog Performance       |                                            | 216       |

|                               |                                            |           |

|                               |                                            |           |

|                               |                                            |           |

|                               |                                            |           |

|                               |                                            |           |

|                               | NG                                         |           |

|                               |                                            |           |

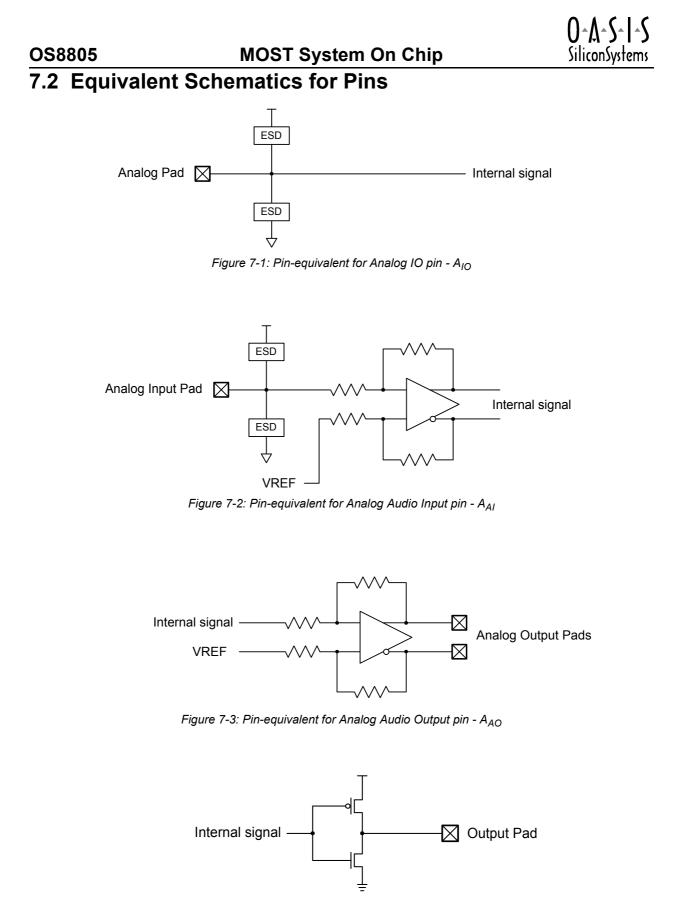

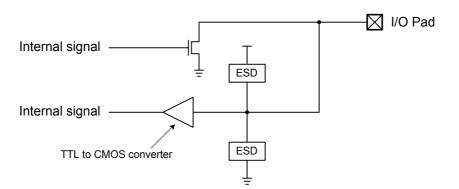

| 7.2 Equivalent Schematics fo  | r Pins                                     |           |

|                               |                                            |           |

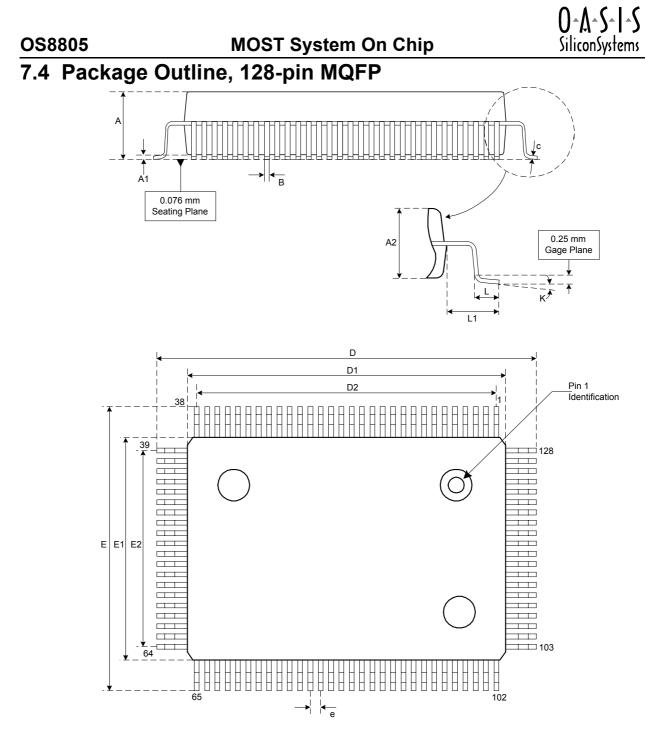

| 7.4 Package Outline, 128-pin  | MQFP                                       | 232       |

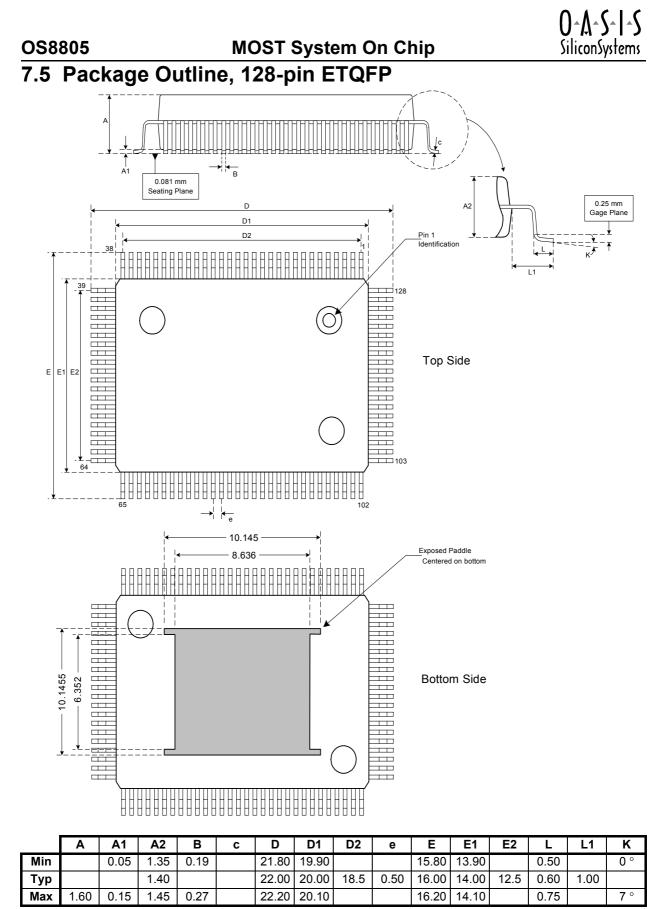

| 7.5 Package Outline, 128-pin  | ETQFP                                      | 233       |

| <b>8 APPLICATION INFORM</b>   | ATION                                      |           |

| 8.1 Power Supplies and Anal   | og Components                              |           |

|                               | -9                                         |           |

|                               | perature                                   |           |

|                               | n                                          |           |

|                               | . OS8804                                   |           |

|                               |                                            |           |

|                               |                                            |           |

|                               |                                            |           |

| APPENDIX B: REVISION          | HISTORY                                    |           |

| INDEX                         |                                            |           |

| Final Product Data Sheet      | © Copyright 2001-2003 Oasis SiliconSystems | DS8805FP5 |

### MOST System On Chip

## LIST OF FIGURES

| Figure 1-1:  | MOST Hardware/Software System Overview                     |     |

|--------------|------------------------------------------------------------|-----|

| Figure 1-2:  | OS8805 Block Diagram                                       | 17  |

| Figure 1-3:  | Host Controller and Control Bus                            | 19  |

| Figure 1-4:  | MOST Processor Overview                                    | 21  |

| Figure 1-5:  | DSP Overview                                               | 23  |

| Figure 2-1:  | Control Bus                                                |     |

| Figure 2-2:  | Host-Controller Opcode Architecture                        | 26  |

| Figure 2-3:  | Host Controller External Program Memory Diagram            | 27  |

| Figure 2-4:  | User Interrupt Vector Table                                | 29  |

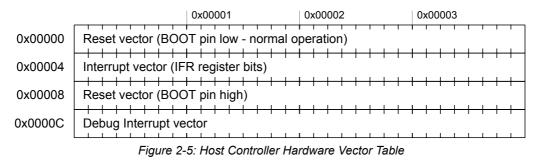

| Figure 2-5:  | Host Controller Hardware Vector Table                      | 35  |

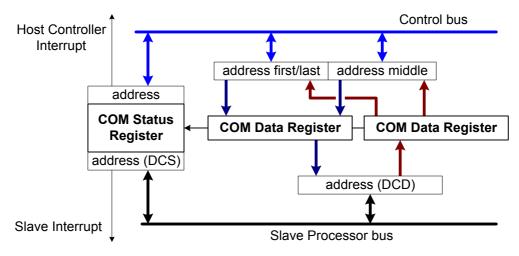

| Figure 2-6:  | Generic COM Port                                           | 41  |

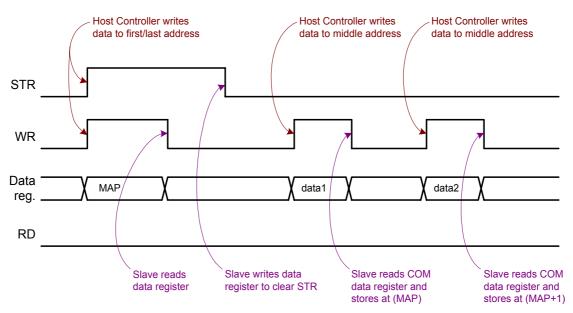

| Figure 2-7:  | Generic COM Port Write Sequence                            | 42  |

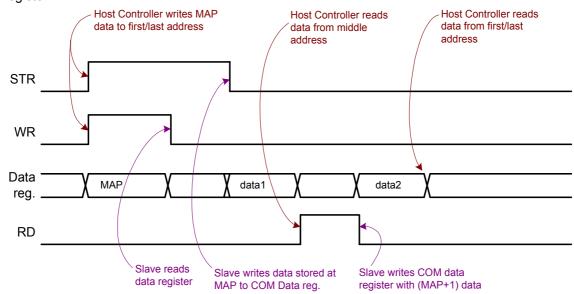

| -            | Generic COM Port Read Sequence                             | 43  |

|              | Clock Manager                                              |     |

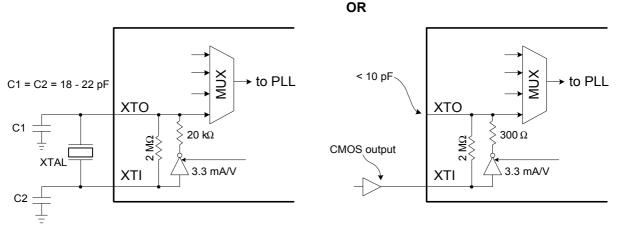

| Figure 2-10: | Crystal Oscillator Input                                   | 49  |

|              | Global Timer                                               |     |

| -            | Global Timer Timing                                        |     |

| -            | Control Port                                               |     |

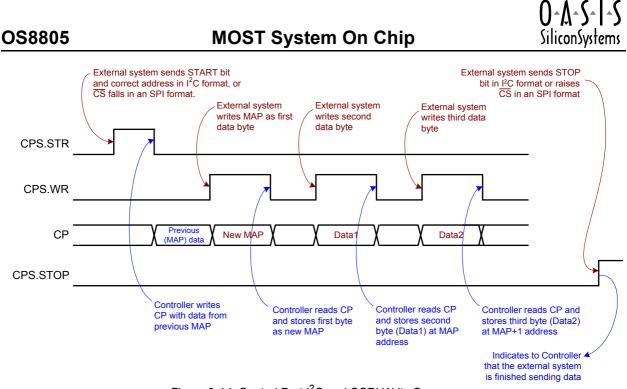

| •            | Control Port I2C and OSPI Write Sequence                   |     |

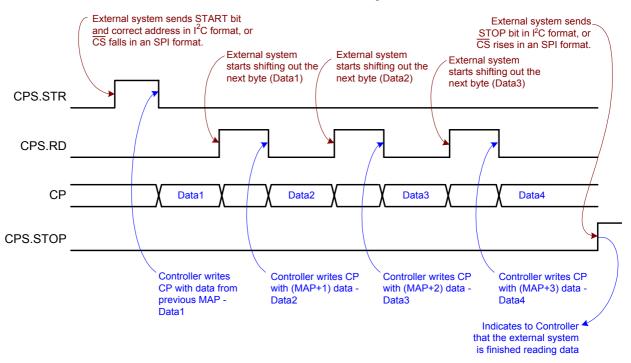

|              | Control Port I2C and OSPI Read Sequence (slave)            |     |

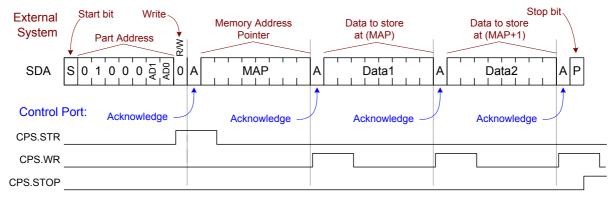

|              | Control Port I2C Slave Write Sequence                      |     |

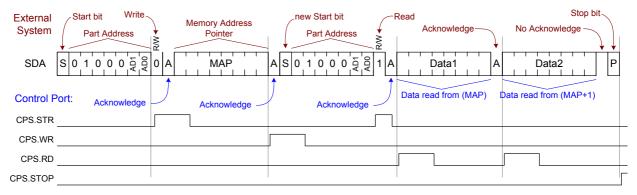

|              | Control Port I2C Slave Read Sequence                       |     |

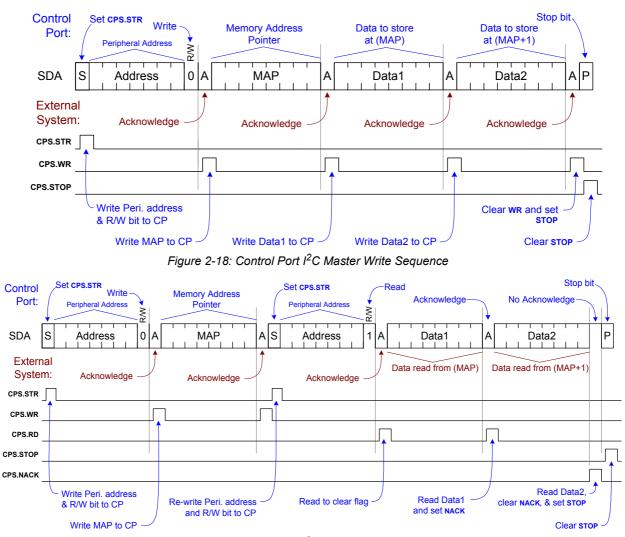

|              | Control Port I <sup>2</sup> C Master Write Sequence        |     |

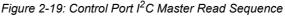

|              | Control Port I <sup>2</sup> C Master Read Sequence         |     |

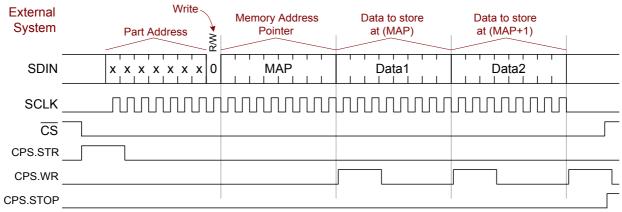

| -            | Control Port OSPI Write Sequence                           |     |

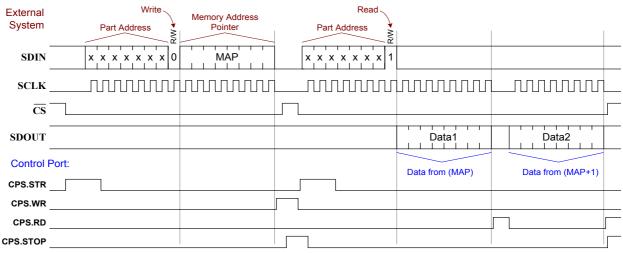

|              | Control Port OSPI Read Sequence                            |     |

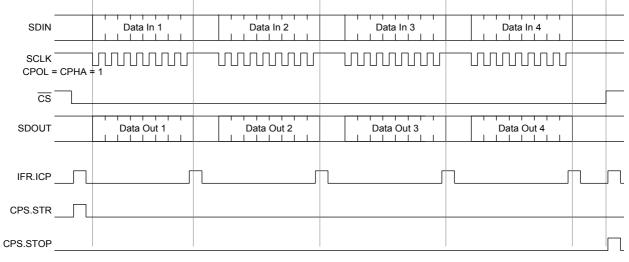

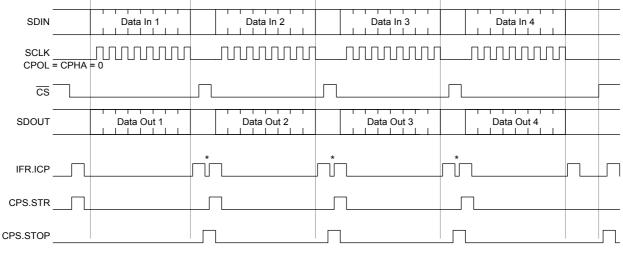

|              | Control Port Generic SPI Sequence (CPHA set)               |     |

|              | Control Port Generic SPI Sequence (CPHA clear)             |     |

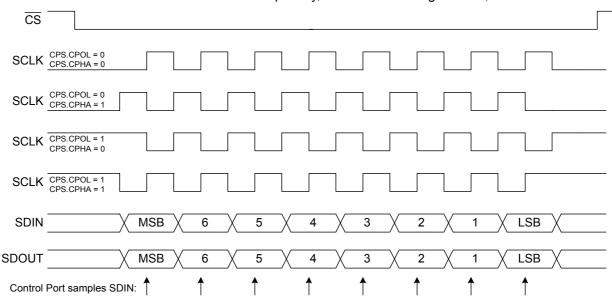

|              | Control Port Generic SPI SCLK Format                       |     |

|              | Debug Port                                                 |     |

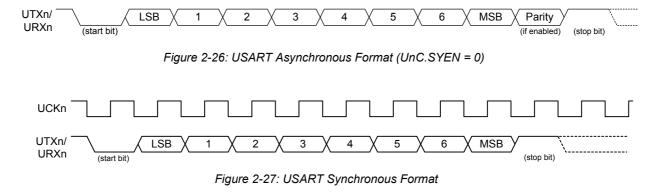

| Figure 2-26: | USART Asynchronous Format (UnC.SYEN = 0)                   | 67  |

|              | USART Synchronous Format                                   |     |

|              | GP Timer                                                   |     |

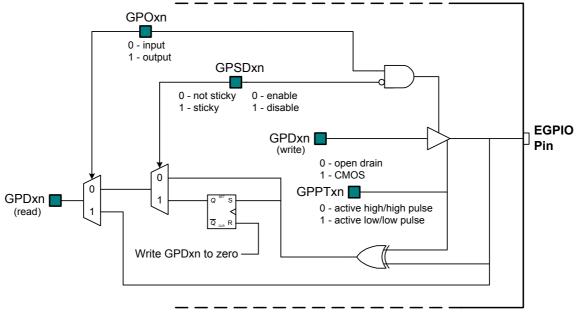

| •            | EGPIO Conceptual Logic                                     |     |

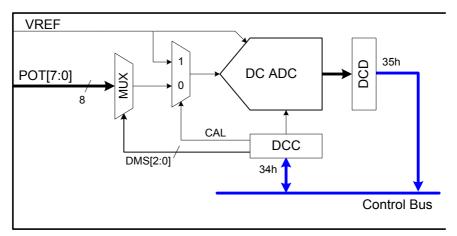

|              | DC Measurement ADC                                         |     |

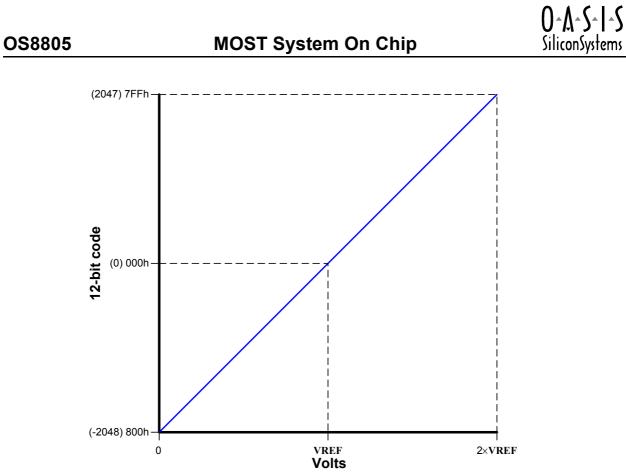

| Figure 2-31: | DC ADC Transfer Function (12-bits)                         |     |

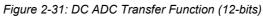

|              | Source Converters                                          |     |

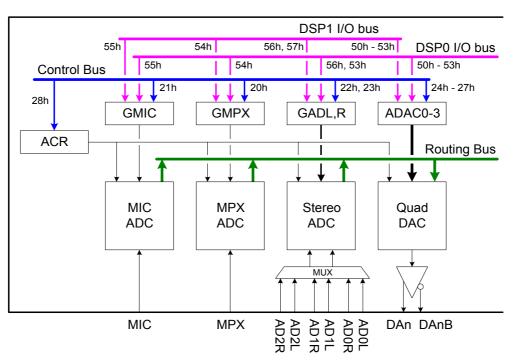

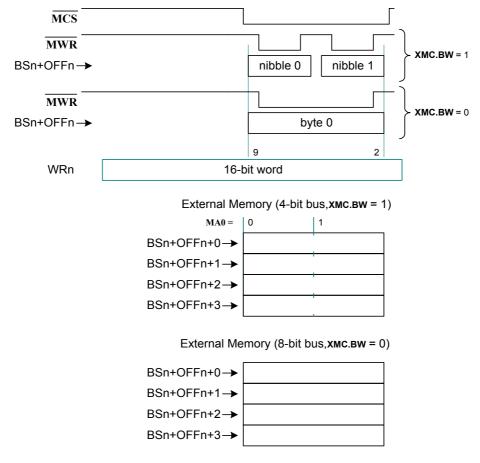

| Figure 2-33: | External Data Memory Port with 16-bit words (XMC.MWW set)  | 95  |

|              | External Data Memory Port with 8-bit words (XMC.MWW clear) |     |

|              | Routing Bus                                                |     |

| Figure 3-2:  | MOST Routing Table (Destinations)                          | 106 |

| Figure 3-3:  | MRA Routing Addresses (Sources)                            | 106 |

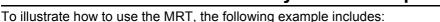

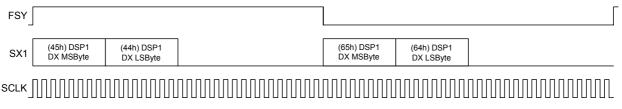

| Figure 3-4:  | MRT Example - Step 1                                       | 107 |

| Figure 3-5:  | MRT Example - Source Port Routing                          |     |

| Figure 3-6:  | MRT Example - Finished Table                               | 109 |

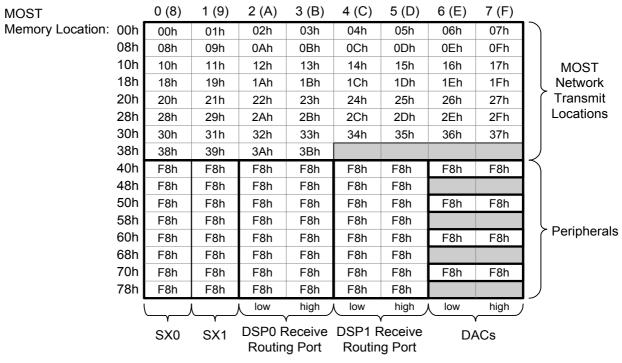

| Figure 3-7:  | MRT Power-Up Defaults                                      | 110 |

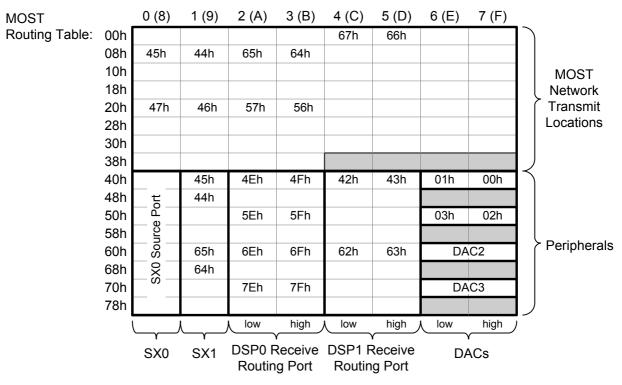

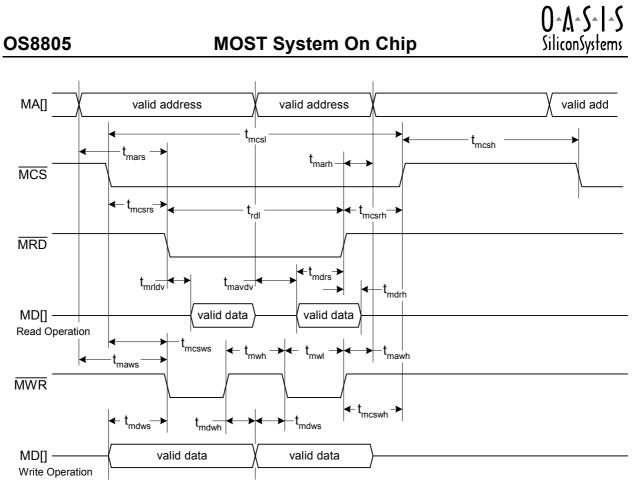

| Figure 3-8:  | MRT Addresses with respect to Source Port Timing           |     |

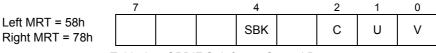

| Figure 3-9:  |                                                            |     |

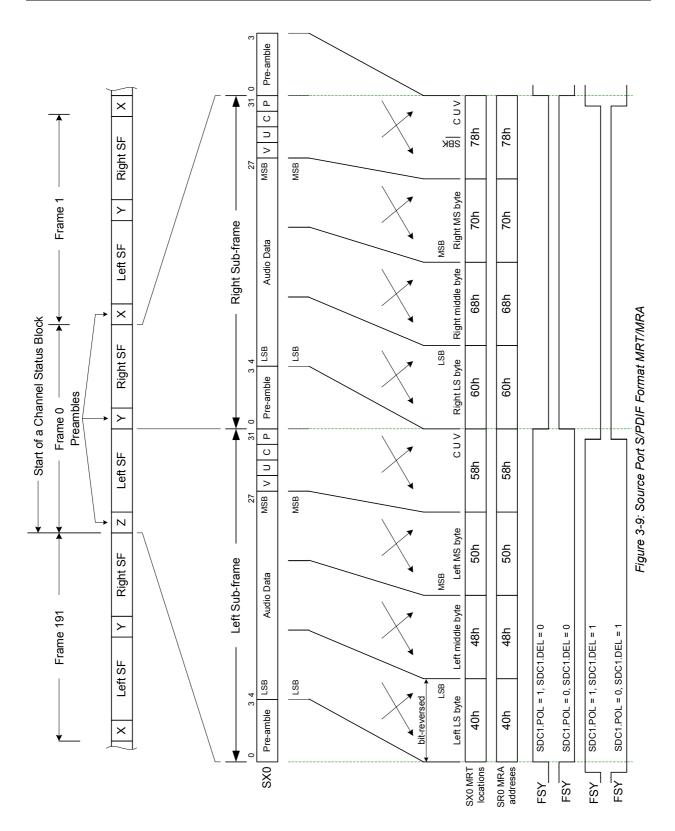

|              | MOST Transceiver Errors and ERR Pin                        |     |

| •            | Control Message Buffers                                    |     |

|              | Packet Data Transfer Polling                               |     |

### **MOST System On Chip**

| •             | ReRoute Example - MRT                                          |     |

|---------------|----------------------------------------------------------------|-----|

|               | ReRoute Example - MRA                                          |     |

|               | MOST Source Ports                                              |     |

|               | Source-Port SCLK Output Timing (bSDC1.EDG = 0)                 |     |

|               | DSP0 I/O Bus                                                   |     |

| Figure 4-2:   | DSP1 I/O Bus                                                   |     |

| Figure 4-3:   | DSP Memory Architecture                                        | 143 |

|               | DSP Vector Table                                               |     |

|               | DSP Source Data Alignment                                      |     |

|               | DSP Destination Data Alignment                                 |     |

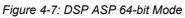

|               | DSP ASP 64-bit Mode                                            |     |

|               | DSP ASP 128-bit Mode                                           |     |

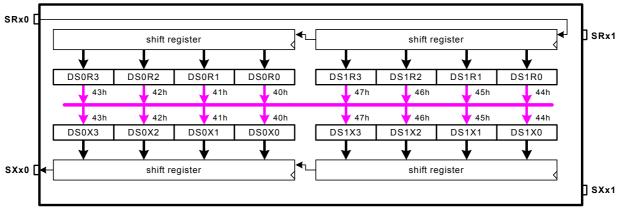

| Figure 4-9:   | DSP Async. Source Port S/PDIF Alignment - 64 Bits/Interrupt    | 171 |

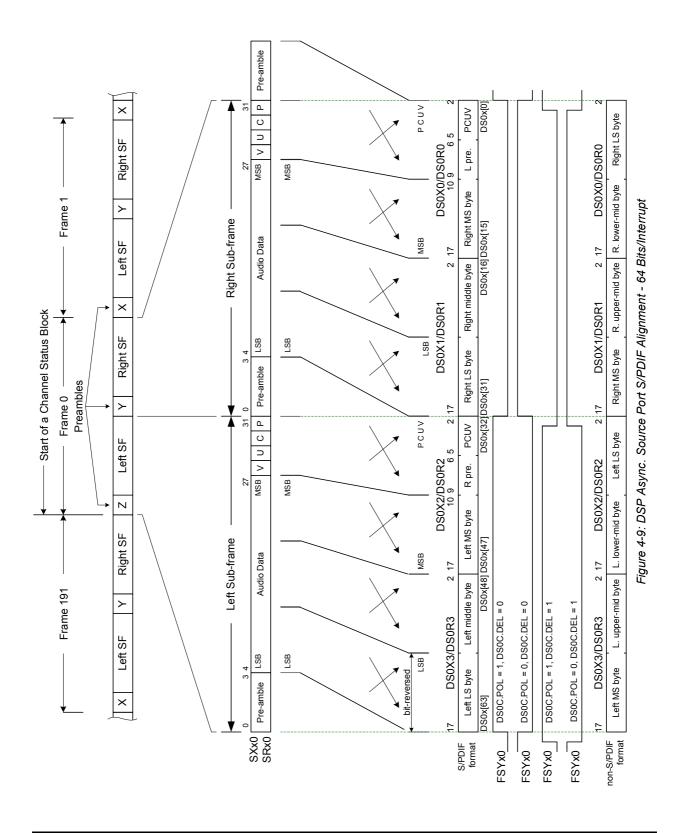

| Figure 4-10:  | DSP Async. Source Port S/PDIF Alignment - 128 Bits/Interrupt   | 172 |

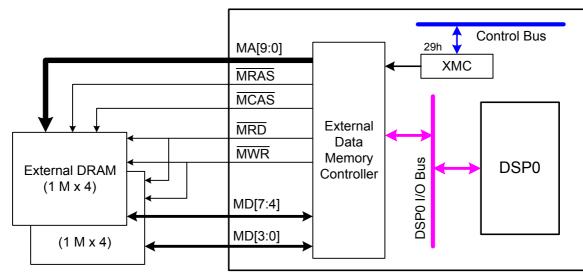

| Figure 4-11:  | DSP0 External DRAM Interface                                   | 175 |

| Figure 4-12:  | DSP0 External SRAM Interface                                   | 175 |

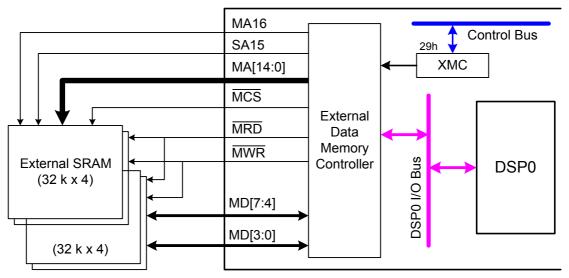

| Figure 4-13:  | DSP0 External Memory Controller                                | 176 |

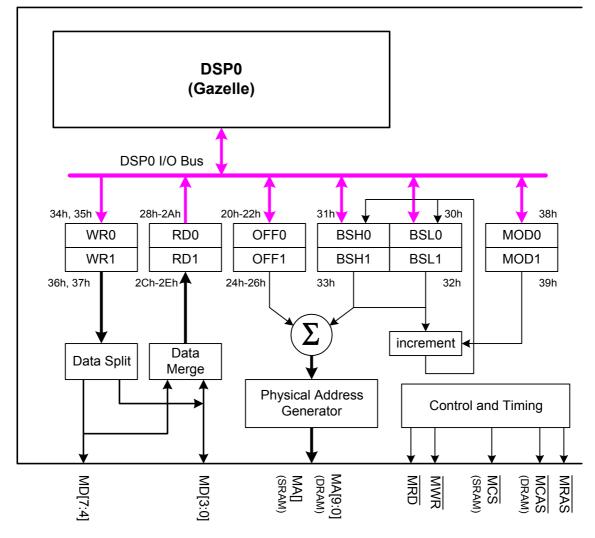

| Figure 4-14:  | DSP0 PWM DACs                                                  | 184 |

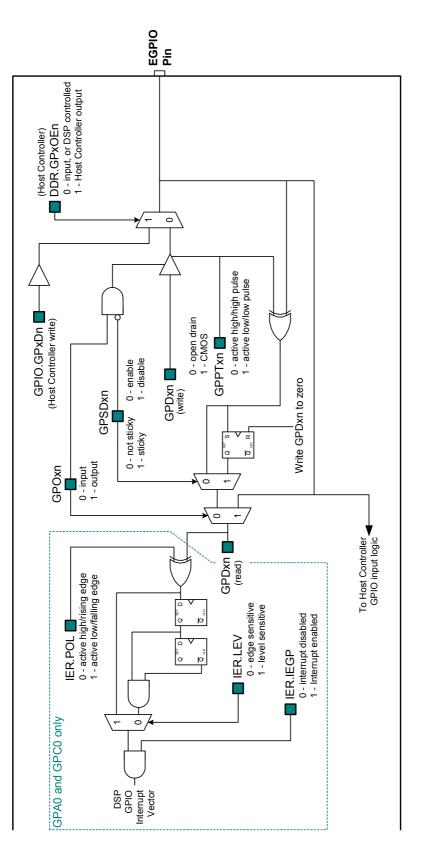

| Figure 4-15:  | DSP EGPIO Conceptual Logic                                     | 187 |

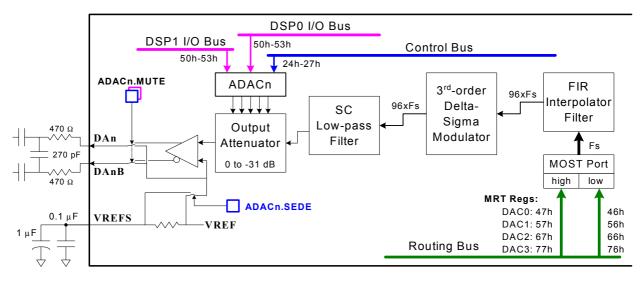

| Figure 5-1:   | DAC Block Diagram                                              | 195 |

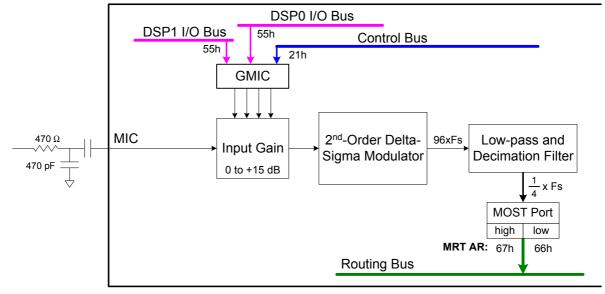

| Figure 5-2:   | Mic ADC                                                        | 196 |

| Figure 5-3:   | MPX ADC                                                        | 197 |

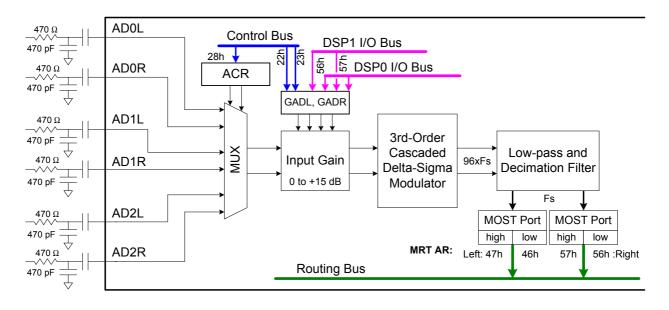

| Figure 5-4:   | Stereo Audio ADCs                                              | 198 |

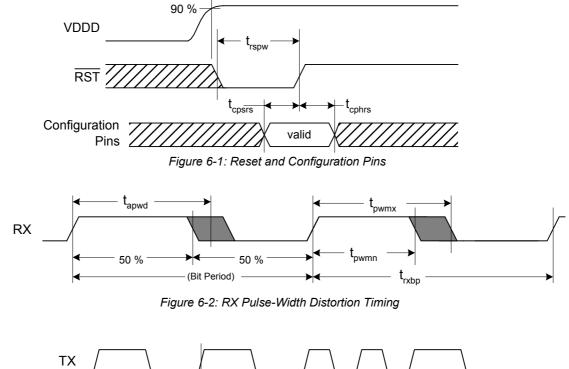

| Figure 6-1:   | Reset and Configuration Pins                                   | 202 |

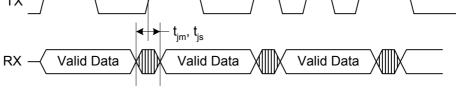

|               | RX Pulse-Width Distortion Timing                               |     |

|               | RX Jitter Tolerance Timing                                     |     |

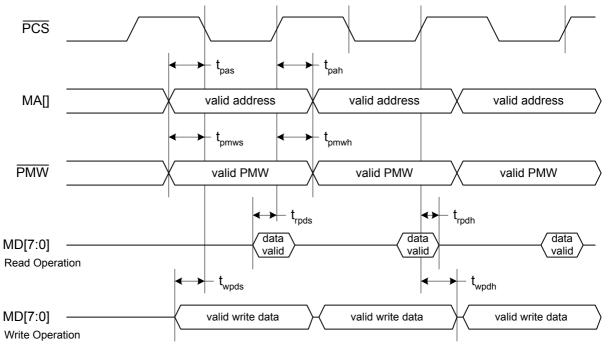

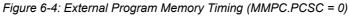

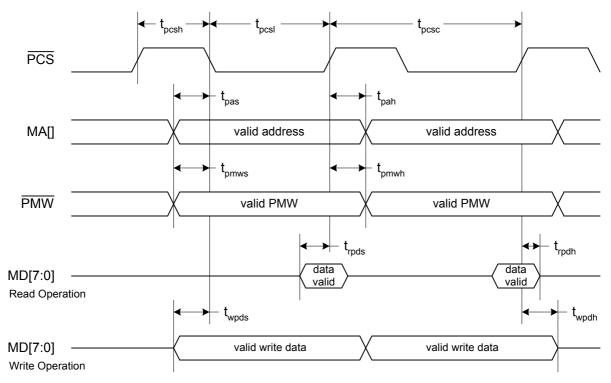

| Figure 6-4:   | External Program Memory Timing (MMPC.PCSC = 0)                 | 203 |

| Figure 6-5:   | External Program Memory Timing (MMPC.PCSC = 1)                 | 204 |

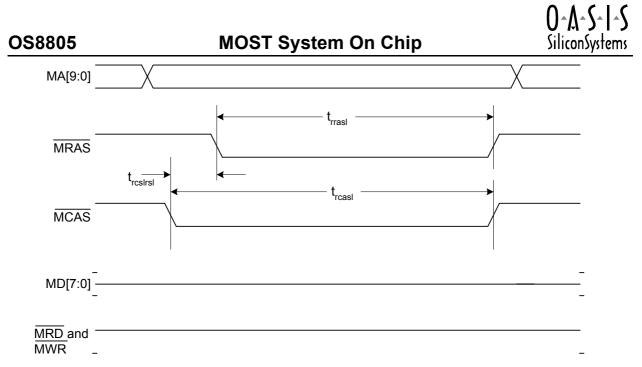

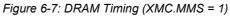

| Figure 6-6:   | DRAM Refresh (CAS-before-RAS) Timing (XMC.MMS = 1)             | 206 |

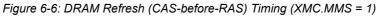

|               | DRAM Timing (XMC.MMS = 1)                                      |     |

|               | SRAM Timing (XMC.MMS = 0)                                      |     |

| -             | Source Port Timing                                             |     |

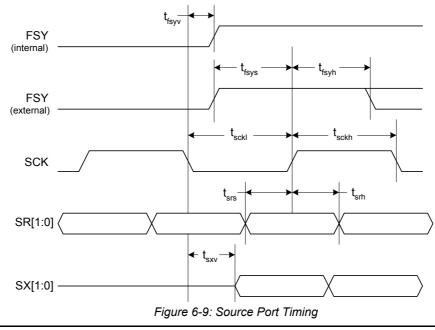

|               | DSP Async. Source Port Timing                                  |     |

| •             | Control/Debug Port - SPI Timing                                |     |

|               | Control/Debug Port - I2C Timing                                |     |

|               | Control/Debug Port - USART Timing                              |     |

| •             | Pin-equivalent for Analog IO pin - AIO                         |     |

|               | Pin-equivalent for Analog Audio Input pin - AAI                |     |

| Figure 7-3:   | Pin-equivalent for Analog Audio Output pin - AAO               |     |

| Figure 7-5:   | Pin-equivalent for Digital Output pin - DOUT                   |     |

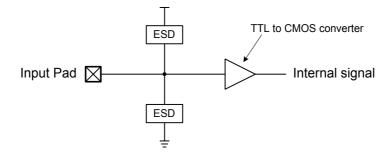

| Figure 7-4:   | Pin-equivalent for Digital Input pin - DIN                     |     |

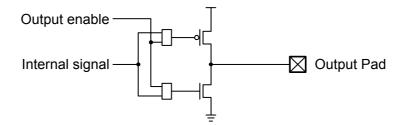

| Figure 7-6:   | Pin-equivalent for Digital Output with high-Z control - DOUTZ  |     |

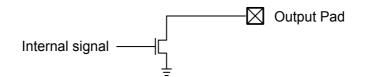

| Figure 7-7:   | Pin-equivalent for Open-Drain Digital Output pin - DOUTD       |     |

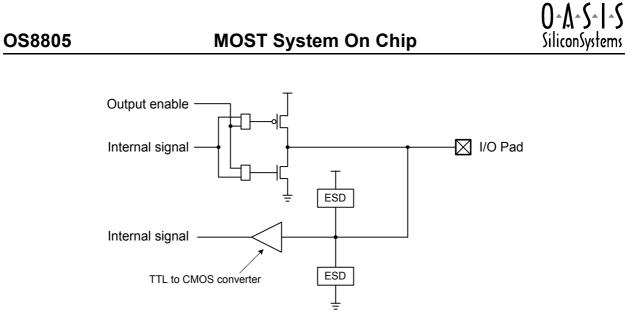

| Figure 7-8:   | Pin-equivalent for Digital I/O pin - DI/O                      |     |

| Figure 7-9:   | Pin-equivalent for Digital Input/Open-Drain Output pin - DI/OD |     |

| •             | OS8805 Functional Pinout                                       |     |

| •             | OS8805 General Purpose I/O Pinout                              |     |

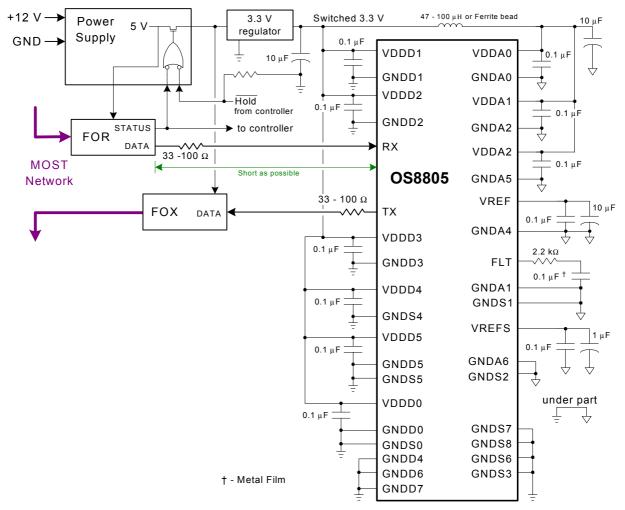

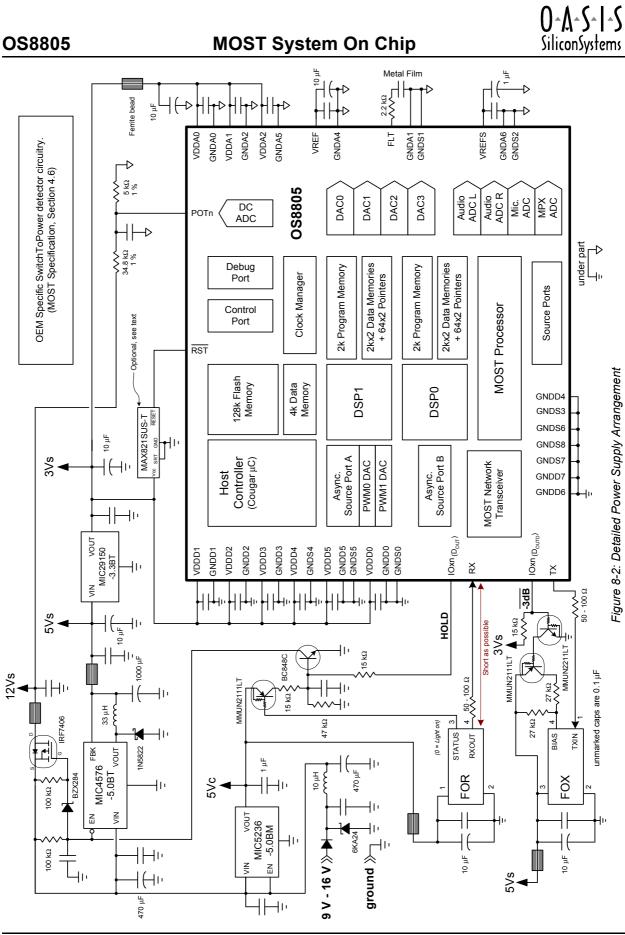

|               | Power Supply Overview Diagram                                  |     |

| Figure 8-2:   | Detailed Power Supply Arrangement                              |     |

| - igui 0 0-2. | Botaliou i ouch ouch i vitaligement                            | 201 |

### MOST System On Chip

### LIST OF TABLES

| Table 2-1:  | Single-Operand Instructions                | .26 |

|-------------|--------------------------------------------|-----|

| Table 2-2:  | Dual-Operand Instructions                  | .27 |

| Table 2-3:  | MMPC Register                              | .28 |

| Table 2-4:  | FMC Register                               | .30 |

| Table 2-5:  | Flash Memory Programming Times (in µs)     | .30 |

| Table 2-6:  | FPBK Register                              |     |

| Table 2-7:  | FPB16 Register                             |     |

| Table 2-8:  | IO Write Locations for FPBK and FPB16 Bits | .32 |

| Table 2-9:  | SPC Register                               | .32 |

| Table 2-10: | SPCH Register                              |     |

|             | DSPC Register                              |     |

|             | DSPCH Register                             |     |

|             | SR Register                                |     |

|             | IFL Register                               |     |

|             | IER Register                               |     |

|             | SP Register                                |     |

|             | PGMP Register                              |     |

|             | Host Controller Instruction Set Summary    |     |

|             | RCS Register                               |     |

|             | RCF, RCM Registers                         |     |

|             | D0CS Register                              |     |

|             | D0CF, D0CM Registers                       |     |

|             | D1CS Register                              |     |

|             | D1CF, D1CM Registers                       |     |

| Table 2-24. | DDOCS Register                             | 45  |

|             | DD0CF, DD0CM Registers                     |     |

|             | DDUCF, DDUCM Registers<br>DD1CS Register   |     |

|             |                                            |     |

|             | DD1CF, DD1CM Registers                     |     |

|             | D0TSPC Register                            |     |

|             | D1TSPC Register                            |     |

|             | CMCS Register                              |     |

|             | CM4 Register                               |     |

|             | Crystal Oscillator Frequencies             |     |

|             | GTR Register                               |     |

|             | CPS Register                               |     |

|             | CP Register                                |     |

|             | DCPS Register                              |     |

|             | DCP Register                               |     |

|             | U0C Register                               |     |

|             | U0DV Register                              |     |

|             | UnDV Values for Standard BAUD Rates        |     |

|             | U0RX Register                              |     |

|             | U0TX Register                              |     |

|             | U1C Register                               |     |

|             | U1DV Register                              |     |

|             | U1RX Register                              |     |

|             | U1TX Register                              |     |

|             | CMP0 Register                              |     |

|             | CMP1 Register                              |     |

|             | CAP0 Register                              |     |

| Table 2-51: | CAP0 Register                              | .74 |

### **MOST System On Chip**

### O-A-S-I-S SiliconSystems

|                |                                                        | Jinconsystems |

|----------------|--------------------------------------------------------|---------------|

| Table 2-52:    | TMR Register                                           | 75            |

| Table 2-53:    | TMOD Register                                          | 75            |

| Table 2-54:    | GPIO Register                                          |               |

|                | GPC Register                                           |               |

|                | DDR Register                                           |               |

| Table 2-57:    | GCTL Register                                          | 77            |

| Table 2-58:    | EGPIO Enable Summary                                   | 79            |

| Table 2-59:    | EGPD1 Register                                         | 80            |

| Table 2-60:    | EGPD2 Register                                         | 80            |

| Table 2-61:    | EGPD3 Register                                         | 80            |

|                | EDD1 Register                                          |               |

|                | EDD2 Register                                          |               |

|                | EDD3 Register                                          |               |

|                | IPOT1 Register                                         |               |

|                | IPOT2 Register                                         |               |

|                | IPOT3 Register                                         |               |

|                | ISOD1 Register                                         |               |

|                | ISOD2 Register                                         |               |

|                | ISOD3 Register                                         |               |

|                | DCC Register                                           |               |

|                | DCD Register                                           |               |

|                | DC ADC Resolution                                      |               |

|                | FPCR Register                                          |               |

|                | ACR Register                                           |               |

|                | ACR Register                                           |               |

|                | GMPX Register                                          |               |

|                | GMIC Register                                          |               |

|                | GADL Register                                          |               |

|                | GADR Register                                          |               |

| Table 2-81:    | ADAC0 Register                                         |               |

| Table 2-82:    | ADAC1 Register                                         |               |

| Table 2-83:    | ADAC2 Register                                         |               |

| Table 2-84:    | ADAC3 Register                                         |               |

| Table 2-85:    | D0PCR Register                                         |               |

| Table 2-86:    | D0PDL Register                                         |               |

|                | D0PC Register                                          |               |

|                | D1PCR Register                                         |               |

|                | D1PDL Register                                         |               |

|                | D1PC Register                                          |               |

|                | XMC Register                                           |               |

|                | WDT Register                                           |               |

|                | RGEN Register                                          |               |

|                | Control Bus Register Summary                           |               |

| Table 3-1:     | MOST Processor MRA and MRT                             |               |

| Table 3-2:     | Source Converter Routing MRA and MRT                   |               |

| Table 3-3:     | Source-Port MOST Routing Table for SX0, SX1            |               |

| Table 3-4:     | Source-Port MOST Routing Addresses for SR0, SR1        |               |

| Table 3-5:     | SPDIF Sub-frame Control Byte                           |               |

| Table 3-6:     | bXCR Register                                          |               |

| Table 3-7:     | bXSR Register                                          |               |

| Table 3-8:     | bNC Register                                           |               |

| Table 3-9:     | bNPR Register                                          |               |

|                | blE Register                                           |               |

|                | bGA Register                                           |               |

|                | Data Sheet © Convright 2001-2003 Qasis Silicon Systems |               |

| Emai Product L | ISTA STREET IST CONVIONT 2001-2003 CASIS SILCONSVETAME |               |

Final Product Data Sheet Restricted Access

### **MOST System On Chip**

### O-A-S-I-S SiliconSystems

| Table 3-12:               | bNAH Register                                 | 117 |

|---------------------------|-----------------------------------------------|-----|

| Table 3-13:               | bNAL Register                                 | 118 |

| Table 3-14:               | bCM2 Register                                 | 118 |

| Table 3-15:               | bNDR Register                                 | 118 |

| Table 3-16:               | bMPR Register                                 | 118 |

| Table 3-17:               | bMDR Register                                 | 118 |

| Table 3-18:               | bSBC Register                                 | 119 |

| Table 3-19:               | bXSR2 Register                                | 119 |

| Table 3-20:               | mCRA Table                                    | 119 |

|                           | bMSGC Register                                |     |

| Table 3-22:               | bMSGS Register                                | 122 |

| Table 3-23:               | mRCMB Buffer                                  | 123 |

|                           | bXTIM Register                                |     |

|                           | bXRTY Register                                |     |

|                           | mXCMB Buffer                                  |     |

|                           | bXTS Register                                 |     |

|                           | System Control Messages - mXCMB               |     |

|                           | Resource Allocate Responses                   |     |

|                           | Resource De-allocate Responses                |     |

|                           | Remote GetSource Response                     |     |

|                           | bAPAH Register                                |     |

|                           | bAPAL Register                                |     |

|                           | bPLDT Register                                |     |

|                           | bPPI Register                                 |     |

|                           | bPCTC Register                                |     |

|                           | bPSTX Register                                |     |

|                           | bPCTS Register                                |     |

|                           | mARP Buffer                                   |     |

|                           | mAXP Buffer                                   |     |

|                           | bSPAR Register                                |     |

|                           | bFPR Register                                 |     |

|                           | bD0RP Register                                |     |

|                           | bD0RS Register                                |     |

|                           | bD1RP Register                                |     |

|                           | bD1RS Register                                |     |

|                           | bSDC1 Register                                |     |

|                           | bSDC2 Register                                |     |

|                           | MOST Routing Bus Register Summary             |     |

| Table 3-49.               | MOST Hardware Control Registers - Bit Summary |     |

| Table 3-30.<br>Table 4-1: | PC Register                                   |     |

| Table 4-2:                | PCI Register                                  |     |

| Table 4-2:                | ISPC Register                                 |     |

| Table 4-3:                | SSPC Register                                 |     |

| Table 4-4.<br>Table 4-5:  | CNT Register                                  |     |

| Table 4-6:                | END Register                                  |     |

| Table 4-0.<br>Table 4-7:  | -                                             |     |

| Table 4-7.<br>Table 4-8:  | STRT Register                                 |     |

| Table 4-6.<br>Table 4-9:  |                                               |     |

|                           | IER Register                                  |     |

|                           | •                                             |     |

|                           | SSR Register                                  |     |

|                           | SACCH Register                                |     |

|                           | SACCH Register                                |     |

|                           | TSSR Register                                 |     |

| 1 able 4-15.              | DSP Instruction Set                           | 103 |

### **MOST System On Chip**

### O-A-S-I-S SiliconSystems

| Table 4-16:  | GTR Register                                                                 | 154 |

|--------------|------------------------------------------------------------------------------|-----|

| Table 4-17:  | DR Register                                                                  | 154 |

| Table 4-18:  | DX Register                                                                  | 155 |

| Table 4-19:  | DR1 Register                                                                 | 155 |

| Table 4-20:  | DX1 Register                                                                 | 155 |

| Table 4-21:  | DCS Register                                                                 | 156 |

| Table 4-22:  | DCD Register                                                                 | 156 |

|              | DDCS Register                                                                |     |

|              | DDCD Register                                                                |     |

| Table 4-25:  | DFLS Register                                                                | 157 |

|              | DFFS Register                                                                |     |

|              | DFSD Register                                                                |     |

|              | DFWD Register                                                                |     |

|              | DFWD Register                                                                |     |

|              | DSP Async. Source Port Pins                                                  |     |

|              | DDIV0 Register                                                               |     |

|              | DDIV1 Register                                                               |     |

|              | DCAP0 Register                                                               |     |

|              | DCAP1 Register                                                               |     |

|              | DTC Register                                                                 |     |

|              | Valid Output Clocking Combinations for Async. Source Ports                   |     |

|              | DS0R0 Register                                                               |     |

|              | DS0R1 Register                                                               |     |

|              | DS0R2 Register                                                               |     |

|              | DS0R3 Register                                                               |     |

|              | DS1R0 Register                                                               |     |

|              | DS1R1 Register                                                               |     |

|              | DS1R2 Register                                                               |     |

|              | DS1R3 Register                                                               |     |

|              | DS0X0 Register                                                               |     |

|              | DS0X1 Register                                                               |     |

|              | DS0X2 Register                                                               |     |

|              | DS0X2 Register                                                               |     |

|              | DS0X5 Register                                                               |     |

|              | DS1X0 Register                                                               |     |

|              | DS1X1 Register                                                               |     |

|              | DS1X2 Register                                                               |     |

|              |                                                                              |     |

|              | DS0C Register                                                                |     |

|              | DS1C Register<br>Valid S/PDIF Clocking Combinations for Async. Source Port 0 |     |

|              | ADAC0 Register                                                               |     |

|              | 5                                                                            |     |

|              | ADAC1 Register                                                               |     |

|              | ADAC2 Register                                                               |     |

|              | ADAC3 Register                                                               |     |

|              | GMPX Register                                                                |     |

|              | GMIC Register                                                                |     |

|              | GADL Register                                                                |     |

|              | GADR Register                                                                |     |

|              | DSP Cycles for EMI Access                                                    |     |

|              | OFF0 Register                                                                |     |

|              | OFF0+- Register                                                              |     |

|              | OFF0++ Register                                                              |     |

|              | OFF1 Register                                                                |     |

| i adle 4-69: | OFF1+- Register                                                              | 1/8 |

Final Product Data Sheet Restricted Access

### **MOST System On Chip**

### O-A-S-I-S SiliconSystems

|             |                                       | · · · · · · · · · · · · · · · · · · · |

|-------------|---------------------------------------|---------------------------------------|

| Table 4-70: | OFF1++ Register                       |                                       |

|             | RD0 Register                          |                                       |

|             | RD0+- Register                        |                                       |

|             | RD0++ Register                        |                                       |

| Table 4-74: | RD1 Register                          |                                       |

|             | RD1+- Register                        |                                       |

|             | RD1++ Register                        |                                       |

|             | BSL0 Register                         |                                       |

| Table 4-78: | BSH0 Register                         |                                       |

|             | BSL1 Register                         |                                       |

| Table 4-80: | BSH1 Register                         |                                       |

|             | WR0+- Register                        |                                       |

|             | WR0++ Register                        |                                       |

|             | WR1+- Register                        |                                       |

| Table 4-84: | WR1++ Register                        |                                       |

| Table 4-85: | MOD0 Register                         |                                       |

| Table 4-86: | MOD1 Register                         |                                       |

| Table 4-87: | PWMD Register                         |                                       |

| Table 4-88: | PWM1D Register                        |                                       |

| Table 4-89: | EGPD Register                         |                                       |

| Table 4-90: | EDD Register                          |                                       |

| Table 4-91: | IPOT Register                         |                                       |

| Table 4-92: | ISOD Register                         |                                       |

| Table 4-93: | EGPD Register                         |                                       |

|             | EDD Register                          |                                       |

|             | IPOT Register                         |                                       |

| Table 4-96: | ISOD Register                         |                                       |

|             | DSP0 Register Summary                 |                                       |

| Table 4-98: | DSP1 Register Summary                 | 193                                   |

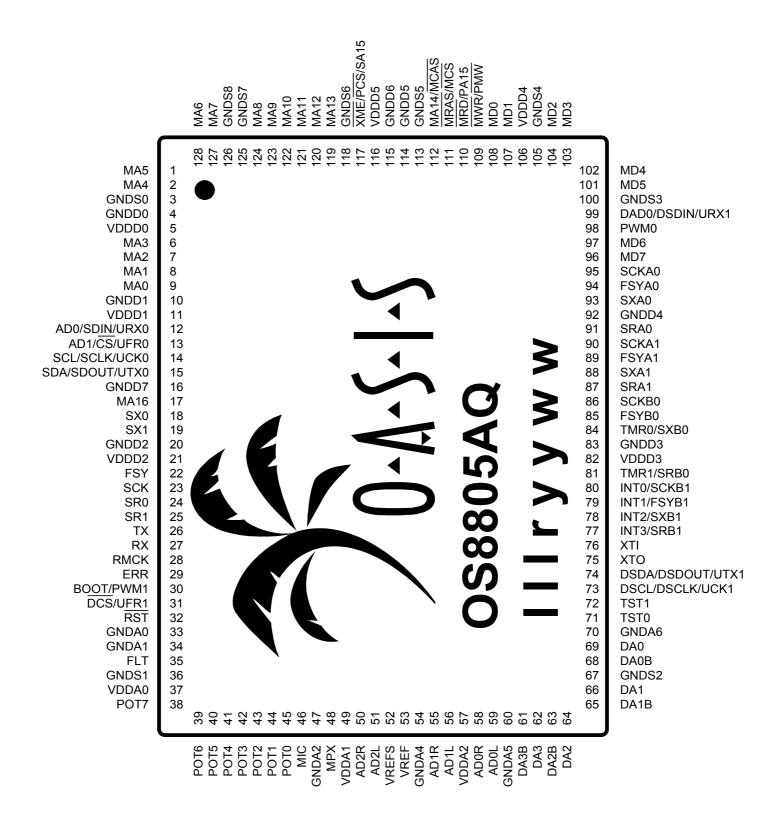

| Table 7-1:  | Pinout List                           | 221                                   |

| Table 7-2:  | Package Outline Dimensions (mm)       | 232                                   |

| Table 7-3:  | Package Outline Dimensions (mm)       |                                       |

| Table 8-1:  | Power Supply Current Derating Factors | 238                                   |

| Table 8-2:  | Crystal Oscillator Specifications     | 240                                   |

| Table B-1:  | Data Sheet Revision Summary           | 243                                   |

|             |                                       |                                       |

#### **MOST System On Chip**

### 1 Overview

The OS8805 is a flexible hardware platform that can be programmed for a wide variety of signal processing system solutions. Software is available from Oasis SiliconSystems for applications including a digital radio, amplifiers, and active speakers. Programming tools such as emulators, assemblers, and C compilers are available to support user-developed applications.

The OS8805 is a monolithic CMOS integrated circuit, which combines high-speed micro-controllers and digital signal processors, with high quality analog circuitry. The OS8805 has four processors, eleven ADCs and DACs, and a variety of digital I/O. The Host Controller has 128k bytes of on-chip Flash Program memory, supporting easy updates during the design process as well as in the field. The programmable Host Controller and fixed-point DSPs enable the OS8805 to be a cost-effective solution for a wide variety of applications.

The MOST Processor provides a standard interface to the MOST Network. It generates the timing for all components on the chip, allowing the entire chip to operate synchronously to the Network. Even when not connected to the Network, the MOST Processor efficiently routes real-time data between resources, such as the DSPs, Source Ports, and Source Converters.

The OS8805 is a complete MOST (Media Oriented Systems Transport) Network Transceiver device capable of more than 24 Mbit/s data throughput when interfacing to a MOST optical Network. All relevant Network management functions are handled on-chip providing a complete system interface to the Physical layer components. Minimal additional components are required due to the high-level of integration on chip. An ultra-low jitter on-chip PLL guarantees high-quality audio and video transmission, and clock recovery over a wide frequency range.

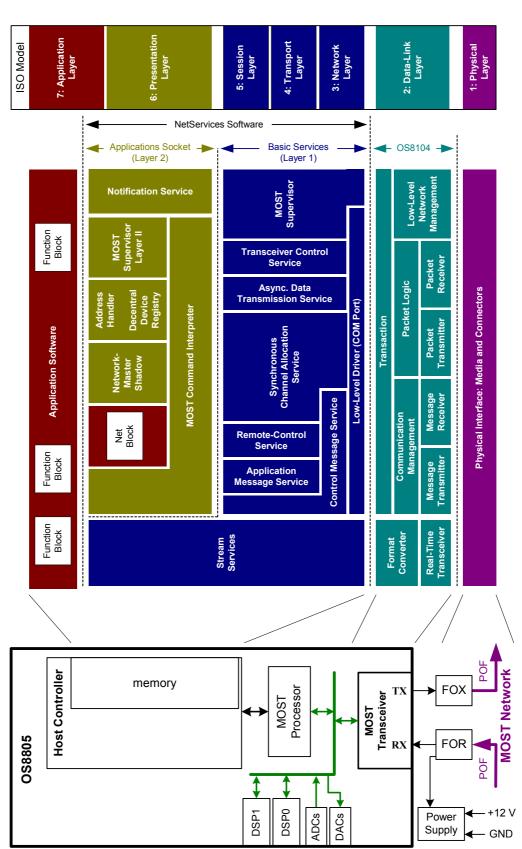

A typical MOST Network node would consist of the OS8805 and the Physical layer devices. The MOST transceiver handles the Data-Link layer protocols and the Host Controller handles the Network layer and higher. Oasis SiliconSystems also offers a NetServices software stack, written in ANSI C, to ease implementation of the MOST Specification software protocol; thereby, drastically shrinking development time. NetServices can be ported to the Host Controller, along with the application's code for the particular node. All Network management functions can be off-loaded from the programmer allowing full concentration on the application being developed. Figure 1-1 illustrates the OS8805, with the matching software-protocol stack implementation. This Figure illustrates the OS8805 streaming synchronous data between the MOST Network and the on-chip ADCs, and DACs, and DSPs. Source Ports even support streaming data to off-chip high-speed controllers.

To minimize costs, the MOST Network supports a peer-to-peer methodology, eliminating excessive hardware overhead such as a hub (although hub-based architectures can also be implemented). In addition to handling Network interface and communication management functions, the MOST transceiver also handles all of the important low-level Network management functions; such as node position sensing (Plugand-Play), network delay detection, start up and shut down, as well as error reporting, fail-safe operation, and channel allocation. Placing all these features in hardware, frees up much of the Host Controller MIPS to focus on higher-level Network functions.

The MOST Network actually consists of three simultaneous networks operating across a single low-cost plastic fiber:

- a Control network to manage the Network and communicate control data across the network,

- a Packet-based network to support nodes that communicate data,

- and a Streaming network that supports high-speed synchronous data with extremely low overhead (such as audio and video).

Each of these three networks, or *data transfer methods*, operates independently (not affecting the other two), providing a robust, dependable, and deterministic system architecture. The OS8805 supports the Control and Streaming portions of the MOST Network, by default. The OS8805 also supports Packet messages if enabled, otherwise it will not acknoledge reception of asynchronous Packets.

### MOST System On Chip

O-A-S-I-S SiliconSystems

Figure 1-1: MOST Hardware/Software System Overview

Final Product Data Sheet Page 16

#### **MOST System On Chip**

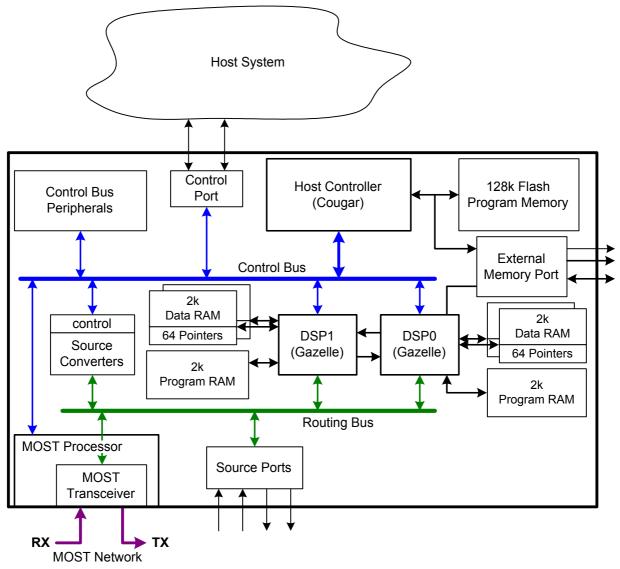

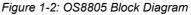

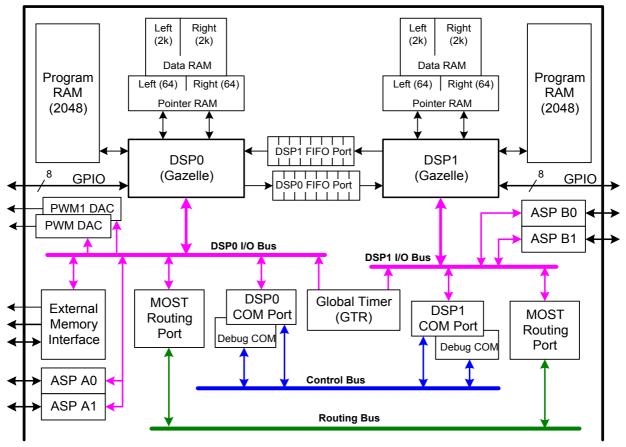

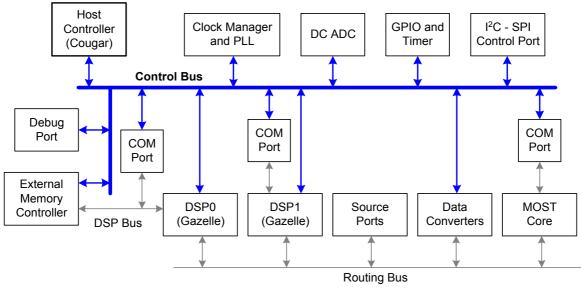

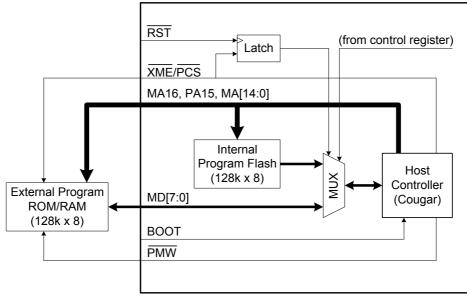

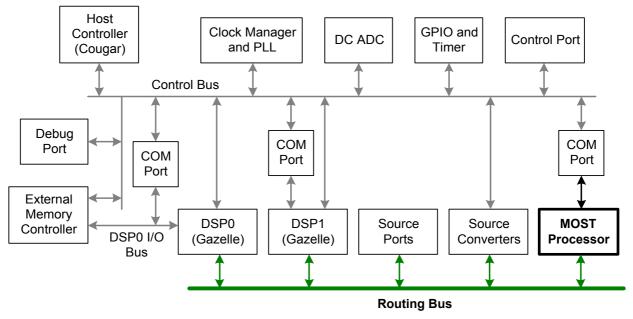

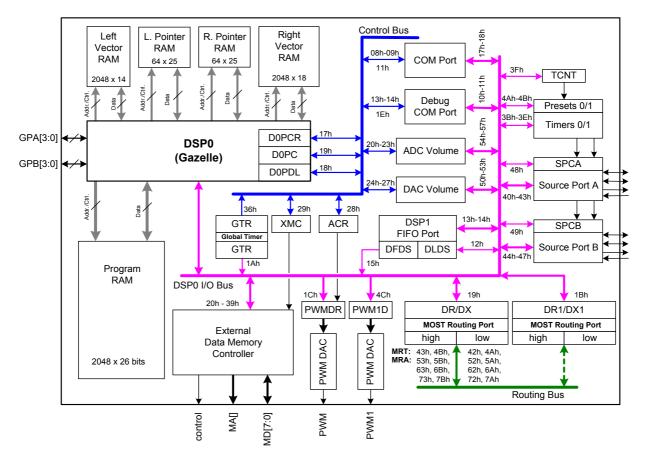

As shown in Figure 1-2, the chip contains four main processors: the Host Controller, the MOST Processor, and two DSPs. The Host Controller operates on the Control bus and communicates with the external Host System. This Controller manages the peripherals on the Control Bus, loads programs into the DSP memories, and configures the MOST Processor and connection to the MOST Network. The data crossing the Control bus is generally low-speed data such as configuration information and messages to or from the MOST Network. The Controller interfaces to the external system through a Control Port. For external systems with intelligence, the Control Port (and the chip) can be configured as a serial device. For stand-alone applications, the Control Port can be configured as a master, wherein the Controller manages the external peripherals in a similar fashion as the peripherals on the Control bus.

The Host Controller generally operates out of on-chip Flash memory, but also supports operation from external memory through the external memory port. If the Controller uses external memory, then DSP0 is limited to the internal data memory. If the Controller runs out of internal Flash, DSP0 can use the external memory port for data-memory expansion.

#### **MOST System On Chip**

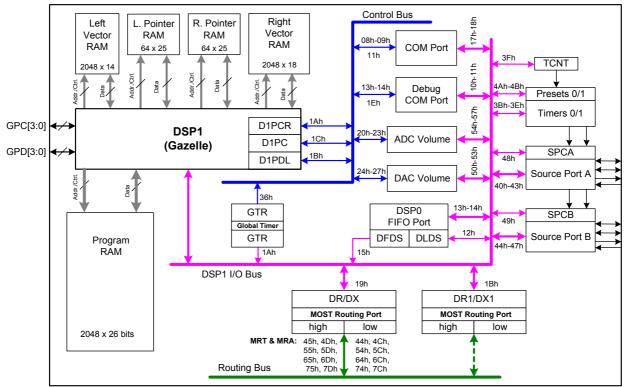

The MOST Processor manages real-time high-speed data traversing the Routing bus and includes a MOST Network transceiver. The high-speed data can be exchanged between the MOST Network and among the devices connected to the Routing bus; such as either DSP, the Source Ports, or the Source Converters (ADCs and DACs). The MOST Processor can transfer up to 15 high-fidelity stereo-audio streams onto or off of the MOST Network, per Fs period. The MOST Routing Table (MRT), programmed by the Host Controller, determines how the high-speed data is routed by the MOST Processor.

The two DSPs are Oasis SiliconSystem's *Gazelle* DSP cores and are identical, with the exception of extra peripherals on DSP0's I/O bus. Each DSP Program RAM must be loaded from the Host Controller. Each DSP can transfer up to 32-bytes per Fs onto and off of the Routing bus. The DSPs also have a FIFO port between them, allowing processing to be split between the DSPs without using Routing-bus bandwidth. Each DSP has an I/O bus with peripherals. Each DSP also has an Asynchronous Source Port with flexible clocking options. This port can be clocked asynchronously to the OS8805 and includes a timer that can reference the asynchronous clock to the internal chip timing and the MOST Network.

The Host Controller manages COM Ports that provide bi-directional communications to each DSP and the MOST Processor. Through the Control bus, the Host Controller also has access to the program controllers of each DSP. This enables the Host Controller to download programs to the DSPs.

Peripherals such as the GPIO pins, Clock Manager, a dual-USART, and the DC measurement ADC reside on the Control bus. The Control Port and Debug Port peripherals are also connected to the Control bus and allow the Host Controller to communicate with external devices. The Source Converters consist of ADCs and DACs that are connected to both the Control and Routing busses. The Host Controller can enable the Converters and adjust the volume, while the high-speed MOST Processor routes the Converter's data across the Routing bus. The Source Ports provide a gateway for high-speed data between the OS8805 and the external system.

Most digital pins that are not used for their primary function, may be configured as GPIO.

### 1.1 Host Controller

The Host Controller has multiple-byte instructions and a CISC architecture, which minimizes the amount of program code required to perform control applications. A byte/word-mode switch enables it to efficiently process byte and word variables without wasting data memory. The Controller operates at a maximum of 8.5 MIPS. Instructions can be one to four bytes long.

The Host Controller addresses 128k bytes of internal Flash or external Program memory, and 4k bytes of internal Data memory for variables. NetServices software is available from Oasis SiliconSystems which runs on the Host Controller and manages both the low- and high-level network protocol processing for the MOST Network.

The Host Controller is the main interface to the external system for control and configuration information. As illustrated in Figure 1-3, the external Host System communicates with the OS8805 through the Control Port. The Host Controller (Controller) reads the Control Port and reacts directly, or passes the information to one of the peripheral processors such as a DSP or the MOST Processor. The Controller also manages all the peripherals that reside on the Control bus.

In some systems, the OS8805 contains all the intelligence and the external Host System is only comprised of peripherals that are managed via the Control Port, in Master mode.

#### **MOST System On Chip**

O-A-S-I-S SiliconSystems

Figure 1-3: Host Controller and Control Bus

### **1.2 Control Bus and Peripherals**

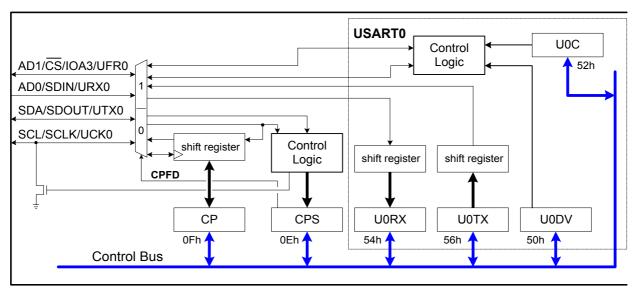

The Host Controller manages all Control bus peripherals. The Control Port can be a slave or a master and provides a serial interface between the Host Controller and the external system. The Control Port can operate in one of four formats: I<sup>2</sup>C, Oasis-specific SPI, generic SPI format, or USART format. In both I<sup>2</sup>C and Oasis-specific SPI (OSPI), the data exchange supports efficient transfer of blocks of data. The generic SPI (GSPI) format does not interpret the data, leaving the data format up to the user. The Control Port can be a master or slave in I<sup>2</sup>C or GSPI formats, and only a slave in the OSPI format.

The Debug Port is a second serial interface between the Host Controller and the external system. Although listed as a "Debug" Port, the port is generic and has a unique interrupt vector. The Debug Port shares pins with three of the GPIO pins and supports the same four formats that the Control Port supports. The Debug Port can also be a master in the  $l^2C$  or GSPI formats only.

#### **MOST System On Chip**

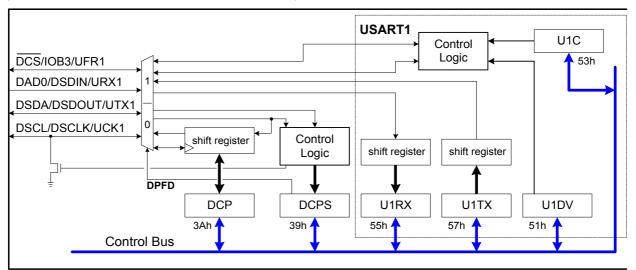

The Control bus also contains three COM Ports, which support inter-processor communications between the Host Controller and the two DSPs, as well as the MOST Processor. The MOST Processor communications utilize a format similar to the Control and Debug Ports in  $I^2C$  mode. The DSPs should be programmed to support the same format used by the MOST Processor to maximize code reuse. Through the MOST COM Port, the Host Controller can initialize the MOST Processor and transmit and receive messages across the MOST Network. The DSP COM Ports can be utilized in the same manner.

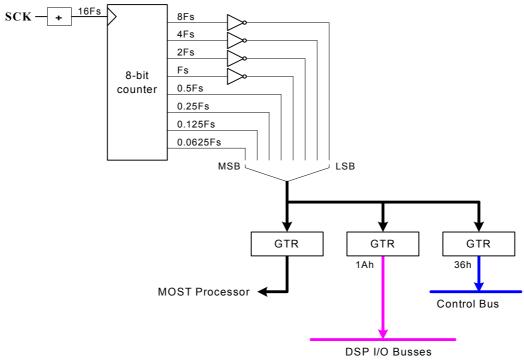

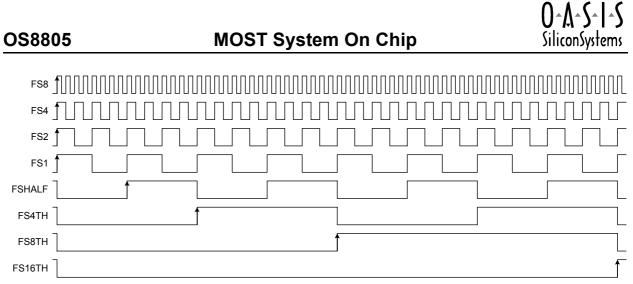

The Global Timer flag register is visible to all I/O busses and supplies timing flags, at up to 8xFs, for synchronized communications across the processors. The Global Timer also provides a periodic time interval, based on the sample frequency Fs.

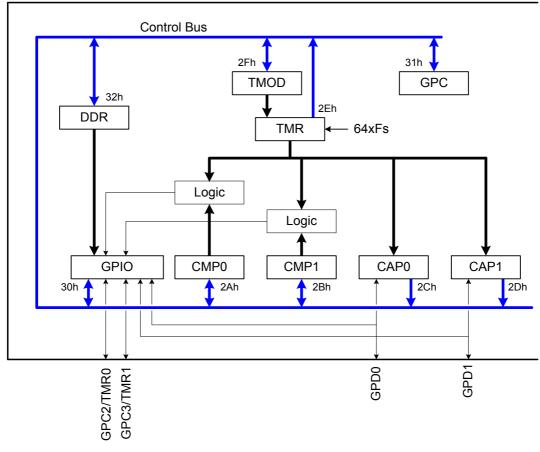

The GPIO pins are multiplexed with the General Purpose Timer, Control Port and the Debug Port. The Timer is a 16-bit timer that counts up at a 64Fs rate and resets when the count reaches the modulo value. Two output-compare registers are provided that can toggle a pin when the Timer reaches a programmed value. Two capture registers save the timer value when a pin changes state and can generate an interrupt.

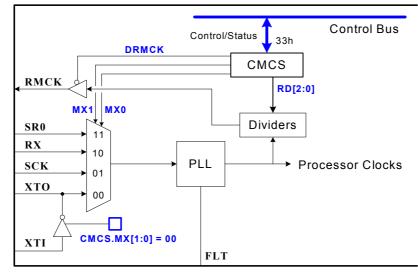

The Clock Manager peripheral contains a PLL and generates all the clocks needed by the OS8805. It also provides an external programmable clock (RMCK), to synchronize external system devices. When the OS8805 is configured as a MOST Network timing-slave device, the timing source is the MOST Network receive pin **RX**. When the OS8805 is configured as a MOST Network master, the timing source can be an external crystal, the external Source Port clock **SCK**, or the external Source Port data pin **SR0** when configured as an SPDIF input.

The DC Measurement ADC peripheral consists of an eight-to-one mux and an over-sampling ADC. The resolution is programmable from 5 to 12 bits. The conversion process takes approximately 1 ms to achieve 12-bit resolution, and 250  $\mu$ s to achieve 10-bit resolution. The POT[7:0] pins support up to eight analog inputs.

### **1.3 MOST Processor and the Routing Bus**

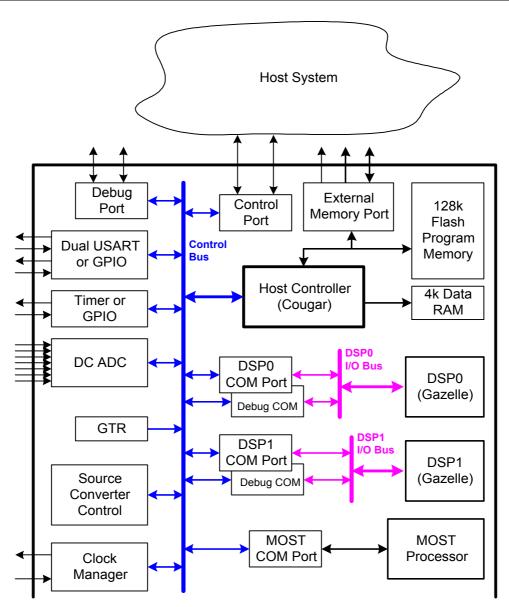

The MOST Processor interfaces to the MOST optical Network and manages the transfer of real-time data between on-chip resources. Included in the MOST Processor is a MOST Network transmitter and receiver. The MOST receiver, in conjunction with the clock manager, recovers the clock, decodes the data, and passes the information to the MOST Processor. The MOST Processor sends data to the transmitter which, encodes the data, and transmits it on the MOST Network.

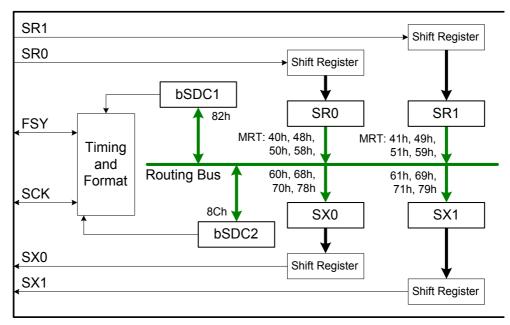

The MOST transceiver uses the TX and RX pins for transmitting and receiving MOST optical network data. The MOST Processor, Routing bus, and Routing bus peripherals are illustrated in Figure 1-4.

The MOST Processor is a hard-coded RISC micro-controller, which is responsible for routing data internally as well as onto the optical Network. For high-speed source data, the MOST Processor acts like a cross-point switch using the MOST Routing Table (MRT) to connect sources and destinations across the Routing bus. For low speed data, such as control messages, the Processor communicates with the Host Controller through the COM port. This port enables the Host Controller to instruct the MOST Processor to send and receive messages and to route the appropriate source data between the MOST Network and the on-chip resources.

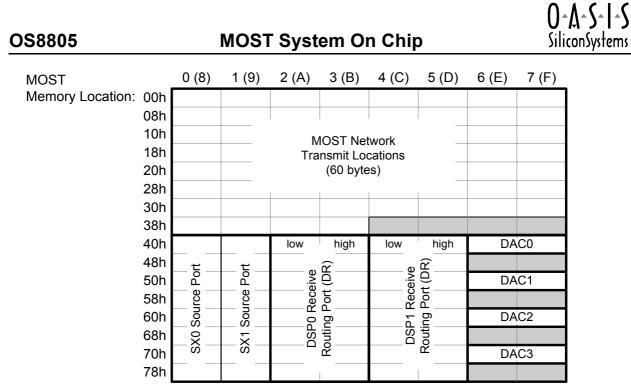

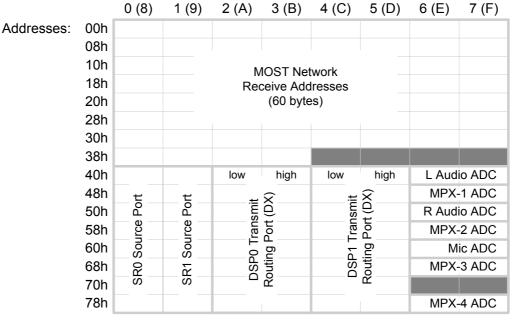

The MOST Network can communicate 60 bytes of synchronous data (Source data) at the audio sample rate (Fs). The MOST Processor can route the received data back onto the network, or (using the Routing bus) to the internal DSPs, Source Converters, or Source Ports. The transmitted MOST data can also come from the DSPs, Source Ports, and Source Converters. Each DSP can sink and source up to 32 bytes per Fs period (sixteen 16-bit channels in each direction). Each Source Port can sink and source up to 8 bytes per Fs period (four 16-bit channels).

The Source Converters consist of: the MPX ADC (16-bit samples at four times the audio sample rate), the stereo audio ADCs (two 16-bit samples at the audio sample rate), the microphone ADC (16-bit samples at ¼ the audio sample rate), and the audio DACs (four 16-bit samples at the audio sample rate).

#### **MOST System On Chip**

The Global Timer peripheral provides inter-processor synchronization. The MOST Processor uses the flags in this register to transfer data across the Routing bus. The DSPs can also use this register to synchronize with the MOST Processor when transferring data across the MOST Routing port.

Figure 1-4: MOST Processor Overview

#### MOST System On Chip

#### 1.3.1 Source Data Ports

**OS8805**

The Source Data Ports move high-speed data between the Routing bus and external devices. The external devices could be extra DACs, DSPs for further processing, or CD transports. Each Source Data Port can transfer up to eight bytes per sample frequency period. Therefore, a maximum of four 16-bit channels can be input to or sent out each Source Port.

Two serial-input and two serial-output ports communicate source data between internal and external components. The data format is programmable via the SDC1 register in the MOST Processor I/O space. Data is clocked through all four ports in the same data format with the same clock and frame sync.

Data is serially shifted into and out of the Source Ports through the serial receive SR[1:0] and the serial transmit SX[1:0] pins. Source port 0 can be configured to transmit and receive SPDIF data (SX0 and SR0). If the OS8805 is configured as a MOST Network master, then the PLL can recover a clock from the SR0 bit stream, when configured for SPDIF. If the chip is a timing-slave, which recovers the clock from the MOST Network RX pin, the SPDIF data and Source Port data must be entered synchronously to the Network RX pin. External synchronization can be achieved by using the OS8805 RMCK output as the master clock for the external system.

#### **1.3.2 Source Data Converters**

The Source Converters are high-speed ADCs and DACs that reside on the Routing bus. The Source Converters consists of four audio-band DACs, two audio-band ADCs, a 4x audio-bandwidth MPX ADC, and a <sup>1</sup>/<sub>4</sub>x audio bandwidth microphone ADC. The MPX, audio, and microphone ADCs are over-sampling deltasigma converters which provide wide dynamic range and excellent linearity. An analog MUX, in front of the audio ADCs, selects one of three stereo input pairs. All ADCs have input gain stages and all DACs have output attenuators. The Host Controller controls the Audio ADC input MUX and the gain and attenuation settings through the Control bus. The Source Converter volume can also be set by either DSP.

The inputs to the ADCs are single-ended and must be AC coupled. The MPX pin is the input to the MPX ADC and the MIC pin is the input to the microphone ADC. The two audio ADC inputs are AD0L-AD0R, AD1L-AD1R, or AD2L-AD2R pins, depending on the state of the input multiplexer.

The ADCs output their data to the Routing bus and MOST Processor. The MOST Processor can then route the data to the MOST transmitter to go out on the Network, route the data to the DSPs for further processing, or route the data out the Source Data Port. Since the MPX ADC runs at 4xFs, the MOST Processor sends the 16-bit audio data to the MOST Network four times per frame. Since the Mic ADC runs at ¼xFs, the MOST Network sees the same copy of Mic data four times before new data is available.

The four DACs can be programmed for single-ended or differential outputs, which are available on the DA[3:0] and DA[3:0]B pins. The DACs are fed data across the Routing bus from the MOST Processor. The MOST Processor can get the data from the MOST Network receiver, the DSPs, or the Source Data Ports.

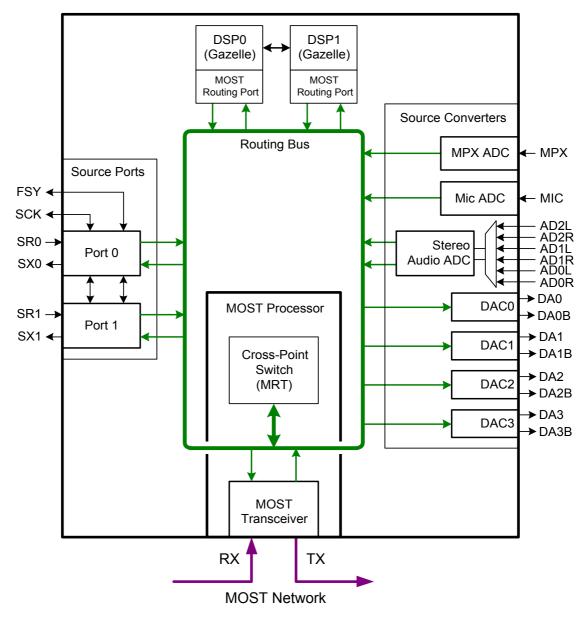

#### **1.4 DSP Processors**

The two DSPs have a RISC architecture, which provides the optimum cost performance trade-off for a wide variety of signal-processing applications. The RAM-based architecture allows software to be developed and downloaded for different system requirements. The DSP processor performs 18x14 bit operations with single-cycle instructions that produce 60 MIPs at 60 MHz. A combination hardware/software stack provides high-speed interrupt servicing for high-priority interrupts and die-area-efficient servicing for low priority interrupts. Special I/O instructions during high-priority interrupts provide low overhead I/O processing.

Figure 1-5: DSP Overview

The Host Controller connects to the DSP's program controller and has read/write access to the program counter, the program control register, and Program memory. This feature allows downloading programs as well as visibility of the DSP internal operation.

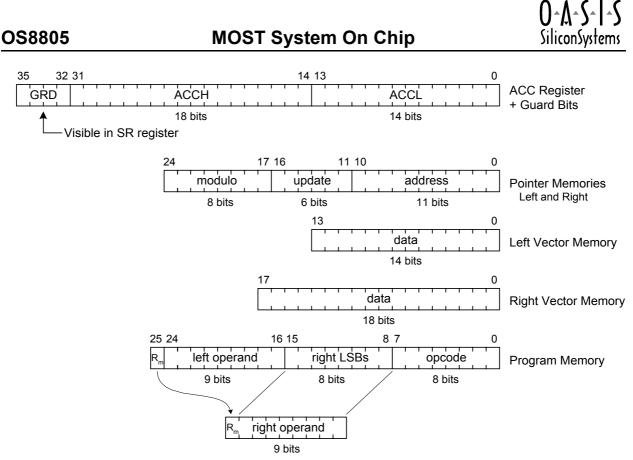

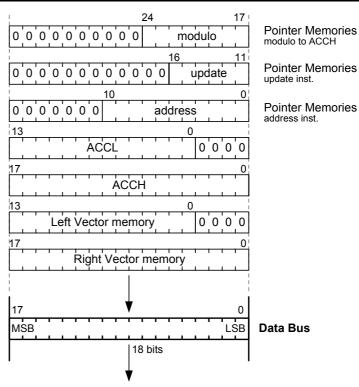

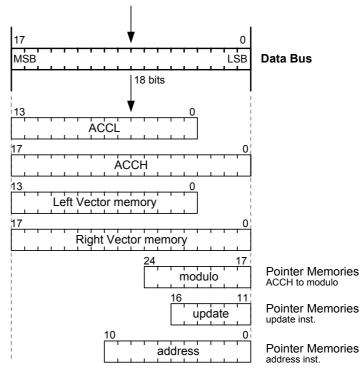

All the memories associated with the DSP processor are on-chip. The Program memory is 26 bits wide and 2048 locations deep. The Data memory section is divided into left and right sides with each side having a Pointer memory and a Vector memory. Each Pointer memory is 25 bits wide and both left and right Pointer memories are 64 locations deep. Left Vector memory is 14 bits wide and 2048 locations deep. Right Vector memory is 18 bits wide and 2048 locations deep.

The left and right Pointer memories store pointer values which consist of a 11-bit address, 6-bit update, and 8-bit modulo field. The accumulator consists of the low accumulator (14 bits), the high accumulator (18 bits), and the guard bits (4 bits).

Each DSP can control up to 8 GPIO pins that are multiplexed with the Asynchronous Source Ports. If the Async. Source Ports are not used, the DSP (or the Host Controller) can utilize the pins as GPIO.

#### **MOST System On Chip**

The MOST Routing Port peripheral supports the transfer of data between the DSP and the Routing bus. The MOST Processor can be programmed to transfer data (in either direction) between the Source Ports, Source Converters, or the MOST Network and the DSPs.

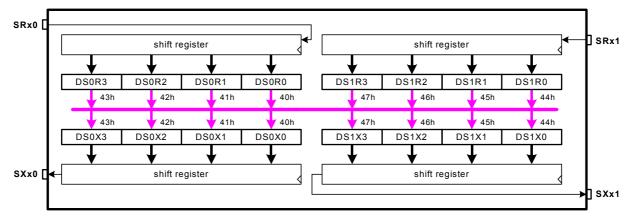

Each DSP has an Asynchronous Source Port (ASP) peripheral with flexible clocking options. ASP A is associated with DSP0 and ASP B is associated with DSP1. Each DSP Asynchronous Source Port is divided in two Source Ports: 0 and 1. Each Port (0 or 1) has a serial data in, serial data out, framing clock, and bit clock. The Async. Source Ports can be clocked off an internal reference or externally clocked, independent of the internal chip clock. A timer connected to each Async. Source Port can reference the external clock to the internal system clock.

The DSPs also have a FIFO Port between the two DSPs supporting the off-loading of tasks from one DSP to the other. The FIFO Port can support simultaneous transfers of 8 words in each direction or up to 16 words in a single direction or time-division multiplexed (not at the same time) scheme.

The DSP I/O bus contains the Global Timer flag register that provides periodic flags at up to 8xFs. These flags support inter-processor synchronization since the same Global Timer is available to the Host Controller and the MOST Processor. As an example, the MOST Processor reads and writes the DSP's MOST Routing port eight times per sample period. The DSPs can use the Global timer **GTR.FS8** flag to update the MOST Routing port. This process synchronizes data flow between the DSPs and the MOST Processor.

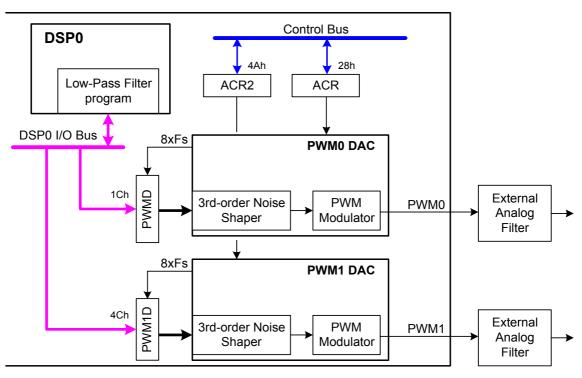

DSP0 has access to the external memory port, if not used by the Host Controller. The external memory port supports direct connection of DRAM or SRAM memory chips. This expands DSP0's data memory up to 512k 16-bit words, when using DRAM, and 64k 16-bit words, when using SRAM. External data communication occurs through 16-bit I/O registers and includes modulo and post-incrementing addressing.

DSP0's I/O bus also includes two pulse-width-modulation (PWM) DAC peripherals for sub-woofer applications or low frequency volume control.

### 1.5 MOST NetServices API

For accelerating development of applications using the OS8805, Oasis SiliconSystems offers the MOST NetServices API. The MOST NetServices API provides software access to the MOST Network. All services that are relevant for MOST Network are available as a software library. This includes basic services like initialization, up to high-level communication tasks. MOST NetServices is modular and can be customized for the OS8805. The MOST NetServices API is implemented in ANSI C, which can be adapted to individual requirements through configuration files.

The MOST NetServices API is organized into two layers: Basic Services (Layer 1) and the Applications Socket (Layer 2). The Basic Services provides low-level services such as network initialization, Control message management through the COM Port, Source Port configuration, and synchronous channel allocation on the network

The Applications Socket (Layer 2) operates on top of Layer 1 and provides a command interpreter and the NetBlock function required on all network devices. The command interpreter provides a simple API for developing new functions within a node. It also supports the MOST Specification Notification Services and functional addressing.

With respect to the ISO communications model, the OS8805 chip, with its on-chip Host Controller supports all network layers except the Physical layer, with MOST Network transceiver containing the Data-Link layer and the Host Controller managing all the upper layers. MOST NetServices Layer 1 supports the Network layer through the Session layer. MOST NetServices Layer 2 supports the Presentation and part of the Application layer. The ISO network model and MOST NetServices is depicted in Figure 1-1.

More information on MOST NetServices is available on the Oasis SiliconSystems web page:

http://www.oasis.com

The Host Controller (Controller) manages data movement across the Control bus. The Host Controller also handles internal and external communication and control between on-chip resources and the Control Port. When power is initially applied to the OS8805, the **CMCS.PD** bit is set, placing the OS8805 in power-down mode. A chip reset, **RST**, or a transition on **RX** or **GPA0-GPA2** is needed to clear **CMCS.PD** and place the Host Controller in normal operation. The Debug Port provides a second serial port that provides on-chip debug capability, with the appropriate debug code programmed into the Host Controller. Although listed as the Debug Port, it can be programmed to serve as an additional control port or as GPIOs. The Controller is also responsible for program downloading into the DSPs' memories. Figure 2-1 highlights the Control Bus section of the OS8805.

Figure 2-1: Control Bus

### 2.1 Architecture

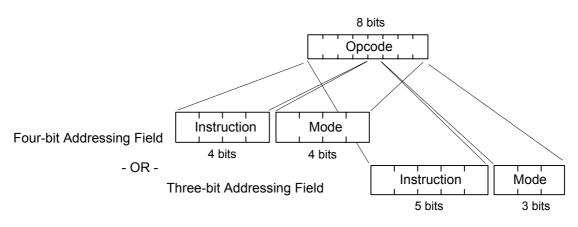

The Host Controller conforms to the Oasis SiliconSystems Cougar 16-bit architecture and is a general purpose CISC architecture processor. The multiple-byte instructions and CISC architecture is optimized to reduce Program memory requirement of control applications. A byte/word mode switch enables it to efficiently process byte and word variables allowing optimal use of data memory. Special I/O instructions and a maximum performance of 8.5 MIPS (2 cycles/instruction at 384Fs) enable it to properly process real-time applications. For programming information on the Controller, see the *Cougar User's Manual*. The OS8805 has 128k bytes of on-chip Flash Program memory and 4k bytes of on-chip Data memory.

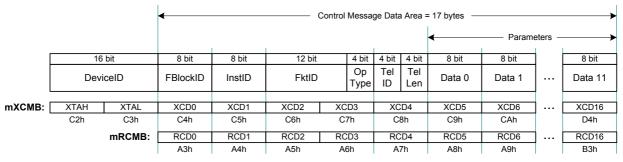

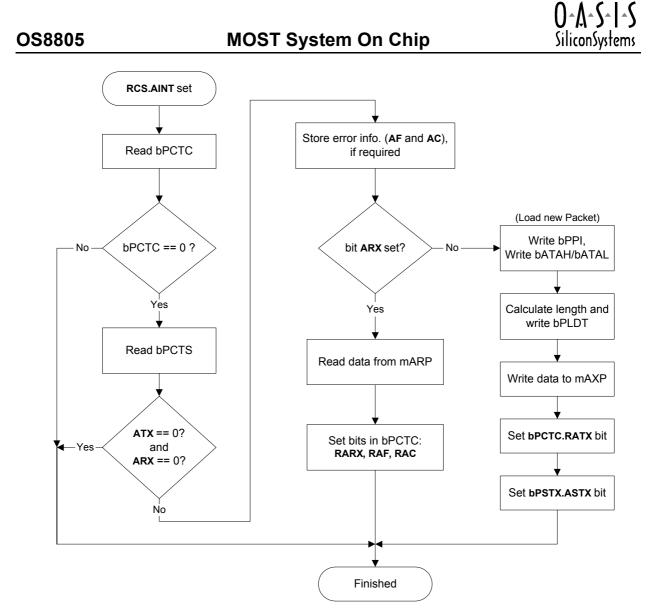

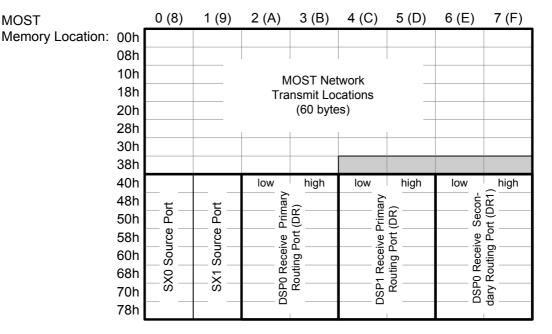

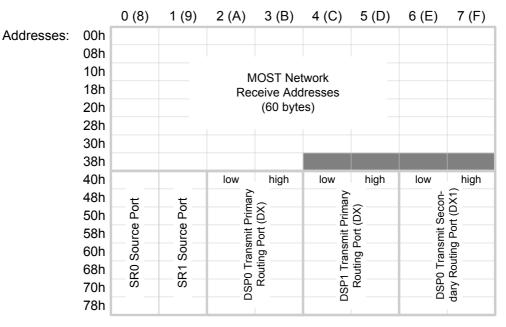

The Cougar Host Controller instructions can be one to four bytes in length. The first byte consists of the opcode, and indicates the addressing mode for the instruction. The following bytes provide an 8- to 16-bit direct memory address or immediate data, or up to an 17-bit jump address. The Controller can access one byte of Program memory every two clock cycles, and operates at a clock frequency of 384×Fs.