# datasheet

PRODUCT SPECIFICATION

1/7.5" CMOS VGA(640 x 480) image sensor with OmniPixel3-GS<sup>™</sup> technology

## Copyright ©2015 OmniVision Technologies, Inc. All rights reserved.

This document is provided "as is" with no warranties whatsoever, including any warranty of merchantability, non-infringement, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification, or sample.

OmniVision Technologies, Inc. and all its affiliates disclaim all liability, including liability for infringement of any proprietary rights, relating to the use of information in this document. No license, expressed or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

The information contained in this document is considered proprietary to OmniVision Technologies, Inc. and all its affiliates. This information may be distributed to individuals or organizations authorized by OmniVision Technologies, Inc. to receive said information. Individuals and/or organizations are not allowed to re-distribute said information.

#### Trademark Information

OmniVision and the OmniVision logo are registered trademarks of OmniVision Technologies, Inc. OmniPixel3-GS is a trademark of OmniVision Technologies, Inc.

All other trademarks used herein are the property of their respective owners.

#### OS VGA (640 x 480) image sensor with OmniPixel3-GS™ technology

datasheet (CSP3) PRODUCT SPECIFICATION

version 2.12 october 2015

To learn more about OmniVision Technologies, visit www.ovt.com.

OmniVision Technologies is publicly traded on NASDAQ under the symbol OVTI.

# applications

- cellular phones

- digital still cameras (DSC)

- digital video camcorders (DVC)

- PC multimedia

- tablets

# features

- 3 µm x 3 µm pixel with OmniPixel3-GS<sup>™</sup> technology

- automatic black level calibration (ABLC)

- programmable controls for frame rate, mirror and flip, cropping and windowing

- support output formats: 8/10-bit RAW

- support for image sizes: 640x480, 320x240, 160x120

- fast mode switching

- supports horizontal and vertical 2:1 and 4:1 monochrome subsampling

# key specifications (typical)

- active array size: 640 x 480

- power supply:

- analog: 2.8V (nominal) core: 1.5V (optional) I/O: 1.8V (nominal)

- power requirements:

active: 117 mW @ 100fps, VGA output standby: 15  $\mu$ A for AVDD, 40  $\mu$ A for DOVDD without input clock, 700  $\mu$ A for DOVDD with input clock

XSHUTDOWN: 5  $\mu A$  for AVDD, 5  $\mu A$  for DOVDD

- temperature range: operating: -30°C to 70°C junction temperature stable image: 0°C to 50°C junction temperature

- output interface: 1-lane MIPI/LVDS serial output

- output formats: 10-bit RGB RAW or BW

- lens size: 1/7.5"

- input clock frequency: 6~27 MHz

# ordering information

- OV07750-A35A-1F (color, lead-free) 35-pin CSP3

- OV07251-A35A-1F (b&w, lead-free) 35-pin CSP3

- supports 2x2 monochrome binning

- one-lane MIPI serial output interface

- one-lane LVDS serial output interface

- embedded 256 bits of one-time programmable (OTP) memory for part identification

- two on-chip phase lock loops (PLLs)

- built-in 1.5V regulator for core

- PWM

- built-in strobe control

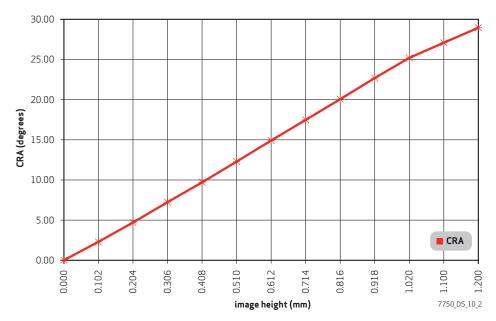

- lens chief ray angle: 29° non-linear

- max S/N ratio: 39dB

- dynamic range: 69.6dB @ 8x gain

- maximum image transfer rate:

640 x 480: 100 fps (see table 2-1)

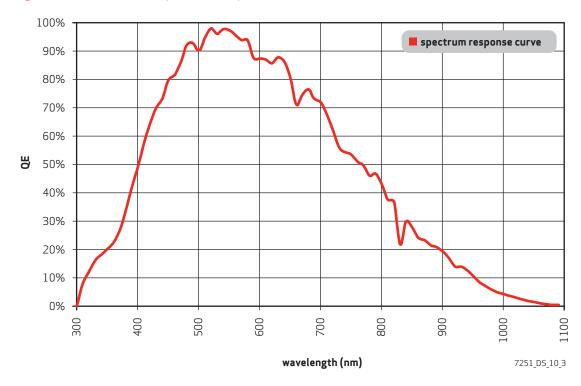

- OV7750 sensitivity: 2080mV/Lux-sec @ 530nm

- OV7251 sensitivity: 7190mV/(µW.cm<sup>-2</sup>.sec) @ 850nm 2800mV/Lux-sec @ 530nm

- scan mode: progressive

- maximum exposure interval: 502 x t<sub>ROW</sub>

- pixel size: 3 µm x 3 µm

- dark current: 350 e<sup>-</sup>/s @ 50°C junction temperature

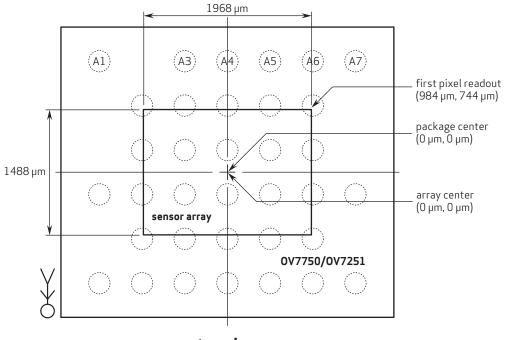

- image area: 1968 μm x 1488 μm

- package dimensions: 3910 µm x 3410 µm

**note** Maximum integration time of dark current depends on read out speed (e.g., for 100fps, max dark current is around 3.5e<sup>-</sup> at 50°C).

CMOS VGA (640 x 480) image sensor with OmniPixel3-GS™ technology

# table of contents

| 1 | signa | al descriptions                            | 1-1  |

|---|-------|--------------------------------------------|------|

| 2 | syste | em level description                       | 2-1  |

|   | 2.1   | overview                                   | 2-1  |

|   | 2.2   | architecture                               | 2-1  |

|   | 2.3   | format and frame                           | 2-3  |

|   |       | 2.3.1 MIPI interface                       | 2-4  |

|   |       | 2.3.2 VSYNC timing in MIPI mode            | 2-5  |

|   | 2.4   | I/O control                                | 2-6  |

|   | 2.5   | power management                           | 2-7  |

|   |       | 2.5.1 power up sequence                    | 2-7  |

|   |       | 2.5.2 power down sequence                  | 2-10 |

|   | 2.6   | reset                                      | 2-14 |

|   |       | 2.6.1 power ON reset generation            | 2-14 |

|   | 2.7   | hardware and software standby              | 2-14 |

|   | 2.8   | system clock control                       | 2-15 |

|   |       | 2.8.1 PLL configuration                    | 2-15 |

|   | 2.9   | serial camera control bus (SCCB) interface | 2-18 |

|   |       | 2.9.1 data transfer protocol               | 2-18 |

|   |       | 2.9.2 message format                       | 2-18 |

|   |       | 2.9.3 read/write operation                 | 2-19 |

|   |       | 2.9.4 SCCB timing                          | 2-22 |

|   |       | 2.9.5 group write and fast mode switching  | 2-23 |

| 3 | block | k level description                        | 3-1  |

|   | 3.1   | pixel array structure                      | 3-1  |

|   | 3.2   | subsampling                                | 3-2  |

| 4 | imag  | e sensor core digital functions            | 4-1  |

|   | 4.1   | mirror and flip                            | 4-1  |

|   | 4.2   | image windowing                            | 4-2  |

|   | 4.3   | test pattern                               | 4-3  |

|   |       | 4.3.1 general color bar                    | 4-3  |

|   |       | 4.3.2 solid color test pattern             | 4-3  |

|   | 4.4   | black level calibration (BLC)              | 4-4  |

|   |       |                                            |      |

|   | 4.5 one time programmable (OTP) memory                                        | 4-7   |

|---|-------------------------------------------------------------------------------|-------|

|   | 4.5.1 OTP memory structure                                                    | 4-7   |

|   | 4.5.2 accessing the OTP memory                                                | 4-7   |

|   | 4.5.3 procedure for accessing OTP memory                                      | 4-9   |

|   | 4.5.4 procedure to read OTP content                                           | 4-9   |

|   | 4.5.5 procedure to program OTP content                                        | 4-9   |

|   | 4.5.6 power supply requirement for OTP memory programming                     | 4-9   |

|   | 4.6 pulse width modulation (PWM)                                              | 4-10  |

|   | 4.7 strobe                                                                    | 4-11  |

|   | 4.8 low power modes                                                           | 4-12  |

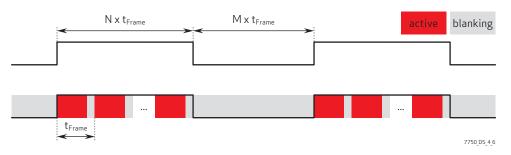

|   | 4.8.1 low frame rate mode                                                     | 4-13  |

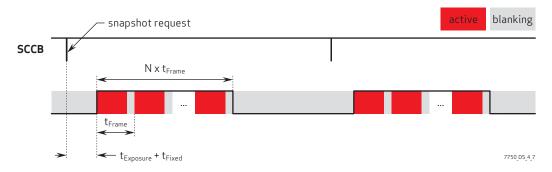

|   | 4.8.2 snapshot mode                                                           | 4-13  |

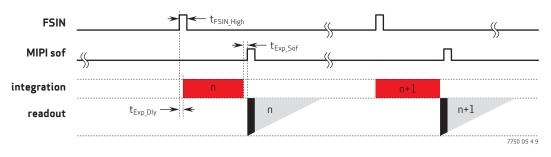

|   | 4.8.3 external trigger snapshot mode                                          | 4-14  |

| 5 | image sensor processor digital functions                                      | 5-1   |

|   | 5.1 ISP general controls                                                      | 5-1   |

|   | 5.2 manual white balance (MWB)                                                | 5-1   |

|   | 5.3 manual exposure and gain control                                          | 5-2   |

| 6 | system control                                                                | 6-1   |

|   | 6.1 mobile industry processor interface (MIPI)                                | 6-1   |

|   | 6.2 low-voltage differential signaling (LVDS)                                 | 6-9   |

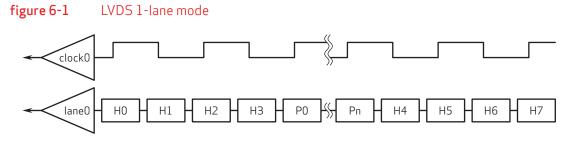

|   | 6.2.1 output modes                                                            | 6-10  |

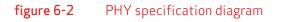

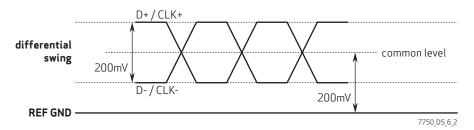

|   | 6.2.2 PHY specification                                                       | 6-11  |

|   | 6.2.3 LVDS lane configuration and sync                                        | 6-11  |

| 7 | register tables                                                               | 7-1   |

|   | 7.1 system control [0x0100 - 0x010A, 0x3001 - 0x301F, 0x3023 - 0x303B, 0x4501 | ] 7-1 |

|   | 7.2 PLL control [0x3080 - 0x3083, 0x3098 - 0x309F, 0x30B0 - 0x30B6]           | 7-8   |

|   | 7.3 SCCB and group hold control [0x3100 - 0x3106, 0x31FF - 0x320F]            | 7-9   |

|   | 7.4 manual AWB_gain control [0x3400 - 0x3406]                                 | 7-10  |

|   | 7.5 manual AEC/AGC [0x3500 - 0x350B, 0x5D00 - 0x5D01, 0x5F00 - 0x5F05]        | 7-11  |

|   | 7.6 analog control [0x3600 - 0x3684]                                          | 7-13  |

|   | 7.7 sensor control [0x3700 - 0x37AF]                                          | 7-14  |

|   | 7.8 timing control [0x3800 - 0x3835, 0x3837]                                  | 7-15  |

|   | 7.9 PWM and strobe control [0x3B80 - 0x3B97]                                  | 7-18  |

|   | 7.10 low power mode control [0x3C00 - 0x3C0F, 0x4A47 - 0x4A49]                | 7-20  |

|   | 7.11 OTP control [0x3D80 - 0x3D87, 0x3D8B]                                    | 7-21  |

|   | 7.12 BLC control [0x4000 - 0x4051]                                            | 7-22  |

|   |                                                                               |       |

|    | 7.13 frame control [0x4240 - 0x4244]                                               | 7-26 |

|----|------------------------------------------------------------------------------------|------|

|    | 7.14 format control [0x4300 - 0x4307, 0x4310 - 0x4316, 0x4320 - 0x4329]            | 7-26 |

|    | 7.15 VFIFO control [0x4600 - 0x4604]                                               | 7-28 |

|    | 7.16 MIPI top [0x4800 - 0x4806, 0x4810 - 0x4849, 0x4850 - 0x4854, 0x4860 - 0x4865] | 7-29 |

|    | 7.17 LVDS control [0x4A00, 0x4A02 ~ 0x4A0F]                                        | 7-38 |

|    | 7.18 ISP top [0x5000 ~ 0x5017, 0x5E00 ~ 0x5E08]                                    | 7-39 |

|    | 7.19 window control [0x5A00 - 0x5A0C]                                              | 7-41 |

| 8  | operating specifications                                                           | 8-1  |

|    | 8.1 absolute maximum ratings                                                       | 8-1  |

|    | 8.2 functional temperature                                                         | 8-1  |

|    | 8.3 DC characteristics                                                             | 8-2  |

|    | 8.4 timing characteristics                                                         | 8-3  |

| 9  | mechanical specifications                                                          | 9-1  |

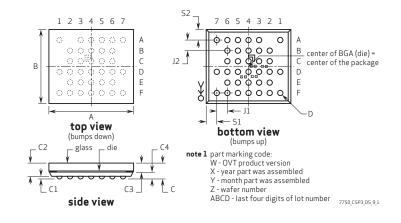

|    | 9.1 physical specifications                                                        | 9-1  |

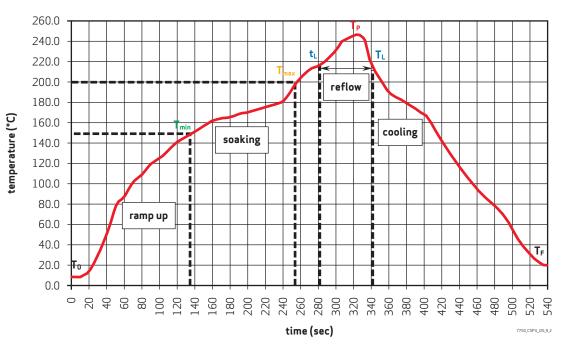

|    | 9.2 IR reflow specifications                                                       | 9-2  |

| 1( | O optical specifications                                                           | 10-1 |

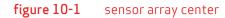

|    | 10.1 sensor array center                                                           | 10-1 |

|    | 10.2 lens chief ray angle (CRA)                                                    | 10-2 |

|    | 10.3 IR cut off wavelength                                                         | 10-3 |

|    | 10.4 spectrum response                                                             | 10-3 |

|    |                                                                                    |      |

Downloaded from Arrow.com.

CMOS VGA (640 x 480) image sensor with OmniPixel3-GS™ technology

# list of figures

| figure 1-1  | pin diagram                                | 1-3  |

|-------------|--------------------------------------------|------|

| figure 2-1  | OV7750/OV7251 block diagram                | 2-2  |

| figure 2-2  | reference design schematic                 | 2-3  |

| figure 2-3  | MIPI timing                                | 2-4  |

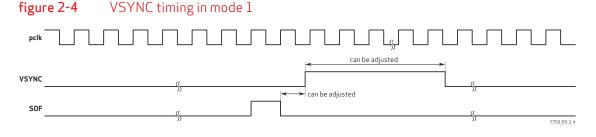

| figure 2-4  | VSYNC timing in mode 1                     | 2-5  |

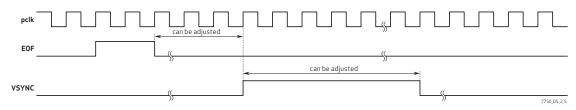

| figure 2-5  | VSYNC timing in mode 2                     | 2-5  |

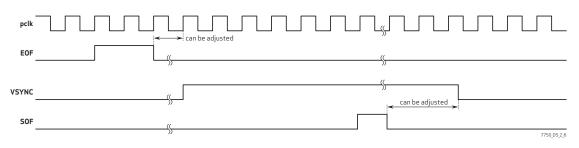

| figure 2-6  | VSYNC timing in mode 3                     | 2-5  |

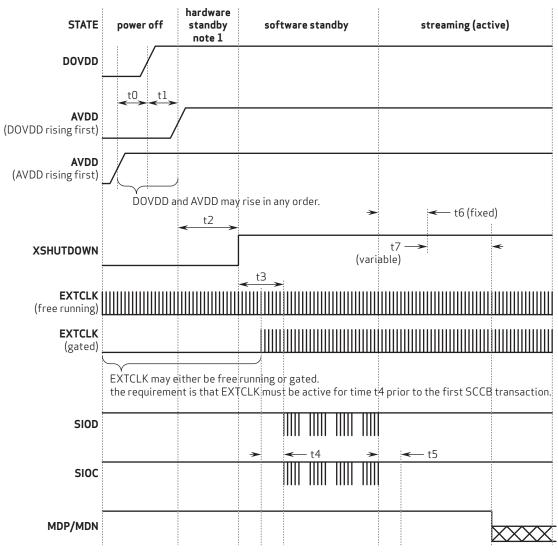

| figure 2-7  | power up sequence (case 1)                 | 2-8  |

| figure 2-8  | power up sequence (case 2)                 | 2-9  |

| figure 2-9  | power down sequence (case 1)               | 2-11 |

| figure 2-10 | power down sequence (case 2)               | 2-12 |

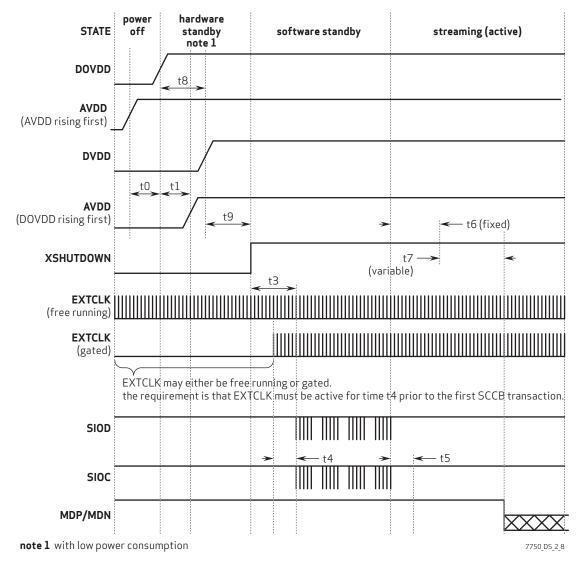

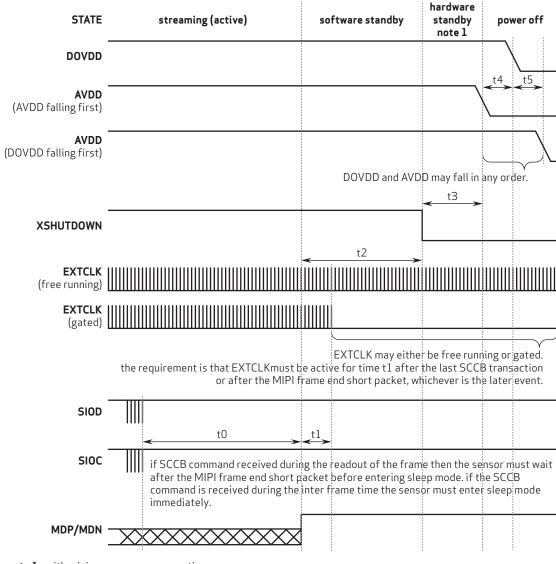

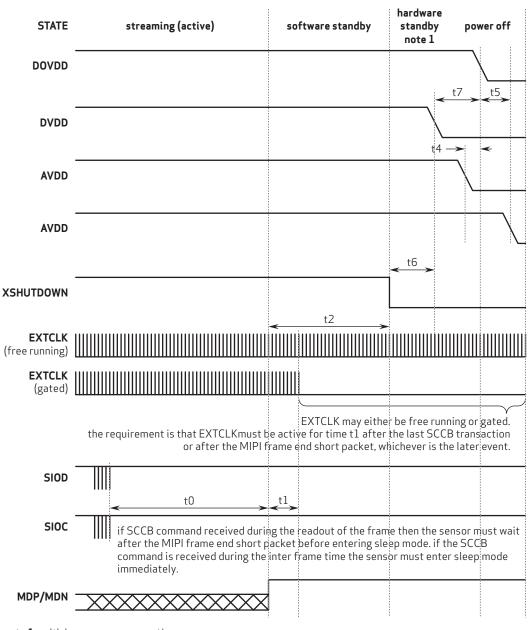

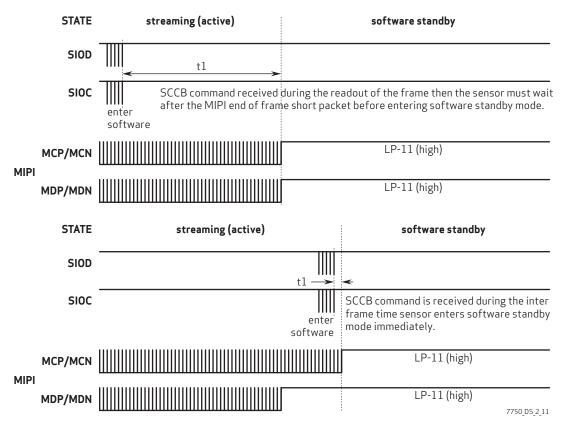

| figure 2-11 | standby sequence                           | 2-13 |

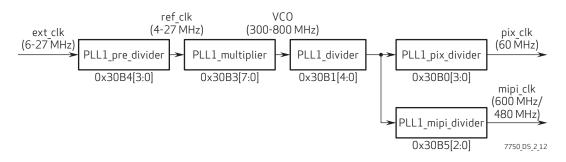

| figure 2-12 | OV7750/OV7251 PLL1 clock diagram           | 2-15 |

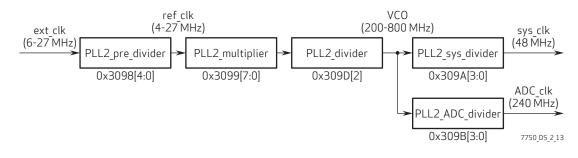

| figure 2-13 | OV7750/OV7251 PLL2 clock diagram           | 2-15 |

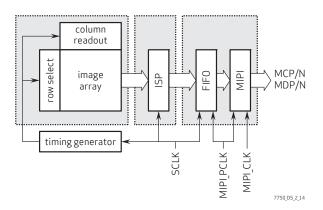

| figure 2-14 | clock connection diagram                   | 2-17 |

| figure 2-15 | message type                               | 2-18 |

| figure 2-16 | SCCB single read from random location      | 2-19 |

| figure 2-17 | SCCB single read from current location     | 2-19 |

| figure 2-18 | SCCB sequential read from random location  | 2-20 |

| figure 2-19 | SCCB sequential read from current location | 2-20 |

| figure 2-20 | SCCB single write to random location       | 2-21 |

| figure 2-21 | SCCB sequential write to random location   | 2-21 |

| figure 2-22 | SCCB interface timing                      | 2-22 |

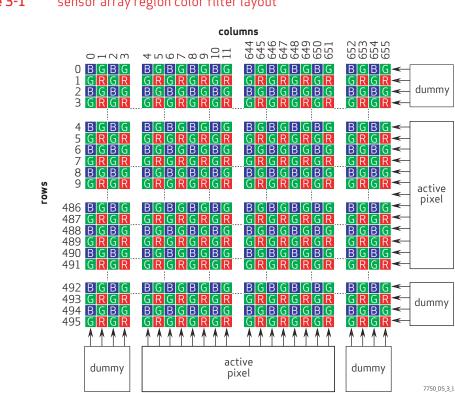

| figure 3-1  | sensor array region color filter layout    | 3-1  |

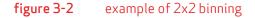

| figure 3-2  | example of 2x2 binning                     | 3-2  |

| figure 3-3  | example of 2:1 subsampling                 | 3-2  |

| figure 3-4  | example of 4:1 subsampling                 | 3-2  |

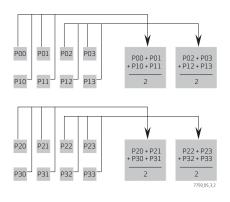

| figure 4-1  | mirror and flip samples                    | 4-1  |

| figure 4-2  | image windowing                            | 4-2  |

| figure 4-3  | test pattern                               | 4-3  |

| figure 4-4  | OTP access                                 | 4-8  |

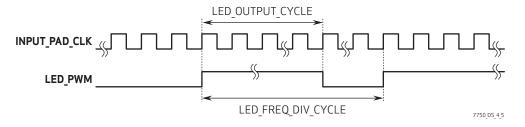

| figure 4-5  | PWM output timing                          | 4-10 |

|             |                                            |      |

### CMOS VGA (640 x 480) image sensor with OmniPixel3-GS™ technology

| figure 4-6  | low frame rate mode timing           | 4-13 |

|-------------|--------------------------------------|------|

| figure 4-7  | snapshot mode timing                 | 4-13 |

| figure 4-8  | external snapshot mode timing        | 4-14 |

| figure 4-9  | frame triggered by red pulse diagram | 4-14 |

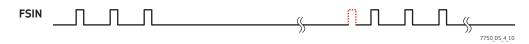

| figure 6-1  | LVDS 1-lane mode                     | 6-10 |

| figure 6-2  | PHY specification diagram            | 6-11 |

| figure 6-3  | LVDS lane configuration and sync     | 6-11 |

| figure 9-1  | package specifications               | 9-1  |

| figure 9-2  | IR reflow ramp rate requirements     | 9-2  |

| figure 10-1 | sensor array center                  | 10-1 |

| figure 10-2 | chief ray angle (CRA)                | 10-2 |

| figure 10-3 | OV7251 spectrum response curve       | 10-3 |

# list of tables

| table 1-1  | signal descriptions                        | 1-1  |

|------------|--------------------------------------------|------|

| table 1-2  | configuration under various conditions     | 1-2  |

| table 1-3  | pad symbol and equivalent circuit          | 1-3  |

| table 2-1  | supported resolution and frame rate        | 2-3  |

| table 2-2  | MIPI timing specifications                 | 2-4  |

| table 2-3  | I/O control registers                      | 2-6  |

| table 2-4  | power up sequence                          | 2-7  |

| table 2-5  | power up sequence timing constraints       | 2-7  |

| table 2-6  | power down sequence                        | 2-10 |

| table 2-7  | power down sequence timing constraints     | 2-10 |

| table 2-8  | hardware and software standby description  | 2-14 |

| table 2-9  | PLL control registers                      | 2-15 |

| table 2-10 | sample PLL configuration                   | 2-17 |

| table 2-11 | PLL speed limitation                       | 2-18 |

| table 2-12 | SCCB interface timing specifications       | 2-22 |

| table 2-13 | context switching control                  | 2-23 |

| table 3-1  | binning-related registers                  | 3-2  |

| table 4-1  | mirror and flip registers                  | 4-1  |

| table 4-2  | image windowing control functions          | 4-2  |

| table 4-3  | general color bar selection control        | 4-3  |

| table 4-4  | solid color test pattern control           | 4-3  |

| table 4-5  | BLC control functions                      | 4-4  |

| table 4-6  | ALS algorithm control registers            | 4-5  |

| table 4-7  | OTP memory structure                       | 4-7  |

| table 4-8  | PWM registers                              | 4-10 |

| table 4-9  | strobe control registers                   | 4-11 |

| table 4-10 | low power mode control registers           | 4-12 |

| table 5-1  | ISP top registers                          | 5-1  |

| table 5-2  | manual AWB_gain registers                  | 5-1  |

| table 5-3  | manual exposure and gain control registers | 5-2  |

| table 6-1  | MIPI top control registers                 | 6-1  |

| table 6-2  | LVDS registers                             | 6-9  |

| table 6-3 PHY specifications                   | 6-11 |

|------------------------------------------------|------|

| table 7-1 system control registers             | 7-1  |

| table 7-2 PLL control registers                | 7-8  |

| table 7-3 SCCB and group hold registers        | 7-9  |

| table 7-4 manual AWB_gain registers            | 7-10 |

| table 7-5 manual AEC/AGC registers             | 7-11 |

| table 7-6 analog control registers             | 7-13 |

| table 7-7 sensor control registers             | 7-14 |

| table 7-8 timing control registers             | 7-15 |

| table 7-9 PWM and strobe control registers     | 7-18 |

| table 7-10 low power mode control registers    | 7-20 |

| table 7-11 OTP control registers               | 7-21 |

| table 7-12 BLC control registers               | 7-22 |

| table 7-13 frame registers                     | 7-26 |

| table 7-14 format control registers            | 7-26 |

| table 7-15 VFIFO control registers             | 7-28 |

| table 7-16 MIPI top control registers          | 7-29 |

| table 7-17 LVDS registers                      | 7-38 |

| table 7-18 ISP top registers                   | 7-39 |

| table 7-19 window control registers            | 7-41 |

| table 8-1 absolute maximum ratings             | 8-1  |

| table 8-2 functional temperature               | 8-1  |

| table 8-3 DC characteristics (TA = 23°C ± 2°C) | 8-2  |

| table 8-4 timing characteristics               | 8-3  |

| table 9-1 package dimensions                   | 9-1  |

| table 9-2 reflow conditions                    | 9-2  |

| table 10-1 CRA versus image height plot        | 10-2 |

# 1 signal descriptions

table 1-1 lists the signal descriptions and their corresponding pin numbers for the OV7750/OV7251 image sensor. The package information is shown in section 9.

### table 1-1 signal descriptions (sheet 1 of 2)

| pin<br>number | signal name | pin<br>type | description                                                |  |

|---------------|-------------|-------------|------------------------------------------------------------|--|

| A1            | NC          | -           | no connect                                                 |  |

| A3            | VH          | reference   | internal analog reference                                  |  |

| A4            | VN2         | reference   | internal analog reference                                  |  |

| A5            | AGND        | ground      | ground for analog circuit                                  |  |

| A6            | NC          | -           | no connect                                                 |  |

| A7            | NC          | -           | no connect                                                 |  |

| B2            | VM          | reference   | internal analog reference                                  |  |

| B3            | MDP         | I/O         | MIPI/LVDS data lane positive output                        |  |

| B4            | VN1         | reference   | internal analog reference                                  |  |

| B5            | AVDD        | power       | power for analog circuit                                   |  |

| B6            | SIOD        | I/O         | SCCB data                                                  |  |

| C2            | EVDD        | power       | power for MIPI circuit (connect to DVDD outside of sensor) |  |

| C3            | MDN         | I/O         | MIPI/LVDS data lane negative output                        |  |

| C4            | SIOC        | input       | SCCB input clock                                           |  |

| C5            | FSIN/VSYNC  | I/O         | FSIN input/ VSYNC output                                   |  |

| C6            | ULPM        | output      | ULPM open-drain output                                     |  |

| D1            | NC          | -           | no connect                                                 |  |

| D2            | EGND        | ground      | ground for MIPI circuit                                    |  |

| D3            | МСР         | output      | MIPI/LVDS clock lane positive output                       |  |

| D4            | DGND        | ground      | ground for I/O and digital circuit                         |  |

| D5            | PWM         | I/O         | PWM output                                                 |  |

| D6            | XSHUTDOWN   | input       | reset (active low with internal pull down resistor)        |  |

| D7            | NC          | -           | no connect                                                 |  |

| E2            | тм          | input       | test mode (active high with internal pull down resistor)   |  |

| E3            | MCN         | output      | MIPI/LVDS clock lane negative output                       |  |

| E4            | DGND        | ground      | ground for I/O and digital circuit                         |  |

|               |             |             |                                                            |  |

10.12.2015

| signal name | pin<br>type                                                 | description                                                                      |

|-------------|-------------------------------------------------------------|----------------------------------------------------------------------------------|

| EXTCLK      | input                                                       | system input clock/scan clock input                                              |

| DOVDD       | power                                                       | power for I/O circuit                                                            |

| NC          | -                                                           | no connect                                                                       |

| NC          | -                                                           | no connect                                                                       |

| DVDD        | reference                                                   | power for digital circuit                                                        |

| STROBE      | I/O                                                         | strobe output                                                                    |

| DVDD        | reference                                                   | power for digital circuit                                                        |

| NC          | _                                                           | no connect                                                                       |

| NC          | _                                                           | no connect                                                                       |

|             | EXTCLK<br>DOVDD<br>NC<br>NC<br>DVDD<br>STROBE<br>DVDD<br>NC | signal nametypeEXTCLKinputDOVDDpowerNC-NC-DVDDreferenceSTROBEI/ODVDDreferenceNC- |

### table 1-1 signal descriptions (sheet 2 of 2)

### table 1-2 configuration under various conditions

| pin<br>number | signal name | XSHUTDOWN <sup>a</sup> | after XSHUTDOWN<br>release <sup>b</sup> | software standby <sup>c</sup>    |

|---------------|-------------|------------------------|-----------------------------------------|----------------------------------|

| B3            | MDP         | high-z                 | high-z by default                       | high-z by default (configurable) |

| <b>B6</b>     | SIOD        | high-z                 | input/open drain                        | input/open drain                 |

| C3            | MDN         | high-z                 | high-z by default                       | high-z by default (configurable) |

| C4            | SIOC        | input                  | input                                   | input                            |

| C5            | FSIN/VSYNC  | high-z                 | high-z by default                       | high-z by default (configurable) |

| C6            | ULPM        | high-z                 | input/open drain                        | input/open drain                 |

| D3            | MCP         | high-z                 | high-z by default                       | high-z by default (configurable) |

| D5            | PWM         | high-z                 | high-z by default                       | high-z by default (configurable) |

| D6            | XSHUTDOWN   | input                  | input                                   | input                            |

| E2            | ТМ          | input                  | input                                   | input                            |

| E3            | MCN         | high-z                 | high-z by default                       | high-z by default (configurable) |

| E5            | EXTCLK      | input                  | input                                   | input                            |

| F4            | STROBE      | high-z                 | high-z by default                       | high-z by default (configurable) |

a. XSHUTDOWN = 0

b. XSHUTDOWN = 1

c. XSHUTDOWN = 1

standby initiated by register

|   |            |                                       | 0V77         | 50/0           | /7251                  |                  |               |

|---|------------|---------------------------------------|--------------|----------------|------------------------|------------------|---------------|

|   | (A1)       |                                       | (A3)         | (A4)           | (A5)                   | (A6)             | (A7)          |

|   | NC         |                                       | VH           | VN2            | AGND                   | NC               | NC            |

|   |            | (B2)<br>VM                            | (B3)<br>MDP  | (B4)<br>VN1    | (B5)<br>AVDD           | (B6)<br>SIOD     |               |

|   |            | (C2)<br>EVDD                          | (C3)<br>MDN  | C4)<br>SIOC    | (C5)<br>FSIN/<br>VSYNC | (C6)<br>ULPM     |               |

|   | (D1)<br>NC | (D2)<br>EGND                          | (D3)<br>MCP  | (D4)<br>DGND   | (D5)<br>PWM >          | (D6)<br>KSHUTDOV | (D7)<br>VN NC |

| , |            | (E2)<br>TM                            | (E3)<br>MCN  | (E4)<br>DGND   | (E5)<br>EXTCLK         | (E6)<br>DOVDD    |               |

|   | (F1)<br>NC | (F2)<br>NC                            | (F3)<br>DVDD | (F4)<br>STROBE | (F5)<br>DVDD           | (F6)<br>NC       | (F7)<br>NC    |

|   |            | · · · · · · · · · · · · · · · · · · · | ·            | Sec. 11        | Sec. 1                 | Sec. 1           | NC            |

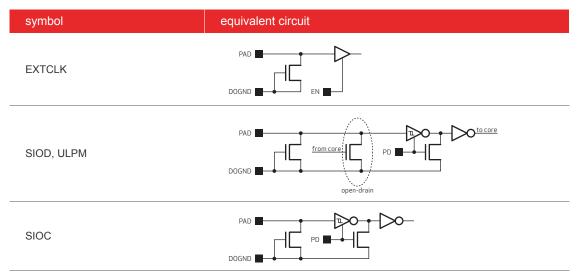

## table 1-3 pad symbol and equivalent circuit (sheet 1 of 2)

## table 1-3 pad symbol and equivalent circuit (sheet 2 of 2)

| symbol                                          | equivalent circuit |

|-------------------------------------------------|--------------------|

| FSIN/VSYNC, STROBE, PWM                         |                    |

| VN1, VN2                                        |                    |

| MDP, MDN, MCP, MCN, EGND,<br>AGND, DGND, VH, VM |                    |

| AVDD, EVDD, DVDD, DOVDD                         |                    |

| TM, XSHUTDOWN                                   |                    |

# 2 system level description

### 2.1 overview

The OV7750 (color) and OV7251 (b&w) image sensors are low voltage, high performance 1/7.5 inch VGA CMOS image sensors that provide the functionality of a single VGA (640x480) camera using OmniPixel3-GS<sup>™</sup> technology. They provide full-frame, sub-sampled, and windowed 8/10-bit MIPI images via the control of the Serial Camera Control Bus (SCCB) interface.

The OV7750/OV7251 has an image array capable of operating at up to 100 frames per second (fps) in 10-bit VGA resolution with complete user control over image quality, formatting and output data transfer.

In addition, OmniVision image sensors use proprietary sensor technology to improve image quality by reducing or eliminating common lighting/electrical sources of image contamination, such as fixed pattern noise, smearing, etc., to produce a clean, fully stable image.

For customized information purposes, the OV7750/OV7251 includes 256 bits of one-time programmable (OTP) memory. The OV7750/OV7251 has one lane MIPI interface.

### 2.2 architecture

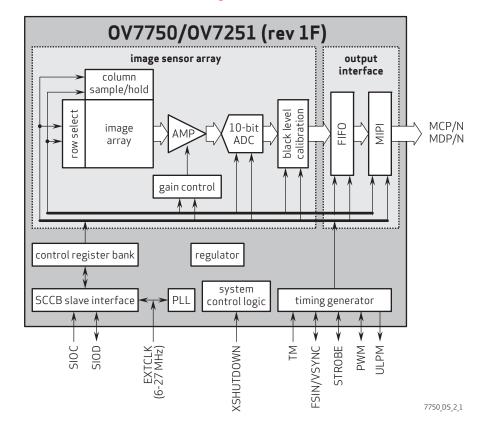

The OV7750/OV7251 sensor core generates streaming pixel data at a constant frame rate. **figure 2-1** shows the functional block diagram.

The timing generator outputs signals to access the image array. The entire pixel array is reset at the same point of time. After the exposure time has elapsed, the pixels stop gathering light and store the collected charge in a storage node. The charge then reads out row by row.

The exposure time is controlled by adjusting the time interval between reset and transferring the charge to storage node. After the data of the pixels in the row has been sampled, it is processed through analog circuitry to correct the offset and multiply the data with corresponding gain. Following analog processing is the ADC which outputs 10-bit data for each pixel in the array. 2-1

### figure 2-1 OV7750/OV7251 block diagram

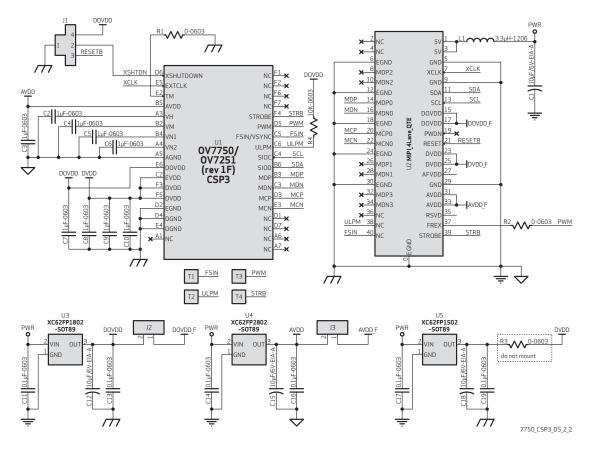

## figure 2-2 reference design schematic

## 2.3 format and frame

The OV7750/OV7251 supports RAW RGB output with a 1-lane MIPI or LVDS interface.

### table 2-1 supported resolution and frame rate

| format <sup>a</sup> | resolution | max<br>frame rate | methodology                   | typical MIPI<br>data rate |

|---------------------|------------|-------------------|-------------------------------|---------------------------|

| full resolution     | 640x480    | 100 fps           | full                          | 1-lane @ 800Mbps          |

| 320x240             | 320x240    | 180 fps           | 2x2 binning, 2:1 sub-sampling | 1-lane @ 800Mbps          |

| 160x120             | 160x120    | 360 fps           | 4:1 sub-sampling              | 1-lane @ 800Mbps          |

a. all formats with minimum 4 dummy lines and 4 dummy pixels

10.12.2015

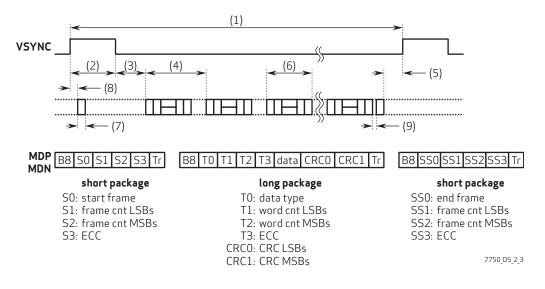

### 2.3.1 MIPI interface

The OV7750/OV7251 supports a single lane MIPI transmitter interface with a data transfer rate of up to 800 Mbps.

### figure 2-3 MIPI timing

### table 2-2 MIPI timing specifications

| mode                       | timing                                                                                                                                                                                                   |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| full resolution<br>640x480 | <ul> <li>(1) 478,848 tp</li> <li>(2) 1,024 tp</li> <li>(3) 11,486 tp</li> <li>(4) 928 tp</li> <li>(5) 21,251 tp</li> <li>(6) 387 tp</li> <li>(7) 2 tp</li> <li>(8) -178 tp</li> <li>(9) 29 tp</li> </ul> |

| 320x240                    | where tp = Tsclk<br>(1) 234,688 tp<br>(2) 1,024 tp<br>(3) 6,496 tp<br>(4) 772 tp<br>(5) 42,422 tp<br>(6) 216 tp<br>(7) 22 tp<br>(8) 404 tp                                                               |

|                            | <ul> <li>(8) -194 tp</li> <li>(9) 9 tp</li> <li>where tp = Tsclk</li> </ul>                                                                                                                              |

#### 2.3.2 VSYNC timing in MIPI mode

The VSYNC rising edge delay is controlled by register vsync\_delay ({0x4314, 0x4315, 0x4316}) in all three VSYNC modes. VSYNC width is controlled by register vsync\_width\_pixel ({0x4311, 0x4312}) for VSYNC modes 1 and 2. The steps of both registers vsync\_delay and vsync\_width\_pixel are 1 system clock cycle.

Note that VSYNC timing in mode 3 is a long VSYNC mode. The register vsync\_width\_pixel ({0x4311, 0x4312}) controls VSYNC falling edge differently.

2.3.2.1 VSYNC mode 1

In mode 1, VSYNC is generated by the internal start of frame (SOF) signal (see figure 2-4).

#### 2.3.2.2 VSYNC mode 2

In mode 2, VSYNC is generated by the internal end of frame (EOF) signal (see figure 2-5).

### figure 2-5 VSYNC timing in mode 2

#### 2.3.2.3 VSYNC mode 3

In mode 3, VSYNC is generated by EOF and SOF (see figure 2-6).

### figure 2-6 VSYNC timing in mode 3

# 2.4 I/O control

# table 2-3 I/O control registers

| function                        | register | description                                                                                 |

|---------------------------------|----------|---------------------------------------------------------------------------------------------|

| output drive capability control | 0x3001   | Bit[6:5]: I/O pin drive capability<br>00: 1x<br>01: 2x<br>10: 3x<br>11: 4x                  |

| STROBE I/O control              | 0x3005   | Bit[3]: input/output control for STROBE pin<br>0: input<br>1: output                        |

| STROBE output select            | 0x3027   | Bit[3]: output selection for STROBE pin<br>0: normal data path<br>1: register control value |

| STROBE output value             | 0x3009   | Bit[3]: STROBE output value                                                                 |

| PWM I/O control                 | 0x3005   | Bit[2]: input/output control for PWM pin<br>0: input<br>1: output                           |

| PWM output select               | 0x3027   | Bit[2]: output selection for PWM pin<br>0: normal data path<br>1: register control value    |

| PWM output value                | 0x3009   | Bit[2]: PWM output value                                                                    |

| FSIN/VSYNC I/O control          | 0x3005   | Bit[1]: input/output control for FSIN pin<br>0: input<br>1: output                          |

| FSIN/VSYNC output select        | 0x3027   | Bit[1]: output selection for FSIN pin<br>0: normal data path<br>1: register control value   |

| FSIN/VSYNC output value         | 0x3009   | Bit[1]: FSIN output value                                                                   |

# 2.5 power management

### 2.5.1 power up sequence

The OV7750/OV7251 can use an internal regulator to provide digital core 1.5V DVDD for the digital core.

| table 2-4 | power up sequ | ence |

|-----------|---------------|------|

|           |               |      |

| case | DVDD     | XSHUTDOWN | power up sequence requirement                                                                                                                                                                                                                                                               |

|------|----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | internal | GPIO      | <ul> <li>Refer to figure 2-7</li> <li>1. AVDD rising can occur before or after DOVDD rising as long as they are rising before XSHUTDOWN rising</li> <li>2. XSHUTDOWN is pulled up after AVDD and DOVDD are stable</li> </ul>                                                                |

| 2    | external | GPIO      | <ul> <li>Refer to figure 2-8</li> <li>AVDD rising can occur before or after DOVDD rising as long as they are rising before XSHUTDOWN rising</li> <li>XSHUTDOWN is pulled up after AVDD and DOVDD are stable</li> <li>DVDD rises after DOVDD, but before XSHUTDOWN is pulled high</li> </ul> |

### table 2-5 power up sequence timing constraints

| constraint                                                           | label | min                 | max           | unit          |

|----------------------------------------------------------------------|-------|---------------------|---------------|---------------|

| AVDD rising – DOVDD rising                                           | tO    | 0                   | 00            | ms            |

| DOVDD rising – AVDD rising                                           | t1    | 0                   | ~             | ms            |

| AVDD or DOVDD rising, whichever is<br>last – XSHUTDOWN rising        | t2    | 1                   |               | ms            |

| XSHUTDOWN rising – first SCCB transaction                            | t3    | 65536               |               | EXTCLK cycles |

| minimum number of EXTCLK cycles prior to the first SCCB transaction  | t4    | 65536               |               | EXTCLK cycles |

| PLL start up/lock time                                               | t5    |                     | 0.2           | ms            |

| entering streaming mode – first frame start sequence (fixed part)    | t6    |                     | 10            | ms            |

| entering streaming mode – first frame start sequence (variable part) | t7    | delay is the exposu | re time value | lines         |

| DOVDD to external DVD rising                                         | t8    | 0                   |               | ms            |

| DOVDD rising to XSHUTDOWN rising                                     | t9    | 0                   |               | ms            |

### figure 2-7 power up sequence (case 1)

note 1 with minimum power consumption

7750\_DS\_2\_7

## figure 2-8 power up sequence (case 2)

### 2.5.2 power down sequence

The digital and analog supply voltages can be powered down in any order (e.g., DOVDD, then AVDD or AVDD, then DOVDD). Similar to the power-up sequence, the EXTCLK input clock may be either gated or continuous. If the SCCB command to exit streaming is received while a frame of MIPI data is being output, then the sensor must wait to the MIPI frame end code before entering software standby mode.

If the SCCB command to exit streaming mode is received during the inter frame time, then the sensor will enter software standby mode immediately.

#### table 2-6 power down sequence

| case | DVDD     | XSHUTDOWN | power down sequence requirement                                                                                                                                                                                           |

|------|----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | internal | GPIO      | <ul> <li>Refer to figure 2-9</li> <li>1. software standby recommended</li> <li>2. pull XSHUTDOWN low for minimum power consumption</li> <li>3. AVDD and DOVDD may fall in any order</li> </ul>                            |

| 2    | external | GPIO      | <ul> <li>Refer to figure 2-10</li> <li>1. software standby recommended</li> <li>2. pull XSHUTDOWN low for minimum power consumption</li> <li>3. pull DVDD low</li> <li>4. AVDD and DOVDD may fall in any order</li> </ul> |

### table 2-7 power down sequence timing constraints

| constraint                                                                 | label | min                                                                                                          | max                               | unit          |

|----------------------------------------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------|

| enter software standby SCCB command device in software standby mode        | t0    | when a frame of M<br>wait for the MIPI er<br>entering the softwa<br>otherwise, enter the<br>mode immediately | nd code before<br>re for standby; |               |

| minimum of EXTCLK cycles after the last SCCB transaction or MIPI frame end | t1    | 512                                                                                                          |                                   | EXTCLK cycles |

| last SCCB transaction or MIPI frame end, XSHUTDOWN falling                 | t2    | 512                                                                                                          |                                   | EXTCLK cycles |

| XSHUTDOWN falling - AVDD falling or<br>DOVDD falling whichever is first    | t3    | 0.0                                                                                                          |                                   | ms            |

| AVDD falling - DOVDD falling                                               | t4    | AVDD and DOVDD                                                                                               |                                   | ms            |

| DOVDD falling - AVDD falling                                               | t5    | order, the falling se<br>from 0 ns to infinity                                                               |                                   | ms            |

| XSHUTDOWN falling - DVDD falling                                           | t6    | 0                                                                                                            |                                   | ms            |

| DVDD falling to DOVDD falling                                              | t7    | 0                                                                                                            |                                   | ms            |

Omn sision.

### figure 2-9 power down sequence (case 1)

**note 1** with minimum power consumption

7750\_DS\_2\_9

### **figure 2-10** power down sequence (case 2)

**note 1** with low power consumption

7750\_DS\_2\_10

## 2.6 reset

The OV7750/OV7251 sensor includes a **XSHUTDOWN** pin (pin **D6**) that forces a complete hardware reset when it is pulled low (GND). The OV7750/OV7251 clears all registers and resets them to their default values when a hardware reset occurs.

### 2.6.1 power ON reset generation

The OV7750/OV7251 has a power on reset that is generated after the core power becomes stable.

### 2.7 hardware and software standby

Two suspend modes are available for the OV7750/OV7251:

- hardware standby

- software standby

### table 2-8 hardware and software standby description

| mode                            | description                                                                                                                                                                                                                                                                          |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| hardware standby with XSHUTDOWN | <ol> <li>enabled by pulling XSHUTDOWN pad low</li> <li>power down all blocks</li> <li>register values are reset to default values</li> <li>no SCCB communication</li> <li>minimum power consumption</li> </ol>                                                                       |

| software standby                | <ol> <li>default mode after power on reset</li> <li>power down all blocks except SCCB and regulator</li> <li>register values are maintained</li> <li>SCCB communication is available</li> <li>low power consumption</li> <li>GPIO can be configured as high/low/tri-state</li> </ol> |

## 2.8 system clock control

The OV7750/OV7251 has two on-chip PLLs which generate the system clock from a 6~27 MHz input clock. A programmable clock divider is provided to generate different frequencies for the system.

### 2.8.1 PLL configuration

### figure 2-12 OV7750/OV7251 PLL1 clock diagram

### figure 2-13 OV7750/OV7251 PLL2 clock diagram

### table 2-9 PLL control registers (sheet 1 of 3)

| function         | address | description                                                                                                                           |  |  |

|------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PLL2_pre_divider | 0x3098  | Bit[4:0]: PLL2 pre-divider<br>0x2: /1<br>0x3: /1.5<br>0x4: /2<br>0x5: /2.5<br>0x6: /3<br>0x8: /4<br>0xC: /6<br>0x10: /8<br>Others: /1 |  |  |

| PLL2_multiplier  | 0x3099  | Bit[7:0]: PLL2 multiplier<br>Multiplier = 0x3099[7:0]                                                                                 |  |  |

10.12.2015

| function         | address | description                                                                                                                                              |

|------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL2_divider     | 0x309D  | Bit[2]: PLL2 divider<br>0: /1<br>1: /1.5                                                                                                                 |

| PLL2_sys_divider | 0x309A  | Bit[3:0]: System clock divider<br>0x2: /4<br>0x3: /6<br>0x4: /8<br>0x5: /10<br>0x6: /12<br>0x7: /14<br>0x8: /16<br>0x9: /18<br>Others: Not allowed       |

| PLL2_ADC_divider | 0x309B  | Bit[3:0]: PLL2 ADC clock divider<br>0x2: /1<br>0x3: /1.5<br>0x4: /2<br>0x5: /2.5<br>0x6: /3<br>0x7: /3.5<br>0x8: /4<br>0x9: /4.5<br>Others: Not allowed  |

| PLL1_multiplier  | 0x30B3  | Bit[7:0]: PLL1 multiplier<br>Multiplier = 0x30B3[7:0]                                                                                                    |

| PLL1_pre_divider | 0x30B4  | Bit[3:0]: PLL1 pre-divider<br>0x0: /1<br>0x1: /1<br>0x2: /2<br>0x3: /3<br>0x4: /4<br>0x5: /1.5<br>0x6: /6<br>0x7: /2.5<br>0x8: /8<br>Others: Not allowed |

| PLL1_pix_divider | 0x30B0  | Bit[3:0]: PLL1 pixel divider<br>0x8: /8<br>0xA: /10<br>Others: Not allowed                                                                               |

| PLL1_divider     | 0x30B1  | Bit[4:0]: PLL1 divider<br>Divider = $0x30B1[4:0]$ , when $1 \le 0x30B1[4:0] \le 16$<br>Others: Not allowed                                               |

## table 2-9 PLL control registers (sheet 2 of 3)

## table 2-9 PLL control registers (sheet 3 of 3)

| function          | address | description                                                     |

|-------------------|---------|-----------------------------------------------------------------|

| PLL1_MIPI_divider | 0x30B5  | Bit[2:0]: PLL1 MIPI divider<br>0x2: /2<br>0x4: /4<br>Others: /1 |

### table 2-10 sample PLL configuration<sup>a</sup>

| name             | address     | value    |

|------------------|-------------|----------|

| PLL2_pre_divider | 0x3098[4:0] | 0x04     |

| PLL2_multiplier  | 0x3099[7:0] | 0x28     |

| PLL2_sys_divider | 0x309A[3:0] | 0x05     |

| PLL2_ADC_divider | 0x309B[3:0] | 0x04     |

| PLL_PLL1D        | 0x309D[2]   | 0x00     |

| PLL1_multiplier  | 0x30B3[7:0] | 0x32     |

| PLL1_pre_divider | 0x30B4[3:0] | 0x02     |

| PLL1_pix_divider | 0x30B0[3:0] | 0x0A     |

| PLL1_divider     | 0x30B1[4:0] | 0x01     |

| SYS_CLK          |             | 48 MHz   |

| MIPI_CLK         |             | 600 Mbps |

| EXTCLK           |             | 24 MHz   |

a. PLL control for VGA @ 100 fps with 1 lane, 10-bit output

## figure 2-14 clock connection diagram

| parameter              | value        |

|------------------------|--------------|

| PLL1_multiplier input  | 4~27 MHz     |

| PLL1_multiplier output | 300~800 MHz  |

| PLL2_multiplier input  | 4~27 MHz     |

| PLL2_multiplier output | 200~800 MHz  |

| SYS_CLK                | up to 51 MHz |

## 2.9 serial camera control bus (SCCB) interface

The Serial Camera Control Bus (SCCB) interface controls the image sensor operation. Refer to the *OmniVision Technologies Serial Camera Control Bus (SCCB) Specification* for detailed usage of the serial control port.

The OV7750/OV7251 responds to two SCCB ID set by register SC\_SCCB\_ID1 (default 0xC0) and SC\_SCCB\_ID2 (default 0xE0). One of them can be used as a broadcasting ID and the other one can be programmed to a unique ID.

#### 2.9.1 data transfer protocol

The data transfer of the OV7750/OV7251 follows the SCCB protocol.

#### 2.9.2 message format

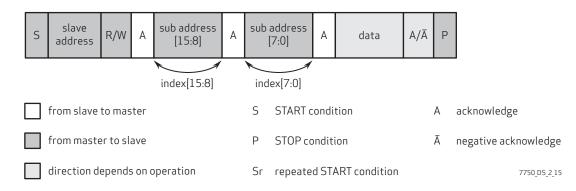

The OV7750/OV7251 supports the message format shown in **figure 2-15**. The repeated START (Sr) condition is not shown in SCCB single read from random location, but is shown in SCCB single read from current location and SCCB sequential read from random location.

### figure 2-15 message type

message type: 16-bit sub-address, 8-bit data, and 7-bit slave address

#### 2.9.3 read / write operation

The OV7750/OV7251 supports four different read operations and two different write operations:

- a single read from random locations

- · a sequential read from random locations

- a single read from current location

- a sequential read from current location

- · single write to random locations

- sequential write starting from random location

The sub-address in the sensor automatically increases by one after each read/write operation.

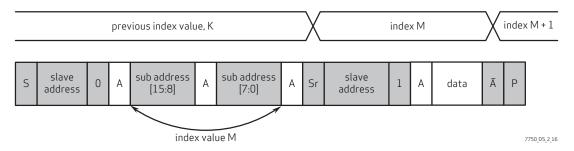

In a single read from random locations, the master does a dummy write operation to desired sub-address, issues a repeated start condition and then addresses the camera again with a read operation. After acknowledging its slave address, the camera starts to output data onto the SIOD line as shown in **figure 2-16**. The master terminates the read operation by setting a negative acknowledge and stop condition.

### figure 2-16 SCCB single read from random location

If the host addresses the camera with read operation directly without the dummy write operation, the camera responds by setting the data from last used sub-address to the SIOD line as shown in **figure 2-17**. The master terminates the read operation by setting a negative acknowledge and stop condition.

### figure 2-17 SCCB single read from current location

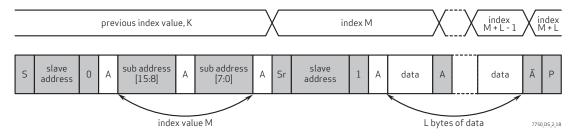

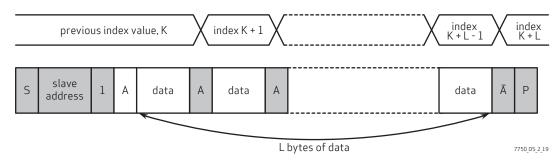

The sequential read from a random location is illustrated in **figure 2-18**. The master does a dummy write to the desired sub-address, issues a repeated start condition after acknowledge from slave and addresses the slave again with read operation. If a master issues an acknowledge after receiving data, it acts as a signal to the slave that the read operation shall continue from the next sub-address. When master has read the last data byte, it issues a negative acknowledge and stop condition.

### figure 2-18 SCCB sequential read from random location

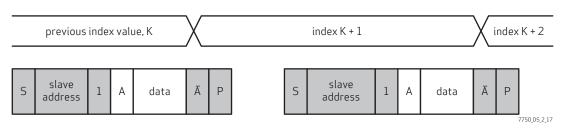

The sequential read from current location is similar to a sequential read from a random location. The only exception is that there is no dummy write operation, as shown in **figure 2-19**. The master terminates the read operation by setting a negative acknowledge and stop condition.

### figure 2-19 SCCB sequential read from current location

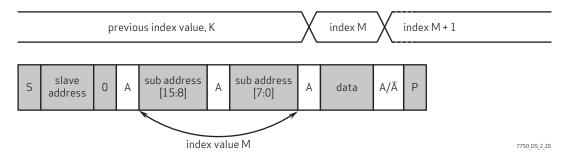

The write operation to a random location is illustrated in **figure 2-20**. The master issues a write operation to the slave, sets the sub-address and data correspondingly after the slave has acknowledged. The write operation is terminated with a stop condition from the master.

### figure 2-20 SCCB single write to random location

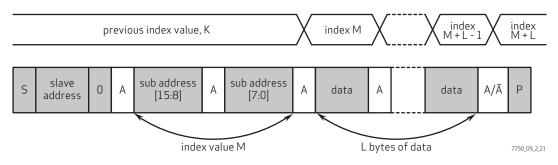

The sequential write is illustrated in **figure 2-21**. The slave automatically increments the sub-address after each data byte. The sequential write operation is terminated with stop condition from the master.

### figure 2-21 SCCB sequential write to random location

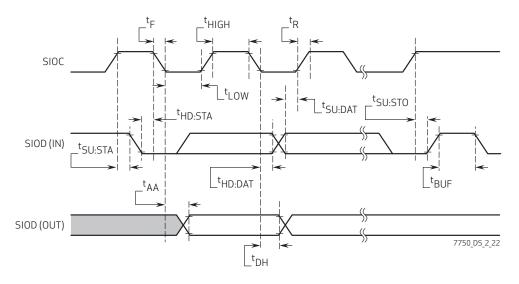

#### 2.9.4 SCCB timing

## figure 2-22 SCCB interface timing

# table 2-12 SCCB interface timing specifications<sup>ab</sup>

| symbol                          | parameter                      | min  | typ | max | unit |

|---------------------------------|--------------------------------|------|-----|-----|------|

| f <sub>SIOC</sub>               | clock frequency                |      |     | 400 | kHz  |

| t <sub>LOW</sub>                | clock low period               | 1.3  |     |     | μs   |

| t <sub>HIGH</sub>               | clock high period              | 0.6  |     |     | μs   |

| t <sub>AA</sub>                 | SIOC low to data out valid     | 0.1  |     | 0.9 | μs   |

| t <sub>BUF</sub>                | bus free time before new start | 1.3  |     |     | μs   |

| t <sub>HD:STA</sub>             | start condition hold time      | 0.6  |     |     | μs   |

| t <sub>SU:STA</sub>             | start condition setup time     | 0.6  |     |     | μs   |

| t <sub>HD:DAT</sub>             | data in hold time              | 0    |     |     | μs   |

| t <sub>SU:DAT</sub>             | data in setup time             | 0.1  |     |     | μs   |

| t <sub>SU:STO</sub>             | stop condition setup time      | 0.6  |     |     | μs   |

| t <sub>R</sub> , t <sub>F</sub> | SCCB rise/fall times           |      |     | 0.3 | μs   |

| t <sub>DH</sub>                 | data out hold time             | 0.05 |     |     | μs   |

a. SCCB timing is based on 400kHz mode

timing measurement shown at the beginning of the rising edge or the end of the falling edge signifies 30%, timing measurement shown in the middle of the rising/falling edge signifies 50%, timing measurement shown at the beginning of the falling edge or the end of the rising edge signifies 70%

#### 2.9.5 group write and fast mode switching

Group write is supported in order to update a group of registers in the same frame. These registers are guaranteed to be written prior to the internal latch at the frame boundary. Group write can be used to switch modes quickly.

### table 2-13 context switching control

| address | register name  | default<br>value | R/W | description                                                                                                                                                                                                                                                                                                              |

|---------|----------------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x3208  | GROUP ACCESS   | -                | W   | Group Access<br>Bit[7:4]: group_ctrl<br>0000: Group hold start<br>0001: Group hold end<br>1010: Group launch<br>1110: Immediate launch<br>others: Reserved<br>Bit[3:0]: group_id<br>0000: Group bank 0, default start<br>from address 0x00<br>0001: Group bank 1, default start<br>from address 0x40<br>others: Reserved |

| 0x3209  | GRP0_PERIOD    | 0x00             | RW  | Frames For Staying in Group 0                                                                                                                                                                                                                                                                                            |

| 0x320A  | GRP1_PERIOD    | 0x00             | RW  | Frames For Staying in Group 1                                                                                                                                                                                                                                                                                            |

| 0x320B  | GRP_SWCTRL     | 0x01             | RW  | Bit[3]: group_switch_repeat<br>Bit[2]: Group switch enable<br>Bit[1:0]: Second group selection                                                                                                                                                                                                                           |

| 0x320D  | GRP_ACT        | _                | R   | Indicates Which Group is Active                                                                                                                                                                                                                                                                                          |

| 0x320E  | FRAME_CNT_GRP0 | -                | R   | frame_cnt_grp0                                                                                                                                                                                                                                                                                                           |

| 0x320F  | FRAME_CNT_GRP1 | _                | R   | frame_cnt_grp1                                                                                                                                                                                                                                                                                                           |

CMOS VGA (640 x 480) image sensor with OmniPixel3-GS™ technology

#### block level description 3

## 3.1 pixel array structure

The OV7750/OV7251 sensor has an image array of 656 columns by 496 rows (325,376 pixels). figure 3-1 shows a cross-section of the image sensor array.

The color filters are arranged in a Bayer pattern. The primary color BG/GR array is arranged in line-alternating fashion. Of the 325, 376 pixels, 316,224 (648x488) are active pixels and can be output. The other pixels are used for black level calibration and interpolation.

#### figure 3-1 sensor array region color filter layout

# 3.2 subsampling

There are two subsampling modes in the OV7750/OV7251: binning and skipping. Both are acceptable methods of reducing output resolution while maintaining the field of view. Binning is usually preferred as it increases the pixel's signal-to-noise ratio. When the binning function is ON, voltage levels of adjacent pixels are averaged. In skipping mode (binning function is OFF), alternate pixels, which are not output, are merely skipped. The OV7750/OV7251 supports 2x2 binning. figure 3-2 illustrates 2x2 binning, where the voltage levels of two horizontal (2x1) adjacent same-color pixels are averaged before entering the ADC.

#### figure 3-3 example of 2:1 subsampling

| P00 | P01 | P02 | P03 | P00 | P02         |

|-----|-----|-----|-----|-----|-------------|

| P10 | P11 | P12 | P13 |     |             |

| P20 | P21 | P22 | P23 | P20 | P22         |

| P30 | P31 | P32 | P33 |     | 7750_DS_3_3 |

#### figure 3-4 example of 4:1 subsampling

| P00      | P01 | P02 | P03 | P04 | P05 | P06 | P07      | P00 | P04         |

|----------|-----|-----|-----|-----|-----|-----|----------|-----|-------------|

| :<br>P20 | P21 | P22 | P23 | P24 | P25 | P26 | P27      | P40 | P44         |

| _        |     | _   | _   | _   |     |     | <u> </u> |     | 7750 DS 3.4 |

#### table 3-1 binning-related registers

| address | register name  | default<br>value | R/W | descriptic | on                 |

|---------|----------------|------------------|-----|------------|--------------------|

| 0x3820  | TIMING_FORMAT1 | 0x00             | RW  | Bit[1]:    | Vertical binning   |

| 0x3821  | TIMING_FORMAT2 | 0x00             | RW  | Bit[0]:    | Horizontal binning |

# 4 image sensor core digital functions

# 4.1 mirror and flip

The OV7750/OV7251 provides mirror and flip readout modes, which respectively reverse the sensor data readout order horizontally and vertically (see **figure 4-1**).

### figure 4-1 mirror and flip samples

### table 4-1 mirror and flip registers

| address | register name      | default<br>value | R/W | description                                                                                      |

|---------|--------------------|------------------|-----|--------------------------------------------------------------------------------------------------|

| 0x3820  | IMAGE_ORIENTATION  | 0x00             | RW  | Timing Control Register<br>Bit[2]: Vertical flip enable<br>0: Normal<br>1: Vertical flip         |

| 0x3821  | IMAGE_ ORIENTATION | 0x00             | RW  | Timing Control Register<br>Bit[2]: Horizontal mirror enable<br>0: Normal<br>1: Horizontal mirror |

# 4.2 image windowing

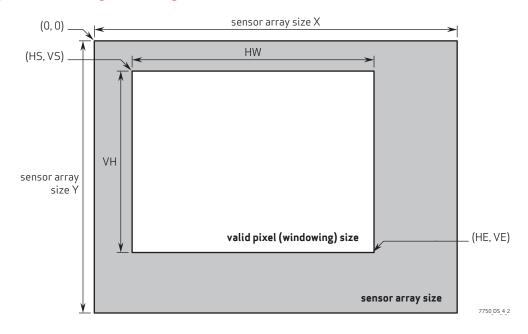

An image windowing area is defined by four parameters, horizontal start (HS), horizontal end (HE), vertical start (VS), and vertical end (VE). By properly setting the parameters, any portion within the sensor array size can output as a visible area. Windowing is achieved by simply masking off the pixels outside of the window; thus, the timing is not affected.

#### figure 4-2 image windowing

#### table 4-2 image windowing control functions

| function         | register         | R/W | description                          |

|------------------|------------------|-----|--------------------------------------|

| horizontal start | {0x3800, 0x3801} | RW  | HS[9:8] = 0x3800<br>HS[7:0] = 0x3801 |

| vertical start   | {0x3802, 0x3803} | RW  | VS[9:8] = 0x3802<br>VS[7:0] = 0x3803 |

| horizontal end   | {0x3804, 0x3805} | RW  | HE[9:8] = 0x3804<br>HE[7:0] = 0x3805 |

| vertical end     | {0x3806, 0x3807} | RW  | VE[9:8] = 0x3806<br>VE[7:0] = 0x3807 |

# 4.3 test pattern

For testing purposes, the OV7750/OV7251 offers three test patterns:

#### 4.3.1 general color bar

## figure 4-3 test pattern

## table 4-3 general color bar selection control

| function          | register | default value | R/W | descriptio | on               |

|-------------------|----------|---------------|-----|------------|------------------|

| general color bar | 0x5E00   | 0x0C          | RW  | Bit[7]:    | Color bar enable |

#### 4.3.2 solid color test pattern

# table 4-4 solid color test pattern control (sheet 1 of 2)

| function                    | register | default value | R/W | description                                                                                                                                                                                    |

|-----------------------------|----------|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| solid color test<br>pattern | 0x4320   | 0x80          | RW  | Bit[7:6]: Pixel order<br>00: GR/BG<br>01: RG/GB<br>10: BG/GR<br>11: GB/RG<br>Bit[1]: Solid color test enable<br>0: Solid color test OFF<br>1: Solid color test enable<br>Bit[0]: Debug control |

| solid color B               | 0x4322   | 0x00          | RW  | Bit[1:0]: solid_color_b[9:8]                                                                                                                                                                   |

| solid color B               | 0x4323   | 0x00          | RW  | Bit[7:0]: solid_color_b[7:0]                                                                                                                                                                   |

| solid color Gb              | 0x4324   | 0x00          | RW  | Bit[1:0]: solid_color_Gb[9:8]                                                                                                                                                                  |

| solid color Gb              | 0x4325   | 0x00          | RW  | Bit[7:0]: solid_color_Gb[7:0]                                                                                                                                                                  |

10.12.2015

| function       | register | default value | R/W | description                   |

|----------------|----------|---------------|-----|-------------------------------|

| solid color R  | 0x4326   | 0x00          | RW  | Bit[1:0]: solid_color_r[9:8]  |

| solid color R  | 0x4327   | 0x00          | RW  | Bit[7:0]: solid_color_r[7:0]  |

| solid color Gr | 0x4328   | 0x00          | RW  | Bit[1:0]: solid_color_Gr[9:8] |

| solid color Gr | 0x4329   | 0x00          | RW  | Bit[7:0]: solid_color_Gr[7:0] |

#### table 4-4 solid color test pattern control (sheet 2 of 2)

# 4.4 black level calibration (BLC)

The pixel array contains several optically shielded (black) lines. These lines are used as reference for black level calibration.

Black level adjustments can be made with registers 0x4000, 0x4001, 0x4002, 0x4003, 0x4004 and 0x4009.

### table 4-5BLC control functions (sheet 1 of 2)

| address | register name | default<br>value | R/W | description                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|---------------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x5000  | ISP CTRL00    | 0x85             | RW  | Bit[0]: BLC enable<br>0: Disable<br>1: Enable                                                                                                                                                                                                                                                                                                                                                                            |

| 0x4001  | BLC CTRL 01   | 0xC2             | RW  | Bit[7]: Slope apply enable<br>0: Disable<br>1: Enable<br>Bit[5:0]: BLC start line number                                                                                                                                                                                                                                                                                                                                 |

| 0x4002  | BLC_AUTO      | 0x45             | RW  | Bit[7]:       Format change enable         0:       BLC will remain the same after format change         1:       BLC will redo after format change         Bit[6]:       BLC auto enable         0:       Get black level manually from register         1:       Calculate black level from auto statistics         Bit[5:0]:       Reset frame number         Frames that will continue to go through BLC after reset |

PRODUCT SPECIFICATION

Downloaded from Arrow.com.

10.12.2015

#### BLC control functions (sheet 2 of 2) table 4-5

| address | register name | default<br>value | R/W | description                                                                                                                                                                                                                                                                                                                                                                     |

|---------|---------------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x4003  | BLC_FREEZE    | 0x08             | RW  | Bit[7]:       BLC redo enable         0:       Normal         1:       Force BLC to redo N frames (where N=0x4003[5:0]) when this bit is set         Bit[6]:       Freeze enable         0:       Normal         1:       BLC black level will not update.         Priority lower than always update.         Bit[5:0]:       Manual frame number         BLC redo frame number |

| 0x4004  | BLC NUM       | 0x04             | RW  | Bit[7:6]: Reserved<br>Bit[5:0]: Number of black lines used                                                                                                                                                                                                                                                                                                                      |

| 0x4009  | BLC_TARGET    | 0x10             | RW  | Bit[7:0]: Black target level[7:0]                                                                                                                                                                                                                                                                                                                                               |

#### ALS algorithm control registers (sheet 1 of 3) table 4-6

| address | register name | default<br>value | R/W                                                                                                         | description                                                                                                                                                                                                                              |

|---------|---------------|------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x4E00  | ALS CTRL 00   | 0x00             | RW                                                                                                          | Bit[5]: Range level adjust enable<br>0: Disable<br>1: Enable<br>Bit[4]: Merge average option enable<br>0: Disable<br>1: Enable<br>Bit[3]: Merge enable<br>0: Disable<br>1: Enable<br>Bit[2]: Reserved<br>Bit[1]: Select abs value enable |

|         |               |                  | Bit[1]: Select abs value enable<br>0: Disable<br>1: Enable<br>Bit[0]: ALS enable<br>0: Disable<br>1: Enable |                                                                                                                                                                                                                                          |

| 0x4E01  | ALS CTRL 01   | 0x01             | RW                                                                                                          | Bit[7]: Clock select<br>Bit[6:0]: Sample period intervals                                                                                                                                                                                |

| 0x4E02  | ALS CTRL 02   | 0x00             | RW                                                                                                          | Bit[7:0]: Manual threshold[15:8]                                                                                                                                                                                                         |

| 0x4E03  | ALS CTRL 03   | 0x00             | RW                                                                                                          | Bit[7:0]: Manual threshold[7:0]                                                                                                                                                                                                          |

| 0x4E04  | ALS CTRL 04   | 0x00             | RW                                                                                                          | Bit[7:0]: Small zone manual threshold[15:8]                                                                                                                                                                                              |

| 0x4E05  | ALS CTRL 05   | 0x00             | RW                                                                                                          | Bit[7:0]: Small zone manual threshold[7:0]                                                                                                                                                                                               |

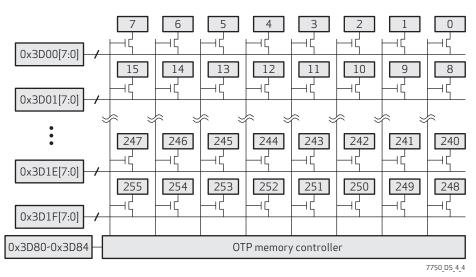

| 0x4E06  | ALS CTRL 06   | 0x00             | RW                                                                                                          | Bit[7:0]: Large zone manual threshold[15:8]                                                                                                                                                                                              |