OV7950/OV7451 CMOS Analog NTSC CAMERACHIP<sup>TM</sup> with OmniPixel<sup>®</sup> Technology

#### **General Description**

The OV7950 (color) and OV7451 (black & white) single chip CMOS CAMERACHIPS<sup>TM</sup> are designed to provide a high level of functionality for all applications requiring a small footprint, low voltage, low power consumption and high performance color or B&W video camera.

Both devices support NTSC composite video output and can directly interface with a VCR TV monitor or other device with 75 ohm loading.

**Note:** The OV7950/OV7451 is available in a lead-free package.

#### **Features**

- Single chip 1/4" format video camera

- Composite video (NTSC) output

- High sensitivity

- Automatic exposure/gain with 16 zone control

- Horizontal and vertical windowing capability

- Auto white balance control

- Aperture/Gamma correction

- 50/60 Hz flicker cancellation

- External frame sync capability (Genlock)

- SPI/EEPROM used to control overlay and set other customer variables

- Two sets of dynamic overlay controls

- Master/slave compatible Serial Camera Control Bus (SCCB) control interface for register programming

- Low power consumption

- Extreme low dark current for high temperature applications

- Defective pixel correction

### Ordering Information

| Product                                 | Package |

|-----------------------------------------|---------|

| OV07950-C10A (Color, NTSC)              | CLCC-48 |

| OV07451-C10A (B&W with microlens, NTSC) | CLCC-48 |

#### **Applications**

- Security/Surveillance cameras

- Video Conferencing

- Video phones

- Video e-mail

- Toys

- Finger print equipment

- Medical and dental equipment

### **Key Specifications**

|                     | W    |                       |                                    |

|---------------------|------|-----------------------|------------------------------------|

|                     |      | Array Size            | 656 x 492                          |

| Power Sup           | nlv  | Analog/ADC/IO         | 3.3 VDC <u>+</u> 5%                |

| Fower Sup           | ріу  | Digital Core          | 1.8 VDC <u>+</u> 5%                |

|                     | Pov  | ver Consumption       | 200 mW                             |

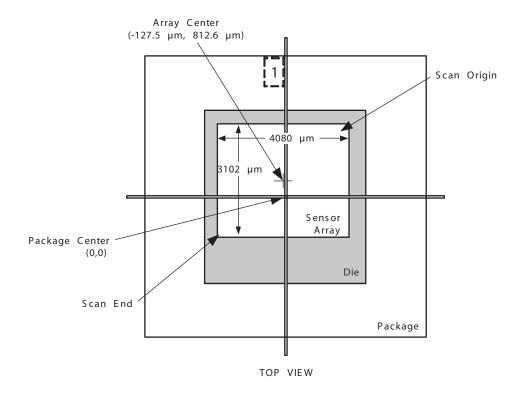

|                     |      | Image Area            | 4.080 mm x 3.102 mm                |

| Exposure            |      | OV7950                | 1/60s - 20 µs                      |

| Time Rar            | ige  | OV7451                | 1/30s - 20 µs                      |

|                     |      | <b>Optical Format</b> | 1/4"                               |

|                     |      | S/N Ratio             | 48 dB                              |

|                     |      | Dynamic Range         | 49 dB                              |

| 7                   |      | Pixel Size            | 6.0 µm x 6.0 µm                    |

| Dark Current        |      |                       | 10 mW/s @ 60°C                     |

| Fixed Pattern Noise |      |                       | 0.22% of V <sub>PEAK-TO-PEAK</sub> |

|                     | Pacl | kage Dimensions       | 14.22 mm x 14.22 mm                |

|                     |      |                       |                                    |

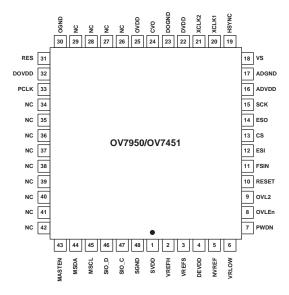

#### Figure 1 OV7950/OV7451 Pin Diagram (Top View)

#### www.DFunctional Description

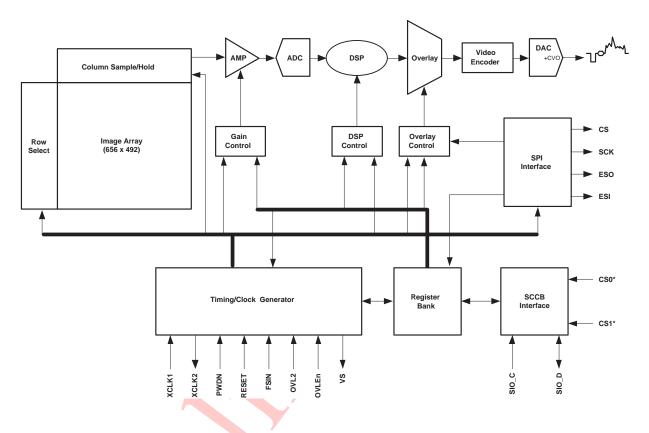

This section describes the various functions of the OV7950/OV7451. Refer to Figure 2 for the functional block diagram of the OV7950/OV7451.

#### Figure 2 Functional Block Diagram

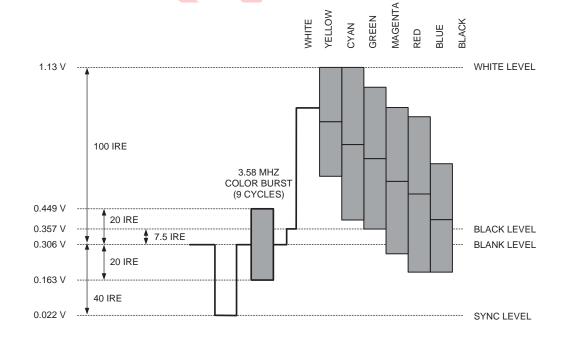

#### **Video Standards**

NTSC TV standards are implemented and available as output in the OV7950/OV7451 CAMERACHIPS. Note that the accuracy and stability of the crystal clock frequency is important to avoid unwanted color shift in the TV video system. OmniVision recommends using a 12.27 MHz crystal when utilizing the OV7950/OV7451 CAMERACHIP.

#### **Video Format**

The OV7950/OV7451 CAMERACHIP supports Composite (CVBS) video format only. Composite signals are generated from the built-in TV encoder. The OV7451 only outputs the luminance signal.

#### **Image Sensor Functions**

#### White Balance

The function of white balance in the OV7950/OV7451 CAMERACHIP is to adjust and calibrate the image device sensitivity on the primary (RGB) colors to match the color cast of the light source. The Auto White Balance (AWB) can be enabled or disabled by register control. If the AWB is enabled, the image sensors continuously perform white balancing.

#### **Mirror and Vertical Flip**

The OV7950/OV7451 provides horizontal mirror and vertical flip functions. These functions can be turned ON or OFF via register settings.

#### www.DataSheet4U.com Multi-Chip Synchronize

The OV7950/OV7451 CAMERACHIP provides the multi-chip Synchronize function where one chip works as the master and all others as slave devices. The master chip provides the frame synchronize signal through pin VS (pin 18). All slave devices then accept the frame synchronize signal through pin FSIN. This mode allows all devices to synchronize together.

#### **Chip Configuration**

The OV7950/OV7451 CAMERACHIP has been designed for ease-of-use in many stand-alone applications. Some functions like serial interface slave address and NTSC selection can be set by connecting appropriate pins high (logic "1") or low (logic "0") through a 10 K $\Omega$  resistor. The OV7950/OV7451 CAMERACHIP also has a serial master and slave interface for programmable access to all register functions.

#### **Additional Picture Controls**

The OV7950/OV7451 CAMERACHIP provides additional picture control functions to enhance image quality and chip performance. These functions are listed as follows:

- AGC gain range control

- Gamma correction

- Brightness

- Contrast

- Full color bar test pattern

#### Serial Camera Control Bus (SCCB)

Many of the functions and configuration registers in the OV7950/OV7451 image sensors are available through the SCCB interface. The OV7950/OV7451 image sensor operates as a slave device that supports up to 400 kbps serial transfer rate using a 7-bit address/data transfer protocol.

#### **SCCB Protocol Format**

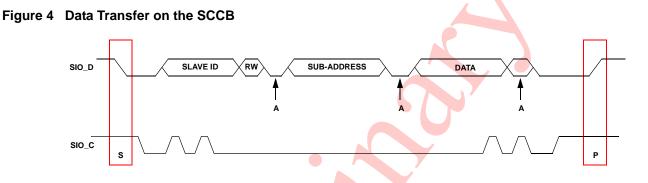

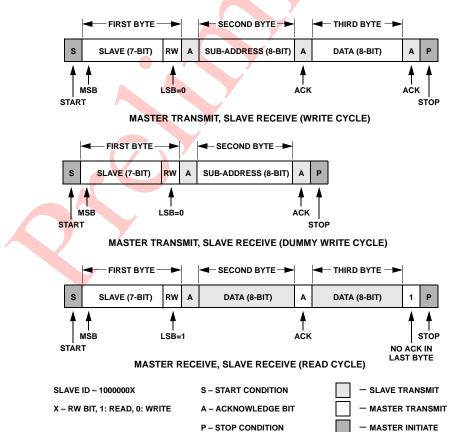

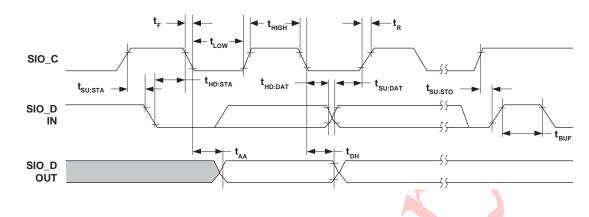

In SCCB operation (see Figure 5), the master must perform the following operations:

- Generate the Start/Stop condition

- Provide the serial clock on SIO\_C

- Place the 7-bit slave address (RW bit) and the 8-bit sub-address on SIO\_D

The receiver must pull down SIO\_D during the acknowledgement bit time. During the write cycle, the OV7950/OV7451 device returns the acknowledgement and, during the read cycle, the master returns the acknowledgement, indicating to the slave that the read cycle can be terminated. Note that the restart feature is not supported here.

Within each byte, the MSB is transferred first. The read/write control bit is the LSB of the first byte. Standard SCCB communications require only two pins, SIO\_C and SIO\_D. SIO\_D is configured as an open drain for bidirectional purposes. A HIGH to LOW transition on the SIO\_D while SIO\_C is HIGH indicates a START condition. A LOW to HIGH transition on the SIO\_D while SIO\_C is HIGH indicates a STOP condition. Only a master can generate START/STOP conditions.

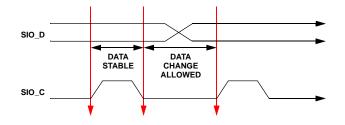

Except for these two special conditions, the protocol that SIO\_D remain stable during the HIGH period of the clock, SIO\_C. Each bit is allowed to change state only when SIO\_C is LOW (see Figure 3 and Figure 4).

The OV7950/OV7451 SCCB interface supports multi-byte write and multi-byte read. The master must supply the sub-address in the write cycle, but not in the read cycle. Therefore, the OV7950/OV7451 takes the read sub-address from the previous write cycle. In multi-byte write or multi-byte read cycles, the sub-address automatically increments after the first data byte so that continuous locations can be accessed in one bus cycle. A multi-byte cycle overwrites its original sub-address; therefore, if a read cycle immediately follows a multi-byte cycle, a single byte write cycle that provides a new address must be inserted.

The OV7950/OV7451 supports a single slave ID. The ID is preset to 60 for write and 61 for read.

In the write cycle, the second byte in the SCCB is the sub-address for selecting the individual on-chip registers, and the third byte is the data associated with this register. Writing to the unimplemented sub-address is ignored.

In the read cycle, the second byte is the data associated with the previously stored sub-address. Reading of an unimplemented sub-address returns unknown.

#### Figure 3 Bit Transfer on the SCCB

#### www.DataSheet4U.com SCCB Master

Connect external SCCB slave-compatible storage device through the OV7950/OV7451 SCCB master interface so the OV7950/OV7451 can self load the configuration data from it. Data stored in the external storage device should be arranged as follows:

| Address | Value                                            |

|---------|--------------------------------------------------|

| 0x00    | Sub_add1 - first configuration register address  |

| 0x01    | Add1_value - first configuration register value  |

| 0x02    | Sub_add2 - second configuration register address |

| 0x03    | Add2_value - second configuration register value |

|         |                                                  |

When the sub\_add = [FF] and add\_value = [FF], the SCCB master will stop operation.

#### Figure 5 SCCB Protocol Format

The OV7950/OV7451 CAMERACHIP has an overlay capability where the user can store an overlay bit map image in an external storage device with an SPI interface.

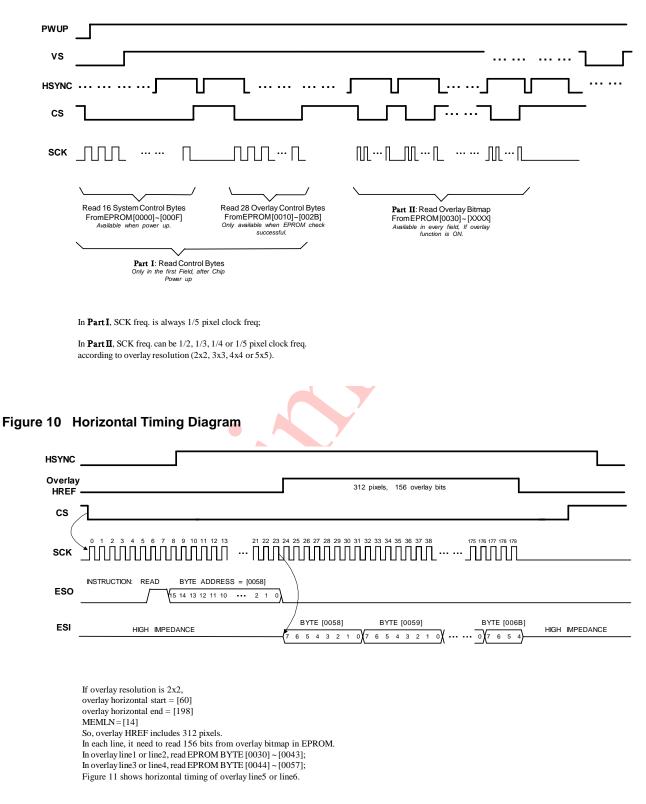

At power up, OV7950/OV7451 will start the SPI interface when the OVLEn pin (pin 8) is set high. [Bit7, Bit0]  $\neq$  "10" in the first address indicates that there is no SPI slave device attached, causing the SPI interface to stop. Otherwise, the OV7950/OV7451 will check bit 6 of first byte for overwrite control. The user can define up to 15 bytes in the control register to overwrite the internal default value (further details defining this register is not available at this time). These 15 bytes only read one time after power up.

If the first byte bit[7] is "1" and bit[0] is "0", OV7950/OV7451 will read the content in address 0x10 to 0x2B for the overlay setting.

#### Figure 6 SPI Overlay Process Sequence

Data formats are defined as follows:

| Address            |                                   | Description                                               |

|--------------------|-----------------------------------|-----------------------------------------------------------|

| 0x10               | Bit[7]:<br>Bit[6]:                | ON/OFF high bit<br>ON/OFF low bit                         |

| 0x11               | Bit[7:6]:<br>Bit[5:4]:<br>Bit[3]: | Opacity1[1:0]<br>Resolution1[1:0]<br>YUV1 all replaced    |

| 0x12               | Bit[7:0]:                         | Y1                                                        |

| 0x13               | Bit[7:0]:                         | U1                                                        |

| 0x14               | Bit[7:0]:                         | V1                                                        |

| 0x15               | Bit[7:0]:                         | V1 start[9:2]                                             |

| 0x16               | Bit[7:0]:                         | V1 end[9:2]                                               |

| 0x17               | Bit[7:0]:                         | H1 start[9:2]                                             |

| 0x18               | Bit[7:0]:                         | H1 end[9:2]                                               |

| 0x19               | Bit[7:0]:                         | V1 start[1:0], V1 end[1:0],<br>H1 start[1:0], H1 end[1:0] |

| 0x1A               | Bit[7:0]:                         | MemLine1[7:0] (unit byte)                                 |

| 0x20               | Bit[7:0]:                         | Overlay set 2 start address low 8-bit                     |

| 0x21               | Bit[7:0]:                         | Overlay set 2 start address<br>high 8-bit                 |

| 0x22               | Bit[7:6]:<br>Bit[5:4]:<br>Bit[3]: | Opacity2[1:0]<br>Resolution2[1:0]<br>YUV2 all replaced    |

| 0x23               | Bit[7:0]:                         | Y2                                                        |

| 0x24               | Bit[7:0]:                         | U2                                                        |

| 0x25               | Bit[7:0]:                         | V2                                                        |

| 0x26               | Bit[7:0]:                         | V2 start[9:2]                                             |

| 0x27               | Bit[7:0]:                         | V2 end[9:2]                                               |

| 0x28               | Bit[7:0]:                         | H2 start[9:2]                                             |

| 0x29               | Bit[7:0]:                         | H2 end[9:2]                                               |

| 0x2A               | Bit[7:0]:                         | V2 start[1:0], V2 end[1:0],<br>H2 start[1:0], H2 end[1:0] |

| 0x2B               | Bit[7:0]:                         | MemLine2[7:0] (unit byte)                                 |

| 0x30 ~ 0xXX        | Bit map 1                         |                                                           |

| Set2 start address | Dit mon 2                         |                                                           |

Set2 start address ~ 0xXX Bit map 2

#### Byte[10]

Overlay function can only be enabled when bit[7] = 1 and bit[6] = 0.

There may be two sets of overlay bitmaps in one EPROM. Byte [11] ~ Byte [1A] are control bytes for first bitmap.

#### www.DataSheet4U.com **Byte [11]**

| Resolution = | 00  | 01  | 10  | 11  |

|--------------|-----|-----|-----|-----|

|              | 2x2 | 3x3 | 4x4 | 5x5 |

When choosing 3x3 or 5x5, be aware that because YUV sampling format is 4:2:2, there may be strong color aliasing around the overlay edges.

| Opacity = | 00  | 01  | 10  | 11   |

|-----------|-----|-----|-----|------|

|           | 25% | 50% | 75% | 100% |

YUV all replaced:

Enable:

Y overlay = Y target x q% + Y original x (1-q%)

U overlay = U target x q% + U original x (1-q%)

V overlay = V target x q% + V original x (1-q%)

Disable:

```

Y overlay = Y target x q\% + Y original x (1-q\%)

```

U overlay = U target

V overlay = V target

The q% is opacity.

#### Byte [12]~[14]

Y, U, V specifies overlay color. In BW mode, only Y needed to be set.

#### Byte [15]~[19]

The user is allowed to specify vertical and horizontal dimensions of their overlay bitmap. If the desired figure is very small compared to the dimensions of the whole screen, they may save a lot of memory.

#### Byte [1A]

Every time when a new line is started, it is necessary to go to a new address for memory reading. For example, if the user specifies 500 points per line, which is not an exact multiple of 8, they need at least 63 bytes ( $63 \times 8 = 504$ ) to save the information. So, they can only specify MemLine[7:0] to be a number equal or larger than [3F].

For example, If MemLine = [40]

Line 1 start address = [30],

reading sequence:

.....

.....

Byte[20]bit7, bit6,...bit0, Byte[21]bit7, bit6...bit0, Byte[22]bit8, bit7.....

Byte[5E]bit8, bit7, bit6, bit5, bit4.

Line 2 start address = [70],

Reading sequence:

Byte[60]bit7, bit6,...bit0, Byte[61]bit7, bit6...bit0, Byte[62]bit8, bit7.....

Byte[9E]bit8, bit7, bit6, bit5, bit4. END

So, in each line, there are 500 bits was read.

#### Byte [20], Byte [21]

These two bytes indicate the 16-bit start address of the second bitmap.

#### Byte [22] ~ Byte [2B]

These are control bytes for second bitmap (refer to description for Byte [11] ~ Byte [1A]).

## www.D.Rin.Description

#### Table 1Pin Description

| Pin<br>Location | Name  | Pin<br>Type | Default<br>(V) | Function/Description                                                               |  |

|-----------------|-------|-------------|----------------|------------------------------------------------------------------------------------|--|

| 01              | SVDD  | Power       | 3.3            | Sensor array power supply                                                          |  |

| 02              | VREFH | Analog      | _              | Internal reference                                                                 |  |

| 03              | VREFS | Analog      | _              | Internal reference                                                                 |  |

| 04              | DEVDD | Power       | 0              | Sensor array decoder power supply                                                  |  |

| 05              | NVREF | Power       | 0              | Internal reference                                                                 |  |

| 06              | VRLOW | Analog      | -              | Internal reference                                                                 |  |

| 07              | PWDN  | Input       | 0              | Power Down Mode ON/OFF Selection<br>0: OFF<br>1: ON                                |  |

| 08              | OVLEn | Input       | 0              | Overlay ON/OFF selection<br>0: OFF<br>1: ON                                        |  |

| 09              | OVL2  | Input       | 0              | Overlay bitmap file selection<br>0: Select first bitmap<br>1: Select second bitmap |  |

| 10              | RESET | Input       | 0              | Hard reset ON/OFF selection<br>0: OFF<br>1: ON                                     |  |

| 11              | FSIN  | Input       | 0              | Frame synchronizing signal input                                                   |  |

| 12              | ESI   | Input       | 0              | SPI interface data input                                                           |  |

| 13              | CS    | Output      | -              | SPI interface chip select signal                                                   |  |

| 14              | ESO   | I/O         | 0              | SPI interface data output                                                          |  |

| 15              | SCK   | I/O         | 0              | SPI interface clock output                                                         |  |

| 16              | ADVDD | Power       | 3.3            | ADC power supply                                                                   |  |

| 17              | ADGND | Power       | 0              | ADC ground                                                                         |  |

| 18              | VS    | Output      | 0              | Frame synchronizing signal output                                                  |  |

| 19              | HSYNC | Output      | 0              | Horizontal valid pixel reference signal output                                     |  |

| 20              | XCLK1 | Input       | -              | Crystal input                                                                      |  |

| 21              | XCLK2 | Output      | _              | Crystal output                                                                     |  |

| 22              | DVDD  | Power       | 1.8            | Digital core power supply                                                          |  |

| 23              | DOGND | Power       | 0              | Digital I/O interface ground                                                       |  |

| 24              | CVO   | Analog      | _              | Composite video signal output                                                      |  |

| 25              | OVDD  | Power       | 3.3            | DAC power supply                                                                   |  |

Proprietary to OmniVision Technologies

7

## www.Daablee14U.conPin Description

| Pin<br>Location | Name   | Pin<br>Type | Default<br>(V) | Function/Description                                                                |

|-----------------|--------|-------------|----------------|-------------------------------------------------------------------------------------|

| 26              | NC     | -           | -              | No connection                                                                       |

| 27              | NC     | -           | _              | No connection                                                                       |

| 28              | NC     | -           | _              | No connection                                                                       |

| 29              | NC     | -           | _              | No connection                                                                       |

| 30              | OGND   | Analog      | -              | DAC ground                                                                          |

| 31              | RES    | Analog      | -              | Internal reference adjustment pin (connect to ground using a 200 $\Omega$ resistor) |

| 32              | DOVDD  | Power       | 3.3            | Digital I/O interface power supply                                                  |

| 33              | PCLK   | Output      | -              | Pixel clock output                                                                  |

| 34              | NC     | -           | -              | No connection                                                                       |

| 35              | NC     | -           | -              | No connection                                                                       |

| 36              | NC     | -           | -              | No connection                                                                       |

| 37              | NC     | -           | -              | No connection                                                                       |

| 38              | NC     | -           | -              | No connection                                                                       |

| 39              | NC     | -           | -              | No connection                                                                       |

| 40              | NC     | -           | -              | No connection                                                                       |

| 41              | NC     | -           | -              | No connection                                                                       |

| 42              | NC     | -           | -              | No connection                                                                       |

| 43              | MASTEN | Input       | -              | Master interface enable                                                             |

| 44              | MSDA   | I/O         |                | Serial master interface data I/O                                                    |

| 45              | MSCL   | 0           |                | Serial master interface clock output                                                |

| 46              | SIO_D  | I/O         | ( < )          | Serial slave interface data I/O                                                     |

| 47              | SIO_C  | Input       |                | Serial slave interface clock input                                                  |

| 48              | SGND   | Power       | 0              | Sensor array ground                                                                 |

|                 |        | 2           | 7              |                                                                                     |

|                 |        |             |                |                                                                                     |

#### www.DElectrical Characteristics

#### Table 2 Operating Conditions

| Parameter                        | Min   | Мах    |

|----------------------------------|-------|--------|

| Operating temperature            | -40°C | +85°C  |

| Storage temperature <sup>a</sup> | -40°C | +125°C |

a. Exceeding the stresses listed may permanently damage the device. This is a stress rating only and functional operation of the sensor at these and any other condition above those indicated in this specification is not implied. Exposure to absolute maximum rating conditions for any extended period may affect reliability.

## Table 3DC Characteristics (-20°C < $T_A$ < 85°C, Voltages Referenced to GND)</th>

| Symbol          | Parameter                                          | Min         | Тур | Max                      | Unit |

|-----------------|----------------------------------------------------|-------------|-----|--------------------------|------|

| Supply          |                                                    |             |     |                          |      |

| VDD1            | Supply voltage (SVDD, DOVDD, EVDD)                 | 3.15        | 3.3 | 3.45                     | V    |

| VDD2            | Supply voltage (DVDD)                              | 1.70        | 1.8 | 1.90                     | V    |

| IDD             | Supply current                                     |             | 60  | _                        | mA   |

| Digital Inpu    | uts                                                |             |     |                          |      |

| V <sub>IL</sub> | Input voltage LOW                                  |             |     | 0.2 x DOVDD              | V    |

| V <sub>IH</sub> | Input voltage HIGH                                 | 0.8 x DOVDD |     |                          | V    |

| C <sub>IN</sub> | Input capacitor                                    |             |     | 10                       | pF   |

| Digital Out     | puts (standard loading 25 pF, 1.2 K $\Omega$ to 3V |             |     |                          |      |

| V <sub>OH</sub> | Output voltage HIGH                                | 2           |     |                          | V    |

| V <sub>OL</sub> | Output voltage LOW                                 |             |     | 0.6                      | V    |

| Serial Inpu     | it                                                 |             |     |                          |      |

| V <sub>IL</sub> | SIO_C and SIO_D                                    | -0.5        | 0   | 1                        | V    |

| V <sub>IH</sub> | SIO_C and SIO_D                                    | 2.5         | 3.3 | V <sub>DOVDD</sub> + 0.5 | V    |

K Y

#### Unit Symbol Parameter Min Тур Max **Clock Input / Crystal Oscillator** fosc Resonator frequency (NTSC) \_ 12.27 \_ MHz 33 pF Load capacitor Parallel resistance 1 MΩ Rise/fall time for external clock input \_ 5 \_ ns Duty cycle for external clock input 40 50 60 % **CVO Analog Video Output Parameters** Video peak signal level 0.969 1.020 1.071 V V<sub>TO P</sub> V<sub>TO\_B</sub> Video black signal level 0.339 0.357 0.375 V Video sync pulse amplitude 0.291 0.306 V 0.321 V<sub>VSYNC</sub> V V<sub>SYNCLEVEL</sub> Sync level 0.017 0.022 0.027 \_ Video output drive current 30 mΑ IVTO I/O Pin Output pin source current (Output = 1.5V) 8 10 12 mΑ ISOURCE 8 12 Output pin sink current (Output = 3V) 10 mΑ ISINK **Miscellaneous Timing** External FSIN cycle time \_ 2 \_ field t<sub>SYNC</sub> Chip power-up time 100 \_ μS t<sub>PU</sub> \_

#### www.Datable 44U.conAC Characteristics (T<sub>A</sub> = 25°C, VDD = 5V)

## www.Datiming\_Specifications

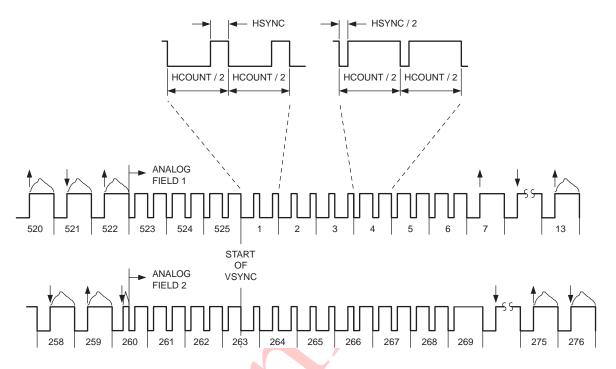

#### **NTSC Timing**

Version 2.5, February 28, 2006

#### www.DQverlay.Timing

### www.DInterface.Timing

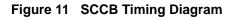

#### Table 5 SCCB Timing Specifications

| Symbol                         | Parameter                      | Min | Тур | Мах | Unit |

|--------------------------------|--------------------------------|-----|-----|-----|------|

| f <sub>SIO_C</sub>             | Clock Frequency                |     |     | 400 | KHz  |

| t <sub>LOW</sub>               | Clock Low Period               | 1.3 |     |     | μs   |

| t <sub>HIGH</sub>              | Clock High Period              | 600 |     |     | ns   |

| t <sub>AA</sub>                | SIO_C low to Data Out valid    | 100 |     | 900 | ns   |

| t <sub>BUF</sub>               | Bus free time before new START | 1.3 |     |     | μs   |

| t <sub>HD:STA</sub>            | START condition Hold time      | 600 |     |     | ns   |

| t <sub>SU:STA</sub>            | START condition Setup time     | 600 |     |     | ns   |

| t <sub>HD:DAT</sub>            | Data-in Hold time              | 0   |     |     | μs   |

| t <sub>SU:DAT</sub>            | Data-in Setup time             | 100 |     |     | ns   |

| t <sub>SU:STO</sub>            | STOP condition Setup time      | 600 |     |     | ns   |

| t <sub>R,</sub> t <sub>F</sub> | SCCB Rise/Fall times           |     |     | 300 | ns   |

| t <sub>DH</sub>                | Data-out Hold time             | 50  |     |     | ns   |

|                                | 7                              |     |     |     |      |

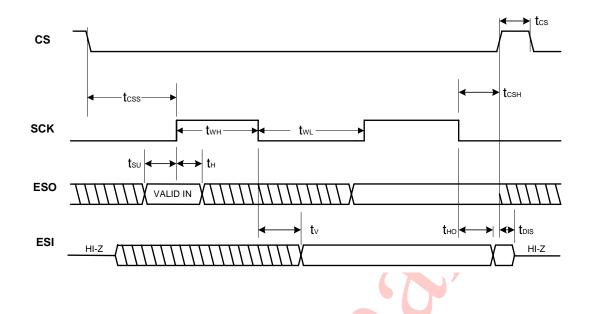

## www.DEiguret12.coSPI Timing Diagram

| Table 6 | SPI Timing Specifications |

|---------|---------------------------|

|---------|---------------------------|

| Table 6          | SPI Timing Specifications |     |     |     |      |

|------------------|---------------------------|-----|-----|-----|------|

| Symbol           | Parameter                 | Min | Тур | Мах | Unit |

| t <sub>WH</sub>  | SCK High Time             | 133 |     |     | ns   |

| t <sub>WL</sub>  | SCK Low Time              | 133 |     |     | ns   |

| t <sub>CS</sub>  | CS High Time              | 250 |     |     | ns   |

| t <sub>CSS</sub> | CS Setup Time             | 250 |     |     | ns   |

| t <sub>CSH</sub> | CS Hold Time              | 250 |     |     | ns   |

| t <sub>SU</sub>  | Data In Setup Time        | 50  |     |     | ns   |

| t <sub>H</sub>   | Data In Hold Time         | 50  |     |     | ns   |

| t <sub>V</sub>   | Output Valid              |     |     | 133 | ns   |

| t <sub>HO</sub>  | Output Hold Time          | 0   |     |     | ns   |

| t <sub>DIS</sub> | Output Disable Time       |     |     | 250 | ns   |

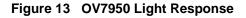

### www.DQV7950 Light Response

#### www.DRegister.Set

Table 7 provides a list and description of the Device Control registers contained in the OV7950/OV7451. The device slave addresses are 60 for write and 61 for read.

| Table 7 | Device Control Register List |

|---------|------------------------------|

|---------|------------------------------|

| Address<br>(Hex) | Register<br>Name | Default<br>(Hex) | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|------------------|------------------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 00               | GAIN             | 00               | RW  | AGC Gain Control<br>Bit[7:0]: Gain setting<br>• Range: 1x - 32x<br>Gain = (Bit[7]+1) x (Bit[6]+1) x (Bit[5]+1) x (Bit[4]+1) x (1+Bit[3:0]/16)<br><b>Note:</b> This register is updated automatically when AGC is enabled. The<br>user can adjust the value through the serial interface if AGC is<br>disabled.                                                                                                     |  |

| 01               | BLUE             | 80               | RW  | Blue Gain Control                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 02               | RED              | 80               | RW  | Red Gain Control                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 03               | GREEN            | 80               | RW  | Green Gain Control                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 04               | AECL             | 88               | RW  | AEC/AGC Control<br>Bit[7:3]: Reserved<br>Bit[2:1]: AGC Gain Control - high 2 bits<br>Bit[0]: Exposure control LSB                                                                                                                                                                                                                                                                                                  |  |

| 05               | BAVG             | 00               | RW  | B Channel Average                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 06               | GAVG             | 00               | RW  | G Channel Average                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 07               | RAVG             | 00               | RW  | R Channel Average                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 08               | COM1             | 10               | RW  | Common Control 1<br>Bit[7]: Mirror function<br>0: Normal image<br>1: Mirror image<br>Bit[6]: Vertical flip function<br>0: Normal image<br>1: Vertically flip image<br>Bit[5]: Reserved<br>Bit[5]: Reserved<br>Bit[4]: VS pin output selection<br>0: Output signal depends on COM7[1] (0x15)<br>1: Output Odd field indicator<br>Bit[3]: Gamma function ON/OFF<br>0: Gamma OFF<br>1: Gamma ON<br>Bit[2:0]: Reserved |  |

| 09               | RSVD             | XX               | _   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 0A               | PIDH             | 79               | R   | Product ID Number MSB (Read only)                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 0B               | PIDL             | 50               | R   | Product ID Number LSB (Read only)                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 0C-0F            | RSVD             | XX               | _   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Address<br>(Hex) | Register<br>Name | Default<br>(Hex) | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|------------------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10               | AEC              | 82               | RW  | Automatic Exposure Control - AEC[8:1] (LSB in AECL[0] (0x04) and MSB in AECH[6:0] (0x39))                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11               | RSVD             | XX               | -   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 12               | COM4             | 50               | RW  | Common Control 4<br>Bit[7]: SRST<br>0: No change<br>1: Initiates system reset and resets all registers to factory<br>default values after which the device resumes normal<br>operation<br>Bit[6:0]: Reserved                                                                                                                                                                                                                                                                                                                                               |

| 13               | COM5             | 8F               | RW  | AEC, AGC, and AWB Auto/Manual Control<br>Bit[7]: AEC speed selection<br>0: Normal<br>1: Faster AEC correction<br>Bit[6]: Reserved<br>Bit[5]: Banding filter ON/OFF selection<br>0: OFF<br>1: ON<br>Bit[4]: Reserved<br>Bit[3]: Small exposure ON/OFF selection<br>0: OFF (minimum exposure is 1 Tv line period (65 μs))<br>1: ON (minimum exposure is 20 μs)<br>Bit[2]: AGC auto/manual control selection<br>0: Manual<br>1: Auto<br>Bit[1]: AWB auto/manual control selection<br>0: Manual<br>1: Auto<br>Bit[0]: Exposure control<br>0: Manual<br>1: Auto |

| Address<br>(Hex) | Register<br>Name | Default<br>(Hex) | R/W | Description                                                                                                                                                                                                                                                                                                         |

|------------------|------------------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14               | COM6             | 80               | RW  | Common Control 6<br>Bit[7:5]: AGC max gain ceiling<br>000: 2x<br>001: 4x<br>010: 8x<br>011: 16x<br>100: 32x<br>101-111: Not allowed<br>Bit[4]: Reserved<br>Bit[3:2]: Digital gain ceiling<br>00: 1x<br>01: 2x<br>10: 4x<br>11: Not allowed<br>Bit[1]: Reserved<br>Bit[0]: Exposure freeze ON/OFF<br>0: OFF<br>1: ON |

| 15               | COM7             | 00               | RW  | Common Control 7<br>Bit[7:2]: Reserved<br>Bit[1]: VSYNC output selection<br>0: Field VSYNC<br>1: Frame VSYNC<br>Bit[0]: Reserved                                                                                                                                                                                    |

| 16               | COM8             | 40               | RW  | Common Control 8<br>Bit[7]: AEC/AGC algorithm selection<br>0: Average-based AEC/AGC control<br>1: Histogram-based AEC/AGC control<br>Bit[6]: Auto/Manual digital gain select<br>0: Auto digital gain<br>1: Manual digital gain<br>Bit[5:4]: Manual set digital gain [1:0]<br>Bit[3:0]: Reserved                     |

| 17-1A            | RSVD             | ХХ               | -   | Reserved                                                                                                                                                                                                                                                                                                            |

| 1B               | PSHFT            | 6A               | RW  | Left Pixel Shift - 1 bit equals 2 pixel shift                                                                                                                                                                                                                                                                       |

| 1C               | MIDH             | 7F               | R   | Manufacturer ID Byte – High (Read only = 0x7F)                                                                                                                                                                                                                                                                      |

| 1D               | MIDL             | A2               | R   | Manufacturer ID Byte – Low (Read only = 0xA2)                                                                                                                                                                                                                                                                       |

| 1E-20            | RSVD             | XX               | _   | Reserved                                                                                                                                                                                                                                                                                                            |

| Address<br>(Hex) | Register<br>Name | Default<br>(Hex) | R/W | Description                                                                                                                                                                                                                                                                      |  |

|------------------|------------------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 21               | COM9             | 00               | RW  | Common Control 9<br>Bit[7]: Reserved<br>Bit[6]: VSYNC output pattern control<br>0: VSYNC can start at line start or half line<br>1: VSYNC can only start at line start<br>Bit[5]: VSYNC output only in field one<br>Bit[4]: VSYNC output only in field two<br>Bit[3:0]: Reserved |  |

| 22-23            | RSVD             | XX               | -   | Reserved                                                                                                                                                                                                                                                                         |  |

| 24               | AECW             | 78               | RW  | Luminance Signal High Range for AEC/AGC operation                                                                                                                                                                                                                                |  |

| 25               | AECB             | 68               | RW  | Luminance Signal Low Range for AEC/AGC operation                                                                                                                                                                                                                                 |  |

| 26               | VWB              | D4               | RW  | Fast Mode Large Step Luminance Range Threshold                                                                                                                                                                                                                                   |  |

| 27-2E            | RSVD             | XX               | -   | Reserved                                                                                                                                                                                                                                                                         |  |

| 2F               | YAVG             | 00               | RW  | Luminance Average Value                                                                                                                                                                                                                                                          |  |

| 30-32            | RSVD             | XX               | _   | Reserved                                                                                                                                                                                                                                                                         |  |

| 33               | VSFT             | 00               | RW  | Vertical Window Shift                                                                                                                                                                                                                                                            |  |

| 34-38            | RSVD             | XX               | _   | Reserved                                                                                                                                                                                                                                                                         |  |

| 39               | AECH             | 82               | RW  | Automatic Exposure Control MSBs<br>Bit[7]: Reserved<br>Bit[6:0]: Automatic exposure control MSBs                                                                                                                                                                                 |  |

| 3A-65            | RSVD             | XX               | -   | Reserved                                                                                                                                                                                                                                                                         |  |

| 66               | MNTR             | 00               | RW  | Monitor<br>Bit[7:4]: Register monitor control (refer to descriptions of registers<br>COM22 (0xED), COM23 (0xEE), COM24 (0xEF) and<br>COM25 (0xF0)<br>Bit[3:0]: Reserved                                                                                                          |  |

| 67-7A            | RSVD             | XX               | -   | Reserved                                                                                                                                                                                                                                                                         |  |

| 7B               | SLOP             | 24               | RW  | Gamma Curve Highest Segment Slop<br>Should be calculated as follows:<br>SLOP[7:0] = (FF - GAM15[7:0] + 1) x 40/30<br><i>Note: Use hex numbers for calculation</i>                                                                                                                |  |

| 7C               | GAM1             | 0F               | RW  | Gamma Curve - 1st segment input end point 0x010 output value                                                                                                                                                                                                                     |  |

| 7D               | GAM2             | 1F               | RW  | Gamma Curve - 2nd segment input end point 0x020 output value                                                                                                                                                                                                                     |  |

| 7E               | GAM3             | 36               | RW  | Gamma Curve - 3rd segment input end point 0x040 output value                                                                                                                                                                                                                     |  |

| 7F               | GAM4             | 54               | RW  | Gamma Curve - 4th segment input end point 0x080 output value                                                                                                                                                                                                                     |  |

| 80               | GAM5             | 5F               | RW  | Gamma Curve - 5th segment input end point 0x0A0 output value                                                                                                                                                                                                                     |  |

| 81               | GAM6             | 6A               | RW  | Gamma Curve - 6th segment input end point 0x0C0 output value                                                                                                                                                                                                                     |  |

| Address<br>(Hex) | Register<br>Name | Default<br>(Hex) | R/W | Description                                                                                                                                                                                                                                                                                                                             |  |

|------------------|------------------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 82               | GAM7             | 74               | RW  | Gamma Curve - 7th segment input end point 0x0E0 output value                                                                                                                                                                                                                                                                            |  |

| 83               | GAM8             | 7C               | RW  | Gamma Curve - 8th segment input end point 0x100 output value                                                                                                                                                                                                                                                                            |  |

| 84               | GAM9             | 84               | RW  | Gamma Curve - 9th segment input end point 0x120 output value                                                                                                                                                                                                                                                                            |  |

| 85               | GAM10            | 8C               | RW  | Gamma Curve - 10th segment input end point 0x140 output value                                                                                                                                                                                                                                                                           |  |

| 86               | GAM11            | 9A               | RW  | Gamma Curve - 11th segment input end point 0x180 output value                                                                                                                                                                                                                                                                           |  |

| 87               | GAM12            | A7               | RW  | Gamma Curve - 12th segment input end point 0x1C0 output value                                                                                                                                                                                                                                                                           |  |

| 88               | GAM13            | BF               | RW  | Gamma Curve - 13th segment input end point 0x240 output value                                                                                                                                                                                                                                                                           |  |

| 89               | GAM14            | D3               | RW  | Gamma Curve - 14th segment input end point 0x2C0 output value                                                                                                                                                                                                                                                                           |  |

| 8A               | GAM15            | E5               | RW  | Gamma Curve - 15th segment input end point 0x340 output value                                                                                                                                                                                                                                                                           |  |

| 8B-9A            | RSVD             | XX               | _   | Reserved                                                                                                                                                                                                                                                                                                                                |  |

| 9B               | MTX1             | 40               | RW  | Color Matrix Parameter M1                                                                                                                                                                                                                                                                                                               |  |

| 9C               | MTX2             | 34               | RW  | Color Matrix Parameter M2                                                                                                                                                                                                                                                                                                               |  |

| 9D               | MTX3             | 0C               | RW  | Color Matrix Parameter M3                                                                                                                                                                                                                                                                                                               |  |

| 9E               | MTX4             | 17               | RW  | Color Matrix Parameter M4                                                                                                                                                                                                                                                                                                               |  |

| 9F               | MTX5             | 29               | RW  | Color Matrix Parameter M5                                                                                                                                                                                                                                                                                                               |  |

| A0               | MTX6             | 40               | RW  | Color Matrix Parameter M6                                                                                                                                                                                                                                                                                                               |  |

| A1               | MTX7             | 1E               | RW  | Color Matrix Control         Bit[7]:       Double matrix - double M1 to M6         Bit[6]:       Reserved         Bit[5]:       Sign bit of M6         Bit[4]:       Sign bit of M5         Bit[3]:       Sign bit of M4         Bit[2]:       Sign bit of M3         Bit[1]:       Sign bit of M2         Bit[0]:       Sign bit of M1 |  |

| A2               | BRT              | 00               | RW  | Brightness Control <ul> <li>Range [00] to [FF}</li> </ul>                                                                                                                                                                                                                                                                               |  |

| A3               | CNTR             | 40               | RW  | Contrast Control                                                                                                                                                                                                                                                                                                                        |  |

| A4-BE            | RSVD             | Xx               | _   | Reserved                                                                                                                                                                                                                                                                                                                                |  |

| BF               | BPTH1            | 90               | RW  | Black Pixel Threshold Level 1                                                                                                                                                                                                                                                                                                           |  |

| C0               | BPTH2            | 40               | RW  | Black Pixel Threshold Level 2                                                                                                                                                                                                                                                                                                           |  |

| C1               | WPTH1            | A0               | RW  | White Pixel Threshold Level 1                                                                                                                                                                                                                                                                                                           |  |

| C2               | WPTH2            | D0               | RW  | White Pixel Threshold Level 2                                                                                                                                                                                                                                                                                                           |  |

| C3               | BPCNT1           | СС               | RW  | Black Pixel Count Number 1                                                                                                                                                                                                                                                                                                              |  |

| C4               | BPCNT2           | F0               | RW  | Black Pixel Count Number 2                                                                                                                                                                                                                                                                                                              |  |

Version 2.5, February 28, 2006

| Address<br>(Hex) | Register<br>Name | Default<br>(Hex) | R/W | Description                                                                                                                                                                                                                                                                                                                             |

|------------------|------------------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C5               | WPCNT1           | 64               | RW  | White Pixel Count Number 1                                                                                                                                                                                                                                                                                                              |

| C6               | WPCNT2           | 80               | RW  | White Pixel Count Number 2                                                                                                                                                                                                                                                                                                              |

| C7-D0            | RSVD             | XX               | _   | Reserved                                                                                                                                                                                                                                                                                                                                |

| D1               | ZONE1            | FF               | RW  | Bit[7:6]:Zone 416-Zone Y average selectBit[5:4]:Zone 3In each zone, the two bits mean:Bit[3:2]:Zone 200:Bit[1:0]:Zone 101:                                                                                                                                                                                                              |

| D2               | ZONE2            | FF               | RW  | Bit[7:6]:       Zone 8         Bit[5:4]:       Zone 7         Bit[3:2]:       Zone 6         Bit[1:0]:       Zone 5                                                                                                                                                                                                                     |

| D3               | ZONE3            | FF               | RW  | Bit[7:6]: Zone 12<br>Bit[5:4]: Zone 11<br>Bit[3:2]: Zone 10<br>Bit[1:0]: Zone 8                                                                                                                                                                                                                                                         |

| D4               | ZONE4            | FF               | RW  | Bit[7:6]:       Zone 16         Bit[5:4]:       Zone 15         Bit[3:2]:       Zone 14         Bit[1:0]:       Zone 13                                                                                                                                                                                                                 |

| D5-EA            | RSVD             | XX               | _   | Reserved                                                                                                                                                                                                                                                                                                                                |

| EB               | COM21            | 00               | RW  | Overlay Data Shift Select                                                                                                                                                                                                                                                                                                               |

| EC               | RSVD             | XX               | -   | Reserved                                                                                                                                                                                                                                                                                                                                |

| ED               | COM22            | -                | R   | Register Monitor when MNTR[7:4] are:0000:SPI input com10001:SPI input com20010:SPI input com30011:SPI input com40100:SPI input com50101:SPI input com60110:SPI input com70111:SPI input com81000:SPI input com91001:SPI input com101010:SPI input com111011:SPI input com121100:SPI input com131101:SPI input com151111:SPI input com16 |

| Address<br>(Hex) | Register<br>Name | Default<br>(Hex) | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------|------------------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EE               | COM23            | -                | R   | Register Monitor when MNTR[7:4] are:         0000:       Overlay control register         Bit[7:6]:       Overlay function OVFF select         0x:       Overlay function OFF         10:       Overlay bitmap 1 control register         Bit[7:6]:       Overlay opacity         00:       25% overlay opacity         01:       Overlay opacity         02:       25% overlay opacity         10:       75% overlay opacity         10:       75% overlay opacity         11:       100% overlay opacity         01:       2x2         01:       3x3         10:       4x4         11:       5x5         0010:       Y overlay target 1         0101:       U overlay target 1         0101:       Overlay tortical window 1 start point MSBs         0101:       Overlay horizontal window 1 start point MSBs         1001:       Overlay topacital window 1 start point LSBs <tr< td=""></tr<> |

| EF               | COM24            | -                | R   | Register Monitor when MNTR[7:4] are:         0000:       V overlay target 2         0001:       Overlay vertical window 2 start point MSBs         0010:       Overlay vertical window 2 stop point MSBs         0011:       Overlay horizontal window 2 start point MSBs         0101:       Overlay horizontal window 2 stop point MSBs         0101:       Overlay horizontal window 2 stop point MSBs         0101:       Overlay horizontal window 2 stop point MSBs         0101:       Reserved         Bit[7:6]:       Overlay vertical window 2 start point LSBs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                  |                  |                  |     | Bit[5:4]:Overlay vertical window 2 stop point LSBsBit[3:2]:Overlay horizontal window 2 start point LSBsBit[1:0]:Overlay horizontal window 2 stop point LSBs0110:Memory length 2 for one line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Address<br>(Hex) | Register<br>Name                                                                                                        | Default<br>(Hex) | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| F0               | COM25                                                                                                                   | _                | R   | Register Monitor when MNTR[7:4] are:0000:Y average zone 10001:Y average zone 20010:Y average zone 30011:Y average zone 40100:Y average zone 50101:Y average zone 60110:Y average zone 70111:Y average zone 81000:Y average zone 91001:Y average zone 101010:Y average zone 111011:Y average zone 121100:Y average zone 131101:Y average zone 141110:Y average zone 151111:Y average zone 16 |  |  |

| F1-F2            | RSVD                                                                                                                    | XX               | _   | Reserved                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| NOTE: All        | NOTE: All other registers are factory-reserved. Please contact OmniVision Technologies for reference register settings. |                  |     |                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

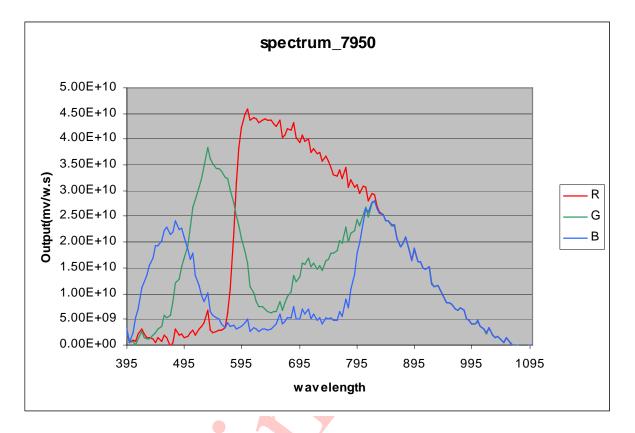

#### www.DPackage Specifications