# P16M648YA7, P32M6416YA7 P16M648YB7, P32M6416YB7

# SDRAM MODULE P16M648YL(X)7, P32M6416YL(X)7

### Features:

- PC-100 and PC133 Compatible

- JEDEC Standard 168-pin, dual in-line memory Module (DIMM)

- TSOP components.

- Single 3.3v <u>+</u>.3v power supply.

- Nonbuffered fully synchronous; all signals measured on positive edge of system clock.

- Internal pipelined operation; column address can be changed every clock cycle.

- Quad internal banks for hiding row access/precharge.

- 64ms 4096 cycle refresh.

- All inputs, outputs, clocks LVTTL compatible.

### **Options:**

8 - 16Mx8 SDRAM TSOP 16 - 16Mx8 SDRAM TSOP

### **Older Versions:**

8 - 16Mx8 SDRAM TSOP 16 - 16Mx8 SDRAM TSOP

#### Part Number:

P16M648YA7 P32M6416YA7

#### **Part Number:**

P16M648YB7 P32M6416YB7

#### **KEY DIMM MODULE TIMING PARAMETERS**

| Module  | Component | Clock     | CAS     |

|---------|-----------|-----------|---------|

| Marking | Marking   | Frequency | Latency |

| -8A     | -8A       | 100MHz    | 3       |

| -75A    | -75A      | 133MHz    | 3       |

### **GENERAL DESCRIPTION**

The P16M648YA7 and P32M6416YA7 is a high performance dynamic random-access 256MB module, organized in a x64 configuration, and utilize quad bank architecture with a synchronous interface. All signals are registered on the positive edge of the clock signals CK0 through CK3. Read and write accesses to the SDRAM are burst oriented; accesses start at a location and continue for a programmed number of locations in a sequence. Accesses begin with an ACTIVE command, which is followed by a READ or WRITE command.

### ABSOLUTE MAXIMUM RATINGS:

| Voltage on Vcc Supply relative to Vss          | 1 to +4.6V     |

|------------------------------------------------|----------------|

| Operating Temperature T <sub>A</sub> (Ambient) | 25 ° to +70 °C |

| Storage Temperature                            | 55 to +125 °   |

| Power Dissipation                              | 8 W            |

| Short Circuit Output Current                   | 50 mA          |

# 168-Pin DIMM PIN ASSIGNMENT (Front View)

| PIN | SYMBOL | PIN | SYMBOL | PIN | SYMBOL | PIN | SYMBOL |

|-----|--------|-----|--------|-----|--------|-----|--------|

| 1   | Vss    | 43  | Vss    | 85  | Vss    | 127 | Vss    |

| 2   | DQ0    | 44  | DU     | 86  | DQ32   | 128 | CKEO   |

| 3   | DQ1    | 45  | S2#    | 87  | DQ33   | 129 | S3#*   |

| 4   | DQ2    | 46  | DQMB2  | 88  | DQ34   | 130 | DQMB6  |

| 5   | DQ3    | 47  | DQMB3  | 89  | DQ35   | 131 | DQMB7  |

| 6   | Vcc    | 48  | DU     | 90  | Vcc    | 132 | RFU    |

| 7   | DQ4    | 49  | Vcc    | 91  | DQ36   | 133 | Vcc    |

| 8   | DQ5    | 50  | NC     | 92  | DQ37   | 134 | NC     |

| 9   | DQ6    | 51  | NC     | 93  | DQ38   | 135 | NC     |

| 10  | DQ7    | 52  | NC     | 94  | DQ39   | 136 | NC     |

| 11  | DQ8    | 53  | NC     | 95  | DQ40   | 137 | NC     |

| 12  | Vss    | 54  | Vss    | 96  | Vss    | 138 | Vss    |

| 13  | DQ9    | 55  | DQ16   | 97  | DQ41   | 139 | DQ48   |

| 14  | DQ10   | 56  | DQ17   | 98  | DQ42   | 140 | DQ49   |

| 15  | DQ10   | 57  | DQ17   | 99  | DQ42   | 141 | DQ43   |

| 16  | DQ12   | 58  | DQ19   | 100 | DQ44   | 142 | DQ51   |

| 17  | DQ13   | 59  | Vcc    | 101 | DQ45   | 143 | Vcc    |

| 18  | Vcc    | 60  | DQ20   | 102 | Vcc    | 144 | DQ52   |

| 19  | DQ14   | 61  | NC     | 103 | DQ46   | 145 | NC     |

| 20  | DQ15   | 62  | NC     | 104 | DQ47   | 146 | NC     |

| 21  | NC     | 63  | CKE1*  | 105 | NC     | 147 | NC     |

| 22  | NC     | 64  | Vss    | 106 | NC     | 148 | Vss    |

| 23  | Vss    | 65  | DQ21   | 107 | Vss    | 149 | DQ53   |

| 24  | NC     | 66  | DQ22   | 108 | NC     | 150 | DQ54   |

| 25  | NC     | 67  | DQ23   | 109 | NC     | 151 | DQ55   |

| 26  | Vcc    | 68  | Vss    | 110 | Vcc    | 152 | Vss    |

| 27  | WE#    | 69  | DQ24   | 111 | CAS#   | 153 | DQ56   |

| 28  | DQMB0  | 70  | DQ25   | 112 | DQMB4  | 154 | DQ57   |

| 29  | DQMB1  | 71  | DQ26   | 113 | DQMB5  | 155 | DQ58   |

| 30  | S0#    | 72  | DQ27   | 114 | S1#*   | 156 | DQ59   |

| 31  | DU     | 73  | Vcc    | 115 | RAS#   | 157 | Vcc    |

| 32  | Vss    | 74  | DQ28   | 116 | Vss    | 158 | DQ60   |

| 33  | A0     | 75  | DQ29   | 117 | A1     | 159 | DQ61   |

| 34  | A2     | 76  | DQ30   | 118 | A3     | 160 | DQ62   |

| 35  | A4     | 77  | DQ31   | 119 | A5     | 161 | DQ63   |

| 36  | A6     | 78  | Vss    | 120 | A7     | 162 | Vss    |

| 37  | A8     | 79  | CK2    | 121 | A9     | 163 | CK3    |

| 38  | A10    | 80  | NC     | 122 | BA0    | 164 | NC     |

| 39  | BA1    | 81  | WP     | 123 | A11    | 165 | SA0    |

| 40  | Vcc    | 82  | SDA    | 124 | Vcc    | 166 | SA1    |

| 41  | Vcc    | 83  | SCL    | 125 | CK1    | 167 | SA2    |

| 42  | CK0    | 84  | Vcc    | 126 | RFU    | 168 | Vcc    |

<sup>\*128</sup>Mb version only

Stresses beyond these may cause permanent damage to the device. This is a stress rating only and functional . operation of the device at or beyond these conditions is not implied. Exposure to these conditions for extended periods may affect reliability.

# P16M648YA7, P32M6416YA7 P16M648YB7,P32M6416YB7

**CAPACITANCE:** (This parameter is sampled.  $VCC = +3.3V \pm 0.3V$ ; f = 1 MHz)

| Parameter                                          | Symbol          | Max   | Max   | Units |

|----------------------------------------------------|-----------------|-------|-------|-------|

|                                                    |                 | 128MB | 256MB |       |

| Input Capacitance: A0 - A10, BAO, RAS#, CAS#, WE#, | C <sub>I1</sub> | 32    | 65    | pF    |

| Input Capacitance: CK0-CK3                         | C <sub>l2</sub> | 20    | 20    | pF    |

| Input Capacitance: S0#-S3#                         | C <sub>I3</sub> | 24    | 24    | pF    |

| Input Capacitance: CKE0, CKE1,                     | C <sub>14</sub> | 45    | 45    | pF    |

| Input Capacitance: DQMB0#, DQMB7                   | C <sub>I5</sub> | 6     | 13    | pF    |

| Input Capacitance: SQL, SA0-SA2                    | C <sub>I6</sub> | 6     | 6     | pF    |

| Input/Output Capacitance: DQ0-DQ63, SDA            | C <sub>IO</sub> | 8     | 10    | pF    |

#### DC ELECTRICAL CHARACTERISTICS AND RECOMMENDED OPERATING CONDITIONS:

| Parameter                                                 | Symbol          | Min  | Max      | Units |

|-----------------------------------------------------------|-----------------|------|----------|-------|

| Supply Voltage                                            | Vdd/Vddq        | 3.0  | 3.6      | V     |

| Input High (Logic 1) Voltage, All inputs                  | V <sub>IH</sub> | 2.2  | Vcc + .3 | V     |

| Input Low (Logic 0) Voltage, All inputs                   | V <sub>IL</sub> | -0.3 | 0.8      | V     |

| Input Leakage Current Any input = 0V ≤ VIN ≤ Vcc          | l <sub>l</sub>  | -10  | 10       | uA    |

| All other pins not under test = 0V                        | l <sub>2</sub>  | -20  | 20       |       |

|                                                           | $I_3$           | -40  | 40       |       |

|                                                           | I <sub>4</sub>  | -80  | 80       |       |

| Output Leakage Current DQs are disabled; 0V ≤ VOUT ≤ VccQ | loz             | -10  | 10       | uA    |

| Output High Voltage (I <sub>OUT</sub> = -4 mA)            | V <sub>OH</sub> | 2.4  |          | V     |

| Output Low Voltage (I <sub>OUT</sub> = 4 mA)              | V <sub>OL</sub> |      | 0.4      | V     |

#### ICC OPERATING CONDITIONS AND MAXIMUM LIMITS: Vcc = 3.3V ± 10%V, Temp. = 25° to 70 °C

| Supply Current                                     |                | Symbol | SIZE  | -75A | -8A  | Units | Notes   |

|----------------------------------------------------|----------------|--------|-------|------|------|-------|---------|

| OPERATING CURRENT: ACTIVE mode, burst = 2, READ or |                | Icc1   | 128MB | 1320 | 1120 | mA    | 1, 2, 3 |

| WRITE, tRC > tRC (MIN), one bank active,           |                |        | 256MB | 2640 | 2240 |       |         |

| CAS latency = 3                                    |                |        |       |      |      |       |         |

| STANDBY CURRENT: POWER-DOWN                        |                | Icc2   | 128MB | 72   | 72   | mA    |         |

| mode, CKE = LOW, no accesses in progress           |                |        | 256MB | 144  | 144  |       |         |

|                                                    |                |        |       |      |      |       |         |

| STANDBY CURRENT: CS# = HIGH, CKE = HIGH            | Ⅎ,             | Icc3   | 128MB | 600  | 480  | mA    | 3, 4    |

| tCK = 15ns, both banks idle                        |                |        | 256MB | 1200 | 960  |       |         |

| STANDBY CURRENT: CS# = HIGH, CKE = HIGH            | H, tCK = 15ns, | Icc4   | 128MB | 600  | 400  | mA    | 3, 4    |

| both banks active after tRCD met, no accesses in   | progress.      |        | 256MB | 1200 | 800  |       |         |

| OPERATING CURRENT: BURST mode after                | CL=3           | Icc5   | 128MB | 1320 | 1160 | mA    | 1, 2, 3 |

| tRCD met, continuous burst, READ, WRITE,           |                |        | 256MB | 2640 | 2320 |       |         |

| $tCK \ge tCK$ MIN, other bank active.              |                |        |       |      |      |       |         |

| AUTO REFRESH CURRENT tRC ≥ tRC (MIN)               |                | Icc6   | 128MB | 2120 | 1960 | mA    | 1, 2, 3 |

|                                                    |                |        | 256MB | 4240 | 3920 |       |         |

#### **NOTES:**

- 1. Icc is dependent on output loading and cycle rates. Specified values are obtained with minimum cycle time and the outputs open.

- 2. The lcc current will decrease as the CAS latency is reduced. This is because maximum cycle rate is slower as CAS latency is reduced.

- 3. Address transitions average one transition every 30ns.

- 4. Other input signals are allowed to transition no more than once in any 30ns period.

2 SpecTek reserves the right to change products or specifications without notice. ©2002 SpecTek

# P16M648YA7, P32M6416YA7 P16M648YB7,P32M6416YB7

AC ELECTRICAL CHARACTERISTICS: Vcc = 3.3V ± 10%V, Temp. = 25° to 70°C (CL = CAS Latency)

| AC CHARACTERISTICS                          |      | -75A | -75A | -8A | -8A |       |       |

|---------------------------------------------|------|------|------|-----|-----|-------|-------|

| PARAMETER                                   | SYM  | MIN  | MAX  | MIN | MAX | UNITS | NOTES |

| Access time from CLK (positive edge) CL = 3 | tAC  |      | 5.4  |     | 6   | ns    |       |

| Address hold time                           | tAH  | .8   |      | 1   |     | ns    |       |

| Address setup time                          | tAS  | 1.5  |      | 2   |     | ns    |       |

| CLK high level width                        | tCH  | 2.5  |      | 3   |     | ns    |       |

| CLK low level width                         | tCL  | 2.5  |      | 3   |     | ns    |       |

| Clock cycle time CL = 3                     | tCK  | 7.5  |      | 10  |     | ns    |       |

| CKE hold time                               | tCKH | .8   |      | 1   |     | ns    |       |

| CKE setup time                              | tCKS | 1.5  |      | 2   |     | ns    |       |

| CS#, RAS#, CAS#, WE#, DQM hold time         | tCMH | .8   |      | 1   |     | ns    |       |

| CS#, RAS#, CAS#, WE#, DQM setup time        | tCMS | 1.5  |      | 2   |     | ns    |       |

| Data-in hold time                           | tDH  | .8   |      | 1   |     | ns    |       |

| Data-in setup time                          | tDS  | 1.5  |      | 2   |     | ns    |       |

| Data-out high impedance time                | tHZ  |      | 9    |     | 9   | ns    | 1     |

| Data-out low impedance time                 | tLZ  | 1    |      | 2   |     | ns    |       |

| Data-out hold time                          | tOH  | 2.7  |      | 3   |     | ns    |       |

| ACTIVE to PRECHARGE command period          | tRAS | 44   | 16K  | 50  | 16K | ns    |       |

| AUTO REFRESH and ACTIVE to ACTIVE           | tRC  | 60   |      | 80  |     | ns    |       |

| command period                              |      |      |      |     |     |       |       |

| ACTIVE to READ or WRITE delay               | tRCD | 22.5 |      | 30  |     | ns    |       |

| Refresh period (4096 cycles) tT = 1ns.      | tREF |      | 64   |     | 64  | ms    |       |

| PRECHARGE command period                    | tRP  | 22.5 |      | 30  |     | ns    |       |

| ACTIVE bank A to ACTIVE bank B command      | tRRD | 15   |      | 20  |     | ns    |       |

| period                                      |      |      |      |     |     |       |       |

| Transition time                             | tΤ   | .3   | 2    | .3  | 2   | ns    |       |

| Write recovery time                         | tWR  | 20   |      | 20  |     | ns    | 2     |

#### AC ELECTRICAL CHARACTERISTICS: Vcc = 3.3V ± 10%V, Temp. = 25° to 70°C (CL = CAS Latency)

| AC CHARACTERISTICS                                      |       | -75A | -75A | -8A | -8A     |       | .,    |

|---------------------------------------------------------|-------|------|------|-----|---------|-------|-------|

| PARAMETER                                               | SYM   | MIN  | MAX  | MIN | MA<br>X | UNITS | NOTES |

| READ/WRITE command to READ/WRITE command                | tCCD  | 1    |      | 1   | ^_      | tCK   |       |

| CKE to clock disable or power-down entry mode           | tCKED | 1    |      | 1   |         | tCK   |       |

| CKE to clock enable or power-down exit setup mode       | tPED  | 1    |      | 1   |         | tCK   |       |

| DQM to input data delay                                 | tDQD  | 0    |      | 0   |         | tCK   |       |

| DQM to data mask during WRITEs                          | tDQM  | 0    |      | 0   |         | tCK   |       |

| DQM to data high-impedance during READs                 | tDQZ  | 2    |      | 2   |         | tCK   |       |

| WRITE command to input data delay                       | tDWD  | 0    |      | 0   |         | tCK   |       |

| Data-in to ACTIVE command                               | tDAL  | 5    |      | 5   |         | tCK   |       |

| Data-in to PRECHARGE command                            | tDPL  | 2    |      | 2   |         | tCK   |       |

| Last data-in to burst STOP command                      | tBDL  | 1    |      | 1   |         | tCK   |       |

| Last data-in to new READ/WRITE command                  | tCDL  | 1    |      | 1   |         | tCK   |       |

| Last data-in to PRECHARGE command                       | tRDL  | 2    |      | 2   |         | tCK   |       |

| LOAD MODE REGISTER command to ACTIVE or REFRESH command | tMRD  | 2    |      | 2   |         | tCK   | 1     |

| Data-out to high impedance from PRECHARGE command CL=3  | tROH  | 3    |      | 3   |         | tCK   |       |

| Transition time                                         | tΤ    | .3   | 2    | .3  | 2       | ns    |       |

| Write recovery time                                     | tWR   | 20   |      | 20  |         | ns    | 2     |

### NOTES:

- tHZ defines the time at which the output achieves the open circuit condition; it is not a reference to Voh or Vol. The last valid data element will meet tOH before going high-Z.

- 2. Timing actually specified by tWR plus tRP clock(s) specified as a reference only at a minimum cycle rate

## P16M648YA7, P32M6416YA7 P16M648YB7, P32M6416YB7

**SERIAL PRESENCE-DETECT OPERATION -** This module incorporates Serial Presence-Detect (SPD). The SPD function is implemented using a 2,048 bit EEPROM, containing 256 bytes of nonvolatile storage. The first 128 bytes can be programmed by SpecTek to identify the module type and various DRAM organization and timing parameters. The remaining 128 bytes of storage are available for use by the customer. System READ/WRITE operations between the master (system logic) and the slave EEPROM device (DIMM) occur via a standard IIC bus using the DIMM's SCL (clock) and SDA (data) signals, together with SA(2:0), which provide 8 unique DIMM/EEPROM addresses.

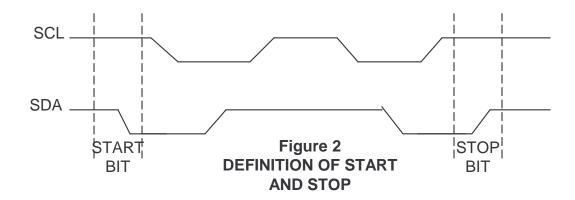

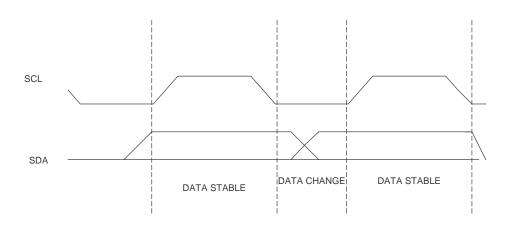

**SPD CLOCK AND DATA CONVENTIONS** - Data states on the SDA line can change only during SCL LOW. SDA state changes during SCL HIGH are reserved for indicating start and stop conditions (Figures 1 and 2).

**SPD START CONDITION -** All commands are preceded by the start condition, which is a HIGH to LOW transition of SDA when SCL is HIGH. The serial PD device continuously monitors the SDA and SCL lines for the start condition and will not respond to any command until this condition has been met.

**SPD STOP CONDITION** - All communications are terminated by a stop condition, which is a LOW to HIGH transition of SDA when SCL is HIGH. The stop condition also places the serial PD device into standby power mode.

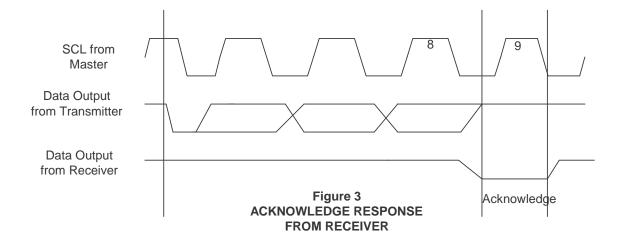

SPD ACKNOWLEDGE - Acknowledge is a software convention used to indicate successful data transfers. The transmitting device, either master or slave, will release the bus after transmitting eight bits of data (Figure 3). The PD device will always respond with an acknowledge after recognition of a start condition and its slave address. If both the device and a write operation have been selected, the PD device will respond with an acknowledge after the receipt of each subsequent eight bit word. In the read mode the PD device will transmit eight bits of data, release the SDA line and monitor the line for an acknowledge. If an acknowledge is not detected, the slave will terminate further data transmissions and await the stop condition to return to standby power mode.

### SERIAL PRESENCE-DETECT EEPROM DC OPERATING CONDITIONS (VCC = $\pm 3.3 \text{V} \pm 0.3 \text{V}$ )

| PARAMETER/CONDITION                                          | Symbol          | MIN      | MAX      | Units |

|--------------------------------------------------------------|-----------------|----------|----------|-------|

| Supply Voltage                                               | Vcc             | 3.0      | 3.6      | V     |

| Input High (Logic 1) Voltage, all inputs                     | V <sub>IH</sub> | Vcc x .7 | Vcc x .5 | V     |

| Input Low (Logic 0) Voltage, all inputs                      | $V_{IL}$        | -1.0     | Vcc x .3 | V     |

| OUTPUT LOW VOLTAGE, I <sub>OUT</sub> =3mA                    | V <sub>OL</sub> |          | 0.4      | V     |

| INPUT LEAKAGE CURRENT, V <sub>IN</sub> = GND to Vcc          | ILI             |          | 10       | μΑ    |

| OUTPUT LEAKAGE CURRENT, V <sub>OUT =</sub> GND to Vcc        | I <sub>LO</sub> |          | 10       | μΑ    |

| STANDBY CURRENT SCL=SDA=Vcc -0.3V, All other inputs = GND or | I <sub>SB</sub> |          | 30       | μΑ    |

| 3.3V +10%                                                    |                 |          |          | ·     |

| POWER SUPPLY CURRENT SCL clock frequency = 100 KHz           | Icc             |          | 2        | μΑ    |

#### SERIAL PRESENCE-DETECT EEPROM AC OPERATING CONDITIONS (VCC = $+3.3V \pm 0.3V$ )

| AC CHARACTERISTICS                                  |                     |     |     |       |       |

|-----------------------------------------------------|---------------------|-----|-----|-------|-------|

| PARAMETER/CONDITION                                 | Symbol              | MIN | MAX | Units | Notes |

| SCL LOW to SDA data-out valid                       | <sup>t</sup> AA     | 0.3 | 3.5 | μs    |       |

| Ildle bus time before a transition can start        | <sup>t</sup> BUF    | 4.7 |     | μs    |       |

| Data-out hold time                                  | ¹DH                 | 300 |     | ns    |       |

| SDA and SCL fall time                               | <sup>t</sup> F      |     | 300 | ns    |       |

| Data-in hold time                                   | <sup>1</sup> HD:DAT | 0   |     | μs    |       |

| Start condition hold time                           | THD:STA             | 4   |     | μs    |       |

| Clock HIGH period                                   | <sup>t</sup> HIGH   | 4   |     | μs    |       |

| Noise suppresssion time constant at SCL, SDA inputs | <sup>t</sup>        |     | 100 | ns    |       |

| Clock LOW period                                    | <sup>t</sup> LOW    | 4.7 |     | μs    |       |

| SDA and SCL rise time                               | <sup>t</sup> R      |     | 1   | μs    |       |

| SCL clock frequency                                 | <sup>t</sup> SCL    |     | 100 | KHz   |       |

| Data-in setup time                                  | 'SU:DAT             | 250 |     | ns    |       |

| Start condition setup time                          | 'SU:STA             | 4.7 |     | μs    |       |

| Stop condition setup time                           | 'SU:STO             | 4.7 |     | μs    |       |

| WRITE cycle time                                    | <sup>t</sup> WR     |     | 10  | ms    | 1     |

**NOTES:** 1. The SPD EEPROM WRITE cycle time (<sup>t</sup>WR) is the time from a valid stop condition of a WRITE sequence to the end of the EEPROM internal erase/program cycle. During the WRITE cycle the EEPROM bus interface circuit is disabled, SDA remains HIGH due to pull-up resistor, and the EEPROM does not respond to its slave address.

4 SpecTek reserves the right to change products or specifications without notice. ©2002 SpecTek

# P16M648YA7, P32M6416YA7 P16M648YB7,P32M6416YB7

Figure 1 DATA VALIDITY