# ZON M3SX/P3SX Single-Phase/Polyphase Electricity Meter SoC

# **General Description**

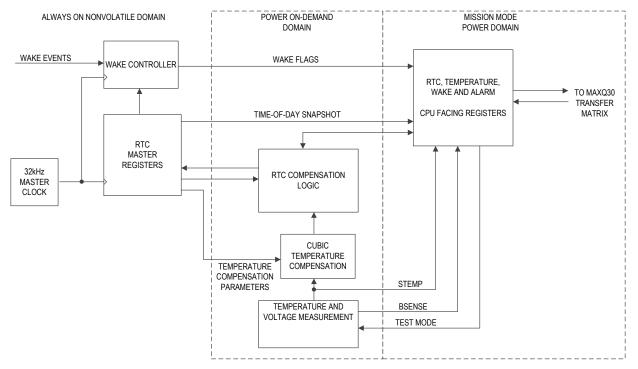

The ZON™ M3SX and P3SX (SY7M163G, SY7M166H) integrate dual 32-bit processors and security engines for single-phase (SY7M163G) and poly-phase (SY7M166H/GH) metering applications with up to 256KB flash, 20KB RAM, and a single-cycle 32x32 + 64 multiplier. The application processor (MPU) is a 32-bit MAXQ®30 Core. The metrology processor (or Compute Engine, CE) is a 32-bit processor dedicated to computing the metrology parameters from voltage and current samples. The integrated security engines (AES-128/192/256, AES-GCM-128, DES, TRNG) provide fast data encryption and decryption for secure smart grid communications. One touch switch pin enables capacitive touch detection.

The SY7T166GH (future product) poly-phase metering SoC provides exceptional temperature stability due to dual temperature trim of the bandgap reference.

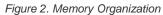

The device family also integrates all the essential metering function blocks: Real-time-clock (RTC) with automatic temperature compensation and multiple serial communication ports (UART, I<sup>2</sup>C, and SPI).

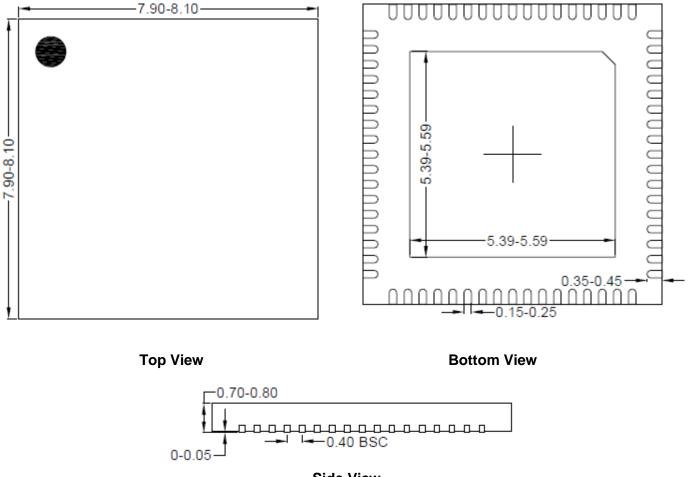

The compact 68-pin QFN package eliminates LCD common pins (LCD segment driver functionality is maintained at certain pins along with GPIO and special functions).

### Applications

- 1-Phase AMI Metering

- 3-Phase AMI Metering

- Energy Monitoring

Ordering Information appears at end of data sheet.

MAXQ is a registered trademark of Maxim Integrated Products, Inc. Rev 1.8; 1/2020

### **Benefits and Features**

- Advanced Metrology Provides Best-In-Class Performance

- Up to Seven Metrology Channels for Polyphase Metering and Up to Four Channels for Single-/ Two-Phase Metering

- 0.1% Typical Accuracy Over 5000:1 Current Range with Integrated Metrology ADCs

- Integrated ADCs Support Current Transformers, Rogowski Coils, and Shunts

- Three Remote ADC Interfaces for Current Sensing with Remote Shunts

- Dedicated RTC Circuit Ensures Accurate Timekeeping

- Integrated Security Engines for Secure Smart Metering

- AES-128/192/256, and AES-GCM-128

- True Random Number Generator, 3DES

- On-Chip CE-OnGuard Protects Metering Operations from Unauthorized Access, and Ensures Authenticity of Peripheral Operations

- Supports Welmec/MID

- Rich Peripheral Support Reduces Board Space and Lowers BOM Cost

- Low-Power ADC for Environmental Monitoring

- SPI (Master and Slave), I<sup>2</sup>C (Master and Slave), 1x UART, One Smart Card Port, One Touch Switch Input

- Single-Cycle 32x32 + 64 Multiply-Accumulate Unit for Demanding Signal Processing

- Dual 32-Bit Programmable Cores Provide High Processing Power and Flexibility

- Metering Core (Compute Engine) with up to 20MIPS at 20MHz, and up to 8KB RAM for Data and Code

- Application Core with up to 20MIPS at 20MHz, 256KB/128KB Flash Code Space, 12KB Data RAM (MPU), 8KB Data RAM (CE), 1KB NVRAM

- Configurable Operation Modes Save Power

- 1.6µA SLP Mode (VBAT)

- 1KB NVRAM in SLP Mode

- QFN-68 package

- ZON M3SX, 128KB flash = SY7M163G

- ZON P3SX, 256KB flash = SY7M166H

- ZON P3SX, 256KB flash, high precision = SY7T166GH (future product)

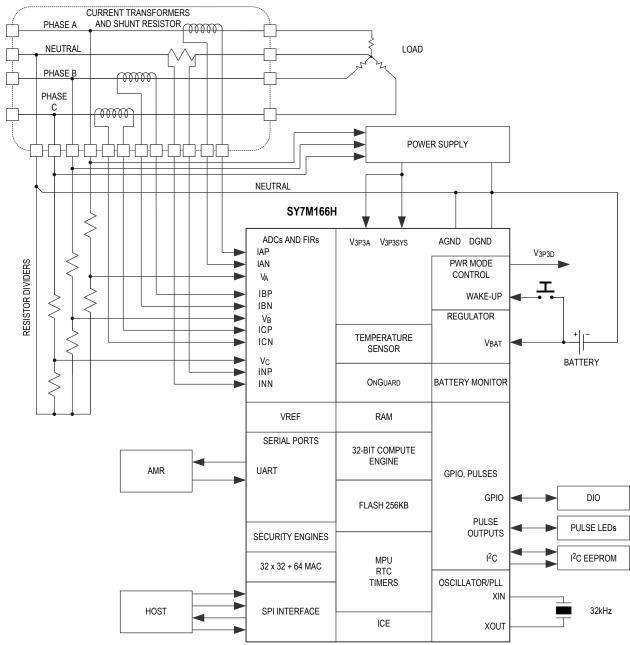

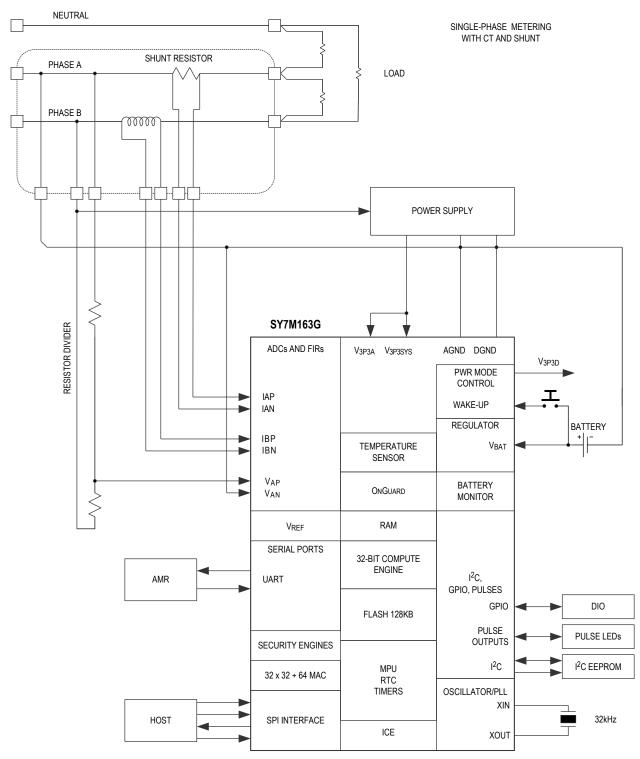

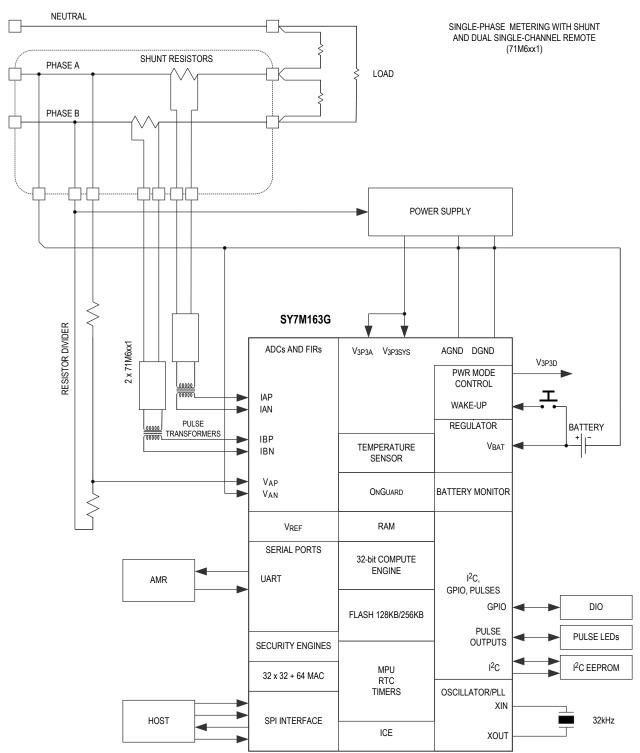

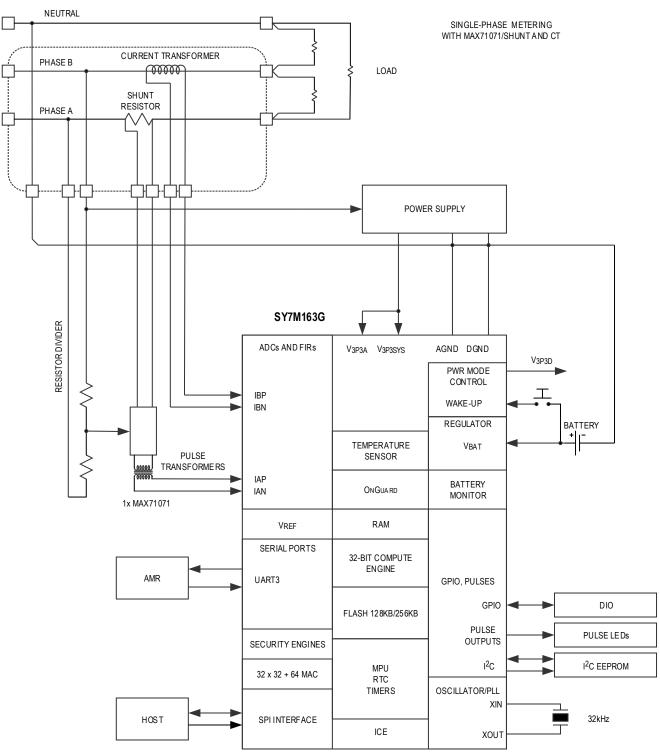

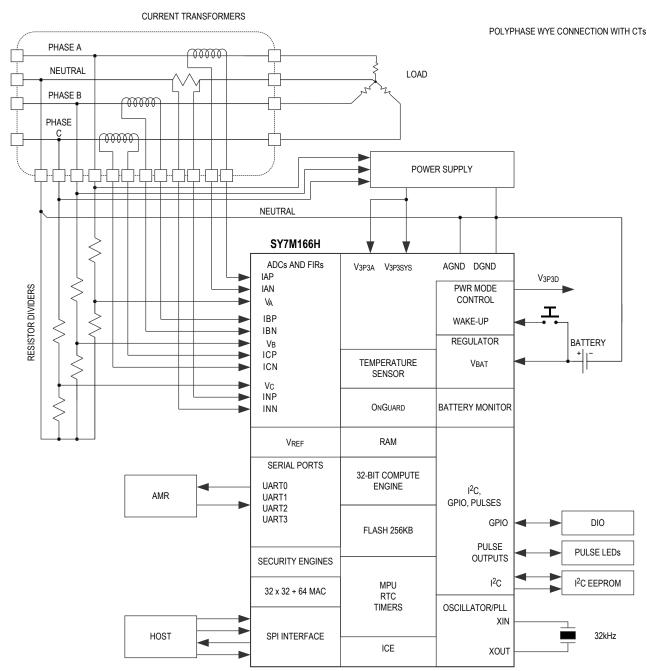

# **Typical Application Circuit**

# **Absolute Maximum Ratings**

| Voltage, Current Supplies and GND Pins                | V |

|-------------------------------------------------------|---|

| V <sub>3P3SYS</sub> , V <sub>3P3A</sub> 0.5V to +3.6V | V |

| V <sub>BAT</sub> 0.5V to +3.8V                        | V |

| Crystal Pins                                          | С |

| XIN, XOUT(-10mA to +10mA), (-0.5V to +3.0V)           |   |

| Digital Pins                                          | D |

| Inputs(-10mA to +10mA), (-0.5V to +6V, MSN/BRN/       |   |

| LCD_ONLY mode)                                        |   |

| Inputs (-10mA to +10mA, (-0.5V to $V_{3P3D}$ + 0.5V, SLP mode)<br>Outputs (-8mA to +8mA), (-0.5V to $V_{3P3SYS}$ + 0.5V)<br>Maximum Combined Sink Current into DIO Pins 100mA<br>Maximum Combined Source Current from DIO Pins |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating Junction Temperature (peak, 100ms)                                                                                                                                                                                   |

| +140°C Operating Junction Temperature (continuous)                                                                                                                                                                             |

| +125°C Storage Temperature Range45°C                                                                                                                                                                                           |

| to +165°C Lead Temperature (soldering, 10s)                                                                                                                                                                                    |

| 300°C Soldering Temperature (reflow)                                                                                                                                                                                           |

| +250°C                                                                                                                                                                                                                         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# Package Thermal Characteristics (Note 1)

#### QFN

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) .....48°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ).......11°C/W Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board.

# **Electrical Characteristics**

| PARAMETER                                                  | SYMBOL               | CONDITIONS                                                                                                                                              | MIN | TYP   | MAX  | UNITS |

|------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------|-------|

| POWER SUPPLY                                               |                      |                                                                                                                                                         |     |       |      |       |

|                                                            | I <sub>V3P3_1</sub>  | V <sub>LS</sub> = LOW_BIAS = 0, preamp gain =<br>8, muxed ADC CLK = 5MHz, staring<br>ADC clock = 1.67MHz, MPU clock =<br>20MHz, standard CE Code pass   |     | 15.6  | 18.5 |       |

|                                                            | I <sub>V3P3_2</sub>  | V <sub>LS</sub> = LOW_BIAS = 0, preamp off,<br>muxed ADC CLK = 5MHz, staring<br>ADC clock = 1.67MHz, MPU clock<br>=20MHz, standard CE Code pass         |     | 15.4  | 18.2 |       |

|                                                            | I <sub>V3P3_3</sub>  | V <sub>LS</sub> = LOW_BIAS = 0, preamp gain =<br>8, muxed ADC CLK = 2.5MHz, staring<br>ADC clock = 0.83MHz, MPU clock =<br>20MHz, standard CE Code pass |     | 13.5  | 16.2 |       |

|                                                            | I <sub>V3P3_4</sub>  | V <sub>LS</sub> = LOW_BIAS = 0, preamp off,<br>muxed ADC CLK = 2.5MHz. staring<br>ADC clock = 0.83MHz, MPU clock =<br>20MHz. standard CE Code pass      |     | 13.45 | 16.1 |       |

| V <sub>3P3A</sub> Current + V <sub>3P3SYS</sub><br>Current | I <sub>V3P3_5</sub>  | $V_{LS}$ = 1, LOW_BIAS = 0, preamp gain<br>= 8, muxed ADC CLK = 1MHz. staring<br>ADC clock = 0.33MHz, MPU clock =<br>4MHz, standard CE Code pass        |     | 5     | 6.8  | mA    |

|                                                            | I <sub>V3P3_6</sub>  | V <sub>LS</sub> = 1, LOW_BIAS = 0, preamp gain<br>= 8, muxed ADC CLK = 0.5MHz.<br>staring ADC clock = 0.08MHz. MPU<br>clock = 0.25MHz, standard CE Code |     | 2.9   | 3.6  |       |

|                                                            | I <sub>V3P3_7</sub>  | Metering off, CE off, ADCs disabled,<br>MPU clock = 20MHz                                                                                               |     | 10.8  | 16   |       |

|                                                            | I <sub>V3P3_9</sub>  | Metering off, CE off, ADCs disabled,<br>MPU clock = 1.25MHz                                                                                             |     | 4.6   | 6.25 |       |

|                                                            | I <sub>V3P3_10</sub> | $V_{LS}$ = 1, LOW_BIAS = 0, preamp off,<br>muxed ADC CLK = 0.5MHz. staring<br>ADC clock = 0.08MHz. MPU clock =<br>0.25MHz, standard CE Code pass        |     | 2.9   | 3.5  |       |

|                                                            | I <sub>V3P3_11</sub> | $V_{LS}$ = 1, LOW_BIAS = 0, preamp off,<br>muxed ADC CLK = 1MHz. starting<br>ADC clock = 0.33MHz, MPU clock =<br>4MHz, standard CE Code pass            |     | 5     | 6.75 |       |

| PARAMETER                                        | SYMBOL             | CONDITIONS                                                                                                                                                                          | MIN | TYP  | MAX  | UNITS |

|--------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|-------|

| POWER SUPPLIES (continue                         | ed)                |                                                                                                                                                                                     |     |      |      |       |

| V <sub>BAT</sub> Current (2.8-3.8V),<br>Brownout | I <sub>BAT1</sub>  | $V_{LS}$ = LOW_BIAS = 0, preamp gain =<br>8, muxed ADC CLK = 5MHz, starting<br>ADC clock = 1.67MHz, MPU clock =<br>20MHz, standard CE Code pass,<br>$V_{3P3SYS/A}$ off              |     | 15.6 | 18.5 | mA    |

|                                                  | I <sub>BAT3</sub>  | $V_{LS} = LOW\_BIAS = 0, preamp gain = 8, muxed ADC CLK = 0.5MHz, starting ADC clock = 0.42MHz, MPU clock = 1.25MHz, standard CE Code pass, V_{3P3SYS/A off}$                       |     | 6.8  | 8.5  |       |

|                                                  | I <sub>BAT4</sub>  | $V_{LS} = 1$ , LOW_BIAS = 0, preamp gain<br>= 8, muxed ADC CLK = 1MHz,<br>staring ADC clock = 0.33MHz,<br>MPU clock = 4MHz, standard CE<br>Code pass, V <sub>3P3SYS/A</sub> off     |     | 5    | 6.75 |       |

|                                                  | I <sub>BAT5</sub>  | $V_{LS}$ = 1, LOW_BIAS = 0, preamp gain<br>= 8, muxed ADC CLK = 1MHz, staring<br>ADC clock = 0.166MHz, MPU clock =<br>2MHz, standard CE Code pass,<br>V <sub>3P3SYS/A</sub> off     |     | 4.2  | 5.75 |       |

|                                                  | I <sub>BAT6</sub>  | $V_{LS}$ = 1, LOW_BIAS = 0, preamp gain<br>= 8, muxed ADC CLK = 0.5MHz,<br>staring ADC clock = 0.08MHz, MPU<br>clock = 0.25MHz, standard CE Code<br>pass, V <sub>3P3SYS/A</sub> off |     | 3.1  | 4    |       |

| VBAT Current MSN                                 | I <sub>BAT10</sub> |                                                                                                                                                                                     |     | 0    | 200  | nA    |

| V <sub>BAT</sub> Current LCD_ONLY                | I <sub>BAT12</sub> | LCD CLK (min), LCD DAC off, no LCD<br>SRAM access, V <sub>3P3SYS/A</sub> off                                                                                                        |     | 3    | 6.4  | μA    |

|                                                  | IBAT13             | LCD CLK (min), LCD DAC on, no<br>LCD SRAM access, $V_{3P3SYS/A}$ off,<br>$V_{BAT} = 2.8V$ to 3.8V                                                                                   |     | 15   | 25   |       |

| VBAT Current SLP                                 | IVBATRTC4          | RTC compensation off                                                                                                                                                                |     | 1.6  | 3.1  | μA    |

| (Note 1, except I <sub>VBATRTC4</sub> )          | IVBATRTC5          | TRANGE = 00, TEMPPER = 5                                                                                                                                                            |     | 21   | 41.1 |       |

| VDAIRIU4/                                        | IVBATRTC6          | TRANGE = 00, TEMPPER = 6                                                                                                                                                            |     | 11   | 25.1 |       |

|                                                  | IVBATRTC7          | TRANGE = 1F, TEMPPER = 5                                                                                                                                                            |     | 7    | 16.1 | μA    |

|                                                                     |                 |                                                                                                                                                                                            | 1                          |       |       |       |

|---------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------|-------|-------|

| PARAMETER                                                           | SYMBOL          | CONDITIONS                                                                                                                                                                                 | MIN                        | TYP   | MAX   | UNITS |

| INPUT SPIKE WIDTH TOLERA                                            | NCE             |                                                                                                                                                                                            | I                          |       |       |       |

| t <sub>SPIKE</sub> , RSTN, and TEST                                 |                 | Positive spike, spike < 200ns is ignored                                                                                                                                                   |                            |       | 1100  | ns    |

| LOGIC LEVELS                                                        |                 |                                                                                                                                                                                            |                            |       |       |       |

| Digital High-Level Input Voltage                                    | V <sub>IH</sub> |                                                                                                                                                                                            | 2                          |       |       | V     |

| Digital Low-Level Input Voltage                                     | V <sub>IL</sub> |                                                                                                                                                                                            |                            |       | +0.6  | V     |

|                                                                     | ۱ <sub>IL</sub> | RSTN                                                                                                                                                                                       | 5                          |       | 175   | μA    |

| Input Pullup Current                                                |                 | All digital inputs except RSTN                                                                                                                                                             | 40                         |       | 175   |       |

| Input Pulldown Current,<br>JTAG_E                                   | IIH             | V <sub>IN</sub> = V <sub>3P3SYS</sub>                                                                                                                                                      | 30                         |       | 160   | μΑ    |

| Digital High-Level Output                                           | V <sub>OH</sub> | I <sub>LOAD</sub> = 1mA                                                                                                                                                                    | V <sub>3P3D</sub> -<br>0.4 |       |       | V     |

| Digital High-Level Output<br>Voltage                                |                 | I <sub>LOAD</sub> = 5mA                                                                                                                                                                    | V <sub>3P3D</sub><br>- 0.6 |       |       |       |

| Digital Low-Level Output                                            | V <sub>OL</sub> | I <sub>LOAD</sub> = -1mA                                                                                                                                                                   |                            |       | 0.4   | V     |

| Voltage                                                             |                 | $I_{LOAD} = -15 mA$                                                                                                                                                                        |                            |       | 0.9   |       |

| Maximum Combined Current<br>MSN Mode                                |                 | $V_{3P3SYS} = 3.0V$ , pull I out of $V_{3P3D}$<br>until $V_{3P3D} = 2.4V$                                                                                                                  | 66                         |       |       | mA    |

| V3P3D SWITCH                                                        |                 |                                                                                                                                                                                            |                            |       |       |       |

| On-Resistance (V <sub>3P3SYS</sub> to<br>V <sub>3P3D</sub> )        |                 | $I(V_{3P3D}) \le 1mA$                                                                                                                                                                      |                            | 6     | 11    | Ω     |

| On-Resistance (V <sub>BAT</sub> to V <sub>3P3D</sub> )              |                 | $I(V_{3P3D}) \le 1mA, V_{BAT} \ge 2.2V.$                                                                                                                                                   |                            | 6     | 11    | Ω     |

| VREF                                                                | 1               |                                                                                                                                                                                            |                            |       |       | 1     |

| V <sub>REF</sub> Voltage                                            |                 | T <sub>A</sub> = +22°C                                                                                                                                                                     | 1.225                      | 1.228 | 1.231 | V     |

| V <sub>REF</sub> PSRR                                               |                 | $\Delta V_{REF} / \Delta V_{3P3A}$ , $V_{3P3A} = 2.8 V$ to 3.6 V                                                                                                                           | -1.5                       |       | +1.5  | mv/V  |

| V <sub>NOM</sub> Definition                                         |                 | $V_{NOM(T)} = V_{REF(22)} + (T-22)TC1 + (T-22)^2TC2$                                                                                                                                       |                            |       |       | V     |

| V <sub>NOM</sub> Temperature Coefficient<br>TC1 (SY7M163G/SY7M166H) |                 | TC1 = -8.164 10 <sup>-5</sup> – 6.267 10 <sup>-6</sup> x<br>TRIMT                                                                                                                          |                            |       |       | V/°C  |

| V <sub>NOM</sub> Temperature Coefficient<br>TC2 (SY7M163G/SY7M166H) |                 | TC2 = -2.667 10 <sup>-7</sup> + 4.6386 10 <sup>-9</sup> x<br>TRIMT                                                                                                                         |                            |       |       | V/°C2 |

| V <sub>NOM</sub> Temperature Coefficient<br>TC1 (SY7T166GH)         |                 | TC1 = -8.2 10 <sup>-5</sup> – 6.267 10 <sup>-6</sup> x TRIMT +<br>{[(VREF(85) –<br>(VNOM(85)]/STEMP(85)} x STEMP<br>Note: VREF(85) and STEMP(85)<br>stored in Info Block during production |                            |       |       | V/°C  |

| V <sub>NOM</sub> Temperature Coefficient<br>TC2 (SY7T166GH)         |                 | TC2 = -2.67 10 <sup>-7</sup> + 4.64 10 <sup>-9</sup> x TRIMT                                                                                                                               |                            |       |       | V/°C2 |

| PARAMETER                                                                             | SYMBOL           | CONDITIONS                                                                                         | MIN   | TYP    | MAX   | UNITS  |

|---------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------|-------|--------|-------|--------|

| V <sub>REF</sub> Deviation from V <sub>NOM(T)</sub><br>(SY7M163G/SY7M166H, Note<br>1) |                  | [(V <sub>REF(T)</sub> - V <sub>NONM(T)</sub> ) x 10 <sup>6</sup> ]/<br>[V <sub>NOM(T)</sub> x 62)] | -43.5 |        | +43.5 | ppm/°C |

| V <sub>REF</sub> Deviation from V <sub>NOM(T)</sub><br>(SY7T166GH, Note 1)            |                  | [(V <sub>REF(T)</sub> - V <sub>NONM(T)</sub> ) x 10 <sup>6</sup> ]/<br>[V <sub>NOM(T)</sub> x 62)] | -15   |        | +15   | ppm/°C |

| POWER FAULT COMPARATO                                                                 | RS               |                                                                                                    |       |        |       |        |

| V <sub>3AOK</sub> Response Time,                                                      |                  | 100mV overdrive falling                                                                            | 100   |        | 400   | μs     |

| Including Filters                                                                     |                  | 100mV overdrive rising                                                                             | 100   |        | 400   |        |

| V <sub>3OK</sub> Response Time,<br>Including Filters                                  |                  | 100mV overdrive falling                                                                            | 100   |        | 400   | μs     |

| V <sub>3P3DOK</sub> Response Time,<br>Including Filters                               |                  | 100mV overdrive, rising                                                                            | 75    |        | 350   | μs     |

| V <sub>3OK</sub> Response Time,<br>Including Filters                                  |                  | 100mV overdrive, falling                                                                           | 100   |        | 400   | μs     |

| V <sub>3P3DOK</sub> Response Time,<br>Including Filters                               |                  | 100mV overdrive, falling                                                                           | 75    |        | 350   | μs     |

| V <sub>DDOK</sub> Response Time,                                                      |                  | 100mV overdrive, rising                                                                            | 75    |        | 350   | μs     |

| Including Filters.                                                                    |                  | 100mV overdrive, falling                                                                           | 100   |        | 425   |        |

| Falling Threshold, $V_{3AOK}$                                                         |                  | V <sub>3P3SYS</sub> falling                                                                        | 2.81  | 2.9    | 2.99  | V      |

| Falling Threshold, V <sub>3OK</sub>                                                   |                  | V <sub>3P3SYS</sub> falling                                                                        | 2.46  |        | 2.60  | V      |

| Falling Threshold, $V_{DDOK}$                                                         |                  | $V_{3P3D}$ falling, measure $V_{DD}$                                                               | 1.4   |        | 1.76  | V      |

| Falling Threshold, V <sub>3P3DOK</sub>                                                |                  | V <sub>3P3D</sub> falling                                                                          | 2.1   | 2.26   | 2.42  | V      |

| VBAT VOLTAGE MONITOR                                                                  |                  |                                                                                                    |       |        |       | 1      |

| Measurement Resolution                                                                | V <sub>LSB</sub> |                                                                                                    |       | 24     |       | mV/LSB |

| Nominal Value                                                                         | BNOM             | V <sub>3P3</sub> = 3.3V, T <sub>A</sub> = +22°C                                                    | 121   | 125    | 130   | LSB    |

| Measurement Error                                                                     |                  | V <sub>BAT</sub> = 2.0V to 4.0V                                                                    |       |        | 4.6   | %      |

| BinZ                                                                                  |                  | Measured using FBAT test mode,<br>(battery frequency is output on TMUX)                            | 250   | 390    | 535   | kΩ     |

| BCURR load                                                                            |                  | [I(V <sub>BAT</sub> ) with BCURR=1] - [I(V <sub>BAT</sub> )<br>with BCURR = 0]                     | 80    | 100    | 130   | μA     |

| TEMPERATURE MONITOR                                                                   |                  |                                                                                                    |       |        |       |        |

| Temperature Error                                                                     |                  | T <sub>A</sub> = +22°C,                                                                            |       | ±3.6   |       | °C     |

| Relative Temperature Error (Note 1)                                                   |                  | -40°C ≤ T <sub>A</sub> ≤ +85°C,                                                                    | -1.75 |        | +1.75 | °C     |

| T <sub>LSB</sub>                                                                      |                  |                                                                                                    |       | 0.0811 |       | °C/LSB |

| TETIME: Measurement time                                                              |                  | Duration of activity on TEMP_VCO<br>from TXUXOUT on TEMP_VCO,<br>(temp measurement only)           | 20    | 35     | 60    | ms     |

| PARAMETER                                                 | SYMBOL | CONDITIONS                                                                | MIN   | TYP MAX   | UNITS  |  |

|-----------------------------------------------------------|--------|---------------------------------------------------------------------------|-------|-----------|--------|--|

| STARING ADCs                                              |        |                                                                           |       |           |        |  |

|                                                           |        | Preamp off                                                                | -250  | +250      |        |  |

|                                                           |        | Preamp GAIN = 4                                                           | -62   | +62       | m)/    |  |

| Usable Input Range                                        |        | Preamp GAIN = 8                                                           | -31   | +31       | mV     |  |

|                                                           |        | Preamp GAIN = 16                                                          | -15   | +15       |        |  |

|                                                           |        | Preamp off                                                                | 140   | 450       |        |  |

|                                                           |        | Preamp GAIN = 4                                                           | 2.5   | 10        | kΩ     |  |

| Input Impedance                                           |        | Preamp GAIN = 8                                                           | 2.5   | 10        | K12    |  |

|                                                           |        | Preamp GAIN = 16                                                          | 2.5   | 10        |        |  |

| LSB Size                                                  |        | FIR_LEN = 15                                                              |       | 97        | nV/LSB |  |

| Digital Full Scale                                        |        |                                                                           | ±     | 3,375,000 | LSB    |  |

| Input Offset Preamp Off                                   |        | Preamp off                                                                | -10   | 10        | mV     |  |

| Input Offset Preamp Gain = 4                              |        |                                                                           | -5.5  | +5.5      | mV     |  |

| Input Offset Preamp Gain = 8                              |        |                                                                           | -3    | +3        | mV     |  |

| Input Offset Preamp Gain = 16                             |        |                                                                           | -2    | +2        | mV     |  |

| Preamp Gain, Gain = 4                                     |        |                                                                           | 3.9   | 4.1       | V/V    |  |

| Preamp Gain, Gain = 8                                     |        |                                                                           | 7.8   | 8.2       | V/V    |  |

| Preamp Gain, Gain = 16                                    |        |                                                                           | 15.6  | 16.4      | V/V    |  |

| Preamp Phase Shift                                        |        |                                                                           |       | 12        | m°     |  |

| Preamp Phase Shift Variation<br>With Temperature (Note 1) |        |                                                                           | -0.27 | +0.27     | m°/°C  |  |

| Channel Gain Variation<br>vs. Supply                      |        | Variation of gain (both preamp and ADC), over supply                      | -40   | +40       | ppm/%  |  |

| Channel Gain Variation<br>vs. Temp (Note 1)               |        | Variation of gain, (both preamp and ADC), over temperature                | -55   | +55       | ppm/°C |  |

| ADC Gain Error vs. Supply                                 |        | $V_{IN} = 200 \text{mV}_{PK}$ , 55Hz, $V_{3P3A} = 2.8\text{V}$<br>to 3.6V |       | 90        | ppm/%  |  |

| THD, Preamp + ADC Preamp<br>Gain = 4                      |        | V <sub>IN</sub> = 62.5mV <sub>PK</sub> , 55Hz                             |       | -85       | dB     |  |

| THD, Preamp + ADC Preamp<br>Gain = 8                      |        | V <sub>IN</sub> = 31.25mV <sub>PK</sub> , 55Hz                            |       | -85       | dB     |  |

| THD, Preamp + ADC Preamp<br>Gain = 16                     |        | V <sub>IN</sub> = 15.6mV <sub>PK</sub> , 55Hz                             | -85   |           | dB     |  |

| THD, Bypass Preamp,<br>20mV <sub>PK</sub> Input           |        | 55Hz                                                                      |       | -85       | dB     |  |

| THD, bypass Preamp,<br>250mV <sub>PK</sub> Input          |        | 55Hz                                                                      |       | -85       | dB     |  |

| PARAMETER                                                    | SYMBOL                     | CONDITIONS                                                                    | MIN  | TYP           | MAX | UNITS                  |

|--------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------|------|---------------|-----|------------------------|

| Preamp Input Equivalent Noise<br>Density                     |                            | Preamp gain = 8, V <sub>IN</sub> = 20mV <sub>PK</sub> ,<br>55Hz, FIR_LEN = 11 |      | 300           |     | $\frac{nV}{\sqrt{Hz}}$ |

| ADC Noise (Bypass Preamp)                                    |                            | V <sub>IN</sub> = 20mV <sub>PK</sub> , 55Hz, FIR_LEN = 11                     |      | 425           |     | LSB                    |

| MUXED ADC                                                    |                            | •                                                                             |      |               |     |                        |

| Usable Input Range                                           |                            |                                                                               | -250 |               | 250 | mV                     |

| Input Impedance                                              |                            |                                                                               | 50   |               | 130 | kΩ                     |

| LSB Size                                                     |                            | FIR_LEN = 15                                                                  |      | 123           |     | nV/LSB                 |

| Digital Full Scale                                           |                            |                                                                               |      | 2,621,40<br>0 | )   | LSB                    |

| Input Offset                                                 |                            |                                                                               | -10  |               | 10  | mV                     |

| ADC Gain Error vs. Supply                                    |                            | $V_{IN} = 200 m V_{PK}$ , 55Hz,<br>$V_{3P3A} = 2.8V$ to 3.6V                  |      |               | 90  | ppm/%                  |

| THD 20mVpk input                                             |                            |                                                                               |      | -85           |     | dB                     |

| THD 250mVpk input                                            |                            |                                                                               |      | -85           |     | dB                     |

| ADC Noise                                                    |                            | V <sub>IN</sub> = 20mV <sub>PK</sub> , 55Hz, FIR_LEN = 11                     |      | 400           |     | LSB                    |

| ADC Input Equivalent Noise<br>Density                        |                            | V <sub>IN</sub> = 20mV <sub>PK</sub> , 55Hz, FIR_LEN = 11                     |      | 2000          |     | $\frac{nV}{\sqrt{Hz}}$ |

| EXTERNAL CRYSTAL OSCILL                                      | ATOR                       |                                                                               |      |               |     |                        |

| RTC Oscillator Frequency                                     | FXTAL                      |                                                                               |      | 32.768        |     | kHz                    |

| Maximum Crystal Power                                        |                            |                                                                               |      |               | 1   | μW                     |

| XIN to XOUT Capacitance                                      | C <sub>XIN_XOUT</sub>      |                                                                               |      |               | 3   | pF                     |

| XIN Capacitance to DGND                                      | C <sub>XIN_DGND</sub>      | $X_{IN} = 100 \text{mV}_{P-P}$                                                |      | 5             |     | pF                     |

| XOUT Capacitance to DGND                                     | C <sub>XOUT_DGN</sub><br>D | X <sub>OUT</sub> = 0V                                                         |      | 5             |     | pF                     |

| Frequency Variation with<br>Voltage, V <sub>BAT</sub> = 3.8V |                            | Reference frequency is V <sub>3P3</sub> = 3.3V                                |      | 0             |     | ppm                    |

| Frequency Variation with<br>Voltage, V <sub>BAT</sub> = 3V   |                            | Reference frequency is V <sub>3P3</sub> = 3.3V                                |      | 0             |     | ppm                    |

| PARAMETER                                                    | SYMBOL                             | CONDITIONS                                                          | MIN                     | TYP                 | MAX                    | UNITS |

|--------------------------------------------------------------|------------------------------------|---------------------------------------------------------------------|-------------------------|---------------------|------------------------|-------|

| Frequency Variation with<br>Voltage, V <sub>BAT</sub> = 2.5V |                                    | Reference frequency is $V_{3P3} = 3.3V$                             |                         | 0                   |                        | ppm   |

| Frequency Variation with<br>Voltage, V <sub>BAT</sub> = 2V   |                                    | Reference frequency is $V_{3P3} = 3.3V$                             |                         | 0                   |                        | ppm   |

| Frequency Variation with<br>Voltage, V <sub>BAT</sub> = 1.8V |                                    | Reference frequency is $V_{3P3} = 3.3V$                             |                         | 0                   |                        | ppm   |

| Maximum Output Voltage                                       |                                    | $V_{IN}$ = .2V <sub>P-P</sub> on XIN, sine wave 32kHz, no test load |                         |                     | 1.5                    | V     |

| HF frequency (Master Clock,<br>Before Prescaler/Divider)     |                                    | PLL output frequency                                                |                         | 58.98               |                        | MHz   |

| INTERNAL 32K OSCILLATOR                                      |                                    |                                                                     |                         |                     |                        |       |

| Nominal Frequency                                            | fosc                               |                                                                     |                         | 32.768              |                        | kHz   |

| Frequency Error                                              |                                    |                                                                     | -2                      |                     | +2                     | %     |

| SPI TIMING (Note 1)                                          |                                    | •                                                                   | -                       |                     |                        |       |

| SPI Master Operating<br>Frequency                            | 1/t <sub>MCK</sub>                 |                                                                     |                         |                     | f <sub>MPUCLK</sub> /2 | MHz   |

| SPI Slave Operating Frequency                                | 1/t <sub>SCK</sub>                 |                                                                     |                         |                     | f <sub>MPUCLK</sub> /4 | MHz   |

| SCLK Output Pulse-Width<br>High/Low                          | <sup>t</sup> MCH, <sup>t</sup> MCL |                                                                     | t <sub>MCK</sub> /2- 35 |                     |                        | ns    |

| MOSI Output Hold Time After<br>SCLK Sample Edge              | <sup>t</sup> MOH                   |                                                                     | t <sub>MCK</sub> /2- 35 |                     |                        | ns    |

| MOSI Output Valid to Sample<br>Edge                          | t <sub>MOV</sub>                   |                                                                     | t <sub>MCK</sub> /2- 35 |                     |                        | ns    |

| MISO Input Valid to SCLK<br>Sample Edge Rise/Fall Setup      | t <sub>MIS</sub>                   |                                                                     | 35                      |                     |                        | ns    |

| MISO Input to SCLK<br>Sample Edge Rise/Fall                  | t <sub>MIH</sub>                   |                                                                     | 0                       |                     |                        | ns    |

| SCLK Input Pulse-Width<br>High/Low                           | <sup>t</sup> SCH, <sup>t</sup> SCL |                                                                     |                         | t <sub>SCK</sub> /2 |                        | ns    |

| SSEL Active to First Shift Edge                              | tSSE                               |                                                                     |                         | 50                  |                        | ns    |

| MOSI Input to SCLK Sample<br>Edge Rise/Fall Setup            | tsis                               |                                                                     | 35                      |                     |                        | ns    |

| MOSI Input from SCLK<br>Sample Edge Transition               | t <sub>SIH</sub>                   |                                                                     | 35                      |                     |                        | ns    |

| MISO Output Valid After SCLK<br>Shift Edge Transition        | t <sub>SOV</sub>                   |                                                                     |                         |                     | 70                     | ns    |

(Limits are 100% tested at  $T_A = +25^{\circ}$ C and  $T_A = +85^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.)

| PARAMETER                                                        | SYMBOL               | CONDITIONS             | MIN     | TYP | MAX | UNITS  |

|------------------------------------------------------------------|----------------------|------------------------|---------|-----|-----|--------|

| I <sup>2</sup> C TIMING 400kHz (Note 1)                          |                      |                        |         |     |     |        |

| Serial Clock Frequency                                           | fSCL                 |                        |         |     | 400 | kHz    |

| Bus Free Time Between a<br>STOP (P) and a START (S)<br>Condition | <sup>t</sup> BUF     |                        | 1300    |     |     | ns     |

| Hold Time, Repeated START<br>Condition, (Sr)                     | t <sub>HD,</sub> STA |                        | 600     |     |     | ns     |

| Low Period of the SCL Clock                                      | tLOW                 |                        | 1300    |     |     | ns     |

| High Period of the SCL Clock                                     | <sup>t</sup> HIGH    |                        | 600     |     |     | ns     |

| Setup Time for a Repeated START Condition (Sr)                   | t <sub>SU,</sub> STA |                        | 600     |     |     | ns     |

| Data Hold Time                                                   | t <sub>HD,</sub> DAT |                        | 0       |     | 900 | ns     |

| Data Setup Time                                                  | t <sub>SU,</sub> DAT |                        | 100     |     |     | ns     |

| Rise Time of Both SDA and SCL Signals, Receiving                 | t <sub>R</sub>       |                        |         | 300 |     | ns     |

| Fall Time of SDA Transmitting                                    | t <sub>F</sub>       |                        |         | 300 |     | ns     |

| Setup Time for STOP (P)<br>Condition                             | t <sub>SU,</sub> STO |                        | 600     |     |     | ns     |

| Capacitive Load for Each Bus<br>Line                             | СВ                   |                        |         |     | 400 | pF     |

| FLASH MEMORY                                                     |                      |                        | ·       |     |     |        |

| Flash Write Cycles (Minimum Endurance)                           |                      |                        | 100,000 |     |     | Cycles |

| Flash Data Retention                                             |                      | T <sub>A</sub> = +25°C | 100     |     |     | Veen   |

|                                                                  |                      | T <sub>A</sub> = +85°C | 25      |     |     | Years  |

| Page, (Sector), Erase Time                                       |                      |                        | 50      |     |     | μs     |

| Mass, (Chip), Erase Time                                         |                      |                        | 20      |     | 40  | ms     |

| Flash Write Time,<br>(Word Program Time)                         |                      |                        | 6       |     | 7.5 | μs     |

Note 1: Parameter not production tested, guaranteed by design to six-sigma.

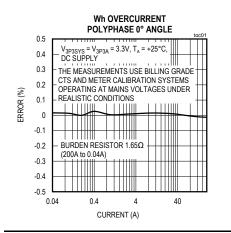

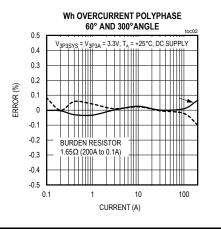

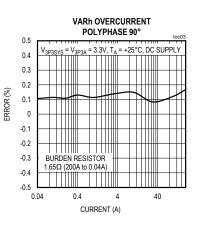

# **Typical Operating Characteristics**

# **Pin Configuration**

# **Pin Configurations (continued)**

# **Pin Description**

| PIN              |                  |                                        |                                                                                                                                                                                                  |

|------------------|------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SY7M166H<br>P3SX | SY7M163G<br>M3SX | NAME                                   | FUNCTIONS                                                                                                                                                                                        |

| 1                | 1                | P1.3/INT2/<br>PB_WAKE1                 | GPIO Port 1 Bit 3, External Interrupt 2, Level-Triggered Wake Input 1                                                                                                                            |

| 2                | 2                | P1.2/INT1/<br>PB_WAKE0                 | GPIO Port 1 Bit 2, External Interrupt 1, Level-Triggered Wake Input 0                                                                                                                            |

| 3                | 3                | P1.1/SEG25/TX3                         | GPIO Port 1 Bit 1, LCD Segment 25, UART3 TxD                                                                                                                                                     |

| 4                | 4                | P1.0/SEG24/<br>RX3/PU_WAKE3            | GPIO Port 1 Bit 0, LCD Segment 24, UART3 RxD Edge-Triggered Wake Input 3                                                                                                                         |

| 5                | 5                | P0.31/7816_IO0                         | GPIO Port 0 Bit 31, ISO UART0 I/O                                                                                                                                                                |

| 6                | 6                | P0.30/<br>7816_CLK0                    | GPIO Port 0 Bit 30, ISO UART0 Clock                                                                                                                                                              |

| 7                | 7                | P0.27/I2CSDA                           | GPIO Port 0 Bit 27, I <sup>2</sup> C SDA                                                                                                                                                         |

| 8                | 8                | P0.26/I2CSCL                           | GPIO Port 0 Bit 26, I <sup>2</sup> C SCL                                                                                                                                                         |

| 9                | 9                | P0.25/T1                               | GPIO Port 0 Bit 25, Timer Channel 1 Output                                                                                                                                                       |

| 10               | 10               | P0.24/T0                               | GPIO Port 0 Bit 24, Timer Channel 0 Output                                                                                                                                                       |

| 11               | 11               | P0.18/SEG18                            | GPIO Port 0 Bit 18, LCD Segment 18                                                                                                                                                               |

| 12               | 12               | P0.17/SEG17                            | GPIO Port 0 Bit 17, LCD Segment 17                                                                                                                                                               |

| 13               | 13               | P0.16/SEG16/<br>SPI_MISO               | GPIO Port 0 Bit 16, LCD Segment 16, SPI Peripheral—Master In, Slave Out                                                                                                                          |

| 14               | 14               | P0.15/SEG15/<br>SPI_MOSI               | GPIO Port 0 Bit 15, LCD Segment 1, SPI Peripheral—Master Out, Slave In                                                                                                                           |

| 15               | 15               | P0.14/SEG14/<br>SPI_SCLK               | GPIO Port 0 Bit 14, LCD Segment 14, SPI Peripheral—Serial Clock                                                                                                                                  |

| 16               | 16               | P0.13/INT0/<br>SEG13/<br>SPI_SSEL/INT0 | GPIO Port 0 Bit 13, External Interrupt 0, LCD Segment 13, SPI Peripheral—<br>Slave Select, internal interrupt 0                                                                                  |

| 17               | 17               | V <sub>DD</sub>                        | Bypass Point for the Internal Core Regulated Power Rail.                                                                                                                                         |

| 18               | 18               | P0.11/SEG11                            | GPIO Port 0 Pin 11, LCD Segment 11                                                                                                                                                               |

| 19               | 19               | P0.10/SEG10                            | GPIO Port 0 Bit 10, LCD Segment 10                                                                                                                                                               |

| 20               | 20               | P0.9/SEG9                              | GPIO Port 0 Bit 9, LCD Segment 9                                                                                                                                                                 |

| 21               | 21               | P0.8/SEG8                              | GPIO Port 0 Bit 8, LCD Segment 8                                                                                                                                                                 |

| 22               | 22               | PU_WAKE2                               | GPIO Port 1 Bit 30, LCD Segment 42, UART2 RxD, Edge-Triggered Wake Input 2                                                                                                                       |

| 23               | 23               | P1.28/RX1/<br>PU_WAKE1                 | GPIO Port 1 Bit 28 UART1 RxD Edge-Triggered Wake Input 1                                                                                                                                         |

| 24               | 24               | P1.27/TDO                              | GPIO Port 1 Bit 27, JTAG Test Data Out                                                                                                                                                           |

| 25               | 25               | P1.26/TCK                              | GPIO Port 1 Bit 26, JTAG Test Clock                                                                                                                                                              |

| 26               | 26               | P1.25/TMS                              | GPIO Port 1 Bit 25, JTAG Test Mode Select                                                                                                                                                        |

| 27               | 27               | P1.24/TDI                              | GPIO Port 1 Bit 24, JTAG Test Data In                                                                                                                                                            |

| 28               | 28               | JTAG_E                                 | JTAG_EJTAG Enable. If high, pins 43–46 are configured as JTAG test pins. If low, pins 43–46 are configured as GPIO.                                                                              |

| 29               | 29               | P1.23/VPULSE                           | GPIO Port 1 Bit 23 CE Meter Pulse—Reactive Energy                                                                                                                                                |

| 30               | 30               | P1.22/WPULSE                           | GPIO Port 1 Bit 22 CE Meter Pulse—Real Power                                                                                                                                                     |

| 31               | 31               | GNDD                                   | Digital Ground                                                                                                                                                                                   |

| 32               | 32               | V3P3D                                  | Internal Switch Output. Provides power to internal blocks and the core regulator. Primarily used to bypass the power supply. It should <u>not</u> be used to provide power for external devices. |

| 33               | 33               | TEST-CLK                               | Test pin for factory test. Connect to DGND as part of the ground plane.                                                                                                                          |

| PIN              |                  |                                |                                                                                                                                                                                                   |

|------------------|------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SY7M166H<br>P3SX | SY7M163G<br>M3SX | NAME                           | FUNCTIONS                                                                                                                                                                                         |

| 34               | 34               | P1.21/TOUCH1/<br>INT8/PB_WAKE3 | GPIO Port 1 Bit 21, Touch Switch 1 Input, External Interrupt 8, Level-Triggered Wake Input 3                                                                                                      |

| 35               | 35               | GNDR                           | Ground Connection                                                                                                                                                                                 |

| 36               | 38               | IAP/RMT0P                      | Current Channel A Positive Input, Remote Channel 0 Positive Input                                                                                                                                 |

| 37               | 39               | IAN/RMTON                      | Current Channel A Negative Input, Remote Channel 0 Negative Input                                                                                                                                 |

| 38               | 40               | IBP/RMT1P                      | Current Channel B Positive Input, Remote Channel 1 Positive Input                                                                                                                                 |

| 39               | 41               | IBN/RTM1N                      | Current Channel B Negative Input, Remote Channel 1 Negative Input                                                                                                                                 |

| 40               | _                | ICP/RMT2P                      | Current Channel C Positive Input, Remote Channel 2 Positive Input                                                                                                                                 |

| 41               | _                | ICN/RMT2N                      | Current Channel C Negative Input, Remote Channel 2 Negative Input                                                                                                                                 |

| 42               | 42               | V <sub>3P3SYS</sub>            | Primary Power Input for Digital Sections of the Device.                                                                                                                                           |

| 43               | 43               | GNDA                           | Analog Ground                                                                                                                                                                                     |

| 44               | 44               | V <sub>3P3A</sub>              | Primary Power Input for the Analog Section of the Device.                                                                                                                                         |

| 45               | _                | VD/INP                         | Single-Ended Analog Input/Neutral Current Channel Input (Single-Ended)                                                                                                                            |

| 46               | 49               | VA                             | Voltage Channel A Input                                                                                                                                                                           |

| 47               | 47               | VB                             | Voltage Channel B Input                                                                                                                                                                           |

| 48               | 48               | GNDA                           | Analog Ground                                                                                                                                                                                     |

| 49               | 46               | V <sub>C</sub>                 | Voltage Channel C Input                                                                                                                                                                           |

| 50               | 50               | VBAT                           | Battery Power (V <sub>BAT</sub> ). This pin provides both primary battery power during BRN mode and secondary battery power for SLP mode (RTC/NVRAM). It supports the NVRAM in BRN and SLP modes. |

| 51               | 51               | XOUT                           | Crystal Oscillator Output. Connect to either a 32,768kHz tuning fork crystal or to a 16MHz AT-cut microprocessor crystal.                                                                         |

| 52               | 52               | XIN                            | Crystal Oscillator Input. Connect to a 32.768kHz tuning fork crystal or to a 16MHz AT-cut microprocessor crystal.                                                                                 |

| 53               | 53               | V <sub>3P3RTC</sub>            | Bypass Point for RTC Power Supply Rail                                                                                                                                                            |

| 54               | 54               | RSTN                           | Device Reset                                                                                                                                                                                      |

| 55               | 55               | V <sub>DD_CAL</sub>            | RTC Calibration Bypass                                                                                                                                                                            |

| 56               | 56               | P1.15/INT6/<br>PU_WAKE5        | GPIO Port 1 Bit 15, External Interrupt 6, Edge-Triggered WAKE 5                                                                                                                                   |

| 57               | 57               | P1.14/INT5/<br>PU_WAKE4        | GPIO Port 1 Bit 14, External Interrupt 5, Edge-Triggered WAKE 4                                                                                                                                   |

| 58               | 58               | P1.13/YPULSE/<br>INT4          | GPIO Port 1 Bit 13, Meter Pulse Y, External Interrupt 4                                                                                                                                           |

| 59               | 59               | P1.14/XPULSE/<br>INT3          | GPIO Port 1 Bit 14, Meter Pulse X, External Interrupt 3                                                                                                                                           |

| 60               | 60               | TMUX1/SEG35                    | Test Multiplexer Output 1, LCD Segment 35                                                                                                                                                         |

| 61               | 61               | TMUX0/SEG34                    | Test Multiplexer Output 0, LCD Segment 34                                                                                                                                                         |

| 62               | 62               | P1.9/SEG31                     | GPIO Port 1 Bit 9, LCD Segment 31                                                                                                                                                                 |

| 63               | 63               | P1.8/SEG30                     | GPIO Port 1 Bit 8, LCD Segment 30                                                                                                                                                                 |

| 64               | 64               | P1.7/SEG29                     | GPIO Port 1 Bit 7, LCD Segment 29                                                                                                                                                                 |

| 65               | 65               | P1.6/SEG28                     | GPIO Port 1 Bit 6, LCD Segment 28                                                                                                                                                                 |

| 66               | 66               | P1.5/SEG27                     | GPIO Port 1 Bit 5, LCD Segment 27                                                                                                                                                                 |

| 67               | 67               | P1.4/SEG26                     | GPIO Port 1 Bit 4, LCD Segment 26                                                                                                                                                                 |

| 68               | 68               | GNDD                           | Digital Ground                                                                                                                                                                                    |

# Simplified Block Diagram

## **Recommended Operating Conditions**

| PARAMETER                                             | CONDITIONS                                                     | MIN  | MAX | UNIT |

|-------------------------------------------------------|----------------------------------------------------------------|------|-----|------|

| V3P3SYS, V3P3A Supply Voltage—Mission Mode*           | $V_{BAT} = 0V \text{ to } 3.8V$                                | 3.0  | 3.6 | V    |

| VBAT Voltage—BRN Mode                                 | V <sub>3PSYS</sub> < 2.8V,<br>V <sub>3P3SYS</sub> (max) > 2.0V | 2.5  | 3.8 | V    |

| $V_{BAT}$ Voltage to maintain RTC and NV RAM—SLP Mode | V3P3SYS < 2.0V                                                 | 2.0  | 3.8 | V    |

| V <sub>3P3SYS</sub> Slew Rate                         |                                                                | -0.1 | 0.1 | V/ms |

| Operating Temperature                                 |                                                                | -40  | +85 | °C   |

$V_{3P3SYS}$  and  $V_{3P3A}$  pins must be tied together.

# **Detailed Description**

### Hardware Overview

The SY7M166H (ZON P3SX) poly-phase and SY7M163G (ZON M3SX) single-phase electricity meter SOCs incorporate a 32-bit MAXQ30 microcontroller core, delivering approximately one MIPS/MHz of clock (nominally, 19.66MHz), a 32-bit dedicated metrology Compute Engine, high-precision ADCs, multichannel metrology AFE, interfaces for remote sensors, and a complete set of peripherals onto a single device. The devices are available in a 68-pin QFN package.

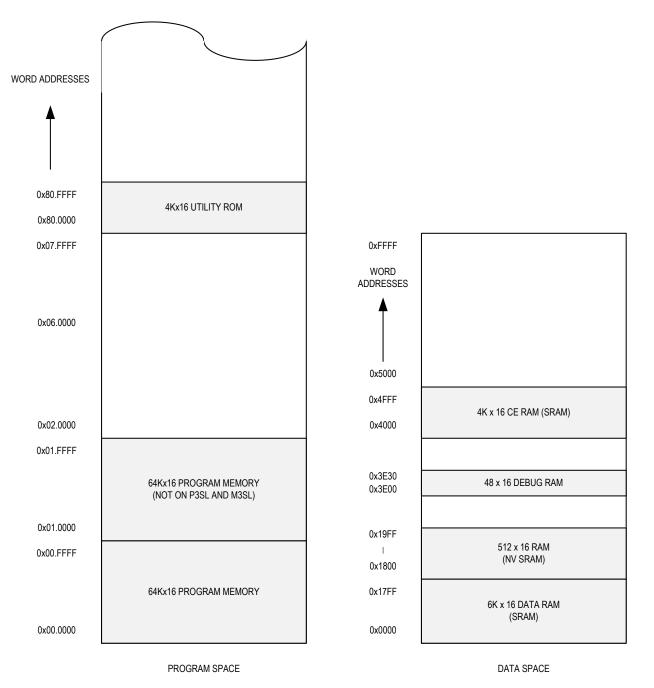

The devices integrate four high-precision 24-bit deltasigma ADCs for measuring three current channels (ADC0, ADC1, ADC2, differential inputs) and three voltage channels (ADC3, single-ended multiplexed inputs). A fixedpoint Compute Engine (CE) processes the ADC samples. The code for the CE resides in RAM and is shared with the MAXQ30 Core.

The devices also contain two (three for polyphase) remote interfaces capable of supporting up to four (six for polyphase) metrology channels. Typically, these channels are assigned to measure the primary parameters of interest, such as line voltage, line current, and neutral current, plus any other analog signal of interest. The remote channels are self-contained and provide inherent isolation to protect the devices from line potentials. In the current channels, select any sensor including current transformers, shunts, or Rogowski coils

The devices are clocked by one 32,768Hz tuning-fork- type crystal that is used as a reference for the RTC. A phase-locked loop multiplies this clock to provide the 19.66MHz required by the core, the 19.66MHz required by the CE, and other clocks required by the system.

In a typical application, the CE of the devices processes the samples from its metrology input channels and per- forms calculations to measure real energy and reactive energy, as well as volt-ampere hours, A<sup>2</sup>h, and V<sup>2</sup>h for four-quadrant metering. These measurements are then accessed by the MAXQ30 Core, processed further, and output using the peripheral devices available to the MPU.

The devices feature a real-time clock to record time-of- use (TOU) metering information for multi-rate applications, and to time-stamp tamper or other events.

The devices include a precision voltage reference. A temperature-correction mechanism guarantees conformance to accuracy standards over temperature. Temperaturedependent external components such as crystal oscillator, current transformers and their corresponding signalconditioning circuits, can be characterized, with their correction factors programmed to produce electricity meters with exceptional accuracy over the industrial temperature range.

The device has one pin that is configurable as touch-detect input. When configured for touch detect, the pin self-oscillates at a frequency dependent on the capacitive load on the pin. A low-power timer circuit measures the oscillation frequency and alerts the MAXQ32 MPU core when the frequency falls below a certain threshold (indicating an increase in the capacitive loading). If desired, this input can wake the MAXQ32 MPU core.

The devices have one UART channel with independent baud-rate generator. This UART channel can connect to driver/receiver chips for RS-232 or, with an additional GPIO pin for transmit enable, for RS-422/RS-485

The devices include one port for a smart card for prepay metering applications. In many applications, the pins can connect directly to the smart card socket. It is also possible to use external transceivers to achieve full ISO 7816 compliance.

The devices include standard peripherals for interfacing serial memory devices and complex display subsystems, among other devices. These devices include one SPI port and one  $I^{2}C$  port.

The devices contain the essential security accelerators for fast and secure data encryption, decryption, and authentication. The true random number generator (TRNG) generates a FIPSx-compliant random number in x1 clock cycles. The AES engine supports three key lengths: 128 bits, 192 bits, and 256 bits. It completes encryption in 2x clock cycles and decryption 3x clock cycles. The AES- GCM supports 128-bits mode only.

### **Analog Front End**

The devices contain three staring delta-sigma ADC converters and one delta-sigma ADC converter that can be configured to multiplex up to four inputs. In a typical polyphase meter application, the three staring converters monitor line current and the fourth multiplexed converter monitors the three line voltages with neutral current. In a single-phase meter application, the three staring converters monitor line current and line voltage. Three ADCs contain preamplifiers that provide a gain of 1, 4, 8, or 16, as required.

Analog inputs sample at up to 5MHz. The samples decimate in a FIR filter with an oversampling ratio of up to 512. Finished samples are available to the CE at up to 10.92ksps per channel.

Inputs to the ADC channels are referenced to AGND and must be scaled so that the signal is no greater than  $250 \text{mV}_{PK}$  above or below AGND.

### Metering

The devices contain two separate metrology subsystems. In the poly-phase devices, the first subsystem is a set of four DC modulators and associated decimation filters. These four modulators are typically configured to monitor line current, with the fourth modulator responsible for monitoring the three voltage channels, or other conditions, such as temperature or a magnetic sensor for tamper detection. The second subsystem consists of three remote interfaces that interface to Silergy's remote sensors. These remote sensors can be configured to measure line currents using current shunts rather than transformers or Rogowski coils, with isolation possible in both the measurement channels and the power circuit provided by inexpensive pulse transformers

The analog section of the devices consists of four analogto-digital converters:

**ADC0:** Dedicated to current channel A (line current). An optional preamplifier can be inserted into the circuit for additional gain.

**ADC1:** Dedicated to current channel B (line current). An optional preamplifier can be inserted into the circuit for additional gain.

**ADC2:** Dedicated to current channel C (line current). An optional preamplifier can be inserted into the circuit for additional gain.

**ADC3:** Can be configured to multiplex among the three voltage inputs, VA, VB, VC, or IN.

### **Remote Channels**