eMCP Specification

# **Embedded MCP specification**

# P6408T2B5X2

Datasheet Preliminary Ver 1.0

Apollo Memory System Company

1

# <Product Specification>

# -Compatible Approved Vendor List-

| Chipset AVL           |                  | Chipset Mod          | lel                            | eMCP PN              |

|-----------------------|------------------|----------------------|--------------------------------|----------------------|

| Mediatek              |                  | MT6582               |                                | 08EMCP08-EL2BV100    |

| ompatible AVL upc     | lated by 2014,Q4 | 1                    |                                |                      |

|                       |                  |                      |                                |                      |

| e Summary             | -:               |                      |                                |                      |

| e Summary             |                  | e 1 – Device         | e Summary                      |                      |

| Product<br>art number |                  | e 1 – Device<br>DRAM | Summary<br>CH & CS<br>For DRAM | Operating<br>voltage |

# -System Performance

|             | Table 2 – e•MMC <sup>™</sup> Device Performance         Typical value |   |  |  |  |

|-------------|-----------------------------------------------------------------------|---|--|--|--|

|             | Read Sequential (MB/s) Write Sequential (MB/s)                        |   |  |  |  |

| P6408T2B5X2 | 70                                                                    | 4 |  |  |  |

Note 2: Performance numbers might be subject to changes without notice.

# eMCP Specification

# < Embedded MMC<sup>™</sup> - NAND>

- Packaged NAND flash memory with *e*•MMC<sup>™</sup> 5.0 interface

- Compliant with *e*•MMC<sup>™</sup> Specification Ver.4.4, 4.41,4.5&5.0

- Supports three different data bus widths : 1 bit(default), 4 bits, 8 bits

- Data transfer rate: up to 52Mbyte/s (using 8 parallel data lines at 52 MHz)

- Single data rate : up to 200Mbyte/s @ HS200(Host clock @ 200MHz)

- Dual data rate : up to 104Mbyte/s @ 52MHz

- Enhanced Write Protection with Permanent and Partial protection options

- Supports Multiple User Data Partition with Enhanced User Data Area options

- Supports Background Operations & High Priority Interrupt (HPI)

- Error free memory access

- Internal error correction code (ECC) to protect data communication

- Internal enhanced data management algorithm

- Solid protection of sudden power failure safe-update operations for data content

- Security

- Support secure bad block erase commands

- Enhanced write Protection with permanent and partial protection options

- Supports Field Firmware Update(FFU)

- Enhanced Device Life time

- Optimal Size

- Supports Production State Awareness

- Supports Power Off Notification for Sleep

#### <Low power DDR2>

- Density: 4Gbits

- Organization

- × 32 bits: 16M words × 32 bits × 8 banks

- Row Address: R0 ~ R13

- Column Address: C0 ~ C9

- Power supply

- VDD1 = 1.70V to 1.95V ,VDD2, VDDQ = 1.14V to 1.30V

- Data rate: 1066Mbps max. (RL = 8)

- Interface: HSUL 12

- Burst lengths (BL): 4, 8, 16

- Burst type (BT)

- Sequential (4, 8, 16)

- Interleave (4, 8)

- Read latency (RL): 5, 6, 7, 8

- Refresh cycles: 8192 cycles/28ms

- Average refresh period: 3.4µs

- Storage temperature range: -40°C to +110°C

- Operating junction temperature range TJ = -15°C to +80°C

# 1. e•MMC<sup>™</sup> Device and System

# 1.1. e•MMC<sup>™</sup> System Overview

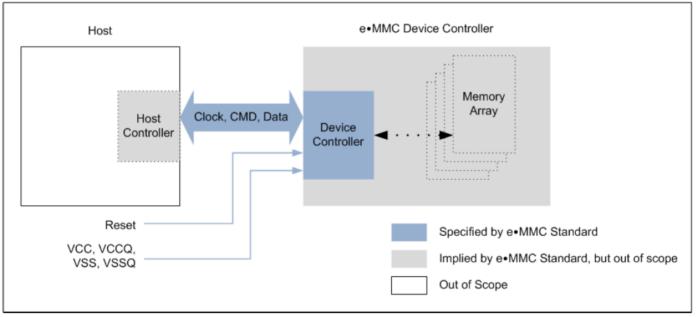

The  $e \cdot MMC^{\mathbb{M}}$  specification covers the behavior of the interface and the Device controller. As part of this specification the existence of a host controller and a memory storage array are implied but the operation of these pieces is not fully specified.

The Apollo NAND Device contains a single chip MMC controller and NAND flash memory module. The micro-controller interfaces with a host system allowing data to be written to and read from the NAND flash memory module. The controller allows the host to be independent from details of erasing and programming the flash memory.

Figure  $1 - e \bullet MMC^{T}$  System Overview

4

#### 1.2. e•MMC<sup>™</sup> Device Overview

The *e*•MMC<sup>™</sup> device transfers data via a configurable number of data bus signals. The communication signals are:

#### 1.2.1 Clock (CLK)

Each cycle of this signal directs a one bit transfer on the command and either a one bit (1x) or a two bits transfer (2x) on all the data lines. The frequency may vary between zero and the maximum clock frequency.

#### 1.2.2 Command (CMD)

This signal is a bidirectional command channel used for Device initialization and transfer of commands. The CMD signal has two operation modes: open-drain for initialization mode, and push-pull for fast command transfer. Commands are sent from the  $e \cdot \text{MMC}^{\text{T}}$  host controller to the  $e \cdot \text{MMC}^{\text{T}}$  Device and responses are sent from the Device to the host.

#### 1.2.3 Input/Outputs (DAT0-DAT7)

These are bidirectional data channels. The DAT signals operate in push-pull mode. Only the Device or the host is driving these signals at a time. By default, after power up or reset, only DATO is used for data transfer. A wider data bus can be configured for data transfer, using either DAT0-DAT3 or DAT0-DAT7, by the  $e \bullet MMC^{\text{TM}}$  host controller. The  $e \bullet MMC^{\text{TM}}$  Device includes internal pull-ups for data lines DAT1-DAT7. Immediately after entering the 4-bit mode, the Device disconnects the internal pull ups of lines DAT1, DAT2, and DAT3. Correspondingly, immediately after entering to the 8-bit mode the Device disconnects the internal pull-ups of lines DAT1-DAT7. The signals on the  $e \bullet MMC^{\text{TM}}$  interface are described in Table 3.

| Table 3 – <i>e</i> •MMC Interface |                                                   |                                                                |  |  |

|-----------------------------------|---------------------------------------------------|----------------------------------------------------------------|--|--|

| Name                              | Type <sup>1</sup>                                 | Description                                                    |  |  |

| CLK                               | 1                                                 | Clock                                                          |  |  |

| DAT0                              | I/O/PP                                            | Data                                                           |  |  |

| DAT1                              | I/O/PP                                            | Data                                                           |  |  |

| DAT2                              | I/O/PP                                            | Data                                                           |  |  |

| DAT3                              | I/O/PP                                            | Data                                                           |  |  |

| DAT4                              | I/O/PP                                            | Data                                                           |  |  |

| DAT5                              | I/O/PP                                            | Data                                                           |  |  |

| DAT6                              | I/O/PP                                            | Data                                                           |  |  |

| DAT7                              | I/O/PP                                            | Data                                                           |  |  |

| CMD                               | I/O/PP/OD                                         | Command/Response                                               |  |  |

| RST_n                             | I                                                 | Hardware reset                                                 |  |  |

| VCC                               | S                                                 | Supply voltage for Core                                        |  |  |

| VCCQ                              | S                                                 | Supply voltage for I/O                                         |  |  |

| VSS                               | S                                                 | Supply voltage ground for Core                                 |  |  |

| VSSQ                              | S                                                 | Supply voltage ground for I/O                                  |  |  |

| Note1 : I: input; O               | : output; <b>PP</b> : push-pull; <b>OD</b> : open | n-drain; NC: Not connected (or logical high); S: power supply. |  |  |

Table 3 – *e*•MMC<sup>™</sup> Interface

Each Device has a set of information registers (see also 0, Device Registers.)

| Name    | Width<br>(bytes) | Description                                                                                                                       | Implementation |

|---------|------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------|

| CID     | 16               | Device Identification number, an individual number for identification.                                                            | Mandatory      |

| RCA     | 2                | Relative Device Address, is the Device system address, dynamically assigned by the host during initialization.                    | Mandatory      |

| DSR     | 2                | Driver Stage Register, to configure the Device's output drivers.                                                                  | Optional       |

| CSD     | 16               | Device Specific Data, information about the Device operation conditions.                                                          | Mandatory      |

| OCR     | 4                | Operation Conditions Register. Used by a special broadcast command to identify the voltage type of the Device.                    | Mandatory      |

| EXT_CSD | 512              | Extended Device Specific Data. Contains information about the Device capabilities and selected modes. Introduced in standard v4.0 | Mandatory      |

# Table 4 – $e \bullet MMC^{T}$ Registers

The host may reset the device by:

- Switching the power supply off and back on. The device shall have its own power-on detection circuitry which puts the device into a defined state after the power-on Device.

- A reset signal

- By sending a special command

# 1.3. Bus Speed Modes

$e \bullet \mathsf{MMC}^{\mathsf{T}}$  defines several bus speed modes. **Table 5** summarizes the various modes.

| Table 5— Bus Speed Modes                           |           |            |           |           |                                             |  |  |

|----------------------------------------------------|-----------|------------|-----------|-----------|---------------------------------------------|--|--|

| Mode Name                                          | Data Rate | IO Voltage | Bus Width | Frequency | Max Data Transfer (implies<br>x8 bus width) |  |  |

| Backwards<br>Compatibility with<br>legacy MMC card | Single    | 3.3/1.8V   | 1, 4, 8   | 0-26MHz   | 26MB/s                                      |  |  |

| High Speed SDR                                     | Single    | 3.3/1.8V   | 4, 8      | 0-52MHz   | 52MB/s                                      |  |  |

| High Speed DDR                                     | Dual      | 3.3/1.8V   | 4, 8      | 0-52MHz   | 104MB/s                                     |  |  |

| HS200                                              | Single    | 1.8V       | 4, 8      | 0-200MHz  | 200MB/s                                     |  |  |

### Table 5— Bus Speed Modes

#### 1.3.1 HS200 Bus Speed Mode

The HS200 mode offers the following features:

- SDR Data sampling method

- CLK frequency up to 200MHz Data rate up to 200MB/s

- 8-bits bus width supported

- Single ended signaling with 4 selectable Drive Strength

- Signaling levels of 1.8V

- Tuning concept for Read Operations

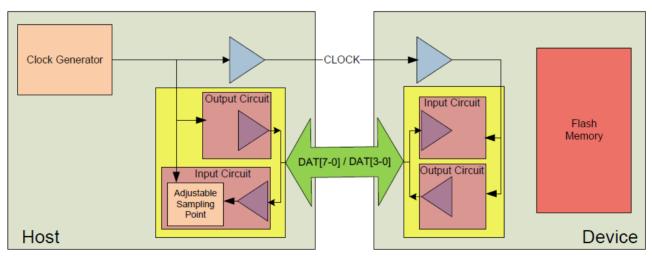

#### 1.3.2 HS200 System Block Diagram

Figure 2 shows a typical HS200 Host and Device system. The host has a clock generator, which supplies CLK to the Device. For write operations, clock and data direction are the same, write data can be transferred synchronous with CLK, regardless of transmission line delay. For read operations, clock and data direction are opposite; the read data received by Host is delayed by round-trip delay, output delay and latency of Host and Device. For reads, the Host needs to have an adjustable sampling point to reliably receive the incoming data.

# 2. e•MMC<sup>™</sup> Functional Description

# 2.1 e•MMC<sup>™</sup> Overview

All communication between host and device are controlled by the host (master). The host sends a command, which results in a device response. For more details, refer to section 6.1 of the JEDEC Standard Specification No.JESD84-B50.

Five operation modes are defined for the  $e \bullet MMC^{T}$  system (hosts and devices):

- Boot mode

- Device identification mode

- Interrupt mode

- Data transfer mode

- Inactive mode

# 2.2 Boot Operation Mode

In boot operation mode, the master ( $e \bullet MMC^{T}$  host) can read boot data from the slave ( $e \bullet MMC^{T}$  device) by keeping CMD line low or sending CMD0 with argument + 0xFFFFFFA, before issuing CMD1. The data can be read from either boot area or user area depending on register setting. For more details, refer to section 6.3 of the JEDEC Standard Specification No.JESD84-B50.

# 2.3 Device Identification Mode

While in device identification mode the host resets the device , validates operation voltage range and access mode, identifies the device and assigns a Relative device Address (RCA) to the device on the bus. All data communication in the Device Identification Mode uses the command line (CMD) only. For more details, refer to section 6.4 of the JEDEC Standard Specification No.JESD84-B50.

# 2.4 Interrupt Mode

The interrupt mode on the  $e \cdot MMC^{T}$  system enables the master ( $e \cdot MMC^{T}$  host) to grant the transmission allowance to the slaves (Device) simultaneously. This mode reduces the polling load for the host and hence, the power consumption of the system, while maintaining adequate responsiveness of the host to a Device request for service. Supporting  $e \cdot MMC^{T}$  interrupt mode is an option, both for the host and the Device. For more details, refer to section 6.5 of the JEDEC Standard Specification No.JESD84-B50.

# 2.5 Data Transfer Mode

When the Device is in *Stand-by* State, communication over the CMD and DAT lines will be performed in push-pull mode. For more details, refer to section 6.6 of the JEDEC Standard Specification No.JESD84-B50.

# 2.6 Inactive Mode

The device will enter inactive mode if either the device operating voltage range or access mode is not valid. The device can also enter inactive mode with GO\_INACTIVE\_STATE command (CMD15). The device will reset to *Pre-idle* state with power cycle. For more details, refer to section 6.1 of the JEDEC Standard Specification No.JESD84-B50.

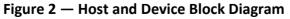

### 2.7 H/W Reset Operation

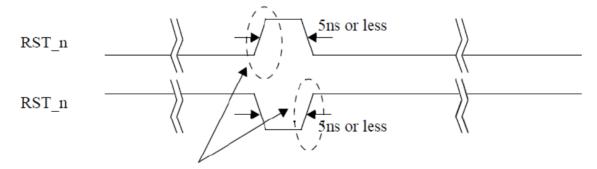

Note1: Device will detect the rising edge of RST\_n signal to trigger internal reset sequence

#### Figure 3 – H/W Reset Waveform

#### Table 6 – H/W Reset Timing Parameters

| Symbol         | Comment                                     | Min              | Max             | Unit    |

|----------------|---------------------------------------------|------------------|-----------------|---------|

| tRSTW          | RST_n pulse width                           | 1                |                 | [us]    |

| tRSCA          | RST_n to Command time                       | 200 <sup>1</sup> |                 | [us]    |

| tRSTH          | RST_n high period (interval time)           | 1                |                 | [us]    |

| Note1 : 74 cyc | les of clock signal required before issuing | CMD1 or CMD0 w   | ith argument Ox | FFFFFFA |

# 2.8 Noise Filtering Timing for H/W Reset

Device must filter out 5ns or less pulse width for noise immunity

Device must not detect these rising edge

#### Figure 4 – Noise Filtering Timing for H/W Reset

Device must not detect 5ns or less of positive or negative RST\_n pulse. Device must detect more than or equal to 1us of positive or negative RST\_n pulse width.

9

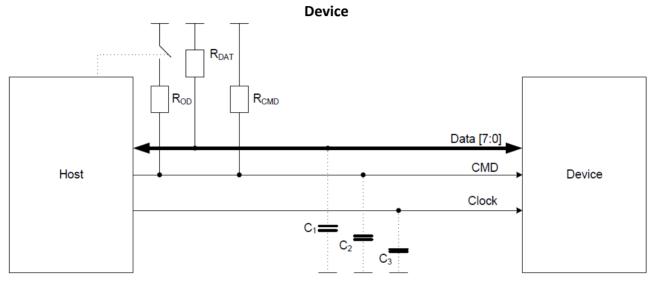

# 3. The e•MMC<sup>™</sup> bus

The  $e \bullet MMC^{\text{\tiny M}}$  bus has ten communication lines and three supply lines:

- **CMD**: Command is a bidirectional signal. The host and Device drivers are operating in two modes, open drain and push/pull.

- DAT0-7 : Data lines are bidirectional signals. Host and Device drivers are operating in push-pull mode

- CLK: Clock is a host to Device signal. CLK operates in push-pull mode

Figure 5 – Bus Circuitry Diagram

The  $R_{OD}$  is switched on and off by the host synchronously to the open-drain and push-pull mode transitions. The host does not have to have open drain drivers, but must recognize this mode to switch on the  $R_{OD}$ .  $R_{DAT}$  and  $R_{CMD}$  are pull-up resistors protecting the CMD and the DAT lines against bus floating device when all device drivers are in a high-impedance mode.

A constant current source can replace the  $R_{OD}$  by achieving a better performance (constant slopes for the signal rising and falling edges). If the host does not allow the switchable  $R_{OD}$  implementation, a fixed  $R_{CMD}$  can be used).

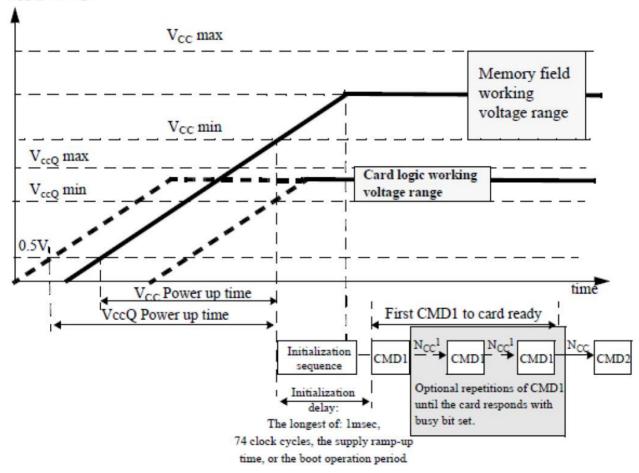

#### 3.1. Power-up

#### 3.1.1 e•MMC<sup>™</sup> power-up

An  $e \cdot \text{MMC}^{\text{M}}$  bus power-up is handled locally in each device and in the bus master. Figure 6 shows the power-up sequence and is followed by specific instructions regarding the power-up sequence. Refer to section 10.1 of the JEDEC Standard Specification No.JESD84-B50 for specific instructions regarding the power-up sequence.

Supply voltage

Figure 6 –  $e \bullet MMC^{T}$  Power-up Diagram

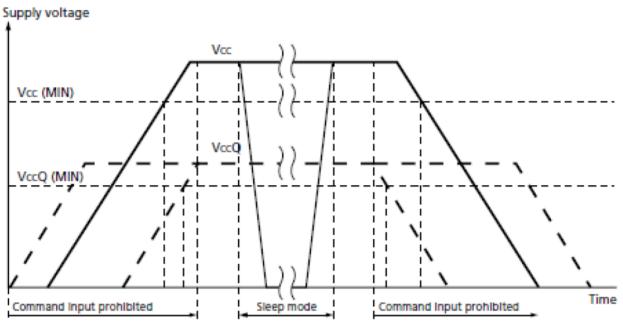

#### 3.1.2 *e*•*MMC*<sup>™</sup> Power Cycling

The master can execute any sequence of  $V_{CC}$  and  $V_{CCQ}$  power-up/power-down. However, the master must not issue any commands until  $V_{CC}$  and  $V_{CCQ}$  are stable within each operating voltage range. After the slave enters sleep mode, the master can power-down  $V_{CC}$  to reduce power consumption. It is necessary for the slave to be ramped up to  $V_{CC}$  before the host issues CMD5 (SLEEP\_AWAKE) to wake the slave unit. For more information about power cycling see Section 10.1.3 of the JEDEC Standard Specification No.JESD84-B50.

Figure 7 – The  $e \bullet MMC^{\text{TM}}$  Power Cycle

### 3.1.3 Bus Operating Conditions

| Parameter                                                                                              | Symbol | Min  | Max.          | Unit | Remark |

|--------------------------------------------------------------------------------------------------------|--------|------|---------------|------|--------|

| Peak voltage on all lines                                                                              |        | -0.5 | VCCQ +<br>0.5 | V    |        |

| All Inputs                                                                                             |        |      |               |      |        |

| Input Leakage Current (before initialization sequence and/or the internal pull up resistors connected) |        | -100 | 100           | μΑ   |        |

| Input Leakage Current (after initialization sequence and the internal pull up resistors disconnected)  |        | -2   | 2             | μA   |        |

| All Outputs                                                                                            |        |      |               |      |        |

| Output Leakage Current (before initialization sequence)                                                |        | -100 | 100           | μΑ   |        |

| Output Leakage Current (after initialization sequence)                                                 |        | -2   | 2             | μΑ   |        |

| Note1 : Initialization sequence is defined in section 10.1                                             |        |      |               |      |        |

#### **Table 7 – General Operating Conditions**

#### 3.1.4 Power supply: e•MMC<sup>™</sup>

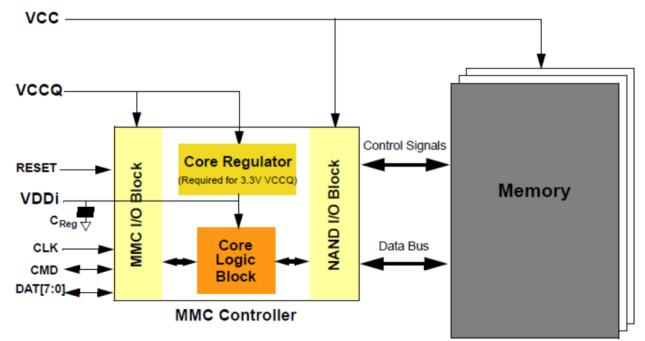

In the  $e \bullet MMC^{\text{T}}$ ,  $V_{CC}$  is used for the NAND flash device and its interface voltage;  $V_{CCQ}$  is for the controller and the MMC interface voltage shown in Figure 8. The core regulator is optional and only required when internal core logic voltage is regulated from  $V_{CCQ}$ . A  $C_{Reg}$  capacitor must be connected to the  $V_{Ddi}$  terminal to stabilize regulator output on the system.

Figure 8 – *e*•MMC<sup>™</sup> Internal Power Diagram

# 3.1.5 *e*•MMC<sup>™</sup> Power Supply Voltage

The  $e \bullet MMC^{\text{TM}}$  supports one or more combinations of VCC and VCCQ as shown in Table 8. The VCCQ must be defined at equal to or less than VCC. The available voltage configuration is shown in Table 9.

| Table 8 – $e$ •MINIC Power Supply Voltage |                                            |                                                                                                                                   |                                                                                                                                                                                                                      |                                                          |  |

|-------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|

| Symbol                                    | MIN                                        | MAX                                                                                                                               | Unit                                                                                                                                                                                                                 | Remarks                                                  |  |

| VCC                                       | 2.7                                        | 3.6                                                                                                                               | V                                                                                                                                                                                                                    |                                                          |  |

|                                           | 2.7                                        | 3.6                                                                                                                               | V                                                                                                                                                                                                                    |                                                          |  |

| VCCQ                                      | 1.65                                       | 1.95                                                                                                                              | V                                                                                                                                                                                                                    |                                                          |  |

| t <sub>PRUH</sub>                         |                                            | 35                                                                                                                                | ms                                                                                                                                                                                                                   |                                                          |  |

| t <sub>PRUL</sub>                         |                                            | 25                                                                                                                                | ms                                                                                                                                                                                                                   |                                                          |  |

|                                           | Symbol<br>VCC<br>VCCQ<br>t <sub>PRUH</sub> | Symbol         MIN           VCC         2.7           VCCQ         2.7           VCCQ         1.65           t <sub>PRUH</sub> t | $\begin{tabular}{ c c c c c c } \hline Symbol & MIN & MAX \\ \hline VCC & 2.7 & 3.6 \\ \hline VCCQ & \hline 2.7 & 3.6 \\ \hline 1.65 & 1.95 \\ \hline t_{PRUH} & 35 \\ \hline t_{PRUH} & 35 \\ \hline \end{tabular}$ | $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$ |  |

# Table 8 – $e \bullet MMC^{T}$ Power Supply Voltage

The  $e \bullet MMC^{\text{M}}$  must support at least one of the valid voltage configurations, and can optionally support all valid voltage configurations (see Table 9).

|                                                                     |           | e mine voltage combination | 5110                   |  |  |  |

|---------------------------------------------------------------------|-----------|----------------------------|------------------------|--|--|--|

|                                                                     | -         | Vcc                        | 2                      |  |  |  |

|                                                                     |           | 1.65V-1.95V                | 2.7V-3.6V <sup>1</sup> |  |  |  |

| Vcc                                                                 | 2.7V-3.6V | Valid                      | Valid                  |  |  |  |

| Note1 : VccQ (I/O) 3.3 volt range is not supported in HS200 devices |           |                            |                        |  |  |  |

# Table 9 – *e*•MMC<sup>™</sup> Voltage Combinations

# eMCP Specification

#### 3.1.6 Bus Signal Line Load

The total capacitance  $C_L$  of each line of the  $e \bullet MMC^{\text{TM}}$  bus is the sum of the bus master capacitance  $C_{HOST}$ , the bus capacitance  $C_{BUS}$  itself, and the capacitance  $C_{DEVICE}$  of the Device connected to this line,

$C_{L} = C_{HOST} + C_{BUS} + C_{DEVICE}$

and requiring the sum of the host and bus capacitances not to exceed 20 pF (see Table 10).

#### Parameter Symbol Min Max Unit Remark Pull-up resistance for CMD 4.7 R<sub>CMD</sub> 50 Kohm to prevent bus floating Pull-up resistance for DAT0-7 10 50 Kohm to prevent bus floating $R_{DAT}$ It is not necessary to put pull-up resistance on RST n (H/W rest) line 50 Kohm Pull-up resistance for RST\_n 4.7 R<sub>RST</sub> n if host does not use H/W reset. (Extended CSD register [162] = 0 b ) Single Device Bus signal line capacitance CL 30 рF $C_{BGA}$ 12 Single Device capacitance рF Maximum signal line inductance 16 nH Impedance on CLK / CMD / 45 55 ohm Impedance match DAT0~7 0 Serial's resistance on CLK line 47 ohm SR<sub>CLK</sub> Serial's resistance on CMD / **SR**<sub>CMD</sub> 0 47 ohm DAT0~7 line SR<sub>DAT0~7</sub> It should be located as close as possible to the 2.2+0.1 4.7+0.22 balls defined in order to minimize connection parasitics CH1 should be placed adjacent to VccQ-VssQ balls VccQ decoupling capacitor μF (#K6 and #K4 accordingly, next to DAT [7..0] CH1 1 2.2 balls), It should be located as close as possible to the balls defined in order to minimize connection parasitics. It should be located as close as possible to the VCC capacitor value 1+0.1 4.7+0.22 μF balls defined in order to minimize connection parasitics To stabilize regulator output to controller core logics. It should be located as close as possible to V<sub>Ddi</sub> capacitor value $C_{REG}$ 1 4.7+0.1 μF the balls defined in order to minimize connection parasitics

#### Table 10 – Capacitance

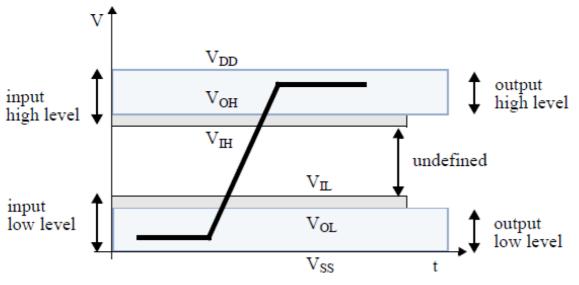

#### 3.1.7 Bus Signal Levels

As the bus can be supplied with a variable supply voltage, all signal levels are related to the supply voltage.

Figure 9 – Bus Signal Levels

#### 3.1.8 Open-drain Mode Bus Signal Level

Table 11 – Open-drain Bus Signal Level

| Parameter           | Symbol | Min       | Max. | Unit | Conditions    |

|---------------------|--------|-----------|------|------|---------------|

| Output HIGH voltage | VOH    | VDD - 0.2 |      | V    | IOH = -100 μA |

| Output LOW voltage  | VOL    |           | 0.3  | V    | IOL = 2 mA    |

The input levels are identical with the push-pull mode bus signal levels.

# 3.1.9 Push-pull mode bus signal level— $e \bullet MMC^{T}$

The device input and output voltages shall be within the following specified ranges for any  $V_{DD}$  of the allowed voltage range

For 2.7V-3.6V V<sub>CCQ</sub> range (compatible with JESD8C.01)

| Table 12 – Push- | pull Signal Level— | ∙High-voltage <i>e</i> •MMC <sup>™</sup> |

|------------------|--------------------|------------------------------------------|

|                  |                    |                                          |

|                     |        | 1 0          | 0            | 0    |                          |

|---------------------|--------|--------------|--------------|------|--------------------------|

| Parameter           | Symbol | Min          | Max.         | Unit | Conditions               |

| Output HIGH voltage | VOH    | 0.75 * VCCQ  |              | V    | IOH = -100 μA @ VCCQ min |

| Output LOW voltage  | VOL    |              | 0.125 * VCCQ | V    | IOL = 100 μA @ VCCQ min  |

| Input HIGH voltage  | VIH    | 0.625 * VCCQ | VCCQ + 0.3   | V    |                          |

| Input LOW voltage   | VIL    | VSS – 0.3    | 0.25 * VCCQ  | V    |                          |

For 1.65V – 1.95V VCCQ range (: Compatible with EIA/JEDEC Standard "EIA/JESD8-7 Normal Range" as defined in the following table.

|                              | Table 15 – Push-pull Signal Level – 1.65-1.95 VCCQ Voltage Range            |                                      |                        |   |            |  |  |  |  |  |

|------------------------------|-----------------------------------------------------------------------------|--------------------------------------|------------------------|---|------------|--|--|--|--|--|

| Parameter                    | Symbol                                                                      | Min                                  | Max. Unit              |   | Conditions |  |  |  |  |  |

| Output HIGH voltage          | VOH                                                                         | V V <sub>CCQ</sub> – 0.45V           |                        | V | IOH = -2mA |  |  |  |  |  |

| Output LOW voltage           | VOL                                                                         |                                      | 0.45V                  | V | IOL = 2mA  |  |  |  |  |  |

| Input HIGH voltage           | VIH                                                                         | 0.65 * V <sub>CCQ</sub> <sup>1</sup> | V <sub>CCQ</sub> + 0.3 | V |            |  |  |  |  |  |

| Input LOW voltage            | VIL                                                                         | $V_{ss} - 0.3$                       | $0.35 * V_{DD}^{2}$    | V |            |  |  |  |  |  |

| Note1 : 0.7 * $V_{DD}$ for N | Note1 : 0.7 * V <sub>DD</sub> for MMC <sup>™</sup> 4.3 and older revisions. |                                      |                        |   |            |  |  |  |  |  |

| Note2 : 0.3 * $V_{DD}$ for N | /IMC™4.3 and                                                                | d older revisions.                   |                        |   |            |  |  |  |  |  |

# Table 13 – Push-pull Signal Level—1.65-1.95 VCCQ Voltage Range

#### **3.1.10** Bus Operating Conditions for HS200

The bus operating conditions for HS200 devices is the same as specified in sections 10.4.1 of JESD84-B50through 10.4.2 of JESD84-B50. The only exception is that  $V_{CCQ}$ =3.3v is not supported.

#### 3.1.11 Device Output Driver Requirements for HS200

Refer to section 10.4.4 of the JEDEC Standard Specification No.JESD84-B50.

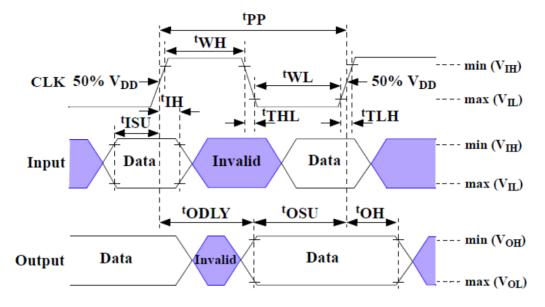

# 3.2. Bus Timing

Data must always be sampled on the rising edge of the clock.

# 3.3. Device Interface Timings

| Table 14 – High-speed Device Interface Timing        |        |     |                 |      |                                 |  |  |  |

|------------------------------------------------------|--------|-----|-----------------|------|---------------------------------|--|--|--|

| Parameter                                            | Symbol | Min | Max.            | Unit | Remark                          |  |  |  |

| Clock CLK <sup>1</sup>                               |        |     |                 |      |                                 |  |  |  |

| Clock frequency Data Transfer Mode (PP) <sup>2</sup> | fPP    | 0   | 52 <sup>3</sup> | MHz  | CL ≤ 30 pF<br>Tolerance:+100KHz |  |  |  |

| Clock frequency Identification Mode (OD)             | fOD    | 0   | 400             | kHz  | Tolerance: +20KHz               |  |  |  |

| Clock high time                                      | tWH    | 6.5 |                 | ns   | $CL \le 30 \text{ pF}$          |  |  |  |

| Clock low time                                       | tWL    | 6.5 |                 | ns   | $CL \le 30 \text{ pF}$          |  |  |  |

| Clock rise time <sup>4</sup>                         | tTLH   |     | 3               | ns   | $CL \le 30 \text{ pF}$          |  |  |  |

| Clock fall time                                      | tTHL   |     | 3               | ns   | $CL \le 30 \text{ pF}$          |  |  |  |

| Inputs CMD, DAT (referenced to CLK)                  |        |     |                 |      |                                 |  |  |  |

| Input set-up time                                    | tISU   | 3   |                 | ns   | $CL \le 30 \text{ pF}$          |  |  |  |

| Input hold time                                      | tIH    | 3   |                 | ns   | $CL \le 30 \text{ pF}$          |  |  |  |

| Outputs CMD, DAT (referenced to CLK)                 |        |     |                 |      |                                 |  |  |  |

| Output delay time during data transfer               | tODLY  |     | 13.7            | ns   | $CL \le 30 \text{ pF}$          |  |  |  |

| Output hold time                                     | tOH    | 2.5 |                 | ns   | $CL \le 30 \text{ pF}$          |  |  |  |

| Signal rise time <sup>5</sup>                        | tRISE  |     | 3               | ns   | $CL \le 30 \text{ pF}$          |  |  |  |

| Signal fall time                                     | tFALL  |     | 3               | ns   | CL ≤ 30 pF                      |  |  |  |

| Note1 · CLK timing is measured at 50% of VI          | חר     |     |                 |      |                                 |  |  |  |

Note1 : CLK timing is measured at 50% of VDD.

Note2 : A  $e \cdot MMC^{TM}$  shall support the full frequency range from 0-26Mhz or 0-52MHz

Note3 : Device can operate as high-speed Device interface timing at 26 MHz clock frequency.

Note4 : CLK rise and fall times are measured by min (VIH) and max (VIL).

Note5 : Inputs CMD DAT rise and fall times are measured by min (VIH) and max (VIL) and outputs CMD DAT rise and fall times are measured by min (VOH) and max (VOL). "

| Table 15 – Backward-compatible Device Interface Timing |        |      |      |      |                        |  |  |  |

|--------------------------------------------------------|--------|------|------|------|------------------------|--|--|--|

| Parameter                                              | Symbol | Min  | Max. | Unit | Remark <sup>1</sup>    |  |  |  |

| Clock CLK <sup>2</sup>                                 |        |      |      |      |                        |  |  |  |

| Clock frequency Data Transfer Mode (PP) <sup>3</sup>   | fPP    | 0    | 26   | MHz  | CL ≤ 30 pF             |  |  |  |

| Clock frequency Identification Mode (OD)               | fOD    | 0    | 400  | kHz  |                        |  |  |  |

| Clock high time                                        | tWH    | 10   |      |      | CL ≤ 30 pF             |  |  |  |

| Clock low time                                         | tWL    | 10   |      | ns   | CL ≤ 30 pF             |  |  |  |

| Clock rise time <sup>4</sup>                           | tTLH   |      | 10   | ns   | CL ≤ 30 pF             |  |  |  |

| Clock fall time                                        | tTHL   |      | 10   | ns   | $CL \le 30 \text{ pF}$ |  |  |  |

| Inputs CMD, DAT (referenced to CLK)                    |        |      |      |      |                        |  |  |  |

| Input set-up time                                      | tISU   | 3    |      | ns   | $CL \le 30 \text{ pF}$ |  |  |  |

| Input hold time                                        | tIH    | 3    |      | ns   | CL ≤ 30 pF             |  |  |  |

| Outputs CMD, DAT (referenced to CLK)                   |        |      |      |      |                        |  |  |  |

| Output set-up time <sup>5</sup>                        | tOSU   | 11.7 |      | ns   | CL ≤ 30 pF             |  |  |  |

| Output hold time <sup>5</sup>                          | tOH    | 8.3  |      | ns   | $CL \le 30 \text{ pF}$ |  |  |  |

Note1: The Device must always start with the backward-compatible interface timing. The timing mode can be switched to high-speed interface timing by the host sending the SWITCH command (CMD6) with the argument for high-speed interface select.

Note2 : CLK timing is measured at 50% of VDD.

Note3 : For compatibility with Devices that support the v4.2 standard or earlier, host should not use > 26 MHz before switching to high-speed interface timing.

Note4 : CLK rise and fall times are measured by min (VIH) and max (VIL).

Note5 : tOSU and tOH are defined as values from clock rising edge. However, there may be Devices or devices which utilize clock falling edge to output data in backward compatibility mode. Therefore, it is recommended for hosts either to settWL value as long as possible within the range which will not go over tCK-tOH(min) in the system or to use slow clock frequency, so that host could have data set up margin for those devices. In this case, each devicewhich utilizes clock falling edge might show the correlation either between tWL and tOSU or between tCK and tOSU for the device in its own datasheet as a note or its application notes.

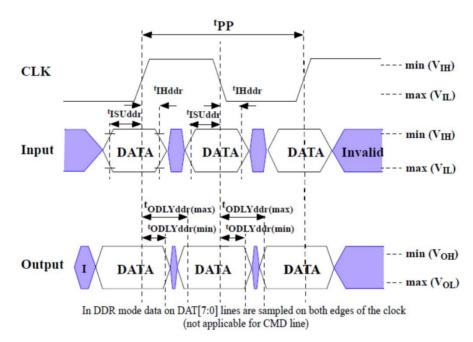

# 3.4. Bus Timing for DAT Signals During Dual Data Rate Operation

These timings applies to the DAT[7:0] signals only when the device is configured for dual data mode operation. In this dual data mode, the DAT signals operates synchronously of both the rising and the falling edges of CLK. The CMD signal still operates synchronously of the rising edge of CLK and therefore complies with the bus timing specified in section 10.5, therefore there is no timing change for the CMD signal.

Figure 11 – Timing Diagram: Data Input/Output in Dual Data Rate Mode

#### 6.1.1 Dual Data Rate Interface Timings

| Table                                          | 16 – High-speed            | – High-speed Dual Data Rate Interface Timing |                              |           |                                 |  |  |

|------------------------------------------------|----------------------------|----------------------------------------------|------------------------------|-----------|---------------------------------|--|--|

| Parameter                                      | Symbol                     | Min                                          | Max.                         | Unit      | Remark                          |  |  |

| Input CLK <sup>1</sup>                         |                            |                                              |                              |           |                                 |  |  |

| Clock duty cycle                               |                            | 45                                           | 55                           | %         | Includes jitter, phase<br>noise |  |  |

| Input DAT (referenced to CLK-DDR mode)         |                            |                                              |                              |           |                                 |  |  |

| Input set-up time                              | tISUddr                    | 2.5                                          |                              | ns        | $CL \le 20 \text{ pF}$          |  |  |

| Input hold time                                | tlHddr                     | 2.5                                          |                              | ns        | $CL \le 20 \text{ pF}$          |  |  |

| Output DAT (referenced to CLK-DDR mode         | )                          |                                              |                              |           |                                 |  |  |

| Output delay time during data transfer         | tODLYddr                   | 1.5                                          | 7                            | ns        | CL ≤ 20 pF                      |  |  |

| Signal rise time (all signals) <sup>2</sup>    | tRISE                      |                                              | 2                            | ns        | CL ≤ 20 pF                      |  |  |

| Signal fall time (all signals)                 | tFALL                      |                                              | 2                            | ns        | CL ≤ 20 pF                      |  |  |

| Note1 : CLK timing is measured at 50% of V     | /DD.                       |                                              |                              |           |                                 |  |  |

| Note2: Inputs CMD, DAT rise and fall time      | s are measured by m        | nin (V <sub>IH</sub> ) and m                 | ax (V <sub>IL</sub> ), and o | utputs CM | D, DAT rise and fall            |  |  |

| times are measured by min (V <sub>OH</sub> ) a | and max (V <sub>oL</sub> ) |                                              |                              |           |                                 |  |  |

# 3.5. Bus Timing Specification in HS200 Mode

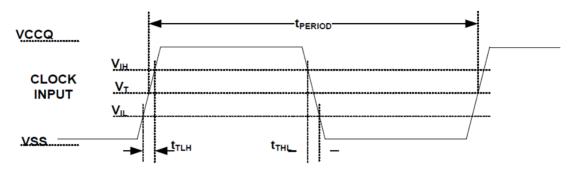

#### 3.5.1 HS200 Clock Timing

Host CLK Timing in HS200 mode shall conform to the timing specified in Figure 12 and **Table 17**. CLK input shall satisfy the clock timing over all possible operation and environment conditions. CLK input parameters should be measured while CMD and DAT lines are stable high or low, as close as possible to the Device.

The maximum frequency of HS200 is 200MHz. Hosts can use any frequency up to the maximum that HS200 mode allows.

Note1 :  $V_{IH}$  denote  $V_{IH}(\text{min.})$  and  $V_{IL}$  denotes  $V_{IL}(\text{max.}).$

Note2 :  $V_T$ =0.975V – Clock Threshold, indicates clock reference point for timing measurements.

#### Figure 12 – HS200 Clock Signal Timing

| Table 17 – HS200 Clock Signal Timing |      |                             |      |                                                                                                                                                                                              |  |  |  |

|--------------------------------------|------|-----------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol                               | Min. | Max.                        | Unit | Remark                                                                                                                                                                                       |  |  |  |

| t <sub>PERIOD</sub>                  | 5    | -                           | ns   | 200MHz (Max.), between rising edges                                                                                                                                                          |  |  |  |

| t <sub>tlh</sub> , t <sub>thl</sub>  | -    | 0.2*<br>t <sub>PERIOD</sub> | ns   | t <sub>TLH</sub> , t <sub>THL</sub> < 1ns (max.) at 200MHz, C <sub>BGA</sub> =12pF, The absolute maximum value of t <sub>TLH</sub> , t <sub>THL</sub> is 10ns regardless of clock frequency. |  |  |  |

| Duty Cycle                           | 30   | 70                          | %    |                                                                                                                                                                                              |  |  |  |

#### Table 17 – HS200 Clock Signal Timing

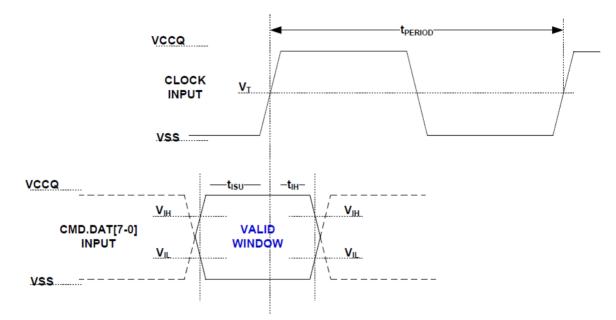

#### 3.5.2 HS200 Device Input Timing

Figure 13 and Table 18 define Device input timing.

Note1:  $t_{ISU}$  and  $t_{IH}$  are measured at  $V_{IL}(max.)$  and  $V_{IH}(min.)$ . Note2:  $V_{IH}$  denote  $V_{IH}(min.)$  and  $V_{IL}$  denotes  $V_{IL}(max.)$ .

#### Figure 13 – HS200 Device Input Timing

|                  | Table 18 – HS200 Device input Timing |      |      |                                |  |  |  |  |  |

|------------------|--------------------------------------|------|------|--------------------------------|--|--|--|--|--|

| Symbol           | Min.                                 | Max. | Unit | Remark                         |  |  |  |  |  |

| t <sub>ISU</sub> | 1.4                                  | -    | ns   | 5pF≤C <sub>BGA</sub> ≤<br>12pF |  |  |  |  |  |

| t <sub>IH</sub>  | 0.8                                  |      | ns   | 5pF≤C <sub>BGA</sub> ≤<br>12pF |  |  |  |  |  |

#### Table 18 – HS200 Device Input Timing

# 4 LPDDR2 Interface

# 4.1. Pin Function and Descriptions

|                                     |        | Table 19 – Pin Function and Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CK_t, CK_c                          | Input  | <b>Clock:</b> CK_t and CK_c are differential clock inputs. All Double Data Rate (DDR) CA inputs are sampled<br>on both positive and negative edge of CK_t. Single Data Rate (SDR) inputs, CS_n and CKE, are<br>sampled at the positive Clock edge.<br>Clock is defined as the differential pair, CK_t and CK_c. The positive Clock edge is defined by the<br>crosspoint of a rising CK_t and a falling CK_c. The negative Clock edge is defined by the crosspoint of<br>a falling CK_t and a rising CK_c.                                              |

| CKE                                 | Input  | <b>Clock Enable:</b> CKE HIGH activates and CKE LOW deactivates internal clock signals and therefore device input buffers and output drivers. Power savings modes are entered and exited through CKE transitions. CKE is considered part of the command code. See Command Truth Table for command code descriptions. CKE is sampled at the positive Clock edge.                                                                                                                                                                                        |

| CS                                  | Input  | <b>Chip Select:</b> CS_n is considered part of the command code. See Command Truth Table for command code descriptions. CS_n is sampled at the positive Clock edge.                                                                                                                                                                                                                                                                                                                                                                                    |

| CA0 – CA9                           | Input  | <b>DDR Command/Address Inputs:</b> Uni-directional command/address bus inputs. CA is considered part of the command code. See Command Truth Table for command code descriptions.                                                                                                                                                                                                                                                                                                                                                                       |

| DQ0 – DQ31                          | I/O    | Data Inputs/Output: Bi-directional data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DQS0_t – DQS3_t,<br>DQS0_c – DQS3_c | 1/0    | Data Strobe (Bi-directional, Differential): The data strobe is bi-directional (used for read and write data) and differential (DQS_t and DQS_c). It is output with read data and input with write data.<br>DQS_t is edge-aligned to read data and centered with write data.<br>DQS0_t and DQS0_c correspond to the data on DQ0 – DQ7,<br>DQS1_t and DQS1_c to the data on DQ8 – DQ15,<br>DQS2_t and DQS2_c to the data on DQ16 – DQ23,<br>DQS3_t and DQS3_c to the data on DQ24 – DQ31.                                                                |

| DM0 – DM3                           | Input  | Input Data Mask: DM is the input mask signal for write data. Input data is masked when DM is<br>sampled HIGH coincident with that input data during a Write access. DM is sampled on both edges of<br>DQS_t. Although DM is for input only, the DM loading shall match the DQ and DQS (or DQS_c).<br>DM0 is the input data mask signal for the data on DQ0-7,<br>DM1 is the input data mask signal for the data on DQ8-15,<br>DM2 is the input data mask signal for the data on DQ16-23,<br>DM3 is the input data mask signal for the data on DQ24-31. |

| VDD1                                | Supply | Core Power Supply 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VDD2                                | Supply | Core Power Supply 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VDDCA                               | Supply | Input Receiver Power Supply: Power supply for CA0-9, CKE, CS_n, CK_t, and CK_c input buffers.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VDDQ                                | Supply | I/O Power Supply: Power supply for Data input/output buffers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VREF(CA)                            | Supply | <b>Reference Voltage for CA Command and Control Input Receiver:</b> Reference voltage for all CA0-9, CKE, CS_n, CK_t, and CK_c input buffers.                                                                                                                                                                                                                                                                                                                                                                                                          |

| VREF(DQ)                            | Supply | Reference Voltage for DQ Input Receiver: Reference voltage for all Data input buffers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VSS                                 | Supply | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VSSCA                               | Supply | Ground for Input Receivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VSSQ                                | Supply | I/O Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ZQ                                  | I/O    | Reference Pin for Output Drive Strength Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

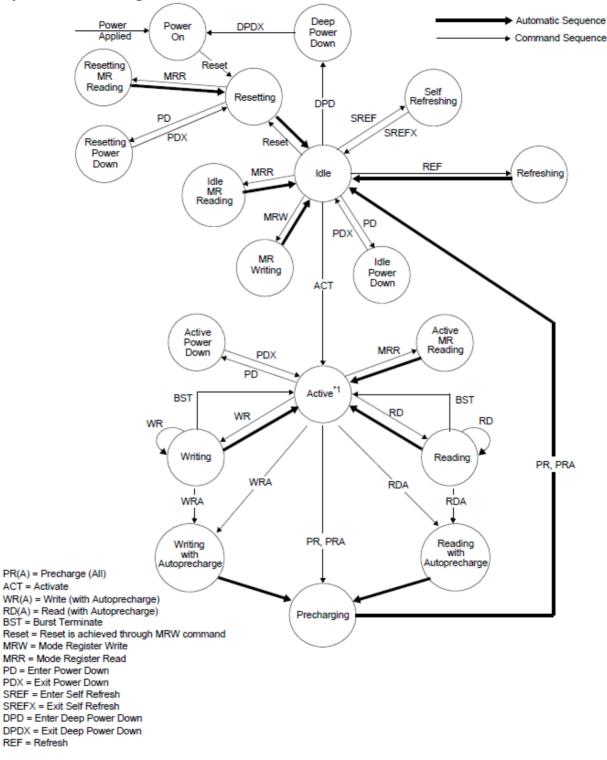

#### 4.2. Simplified State Diagram

#### Figure 14 — Simplified Bus Interface State Diagram

Note 1: For DDR2 Mobile RAM in the Idle state, all banks are precharged.

## 4.3. Electrical Conditions

All voltages are referenced to VSS (GND)

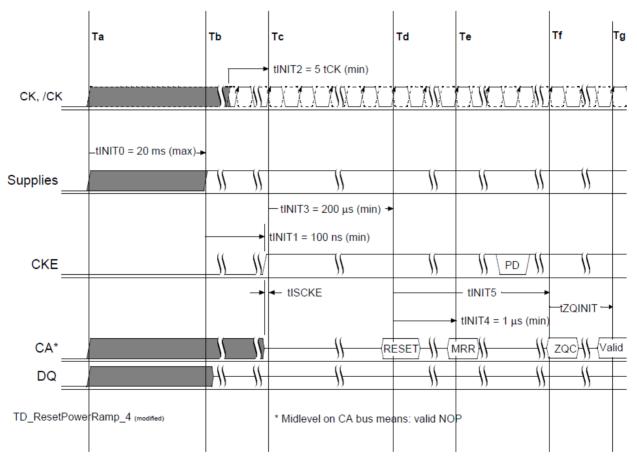

- Execute power-up and Initialization sequence before proper device operation is achieved.

- Operation or timing that is not specified is illegal, and after such an event, in order to guarantee proper operation, the DDR2 Mobile RAM Device must be powered down and then restarted through the specialized initialization sequence before normal operation can continue.

# 4.3.1 Absolute Maximum Ratings

| Table 20 Absolute Maximum Ratings    |           |      |      |      |      |  |  |  |  |

|--------------------------------------|-----------|------|------|------|------|--|--|--|--|

| Parameter                            | Symbol    | min. | max. | Unit | Note |  |  |  |  |

| VDD1 supply voltage relative to VSS  | VDD1      | -0.4 | 2.3  | V    | 2    |  |  |  |  |

| VDD2 supply voltage relative to VSS  | VDD2      | -0.4 | 1.6  | V    | 2    |  |  |  |  |

| VDDQ supply voltage relative to VSSQ | VDDQ      | -0.4 | 1.6  | V    | 2, 3 |  |  |  |  |

| Voltage on any ball relative to VSS  | VIN, VOUT | -0.4 | 1.6  | V    |      |  |  |  |  |

| Storage Temperature                  | TSTG      | -40  | 110  | °C   |      |  |  |  |  |

Notes: 1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. See Power-Ramp section "Power-up, initialization and Power-Off" on section7.6 for relationship between power supplies.

- 3. VREF  $\leq$  0.6 x VDDQ; however, VREF may be  $\geq$  VDDQ provided that VREF  $\leq$  300mV.

- 4. Storage Temperature is the case surface temperature on the center/top side of the DDR2 Mobile RAM Device. For the measurement conditions, please refer to JESD51-2 standard.

#### Caution

Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

| Table 21 Recommended DC Operating Conditions(TJ = -15°C to +80°C) |        |      |      |      |      |  |  |  |

|-------------------------------------------------------------------|--------|------|------|------|------|--|--|--|

| Parameter                                                         | Symbol | min. | max. | Unit | Note |  |  |  |

| Core Power1                                                       | VDD1   | 1.7  | 1.8  | 1.95 | V    |  |  |  |

| Core Power2, Input Buffer Power                                   | VDD2   | 1.14 | 1.2  | 1.3  | V    |  |  |  |

| I/O Buffer Power                                                  | VDDQ   | 1.14 | 1.2  | 1.3  | V    |  |  |  |

#### 4.3.2 Recommended DC Operating Conditions

#### 4.3.3 AC and DC Input Measurement Levels

#### 4.3.3.1 AC and DC Input Levels for Single-Ended CA/CS Signals Table 22 Single-Ended AC and DC Input Levels for CA/CS Inputs

| •                                  |            |             | •            |              |      |      |

|------------------------------------|------------|-------------|--------------|--------------|------|------|

| Parameter                          | Symbol     | Speed       | min.         | max.         | Unit | Note |

| AC input logic high                |            | 533 to 1066 | VREF + 0.220 | Note 2       |      | 4.0  |

|                                    | VIHCA(AC)  | 400         | VREF + 0.300 | Note 2       | V    | 1, 2 |

| AC input logic low                 | VILCA(AC)  | 533 to 1066 | – Note 2     | VREF – 0.220 | v    | 1 2  |

|                                    | VILCA(AC)  | 400         | Note 2       | VREF – 0.300 | v    | 1, 2 |

| DC input logic high                | VIHCA(DC)  | 533 to 1066 | VREF + 0.130 | VDD2         | V    | 1    |

| De input logic llight              | VINCA(DC)  | 400         | VREF + 0.200 | VDD2         |      | T    |

| DC input logic low                 |            | 533 to 1066 | – VSS        | VREF – 0.130 | v    | 1    |

| DC input logic low                 | VILCA(DC)  | 400         | v 33         | VREF – 0.200 | v    | Т    |

| Reference Voltage for CA/CS inputs | VREFCA(DC) |             | 0.49 × VDD2  | 0.51 × VDD2  | V    | 3, 4 |

|                                    |            |             |              |              |      |      |

Notes: 1. For CA/CS input only pins. VREF = VREFCA(DC).

2. See "Overshoot and Undershoot Specifications", please refer to JESD209-2F standard.

2. The ac peak noise on VREFCA may not allow VREFCA to deviate from VREFCA(DC) by more than ± 1% VDD2 (for reference: 26dditio. ± 12 mV).

3. For reference: 26dditio. VDD2/2  $\pm$  12 mV.

#### 4.3.3.2 AC and DC Input Levels for CKE

#### Table 23 Single-Ended AC and DC Input Levels for CKE

| Parameter            | Symbol | min.       | max.       | U | Init Note |

|----------------------|--------|------------|------------|---|-----------|

| CKE Input High Level | VIHCKE | 0.8 × VDD2 | Note 1     | V | 1         |

| CKE Input Low Level  | VILCKE | Note 1     | 0.2 × VDD2 | V | 1         |

Note: 1. See "Overshoot and Undershoot Specifications", please refer to JESD209-2F standard.

#### 4.3.3.3 AC and DC Input Levels for Single-Ended Data Signals Table 24 Single-Ended AC and DC Input Levels for DQ and DM

| Parameter                           | Symbol     | Speed       | min.         | max.         | Unit | Note |

|-------------------------------------|------------|-------------|--------------|--------------|------|------|

| AC input logic high                 | VIHDQ(AC)  | 533 to 1066 | VREF + 0.220 | Note 2       | V    | 1 2  |

| AC input logic high                 | VINDQ(AC)  | 400         | VREF + 0.300 | Note 2       | V    | 1, 2 |

| AC input logic low                  | VILDQ(AC)  | 533 to 1066 | - Note 2     | VREF – 0.220 | V    | 1 7  |

|                                     | VILDQ(AC)  | 400         | - Note 2     | VREF – 0.300 | v    | 1, 2 |

| DC input logic high                 |            | 533 to 1066 | VREF + 0.130 | VDDQ         | V    | 1    |

| DC input logic high                 | VIHDQ(DC)  | 400         | VREF + 0.200 | VDDQ         |      | 1    |

| DC input logic low                  |            | 533 to 1066 | - VSSQ       | VREF – 0.130 | V    | 1    |

| DC input logic low                  | VILDQ(DC)  | 400         | - vssq       | VREF – 0.200 | v    | т    |

| Reference Voltage for DQ, DM inputs | VREFDQ(DC) |             | 0.49 × VDDQ  | 0.51 × VDDQ  | V    | 3, 4 |

Notes: 1. For DQ input only pins. VREF = VREFDQ(DC).

2. See "Overshoot and Undershoot Specifications", please refer to JESD209-2F standard.

3. The ac peak noise on VREFDQ may not allow VREFDQ to deviate from VREFDQ(DC) by more than ± 1% VDDQ (for reference: 26dditio. ± 12 mV).

4. For reference: 26dditio. VDDQ  $\pm$  12 mV.

#### 4.3.3.4 Differential Swing Requirements for Clock (CK – /CK) and Strobe (DQS – /DQS) Table 25 Differential AC and DC Input Levels

| Parameter                  | Symbol      | min.                 | max.                        | Unit | Note |

|----------------------------|-------------|----------------------|-----------------------------|------|------|

| Differential input high    | VIHdiff(DC) | 2 × (VIH(DC) – VREF) | Note 3                      | V    | 1    |

| Differential input low     | VILdiff(DC) | Note 3               | 2 × (VIL(DC) – VREF)        | V    | 1    |

| Differential input high AC | VIHdiff(AC) | 2 × (VIH(AC) – VREF) | Note 3                      | V    | 2    |

| Differential input low AC  | VILdiff(AC) | Note 3               | $2 \times (VIL(AC) - VREF)$ | V    | 2    |

Notes: 1. Used to define a differential signal slew-rate.

2. For CK – /CK use VIH/VIL(AC) of CA and VREFCA; for DQS – /DQS, use VIH/VIL(AC) of DQs and VREFDQ; if a reduced AC-high or AC-low level is used for a signal group, then the reduced level applies also here.

3. These values are not defined, however the single-ended signals CK, /CK, DQS, and /DQS need to be within the respective limits (VIH(DC) max, VIL(DC)min) for single-ended signals as well as the limitations for overshoot and undershoot. Refer to "Overshoot and Undershoot Specifications", please refer to JESD209-2F standard

4. For CK and /CK, VREF = VREFCA(DC). For DQS and /DQS, VREF = VREFDQ(DC).

| Table 26 Allowed Time | able 26 Allowed Time Before Ringback (tDVAC) for CK – /CK and DQS – /DQS |                                                       |  |  |  |  |  |  |  |  |

|-----------------------|--------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|--|--|--|--|

| Slew Rate [V/ns]      | <b>tDVAC</b> [ps]<br>@ <b> VIH/Ldiff(AC) </b> = 440mV                    | <b>tDVAC</b> [ps]<br>@ <b> VIH/Ldiff(AC) </b> = 600mV |  |  |  |  |  |  |  |  |

|                       | min.                                                                     | min.                                                  |  |  |  |  |  |  |  |  |

| > 4.0                 | 175                                                                      | 75                                                    |  |  |  |  |  |  |  |  |

| 4                     | 170                                                                      | 57                                                    |  |  |  |  |  |  |  |  |

| 3                     | 167                                                                      | 50                                                    |  |  |  |  |  |  |  |  |

| 2                     | 163                                                                      | 38                                                    |  |  |  |  |  |  |  |  |

| 1.8                   | 162                                                                      | 34                                                    |  |  |  |  |  |  |  |  |

| 1.6                   | 161                                                                      | 29                                                    |  |  |  |  |  |  |  |  |

| 1.4                   | 159                                                                      | 22                                                    |  |  |  |  |  |  |  |  |

| 1.2                   | 155                                                                      | 13                                                    |  |  |  |  |  |  |  |  |

| 1                     | 150                                                                      | 0                                                     |  |  |  |  |  |  |  |  |

| < 1.0                 | 150                                                                      | 0                                                     |  |  |  |  |  |  |  |  |

#### 4.3.3.5 Single-ended Requirements for Differential Signals Table 27 Single-ended Levels for CK, DQS, /CK, /DQS

|                             | 0        |             | , ,,, ,,           |                    |      |      |

|-----------------------------|----------|-------------|--------------------|--------------------|------|------|

| Parameter                   | Symbol   | Speed       | min.               | max.               | Unit | Note |

| Single-ended high-level for |          | 533 to 1066 | (VDDQ / 2) + 0.220 | - Note 3           | V    | 1 2  |

| strobes                     |          | 400         | (VDDQ / 2) + 0.300 | Note 5             | v    | 1, 2 |

| Single-ended high-level for | VSEH(AC) | 533 to 1066 | (VDD2 / 2) + 0.220 | Note 3             | V    | 1 0  |

| СК, /СК                     |          | 400         | (VDD2 / 2) + 0.300 | Note 3             | v    | 1, 2 |

| Single-ended low-level for  |          | 533 to 1066 | - Note 3           | (VDDQ / 2) – 0.220 | V    | 1 0  |

| strobes                     |          | 400         | - Note 3           | (VDDQ / 2) - 0.300 | V    | 1, 2 |

| Single-ended low-level for  | VSEL(AC) | 533 to 1066 | - Note 3           | (VDD2 / 2) – 0.220 | V    | 1 2  |

| СК, /СК                     |          | 400         | - Note 3           | (VDD2 / 2) – 0.300 | v    | 1, 2 |

|                             |          |             |                    |                    |      |      |

Notes: 1. For CK, /CK use VSEH/VSEL(AC) of CA; for strobes (DQS0, /DQS0, DQS1, /DQS1, DQS2, /DQS2, DQS3, /DQS3) use VIH/VIL(AC) of DQs.

2. VIH(AC)/VIL(AC) for DQs is based on VREFDQ; VSEH(AC)/VSEL(AC) for CA is based on VREFCA; if a reduced Achigh or AC-low level is used for a signal group, then the reduced level applies also here

3. These values are not defined, however the single-ended signals CK, /CK, DQS0, /DQS0, DQS1, /DQS1, DQS2, /DQS2, DQS3, /DQS3 need to be within the respective limits (VIH(DC) max, VIL(DC)min) for single-ended signals as well as the limitations for overshoot and undershoot. Refer to "Overshoot and Undershoot Specifications", please refer to JESD209-2F standard.

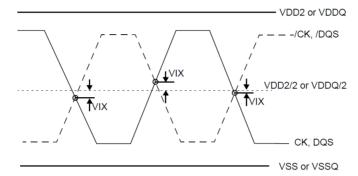

#### 4.3.4 Differential Input Cross Point Voltage

To guarantee tight setup and hold times as well as output skew parameters with respect to clock and strobe, each cross point voltage of differential input signals (CK, /CK and DQS, /DQS) must meet the requirements in Table 28. The differential input cross point voltage VIX is measured from the actual cross point of true and complement signals to the midlevel between of VDD and VSS.

Figure 22 — VIX Definition

#### Table 28 Cross Point Voltage for Differential Input Signals (CK, DQS)

| Parameter                                                               | Symbol | min. | max. | Unit | Note |

|-------------------------------------------------------------------------|--------|------|------|------|------|

| Differential Input Cross Point Voltage relative to VDD2/2 for CK, /CK   | VIXCA  | -120 | 120  | mV   | 1, 2 |

| Differential Input Cross Point Voltage relative to VDDQ/2 for DQS, /DQS | VIXDQ  | -120 | 120  | mV   | 1, 2 |

Notes: 1. The typical value of VIX(AC) is expected to be about 0.5 × VDD of the transmitting device, and VIX(AC) is expected to track variations in VDD. VIX(AC) indicates the voltage at which differential input signals must cross.

2. For CK and /CK, VREF = VREFCA(DC). For DQS and /DQS, VREF = VREFDQ(DC).

#### AC and DC Output Measurement Levels

#### 4.3.4.1 Single Ended AC and DC Output Levels

Table 29 shows the output levels used for measurements of single ended signals.

#### Table 29 Single-ended AC and DC Output Levels

| Parameter                                                 | Sy      | mbol   | Value             | Unit | Note |

|-----------------------------------------------------------|---------|--------|-------------------|------|------|

| DC output high measurement level (for IV curve linearity) | VO      | H(DC)  | 0.9 × VDDQ        | V    | 1    |

| DC output low measurement level (for IV curve linearity)  | VO      | )L(DC) | $0.1 \times VDDQ$ | V    | 2    |

| AC output high measurement level (for output slew rate)   | VOH(AC) |        | VREFDQ + 0.12     | V    |      |

| AC output low measurement level (for output slew rate)    | VOL(AC) |        | VREFDQ – 0.12     | V    |      |

| Output Leakage current (DQ, DM, DQS, /DQS)                | IOZ     | min.   | -5                | μΑ   |      |

| (DQ, DQS, /DQS are disabled; 0V . VOUT . VDDQ)            | 102     | max.   | 5                 | μΑ   |      |

| Delta PON between null up and null down for DO /DM        |         | min.   | -15               | %    |      |

| Delta RON between pull-up and pull-down for DQ/DM         | MMPUPD  | max.   | 15                | %    |      |

Notes: 1. IOH = -0.1mA. 2.IOL = 0.1mA.

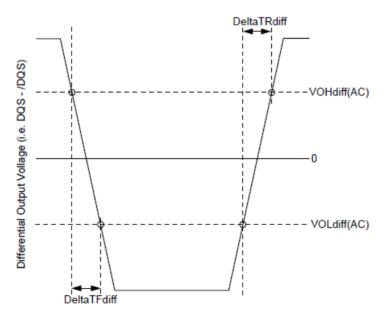

#### 4.3.4.2 Differential AC and DC Output Levels

Table 30 shows the output levels used for measurements of differential signals.

#### Table 30 Differential AC and DC Output Levels

| Parameter                                                     | Symbol      | Value       | Unit | Note |

|---------------------------------------------------------------|-------------|-------------|------|------|

| AC differential output high measurement level (for output SR) | VOHdiff(AC) | +0.2 × VDDQ | V    |      |

| AC differential output low measurement level (for output SR)  | VOLdiff(AC) | -0.2 × VDDQ | V    |      |

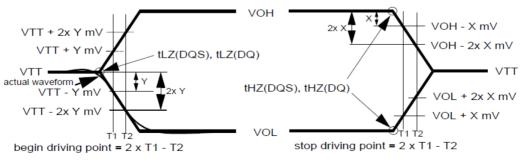

#### 4.3.4.3 Single Ended Output Slew Rate

With the reference load for timing measurements, output slew rate for falling and rising edges is defined and measured between VOL(AC) and VOH(AC) for single ended signals as shown in Table 31 and Figure 16.

#### Measured Description Defined by from to Single-ended output slew rate for rising edge VOL(AC) VOH(AC) [VOH(AC) – VOL(AC)] / DeltaTRse VOL(AC) [VOH(AC) - VOL(AC)] / DeltaTFse Single-ended output slew rate for falling edge VOH(AC) DeltaTRse Single Ended Output Vollage (i.e. DQ) - VOH (AC) VREF VOL (AC) DeltaTFse

#### Table 31 Single-ended Output Slew Rate Definition

#### Table 32 Output Slew Rate (single-ended)

| Parameter                                                  | Symbol | min. | max. | Unit |

|------------------------------------------------------------|--------|------|------|------|

| Single-ended Output Slew Rate (RON = $40\Omega \pm 30\%$ ) | SRQse  | 1.5  | 3.5  | V/ns |

| Single-ended Output Slew Rate (RON = $60\Omega \pm 30\%$ ) | SRQse  | 1.0  | 2.5  | V/ns |

| Output slew-rate matching Ratio (Pull-up to Pull-down)     |        | 0.7  | 1.4  |      |

Remark: SR: Slew Rate, Q: Query Output (like in DQ, which stands for Data-in, Query-Output), se: Single-ended Signals

Notes: 1. Measured with output reference load.