### PACE1753/SOS SINGLE CHIP, MIL-STD-1750A MEMORY MANAGEMENT UNIT (MMU) CMOS/SOS SPACE PROCESSOR MICROPERIPHERAL

#### **FEATURES**

- Implements the MIL-STD-1750A Instruction Set Architecture for Memory Management and Protection of up to 1 Megaword. All mapping memory (10,240 bits) for both the MMU and BPU functions are included on the chip.

- Designed to interface memory to the PACE1750A/AE.

- Provides the following additional functions:

- EDAC, Error Detection and Correction—or parity generation and detection

- Correct data register—for diagnostics

- First memory failing address register

- Illegal address error detection programmable

- Multi-Master arbitration

- 8-bit extended address laches and drivers on chip.

- 20, 25 and 30 MHz operation over the Military Temperature Range

- Single 5V ± 10% Power Supply

- Available with Class S manufacturing, screening, and testing.

- SOS Insulated substrate latch-up immunity and excellent SEU tolerance.

- SOS devices are fully interchangeable with application-proven SMD CMOS P1753 devices.

- Available in:

- 68-Lead Quad Pack (Leaded Chip Carrier) with optional Gull Wing.

# MEMORY MANAGEMENT UNIT AND BLOCK PROTECT UNIT "COMBO" (PACE1753)—FUNCTIONAL DESCRIPTION

The PACE1753 (COMBO) is a support chip for the PACE1750A/AE microprocessor family. It provides the following supporting functions to the system:

- Memory management and access protection for up to 1M words.

- 2 Physical memory write protection for up to 1M words memory in pages of 1K words each. Separate protection is provided for the CPU and for DMA in systems which include DMA.

- Detection of illegal I/O accesses (as defined by MIL-STD-1750A) or access to an unimplemented block of memory. In each case an error flag is generated to the processor.

- 4 Detection of double errors on the data bus and correction of single errors. An error signal is generated to the processor when a multiple error is detected.

- RDYA generation. Up to three wait states can be inserted in the address phase of the bus by generating a not-ready, RDYA low signal. The number of wait states required can be programmed in an internal register in the COMBO.

- 6. Bus arbitration for up to 4 masters. Arbitration is done on a fixed priority basis (i.e. by interconnection of hardware). (In 68 pin package only).

#### **ABSOLUTE MAXIMUM RATINGS<sup>1</sup>**

| Supply Voltage Range                                      | 0.5V to +7.0V                  |

|-----------------------------------------------------------|--------------------------------|

| Input Voltage Range                                       | 0.5V to V <sub>CC</sub> + 0.5V |

| Storage Temperature Range                                 | −65°C to +150°C                |

| Input Current Range                                       | -30mA to +5mA                  |

| Current applied to any output <sup>3</sup>                | 150mA                          |

| Maximum Power Dissipation <sup>2</sup>                    | 1.5W                           |

| Lead Temperature Range (soldering 10 seconds)             | 300°C                          |

| Thermal resistance (θ <sub>JC</sub> ): QL and QG packages | 8°C/W                          |

#### Notes

- Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

- 2. Must with stand the added power dissipation due to short circuit test e.g.,  ${\rm I}_{\rm OS}.$

- 3. Duration 1 second or less.

# RECOMMENDED OPERATING CONDITIONS

| Supply Voltage Range                                                                                     | 4.5V to +5.5V        |

|----------------------------------------------------------------------------------------------------------|----------------------|

| Case Operating<br>Temperature Range                                                                      | –55°C to +125°C      |

| Operating Maximum Power Dissipation (Outputs Open) Device Type 20MHz Device Type 30MHz Device Type 40MHz | 0.5W<br>0.6W<br>0.7W |

#### **DC ELECTRICAL SPECIFICATIONS** (Over recommended operating conditions)

| Symbol            | Parameter                                                                                        | Min                   | Max                   | Unit | Conditi                                                                        | ons <sup>1</sup>          |  |  |

|-------------------|--------------------------------------------------------------------------------------------------|-----------------------|-----------------------|------|--------------------------------------------------------------------------------|---------------------------|--|--|

| V <sub>IH</sub>   | Input HIGH Voltage                                                                               | 2.0                   | V <sub>CC</sub> + 0.5 | V    |                                                                                |                           |  |  |

| V <sub>IL</sub>   | Input LOW Voltage <sup>2</sup>                                                                   | -0.5                  | 0.8                   | V    |                                                                                |                           |  |  |

| V <sub>CD</sub>   | Input Clamp Diode Voltage                                                                        |                       | -1.2                  | V    | $V_{CC} = 4.5V, I_{IN} = -18mA$                                                |                           |  |  |

|                   | 0. (** (111011)/2/62                                                                             | 2.4                   |                       | V    | $V_{CC} = 4.5V$ ,                                                              | $I_{OH} = -8.0 \text{mA}$ |  |  |

| V <sub>OH</sub>   | Output HIGH Voltage                                                                              | V <sub>CC</sub> - 0.2 |                       | V    | $V_{IN} = 0.8V, 2.0V$                                                          | $I_{OH} = -300 \mu A$     |  |  |

|                   | Output LOW Voltage,4                                                                             |                       | 0.65                  | V    | $V_{CC} = 4.5V$ ,                                                              | $I_{OL} = 8.0 \text{mA}$  |  |  |

| V <sub>OL</sub>   | except EXT ADR <sub>0</sub> – EXT ADR <sub>7</sub>                                               |                       | 0.2                   | V    | $V_{IN} = 0.8V, 2.0V$                                                          | I <sub>OL</sub> = 300μA   |  |  |

|                   | Output LOW Voltage,4                                                                             |                       | 0.65                  | V    | $V_{CC} = 4.5V,$                                                               | $I_{OL} = 20.0 \text{mA}$ |  |  |

| V <sub>OL</sub>   | $EXTADR_0-EXTADR_7$                                                                              |                       | 0.2                   | V    | $V_{IN} = 0.8V, 2.0V$                                                          | I <sub>OL</sub> = 300μA   |  |  |

| I <sub>ІН</sub>   | Input HIGH Current,<br>except $IB_0 - IB_{15}$ ,<br>$EDC_0 - EDC_5$ ,<br>$EXT ADR_0 - EXT ADR_7$ |                       | 300                   | μΑ   | $V_{IN} = V_{CC},$ $V_{CC} = 5.5V$                                             |                           |  |  |

| I <sub>IH</sub>   | Input HIGH Current,<br>$IB_0 - IB_{15}$ , $EDC_0 - EDC_5$ ,<br>$EXT ADR_0 - EXT ADR_7$           |                       | 100                   | μΑ   | $V_{IN} = V_{CC},$<br>$V_{CC} = 5.5V$                                          |                           |  |  |

| I <sub>I</sub> L  | Input LOW Current,<br>except $IB_0 - IB_{15}$ ,<br>$EDC_0 - EDC_5$ ,<br>$EXT ADR_0 - EXT ADR_7$  |                       | -50                   | μΑ   | $V_{IN} = GND,$<br>$V_{CC} = 5.5V$                                             |                           |  |  |

| I <sub>IL</sub>   | Input LOW Current,<br>$IB_0 - IB_{15}$ , $EDC_0 - EDC_5$ ,<br>$EXT ADR_0 - EXT ADR_7$            |                       | -50                   | μΑ   | $V_{IN} = GND,$<br>$V_{CC} = 5.5V$                                             | ** *                      |  |  |

| I <sub>OZH</sub>  | Output Three-State Current                                                                       |                       | 50                    | μΑ   | $V_{OUT} = 2.4V, V_{CC}$                                                       | = 5.5V                    |  |  |

| I <sub>OZL</sub>  | Output Three-State Current                                                                       |                       | -50                   | μΑ   | $V_{OUT} = 0.5V, V_{CC}$                                                       | = 5.5V                    |  |  |

| Iccac             | Quiescent Power Supply<br>Current (CMOS Input<br>Levels, Active)                                 |                       | 60                    | mA   | $V_{IN}$ < 0.2V or < $V_{CC}$ - 0.2V f = 0MHz, Outputs Open, $V_{CC}$ = 5.5V   |                           |  |  |

| I <sub>CCQT</sub> | Quiescent Power Supply<br>Current (TTL Input<br>Levels, Active)                                  |                       | 110                   | mA   | $V_{IN} = 3.4V$ , $f = 0MHz$ ,<br>All Inputs, Outputs Open,<br>$V_{CC} = 5.5V$ |                           |  |  |

|                   | Dynamic Power Supply                                                                             |                       | 90                    | mA   | $V_{CC} = 0V \text{ to } V_{CC},$                                              | F = 20MHz                 |  |  |

| I <sub>CCD</sub>  | Current                                                                                          |                       | 100                   | mA   | tr = tf = 2.5 ns,<br>Outputs Open,                                             | F = 30MHz                 |  |  |

|                   |                                                                                                  |                       | 125                   | mA   | V <sub>CC</sub> = 5.5V                                                         | F = 40MHz                 |  |  |

| I <sub>OS</sub>   | Output Short Circuit Current <sup>3</sup>                                                        | -25                   |                       | mA   | $V_{OUT} = GND, V_{CC} = 5.5V$                                                 |                           |  |  |

| C <sub>IN</sub>   | Input Capacitance                                                                                |                       | 10                    | pF   | Inputs Only                                                                    |                           |  |  |

| C <sub>OUT</sub>  | Output/Bi-directional<br>Capacitance                                                             |                       | 15                    | pF   | Outputs Only<br>(Including I/O Buff                                            | ers)                      |  |  |

#### Notes

- $1. \quad 4.5 \text{V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{V}, \\ -55^{\circ}\text{C} \leq \text{T}_{\text{C}} \leq +125^{\circ}\text{C}. \quad \text{Unless otherwise specified, testing shall be conducted at worst-case conditions.}$

- 2.  $V_{IL} = -3.0V$  for pulse widths less than or equal to 20ns.

- 3. Duration of the short should not exceed one second; only one output may be shorted at a time.

- $4. \ Test \ may be performed \ by \ setting/forcing \ the \ parameter \ limit \ (voltage) \ and \ measuring \ the \ appropriate \ current \ parameter.$

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 4.5V)$

|                                                              |                                   | 20 MHz |     | 251 | ЛНz | z 30 MHz |     |      |

|--------------------------------------------------------------|-----------------------------------|--------|-----|-----|-----|----------|-----|------|

| Symbol                                                       | Parameter                         | Min    | Max | Min | Max | Min      | Max | Unit |

| TD/Ī(EXT ADR) <sub>V</sub>                                   | MMU Cache Hit                     |        | 27  |     | 23  |          | 21  | ns   |

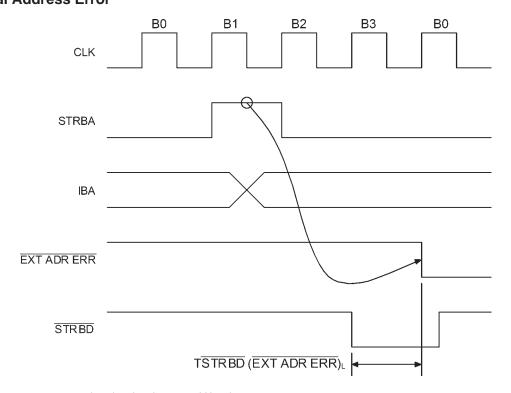

| TSTRBD (EXT ADR ERR) <sub>L</sub>                            | External Address Error            |        | 37  |     | 33  |          | 30  | ns   |

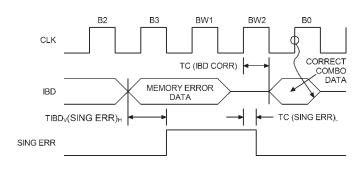

| TC (IBD CORR)                                                | Error Correction Read Cycle       |        | 32  |     | 28  |          | 26  | ns   |

| IBD <sub>V</sub> (SING ERR) <sub>H</sub>                     | Error Correction Read Cycle       |        | 37  |     | 33  |          | 31  | ns   |

| TC (SING ERR) <sub>L</sub>                                   | Error Correction Read Cycle       |        | 27  |     | 23  |          | 21  | ns   |

| $TIBD_V$ (EDC GEN) $_V$                                      | EDAC or Parity Write Cycle        |        | 32  |     | 28  |          | 26  | ns   |

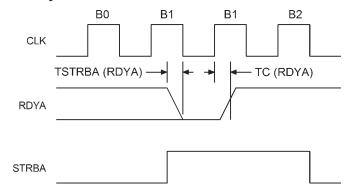

| TSTRBD (EX RDY) <sub>L</sub>                                 | MMU Cache Miss                    |        | 27  |     | 23  |          | 21  | ns   |

| TC (EX RDY) <sub>H</sub>                                     | MMU Cache Miss                    |        | 27  |     | 23  |          | 21  | ns   |

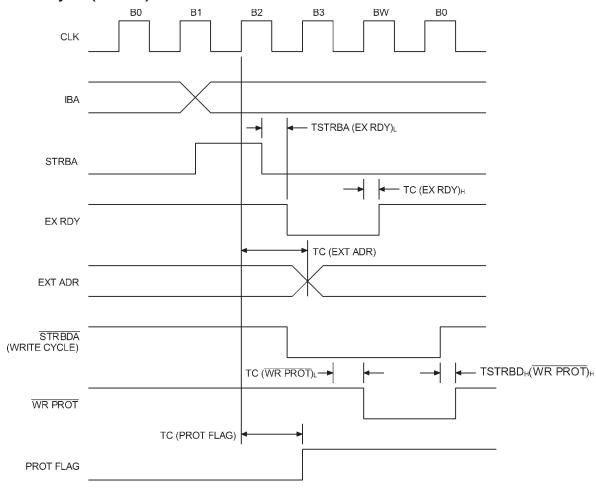

| TC (WR PROT) <sub>L</sub>                                    | MMU Cache Miss                    |        | 36  |     | 32  |          | 30  | ns   |

| $\overline{\text{TSTRBD}}_{\text{H}}$ (WR PROT) <sub>H</sub> | MMU Cache Miss                    |        | 27  |     | 23  |          | 21  | ns   |

| TC (GNT1) <sub>H</sub>                                       | Arbiter LOW to HIGH Priority      |        | 34  |     | 30  |          | 28  | ns   |

| TC (GNT0) <sub>L</sub>                                       | Arbiter LOW to HIGH Priority      |        | 34  |     | 30  |          | 28  | ns   |

| TC (GNT0) <sub>H</sub>                                       | Arbiter HIGH to LOW Priority      |        | 34  |     | 30  |          | 28  | ns   |

| TC (GNT1) <sub>L</sub>                                       | Arbiter HIGH to LOW Priority      |        | 34  |     | 30  |          | 28  | ns   |

| TC (RDYA)                                                    | Address Ready                     |        | 32  |     | 28  |          | 26  | ns   |

| TFC (IB OUT) <sub>V</sub>                                    | Clock to IB Out Valid (I/O Read)  |        | 40  |     | 38  |          | 36  | ns   |

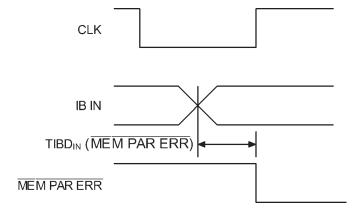

| TIBD <sub>IN</sub> (MEM PAR ERR)                             | Parity Mode                       |        | 36  |     | 32  |          | 30  | ns   |

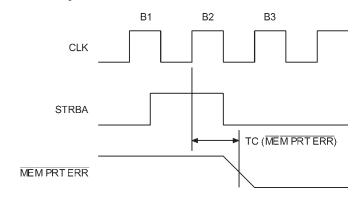

| TC (MEM PRT ERR)                                             | Memory Protect Error              |        | 64  |     | 60  |          | 58  | ns   |

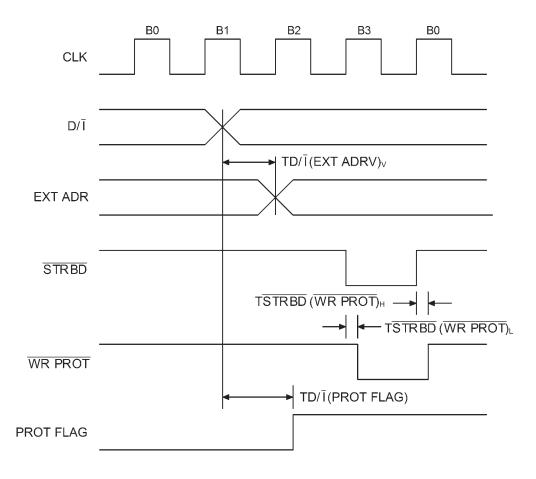

| TSTRBD (WR PROT)                                             | Write Protect Cache Hit           |        | 27  |     | 23  |          | 21  | ns   |

| TC (WR PROT) <sub>L</sub>                                    | Write Protect Cache Miss          |        | 37  |     | 33  |          | 31  | ns   |

| TSTRBD <sub>H</sub> (WR PROT) <sub>H</sub>                   | Write Protect Cache Miss          |        | 27  |     | 23  |          | 21  | ns   |

| TD/Ī (PROT FLAG)                                             | Cache Hit (BPU Protection Error)  |        | 52  |     | 48  |          | 46  | ns   |

| TD/Ī (PROT FLAG)                                             | Cache Hit (MMU Key-Lock Error)    |        | 42  |     | 38  |          | 36  | ns   |

| TC (PROT FLAG)                                               | Cache Miss (BPU Protection Error) |        | 67  |     | 63  |          | 61  | ns   |

| TC (PROT FLAG)                                               | Cache Hit (MMU Key-Lock Error)    |        | 52  |     | 48  |          | 46  | ns   |

| TC (EXT ADR)                                                 | Clock to EXT ADR Valid (Miss)     |        | 38  |     | 34  |          | 32  | ns   |

#### Notes:

- $1. \quad 4.5 \text{V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{V}, \\ -55^{\circ}\text{C} \leq \text{T}_{\text{C}} \leq +125^{\circ}\text{C}. \quad \text{Unless otherwise specified, testing shall be conducted at worst-case conditions.}$

- 2.  $V_{IL} = -3.0V$  for pulse widths less than or equal to 20ns.

- 3. Duration of the short should not exceed one second; only one output may be shorted at a time.

- 4. Pulse width of  $\overline{WR}$  PROT/PROT FLAG shall be  $\geq$  80% of  $\overline{STRBD}$  pulse width.

- 5. Functional tests shall consist of the same functional tests used when testing the equivalent bulk CMOS, MIL-STD-883 compliant, Class B SMD 5962-89505 device.

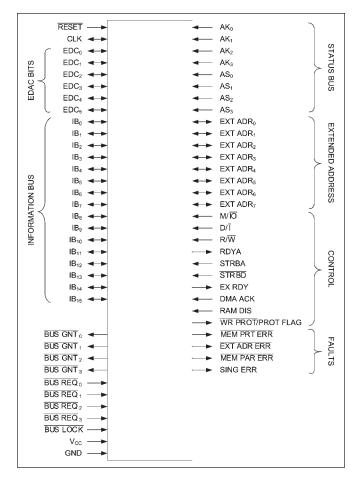

#### TERMINAL CONNECTIONS - PACKAGES QL AND QG

| Case Out           | lines                |                    | ι                    | J and Y            |                    |

|--------------------|----------------------|--------------------|----------------------|--------------------|--------------------|

| Terminal<br>Number | Terminal<br>Symbol   | Terminal<br>Number | Terminal<br>Symbol   | Terminal<br>Number | Terminal<br>Symbol |

| 1                  | GND                  | 24                 | IB <sub>12</sub>     | 47                 | AS <sub>1</sub>    |

| 2                  | EDC <sub>0</sub>     | 25                 | IB <sub>13</sub>     | 48                 | AS <sub>0</sub>    |

| 3                  | EDC <sub>1</sub>     | 26                 | IB <sub>14</sub>     | 49                 | BUS REQ 2          |

| 4                  | EDC <sub>2</sub>     | 27                 | IB <sub>15</sub>     | 50                 | AK <sub>3</sub>    |

| 5                  | RESET                | 28                 | MEM PRT ERR          | 51                 | AK <sub>2</sub>    |

| 6                  | EDC <sub>3</sub>     | 29                 | MEM PAR ERR          | 52                 | BUS GNT 1          |

| 7                  | EDC <sub>4</sub>     | 30                 | EXT ADR ERR          | 53                 | AK <sub>1</sub>    |

| 8                  | EDC <sub>5</sub>     | 31                 | RAM DIS              | 54                 | AK <sub>0</sub>    |

| 9                  | BUS GNT <sub>2</sub> | 32                 | SING ERR             | 55                 | CLK                |

| 10                 | IB <sub>0</sub>      | 33                 | DMA ACK              | 56                 | STRBA              |

| 11                 | IB <sub>1</sub>      | 34                 | GND                  | 57                 | STRBD              |

| 12                 | IB <sub>2</sub>      | 35                 | V <sub>CC</sub>      | 58                 | BUS REQ 0          |

| 13                 | IB <sub>3</sub>      | 36                 | EXT ADR <sub>0</sub> | 59                 | EX RDY             |

| 14                 | IB <sub>4</sub>      | 37                 | EXT ADR <sub>1</sub> | 60                 | WR PROT/PROT FLAG  |

| 15                 | IB <sub>5</sub>      | 38                 | EXT ADR <sub>2</sub> | 61                 | R/W                |

| 16                 | IB <sub>6</sub>      | 39                 | EXT ADR <sub>3</sub> | 62                 | D/Ī                |

| 17                 | IB <sub>7</sub>      | 40                 | EXT ADR <sub>4</sub> | 63                 | M/ <del>IO</del>   |

| 18                 | BUS REQ <sub>3</sub> | 41                 | EXT ADR <sub>5</sub> | 64                 | RDYA               |

| 19                 | IB <sub>8</sub>      | 42                 | EXT ADR <sub>6</sub> | 65                 | BUS GNT 0          |

| 20                 | IB <sub>9</sub>      | 43                 | EXT ADR <sub>7</sub> | 66                 | BUS LOCK           |

| 21                 | BUS GNT <sub>3</sub> | 44                 | GND                  | 67                 | BUS REQ 1          |

| 22                 | IB <sub>10</sub>     | 45                 | AS <sub>3</sub>      | 68                 | V <sub>CC</sub>    |

| 23                 | IB <sub>11</sub>     | 46                 | AS <sub>2</sub>      |                    |                    |

## **1**

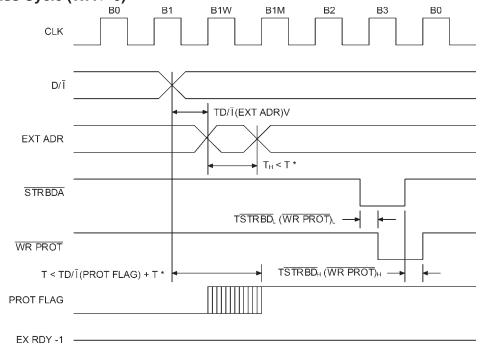

#### **MMU Cache Hit**

#### **External Address Error**

#### Note:

#### **Error Correction (Write Cycle)**

# CLK | B0 | B1 | B2 | B3 | B0 | TIBD<sub>V</sub> (EDC GEN)<sub>V</sub> | | EDC GEN |

#### **Memory Protect Error**

#### **Error Correction (Read Cycle)**

#### **Ready Address**

#### **Memory Parity Error**

#### Note:

#### MMU Cache Miss Cycle (WA = 0)

#### MMU Cache Miss Cycle (WA > 0)

<sup>\*</sup> The WR PROT/PROT FLAG signal is programmed as WR PROT or PROT FLAG. (See BPU Description), T = 1 Clock Period. **Note:**

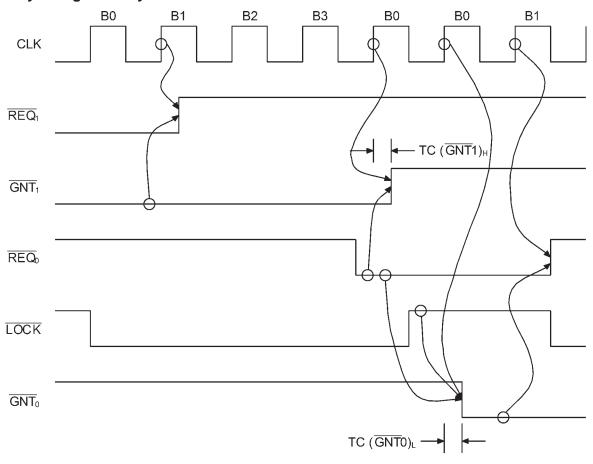

#### **Low Priority to High Priority Transition**

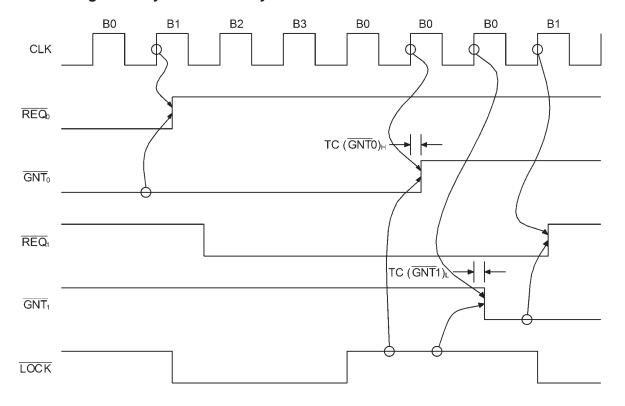

#### **Bus Arbitrator High Priority to Low Priority Transition**

#### Note:

#### **SWITCHING WAVEFORMS AND TEST CIRCUIT** (Continued)

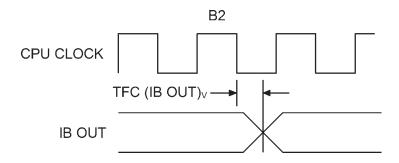

#### IB Bus Output (0:15)

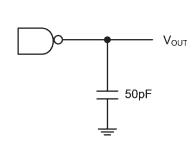

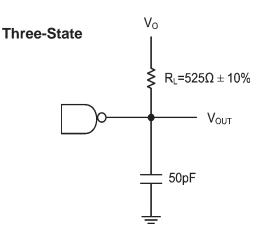

#### **Standard Output (Non Three-State)**

#### Note:

| Parameter | Vo                 | V <sub>MEA</sub>       |

|-----------|--------------------|------------------------|

| TPLZ      | ≥ 3V               | 0.5V                   |

| TPHZ      | 0V                 | V <sub>CC</sub> - 0.5V |

| TPXL      | V <sub>CC</sub> /2 | 1.5V                   |

| TPXH      | V <sub>CC</sub> /2 | 1.5V                   |

#### **PIN FUNCTIONS**

| Symbol                                         | Name                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUS REQ <sub>0</sub> -<br>BUS REQ <sub>3</sub> | Bus Request <sup>1</sup>    | Active LOW inputs that indicate a requirement for the bus from 4 masters on the bus. The master assigned to pin $\overline{\text{BUS}}$ - $\overline{\text{REQ}}_0$ has highest priority; the master assigned to pin $\overline{\text{BUS}}$ - $\overline{\text{REQ}}_3$ has lowest priority.                                                                                                                                                               |

| BUS LOCK                                       | Bus Lock <sup>1</sup>       | An active LOW input that indicates that the one master assigned<br>the bus is using the bus. A new master will receive a bus grant only<br>after this signal becomes inactive.                                                                                                                                                                                                                                                                              |

| BUS GNT <sub>0</sub> - BUS GNT <sub>3</sub>    | Bus Grant <sup>1</sup>      | Active LOW outputs indicating which master was granted the bus. It remains active during BUS LOCK unless a higher master request occurs, which resets it. However, the higher master will be granted the bus only after the present master's BUS LOCK releases the bus.                                                                                                                                                                                     |

| M/ĪO                                           | Memory or I/O               | An input signal that indicates whether the current bus cycle is a memory (HIGH) or I/O (LOW) cycle.                                                                                                                                                                                                                                                                                                                                                         |

| D/Ī                                            | Data or Instruction         | An input signal that indicates whether the current bus cycle access is for data (HIGH) or instruction (LOW).                                                                                                                                                                                                                                                                                                                                                |

| R/W                                            | Read or Write               | An input signal that indicates the direction of data flow on the bus. A HIGH indicates a memory read or input operation into the master and a LOW indicates a memory write or output operation from the master.                                                                                                                                                                                                                                             |

| STRBA                                          | Address Strobe              | An active HIGH input used to latch the address at the HIGH-to-LOW transition of the strobe.                                                                                                                                                                                                                                                                                                                                                                 |

| STRBD                                          | Data Strobe                 | An active LOW input used to strobe data in memory and I/O cycles.                                                                                                                                                                                                                                                                                                                                                                                           |

| CPU-CLK                                        | CPU Clock                   | A single-phase input clock signal (0-40MHz, 40% to 60% duty cycle.)                                                                                                                                                                                                                                                                                                                                                                                         |

| RESET                                          | Reset                       | An active LOW input that initializes the device.                                                                                                                                                                                                                                                                                                                                                                                                            |

| AK <sub>0</sub> - AK <sub>3</sub>              | Access Key                  | Active HIGH inputs used to match the access lock in the MMU page for memory accesses. A mismatch will cause the MEM PRT ERR signal to become active.                                                                                                                                                                                                                                                                                                        |

| AS <sub>0</sub> - AS <sub>3</sub>              | Address State               | Active HIGH inputs that select the page register group in the MMU. In the DMA physical demultiplexed mode, AS(0:1) will receive the 9th and 10th most significant bits of the physical address for use in the BPU function.                                                                                                                                                                                                                                 |

| EXT ADR <sub>0</sub> -<br>EXT ADR <sub>7</sub> | Extended Addresses Bus      | A bi-directional active HIGH bus. In CPU cycles, it is an output bus which is used to select one of 256 pages, 4K words each, expanding the direct addressing space to 1M word. In DMA cycles, indicated by DMA-ACK being active, it is also an output bus except when programmed for the physical demultiplexed DMA mode. In this case it becomes an input to receive the 8 most significant bits of the DMA physical address for use in the BPU function. |

| IB <sub>0</sub> - IB <sub>15</sub>             | Information Bus             | An active HIGH bi-directional time multiplexed address/data bus.<br>$\ensuremath{IB}_0$ is the most significant bit.                                                                                                                                                                                                                                                                                                                                        |

| EDC <sub>0</sub> - EDC <sub>5</sub>            | Detection/Correction<br>Bus | An active HIGH bi-directional bus used for detection of errors on the data bus ( ${\rm IB}_0$ - ${\rm IB}_{15}$ ) and correction of single errors. When working in parity mode EDC $_0$ is the parity bit. EDC $_0$ - EDC $_5$ are undefined in this case.                                                                                                                                                                                                  |

#### PIN FUNCTIONS (Continued)

| Symbol                | Name                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEM PRT ERR           | Memory Protect Error                | An active LOW output generated by the MMU or BPU blocks to signal to the CPU a protected memory violation. The error is generated in one of the following conditions: a mismatch in the access keys in the MMU page, an access to an execution protected page during instruction cycles, an access to a write-protected page during data cycles, or an access to a page write-protected by the BPU.                           |

| MEM PAR ERR           | Memory Parity Error                 | An active LOW output which signals to the CPU an error on the data bus during a memory cycle. Two detection modes can be selected by programming the control register: EDAC mode (6 Hamming code parity bits) or single bit parity mode (even or odd parity). The signal is inactive when none of the above modes are selected (default after Reset).                                                                         |

| EXT ADR ERR           | External Address Error              | An active LOW output which signals to the CPU an unimplemented memory or illegal I/O access.                                                                                                                                                                                                                                                                                                                                  |

| SING ERR              | Single Error                        | An active HIGH output to signal detection of a single error on the data bus in memory cycles. It is high impedance when the EDAC function is disabled by the program (default state after Reset).                                                                                                                                                                                                                             |

| RAM DIS               | RAM-Disable                         | An active HIGH input from the P1754 device which enables the corrected data on the data bus when the EDAC function is enabled. An internal one clock delay is generated before the data is output on the bus to allow external memory to disconnect itself from the bus.                                                                                                                                                      |

| EX RDY                | Data Ready                          | An active HIGH output that indicates that no wait states are requested. It becomes inactive for one clock (inserting one wait state) whenever a memory page different than the current one is accessed (causing a miss).                                                                                                                                                                                                      |

| RDYA                  | Address Ready                       | An active HIGH output that indicates that no wait states are requested when STRBA is active. Wait states are inserted when this signal becomes inactive during STRBA. Up to three wait states can be inserted by programming an internal register. Three wait states are inserted after Reset (default).                                                                                                                      |

| WR PROT/<br>PROT FLAG | Write Protected/<br>Protection Flag | Either an active LOW output (following STRBD timing) during legal memory write cycles, when no protection error occurs, or an active HIGH level indicating a protection error in a write cycle. Each mode can be selected by programming the control register. Default mode after Reset is write-protected.                                                                                                                   |

| DMA ACK               | DMA Acknowledge                     | An active HIGH input from the DMA controller which indicates a DMA cycle. Used to select the DMA table in the BPU memory for protection. For example, this could allow the DMA channel to update the program which could be write-protected from the processor. In the physical DMA mode, it will cause the Extended Address Lines (EXT ADR <sub>0-7</sub> ) to become inputs, providing BPU protection of the DMA transfers. |

#### Note:

<sup>1.</sup> Used for Bus Arbitration; only available on 68-lead devices.

| Standardized Military Drawing Part Number | Pyramid Semiconductor<br>CAGE Number | Pyramid Semiconductor<br>Part Number |

|-------------------------------------------|--------------------------------------|--------------------------------------|

| 5962-8950501UX                            | 3DTT2                                | P1753-20QLMB                         |

| 5962-8950501YX                            | 3DTT2                                | P1753-20QGMB                         |

| 5962-8950501ZX                            | 3DTT2                                | P1753-20PGMB                         |

| 5962-8950502UX                            | 3DTT2                                | P1753-30QLMB                         |

| 5962-8950502YX                            | 3DTT2                                | P1753-30QGMB                         |

| 5962-8950502ZX                            | 3DTT2                                | P1753-30PGMB                         |

| 5962-8950503UX                            | 3DTT2                                | P1753-40QLMB                         |

| 5962-8950503YX                            | 3DTT2                                | P1753-40QGMB                         |

| 5962-8950503ZX                            | 3DTT2                                | P1753-40PGMB                         |

| 5962-8950504TX                            | 3DTT2                                | P1753-20GMB                          |

| 5962-8950504XX                            | 3DTT2                                | P1753-20CMB                          |

| 5962-8950505TX                            | 3DTT2                                | P1753-30GMB                          |

| 5962-8950505XX                            | 3DTT2                                | P1753-30CMB                          |

| 5962-8950506TX                            | 3DTT2                                | P1753-40GMB                          |

| 5962-8950506XX                            | 3DTT2                                | P1753-40CMB                          |

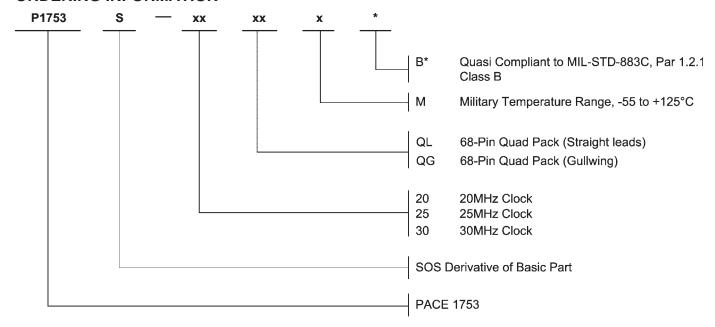

#### **ORDERING INFORMATION**

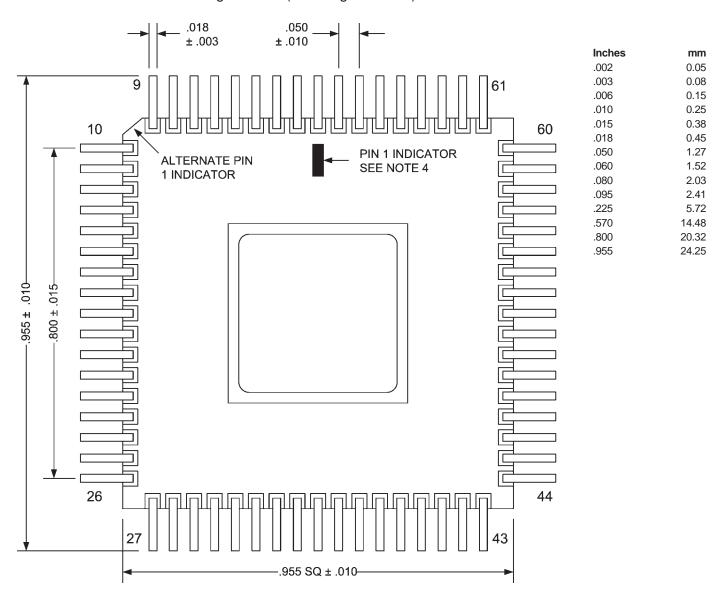

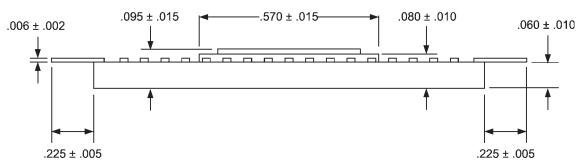

#### **CASE OUTLINE 1:**

68 Lead Quad Pack with Straight Leads (Ordering Code QL)

#### **NOTES:**

- 1) Dimensions are in inches.

- $2)\,Metric\,equivalents\,are\,given\,for\,general\,information\,only.$

- 3) Unless otherwise specified, tolerances are .02 (0.5 mm) for two place decimals and .005 (0.13 mm) for three place decimals.

- 4) Pin 1 indicator can be either rectangle, dot, or triangle at specified location or referenced to the uniquely beveled corner.

- 5) Corners indicated as notched may be either notched or square.

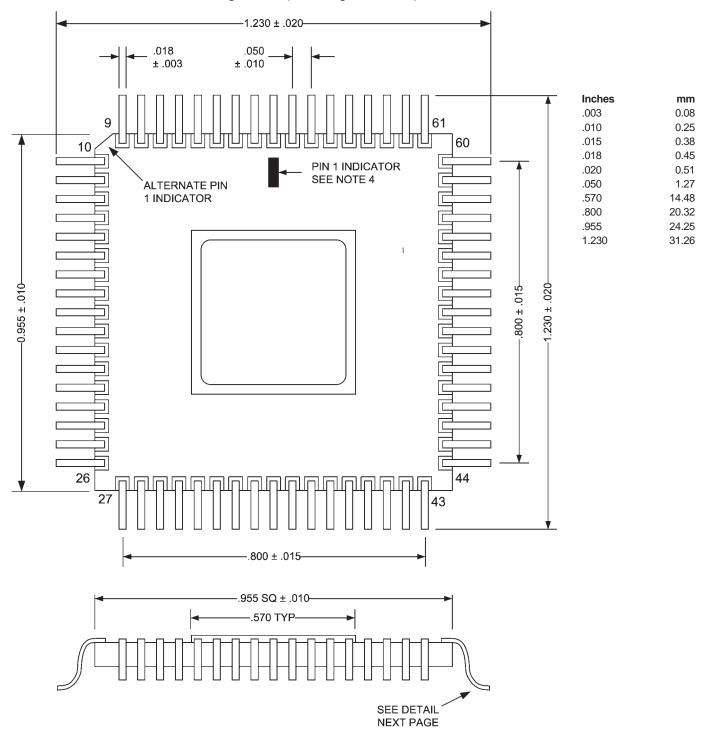

#### **CASE OUTLINE 2:**

68 Lead Quad Pack with Gullwing Leads (Ordering Code QG)

#### **NOTES:**

- 1) Dimensions are in inches.

- 2) Metric equivalents are given for general information only.

- 3) Unless otherwise specified, tolerances are .02 (0.5 mm) for two place decimals and .005 (0.13 mm) for three place decimals.

- 4) Pin 1 indicator can either be rectangle, dot, or triangle at specified location or referenced to the uniquely beveled corner.

- 5) Corners indicated as notched my be either notched or square (with radius).

- $6) \, Case \, 2 \, is \, derived \, from \, Case \, 1 \, by \, forming \, the \, leads \, to \, the \, shown \, gullwing \, configuration.$

#### **LEAD FORM DETAIL**

| Symmle of | INC     | HES   |                                     | Φ1            |

|-----------|---------|-------|-------------------------------------|---------------|

| Symbol –  | Min     | Max   | A0**                                |               |

| А         | 0.048   | 0.090 | <u> </u>                            |               |

| A1        | 0.011   | 0.031 |                                     | ► L4          |

| В         | 0.016   | 0.021 |                                     |               |

| С         | 0.004   | 0.008 |                                     |               |

| e1        | 0.050   | BSC   |                                     |               |

| D         | 1.210   | 1.250 |                                     |               |

| D1        | 0.945   | 0.965 | /                                   |               |

| D2        | 0.800   | BSC   | /                                   |               |

| Е         | 1.210   | 1.250 |                                     |               |

| E1        | 0.945   | 0.965 |                                     | R1            |

| E2        | 0.800   | BSC   |                                     |               |

| L*        | 0.270 N |       |                                     |               |

| L0        | 0.120   | 0.210 |                                     |               |

| L3        | 0.040   | 0.050 |                                     |               |

| L4        | 0.086   | 0.109 | / A                                 | C             |

| R1        | 0.018   | 0.020 |                                     |               |

| R2        | 0.018   | 0.020 |                                     |               |

| Φ1        | 4°      | 8°    |                                     |               |

| Φ2        | -1°     | 7°    |                                     | R2            |

| A0**      |         | 0.141 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | RZ            |

|           |         |       | A1 /                                |               |

|           |         |       |                                     |               |

|           |         |       | <u> </u>                            |               |

|           |         |       |                                     |               |

|           |         |       | <u>_</u>                            | <u> </u>      |

|           |         |       | <b>↑</b>                            | 112 >         |

|           |         |       |                                     | <b>◄-L3-▶</b> |

|           |         |       |                                     | Φ2            |

|           |         |       |                                     |               |

|           |         |       |                                     |               |

|           |         |       |                                     |               |

|           |         |       |                                     | <b>■</b> LO   |

<sup>\*</sup> Lead length in the straight lead configuration, prior to leadforming (used for all test and in-process WIP operations).

\*\* Measured from the highest of the top of the leads or the top of the lid.

#### **REVISIONS**

| DOCUMENT NUMBER: MICRO-8 DOCUMENT TITLE: PACE175 |               |                    | 3<br>53/SOS CMOS MMU/COMBO    |

|--------------------------------------------------|---------------|--------------------|-------------------------------|

| REV.                                             | ISSUE<br>DATE | ORIG. OF<br>CHANGE | DESCRIPTION OF CHANGE         |

| ORIG                                             | May-89        | RKK                | New Data Sheet                |

| А                                                | Jul-04        | JDB                | Added Pyramid logo            |

| В                                                | Aug-05        | JDB                | Re-created electronic version |