# **Data Sheet**

# PAW3335DB-TZDU: Low Power Optical Gaming Navigation Chip

## **General Description**

PAW3335DB-TZDU is PixArt Imaging's new low power gaming navigation chip suitable for wired and wireless gaming application. It has the latest state-of-the-art low-power architecture and automatic power management modes, making it ideal for battery-operated, power-sensitive cordless gaming devices. It provides excellent gaming experience with the features of high speed and high resolution even in low power mode to fulfill gamers' need. It is packaged in an 8pin staggered dual-in-line package (DIP) and designed to be used with LOAC-LSG1 lens to achieve optimum performance.

### **Key Features**

- Low power consumption of typical 1.7mA @ run mode

- Programmable rest modes

- Small form factor PDIP 8L molded lead-frame package

- Operating Voltage: 1.80V 2.10V

- High speed motion detection 400ips and acceleration 40g

- Selectable resolutions up to 16000cpi

- Three-wire serial port interface (SDIO)

- Internal oscillator no clock input needed

- Customizable response time and downshift time for rest modes

- Angle snapping

- Lift detection options

- 1mm setting

- 2mm setting

### Applications

- Wired and wireless Gaming Optical Mouse

- Trackball application

### **Key Parameters**

| Parameter                   | Value                                 |

|-----------------------------|---------------------------------------|

| Power Supply Voltage (V)    | VDD: 1.80 – 2.10V                     |

| Interface                   | 3-wire Serial Peripheral<br>Interface |

| Supply Current @ VDD = 1.9V | Run: 1.7 mA<br>Power Down: 3uA        |

| Note: includes LED current  |                                       |

| Resolution (cpi)            | Up to 16000                           |

| Tracking Speed (ips)        | 400                                   |

| Acceleration (g)            | 40                                    |

| Package Type (mm)           | 8L PDIP, 9.9 x 12.85 x 6.1            |

### **Ordering Information**

| Part Number    | Package Type    |  |  |  |  |  |

|----------------|-----------------|--|--|--|--|--|

| PAW3335DB-TZDU | 8L PDIP         |  |  |  |  |  |

| LOAC-LSG1      | Small Trim Lens |  |  |  |  |  |

For any additional inquiries, please contact us at http://www.pixart.com

### **Contents**

| Data S  | heet                                                 |          |

|---------|------------------------------------------------------|----------|

| PAW3    | 335DB-TZDU: Low Power Optical Gaming Navigation Chip | <i>2</i> |

| Ger     | neral Description                                    | 1        |

| Key     | Features                                             | 1        |

|         | plications                                           |          |

| Key     | Parameters                                           |          |

| Ord     | dering Information                                   |          |

| List of | Figures                                              |          |

|         | Tables                                               |          |

| 1.0     | Introduction                                         |          |

| 1.1     |                                                      |          |

| 1.2     |                                                      | 6        |

| 2.0     | Operating Specifications                             | 8        |

| 2.1     | Regulatory Requirements                              | 8        |

| 2.2     |                                                      |          |

| 2.3     |                                                      |          |

| 2.4     |                                                      |          |

| 2.5     |                                                      |          |

| 2.6     | AC Characteristics                                   | 10       |

| 3.0     | Mechanical Specifications                            | 12       |

| 3.1     | Mechanical Dimension                                 | 12       |

| 3.2     | Assembly Drawings                                    | 13       |

| 3.3     | Package Marking                                      | 17       |

| 4.0     | System Level Description                             | 18       |

| 4.1     | Reference Application Schematic Diagram              | 18       |

| 4.2     | PCB Assembly Recommendation                          | 19       |

| 5.0     | Power States & Sequence                              | 20       |

| 5.1     | Power-Up Sequence                                    | 20       |

| 5.2     | Power-Up Initialization Register Setting             | 20       |

| 5.3     | Power-Down Sequence                                  | 23       |

| 6.0     | Serial Peripheral Interface Communication            | 24       |

| 6.1     | Signal Description                                   | 24       |

| 6.2     | Motion Bit Timing                                    | 24       |

| 6.3     | Chip Select Operation                                | 24       |

| Versio  | on 1.12   27 June 2019   11032EN                     |          |

| 6.4  | Write Operation                                 | 25 |

|------|-------------------------------------------------|----|

| 6.5  | Read Operation                                  | 26 |

| 6.6  | Required Timing between Read and Write Commands | 27 |

| 6.7  | Burst Mode Operation                            | 28 |

| 7.0  | RawData Grab                                    | 29 |

| 8.0  | Power Management for Wireless Mode              | 30 |

| 9.0  | Universal Lift Cut Off Setting                  | 31 |

| 10.0 | Universal Lift Cut Off Setting                  | 32 |

| 10.1 |                                                 | 32 |

| 10.2 |                                                 |    |

| 10.3 | Bit Masks for Register Write                    | 50 |

| 11.0 | Document Revision History                       |    |

## **List of Figures**

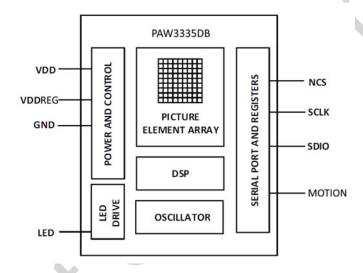

| Figure 1. Functional Block Diagram                                                                 | 6  |

|----------------------------------------------------------------------------------------------------|----|

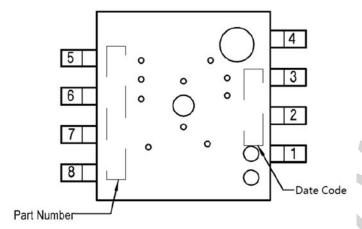

| Figure 2. Pin Configuration                                                                        | 7  |

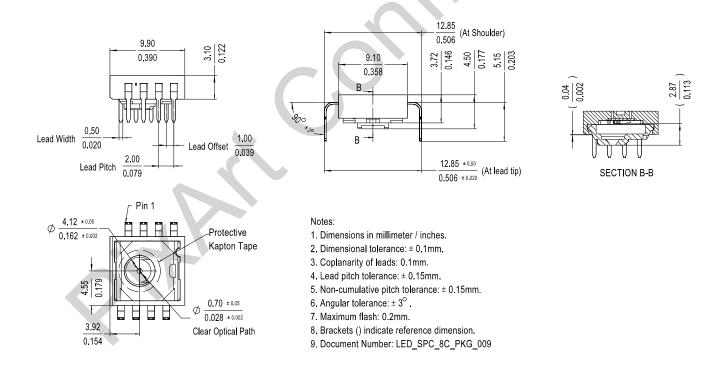

| Figure 3. Package Drawing Outline                                                                  | 12 |

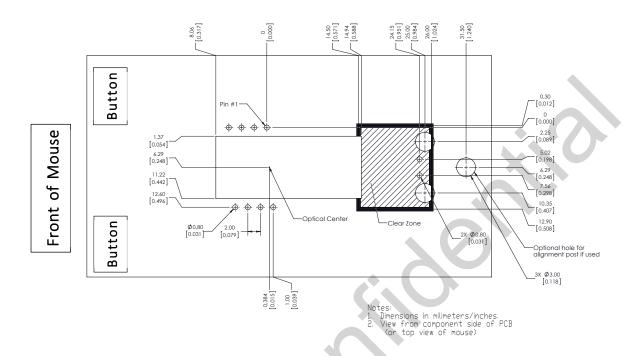

| Figure 4. Recommended chip orientation, mechanical cutouts & spacing (Top View)                    | 13 |

| Figure 5. Distance from Lens Reference Plane to Surface                                            | 13 |

| Figure 6. 2D Assembly                                                                              | 14 |

| Figure 7. 2D Mouse Assembly                                                                        | 15 |

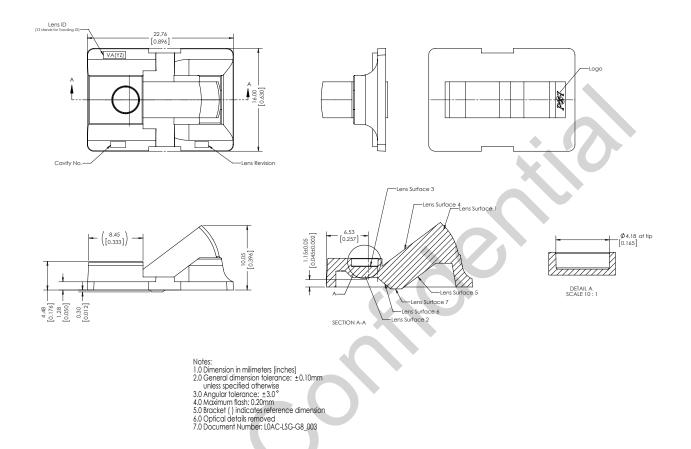

| Figure 8. LOAC-LSG1 Lens Outline Drawing                                                           | 16 |

| Figure 9. Recommended Base Plate Design with LOAC-LSG1 Lens                                        | 17 |

| Figure 10. PAW3335DB-TZDU Reference Mouse Schematic                                                | 18 |

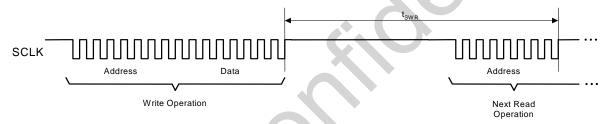

| Figure 11. Write Operation                                                                         | 25 |

| Figure 12. SDIO Setup & Hold Time during write operation                                           | 25 |

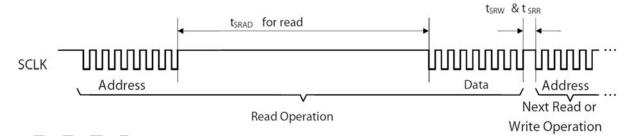

| Figure 13. Read Operation                                                                          | 26 |

| Figure 14. SDIO Delay & Hold Time during read operation                                            | 26 |

| Figure 15. Timing between two Write commands                                                       | 27 |

| Figure 16. Timing between Write & Read commands                                                    | 27 |

| Figure 17. Timing between Read & Subsequent Write or Read commands                                 | 27 |

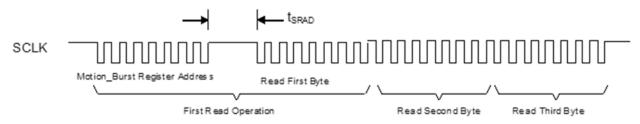

| Figure 18. Motion Burst Timing                                                                     | 28 |

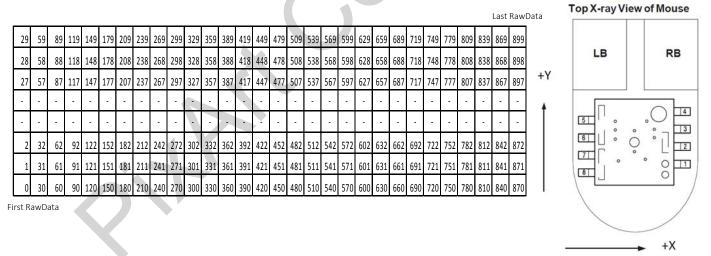

| Figure 19. RawData Address Map for 30x30 (Chip looking on the navigation surface through the lens) | 29 |

### **List of Tables**

| Table 1. PAW3335DB-TZDU Pins Description          | 7  |

|---------------------------------------------------|----|

| Table 2. Absolute Maximum Ratings                 | 8  |

| Table 3. Recommended Operating Conditions         | 8  |

| Table 4. Thermal Specifications                   | 9  |

| Table 5. DC Electrical Specifications             | 9  |

| Table 5. DC Electrical Specifications             | 10 |

| Table 7. Package Dimensions                       |    |

| Table 8. Code Identification                      |    |

| Table 9. Recommended R <sub>LED</sub>             | 18 |

| Table 10. Recommended R1                          | 18 |

| Table 11. State of Signal Pins after VDD is Valid | 22 |

| Table 12. Status during Shutdown Mode             | 23 |

| Table 13. Rest Modes Response & Downshift Time    | 30 |

| Table 14. Lift Cut Off Setting for LOAC-LSG1      |    |

| Table 15. Register List                           | 32 |

#### 1.0 Introduction

#### 1.1 Overview

PAW3335DB-TZDU is based on Optical Navigation Technology, which measures changes in position by optically acquiring sequential surface images (frames) and mathematically determining the direction and magnitude of movement. PAW3335DB-TZDU contains an Image Acquisition System (IAS), a Digital Signal Processor (DSP), and a three-wire serial port. The IAS acquires microscopic surface images via the lens and illumination system. These images are processed by the DSP to determine the direction and distance of motion. The DSP calculates the  $\Delta X$  and  $\Delta Y$  relative displacement values. An external microcontroller reads and translates the  $\Delta X$  and  $\Delta Y$  information from the chip serial port into PS2, USB, or RF signals before sending them to the host PC.

Note: Throughout this document PAW3335DB-TZDU is referred to as the chip.

Figure 1. Functional Block Diagram

#### 1.2 Terminology

| Term   | Description                 |

|--------|-----------------------------|

| DSP    | Digital Signal Processing   |

| LED    | Light Emitting Diode        |

| NCS    | Chip Select                 |

| VDDREG | LDO output for digital core |

| VDD    | Supply voltage              |

| SCLK   | Serial Clock                |

| SDIO   | Serial Data In & Out        |

| SPI    | Serial Peripheral Interface |

| GND    | Ground                      |

| MOTION | Motion Detect               |

Version 1.12 | 01 Mar 2019 | 11032EN

### Pins Description

Figure 2. Pin Configuration

Table 1. PAW3335DB-TZDU Pins Description

| Pin No. | Name   | Туре         | Description                                  |

|---------|--------|--------------|----------------------------------------------|

| 1       | LED    | Input        | LED Illumination Control input               |

| 2       | VDDREG | Power        | LDO output (only for sensor internal usage). |

| 3       | VDD    | Power        | Power supply                                 |

| 4       | SCLK   | Input        | Serial clock input                           |

| 5       | MOTION | Output       | Motion Detect                                |

| 6       | GND    | Gnd          | Ground                                       |

| 7       | SDIO   | Input/Output | Serial data in/out                           |

| 8       | NCS    | Input        | Chip select (active low)                     |

### 2.0 Operating Specifications

#### 2.1 Regulatory Requirements

- Passes FCC "Part15 Subpart, Class B", "ICES-003:2016 Issue 6, Class B" and "ANSI C63.4:2014" when assembled into a

mouse with shielded USB cable using ferrite bead and following PixArt's recommendations.

- Passes IEC 62471:2006 Photo biological safety of lamps and lamp systems.

### 2.2 Absolute Maximum Ratings

Table 2. Absolute Maximum Ratings

| Parameters              | Symbol              | Min. | Max. | Unit | Notes                                             |

|-------------------------|---------------------|------|------|------|---------------------------------------------------|

| Storage Temperature     | Ts                  | -40  | 85   | °C   |                                                   |

| Lead Solder Temperature | T <sub>SOLDER</sub> |      | 260  |      | For 10 seconds, 1.6mm below seating plane         |

| Supply Voltage          | $V_{DD}$            | -0.5 | 2.1  | V    | Including V <sub>NA</sub> of 100 mV <sub>pp</sub> |

| ESD                     | ESD <sub>HBM</sub>  |      | 2    | kV   | All pins, Human Body Model                        |

| Input Voltage           | V <sub>IN</sub>     | -0.5 | VDD  | V    | All I/O pins                                      |

#### Notes:

- 1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are the stress ratings only and functional operation of the device at these or any other condition beyond those indicated for extended period of time may affect device reliability.

- 2. The maximum ratings do not reflect eye-safe operation.

- 3. The inherent design of this component causes it to be sensitive to electrostatic discharge. The ESD threshold is listed above. To prevent ESD induced damage, take adequate ESD precautions when handling this product

### 2.3 Recommended Operating Conditions

**Table 3. Recommended Operating Conditions**

| Description                                                  | Symbol              | Min. | Тур. | Max. | Unit       | Notes                                             |

|--------------------------------------------------------------|---------------------|------|------|------|------------|---------------------------------------------------|

| Operating Temperature                                        | T <sub>A</sub>      | 0    |      | 40   | °C         |                                                   |

| Power Supply Voltage                                         | $V_{DD}$            | 1.8  | 1.9  | 2.1  | V          | Including V <sub>NA</sub> of 100 mV <sub>pp</sub> |

| Power Supply Rise Time                                       | $t_{RT}$            | 0.15 |      | 20   | ms         | 0 to Min. VDD                                     |

| Supply Noise                                                 | $V_{NA}$            |      |      | 100  | $mV_{p-p}$ | 10kHz – 75MHz                                     |

| Serial Port Clock Frequency                                  | $f_{SCLK}$          |      |      | 8    | MHz        | Active drive, 50% duty cycle                      |

| Distance from Lens<br>Reference Plane to Tracking<br>Surface | Z                   | 2.20 | 2.40 | 2.60 | mm         |                                                   |

| Speed                                                        | S                   | 400  |      |      | ips        | PixArt standard gaming surfaces                   |

| Acceleration                                                 | А                   | 40   |      |      | g          | In run mode PixArt standard gaming surfaces       |

| Load Capacitance                                             | $C_L$               |      |      | 20   | pF         | SDIO, MOTION                                      |

| Lift Cutoff 1mm setting                                      | Lift <sub>1mm</sub> |      | 1    |      | mm         | LOAC-LSG1                                         |

| Lift Cutoff 2mm setting                                      | Lift <sub>2mm</sub> |      | 2    |      | mm         | LOAC-LSG1                                         |

Note: PixArt does not guarantee the chip performance if the operating temperature is beyond the specified limit.

Version 1.12 | 27 June 2019 | 11032EN

SEE. FEEL. TOUCH.

### 2.4 Thermal Specifications

## Table 4. Thermal Specifications

| Parameters                   | Symbol         | Min. | Тур. | Max. | Unit | Notes                                                        |

|------------------------------|----------------|------|------|------|------|--------------------------------------------------------------|

| Storage Temperature          | Ts             | -25  | -    | 80   | °C   |                                                              |

| Lead-free Solder Temperature | T <sub>P</sub> | -    | -    | 260  | /    | For 10 seconds, 1.6mm below seating plane for wave soldering |

### 2.5 DC Characteristics

Table 5. DC Electrical Specifications

| Parameters                         | Symbol                | Min.     | Тур. | Max.        | Unit     | Condition                             |  |  |

|------------------------------------|-----------------------|----------|------|-------------|----------|---------------------------------------|--|--|

| DC Supply Current in various modes | I <sub>DD_RUN</sub>   |          | 1.7  |             | mA       | Average Run current                   |  |  |

|                                    | I <sub>DD_REST1</sub> |          | 610  |             | uA       |                                       |  |  |

| Note: Includes I                   | I <sub>DD_REST2</sub> |          | 25   |             | uA       |                                       |  |  |

| Note: Includes I <sub>LED</sub>    | I <sub>DD_REST3</sub> |          | 5    |             | uA       | No load on SDIO & MOTION              |  |  |

| Power Down Current                 | I <sub>PD</sub>       |          | 3    |             | uA       |                                       |  |  |

| Input Low Voltage                  | V <sub>IL</sub>       |          |      | 0.3*<br>VDD | V        | SCLK, SDIO, NCS                       |  |  |

| Input High Voltage                 | V <sub>IH</sub>       | 0.7* VDD |      |             | V        | SCLK, SDIO, NCS                       |  |  |

| Input Hysteresis                   | V <sub>I_HYS</sub>    |          | 100  |             | mV       | SCLK, SDIO, NCS,                      |  |  |

| Input Leakage Current              | I <sub>LEAK</sub>     |          | ± 1  | ± 10        | uA       | Vin=VDD or 0V, SCLK, SDIO,<br>NCS     |  |  |

| Output Low Voltage                 | V <sub>OL</sub>       |          |      | 0.45        | >        | I <sub>OUT</sub> = 1mA, SDIO, MOTION  |  |  |

| Output High Voltage                | V <sub>OH</sub>       | VDD-0.45 |      |             | <b>V</b> | I <sub>OUT</sub> = -1mA, SDIO, MOTION |  |  |

| Input Capacitance                  | C <sub>in</sub>       |          | 10   |             | рF       | SCLK, SDIO, NCS                       |  |  |

Note: All the parameters are tested under recommended operating conditions. Typical values at 25 °C, V<sub>DD</sub> = 1.9 V & LED current = 24mA

### 2.6 AC Characteristics

Table 6. AC Electrical Specifications

| Parameters                                       | Symbol                               | Min.  | Тур. | Max.  | Unit | Conditions                                                                                                                                                                  |

|--------------------------------------------------|--------------------------------------|-------|------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Motion Delay After Reset                         | t <sub>MOT-RST</sub>                 | 50    |      |       | ms   | From reset to valid motion, assuming motion is present                                                                                                                      |

| Shutdown                                         | t <sub>stdwn</sub>                   |       |      | 500   | ms   | From Shutdown mode active to low current This timing could be affected by Rest3 period                                                                                      |

| Wake up from Shutdown                            | t <sub>WAKEUP</sub>                  | 50    |      |       | ms   | From Shutdown mode inactive to valid motion.  Notes: A RESET must be asserted after a shutdown. Refer to section "5.2 Power Down Sequence", also note t <sub>MOT-RST.</sub> |

| SDIO Output Rise Time                            | t <sub>r-SDIO</sub>                  |       | 6    | A . ( | ns   | C <sub>L</sub> = 20pF                                                                                                                                                       |

| SDIO Output Fall Time                            | t <sub>f-SDIO</sub>                  |       | 6    |       | ns   | C <sub>L</sub> = 20pF                                                                                                                                                       |

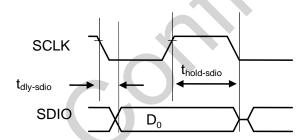

| SDIO Output Delay After SCLK                     | t <sub>DLY-SDIO</sub>                |       |      | 38    | ns   | From SCLK falling edge to SDIO output data valid $C_L = 20pF$                                                                                                               |

| SDIO Output Hold Time                            | t <sub>hold-SDIO</sub>               | 31.25 |      |       | ns   | Data held until next falling SCLK edge                                                                                                                                      |

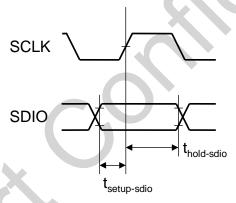

| SDIO input Hold Time                             | thold-SDIO input                     | 31.25 |      |       | ns   | Amount of time data is valid after SCLK rising edge                                                                                                                         |

| SDIO input Setup Time                            | t <sub>setup-</sub> SDIO input       | 31.25 |      |       | ns   | From data valid to SCLK rising edge                                                                                                                                         |

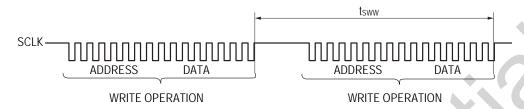

| SPI Time Between Write<br>Commands               | tsww                                 | 5     |      |       | μs   | From rising SCLK for last bit of the first data byte, to rising SCLK for last bit of the second data byte.                                                                  |

| SPI Time Between Write And<br>Read Commands      | t <sub>swr</sub>                     | 5     |      |       | μs   | From rising SCLK for last bit of the 1st data byte, to rising SCLK for last bit of the second address byte                                                                  |

| SPI Time Between Read And<br>Subsequent Commands | t <sub>SRW</sub><br>t <sub>SRR</sub> | 2     |      |       | μs   | From rising SCLK for last bit of the 1st data byte, to falling SCLK for the 1st bit of data being read.                                                                     |

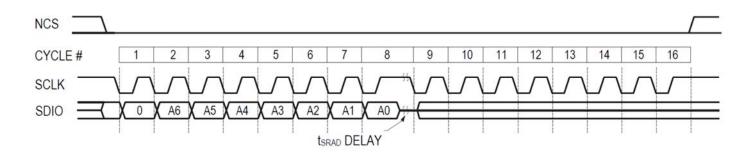

| SPI Read Address-Data Delay                      | t <sub>SRAD</sub>                    | 2     |      |       | μs   | From rising SCLK for last bit of the address byte, to falling SCLK for the 1st bit of data being read.                                                                      |

| NCS Inactive After Motion<br>Burst               | t <sub>BEXIT</sub>                   | 500   |      |       | ns   | Minimum NCS inactive time after motion burst before next SPI usage                                                                                                          |

| NCS To SCLK Active                               | t <sub>NCS-SCLK</sub>                | 120   |      |       | ns   | From last NCS falling edge to 1st SCK rising edge.                                                                                                                          |

| Parameters                         | Symbol                      | Min. | Тур. | Max. | Unit | Conditions                                                                                                                                                            |

|------------------------------------|-----------------------------|------|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK To NCS Inactive SDIO<br>Read  | t <sub>SCLK-NCS read</sub>  | 120  |      |      | ns   | From last SCLK rising edge to NCS rising edge, for valid SDIO data transfer                                                                                           |

| SCLK To NCS Inactive SDIO<br>Write | t <sub>SCLK-NCS write</sub> | 1    |      |      | μs   | From last SCLK rising edge to NCS rising edge, for valid SDIO data transfer                                                                                           |

| NCS To SDIO High-Z                 | t <sub>NCS-SDIO</sub>       |      |      | 500  | ns   | From NCS rising edge to SDIO high-Z state                                                                                                                             |

| Transient Supply Current           | IDDT                        |      | 70   |      | mA   | Max supply current during the supply ramp from 0V to V <sub>DD</sub> with min 150us and max 20ms rise time. (Does not include charging currents of bypass capacitors) |

Note: All the parameters are tested under recommended operating conditions. Typical values at 25 °C & VDD=1.9V

## 3.0 Mechanical Specifications

### 3.1 Mechanical Dimension

Table 7. Package Dimensions

| Parameters                         | Nominal | Min.  | Max.  | Unit |

|------------------------------------|---------|-------|-------|------|

| Package Body Dimension X           | 9.90    | 9.80  | 10.00 | mm   |

| Package Body Dimension Y           | 9.10    | 9.00  | 9.20  | mm   |

| Package Width (inclusive pins)     | 12.85   | 12.35 | 13.35 | mm   |

| Lead Length                        | 5.15    | 5.05  | 5.25  | mm   |

| Lead Pitch                         | 2.00    | 1.85  | 2.15  | mm   |

| Total Lead Count                   | 8       | -     |       | -    |

| Lead Offset                        | 1.00    | -     | -     | mm   |

| Lead Width                         | 0.50    | 0.40  | 0.60  | mm   |

| Hole Diameter                      | 0.70    | 0.65  | 0.75  | mm   |

| Center of Hole from edge of body X | 4.55    | 4.45  | 4.65  | mm   |

| Center of Hole from edge of body Y | 3.92    | 3.82  | 4.02  | mm   |

Figure 3. Package Drawing Outline

#### 3.2 Assembly Drawings

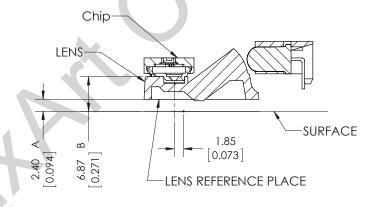

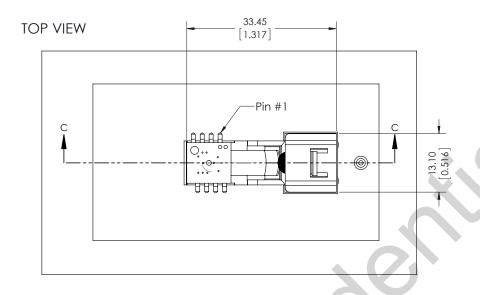

Figure 4. Recommended chip orientation, mechanical cutouts & spacing (Top View)

Note

A -Distance from object surface to lens reference place B -Distance from object surface to Chip reference place

Figure 5. Distance from Lens Reference Plane to Surface

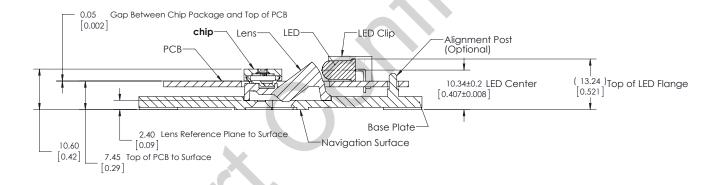

Figure 6. 2D Assembly

Note: The LED should be bent 90 degree with LED flange touching the PCB.

Figure 7. 2D Mouse Assembly

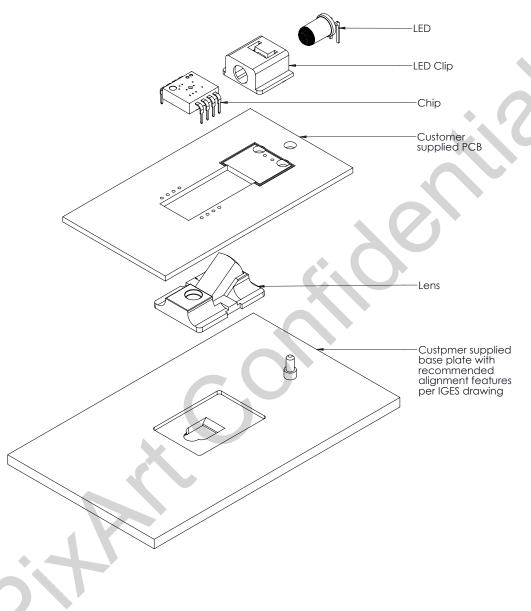

Figure 8. LOAC-LSG1 Lens Outline Drawing

Figure 9. Recommended Base Plate Design with LOAC-LSG1 Lens

## 3.3 Package Marking

Refer to Figure 2. Pin Configuration

Table 8. Code Identification

| Code           | Marking        | Description                              |

|----------------|----------------|------------------------------------------|

| Product Number | PAW3335DB-TZDU | Part number label                        |

| Lot Code       | YYWWXXXXX      | YYWW=Date code<br>XXXXX= PixArt Reserved |

### 4.0 System Level Description

### 4.1 Reference Application Schematic Diagram

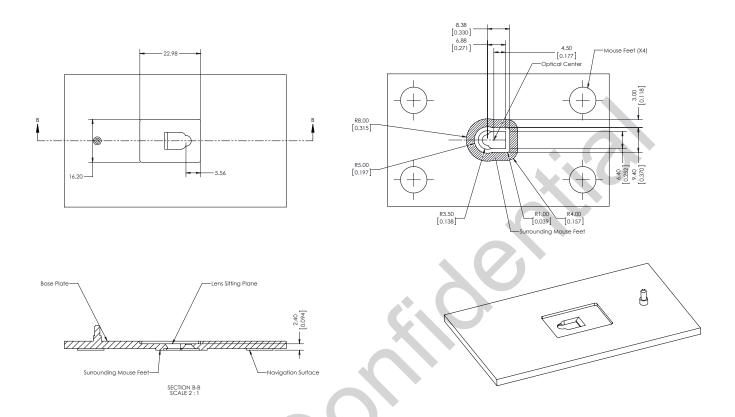

Figure 10. PAW3335DB-TZDU Reference Mouse Schematic

PixArt recommends to use HSDL-4261IR LED with the PAW3335DB-TZDU chip. Table 9 shows the recommended value of  $R_{LED}$  and  $V_{LED}$  to obtain 24mA current for LED. Recommend to use  $R_{LED}$  with 1% tolerance.

Table 9. Recommended RLED

| V <sub>LED</sub> (V) | Recommended $R_{LED}(\Omega)$ |

|----------------------|-------------------------------|

| 1.9                  | 18                            |

Table 10 shows the recommended value of R1 for 2MHz, 4MHz and 8MHz of serial port clock frequency. Recommend to use R1 with 1% tolerance.

Table 10. Recommended R1

| Serial Port Clock<br>Frequency (MHz) | Recommended R1 (Ω) |

|--------------------------------------|--------------------|

| 2                                    | 3.3k               |

| 4                                    | 1.0k               |

| 8                                    | 240                |

#### 4.2 PCB Assembly Recommendation

- 1. Insert the integrated chip and all other electrical components into PCB.

- 2. Wave-solder the entire assembly in a no-wash solder process utilizing solder-fixture. A solder-fixture is required to protect the chip from flux spray and wave solder.

- 3. Avoid getting any solder flux onto the chip body as there is potential for flux to seep into the chip package. The solder fixture should be designed to expose only the chip leads to flux spray & molten solder while shielding the chip body and optical apertures. The fixture should also set the chip at the correct position and height on the PCB.

- 4. Place the lens onto the base plate. Care must be taken to avoid contamination on the optical surfaces.

- 5. Remove the protective kapton tapes from optical apertures of the chip. Care must be taken to prevent contaminants from entering the apertures. Do not place the PCB with the chip facing up during the entire product assembly process. Hold the PCB vertically when removing kapton tape.

- 6. Remove the protective kapton tapes from optical apertures of the chip. Care must be taken to prevent contaminants from entering the apertures. Do not place the PCB with the chip facing up during the entire mouse assembly process. Hold the PCB vertically when removing kapton tape.

- 7. Insert PCB assembly over the lens onto the base plate aligning post to retain PCB assembly. The chip package will self-align to the lens via the guide posts. The optical position reference for the PCB is set by the base plate and lens. Note that the PCB motion due to button presses must be minimized to maintain optical alignment.

- 8. Install mouse top case. There must be a feature in the top case to press down onto the PCB assembly to ensure all components are stacked or interlocked to the correct vertical height

### 5.0 Power States & Sequence

### 5.1 Power-Up Sequence

Although the sensor performs an internal power up self-reset, it is still recommend that the Power\_Up\_Reset register is written every time power is applied. The appropriate sequence is as follows:

- 1. Apply power to VDD.

- 2. Wait for 50ms.

- 3. Drive NCS high, and then low to reset the SPI port.

- 4. Write 0x5A to Power\_Up\_Reset register.

- 5. Wait for at least 5ms.

- 6. Load Power-up initialization register setting.

- 7. Read from registers 0x02, 0x03, 0x04, 0x05 and 0x06 one time regardless of the motion bit state.

### 5.2 Power-Up Initialization Register Setting

- Write register 0x40 with value 0x80

- Write register 0x55 with value 0x01

- Wait for at least 1ms

- Write register 0x7F with value 0x0E

- Write register 0x43 with value 0x1D

- Read register 0x46 and store in Var"R1"

- Write register 0x43 with value 0x1E

- Read register 0x46 and store in Var"R2"

- Write register 0x7F with value 0x14

- Write register 0x6A with value "R1"

- Write register 0x6C with value "R2"

- Write register 0x7F with value 0x00

- Write register 0x55 with value 0x00

- Write register 0x4E with value 0x23

- Write register 0x77 with value 0x18

- Write register 0x7F with value 0x05

- Write register 0x53 with value 0x0C

- Write register 0x5B with value 0xEA

- Write register 0x61 with value 0x13

- Write register 0x62 with value 0x0B

- Write register 0x64 with value 0xD8

- Write register 0x6D with value 0x86

- Write register 0x7D with value 0x84Write register 0x7E with value 0x00

- Write register 0x7F with value 0x06

- Write register 0x60 with value 0x80

- Write register 0x61 with value 0x00

- Write register 0x7E with value 0x40

- Write register 0x7F with value 0x0A

- Write register 0x4A with value 0x23

- Write register 0x4C with value 0x28

- Write register 0x49 with value 0x00

- Write register 0x4F with value 0x02

- Write register 0x7F with value 0x07

- Write register 0x42 with value 0x16

- Write register 0x7F with value 0x09

- Write register 0x40 with value 0x03

- Write register 0x7F with value 0x0C

- Write register 0x54 with value 0x00

- Write register 0x44 with value 0x44

- Write register 0x56 with value 0x40

- Write register 0x42 with value 0x0C

- Write register 0x43 with value 0xA8

- Write register 0x4E with value 0x8B

- Write register 0x59 with value 0x63

- Write register 0x7F with value 0x0D

- Write register 0x5E with value 0xC3

- Write register 0x4F with value 0x02

- Write register 0x4F with value 0x02

- Write register 0x4A with value 0x67

- Write register 0x6D with value 0x82

- Write register oxob with value oxoz

- Write register 0x73 with value 0x83

- Write register 0x74 with value 0x00

- Write register 0x7A with value 0x16

- Write register 0x63 with value 0x14

- Write register 0x62 with value 0x14

- Write register 0x7F with value 0x10

- Write register 0x48 with value 0x0F

- Write register 0x49 with value 0x88

- Write register 0x4C with value 0x1D

- Write register 0x4F with value 0x08

- Write register 0x51 with value 0x6F

- Write register 0x52 with value 0x90

- Write register 0x54 with value 0x64

- Write register 0x55 with value 0XF0

- Write register 0x5C with value 0x40

- Write register 0x61 with value 0xEE

- Write register 0x62 with value 0xE5

- Write register 0x7F with value 0x00

- Write register 0x5B with value 0x40Write register 0x61 with value 0xAD

- Write register 0x51 with value 0xEA

- Write register 0x19 with value 0x9F

- Read register 0x20 at 1ms interval until 0x0F is obtained of read up to 55ms, this register read interval must be carried out at 1ms interval with timing tolerance of +/- 1%.

- Write register 0x19 with value 0x10

- Write register 0x61 with value 0xD5

- Write register 0x40 with value 0x00

- Write register 0x7F with value 0x00

- Write register 0x77 with value 0x2F

- Write register 0x7F with value 0x0D

- Write register 0x4E with value 0x6B

- Write register 0x7F with value 0x05

- Write register 0x44 with value 0xA8

- Write register 0x4A with value 0x14

- Write register 0x7F with value 0x00

- Write register 0x4F with value 0x46

- Write register 0x4D with value 0xD0

During power-up there will be a period of time after the power supply is high but before any clocks are available. The table below shows the state of the various pins during power-up and reset.

Table 11. State of Signal Pins after VDD is Valid

| Pin   | After Reset    |

|-------|----------------|

| NCS   | Functional     |

| SCLK  | Depends on NCS |

| SDIO  | Depends on NCS |

| XYLED | Functional     |

#### 5.3 Power-Down Sequence

PAW3335DB-TZDU can be set in Shutdown mode by writing to Shutdown register 0x3B with value 0xB6. The SPI port should not be accessed when Shutdown mode is asserted, except the power-up command (writing 0x5A to register 0x3A). Other ICs on the same SPI bus can be accessed, as long as the chip's NCS pin is not asserted.

To de-assert Shutdown mode:

- 1. Drive NCS high, and then low to reset the SPI port.

- 2. Write 0x5A to Power\_Up\_Reset register.

- 3. Wait for at least 5ms.

- 4. Load power up initialization register setting as per Section 5.0, step 6.

- 5. Read from registers 0x02, 0x03, 0x04, 0x05 and 0x06 one time regardless of the motion bit state.

Table 12. Status during Shutdown Mode

| Pin   | Status during Shutdown Mode |

|-------|-----------------------------|

| NCS   | High *1                     |

| SCLK  | Ignore if NCS = 1 *2        |

| SDIO  | Ignore if NCS = 1*3         |

| XYLED | High                        |

<sup>\*1.</sup> NCS pin must be held to 1 (high) if SPI bus is shared with other devices. It must be held to 1 (high) during Shutdown unless powering up the chip. It must be held to 0 (low) if the chip is to be re-powered up from shutdown (writing 0x5A to register 0x3A).

<sup>\*2.</sup> SCLK is ignored if NCS is 1 (high). It is functional if NCS is 0 (low).

<sup>\*3.</sup> SDIO should be pulled up during Shutdown in order to meet the low power consumption specification in the data sheet.

### 6.0 Serial Peripheral Interface Communication

#### 6.1 Signal Description

The synchronous serial port is used to write and read parameters in the chip. The port is a three wire serial port. The host micro-controller always initiates communication and the chip never initiates communication. SCLK, SDIO & NCS may be driven directly by a micro-controller. The port pins cannot be shared with other SPI slave devices. When the NCS pin is high, the inputs are ignored.

The lines that comprise the SPI port:

| Pin  | Description                                                                                            |

|------|--------------------------------------------------------------------------------------------------------|

| SCLK | Clock input, generated by the master (microcontroller).                                                |

| SDIO | Input/output data                                                                                      |

| NCS  | Chip select input (active low). NCS can also be used to reset the serial port in the event of an error |

### 6.2 Motion Bit Timing

The motion bit is an output that signals the micro-controller when motion has occurred. The motion bit turns to "1" whenever the motion is detected; in other words, whenever there is non-zero data in the Delta\_X\_L, Delta\_X\_H, Delta\_Y\_L or Delta\_Y\_H registers. Clearing the motion bit by reading MOTION registers will set the Motion bit back to "0".

### 6.3 Chip Select Operation

The serial port is activated after NCS goes low. If NCS is raised during a transaction, the entire transaction is aborted and the serial port will reset. After a transaction is aborted, the normal address-to-data or transaction-to-transaction delay is still required before beginning the next transaction. In order to improve communication reliability, all serial transactions should be framed by NCS.

In other words, the port should not remain enabled during periods of non-use because ESD and EFT/B events could be interpreted as serial communication and set the chip into unknown state. In addition, NCS must be raised after each burst-mode transaction is complete to terminate burst-mode. The port is not available for further use until burst-mode is terminated.

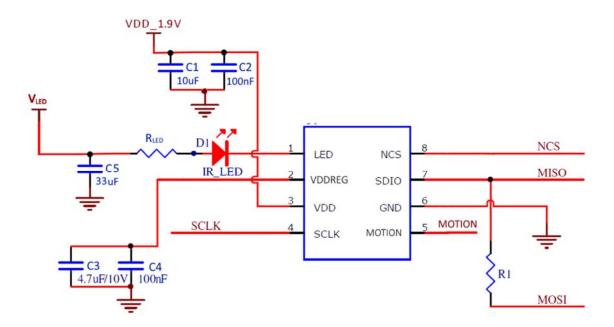

#### 6.4 Write Operation

Write operation is defined as data going from the micro-controller to the chip. It is always initiated by the micro-controller and consists of two bytes. The first byte contains the address (seven bits) and has a "1" as its MSB to indicate write sequence. The second byte contains the data. The chip reads SDIO on the rising edges of SCLK.

SDIO DRIVEN BY MICRO-CONTROLLER

Figure 11. Write Operation

Figure 12. SDIO Setup & Hold Time during write operation

#### 6.5 Read Operation

A read operation is defined as data going from the chip to the microcontroller. It is always initiated by the microcontroller and consists of two bytes. The first byte contains the address, is sent by the microcontroller over SDIO and has a "0" as its MSB to indicate data direction. The second byte contains the data and is driven by the chip over SDIO. The chip outputs SDIO bits on falling edges of SCLK and samples SDIO bits on every rising edge of SCLK.

Figure 13. Read Operation

Figure 14. SDIO Delay & Hold Time during read operation

**Note:** The high state of SCLK is also the SDIO data hold time of the chip. The falling edge of SCLK is the start of the next read or write command, the chip will hold the state of data on SDIO until the falling edge of SCLK.

#### 6.6 Required Timing between Read and Write Commands

Required timing between Read and Write Commands (tsxx).

There are minimum timing requirements between read and write commands on the serial port.

Figure 15. Timing between two Write commands

If the rising edge of the SCLK for the last data bit of the second write command occurs before the required delay (t<sub>sww</sub>), then the first write command may not complete correctly.

Figure 16. Timing between Write & Read commands

If the rising edge of SCLK for the last address bit of the read command occurs before the required delay (t<sub>SWR</sub>), the write command may not complete correctly.

Figure 17. Timing between Read & Subsequent Write or Read commands

If the rising edge of SCLK for the last address bit of the read command occurs before the  $t_{SWR}$  required delay, the write command may not be completed correctly. During a read operation SCLK should be delayed at least  $t_{SRAD}$  after the last address data bit to ensure that the chip has sufficient time to prepare the requested data.

The falling edge of SCLK for the first address bit of either the read or write command must be at least 2us after the last SCLK rising edge of the last data bit of the previous read operation. In addition, during a read operation SCLK should be delayed after the last address data bit to ensure that the chip has sufficient time to prepare the requested data.

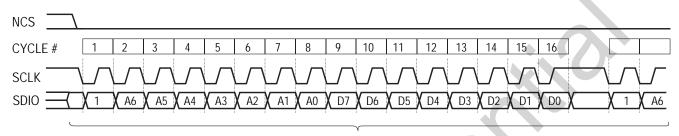

#### 6.7 Burst Mode Operation

Burst mode is a special serial port operation mode which may be used to reduce the serial transaction time for predefined registers. The speed improvement is achieved by continuous data clocking to or from multiple registers without the need to specify the register address and by not requiring the normal delay period between data bytes.

Figure 18. Motion Burst Timing

#### **Motion Burst Read**

Reading the Burst\_Motion\_Read register activates this mode. The chip will respond with the following motion burst report in order. Motion burst report:

BYTE[00] = Motion

BYTE[01] = Chip Observation

BYTE[02] = Delta\_X\_L

BYTE[03] = Delta X H

BYTE[04] = Delta Y L

BYTE[05] = Delta\_Y\_H

BYTE[06] = SQUAL

BYTE[07] = Raw\_Data\_Sum

BYTE[08] = Maximum Raw Data

BYTE[09] = Minimum Raw Data

BYTE[10] = Shutter Upper

BYTE[11] = Shutter\_Lower

After sending the register address, the microcontroller must wait for  $t_{SRAD}$ , and then begin reading data. All data bits can be read with no delay between bytes by driving SCLK at the normal rate. The data are latched into the output buffer after the last address bit is received. After the burst transmission is complete, the microcontroller must raise the NCS line for at least  $t_{BEXIT}$  to terminate burst mode. The serial port is not available for use until it is reset with NCS, even for a second burst transmission.

#### Procedure to start motion burst as below.

- 1. Pull NCS line to low.

- 2. Read Motion\_Burst register (address 0x16).

- 3. Wait for t<sub>SRAD</sub>.

- 4. Start reading SPI Data continuously up to 12 bytes.

Motion burst may be terminated by pulling NCS high for at least t<sub>BEXIT</sub>.

- 5. To read new motion burst data, start again from step 1.

Burst mode must be terminated by the micro-controller by raising the NCS line for at least  $t_{\text{BEXIT}}$ . The serial port is not available for use until it is reset with NCS signal, even for a second Burst transmission.

**Note:** Motion burst data can be read from Motion\_Burst register even in rest modes.

Version 1.12 | 27 June 2019 | 11032EN

SEE. FEEL. TOUCH.

#### 7.0 RawData Grab

Rawdata grab is the way to download a full array of rawdata values from a single frame. Once rawdata grab is enabled, the next complete frame image will be stored to memory. In order to stream out the RawData values, register read operation is used.

Procedure to start frame capture burst mode is listed as below:

- 1. Write register 0x7F with value 0x00

- 2. Write register 0x40 with value 0x80

- 3. Write register 0x7F with value 0x13

- 4. Write register 0x47 with value 0x30

- 5. Write register 0x7F with value 0x00

- 6. Write register 0x55 with value 0x04

- 7. Continuously read register 0x02 until getting both OP\_Mode1 and OP\_Mode0 equal to 0.

- 8. Write register 0x58 with value 0xFF

- 9. Continuously read register 0x59 until getting PG\_FIRST as "1"

- 10. Continuously read register 0x59 until getting PG VALID as "1".

- 11. Read register 0x58 for 7 bit ADC data (RAWDATA 6-0). Repeat (10) and (11) for 900 times to form a complete picture element array information.

- 12. Write register 0x55 with value 0x00

- 13. Write register 0x40 with value 0x00

- 14. Write register 0x7F with value 0x13

- 15. Write register 0x47 with value 0x20

- 16. Write register 0x7F with value 0x00

Figure 19. RawData Address Map for 30x30 (Chip looking on the navigation surface through the lens)

**Note**: The X/Y reporting direction shown above follows all the power up initialization sequence in the Power Up section.

### 8.0 Power Management for Wireless Mode

PAW3335DB-TZDU has three power-saving modes. Each mode has a different motion detection period with its respective response time to mouse motion. Response time is the time taken for the chip to 'wake up' from rest mode when motion is detected. When left idle, the chip automatically changes or downshift from Run mode to Rest1, then to Rest2 and finally to Rest3 which consumes the least amount of current.

The current consumption is lowest at Rest3 and highest at Rest1. However the time required for chip to respond to motion from Rest1 is the shortest and longest from Rest3. Downshift time is the elapsed time (under no motion condition) from an existing mode to the next mode. For example, it takes 20s for the chip which is in Rest1 mode to change (downshift) to Rest2. The response time and downshift time for each mode is shown in the following table.

However user can change the timing setting for each mode via register 0x77 through 0x7C.

Table 13. Rest Modes Response & Downshift Time

| Mode  | Response Time | Downshift Time |

|-------|---------------|----------------|

| Rest1 | 1ms           | 512ms          |

| Rest2 | 32ms          | 20s            |

| Rest3 | 500ms         | 600s           |

**Note:** These timings are based on Power-Up Initialization Register Setting in section 5.0 and subjected to change if any of the register 0x77 to 0x7C value is updated

## 9.0 Universal Lift Cut Off Setting

The Universal Lift Cut Off setting applies to all PixArt Standard Gaming Surfaces. The lift-cut off can be set to 1mm and 2mm when mated with the LOAC lens, per the register settings in the table below.

Please note that upon sensor start-up per the recommended Power-Up Sequence, the lift cut off is set to 1mm as default.

Table 14. Lift Cut Off Setting for LOAC-LSG1

| Lens      | Lift Cut Off Setting | Register Setting                      |

|-----------|----------------------|---------------------------------------|

|           |                      | - Write register 0x7F with value 0x0C |

|           |                      | - Write register 0x40 with value 0xA0 |

|           |                      | - Write register 0x41 with value 0x70 |

|           |                      | - Write register 0x42 with value 0x0C |

|           |                      | - Write register 0x43 with value 0xA8 |

|           |                      | - Write register 0x44 with value 0x44 |

|           | 1mm setting          | - Write register 0x45 with value 0x04 |

|           | (Default in Power Up | - Write register 0x4A with value 0x19 |

|           | Sequence)            | - Write register 0x4B with value 0x18 |

|           | Sequence             | - Write register 0x4C with value 0x60 |

|           |                      | - Write register 0x4E with value 0x8B |

|           |                      | - Write register 0x54 with value 0x00 |

|           |                      | - Write register 0x56 with value 0x40 |

|           |                      | - Write register 0x59 with value 0x63 |

|           |                      | - Write register 0x6D with value 0x7F |

| LOAC-LSG1 |                      | - Write register 0x7F with value 0x00 |

| LUAC LOGI | X                    | - Write register 0x7F with value 0x0C |

|           |                      | - Write register 0x40 with value 0x14 |

|           |                      | - Write register 0x41 with value 0x14 |

|           |                      | - Write register 0x42 with value 0x20 |

|           |                      | - Write register 0x43 with value 0x18 |

|           |                      | - Write register 0x44 with value 0xC7 |

|           |                      | - Write register 0x45 with value 0x05 |

|           | 2mm setting          | - Write register 0x4A with value 0x0A |

|           | Ziiiiii Settiiig     | - Write register 0x4B with value 0x08 |

|           |                      | - Write register 0x4C with value 0x45 |

|           |                      | - Write register 0x4E with value 0x0F |

|           |                      | - Write register 0x54 with value 0x00 |

|           |                      | - Write register 0x56 with value 0x2A |

|           |                      | - Write register 0x59 with value 0x93 |

|           |                      | - Write register 0x6D with value 0x5F |

|           |                      | - Write register 0x7F with value 0x00 |

### 10.0 Registers

### 10.1 Registers List

The chip registers are accessible via the serial port. The registers are used to read motion data and status as well as to set the device configuration.

Table 15. Register List

| Address | Register Name         | Access | Reset Value |

|---------|-----------------------|--------|-------------|

| 0x00    | Product_ID            | R      | 0x4E        |

| 0x02    | Motion                | RW     | 0x20        |

| 0x03    | Delta_X_L             | R      | 0x00        |

| 0x04    | Delta_X_H             | R      | 0x00        |

| 0x05    | Delta_Y_L             | R      | 0x00        |

| 0x06    | Delta_Y_H             | R      | 0x00        |

| 0x07    | SQUAL                 | R      | 0x00        |

| 0x08    | Raw_Data_Sum          | R      | 0x00        |

| 0x09    | Maximum_ Raw_Data     | R      | 0x00        |

| 0x0A    | Minimum_ Raw_Data     | R      | 0x7F        |

| 0x0B    | Shutter_Lower         | R      | 0x00        |

| 0x0C    | Shutter_Upper         | R      | 0x01        |

| 0x15    | Chip_Observation      | RW     | 0x40        |

| 0x16    | Burst_Motion_Read     | R      | 0x00        |

| 0x3A    | Power_Up_Reset        | W      | 0x00        |

| 0x3B    | Shutdown              | W      | 0x00        |

| 0x40    | Performance           | RW     | 0x00        |

| 0x4E    | Resolution            | RW     | 0x12        |

| 0x56    | Angle_Snap            | RW     | 0x04        |

| 0x58    | Raw_Data _Grab        | RW     | 0x00        |

| 0x59    | Raw_Data _Grab_Status | R      | 0x00        |

| 0x5A    | Ripple_Control        | RW     | 0x10        |

| 0x5B    | Axis_Control          | RW     | 0x60        |

| 0x5F    | Inv_Product_ID        | R      | 0xB1        |

| 0x77    | Run_DownShift         | RW     | 0x0C        |

| 0x78    | Rest1_Period          | RW     | 0x01        |

| 0x79    | Rest1_Downshift       | RW     | 0x4F        |

| 0x7A    | Rest2_Period          | RW     | 0x08        |

| 0x7B    | Rest2_Downshift       | RW     | 0x4A        |

| 0x7C    | Rest3_Period          | RW     | 0x3F        |

| 0x7D    | Run_Downshift_Mult    | RW     | 0x07        |

| 0x7E    | Rest_Downshift_Mult   | RW     | 0x77        |

#### 10.2 Register Descriptions

| Register Name | Product_ID |   |   |                                    |       |      |   |   |

|---------------|------------|---|---|------------------------------------|-------|------|---|---|

| Address       | 0x00       |   |   |                                    |       |      |   |   |

| Access        | Read       |   |   | Reset                              | Value | 0x4E |   |   |

| Bit           | 7          | 6 | 5 | 4                                  | 3     | 2    | 1 | 0 |

| Field         |            |   |   | PID                                | 7-0   |      |   |   |

| Description   |            |   |   | ification assig<br>sed to verify t |       |      |   |   |

| Register Name | Motion     |          |   |             |             |          |                      |                      |

|---------------|------------|----------|---|-------------|-------------|----------|----------------------|----------------------|

| Address       | 0x02       |          |   |             | <b>\</b> () |          |                      |                      |

| Access        | Read/Write |          |   | Reset Value |             | 0x20     |                      |                      |

| Bit           | 7          | 6        | 5 | 4           | 3           | 2        | 1                    | 0                    |

| Field         | MOT        | Reserved | 1 | Reserved    | Reserved    | Reserved | OP_Mode <sub>1</sub> | OP_Mode <sub>0</sub> |

This register allows the user to determine if motion has occurred since the last time it was read.

The procedure to read the motion registers (Delta\_X\_L, Delta\_X\_H, Delta\_Y\_L and Delta\_Y\_H) is as follows:

- 1. Read the Motion register. This will freeze the Delta\_X\_L, Delta\_X\_H, Delta\_Y\_L and Delta\_Y\_H register values.

- 2. If the MOT bit is set, Delta\_X\_L, Delta\_X\_H, Delta\_Y\_L and Delta\_Y\_H registers should be read in the given sequence to get the accumulated motion. Note: if Delta\_X\_L, Delta\_X\_H, Delta\_Y\_L and Delta\_Y\_H registers are not read before the motion register is read for the second time, the data in Delta X L, Delta X H, Delta Y L and Delta Y H will be lost.

- 3. To read a new set of motion data (Delta\_X\_L, Delta\_X\_H, Delta\_Y\_L and Delta\_Y\_H), repeat from Step 1.

#### Description

| Field Name                                             | Description                                    |

|--------------------------------------------------------|------------------------------------------------|

| MOT                                                    | Motion since last report                       |

|                                                        | 0 = No motion                                  |

|                                                        | 1 = Motion occurred, data ready for reading in |

|                                                        | Delta_X_L, Delta_X_H, Delta_Y_L and            |

|                                                        | Delta_Y_H registers                            |

| OP_Mode <sub>1:0</sub>                                 | 00 – Run Mode                                  |

|                                                        | 01 - Rest 1                                    |

|                                                        | 10 - Rest 2                                    |

|                                                        | 11 - Rest 3                                    |

| Write any value to this register will clear all motion | n data.                                        |

Version 1.12 | 27 June 2019 | 11032EN

SEE. FEEL. TOUCH.

| Register Name | DELTA_X_L      |                |                       |                |                |                |                |                |

|---------------|----------------|----------------|-----------------------|----------------|----------------|----------------|----------------|----------------|

| Address       | 0x03           |                |                       |                |                |                |                |                |

| Access        | Read           |                |                       | Reset          | Value          | 0x00           |                |                |

| Bit           | 7              | 6              | 5                     | 4              | 3              | 2              | 1              | 0              |

| Field         | X <sub>7</sub> | X <sub>6</sub> | <b>X</b> <sub>5</sub> | X <sub>4</sub> | X <sub>3</sub> | X <sub>2</sub> | X <sub>1</sub> | X <sub>0</sub> |

|               |                |                |                       |                |                |                |                |                |

16 bits 2's complement number. Lower 8 bits of Delta\_X.

X movement is counts since last report. Absolute value is determined by resolution.

| Description | Motion  | -32768 | -32767 |               | -2   | -1   | 0   | +1  | +2  |        | +32766 | +32767 |  |

|-------------|---------|--------|--------|---------------|------|------|-----|-----|-----|--------|--------|--------|--|

| •           |         |        | v      | 11            |      |      | Ĭ   |     |     | 11     |        | 100    |  |

|             |         | _      | _      | $\neg \vdash$ | _    | _    | _   | _   | _   | $\neg$ |        | _      |  |

|             |         | 1      | - 1    | ))            | 1    | - 1  | - 1 | - 1 | - 1 | ))     | - 1    | - 1    |  |

|             | Delta_X | 8000   | 8001   |               | FFFE | FFFF | 00  | 01  | 02  |        | 7FFE   | 7FFF   |  |

|             |         |        |        |               |      |      |     |     | 7   | ,      |        |        |  |

| Register Name | DELTA_X_H       |                 |                 |                              |                     |                 |                |                |

|---------------|-----------------|-----------------|-----------------|------------------------------|---------------------|-----------------|----------------|----------------|

| Address       | 0x04            |                 |                 |                              |                     |                 |                |                |

| Access        | Read            |                 |                 | Reset Value                  |                     | 0x00            |                |                |

| Bit           | 7               | 6               | 5               | 4                            | 3                   | 2               | 1              | 0              |

| Field         | X <sub>15</sub> | X <sub>14</sub> | X <sub>13</sub> | X <sub>12</sub>              | X <sub>111</sub>    | X <sub>10</sub> | X <sub>9</sub> | X <sub>8</sub> |

| Description   | Delta_X_H m     | ust be read     | after Delta_    | x_L to have the rox02, 0x03, | –<br>he full motior |                 | e read seque   | ntially.       |

| Register Name | DELTA_Y_I      | L              |                 |                |           |                |                |                |                |

|---------------|----------------|----------------|-----------------|----------------|-----------|----------------|----------------|----------------|----------------|

| Address       | 0x05           |                |                 |                |           |                |                |                |                |

| Access        | Read           |                |                 | Re             | eset Valu | ıe             | 0x00           |                |                |

| Bit           | 7              | 6              | 5               | 4              |           | 3              | 2              | 1              | 0              |

| Field         | Y <sub>7</sub> | Y <sub>6</sub> | Y <sub>5</sub>  | Y <sub>4</sub> |           | Y <sub>3</sub> | Y <sub>2</sub> | Y <sub>1</sub> | Y <sub>0</sub> |

| Description   | Y movemen      | -32768 -327    | since last repo | ort. Absolu    | te value  | +1             | +2             | +32766 +3276   | 7              |

|               | Delta Y        | 8000 80        | 01 FFF          | E FFFF         | 00        | 01             | 02             | 7FFE 7FFF      |                |

| Register Name | DELTA_Y_H       |                                                                                                       |                 |                  |                 |                 |            |                |  |  |  |

|---------------|-----------------|-------------------------------------------------------------------------------------------------------|-----------------|------------------|-----------------|-----------------|------------|----------------|--|--|--|

| Address       | 0x06            |                                                                                                       |                 |                  |                 |                 |            |                |  |  |  |

| Access        | Read            |                                                                                                       |                 | Reset Value      |                 | 0x00            |            |                |  |  |  |

| Bit           | 7               | 6                                                                                                     | 5               | 4                | 3               | 2               | 1          | 0              |  |  |  |

| Field         | Y <sub>15</sub> | Y <sub>14</sub>                                                                                       | Y <sub>13</sub> | Y <sub>12</sub>  | Y <sub>11</sub> | Y <sub>10</sub> | <b>Y</b> 9 | Y <sub>8</sub> |  |  |  |

| Description   |                 |                                                                                                       |                 | per 8 bits of De | _               | n data.         |            |                |  |  |  |

|               | Note: It is re  | <b>Note:</b> It is recommended that register 0x02, 0x03, 0x04, 0x05 and 0x06 to be read sequentially. |                 |                  |                 |                 |            |                |  |  |  |

| Register Name | SQUAL                                        |                                           |                                                                   |                                                                                                       |                             |                                                  |                                        |                 |

|---------------|----------------------------------------------|-------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------|----------------------------------------|-----------------|

| Address       | 0x07                                         |                                           |                                                                   |                                                                                                       |                             |                                                  |                                        |                 |

| Access        | Read                                         |                                           |                                                                   | Reset                                                                                                 | : Value                     | 0x00                                             |                                        |                 |

| Bit           | 7                                            | 6                                         | 5                                                                 | 4                                                                                                     | 3                           | 2                                                | 1                                      | 0               |

| Field         | SQ <sub>7</sub>                              | SQ <sub>6</sub>                           | SQ₅                                                               | SQ <sub>4</sub>                                                                                       | SQ₃                         | SQ <sub>2</sub>                                  | SQ <sub>1</sub>                        | SQ <sub>0</sub> |

| Description   | chip in the  Number of  The maxim changes in | reatures = S<br>um SQUAL r<br>SQUAL, vari | ne. Use the for<br>SQUAL Regist<br>egister value<br>ations in SQL | r is a measure<br>ollowing form<br>er Value * 4<br>is 0xB6. Since<br>JAL when lool<br>hip is in run m | ula to find the small chang | e total numb<br>ges in the cur<br>ace is expecte | er of valid fe<br>rent frame ca<br>ed. | atures.         |

| Register Name | RAWDATA_                              | SUM                                                             |                                                  |                                                                             |                                  |                  |                  |                      |

|---------------|---------------------------------------|-----------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------|------------------|------------------|----------------------|

| Address       | 0x08                                  |                                                                 |                                                  |                                                                             |                                  |                  |                  |                      |

| Access        | Read                                  |                                                                 |                                                  | Reset                                                                       | Value                            | 0x00             |                  |                      |

| Bit           | 7 6 5                                 |                                                                 |                                                  | 4                                                                           | 3                                | 2                | 1                | 0                    |

| Field         | RDS <sub>7</sub>                      | RDS <sub>6</sub>                                                | RDS <sub>5</sub>                                 | RDS <sub>4</sub>                                                            | RDS₃                             | RDS <sub>2</sub> | RDS <sub>1</sub> | RDS <sub>0</sub>     |

| Description   | counter white follows the Average pix | ich sums all 9<br>formula belo<br>el value = PIX<br>um register | 900 rawdata<br>ow:<br>X_ACCUM*5:<br>value is 0xD | average rawda<br>in the current<br>12/900<br>F(hex) or 223<br>rframe. Disab | t frame. To fii<br>B(dec) and th | nd the averag    | ge rawdata vo    | alue<br>ue is 0. The |

| Register Name | MAXIMUM          | _RAWDATA                                                                                                                          |                  |                  |                  |                  |         |                  |

|---------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|------------------|---------|------------------|

| Address       | 0x09             |                                                                                                                                   |                  |                  |                  |                  |         |                  |

| Access        | Read             |                                                                                                                                   |                  | Reset            | Value            | 0x00             |         |                  |

| Bit           | 7                | 6                                                                                                                                 | 5                | 4                | 3                | 2                | 1       | 0                |

| Field         | MRD <sub>7</sub> | $MRD_6$                                                                                                                           | MRD <sub>5</sub> | MRD <sub>4</sub> | MRD <sub>3</sub> | MRD <sub>2</sub> | $MRD_1$ | MRD <sub>0</sub> |

| Description   |                  | Maximum RawData value in current frame. Minimum value = 0, maximum value = 127. The maximum rawdata value can change every frame. |                  |                  |                  |                  |         |                  |

| Register Name | MINIMUM_           | RAWDATA   |                                  |                     |                    |                    |               |                    |

|---------------|--------------------|-----------|----------------------------------|---------------------|--------------------|--------------------|---------------|--------------------|

| Address       | 0x0A               | 0x0A      |                                  |                     |                    |                    |               | _                  |

| Access        | Read               |           |                                  | Reset               | : Value            | 0x7F               |               |                    |

| Bit •         | 7                  | 6         | 5                                | 4                   | 3                  | 2                  | 1             | 0                  |

| Field         | MinRD <sub>7</sub> | $MinRD_6$ | MinRD <sub>5</sub>               | MinRD <sub>4</sub>  | MinRD <sub>3</sub> | MinRD <sub>2</sub> | $MinRD_1$     | MinRD <sub>0</sub> |

| Description   |                    |           | e in current fr<br>ge every fram | rame. Minimu<br>ne. | um value = 0,      | maximum va         | lue = 127. Th | e minimum          |

| Register Name | SHUTTER_L      | SHUTTER_LOWER  |                |                |                |                |       |                |  |  |

|---------------|----------------|----------------|----------------|----------------|----------------|----------------|-------|----------------|--|--|

| Address       | 0x0B           |                |                |                |                |                |       |                |  |  |

| Access        | Read           |                |                | Reset          | Value          | 0x00           |       |                |  |  |

| Bit           | 7              | 6              | 5              | 4              | 3              | 2              | 1     | 0              |  |  |

| Field         | S <sub>7</sub> | S <sub>6</sub> | S <sub>5</sub> | S <sub>4</sub> | S <sub>3</sub> | S <sub>2</sub> | $S_1$ | S <sub>0</sub> |  |  |

| Description   | Lower byte     | of the 12-bit  | Shutter regi   | ster.          |                |                |       |                |  |  |

| Register Name | SHUTTER_L                 | SHUTTER_UPPER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                              |            |                             |                                                                    |                                 |                                                                 |  |  |