# Numonyx<sup>®</sup> Embedded Flash Memory (J3 65 nm) Single Bit per Cell (SBC)

32, 64, and 128 Mbit

## **Datasheet**

## **Product Features**

- Architecture

- Symmetrical 128-KB blocks

- 128 Mbit (128 blocks)

- 64 Mbit (64 blocks)

- 32 Mbit (32 blocks)

- Blank Check to verify an erased block

- Performance

- Initial Access Speed: 75ns

- 25 ns 8-word Asynchronous page-mode reads

- 256-Word write buffer for x16 mode, 256-Byte write buffer for x8 mode;

1.41 µs per Byte Effective programming time

- System Voltage

- $V_{CC} = 2.7 V \text{ to } 3.6 V$

- $V_{CCQ} = 2.7 V \text{ to } 3.6 V$

- Packaging

- 56-Lead TSOP

- 64-Ball Easy BGA package

- Security

- Enhanced security options for code protection

- Absolute protection with  $V_{PEN} = Vss$

- Individual block locking

- Block erase/program lockout during power transitions

- Password Access feature

- One-Time Programmable Register:

64 OTP bits, programmed with unique information by Numonyx

64 OTP bits, available for customer programming

- Software

- Program and erase suspend support

- Numonyx<sup>®</sup> Flash Data Integrator (FDI)

- Common Flash Interface (CFI) Compatible

- Scalable Command Set

- Quality and Reliability

- Operating temperature: -40 °C to +85 °C

- 100K Minimum erase cycles per block

- 65 nm Flash Technology

- JESD47E Compliant

8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-3900

www.micron.com/productsupport Customer Comment Line: 800-932-4992

Micron and the Micron logo are trademarks of Micron Technology, Inc.

All other trademarks are the property of their respective owners.

This data sheet contains minimum and maximum limits specified over the power supply and temperature range set forth herein.

Although considered final, these specifications are subject to change, as further product development and data characterization sometimes occur.

## Contents

| 1.0 | 1.1<br>1.2<br>1.3                 | AcronymsConventions                                                                                                                                                     | 6<br>7                       |

|-----|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 2.0 | Funct<br>2.1<br>2.2               | tional Overview                                                                                                                                                         | . 11                         |

| 3.0 | Packa<br>3.1<br>3.2               | age Information56-Lead TSOP Package for 32-, 64-, 128-Mbit                                                                                                              | . 13                         |

| 4.0 | <b>Ballo</b> 4.1 4.2 4.3          | uts/Pinouts and Signal Descriptions  Easy BGA Ballout for 32-, 64-, 128-Mbit  56-Lead TSOP Package Pinout for 32-, 64-,128-Mbit  Signal Descriptions                    | . 16<br>. 17                 |

| 5.0 | Maxii<br>5.1<br>5.2<br>5.3        | Mum Ratings and Operating Conditions  Absolute Maximum Ratings  Operating Conditions  Power-Up/Down  5.3.1 Power-Up/Down Sequence  5.3.2 Power Supply Decoupling  Reset | . 19<br>. 19<br>. 19<br>. 19 |

| 6.0 | 6.1<br>6.2<br>6.3                 | rical Characteristics  DC Current Specifications  DC Voltage specifications  Capacitance                                                                                | . 21<br>. 22                 |

| 7.0 | AC CH<br>7.1<br>7.2<br>7.3<br>7.4 | Paracteristics Read Specifications Program, Erase, Block-Lock Specifications Reset Specifications AC Test Conditions                                                    | . 24<br>. 28<br>. 28         |

| 8.0 | Bus I                             | nterface                                                                                                                                                                | . 30                         |

|     | 8.1                               | Bus Reads                                                                                                                                                               | . 31<br>. 31                 |

|     | 8.2<br>8.3                        | Bus WritesStandby8.3.1 Reset/Power-Down                                                                                                                                 | . 33                         |

|     | 8.4                               | Device Commands                                                                                                                                                         |                              |

| 9.0 |                                   | Operations                                                                                                                                                              |                              |

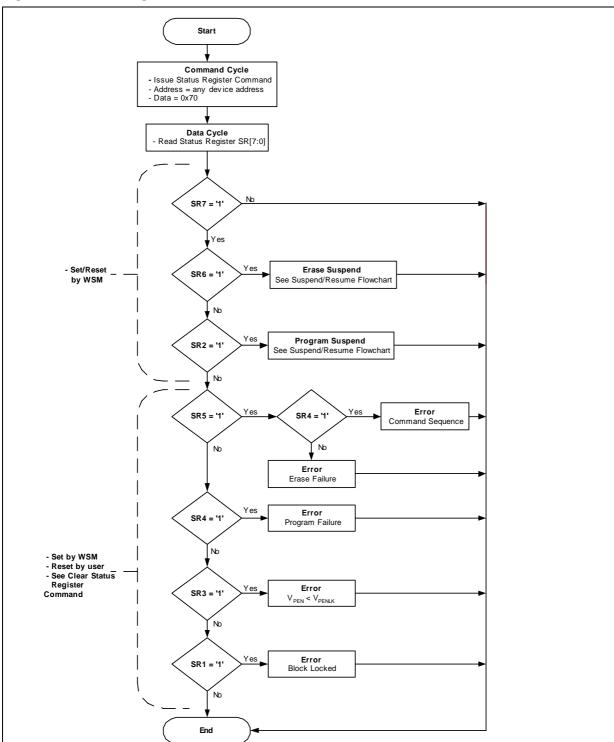

|     | 9.1                               | Status Register                                                                                                                                                         |                              |

|     | 9.2                               | 9.1.1 Clearing the Status Register                                                                                                                                      |                              |

|     | J. L                              | 9.2.1 Read Array                                                                                                                                                        |                              |

|     |                                   | 9.2.2 Read Status Register                                                                                                                                              | . 36                         |

|     |                                   | 9.2.3 Read Device Information                                                                                                                                           | . 36                         |

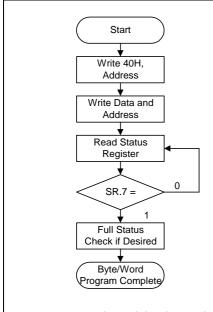

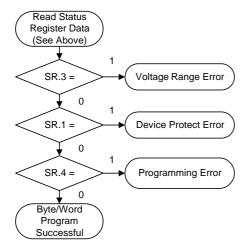

|     | 9.3                               | Programming Operations                                                                                                                                                  | . 36                         |

|      |       | 9.3.1    | Single-Word/Byte Programming                    |    |

|------|-------|----------|-------------------------------------------------|----|

|      |       | 9.3.2    | Buffered Programming                            | 37 |

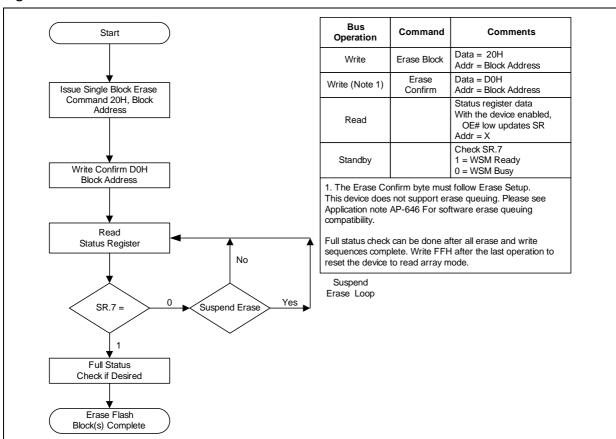

|      | 9.4   | Block E  | rase Operations                                 | 38 |

|      | 9.5   | Blank C  | Check                                           | 39 |

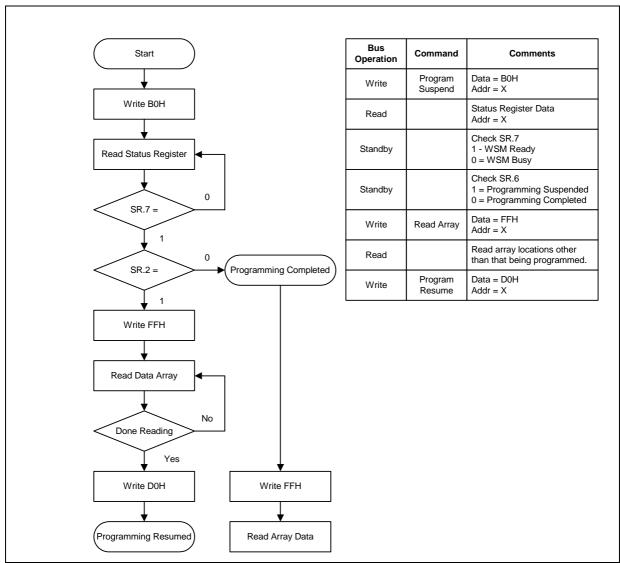

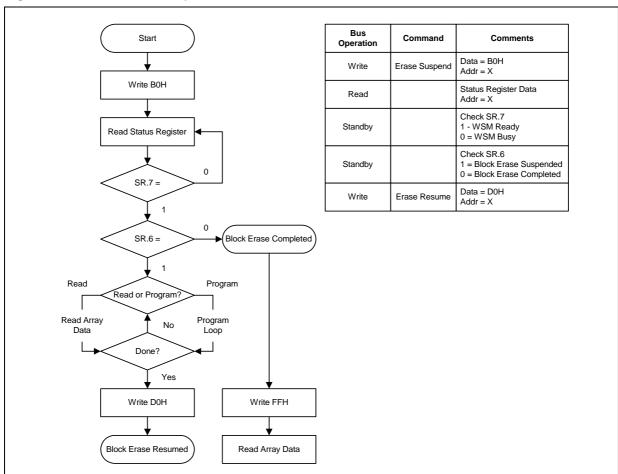

|      | 9.6   | Suspen   | nd and Resume                                   | 39 |

|      | 9.7   | Status   | Signal                                          | 41 |

|      | 9.8   | Security | y and Protection                                | 42 |

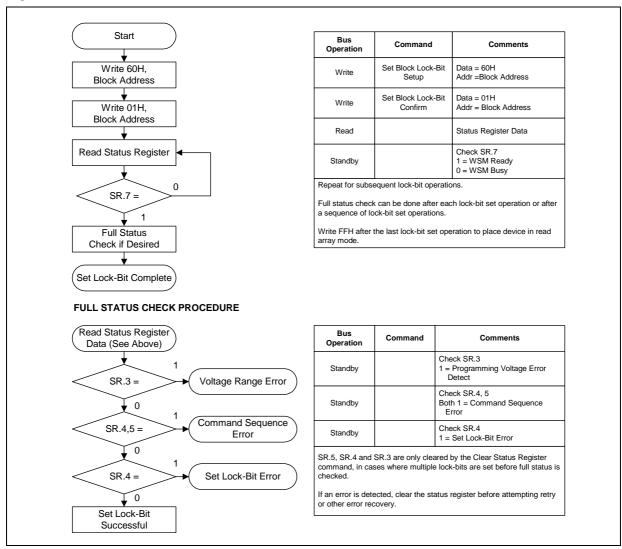

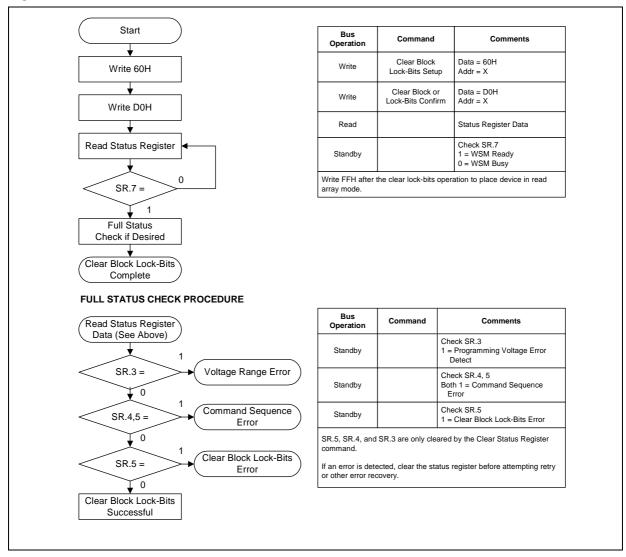

|      |       | 9.8.1    | Normal Block Locking                            | 42 |

|      |       | 9.8.2    | Configurable Block Locking                      | 43 |

|      |       | 9.8.3    | Password Access                                 | 43 |

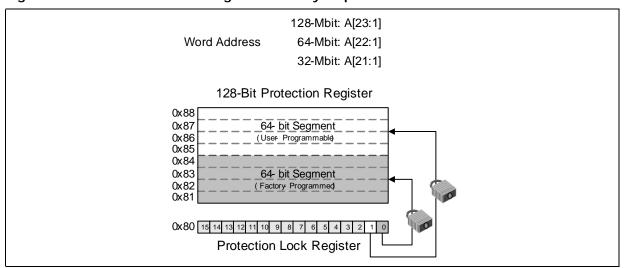

|      |       | 9.8.4    | 128-bit OTP Protection Register                 | 43 |

|      |       | 9.8.5    | Reading the 128-bit OTP Protection Register     | 43 |

|      |       | 9.8.6    | Programming the 128-bit OTP Protection Register | 43 |

|      |       | 9.8.7    | Locking the 128-bit OTP Protection Register     |    |

|      |       | 9.8.8    | VPEN Protection                                 |    |

| 10 O | ID Co | ndes     |                                                 | 46 |

|      |       |          |                                                 |    |

|      |       |          | mand Codes                                      |    |

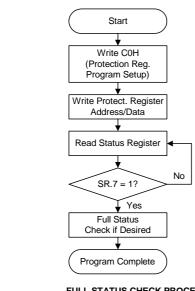

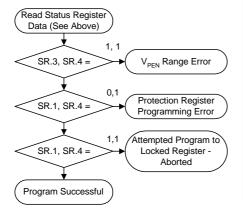

| 12.0 | Flow  | Charts.  |                                                 | 48 |

| 13.0 | Comn  | non Fla  | sh Interface                                    | 57 |

|      | 13.1  |          | Structure Output                                |    |

|      | 13.2  |          | Structure Overview                              |    |

|      | 13.3  |          | Status Register                                 |    |

|      | 13.4  |          | ery Identification String                       |    |

|      |       |          | Interface Information                           |    |

|      | 13.6  |          | Geometry Definition                             |    |

|      | 13.7  |          | y-Vendor Specific Extended Query Table          |    |

| Α    | Addit |          | nformation                                      |    |

|      |       |          |                                                 |    |

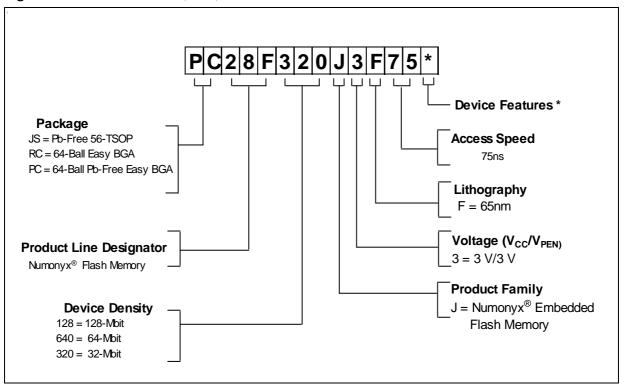

| В    | ordei | ring int | formation                                       |    |

# **Revision History**

| Date       | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| May 2009   | 01       | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| March 2010 | 02       | Add Blank Check function and command.  Add Blank Check specification tBC/MB, update Clear Block Lock-Bits Max Time and Program time in Table 13, "Configuration Performance" on page 28.  Update I <sub>CCR</sub> in Table 7, "DC Current Characteristics" on page 21.  Order information with device features digit.  Update part number information in Valid Combination table.  Add a note to clarify the SR output after E8 command in Figure 16, "Write to Buffer Flowchart" on page 48.  State JESD47E Compliant at front page.  Update ECR.13 description in Table 18, "Enhanced Configuration Register" on page 32. |

| Jan 2011   | 03       | Correct the typo of comment for offset 24h at CFI from 2048µs to 1024µs.  Correct the typo of t <sub>AVQV</sub> and t <sub>ELQV</sub> to Max Specifications.  Emphasize the valid and legal command usage at Section 11.0, "Device Command Codes" on page 47.  Put a link for part numbers after Table 46, "Valid Combinations" on page 65.  Add Buffer Program Time for 128 Words (256 Bytes) at Table 13, "Configuration Performance" on page 28.  Add JEDEC standard lead width for TSOP56 package at Table 1, "56-Lead TSOP Dimension Table" on page 13.                                                                |

| Jan 2018   | 04       | Added Important Notes and Warnings section for further clarification aligning to industry standards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## **Important Notes and Warnings**

Micron Technology, Inc. ("Micron") reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions. This document supersedes and replaces all information supplied prior to the publication hereof. You may not rely on any information set forth in this document if you obtain the product described herein from any unauthorized distributor or other source not authorized by Micron.

**Automotive Applications.** Products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets. Distributor and customer/distributor shall assume the sole risk and liability for and shall indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting directly or indirectly from any use of nonautomotive-grade products in automotive applications. Customer/distributor shall ensure that the terms and conditions of sale between customer/distributor and any customer of distributor/customer (1) state that Micron products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets and (2) require such customer of distributor/customer to indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting from any use of non-automotive-grade products in automotive applications.

Critical Applications. Products are not authorized for use in applications in which failure of the Micron component could result, directly or indirectly in death, personal injury, or severe property or environmental damage ("Critical Applications"). Customer must protect against death, personal injury, and severe property and environmental damage by incorporating safety design measures into customer's applications to ensure that failure of the Micron component will not result in such harms. Should customer or distributor purchase, use, or sell any Micron component for any critical application, customer and distributor shall indemnify and hold harmless Micron and its subsidiaries, subcontractors, and affiliates and the directors, officers, and employees of each against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, or death arising in any way out of such critical application, whether or not Micron or its subsidiaries, subcontractors, or affiliates were negligent in the design, manufacture, or warning of the Micron product.

Customer Responsibility. Customers are responsible for the design, manufacture, and operation of their systems, applications, and products using Micron products. ALL SEMICONDUCTOR PRODUCTS HAVE INHERENT FAILURE RATES AND LIMITED USEFUL LIVES. IT IS THE CUSTOMER'S SOLE RESPONSIBILITY TO DETERMINE WHETHER THE MICRON PRODUCT IS SUITABLE AND FIT FOR THE CUSTOMER'S SYSTEM, APPLICATION, OR PRODUCT. Customers must ensure that adequate design, manufacturing, and operating safeguards are included in customer's applications and products to eliminate the risk that personal injury, death, or severe property or environmental damages will result from failure of any semiconductor component.

**Limited Warranty.** In no event shall Micron be liable for any indirect, incidental, punitive, special or consequential damages (including without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort, warranty, breach of contract or other legal theory, unless explicitly stated in a written agreement executed by Micron's duly authorized representative.

## 1.0 Introduction

This document contains information pertaining to the Numonyx $^{\circledR}$  Embedded Flash Memory (J3 65 nm) Single Bit per Cell (SBC) device features, operation, and specifications.

Unless otherwise indicated throughout the rest of this document, the Numonyx $^{(\!R\!)}$  Embedded Flash Memory (J3 65 nm) Single Bit per Cell (SBC) device is referred to as J3 65 nm SBC.

The J3 65 nm SBC device provides improved mainstream performance with enhanced security features, taking advantage of the high quality and reliability of the NOR-based 65 nm technology. Offered in 128-Mbit, 64-Mbit, and 32-Mbit densities, the J3 65 nm SBC device brings reliable, low-voltage capability (3 V read, program, and erase) with high speed, low-power operation. The J3 65 nm SBC device takes advantage of proven manufacturing experience and is ideal for code and data applications where high density and low cost are required, such as in networking, telecommunications, digital set top boxes, audio recording, and digital imaging. Numonyx Flash Memory components also deliver a new generation of forward-compatible software support. By using the Common Flash Interface (CFI) and Scalable Command Set (SCS), customers can take advantage of density upgrades and optimized write capabilities of future Numonyx Flash Memory devices.

## 1.1 Nomenclature

| J3 65 nm SBC     | Numonyx <sup>®</sup> Embedded                                                      | lumonyx® Embedded Flash Memory (J3 65 nm) Single Bit per Cell (SBC) |  |  |  |  |

|------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------|--|--|--|--|

| AMIN             | All Densities                                                                      | AMIN = A0 for x8                                                    |  |  |  |  |

| AIVIIII          | All Densities                                                                      | AMIN = A1  for  x16                                                 |  |  |  |  |

|                  | 32 Mbit                                                                            | AMAX = A21                                                          |  |  |  |  |

| AMAX             | 64 Mbit                                                                            | AMAX = A22                                                          |  |  |  |  |

|                  | 128 Mbit AMAX = A23                                                                |                                                                     |  |  |  |  |

| Block            | A group of flash cells that share common erase circuitry and erase simultaneously. |                                                                     |  |  |  |  |

| Clear            | Indicates a logic zero                                                             | (0)                                                                 |  |  |  |  |

| Program          | Writes data to the flas                                                            | h array                                                             |  |  |  |  |

| Set              | Indicates a logic one (1)                                                          |                                                                     |  |  |  |  |

| VPEN             | Refers to a signal or package connection name                                      |                                                                     |  |  |  |  |

| V <sub>PEN</sub> | Refers to timing or vol                                                            | ltage levels                                                        |  |  |  |  |

#### 1.2 **Acronyms**

| SBC | Single Bit per Cell                  |

|-----|--------------------------------------|

| FDI | Flash Data Integrator                |

| CFI | Common Flash Interface               |

| scs | Scalable Command Set                 |

| cui | Command User Interface               |

| ОТР | One Time Programmable                |

| PLR | Protection Lock Register             |

| PR  | Protection Register                  |

| PRD | Protection Register Data             |

| RFU | Reserved for Future Use              |

| SR  | Status Register                      |

| SRD | Status Register Data                 |

| WSM | Write State Machine                  |

| ECR | Enhanced Configuration Register      |

| ECD | Enhanced Configuration Register Data |

#### 1.3 **Conventions**

h Hexadecimal Suffix

K(noun) 1,000

M (noun) 1,000,000

Nibble 4 bits Byte 8 bits Word 16 bits

Κb 1,024 bits

KΒ 1,024 bytes

ΚW 1,024 words 1,048,576 bits Mb

1,048,576 bytes MB

1,048,576 words MW

Kbit 1,024 bits

Mbit 1,048,576 bits

Square brackets ([]) will be used to designate group membership or to define a group of signals with similar function (i.e. A[21:1], SR[4,1] and D[15:0]). **Brackets**

00FFh Denotes 16-bit hexadecimal numbers

00FF 00FFh Denotes 32-bit hexadecimal numbers

DQ[15:0] Data I/O signals

## 2.0 Functional Overview

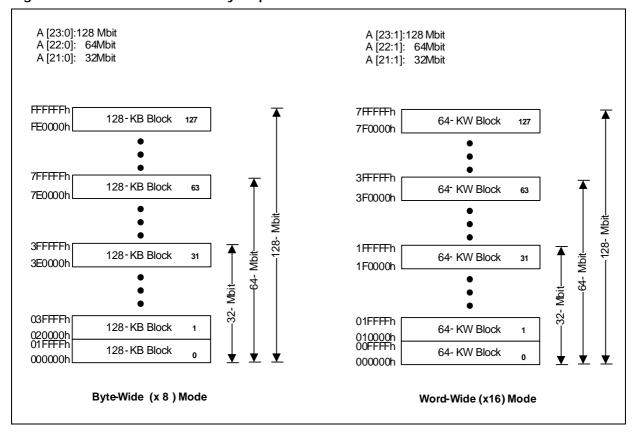

The J3 65 nm SBC family contains high-density memory organized in any of the following configurations:

- 16-MB or 8-MW (128-Mbit), organized as one-hundred-twenty-eight 128-KB erase blocks.

- 8-MB or 4-MW (64-Mbit), organized as sixty-four 128-KB erase blocks.

- 4-MB or 2-MW (32-Mbit), organized as thirty-two 128-KB erase blocks.

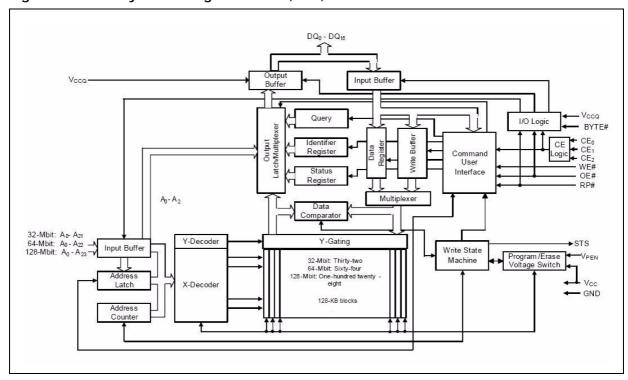

These devices can be accessed as 8- or 16-bit words. See Figure 1, "Memory Block Diagram for 32-, 64-, 128-Mbit" on page 11 for further details.

A 128-bit Protection Register has multiple uses, including unique flash device identification.

The J3 65 nm SBC device includes new security features that were not available on the (previous)  $0.13\mu m$  versions of the J3 family. These new security features prevent altering of code through different protection schemes that can be implemented, based on user requirements.

The J3 65 nm SBC optimized architecture and interface dramatically increases read performance by supporting page-mode reads. This read mode is ideal for non-clock memory systems.

Its Common Flash Interface (CFI) permits software algorithms to be used for entire families of devices. This allows device-independent, JEDEC ID-independent, and forward- and backward-compatible software support for the specified flash device families. Flash vendors can standardize their existing interfaces for long-term compatibility.

The Scalable Command Set (SCS) allows a single, simple software driver in all host systems to work with all SCS-compliant flash memory devices, independent of system-level packaging (e.g., memory card, SIMM, or direct-to-board placement). Additionally, SCS provides the highest system/device data transfer rates and minimizes device and system-level implementation costs.

A Command User Interface (CUI) serves as the interface between the system processor and internal operation of the device. A valid command sequence written to the CUI initiates device automation. An internal Write State Machine (WSM) automatically executes the algorithms and timings necessary for block erase, program, and lock-bit configuration operations.

A block erase operation erases one of the device's 128-KB blocks typically within one second, independent of other blocks. Each block can be independently erased 100,000 times. Block erase suspend mode allows system software to suspend block erase to read or program data from any other block. Similarly, program suspend allows system software to suspend programming (byte/word program and write-to-buffer operations) to read data or execute code from any other block that is not being suspended.

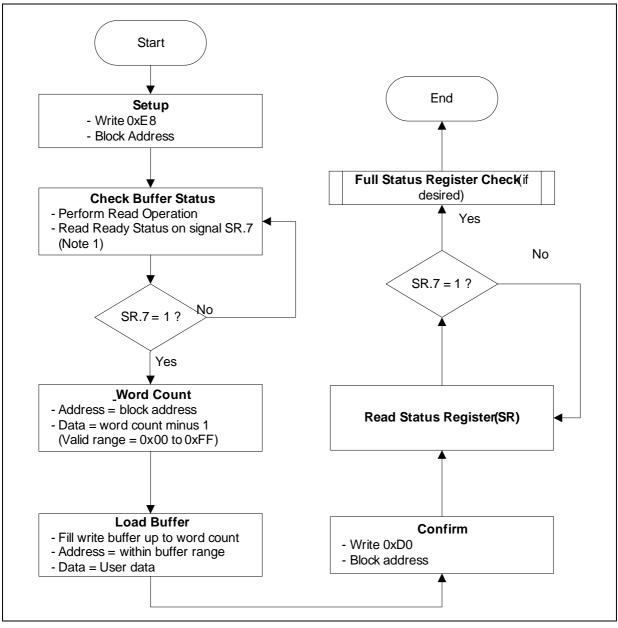

Each device incorporates a Write Buffer of 256-Byte (x8 mode) or 256-Word (x16 mode) to allow optimum programming performance. By using the Write Buffer data is programmed more efficiently in buffer increments.

Memory Blocks are selectively and individually lockable in-system. Individual block locking uses block lock-bits to lock and unlock blocks. Block lock-bits gate block erase and program operations. Lock-bit configuration operations set and clear lock-bits (using the Set Block Lock-Bit and Clear Block Lock-Bits commands).

The Status Register indicates when the WSM's block erase, program, or lock-bit configuration operation completes.

The STS (status) output gives an additional indicator of WSM activity by providing both a hardware signal of status (versus software polling) and status masking (interrupt masking for background block erase, for example). Status indication using STS minimizes both CPU overhead and system power consumption. When configured in level mode (default mode), it acts as a RY/BY# signal. When low, STS indicates that the WSM is performing a block erase, program, or lock-bit configuration. STS-high indicates that the WSM is ready for a new command, block erase is suspended (and programming is inactive), program is suspended, or the device is in reset/power-down mode. Additionally, the configuration command allows the STS signal to be configured to pulse on completion of programming and/or block erases.

Three CE signals are used to enable and disable the device. A unique CE logic design (see Table 17, "Chip Enable Truth Table for 32-, 64-, 128-Mb" on page 30) reduces decoder logic typically required for multi-chip designs. External logic is not required when designing a single chip, a dual chip, or a 4-chip miniature card or SIMM module.

The BYTE# signal allows either x8 or x16 read/writes to the device:

- BYTE#-low enables 8-bit mode; address A0 selects between the low byte and high byte.

- BYTE#-high enables16-bit operation; address A1 becomes the lowest order address and address A0 is not used (don't care).

Figure 1, "Memory Block Diagram for 32-, 64-, 128-Mbit" on page 11 shows a device block diagram.

When the device is disabled (see Table 17, "Chip Enable Truth Table for 32-, 64-, 128-Mb" on page 30), with CEx at  $V_{IH}$  and RP# at  $V_{IH}$ , the standby mode is enabled. When RP# is at  $V_{IL}$ , a further power-down mode is enabled which minimizes power consumption and provides write protection during reset. A reset time ( $t_{PHQV}$ ) is required from RP# going high until data outputs are valid. Likewise, the device has a wake time ( $t_{PHWL}$ ) from RP#-high until writes to the CUI are recognized. With RP# at  $V_{IL}$ , the WSM is reset and the Status Register is cleared.

#### **Block Diagram** 2.1

Figure 1: Memory Block Diagram for 32-, 64-, 128-Mbit

## 2.2 Memory Map

Figure 2: J3 65 nm SBC Memory Map

#### **Package Information** 3.0

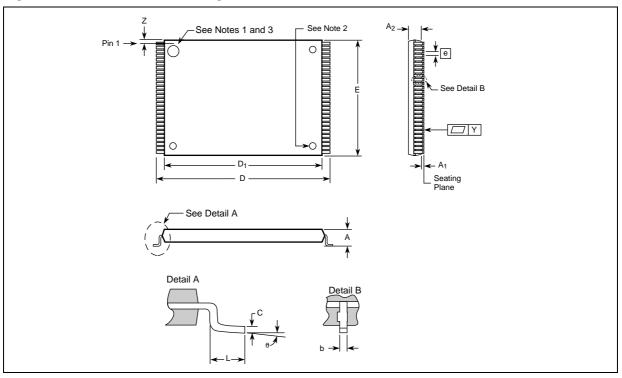

#### 3.1 56-Lead TSOP Package for 32-, 64-, 128-Mbit

Figure 3: 56-Lead TSOP Package Mechanical

- One dimple on package denotes Pin 1.

- 1. 2. 3. If two dimples, then the larger dimple denotes Pin 1.

Pin 1 will always be in the upper left corner of the package, in reference to the product mark.

Table 1: 56-Lead TSOP Dimension Table

| Parameter               | Sumbal         | Millimeters |        |        | Inches |        |        |  |

|-------------------------|----------------|-------------|--------|--------|--------|--------|--------|--|

| Parameter               | Symbol         | Min         | Nom    | Max    | Min    | Nom    | Max    |  |

| Package Height          | А              | _           | _      | 1.200  | _      | _      | 0.047  |  |

| Standoff                | A <sub>1</sub> | 0.050       | _      | _      | 0.002  | _      | _      |  |

| Package Body Thickness  | A <sub>2</sub> | 0.965       | 0.995  | 1.025  | 0.038  | 0.039  | 0.040  |  |

| Lead Width <sup>1</sup> | b              | 0.170       | 0.220  | 0.270  | 0.0067 | 0.0087 | 0.0106 |  |

| Lead Thickness          | С              | 0.100       | 0.150  | 0.200  | 0.004  | 0.006  | 0.008  |  |

| Package Body Length     | $D_1$          | 18.200      | 18.400 | 18.600 | 0.717  | 0.724  | 0.732  |  |

| Package Body Width      | E              | 13.800      | 14.000 | 14.200 | 0.543  | 0.551  | 0.559  |  |

| Lead Pitch              | е              | _           | 0.500  | _      | _      | 0.0197 | _      |  |

| Terminal Dimension      | D              | 19.800      | 20.00  | 20.200 | 0.780  | 0.787  | 0.795  |  |

| Lead Tip Length         | L              | 0.500       | 0.600  | 0.700  | 0.020  | 0.024  | 0.028  |  |

Table 1: 56-Lead TSOP Dimension Table

| Parameter                 | Symbol |       | Millimeters |       | Inches |       |       |

|---------------------------|--------|-------|-------------|-------|--------|-------|-------|

| Farameter                 | Зушьог | Min   | Nom         | Max   | Min    | Nom   | Max   |

| Lead Count                | N      | _     | 56          | _     | _      | 56    | _     |

| Lead Tip Angle            | θ      | 0°    | 3°          | 5°    | 0°     | 3°    | 5°    |

| Seating Plane Coplanarity | Y      | _     | _           | 0.100 | _      | -     | 0.004 |

| Lead to Package Offset    | Z      | 0.150 | 0.250       | 0.350 | 0.006  | 0.010 | 0.014 |

<sup>1.</sup> For legacy lead width, 0.15mm (Typ), 0.10mm (Min), 0.20mm (Max).

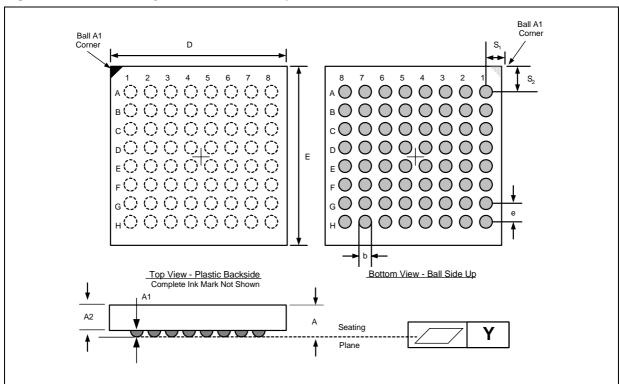

## 3.2 64-Ball Easy BGA Package for 32-, 64-, 128-Mbit

Figure 4: 64-Ball Easy BGA Mechanical Specifications

Table 2: Easy BGA Package Dimensions Table (Sheet 1 of 2)

| Parameter              | Symbol | Millimeters |       |       | Inches |        |        |

|------------------------|--------|-------------|-------|-------|--------|--------|--------|

| rai ailletei           | Symbol | Min         | Nom   | Max   | Min    | Nom    | Max    |

| Package Height         | Α      | _           | _     | 1.200 | _      | _      | 0.0472 |

| Ball Height            | A1     | 0.250       | _     | _     | 0.0098 | _      | _      |

| Package Body Thickness | A2     | _           | 0.780 | _     | _      | 0.0307 | _      |

| Ball (Lead) Width      | b      | 0.310       | 0.410 | 0.510 | 0.012  | 0.016  | 0.020  |

Table 2: Easy BGA Package Dimensions Table (Sheet 2 of 2)

| Parameter                          | Symbol | IV     | lillimeter | s      | Inches |        |        |

|------------------------------------|--------|--------|------------|--------|--------|--------|--------|

| Parameter                          |        | Min    | Nom        | Max    | Min    | Nom    | Max    |

| Package Body Width                 | D      | 9.900  | 10.000     | 10.100 | 0.3898 | 0.3937 | 0.3976 |

| Package Body Length                | Е      | 12.900 | 13.000     | 13.100 | 0.5079 | 0.5118 | 0.5157 |

| Pitch                              | е      | _      | 1.000      | _      | _      | 0.0394 | _      |

| Ball (Lead) Count                  | N      | _      | 64         | _      | _      | 64     | _      |

| Seating Plane Coplanarity          | Υ      | _      | _          | 0.100  | _      | _      | 0.0039 |

| Corner to Ball A1 Distance Along D | S1     | 1.400  | 1.500      | 1.600  | 0.0551 | 0.0591 | 0.0630 |

| Corner to Ball A1 Distance Along E | S2     | 2.900  | 3.000      | 3.100  | 0.1142 | 0.1181 | 0.1220 |

#### **Ballouts/Pinouts and Signal Descriptions** 4.0

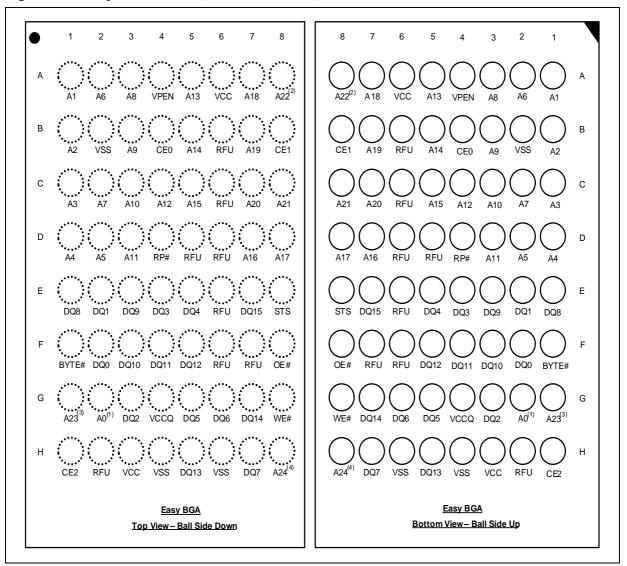

J3 65 nm SBC is available in two package types. All densities of the J3 65 nm SBC devices are supported on both 64-ball Easy BGA and 56-lead Thin Small Outline Package (TSOP) packages. The figures below show the ballouts/Pinouts.

#### 4.1 Easy BGA Ballout for 32-, 64-, 128-Mbit

Figure 5: Easy BGA Ballout (32/64/128 Mbit)

- A0 is the least significant address bit. 1.

- 2. A22 is valid for 64-Mbit density and above. On 32-Mbit, it is a no-connect (NC).

- A23 is valid for 128-Mbit density. On 32- and 64-Mbit, it is a no-connect (NC). A24 is a no connect (NC) on 128-, 64-, 32- Mbit, reserved for 256-Mbit. 3.

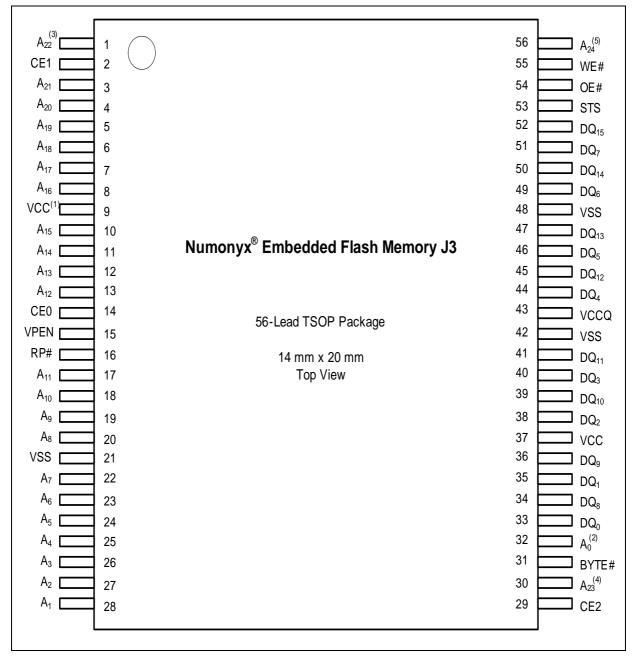

#### 56-Lead TSOP Package Pinout for 32-, 64-,128-Mbit 4.2

56-Lead TSOP Package Pinout (32/64/128 Mbit) Figure 6:

- 1. 2. No internal connection for pin 9; it may be driven or floated. For legacy designs, the pin can be tied to  $V_{CC}$ .

- A0 is the least significant address bit.

- 3. A22 is valid for 64-Mbit density and above. On 32-Mbit, it is a no-connect (NC).

- A23 is valid for 128-Mbit density. On 32- and 64-Mbit, it is a no-connect (NC). A24 is a no connect (NC) on 128-, 64-, 32- Mbit, reserved for 256-Mbit. 4.

#### **Signal Descriptions** 4.3

Table 3 lists the active signals used on J3 65 nm SBC and provides a description of each.

Table 3: Signal Descriptions for J3 65 nm SBC

| Symbol   | Туре                 | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0       | Input                | BYTE-SELECT ADDRESS: Selects between high and low byte when the device is in x8 mode. This address is latched during a x8 program cycle. Not used in x16 mode (i.e., the A0 input buffer is turned off when BYTE# is high).                                                                                                                                                                                                                                                                                                                                                                     |

| A[MAX:1] | Input                | ADDRESS INPUTS: Inputs for addresses during read and program operations. Addresses are internally latched during a program cycle:  32-Mbit — A[21:1]  64-Mbit — A[22:1]  128-Mbit — A[23:1]                                                                                                                                                                                                                                                                                                                                                                                                     |

| DQ[7:0]  | Input/<br>Output     | LOW-BYTE DATA BUS: Inputs data during buffer writes and programming, and inputs commands during CUI writes. Outputs array, CFI, identifier, or status data in the appropriate read mode. Data is internally latched during write operations.                                                                                                                                                                                                                                                                                                                                                    |

| DQ[15:8] | Input/<br>Output     | HIGH-BYTE DATA BUS: Inputs data during x16 buffer writes and programming operations. Outputs array, CFI, or identifier data in the appropriate read mode; not used for Status Register reads. Data is internally latched during write operations in x16 mode. D[15:8] float in x8 mode.                                                                                                                                                                                                                                                                                                         |

| CE[2:0]  | Input                | CHIP ENABLE: Activates the 32-, 64-, 128-Mbit devices' control logic, input buffers, decoders, and sense amplifiers. When the device is de-selected (see Table 17, "Chip Enable Truth Table for 32-, 64-, 128-Mb" on page 30), power reduces to standby levels.  All timing specifications are the same for these three signals. Device selection occurs with the first edge of CE0, CE1, or CE2 that enables the device. Device deselection occurs with the first edge of CE0, CE1, or CE2 that disables the device (see Table 17, "Chip Enable Truth Table for 32-, 64-, 128-Mb" on page 30). |

| RP#      | Input                | <b>RESET</b> : RP#-low resets internal automation and puts the device in power-down mode. RP#-high enables normal operation. Exit from reset sets the device to read array mode. When driven low, RP# inhibits write operations which provides data protection during power transitions.                                                                                                                                                                                                                                                                                                        |

| OE#      | Input                | OUTPUT ENABLE: Activates the device's outputs through the data buffers during a read cycle. OE# is active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| WE#      | Input                | <b>WRITE ENABLE</b> : Controls writes to the CUI, the Write Buffer, and array blocks. WE# is active low. Addresses and data are latched on the rising edge of WE#.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| STS      | Open Drain<br>Output | STATUS: Indicates the status of the internal state machine. When configured in level mode (default), it acts as a RY/BY# signal. When configured in one of its pulse modes, it can pulse to indicate program and/or erase completion. For alternate configurations of the Status signal, see the Configurations command and Section 9.7, "Status Signal" on page 41. STS is to be tied to VCCQ with a pull-up resistor.                                                                                                                                                                         |

| BYTE#    | Input                | BYTE ENABLE: BYTE#-low places the device in x8 mode; data is input or output on D[7:0], while D[15:8] is placed in High-Z. Address A0 selects between the high and low byte. BYTE#-high places the device in x16 mode, and turns off the A0 input buffer, the address A1 becomes the lowest-order address bit.                                                                                                                                                                                                                                                                                  |

| VPEN     | Input                | <b>ERASE / PROGRAM / BLOCK LOCK ENABLE</b> : For erasing array blocks, programming data, or configuring lock-bits. With $V_{PEN} \le V_{PENLK}$ , memory contents cannot be altered.                                                                                                                                                                                                                                                                                                                                                                                                            |

| VCC      | Power                | <b>CORE Power Supply:</b> Core (logic) source voltage. Writes to the flash array are inhibited when $V_{CC} \leq V_{Lko}$ . Caution: Device operation at invalid Vcc voltages should not be attempted.                                                                                                                                                                                                                                                                                                                                                                                          |

| VCCQ     | Power                | <b>I/O Power Supply</b> : Power supply for Input/Output buffers. This ball can be tied directly to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VSS      | Supply               | GROUND: Ground reference for device logic voltages. Connect to system ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| NC       | _                    | No Connect: Lead is not internally connected; it may be driven or floated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RFU      | _                    | Reserved for Future Use: Balls designated as RFU are reserved by Numonyx for future device functionality and enhancement.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

#### 5.0 **Maximum Ratings and Operating Conditions**

#### 5.1 **Absolute Maximum Ratings**

Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent Warning:

damage. These are stress ratings only.

NOTICE: This document contains information available at the time of its release. The specifications are subject to change without notice. Verify with your local Numonyx sales office that you have the latest datasheet before finalizing a design.

Table 4: **Absolute Maximum Ratings**

| Parameter                                                  | Min  | Max                          | Unit | Notes |

|------------------------------------------------------------|------|------------------------------|------|-------|

| Temperature under Bias Expanded (T <sub>A</sub> , Ambient) | -40  | +85                          | °C   | _     |

| Storage Temperature                                        | -65  | +125                         | °C   | _     |

| VCC Voltage                                                | -2.0 | +5.6                         | V    | 2     |

| VCCQ Voltage                                               | -2.0 | +5.6                         | V    | 2     |

| Voltage on any input/output signal (except VCC, VCCQ)      | -2.0 | V <sub>CCQ</sub> (max) + 2.0 | V    | 1     |

| I <sub>SH</sub> Output Short Circuit Current               | _    | 100                          | mA   | 3     |

#### Notes:

- Voltage is referenced to  $V_{SS}$ . During infrequent non-periodic transitions, the voltage potential between  $V_{SS}$  and input/output pins may undershoot to -2.0 V for periods < 20 ns or overshoot to  $V_{CCQ}$  (max) + 2.0 V for periods < 20 ns. During infrequent non-periodic transitions, the voltage potential between  $V_{CC}$  and the supplies may undershoot to -2.01.

- 2. V for periods < 20 ns or  $V_{SUPPLY}$  (max) + 2.0 V for periods < 20 ns. Output shorted for less than one second. No more than one output pin/ball can be shorted at a time.

- 3.

#### 5.2 **Operating Conditions**

Warning: Operations beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

Table 5: Temperature and V<sub>CC</sub> Operating Condition

| Symbol          | mbol Parameter        |       | Max | Unit | Test Condition      |

|-----------------|-----------------------|-------|-----|------|---------------------|

| T <sub>A</sub>  | Operating Temperature | -40.0 | +85 | °C   | Ambient Temperature |

| V <sub>CC</sub> | VCC Supply Voltage    | 2.70  | 3.6 | V    | _                   |

| $V_{CCQ}$       | VCCQ Supply Voltage   | 2.70  | 3.6 | V    | _                   |

#### 5.3 Power-Up/Down

This section provides an overview of system level considerations with regards to the flash device. It includes a brief description of power-up/down sequence and decoupling design considerations.

#### 5.3.1 Power-Up/Down Sequence

To prevent conditions that could result in spurious program or erase operations, the power-up/power-down sequence shown in Table 6 is recommended. For DC voltage characteristics refer to Table 8. Note that each power supply must reach its minimum voltage range before applying/removing the next supply voltage.

Table 6: Power-Up/Down Sequence

| Power Supply<br>Voltage |     | Power-Up Sequence  |                    |                                        |     | Power-Down Sequence |                    |                                        |  |

|-------------------------|-----|--------------------|--------------------|----------------------------------------|-----|---------------------|--------------------|----------------------------------------|--|

| V <sub>CC(min)</sub>    | 1st | 1st                | 1st <sup>(1)</sup> |                                        | 3rd | 2nd                 | 2nd <sup>(1)</sup> |                                        |  |

| V <sub>CCQ(min)</sub>   | 2nd | 2nd <sup>(1)</sup> | 150                | Sequencing not required <sup>(1)</sup> | 2nd | 1st <sup>(1)</sup>  | Zilu               | Sequencing not required <sup>(1)</sup> |  |

| V <sub>PEN(min)</sub>   | 3rd | Ziiu' '            | 2nd                | -                                      | 1st | 13(, ,              | 1st                | -                                      |  |

## Note:

Device inputs must not be driven until all supply voltages reach their minimum range. RP# should be low during power transitions.

## 5.3.2 Power Supply Decoupling

When the device is enabled, many internal conditions change. Circuits are energized, charge pumps are switched on, and internal voltage nodes are ramped. All of this internal activities produce transient signals. The magnitude of the transient signals depends on the device and system loading. To minimize the effect of these transient signals, a 0.1  $\mu\text{F}$  ceramic capacitor is required across each VCC/VSS and VCCQ signal. Capacitors should be placed as close as possible to device connections.

Additionally, for every eight flash devices, a 4.7  $\mu$ F electrolytic capacitor should be placed between VCC and VSS at the power supply connection. This 4.7  $\mu$ F capacitor should help overcome voltage slumps caused by PCB trace inductance.

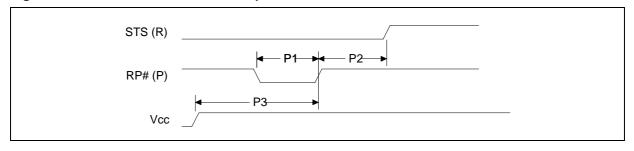

## 5.4 Reset

By holding the flash device in reset during power-up and power-down transitions, invalid bus conditions may be masked. The flash device enters reset mode when RP# is driven low. In reset, internal flash circuitry is disabled and outputs are placed in a high-impedance state. After return from reset, a certain amount of time is required before the flash device is able to perform normal operations. After return from reset, the flash device defaults to asynchronous page mode. If RP# is driven low during a program or erase operation, the program or erase operation will be aborted and the memory contents at the aborted block or address are no longer valid. See Figure 12, "AC Waveform for Reset Operation" on page 28 for detailed information regarding reset timings.

Power supplies connected or sequenced together.

#### **Electrical Characteristics** 6.0

#### **DC Current Specifications** 6.1

Table 7: **DC Current Characteristics**

|                                        | V <sub>CCQ</sub>                                                  | 2   | .7 - 3.6                                                          | ٥V   |                                                                                                                                                                                                                                                |       |  |

|----------------------------------------|-------------------------------------------------------------------|-----|-------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|

|                                        | V <sub>CC</sub>                                                   | 2   | .7 - 3.6                                                          | v    | Test Conditions                                                                                                                                                                                                                                | Notes |  |

| Symbol                                 | Parameter                                                         | Тур | Max                                                               | Unit |                                                                                                                                                                                                                                                |       |  |

| I <sub>LI</sub>                        | Input and V <sub>PEN</sub> Load Current                           | _   | ±1                                                                | μА   | $V_{CC} = V_{CC}$ Max; $V_{CCQ} = V_{CCQ}$ Max<br>$V_{IN} = V_{CCQ}$ or $V_{SS}$                                                                                                                                                               | 1     |  |

| I <sub>LO</sub>                        | Output Leakage Current                                            | _   | ±10                                                               | μА   | $V_{CC} = V_{CC}$ Max; $V_{CCQ} = V_{CCQ}$ Max $V_{IN} = V_{CCQ}$ or $V_{SS}$                                                                                                                                                                  | 1     |  |

| I <sub>CCS</sub>                       | V <sub>CC</sub> Standby Current                                   | 50  | 120                                                               | μА   | CMOS Inputs, $V_{CC} = V_{CC}$ Max; $V_{CCQ} = V_{CCQ}$ Max; $V_{CCQ} = V_{CCQ}$ Device is disabled (see Table 17, "Chip Enable Truth Table for 32-, 64-, 128-Mb" on page 30), RP# = $V_{CCQ} \pm 0.2 \text{ V}$                               | 1,2,3 |  |

| ccs                                    | V <sub>CC</sub> Standby Current  0.71 2 mA                        |     | TTL Inputs, V <sub>CC</sub> = V <sub>CC</sub> Max, Vccq = VccqMax |      |                                                                                                                                                                                                                                                |       |  |

| I <sub>CCD</sub>                       | V <sub>CC</sub> Power-Down Current                                | 50  | 120                                                               | μΑ   | $RP\# = V_{SS} \pm 0.2 \text{ V, } I_{OUT} (STS) = 0 \text{ mA}$                                                                                                                                                                               | _     |  |

|                                        |                                                                   | 15  | 20                                                                | mA   | CMOS Inputs, $V_{CC} = V_{CC}$ Max, $V_{CCQ} = V_{CCQ}$ Max using standard 8 word page mode reads.  Device is enabled (see Table 17, "Chip Enable Truth Table for 32-, 64-, 128-Mb" on page 30) $f = 5 \text{ MHz}$ , $I_{OUT} = 0 \text{ mA}$ |       |  |

| I <sub>CCR</sub>                       | 8-Word Page                                                       | 30  | 54                                                                | mA   | CMOS Inputs, $V_{CC} = V_{CC}$ Max, $V_{CCQ} = V_{CCQ}$ Max using standard 8 word page mode reads. Device is enabled (see Table 17, "Chip Enable Truth Table for 32-, 64-, 128-Mb" on page 30) $f = 33 \text{ MHz}$ , $I_{OUT} = 0 \text{ mA}$ | 1,3   |  |

| т                                      | V Program or Sot Lock-Rit Current                                 | 35  | 60                                                                | mA   | CMOS Inputs, V <sub>PEN</sub> = V <sub>CC</sub>                                                                                                                                                                                                | 1,4   |  |

| I <sub>CCW</sub>                       | V <sub>CC</sub> Program or Set Lock-Bit Current                   | 40  | 70                                                                | mA   | TTL Inputs, $V_{PEN} = V_{CC}$                                                                                                                                                                                                                 | 1,4   |  |

| I <sub>CCE</sub>                       | V <sub>CC</sub> Block Erase or V <sub>CC</sub> Blank Check or     | 35  | 70                                                                | mA   | CMOS Inputs, $V_{PEN} = V_{CC}$                                                                                                                                                                                                                | 1,4   |  |

| $I_{CCBC}$                             | Clear Block Lock-Bits Current                                     | 40  | 80                                                                | mA   | TTL Inputs, $V_{PEN} = V_{CC}$                                                                                                                                                                                                                 | 1,4   |  |

| I <sub>CCWS</sub><br>I <sub>CCES</sub> | V <sub>CC</sub> Program Suspend or Block Erase<br>Suspend Current | _   | 10                                                                | mA   | Device is enabled (see Table 17, "Chip<br>Enable Truth Table for 32-, 64-,<br>128-Mb" on page 30)                                                                                                                                              | 1,5   |  |

- All currents are in RMS unless otherwise noted. These currents are valid for all product versions (packages and speeds). 1. Contact Numonyx or your local sales office for information about typical specifications.

- 2. 3. 4. 5. CMOS inputs are either  $V_{CC} \pm 0.2 \text{ V}$  or  $V_{SS} \pm 0.2 \text{ V}$ . TTL inputs are either  $V_{IL}$  or  $V_{IH}$ . Sampled, not 100% tested.  $I_{CCWS}$  and  $I_{CCES}$  are specified with the device selected. If the device is read or written while in erase suspend mode, the device's current draw is  $I_{CCR}$  and  $I_{CCWS}$ .

#### **DC Voltage specifications** 6.2

Table 8: **DC Voltage Characteristics**

|                    | V <sub>CCQ</sub>                                                          | ;                      | 2.7 - 3.6 V            |                 |                                                                                                                         |         |

|--------------------|---------------------------------------------------------------------------|------------------------|------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------|---------|

|                    | V <sub>cc</sub>                                                           |                        | 2.7 - 3.6 V            | Test Conditions | Notes                                                                                                                   |         |

| Symbol             | Parameter                                                                 | neter Min M            |                        | Unit            | -                                                                                                                       |         |

| V <sub>IL</sub>    | Input Low Voltage                                                         | -0.5                   | 0.8                    | V               | -                                                                                                                       | 2, 5, 6 |

| V <sub>IH</sub>    | Input High Voltage                                                        | 2.0                    | V <sub>CCQ</sub> + 0.5 | V               | _                                                                                                                       | 2, 5, 6 |

| V                  | Output Low Voltage                                                        | _                      | 0.4                    | V               | $V_{CC} = V_{CC}Min$ $V_{CCQ} = V_{CCQ}Min$ $I_{OL} = 2 mA$                                                             | 1, 2    |

| V <sub>OL</sub>    | Output Low Voltage                                                        | _                      | 0.2                    | V               | $V_{CC} = V_{CC}Min$ $V_{CCQ} = V_{CCQ}Min$ $I_{OL} = 100 \mu Å$                                                        | 1,2     |

| V                  | Output High Voltage                                                       | $0.85 \times V_{CCQ}$  | _                      | V               | $\begin{aligned} & V_{CC} = V_{CCMIN} \\ & V_{CCQ} = V_{CCQ} \text{ Min} \\ & I_{OH} = -2.5 \text{ mA} \end{aligned}$   | 1, 2    |

| V <sub>OH</sub>    | Output High Voltage                                                       | V <sub>CCQ</sub> - 0.2 | _                      | V               | $\begin{aligned} & V_{CC} = V_{CCMIN} \\ & V_{CCQ} = V_{CCQ} \text{ Min} \\ & I_{OH} = -100  \mu\text{A} \end{aligned}$ | 1,2     |

| V <sub>PENLK</sub> | V <sub>PEN</sub> Lockout during Program,<br>Erase and Lock-Bit Operations | _                      | 2.2                    | V               | _                                                                                                                       | 2, 3    |

| $V_{PENH}$         | V <sub>PEN</sub> during Block Erase, Program, or Lock-Bit Operations      | 2.7                    | 3.6                    | V               | _                                                                                                                       | 3       |

| $V_{LKO}$          | V <sub>CC</sub> Lockout Voltage                                           | _                      | 2.0                    | V               | _                                                                                                                       | 4       |

## Notes:

Includes STS.

Sampled, not 100% tested.

#### 6.3 Capacitance

Table 9: Capacitance

| Symbol           | Parameter <sup>1</sup> | Туре | Max | Unit | Condition <sup>2</sup>   |

|------------------|------------------------|------|-----|------|--------------------------|

| C <sub>IN</sub>  | Input Capacitance      | 6    | 7   | pF   | $V_{IN} = 0.0 V$         |

| C <sub>OUT</sub> | Output Capacitance     | 4    | 5   | pF   | V <sub>OUT</sub> = 0.0 V |

#### Notes:

Sampled, not 100% tested.  $T_A = -40$  °C to +85 °C,  $V_{CC} = V_{CCQ} = 0$  to 3.6 V.

<sup>2.</sup> 3.

<sup>4.</sup>

Sampled, not 100% tested. Block erases, programming, and lock-bit configurations are inhibited when  $V_{PEN} \le V_{PENLK}$ , and not guaranteed in the range between  $V_{PENLK}$  (max) and  $V_{PENH}$  (min), and above  $V_{PENH}$  (max). Block erases, programming, and lock-bit configurations are inhibited when  $V_{CC} \le V_{LKO}$ , and not guaranteed in the range between  $V_{LKO}$  and  $V_{CC}$  (min), and above  $V_{CC}$  (max). Includes all operational modes of the device. Input/Output signals can undershoot to -1.0V referenced to  $V_{SS}$  and can overshoot to  $V_{CCQ} + 1.0V$  for duration of 2ns or less, the  $V_{CCQ}$  valid range is referenced to  $V_{SS}$ .

#### 7.0 **AC Characteristics**

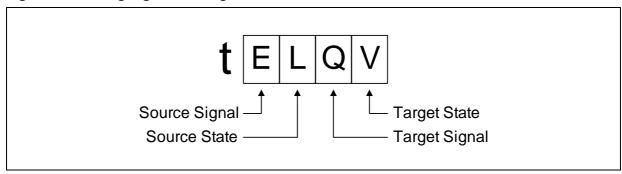

Timing symbols used in the timing diagrams within this document conform to the following convention.

Figure 7: Timing Signal Naming Convention

Table 10: Timing Signal Name Decoder

| Signal                                                 | Code | State   | Code |

|--------------------------------------------------------|------|---------|------|

| Address                                                | A    | High    | Н    |

| Data - Read                                            | Q    | Low     | L    |

| Data - Write                                           | D    | High-Z  | Z    |

| Chip Enable (CE)                                       | Е    | Low-Z   | X    |

| Output Enable (OE#)                                    | G    | Valid   | V    |

| Write Enable (WE#)                                     | W    | Invalid | I    |

| Status (STS)                                           | R    |         |      |

| Reset (RP#)                                            | Р    |         |      |

| Byte Enable (BYTE#)                                    | F    |         |      |

| Erase/Program/Block Lock<br>Enable (V <sub>PEN</sub> ) | V    |         |      |

Note:

Exceptions to this convention include  $t_{ACC}$  and  $t_{APA}$ .  $t_{ACC}$  is a generic timing symbol that refers to the aggregate initial-access delay as determined by tavQv,  $t_{ELQV}$  and  $t_{GLQV}$  (whichever is satisfied last) of the flash device.  $t_{APA}$  is specified in the flash device's data sheet, and is the address-to-data delay for subsequent page-mode reads.

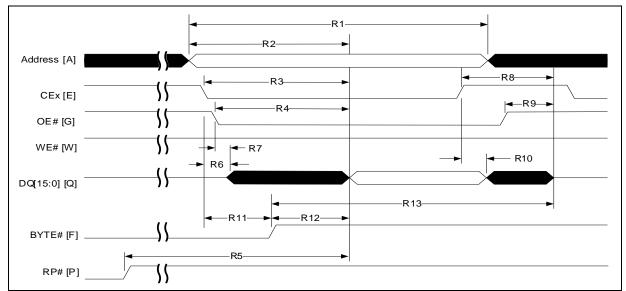

#### **Read Specifications** 7.1

**Table 11: Read Operations**

|     | Asynchronous Specifications $V_{CC} = 2.7 \text{ V} - 3.6 \text{ V}^{(3)}$ and $V_{CCQ} = 2.7 \text{ V} - 3.6 \text{ V}^{(3)}$ |                                                                         |          |     |     |      |       |  |  |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------|-----|-----|------|-------|--|--|--|

| #   | Sym                                                                                                                            | Parameter                                                               | Density  | Min | Max | Unit | Notes |  |  |  |

| R1  | t <sub>AVAV</sub>                                                                                                              | Read/Write Cycle Time                                                   |          | 75  | _   | ns   | 1,2   |  |  |  |

| R2  | t <sub>AVQV</sub>                                                                                                              | Address to Output Delay                                                 | A.II     | _   | 75  | ns   | 1,2   |  |  |  |

| R3  | t <sub>ELQV</sub>                                                                                                              | CEX to Output Delay                                                     | All      | _   | 75  | ns   | 1,2   |  |  |  |

| R4  | t <sub>GLQV</sub>                                                                                                              | OE# to Non-Array Output Delay                                           |          | _   | 25  | ns   | 1,2,4 |  |  |  |

|     |                                                                                                                                |                                                                         | 32 Mbit  | _   | 150 |      | 1,2   |  |  |  |

| R5  | t <sub>PHQV</sub>                                                                                                              | RP# High to Output Delay                                                | 64 Mbit  | _   | 180 | ns   | 1,2   |  |  |  |

|     |                                                                                                                                |                                                                         | 128 Mbit | _   | 210 | 1    | 1,2   |  |  |  |

| R6  | t <sub>ELQX</sub>                                                                                                              | CEX to Output in Low Z                                                  |          | 0   | _   | ns   | 1,2,5 |  |  |  |

| R7  | t <sub>GLQX</sub>                                                                                                              | OE# to Output in Low Z                                                  |          | 0   | _   | ns   | 1,2,5 |  |  |  |

| R8  | t <sub>EHQZ</sub>                                                                                                              | CEX High to Output in High Z                                            |          | _   | 25  | ns   | 1,2,5 |  |  |  |

| R9  | t <sub>GHQZ</sub>                                                                                                              | OE# High to Output in High Z                                            |          | _   | 15  | ns   | 1,2,5 |  |  |  |

| R10 | t <sub>OH</sub>                                                                                                                | Output Hold from Address, CEx, or OE#<br>Change, Whichever Occurs First |          | 0   | _   | ns   | 1,2,5 |  |  |  |

| R11 | t <sub>ELFL/</sub> t <sub>ELFH</sub>                                                                                           | CEX Low to BYTE# High or Low                                            | All      | _   | 10  | ns   | 1,2,5 |  |  |  |

| R12 | $t_{FLQV/}t_{FHQV}$                                                                                                            | BYTE# to Output Delay                                                   |          | _   | 1   | μs   | 1,2   |  |  |  |

| R13 | t <sub>FLQZ</sub>                                                                                                              | BYTE# to Output in High Z                                               |          | _   | 1   | μs   | 1,2,5 |  |  |  |

| R14 | t <sub>EHEL</sub>                                                                                                              | CEx High to CEx Low                                                     |          | 0   | _   | ns   | 1,2,5 |  |  |  |

| R15 | t <sub>APA</sub>                                                                                                               | Page Address Access Time                                                |          | _   | 25  | ns   | 5, 6  |  |  |  |

| R16 | t <sub>GLQV</sub>                                                                                                              | OE# to Array Output Delay                                               |          | _   | 25  | ns   | 1,2,4 |  |  |  |

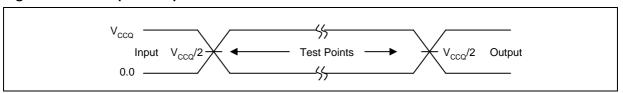

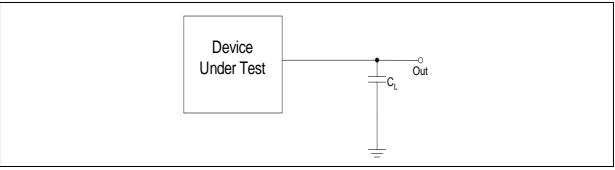

- CE<sub>X</sub> low is defined as the combination of pins CE0, CE1 and CE2 that enable the device. CE<sub>X</sub> high is defined as the combination of pins CE0, CE1, and CE2 that disable the device (see Table 17, "Chip Enable Truth Table for 32-, 64-, 128-Mb" on page 30). See AC Input/Output Reference Waveforms for the maximum allowable input slew rate.

OE# may be delayed up to t<sub>ELOV</sub>-t<sub>GLOV</sub> after the falling edge of CE<sub>X</sub> (see note 1 and Table 17, "Chip Enable Truth Table for 32-, 64-, 128-Mb" on page 30) without impact on t<sub>ELOV</sub>-see Figure 13, "AC Input/Output Reference Waveform" on page 29 and Figure 14, "Transient Equivalent Testing Load Circuit" on page 29 for testing characteristics.

- 2. 3.

- 4.

- 5.

- Sampled, not 100% tested. For devices configured to standard word/byte read mode, R15 ( $t_{APA}$ ) will equal R2 ( $t_{AVQV}$ ).

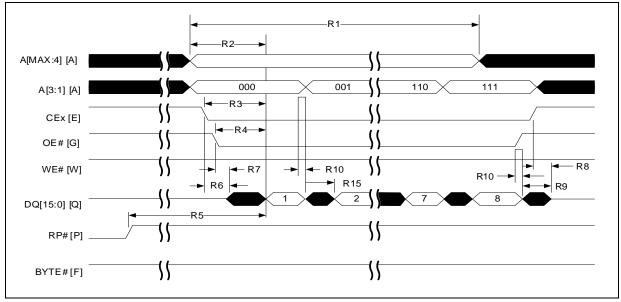

Figure 8: Single-Word Asynchronous Read Waveform

#### Notes:

- $CE_X$  low is defined as the combination of pins CE0, CE1, and CE2 that enable the device.  $CE_X$  high is defined as the combination of pins CE0, CE1, and CE2 that disable the device (see Table 17, "Chip Enable Truth Table for 32-, 64-, 128-Mb" on page 30).

- When reading the flash array a faster  $t_{GLQV}$  (R16) applies. For non-array reads, R4 applies (i.e., Status Register reads, 2. query reads, or device identifier reads).

Figure 9: 8-Word Asynchronous Page Mode Read

- $CE_X$  low is defined as the combination of pins CE0, CE1, and CE2 that enable the device.  $CE_X$  high is defined as the combination of pins CE0, CE1, and CE2 that disable the device (see Table 17, "Chip Enable Truth Table for 32-, 64-, 128-Mb" on page 30). In this diagram, BYTE# is asserted high.

- 2.

**Table 12: Write Operations**

| #   | Symbol                                 | Parameter                                                     | Density  |     | for All<br>eds | Unit | Notes            |

|-----|----------------------------------------|---------------------------------------------------------------|----------|-----|----------------|------|------------------|

|     |                                        |                                                               |          | Min | Max            |      |                  |

|     |                                        |                                                               | 32 Mbit  | 150 | _              |      |                  |

| W1  | t <sub>PHWL</sub> (t <sub>PHEL</sub> ) | RP# High Recovery to WE# (CE <sub>X</sub> ) Going Low         | 64 Mbit  | 180 | _              |      | 1,2,3,4          |

|     |                                        |                                                               | 128 Mbit | 210 | _              |      |                  |

| W2  | t <sub>ELWL</sub> (t <sub>WLEL</sub> ) | CE <sub>X</sub> (WE#) Low to WE# (CE <sub>X</sub> ) Going Low |          | 0   | _              |      | 1,2,3,5          |

| W3  | t <sub>WP</sub>                        | Write Pulse Width                                             |          | 60  | _              |      | 1,2,3,5          |

| W4  | t <sub>DVWH</sub> (t <sub>DVEH</sub> ) | Data Setup to WE# (CE <sub>X</sub> ) Going High               |          | 50  | _              |      | 1,2,3,6          |

| W5  | t <sub>AVWH</sub> (t <sub>AVEH</sub> ) | Address Setup to WE# (CE <sub>X</sub> ) Going High            |          | 55  | _              |      | 1,2,3,6          |

| W6  | t <sub>WHEH</sub> (t <sub>EHWH</sub> ) | CE <sub>X</sub> (WE#) Hold from WE# (CE <sub>X</sub> ) High   |          | 0   | _              | ns   | 1,2,3            |

| W7  | t <sub>WHDX</sub> (t <sub>EHDX</sub> ) | Data Hold from WE# (CE <sub>X</sub> ) High                    |          | 0   | _              |      | 1,2,3            |

| W8  | t <sub>WHAX</sub> (t <sub>EHAX</sub> ) | Address Hold from WE# (CE <sub>X</sub> ) High                 | All      | 0   | _              |      | 1,2,3            |

| W9  | t <sub>WPH</sub>                       | Write Pulse Width High                                        |          | 30  | _              |      | 1,2,3,7          |

| W11 | t <sub>VPWH</sub> (t <sub>VPEH</sub> ) | V <sub>PEN</sub> Setup to WE# (CE <sub>X</sub> ) Going High   |          | 0   | _              |      | 1,2,3,4          |

| W12 | t <sub>WHGL</sub> (t <sub>EHGL</sub> ) | Write Recovery before Read                                    | ]        | 35  | _              |      | 1,2,3,8          |

| W13 | t <sub>WHRL</sub> (t <sub>EHRL</sub> ) | WE# (CE <sub>X</sub> ) High to STS Going Low                  | ]        | _   | 500            |      | 1,2,3,9          |

| W15 | t <sub>QVVL</sub>                      | V <sub>PEN</sub> Hold from Valid SRD, STS Going High          |          | 0   | _              |      | 1,2,3,4,<br>9,10 |

- $CE_X$  low is defined as the combination of pins CE0, CE1, and CE2 that enable the device.  $CE_X$  high is defined as the combination of pins CE0, CE1, and CE2 that disable the device (see Table 17, "Chip Enable Truth Table for 32-, 64-, 128-Mb" on page 30). 1.

- Read timing characteristics during block erase, program, and lock-bit configuration operations are the same as during read-only operations. Refer to *AC Characteristics—Read-Only Operations*. A write operation can be initiated and terminated with either CE<sub>X</sub> or WE#. 2.

- 3.

- Sampled, not 100% tested.

- Write pulse width  $(t_{WP})$  is defined from  $CE_X$  or WE# going low (whichever goes low last) to  $CE_X$  or WE# going high (whichever goes high first). Hence,  $t_{WP} = t_{WLWH} = t_{ELEH} = t_{WLEH} = t_{ELWH}$ . Refer to Table 18, "Enhanced Configuration Register" on page 32 for valid  $A_{IN}$  and  $D_{IN}$  for block erase, 5.

- 6. program, or lock-bit configuration.

- program, or lock-bit configuration. Write pulse width high  $(t_{WPH})$  is defined from  $CE_X$  or WE# going high (whichever goes high first) to  $CE_X$  or WE# going low (whichever goes low first). Hence,  $t_{WPH} = t_{WHWL} = t_{EHEL} = t_{WHEL} = t_{EHWL}$ . For array access,  $t_{AVQV}$  is required in addition to  $t_{WHGL}$  for any accesses after a write. STS timings are based on STS configured in its RY/BY# default mode.  $V_{PEN}$  should be held at  $V_{PENH}$  until determination of block erase, program, or lock-bit configuration success (SR[5:3,1] = 0). 7.

- 8.

- 10.

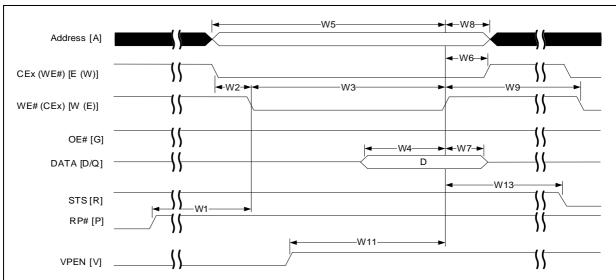

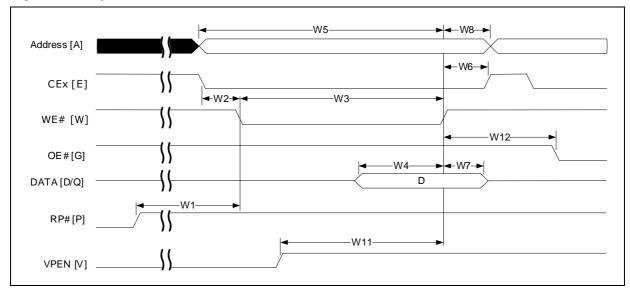

Figure 10: Asynchronous Write Waveform

Figure 11: Asynchronous Write to Read Waveform

#### Program, Erase, Block-Lock Specifications 7.2