#### PRODUCT BRIEF

August 2004 Revision 1.1

#### PC8374T SafeKeeper<sup>™</sup> Desktop TrustedI/O

#### **General Description**

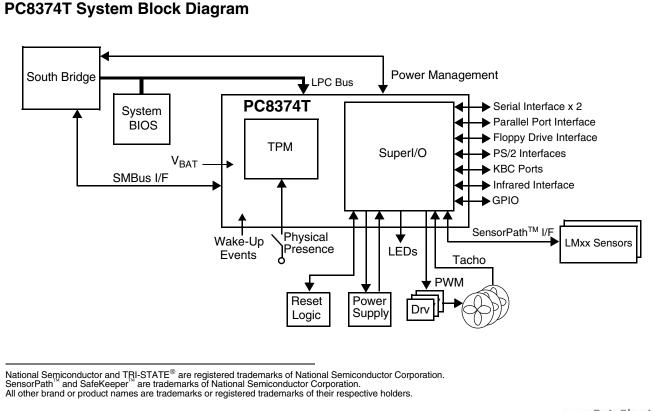

The National Semiconductor PC8374T Advanced I/O product is a member of the PC837x SuperI/O family. All PC837x devices are highly integrated and are pin and software compatible, thus providing drop-in interchangeability and enabling a variety of assembly options using only a single motherboard and BIOS.

PC8374T integration allows for a reduced system board size and saves on total system cost.

The PC8374T includes legacy SuperI/O functions, Trusted Platform Module (TPM), system glue functions, health monitoring and control, commonly used functions such as GPIO, and ACPI-compliant Power Management support.

The Trusted Platform Module provides a solution for PC security, based on the TCG standard. The complete security solution includes hardware, software, and firmware.

The PC8374T integrates miscellaneous analog and digital system glue functions to reduce the number of discrete components required. The host communicates with the functions integrated in the PC8374T through an LPC Bus Interface.

The PC8374T supports both I/O and memory mapping of module registers and enables building legacy-free systems.

#### **Outstanding Features**

- TCG 1.1b based Trusted Platform Module (TPM)

- Integrated non-volatile secure storage

- Hardware and software protection schemes

- Tamper resistance schemes

- Pin compatible to integrated TPM 1.2 device

- Legacy modules: Parallel Port, Floppy Disk Controller (FDC), two Serial Ports, Serial InfraRed Port and a Keyboard and Mouse Controller (KBC)

- Glue functions to complement the South Bridge functionality

- System health support, including SensorPath<sup>™</sup> sensor interface, and fan monitor and control

- V<sub>SB3</sub>-powered Power Management with 19 wake-up sources

- Controls three LED indicators

- 16 GPIO pins with a variety of wake-up options

- I/O-mapped and memory-mapped registers

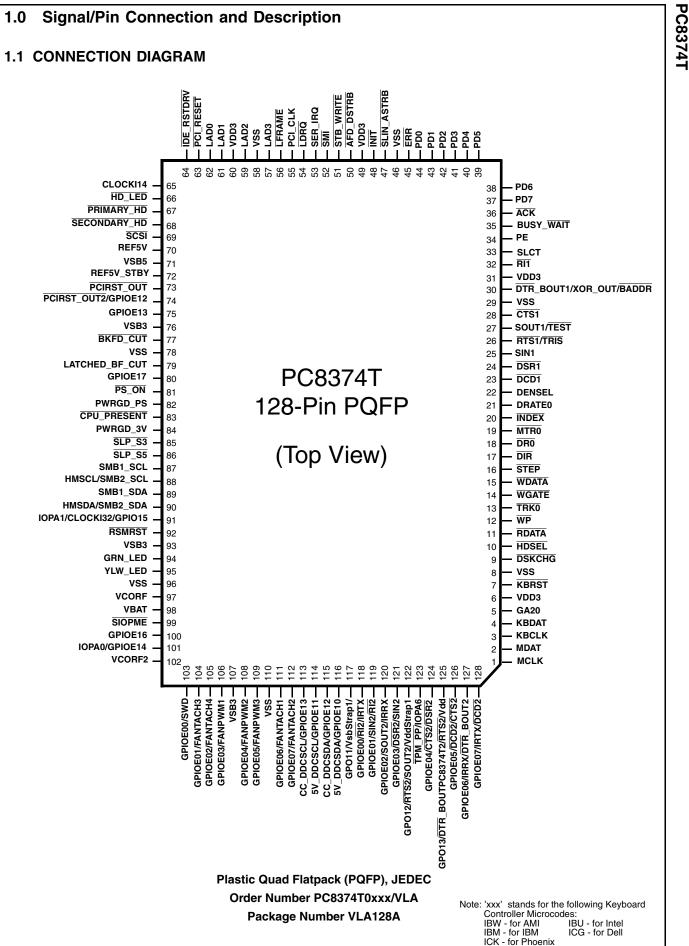

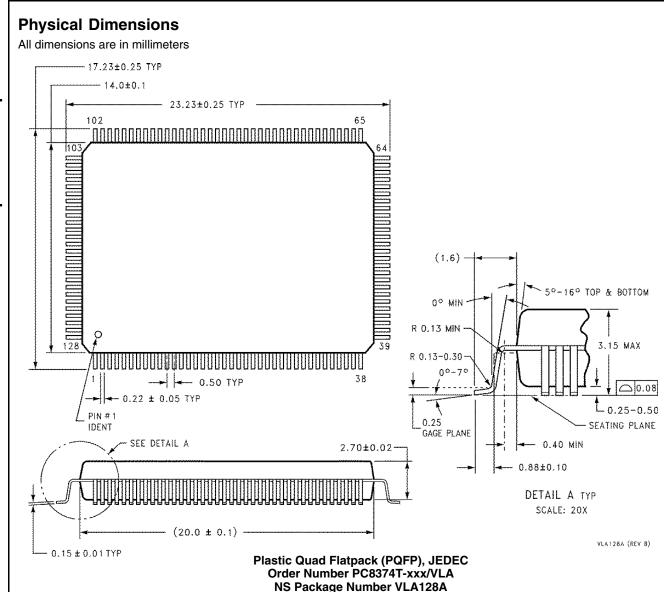

- 128-pin PQFP package

#### Features

#### **Trusted Platform Module (TPM)**

- TCG 1.1b compliant

- Processing Unit

- 16-bit embedded RISC processor core

- Internal Memory

- On-chip Non-Volatile memory for secure storage

- On-chip data RAM

- Host Interface

- Using LPC Bus

- Command/Data/Status standard interface

- Secured General-Purpose I/O (GPIO)

- Internal processor controlled

- Three GPIO pins, one used for Physical Presence

- I/O pins individually configured as input or output

- Configurable internal pull-up resistors

- Owner authorization control

- Power Management Controller (PMC); power modes, switched by software or hardware

- TPM Firmware

- V<sub>SB3</sub> RAM-based storage for loadable keys

- Tamper Resistance

- Clock Jitter protection

- Protection on reference clock

- Protection of security functions from LPC clock jitter

- Power analysis resistance

- Low and High Frequency monitor

- Voltage attack detector

- Low Voltage

- Glitch and brownout detector

- Secure storage contents protection

- Permanent disable of all TPM test mechanisms when locked

#### System Health Support

- SensorPath interface to sensors optimizes digital/analog partitioning

- Simplifies board design and routing

- Supports distributed sensors and centralized control

- Health monitoring is self-contained and requires minimal host attention

- Faster boot time

- Off loads SMBus, and enables ASF compliance

- Fan Monitor and Control

- Three PWM-based fan controls

- Four 16-bit resolution tachometer inputs

- Software or local temperature feedback control

- Heceta6-compatible register set accessible via the LPC interface and SMBus

- Supports the following combinations of LMxx devices:

- □ LM96011

- LM96011 and LM95010

- □ LM96012

- □ LM96010

- Simultaneous read support via LPC interface and SMBus

#### **General-Purpose Modules**

- All 16 GPIO pins powered by V<sub>SB3</sub>

- Each pin individually configured as input or output

- Programmable features for each output pin:

- Drive type (open-drain, push-pull or TRI-STATE<sup>®</sup>)

- TRI-STATE on detection of falling V<sub>DD3</sub> for V<sub>SB3</sub>-powered pins driving V<sub>DD</sub>-supplied devices

- Programmable option for internal pull-up resistor on each input pin (some with internal pull-down resistor option)

- Lock option for the configuration and data of each output pin

- 15 GPIO pins generate IRQ/SIOPME/SMI for wake-up events; each GPIO has separate:

- Enable control of event status routing to IRQ

- Enable control of event status routing to SIOPME

- Polarity and edge/level selection

- Programmable debouncing

#### **Glue Functions**

- Generates the power-related signals:

- Main Power good

- Power distribution control (for switching between Main and Standby regulators)

- Resume reset (Master Reset) according to the 5V standby supply status

- Main power supply turn on (PS\_ON)

- Voltage translation between 2.5V or 3.3V levels (DDC) and 5V levels (VGA) for the SMBus serial clock and data signals

- Isolation circuitry for the SMBus serial clock and data signals

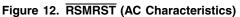

- Buffers PCI\_RESET to generate three reset output signals

- Generates "highest active supply" reference voltage

- Based on 3.3V and 5V Main supplies

- Based on 3.3V and 5V Standby supplies

- High-current LED driver control for Hard Disk Drive activity indication

- Software selectable alternative functionality, through pin multiplexing

#### Features (Continued)

#### **Bus Interface**

- LPC Bus Interface

- Based on Intel's LPC Interface Specification Revision 1.1, August 2002

- I/O, Memory and 8-bit Firmware Memory read and write cycles, Firmware Memory writes may insert wait cycles

- Up to four 8-bit DMA channels

- Serial IRQ (SERIRQ)

- Supports SuperI/O register memory and I/O mapping

- Configuration Control

- PnP Configuration Register structure

- Compliant with PC01 Specification Revision 1.0, 1999-2000

- Base Address strap (BADDR) to setup the address of the Index-Data register pair (defaults to 2Eh/2Fh)

- TPM Index-Data register pair Base Address set by the TPM (defaults to 7Eh/7Fh) or via SuperI/O Configuration registers

- Flexible resource allocation for all logical devices:

- Relocatable base address

- I5 IRQ routing options to serial IRQ

- **Up to four optional 8-bit DMA channels**

- Configurable feature sets:

- V<sub>SB3</sub>-powered pin multiplexing

#### Legacy Modules

- Serial Ports 1 and 2

- Software compatible with the NS16550A and NS16450

- Support shadow register for write-only bit monitoring

- Data rates up to 1.5 Mbaud

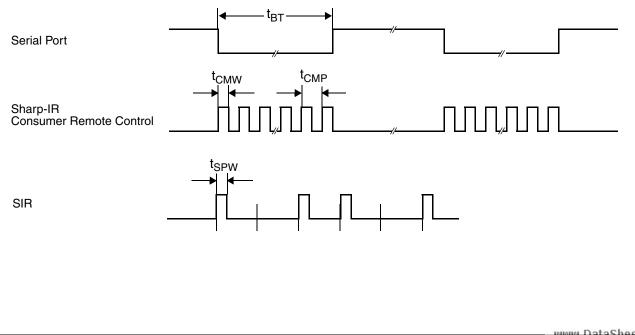

- Serial Infrared Port (SIR)

- Software compatible with the 16550A and the 16450

- Shadow register support for write-only bit monitoring

- HP-SIR

- ASK-IR option of SHARP-IR

- DASK-IR option of SHARP-IR

- Consumer Remote Control supports RC-5, RC-6, NEC, RCA and RECS 80

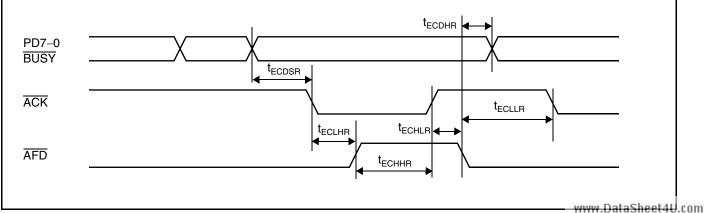

- IEEE 1284-compliant Parallel Port

- ECP, with Level 2 (14 mA sink and source output buffers)

- Software or hardware control

- Enhanced Parallel Port (EPP) compatible with EPP 1.7 and EPP 1.9

- Supports EPP as mode 4 of the Extended Control Register (ECR)

- Selection of internal pull-up or pull-down resistor for Paper End (PE) pin

- Supports a demand DMA mode mechanism and a DMA fairness mechanism for improved bus utilization

- Protection circuit that prevents damage to the parallel port when a printer connected to it is powered up or is operated at high voltages (in both cases, even if the PC8374T is in power-down state)

- Floppy Disk Controller (FDC)

- Software compatible with the PC8477 (the PC8477 contains a superset of the FDC functions in the μDP8473, NEC μPD765A/B and N82077 devices)

- Error-free handling of data overrun and underrun

- Programmable write protect

- Supports FM and MFM modes

- Supports Enhanced mode command for three-mode Floppy Disk Drive (FDD)

- Perpendicular recording drive support for 2.88 MBytes

- Burst (16-byte FIFO) and Non-Burst modes

- Full support for IBM Tape Drive Register (TDR) implementation of AT and PS/2 drive types

- High-performance digital separator

- Supports fast tape drives (2 Mbps) and standard tape drives (1 Mbps, 500 Kbps and 250 Kbps)

- Keyboard and Mouse Controller (KBC)

- 8-bit microcontroller, software compatible with 8042AH and PC87911

- Standard interface (60h, 64h, IRQ1 and IRQ12)

- Supports two external swapable PS/2 interfaces for keyboard and mouse

- Programmable, dedicated quasi-bidirectional I/O lines (GA20/P21, KBRST/P20)

#### **Power Management**

- Supports ACPI Specification Revision 2.0b, July 27, 2000

- System Wake-Up Control (SWC)

- Optional routing of events to generate SCI (SIOPME) on detection of:

- Keyboard or Mouse events

- □ Ring Indication RI on each of the two serial ports

- General-Purpose Input Events from 15 GPIO pins

- IRQs of the Keyboard and Mouse Controller

- □ IRQs of the other internal modules

- Optional routing of the SCI (SIOPME) to generate IRQ (SERIRQ)

- Implements the GPE1\_BLK of the ACPI General Purpose (Generic) Register blocks with "child" events

- V<sub>SB3</sub>-powered event detection and event-logic configuration

- Enhanced Power Management (PM), including:

- Special configuration registers for power down

- Low-leakage pins

- Low-power CMOS technology

- Ability to disable all modules

- High-current LED drivers control (two LEDs) for power status indication with:

- Standard blinking, controlled by software

- Advanced blinking, controlled by power supply status, sleep state or software

- Special blinking, controlled by power supply status, sleep state and software bit

- V<sub>BAT</sub> powered indication of the Main power supply state before an AC power failure

#### Features (Continued)

#### Clocking, Supply, and Package Information

- Clocks

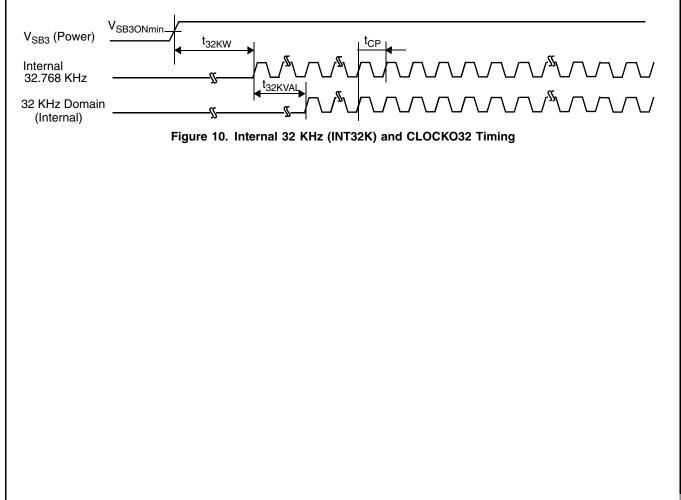

- On-chip Low-Frequency Clock Generator:

- Generates 32.768 KHz internal clock

- On-chip Superl/O Clock Generator:

- Generates 48 MHz

- V<sub>DD3</sub> powered

- Protection

- All device pins are 5V tolerant and back-drive protected (except LPC bus pins)

- High ESD protection of all the device pins

- Pin multiplexing selection lock

- Configuration register lock

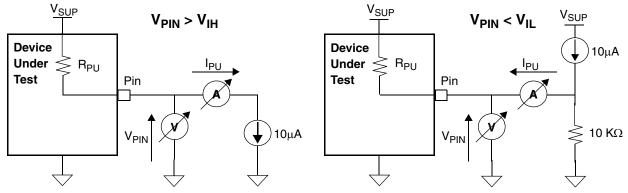

- Testability

- XOR tree structure

- Includes all the device pins (except the supply and the analog pins)

- □ Selected at power-up by strap input (TEST)

- TRI-STATE device pins, selected at power-up by strap input (TRIS)

- Power Supply

- 3.3V supply operation

- Separate pin pairs for main (V<sub>DD3</sub>) and standby (V<sub>SB3</sub>) power supplies

- Backup battery input (V<sub>BAT</sub>) for SWC indications

- Low standby power consumption

- Very low power consumption from backup battery (less than 1  $\mu\text{A})$

- Package

- 128-pin PQFP

PC8374T

| Pin | Pin Name                    | Pin | Pin Name         | Pin | Pin Name              | Pin | Pin Name                                    |

|-----|-----------------------------|-----|------------------|-----|-----------------------|-----|---------------------------------------------|

| 1   | MCLK                        | 33  | SLCT             | 65  | CLOCKI14              | 97  | V <sub>CORF</sub>                           |

| 2   | MDAT                        | 34  | PE               | 66  | HD_LED                | 98  | V <sub>BAT</sub>                            |

| 3   | KBCLK                       | 35  | BUSY_WAIT        | 67  | PRIMARY_HD            | 99  | SIOPME                                      |

| 4   | KBDAT                       | 36  | ACK              | 68  | SECONDARY_HD          | 100 | GPIOE16                                     |

| 5   | GA20                        | 37  | PD7              | 69  | SCSI                  | 101 | IOPA0/GPIOE14                               |

| 6   | V <sub>DD3</sub>            | 38  | PD6              | 70  | REF5V                 | 102 | V <sub>CORF2</sub>                          |

| 7   | KBRST                       | 39  | PD5              | 71  | V <sub>SB5</sub>      | 103 | GPIOE00/SWD                                 |

| 8   | V <sub>SS</sub>             | 40  | PD4              | 72  | REF5V_STBY            | 104 | GPIOE01/FANTACH3                            |

| 9   | DSKCHG                      | 41  | PD3              | 73  | PCIRST_OUT            | 105 | FANTACH4/GPIOE02                            |

| 10  | HDSEL                       | 42  | PD2              | 74  | PCIRST_OUT2/GPIOE12   | 106 | GPIOE03/FANPWM1                             |

| 11  | RDATA                       | 43  | PD1              | 75  | GPIOE13               | 107 | V <sub>SB3</sub>                            |

| 12  | WP                          | 44  | PD0              | 76  | V <sub>SB3</sub>      | 108 | GPIOE04/FANPWM2                             |

| 13  | TRK0                        | 45  | ERR              | 77  | BKFD_CUT              | 109 | GPIOE05/FANPWM3                             |

| 14  | WGATE                       | 46  | V <sub>SS</sub>  | 78  | V <sub>SS</sub>       | 110 | V <sub>SS</sub>                             |

| 15  | WDATA                       | 47  | SLIN_ASTRB       | 79  | LATCHED_BF_CUT        | 111 | GPIOE06/FANTACH1                            |

| 16  | STEP                        | 48  | INIT             | 80  | GPIOE17               | 112 | GPIOE07/FANTACH2                            |

| 17  | DIR                         | 49  | V <sub>DD3</sub> | 81  | PS_ON                 | 113 | CC_DDCSCL/GPIOE13                           |

| 18  | DR0                         | 50  | AFD_DSTRB        | 82  | PWRGD_PS              | 114 | 5V_DDCSCL/GPIOE11                           |

| 19  | MTR0                        | 51  | STB_WRITE        | 83  | CPU_PRESENT           | 115 | CC_DDCSDA/GPIOE12                           |

| 20  | INDEX                       | 52  | SMI              | 84  | PWRGD_3V              | 116 | 5V_DDCSDA/GPIOE10                           |

| 21  | DRATE0                      | 53  | SER_IRQ          | 85  | SLP_S3                | 117 | GPO11/VsbStrap1                             |

| 22  | DENSEL                      | 54  | LDRQ             | 86  | SLP_S5                | 118 | GPIOE00/RI2/IRTX                            |

| 23  | DCD1                        | 55  | PCI_CLK          | 87  | SMB1_SCL              | 119 | GPIOE01/SIN2/RI2                            |

| 24  | DSR1                        | 56  | LFRAME           | 88  | SMB2_SCL/HMSCL        | 120 | GPIOE02/SOUT2/IRRX                          |

| 25  | SIN1                        | 57  | LAD3             | 89  | SMB1_SDA              | 121 | GPIOE03/DSR2/SIN2                           |

| 26  | RTS1/TRIS                   | 58  | V <sub>SS</sub>  | 90  | SMB2_SDA/HMSDA        | 122 | GPO12/RTS2/SOUT2/<br>VddStrap1              |

| 27  | SOUT1/TEST                  | 59  | LAD2             | 91  | IOPA1/CLOCKI32/GPIO15 | 123 | TPM_PP/IOPA6                                |

| 28  | CTS1                        | 60  | V <sub>DD3</sub> | 92  | RSMRST                | 124 | GPIOE04/CTS2/DSR2                           |

| 29  | V <sub>SS</sub>             | 61  | LAD1             | 93  | V <sub>SB3</sub>      | 125 | GP <u>O13/DTR_</u> BOUT2/<br>RTS2/VddStrap2 |

| 30  | DTR_BOUT1/BADDR/<br>XOR_OUT | 62  | LAD0             | 94  | GRN_LED               | 126 | GPIOE05/DCD2/CTS2                           |

| 31  | V <sub>DD3</sub>            | 63  | PCI_RESET        | 95  | YLW_LED               | 127 | G <u>PIO</u> E06/IRRX/<br>DTR_BOUT2         |

| 32  | RI1                         | 64  | IDE_RSTDRV       | 96  | V <sub>SS</sub>       | 128 | GPIOE07/IRTX/DCD2                           |

#### **1.2 BUFFER TYPES AND SIGNAL/PIN DIRECTORY**

The signal DC characteristics of the pins described in Section 1.4 on page 10 are denoted by buffer type symbols, which are defined in Table 1 and described in further detail in Section 2.2 on page 22.

#### Table 1. Buffer Types

| Symbol            | Description                                                                                 |

|-------------------|---------------------------------------------------------------------------------------------|

| IN <sub>T</sub>   | Input, TTL compatible                                                                       |

| IN <sub>TS</sub>  | Input, TTL compatible, with 250 mV Schmitt Trigger                                          |

| IN <sub>TS2</sub> | Input, TTL compatible, with 200 mV Schmitt Trigger                                          |

| IN <sub>TS4</sub> | Input, TTL compatible, with 400 mV Schmitt Trigger                                          |

| IN <sub>PCI</sub> | Input, PCI 3.3V compatible                                                                  |

| IN <sub>SM</sub>  | Input, SMBus compatible                                                                     |

| IN <sub>ULR</sub> | Input, power, resistor protected (not characterized)                                        |

| AI                | Input, analog (0-5.5V tolerant)                                                             |

| O <sub>p/n</sub>  | Output, TTL/CMOS compatible, push-pull buffer capable of sourcing $p$ mA and sinking $n$ mA |

| OD <sub>n</sub>   | Output, TTL/CMOS compatible, open-drain buffer capable of sinking <i>n</i> mA               |

| O <sub>PCI</sub>  | Output, PCI 3.3V compatible,                                                                |

| AO                | Output, analog (0-5.5V tolerant)                                                            |

| SW <sub>SM</sub>  | Input/Output switch, SMBus compatible                                                       |

| PWR               | Power pin                                                                                   |

| GND               | Ground pin                                                                                  |

WWW.DataSheet4U.com

## **1.3 PIN MULTIPLEXING**

Table 2 shows only multiplexed pins, their associated functional blocks and the configuration bits for the selection of the multiplexed options used in the PC8374T.

# Table 2. Pin Multiplexing Configuration

|          |                   |                   |                     |                   |                     | )                 |                         |                        |                    |

|----------|-------------------|-------------------|---------------------|-------------------|---------------------|-------------------|-------------------------|------------------------|--------------------|

| Pin      | Default<br>Signal | Function<br>Block | Alternate<br>Signal | Function<br>Block | Alternate<br>Signal | Function<br>Block | Configuration Select    | Strap or<br>Wake-Up    | Function<br>Block  |

| 26       | RTS1              |                   |                     |                   |                     |                   |                         | TRIS                   |                    |

| 27       | SOUT1             | Serial<br>Port 1  |                     |                   |                     |                   |                         | TEST                   | Config<br>(Straps) |

| 90<br>90 | DTR_BOUT1         | -                 | XOR_OUT             | Config            |                     |                   | TEST (strap)            | BADDR                  | (242.0)            |

| 74       | PCIRST_OUT2       | Glue              | GPIOE12             | GPIO              |                     |                   | SIOCF4.nPCIRSTO2        | GPIOE12                |                    |

| 75       | GPIOE13           | GPIO              |                     |                   |                     |                   |                         | GPIOE13                | 2000               |

| 91       | GPIO15            | GPIO              | CLOCK132            | TPM               | IOPA1               | MGT               | TPM Firmware Controlled |                        |                    |

| 101      | GPIOE14           | GPIO              | IOPA0               | TPM               |                     |                   | TPM Firmware Controlled | GPIOE14                |                    |

| 103      | SWD               | МН                | GPIOE00             | GPIO              |                     |                   | SIOCF4.nSWD             | GPIOE00                | SWC                |

| 104      | GPIOE01           |                   | <b>FANTACH3</b>     |                   |                     |                   | SIOCF2. TACH3EN         | GPIOE01                |                    |

| 105      | GPIOE02           |                   | FANTACH4            |                   |                     |                   | SIOCF2.TACH4EN          | GPIOE02                |                    |

| 106      | GPIOE03           |                   | FANPWM1             |                   |                     |                   | SIOCF3.PWM1EN           | GPIOE03                |                    |

| 108      | GPIOE04           | GPIO              | FANPWM2             | MH                |                     |                   | SIOCF3.PWM2EN           | GPIOE04                |                    |

| 109      | GPIOE05           |                   | FANPWM3             |                   |                     |                   | SIOCF3.PWM3EN           | GPIOE05                |                    |

| 111      | GPIOE06           |                   | FANTACH1            |                   |                     |                   | SIOCF2. TACH1EN         | GPIOE06                | SWC                |

| 112      | GPIOE07           |                   | FANTACH2            |                   |                     |                   | SIOCF2. TACH2EN         | GPIOE07                |                    |

| 113      | CC_DDCSCL         |                   | GPIOE13             |                   |                     |                   |                         | GPIOE13                |                    |

| 114      | 5V_DDCSCL         |                   | GPIOE11             |                   |                     |                   | SIOCF2.GPI003EN         | GPIOE11                |                    |

| 115      | CC_DDCSDA         |                   | GPIOE12             | 2                 |                     |                   |                         | GPIOE12                |                    |

| 116      | 5V_DDCSDA         |                   | GPIOE10             |                   |                     |                   |                         | GPIOE10                |                    |

| 117      | GPO11             | GPIO              |                     |                   |                     |                   |                         | VsbStrap1 <sup>1</sup> | Strap              |

|               |                                                            |                   | Table               | Table 2. Pin Multiplexing Configuration (Continued) | exing Config          | uration (Cor      | itinued)                                              |                        |                    |

|---------------|------------------------------------------------------------|-------------------|---------------------|-----------------------------------------------------|-----------------------|-------------------|-------------------------------------------------------|------------------------|--------------------|

| Pin           | Default<br>Signal                                          | Function<br>Block | Alternate<br>Signal | Function<br>Block                                   | Alternate<br>Signal   | Function<br>Block | Configuration Select                                  | Strap or<br>Wake-Up    | Function<br>Block  |

| 118           | GPIOE00                                                    |                   | RIZ                 |                                                     | IRTX                  | InfraRed          | SIOCF3.373COMP AND<br>SIOCF3.SP2EN AND<br>SIOCF3.IREN | RIZ                    | SWC                |

| 119           | GPIOE01                                                    |                   | SIN2                |                                                     | <u>RI2</u>            | Serial<br>Port 2  | SIOCF3.373COMP AND<br>SIOCF3.SP2EN                    | <u>RI2</u>             |                    |

| 120           | GPIOE02                                                    |                   | SOUT2               | Serial                                              | ІЯКХ                  | InfraRed          | SIOCF3.373COMP AND<br>SIOCF3.SP2EN AND<br>SIOCF3.IREN |                        |                    |

| 121           | GPIOE03                                                    |                   | DSR2                | Port 2                                              | SIN2                  |                   |                                                       | 1                      |                    |

| 122           | GPO12                                                      | GPIO              | RTS2                |                                                     | SOUT2                 |                   |                                                       | VddStrap1 <sup>2</sup> | Config<br>(Straps) |

| 124           | GPIOE04                                                    |                   | <u>CTS2</u>         |                                                     | DSR2                  |                   | SIOCF3.373COMP AND<br>SIOCF3.SP2EN                    |                        |                    |

| 125           | GPO13                                                      |                   | DTR_BOUT2           |                                                     | <u>RTS2</u>           | Serial<br>Port 2  |                                                       | VddStrap2              | Config<br>(Straps) |

| 126           | GPIOE05                                                    |                   | DCD2                |                                                     | <u>CTS2</u>           |                   |                                                       |                        |                    |

| 127           | GPIOE06                                                    |                   | IRRX                | InfraRed                                            | <u>DTR_</u> BOUT<br>2 |                   | SIOCF3.373COMP AND<br>SIOCF3.SP2EN AND                |                        |                    |

| 128           | GPIOE07                                                    |                   | IRTX                |                                                     | DCD2                  |                   | SIOCF3.IREN                                           |                        |                    |

| 123           | <u>TPM_PP</u>                                              | МЧТ               | IOPA6               | MGT                                                 |                       |                   | TPM Firmware controlled                               |                        |                    |

| <del>- </del> | 1. V <sub>SB</sub> strap input. Reserved for National use. | leserved for      | National use.       |                                                     |                       |                   |                                                       |                        |                    |

2. V<sub>DD</sub> strap input. Reserved for National use.

#### 1.0 Signal/Pin Connection and Description (Continued)

#### 1.4 DETAILED SIGNAL/PIN DESCRIPTIONS

This section describes all signals of the PC8374T device. The signals are organized by functional group.

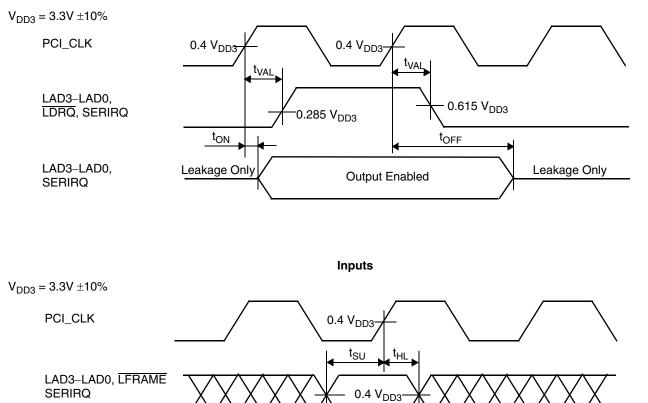

#### 1.4.1 LPC Interface

| Signal    | Pin(s)           | I/O | Buffer Type                         | Power Well       | Description                                                                                                                           |

|-----------|------------------|-----|-------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| LAD3-0    | 57, 59,<br>61-62 | I/O | IN <sub>PCI</sub> /O <sub>PCI</sub> | V <sub>DD3</sub> | LPC Address-Data. Multiplexed command, address bi-directional data and cycle status.                                                  |

| PCI_CLK   | 55               | I   | IN <sub>PCI</sub>                   | V <sub>DD3</sub> | LPC Clock. PCI clock used for the LPC bus (up to 33 MHz).                                                                             |

| LFRAME    | 56               | I   | IN <sub>PCI</sub>                   | V <sub>DD3</sub> | <b>LPC Frame.</b> Low pulse indicates the beginning of a new LPC cycle or termination of a broken cycle.                              |

| LDRQ      | 54               | 0   | O <sub>PCI</sub>                    | V <sub>DD3</sub> | LPC DMA Request. Encoded DMA request for LPC interface.                                                                               |

| PCI_RESET | 63               | I   | IN <sub>PCI</sub>                   | V <sub>DD3</sub> | LPC Reset. PCI system reset used for the LPC bus (Hardware Reset).                                                                    |

| SER_IRQ   | 53               | I/O | IN <sub>PCI</sub> /O <sub>PCI</sub> | $V_{DD3}$        | Serial IRQ. The interrupt requests are serialized over a single pin, where each IRQ level is delivered during a designated time slot. |

| SMI       | 52               | 0   | OD <sub>6</sub>                     | V <sub>DD3</sub> | System Management Interrupt. Active (low) level indicates that an SMI occurred. External pull-up resistor to $V_{DD3}$ is required.   |

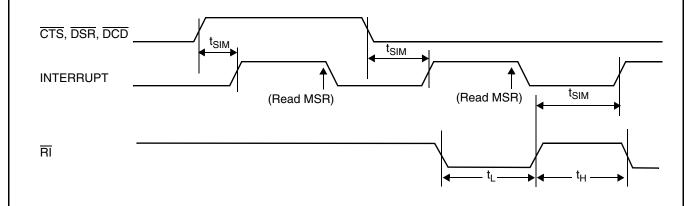

#### 1.4.2 Serial Port 1 and Serial Port 2 (UART1 and UART2)

| Signal    | Pin(s)        | I/O | Buffer Type      | Power Well       | Description                                                                                                                                                                                                                                                                                                                                                                          |

|-----------|---------------|-----|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTS1      | 28            | I   | IN <sub>TS</sub> | V <sub>DD3</sub> | Clear to Send. When low, indicates that the modem or other data                                                                                                                                                                                                                                                                                                                      |

| CTS2      | 124 or<br>126 | I   | IN <sub>TS</sub> | V <sub>DD3</sub> | transfer device is ready to exchange data.                                                                                                                                                                                                                                                                                                                                           |

| DCD1      | 23            | Ι   | IN <sub>TS</sub> | V <sub>DD3</sub> | Data Carrier Detected. When low, indicates that the modem or                                                                                                                                                                                                                                                                                                                         |

| DCD2      | 126 or<br>128 | Ι   | IN <sub>TS</sub> | V <sub>DD3</sub> | other data transfer device has detected the data carrier.                                                                                                                                                                                                                                                                                                                            |

| DSR1      | 24            | Ι   | IN <sub>TS</sub> | V <sub>DD3</sub> | <b>Data Set Ready.</b> When low, indicates that the data transfer                                                                                                                                                                                                                                                                                                                    |

| DSR2      | 121 or<br>124 | I   | IN <sub>TS</sub> | V <sub>DD3</sub> | device, e.g., modem, is ready to establish a communications link.                                                                                                                                                                                                                                                                                                                    |

| DTR_BOUT1 | 30            | 0   | O <sub>4/8</sub> | V <sub>DD3</sub> | Data Terminal Ready. When low, indicates to the modem or                                                                                                                                                                                                                                                                                                                             |

| DTR_BOUT2 | 125 or<br>127 | 0   | O <sub>4/8</sub> | V <sub>DD3</sub> | other data transfer device that the corresponding UART is ready<br>to establish a communications link. After a system reset, these<br>pins provide the DTR function and set these signals to inactive<br>high.<br><b>Baud Output.</b> Provides the associated serial channel baud rate<br>generator output signal if test mode is selected, i.e., bit 7 of<br>EXCR1 register is set. |

| RI1       | 32            | I   | IN <sub>TS</sub> | V <sub>DD3</sub> | Ring Indicator. When low, indicates that a telephone ring signal                                                                                                                                                                                                                                                                                                                     |

| RI2       | 118 or<br>119 | I   | IN <sub>TS</sub> | V <sub>DD3</sub> | was received by the modem. These pins are monitored during $V_{DD}$ power-off for wake-up event detection.                                                                                                                                                                                                                                                                           |

| RTS1      | 26            | 0   | O <sub>4/8</sub> | V <sub>DD3</sub> | Request to Send. When low, indicates to the modem or other                                                                                                                                                                                                                                                                                                                           |

| RTS2      | 122 or<br>125 | 0   | O <sub>4/8</sub> | V <sub>DD3</sub> | data transfer device that the corresponding UART device is ready to exchange data. A system reset sets these signals to inactive high.                                                                                                                                                                                                                                               |

| SIN1      | 25            | Ι   | IN <sub>TS</sub> | V <sub>DD3</sub> | Serial Input. Receives composite serial data from the                                                                                                                                                                                                                                                                                                                                |

| SIN2      | 119 or<br>121 | Ι   | IN <sub>TS</sub> | V <sub>DD3</sub> | communications link (peripheral device, modem or other data transfer device).                                                                                                                                                                                                                                                                                                        |

| Signal | Pin(s)        | I/O | Buffer Type      | Power Well | Description                                                                                                                           |

|--------|---------------|-----|------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------|

| SOUT1  | 27            | 0   | O <sub>4/8</sub> | 000        | Serial Output. Sends composite serial data to the                                                                                     |

| SOUT2  | 120 or<br>122 | 0   | O <sub>4/8</sub> |            | communications link (peripheral device, modem or other data transfer device). These signals are set active high after a system reset. |

#### 1.4.3 InfraRed Port

| Signal | Pin(s)        | I/O | Buffer Type       | Power Well       | Description                                     |

|--------|---------------|-----|-------------------|------------------|-------------------------------------------------|

| IRRX   | 127 or<br>120 | Ι   | IN <sub>TS</sub>  | V <sub>DD3</sub> | InfraRed Receive. InfraRed serial input data.   |

| IRTX   | 128 or<br>118 | 0   | O <sub>6/12</sub> | V <sub>DD3</sub> | InfraRed Transmit. InfraRed serial output data. |

#### 1.4.4 Parallel Port

| Signal     | Pin(s) | I/O | Buffer Type                           | Power Well       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|--------|-----|---------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACK        | 36     | I   | IN <sub>T</sub>                       | V <sub>DD3</sub> | <b>Acknowledge.</b> Pulsed low by the printer to indicate that it has received data from the parallel port.                                                                                                                                                                                                                                                                                                                                  |

| AFD_DSTRB  | 50     | 0   | OD <sub>14</sub> , O <sub>14/14</sub> | V <sub>DD3</sub> | <b>AFD</b> - Automatic Feed. When low, instructs the printer to automatically feed a line after printing each line. This pin is in TRI-STATE after a 0 is loaded into the corresponding control register bit. An external 4.7 K $\Omega$ pull-up resistor must be connected to this pin.<br><b>DSTRB</b> - Data Strobe (EPP). Active low; used in EPP mode to denote a data cycle. When the cycle is aborted, DSTRB becomes inactive (high). |

| BUSY_WAIT  | 35     | I   | IN <sub>T</sub>                       | V <sub>DD3</sub> | <ul><li>Busy. Set high by the printer when it cannot accept another character.</li><li>Wait. In EPP mode, the parallel port device uses this active low signal to extend its access cycle.</li></ul>                                                                                                                                                                                                                                         |

| ERR        | 45     | Ι   | IN <sub>T</sub>                       | V <sub>DD3</sub> | Error. Set active low by the printer when it detects an error.                                                                                                                                                                                                                                                                                                                                                                               |

| INIT       | 48     | 0   | OD <sub>14</sub> , O <sub>14/14</sub> | V <sub>DD3</sub> | <b>Initialize.</b> When low, initializes the printer. This signal is in TRI-STATE after a 1 is loaded into the corresponding control register bit. An external 4.7 K $\Omega$ pull-up resistor must be connected to this pin.                                                                                                                                                                                                                |

| PD7-0      | 37-44  | I/O | IN <sub>T</sub> /O <sub>14/14</sub>   | V <sub>DD3</sub> | <b>Parallel Port Data.</b> Transfers data to and from the peripheral data bus and the appropriate parallel port data register. These signals have a high current drive capability.                                                                                                                                                                                                                                                           |

| PE         | 34     | I   | IN <sub>T</sub>                       | V <sub>DD3</sub> | <b>Paper End.</b> Set high by the printer when it is out of paper.<br>This pin has an internal weak pull-up or pull-down resistor.                                                                                                                                                                                                                                                                                                           |

| SLCT       | 33     | I   | IN <sub>T</sub>                       | V <sub>DD3</sub> | Select. Set active high by the printer when the printer is selected.                                                                                                                                                                                                                                                                                                                                                                         |

| SLIN_ASTRB | 47     | 0   | OD <sub>14</sub> , O <sub>14/14</sub> | V <sub>DD3</sub> | <b>SLIN</b> - Select Input. When low, selects the printer. This signal is in TRI-STATE after a 0 is loaded into the corresponding control register bit. An external 4.7 K $\Omega$ pull-up resistor must be connected to this pin.<br><b>ASTRB</b> - Address Strobe (EPP). Active low, used in EPP mode to denote an address cycle. When the cycle is aborted, ASTRB becomes inactive (high).                                                |

#### 1.0 Signal/Pin Connection and Description (Continued)

| Signal    | Pin(s) | I/O | Buffer Type                           | Power Well | Description                                                                                                                                                                                                                                                                                         |

|-----------|--------|-----|---------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STB_WRITE | 51     | 0   | OD <sub>14</sub> , O <sub>14/14</sub> |            | $\overline{\text{STB}}$ - Data Strobe. When low, Indicates to the printer that valid data is available at the printer port. This signal is in TRI-STATE after a 0 is loaded into the corresponding control register bit. An external 4.7 K $\Omega$ pull-up resistor must be connected to this pin. |

|           |        |     |                                       |            | <b>WRITE</b> - Write Strobe. Active low, used in EPP mode to denote an address or data write cycle. When the cycle is aborted, WRITE becomes inactive (high).                                                                                                                                       |

#### 1.4.5 Floppy Disk Controller (FDC)

| Signal | Pin(s) | I/O | Buffer Type                        | Power Well       | Description                                                                                                                                                                                                |

|--------|--------|-----|------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DENSEL | 22     | 0   | OD <sub>12</sub> O <sub>6/12</sub> | V <sub>DD3</sub> | <b>Density Select.</b> Indicates that a high FDC density data rate (500 Kbps, 1 Mbps or 2 Mbps) or a low density data rate (250 or 300 Kbps) is selected.                                                  |

| DIR    | 17     | 0   | OD <sub>12</sub> O <sub>6/12</sub> | V <sub>DD3</sub> | <b>Direction.</b> Determines the direction of the Floppy Disk Drive (FDD) head movement (active = step in; inactive = step out) during a seek operation.                                                   |

| DR0    | 18     | 0   | OD <sub>12</sub> O <sub>6/12</sub> | V <sub>DD3</sub> | <b>Drive Select.</b> Active low signal controlled by bit 0 of the Digital Output Register (DOR).                                                                                                           |

| DRATE0 | 21     | 0   | OD <sub>12</sub> O <sub>6/12</sub> | V <sub>DD3</sub> | <b>Data Rate.</b> Reflects the value of bit 0 of either Configuration<br>Control Register (CCR) or Data Rate Select Register (DSR),<br>whichever was written to last.                                      |

| DSKCHG | 9      | I   | IN <sub>TS</sub>                   | V <sub>DD3</sub> | Disk Change. Indicates that the drive door was opened.                                                                                                                                                     |

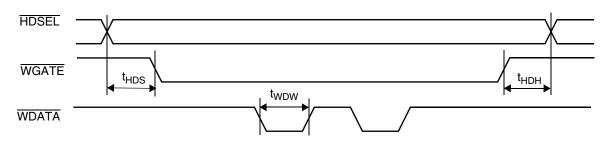

| HDSEL  | 10     | 0   | OD <sub>12</sub> O <sub>6/12</sub> | V <sub>DD3</sub> | <b>Head Select.</b> Selects which side of the FDD is accessed. Active (low) selects side 1; inactive selects side 0.                                                                                       |

| INDEX  | 20     | I   | IN <sub>TS</sub>                   | V <sub>DD3</sub> | Index. Indicates the beginning of an FDD track.                                                                                                                                                            |

| MTR0   | 19     | 0   | OD <sub>12</sub> O <sub>6/12</sub> | V <sub>DD3</sub> | <b>Motor Select.</b> Active low motor enable signal for drive 0, controlled by bit D4 of the Digital Output Register (DOR).                                                                                |

| RDATA  | 11     | Ι   | IN <sub>TS</sub>                   | V <sub>DD3</sub> | Read Data. Raw serial input data stream read from the FDD.                                                                                                                                                 |

| STEP   | 16     | 0   | OD <sub>12</sub> O <sub>6/12</sub> | V <sub>DD3</sub> | <b>Step.</b> Issues pulses to the disk drive at a software programmable rate to move the head during a seek operation.                                                                                     |

| TRK0   | 13     | Ι   | IN <sub>TS</sub>                   | V <sub>DD3</sub> | <b>Track 0.</b> Indicates to the controller that the head of the selected floppy disk drive is at track 0.                                                                                                 |

| WDATA  | 15     | 0   | OD <sub>12</sub> O <sub>6/12</sub> | V <sub>DD3</sub> | Write Data. Carries out the pre-compensated serial data that is written to the FDD. Pre-compensation is software selectable.                                                                               |

| WGATE  | 14     | 0   | OD <sub>12</sub> O <sub>6/12</sub> | V <sub>DD3</sub> | <b>Write Gate.</b> Enables the write circuitry of the selected FDD.<br>WGATE is designed to prevent glitches during power-up and<br>power-down. This prevents writing to the disk when power is<br>cycled. |

| WP     | 12     | Ι   | IN <sub>TS</sub>                   | V <sub>DD3</sub> | Write Protected. Indicates that the disk in the selected drive is write protected.                                                                                                                         |

## PC8374T

#### 1.4.6 Keyboard and Mouse Controller (KBC)

| Signal | Pin(s) | I/O | Buffer Type                                            | Power Well       | Description                                                                                                                                                                            |

|--------|--------|-----|--------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

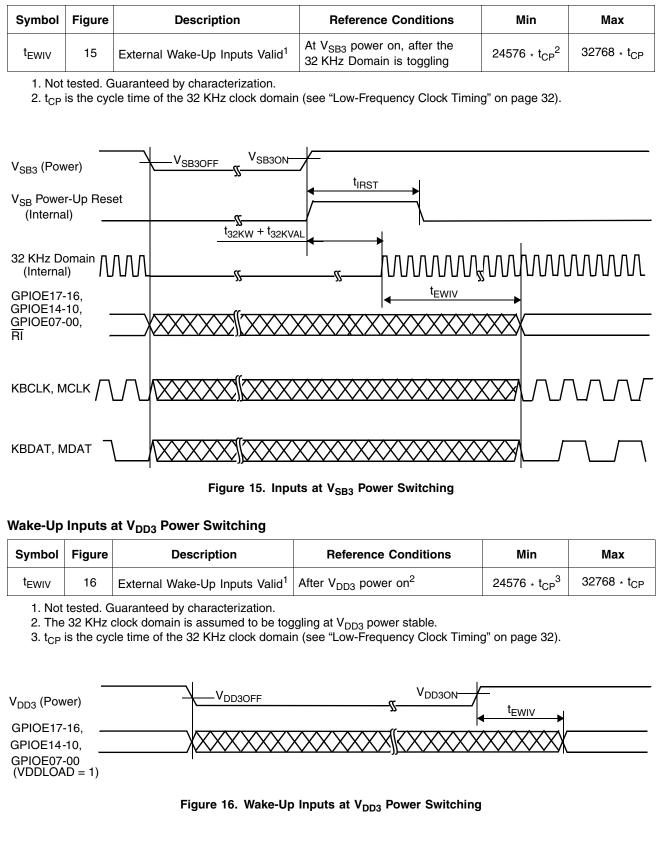

| KBCLK  | 3      | I/O | IN <sub>TS</sub> /OD <sub>14</sub>                     | V <sub>DD3</sub> | <b>Keyboard Clock.</b> Keyboard clock signal. External pull-up resistor is required for PS/2 compliance. This pin is monitored during $V_{DD3}$ power-off for wake-up event detection. |

| KBDAT  | 4      | I/O | IN <sub>TS</sub> /OD <sub>14</sub>                     | V <sub>DD3</sub> | <b>Keyboard Data.</b> Keyboard data signal. External pull-up resistor is required for PS/2 compliance. This pin is monitored during $V_{DD3}$ power-off for wake-up event detection.   |

| MCLK   | 1      | I/O | IN <sub>TS</sub> /OD <sub>14</sub>                     | V <sub>DD3</sub> | <b>Mouse Clock.</b> Mouse clock signal. External pull-up resistor is required for PS/2 compliance. This pin is monitored during $V_{DD3}$ power-off for wake-up event detection.       |

| MDAT   | 2      | I/O | IN <sub>TS</sub> /OD <sub>14</sub>                     | V <sub>DD3</sub> | <b>Mouse Data.</b> Mouse data signal. External pull-up resistor is required for PS/2 compliance. This pin is monitored during $V_{DD3}$ power-off for wake-up event detection.         |

| KBRST  | 7      | I/O | IN <sub>T</sub> /OD <sub>8</sub> ,<br>O <sub>4/8</sub> | V <sub>DD3</sub> | KBD Reset. Keyboard reset (P20) quasi-bidirectional output.                                                                                                                            |

| GA20   | 5      | I/O | IN <sub>T</sub> /OD <sub>8</sub> ,<br>O <sub>4/8</sub> | V <sub>DD3</sub> | Gate A20. KBC gate A20 (P21) quasi-bidirectional output.                                                                                                                               |

#### 1.4.7 General-Purpose I/O (GPIO)

| Signal                 | Pin(s)                      | I/O                                                        | Buffer Type                                                                  | Power Well                                                                                                                                                                             | Description                                                                                                                                                                                  |

|------------------------|-----------------------------|------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOE00                | 103                         |                                                            | IN <sub>TS</sub> /<br>OD <sub>8</sub> , O <sub>4/8</sub>                     | <sup>V SB3</sup> independently as input or I/O, with or without static pu                                                                                                              | <b>General-Purpose I/O Ports.</b> Each pin is configured independently as input or I/O, with or without static pull-up (and some also with or without static pull-down) and with either open |

|                        | 118                         | IN <sub>TS</sub> /<br>OD <sub>12</sub> , O <sub>6/12</sub> | V <sub>DD3</sub>                                                             | drain or push-pull output type. These pins have event detection capability to generate a wake-up event or an interrupt.<br><b>Note:</b> If GPIOE12 is configured (on pin 74) make sure |                                                                                                                                                                                              |

| GPIOE01-06             | 104-106,<br>108-109,<br>111 |                                                            | IN <sub>TS</sub> /<br>OD <sub>8</sub> , O <sub>4/8</sub><br>V <sub>DD3</sub> | V <sub>SB3</sub>                                                                                                                                                                       | that the pin's default function does not interfere with<br>the circuit connected to the GPIO. Failure to do so may<br>result in irreversible damage to the chip.                             |

|                        | 119-121,<br>124,<br>126-127 | , OD <sub>8</sub> , O <sub>4/8</sub>                       |                                                                              | V <sub>DD3</sub>                                                                                                                                                                       |                                                                                                                                                                                              |

| GPIOE07                | 112                         |                                                            |                                                                              |                                                                                                                                                                                        |                                                                                                                                                                                              |

|                        | 128                         |                                                            | IN <sub>TS</sub> /<br>OD <sub>12</sub> , O <sub>6/12</sub>                   | V <sub>DD3</sub>                                                                                                                                                                       |                                                                                                                                                                                              |

| GPIOE10-13             | 116, 114,<br>115, 113       |                                                            | IN <sub>TS2</sub> /<br>OD <sub>6</sub> , O <sub>3/6</sub>                    |                                                                                                                                                                                        |                                                                                                                                                                                              |

| GPIOE12-13             | 74-75                       |                                                            | IN <sub>TS</sub> /                                                           |                                                                                                                                                                                        |                                                                                                                                                                                              |

| GPIOE14,<br>GPIOE16-17 | 101,<br>100, 80             |                                                            | OD <sub>8</sub> , O <sub>4/8</sub>                                           | V <sub>SB3</sub>                                                                                                                                                                       |                                                                                                                                                                                              |

| GPIO15                 | 91                          |                                                            | IN <sub>TS</sub> /<br>OD <sub>8</sub> , O <sub>4/8</sub>                     |                                                                                                                                                                                        | <b>General-Purpose I/O Port.</b> This pin is configured independently as input or I/O with or without static pull-up and with either open-drain or push-pull output type.                    |

| GPO11                  | 117                         |                                                            | OD <sub>8</sub> , O <sub>4/8</sub>                                           |                                                                                                                                                                                        | General-Purpose Output Port. This pin is configured                                                                                                                                          |

| GPO12-13               | 122, 125                    | 0                                                          |                                                                              | V <sub>DD3</sub>                                                                                                                                                                       | independently as output, with or without static pull-up and with<br>either open-drain or push-pull output type.                                                                              |

#### 1.0 Signal/Pin Connection and Description (Continued)

#### 1.4.8 Health Management (HM)

| Signal     | Pin(s)              | I/O | Buffer Type                         | Power Well       | Description                                                                                                                                                 |

|------------|---------------------|-----|-------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SWD        | 103                 | I/O | IN <sub>SM</sub> /OD <sub>6</sub>   | V <sub>SB3</sub> | <b>SensorPath<sup>™</sup> Data.</b> Bidirectional, SensorPath Data interface signal to LMxx sensor device(s). An internal pull-up for this pin is optional. |

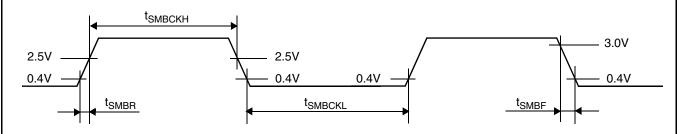

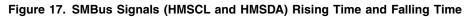

| HMSCL      | 88                  | I/O | IN <sub>SM</sub> /OD <sub>6</sub>   | V <sub>SB3</sub> | Health Management SMBus Serial Clock. Serial clock signal. External pull-up resistor is required.                                                           |

| HMSDA      | 90                  | I/O | IN <sub>SM</sub> /OD <sub>6</sub>   | V <sub>SB3</sub> | Health Management SMBus Serial Data. Serial data signal.<br>External pull-up resistor is required.                                                          |

| FANTACH1-4 | 111-112,<br>104-105 | I   | IN <sub>TS</sub>                    | V <sub>DD3</sub> | Fan Inputs. Used to feed the fan's tachometer pulse to the Fan Speed Monitor.                                                                               |

| FANPWM1-3  | 106,<br>108-109     | 0   | OD <sub>12</sub> ,O <sub>6/12</sub> | V <sub>DD3</sub> | <b>Fan Outputs.</b> Pulse Width Modulation (PWM) signals, used to control the speed of cooling fans by controlling the voltage supplied to the fan motors.  |

#### 1.4.9 Trusted Platform Module (TPM)

| Signal                    | Pin(s)             | I/O | Buffer Type                                              | Power Well | Description                                                                                                                                                                                                                                                         |

|---------------------------|--------------------|-----|----------------------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPM_PP                    | 123                | I   | IN <sub>TS</sub>                                         | $V_{SB3}$  | Physical Presence Input. Indicates owner's physical presence.                                                                                                                                                                                                       |

| IOPA0,<br>IOPA1,<br>IOPA6 | 101,<br>91,<br>123 | I/O | IN <sub>TS</sub> /<br>OD <sub>8</sub> , O <sub>4/8</sub> | 000        | <b>General-Purpose I/O Ports.</b> Each pin is configured independently as input or I/O, with or without static pull-up and with either open-drain or push-pull output type. These pins have event detection capability to generate a wake-up event or an interrupt. |

#### 1.4.10 System Wake-Up Control (SWC)

| Signal                 | Pin(s)                          | I/O | Buffer Type       | Power Well       | Description                                                                                                                                                                         |

|------------------------|---------------------------------|-----|-------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOE00-07             | 103-106,<br>108-109,<br>111-112 |     | IN <sub>TS</sub>  | V <sub>SB3</sub> | <b>Wake-Up Inputs.</b> Generates a wake-up event. These pins have programmable debouncing. When the pin is not used, the internal pull-up resistor must be enabled to allow the pin |

|                        | 118-121,<br>124,<br>126-128     | 1   | in 18             | V <sub>DD3</sub> | to be left not connected.                                                                                                                                                           |

| GPIOE10-13             | 116, 114,<br>115, 113           | I   | IN <sub>TS2</sub> |                  |                                                                                                                                                                                     |

| GPIOE12-13             | 74-75                           |     |                   | V <sub>SB3</sub> |                                                                                                                                                                                     |

| GPIOE14,<br>GPIOE16-17 | 101,<br>100, 80                 |     | IN <sub>TS</sub>  |                  |                                                                                                                                                                                     |

| <u>RI1</u><br>RI2      | 32,<br>118 or<br>119            | I   | IN <sub>TS</sub>  | V <sub>SB3</sub> | <b>Ring Indicator Wake-Up.</b> When low, generates a wake-up event, indicating that a telephone ring signal was received by the modem.                                              |

| KBCLK                  | 3                               | Ι   | IN <sub>TS</sub>  | V <sub>SB3</sub> | Keyboard Clock Wake-Up. Generates a wake-up event when a specific keyboard sequence is detected.                                                                                    |

| KBDAT                  | 4                               | I   | IN <sub>TS</sub>  | V <sub>SB3</sub> | <b>Keyboard Data Wake-Up.</b> Generates a wake-up event when a specific keyboard sequence is detected.                                                                              |

| MCLK                   | 1                               | I   | IN <sub>TS</sub>  | V <sub>SB3</sub> | Mouse Clock Wake-Up. Generates a wake-up event when a specific mouse action is detected.                                                                                            |

| Signal                   | Pin(s)    | I/O | Buffer Type                        | Power Well       | Description                                                                                                                                                                                               |  |

|--------------------------|-----------|-----|------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MDAT                     | 2         | I   | IN <sub>TS</sub>                   | V <sub>SB3</sub> | Mouse Data Wake-Up. Generates a wake-up event when a specific mouse action is detected.                                                                                                                   |  |

| SIOPME                   | 99        | 0   | OD <sub>8</sub> , O <sub>4/8</sub> | V <sub>SB3</sub> | <b>Power Management Event (SCI).</b> Active level indicates that wake-up event occurred, causing the system to exit its currer sleep state. This signal has programmable polarity (default i active low). |  |

| <u>SLP_S3,</u><br>SLP_S5 | 85,<br>86 | I   | IN <sub>TS4</sub>                  | V <sub>SB3</sub> | Sleep States 3 to 5. Active (low) level indicates the system is in one of the sleep states S3 or S5. These signals are generated by an external ACPI controller.                                          |  |

| YLW_LED,<br>GRN_LED      | 95,<br>94 | 0   | OD <sub>24</sub>                   | V <sub>SB3</sub> | <b>Power LEDs.</b> Yellow and green LED drivers. Each indicates the Main power status or blinks under software control.                                                                                   |  |

#### 1.4.11 Clocks

| Signal   | Pin(s) | I/O | Buffer Type      | Power Well | Description                                                                                                          |

|----------|--------|-----|------------------|------------|----------------------------------------------------------------------------------------------------------------------|

| CLOCKI32 | 91     | Ι   | IN <sub>TS</sub> | $V_{SB3}$  | Low-Frequency Clock Input. 32.768 KHz clock for the TPM timing.                                                      |

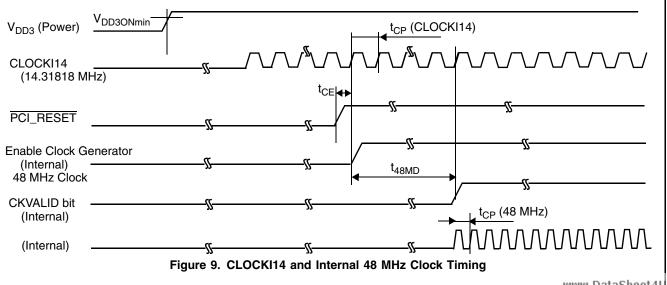

| CLOCKI14 | 65     | Ι   | IN <sub>TS</sub> |            | High-Frequency Clock Input. 14.31818 MHz clock for the on-<br>chip, 48 MHz Clock Generator (for the Legacy modules). |

#### 1.4.12 Glue Functions

| Signal             | Pin(s) | I/O | Buffer Type        | Power Well       | Description                                                                                                                                                                                                                          |

|--------------------|--------|-----|--------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

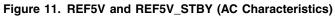

| REF5V              | 70     | 0   | AO                 | V <sub>SB3</sub> | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                 |

| REF5V_STBY         | 72     | 0   | AO                 | V <sub>SB3</sub> | Standby Highest Active Supply, Reference Output. Reference voltage equal to the highest voltage between $V_{SB5}$ and $V_{SB3}$ . External pull-up resistor to $V_{SB5}$ is required.                                                |

| PS_ON              | 81     | 0   | OD <sub>6</sub>    | V <sub>SB3</sub> | $\begin{array}{l} \mbox{Main Power Supply On/Off Control.} \ \mbox{Active (low) level turns} \\ \mbox{the main power supply (V_{DD}) on.} \ \mbox{External pull-up resistor to} \\ \mbox{V}_{SB5} \ \mbox{is required.} \end{array}$ |

| PWRGD_PS           | 82     | I   | IN <sub>TS4</sub>  | V <sub>SB3</sub> | <b>Power Good Signal from the Power Supply.</b> Active level indicates the Main power supply voltage is valid.                                                                                                                       |

| PWRGD_3V           | 84     | 0   | O <sub>3/6</sub>   | V <sub>SB3</sub> | <b>Power Good Output.</b> Active level indicates: Main supply voltage is valid and the system is in a higher than S3 sleep state.                                                                                                    |

| CPU_PRESENT        | 83     | I   | IN <sub>TS4</sub>  | V <sub>SB3</sub> | <b>CPU Present.</b> Active (low) level indicates a processor is currently plugged in.                                                                                                                                                |

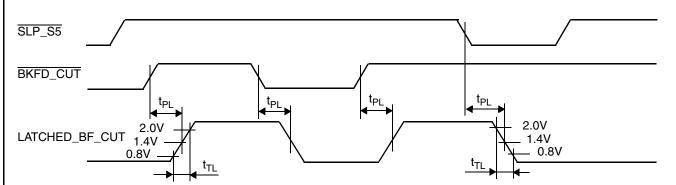

| BKFD_CUT           | 77     | 0   | OD <sub>6</sub>    | V <sub>SB3</sub> | <b>Backfeed-Cut Control.</b> Power distribution control (when switching between main and standby regulators) for system transition into and out of the S3 sleep state. External pull-up resistor to $V_{SB5}$ is required.           |

| LATCHED_BF_<br>CUT | 79     | 0   | O <sub>14/14</sub> | V <sub>SB3</sub> | <b>Latched Backfeed-Cut.</b> Power distribution control (when switching between main and standby regulators) for system transition into and out of the S5 sleep state.                                                               |

| VSB5               | 71     | I   | AI                 | V <sub>SB3</sub> | Standby 5V Power Supply. Used for Resume Reset generation (Range: 0-5.5V, Backdrive protected).                                                                                                                                      |

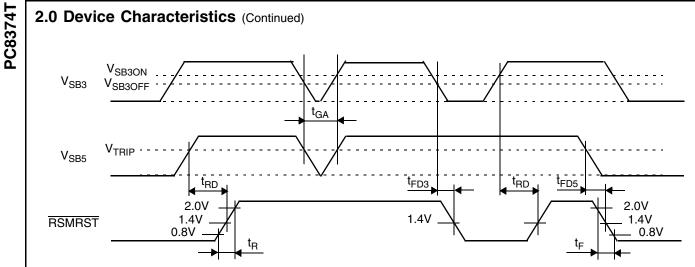

| RSMRST             | 92     | 0   | O <sub>3/6</sub>   | V <sub>SB3</sub> | Resume Reset. Power-Up reset signal based on the $V_{SB5}$ supply voltage.                                                                                                                                                           |

| Signal       | Pin(s) | I/O | Buffer Type        | Power Well       | Description                                                                                                                                                                                                                    |  |  |  |

|--------------|--------|-----|--------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PRIMARY_HD   | 67     | I   | IN <sub>TS4</sub>  | V <sub>DD3</sub> | <b>Primary Drive.</b> Active (low) level indicates that the primary IDE drive is active.                                                                                                                                       |  |  |  |

| SECONDARY_HD | 68     | I   | IN <sub>TS4</sub>  | V <sub>DD3</sub> | Secondary Drive. Active (low) level indicates that the secondary IDE drive is active.                                                                                                                                          |  |  |  |

| SCSI         | 69     | Ι   | IN <sub>TS4</sub>  | V <sub>DD3</sub> | SCSI Drive. Active (low) level indicates that the SCSI drive is active.                                                                                                                                                        |  |  |  |

| HD_LED       | 66     | 0   | OD <sub>12</sub>   | V <sub>DD3</sub> | Hard Drive LED. Red LED driver. When low, indicates that at least one drive is active.                                                                                                                                         |  |  |  |

| CC_DDCSCL    | 113    | I/O | SW <sub>SM</sub>   | V <sub>SB3</sub> | Chipset Cluster (2.5V or 3.3V) Level DDC Serial Clock.<br>SMBus serial clock signal with 2.5V or 3.3V logic levels for<br>Data Display Channel (DDC) interface. External pull-up<br>resistor to $V_{DD3}$ or 2.5V is required. |  |  |  |

| 5V_DDCSCL    | 114    | I/O | SW <sub>SM</sub>   | V <sub>SB3</sub> | <b>5V Level DDC Serial Clock.</b> SMBus serial clock signal with 5V logic levels for VGA monitor interface. External pull-up resistor to $V_{DD5}$ is required.                                                                |  |  |  |

| CC_DDCSDA    | 115    | I/O | SW <sub>SM</sub>   | V <sub>SB3</sub> | Chipset Cluster (2.5V or 3.3V) Level DDC Serial Data.<br>SMBus serial data signal with 2.5V or 3.3V logic levels for<br>DDC interface. External pull-up resistor to $V_{DD3}$ or 2.5V is<br>required.                          |  |  |  |

| 5V_DDCSDA    | 116    | I/O | SW <sub>SM</sub>   | V <sub>SB3</sub> | <b>5V Level DDC Serial Data.</b> SMBus serial data signal with 5V logic levels for VGA monitor interface. External pull-up resistor to $V_{DD5}$ is required.                                                                  |  |  |  |

| SMB1_SCL     | 87     | I/O | SW <sub>SM</sub>   | V <sub>SB3</sub> | <b>Bus 1 Serial Clock.</b> Serial clock signal of SMBus 1 (3.3V logic levels). External pull-up resistor to the 3.3V supply is required.                                                                                       |  |  |  |