# National Semiconductor

## ADVANCE INFORMATION

November 1990

# PC87120 SuperAT™

# 1.0 General Description

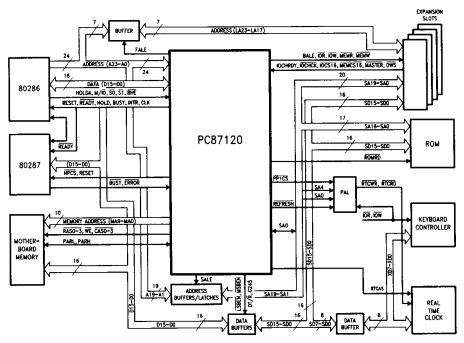

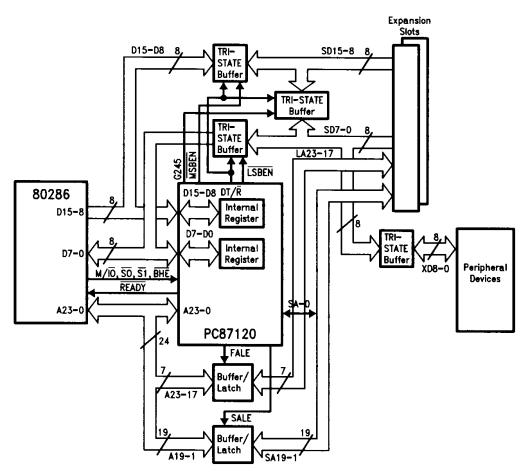

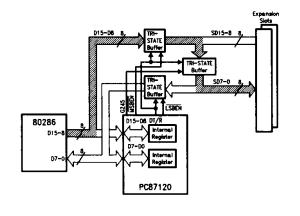

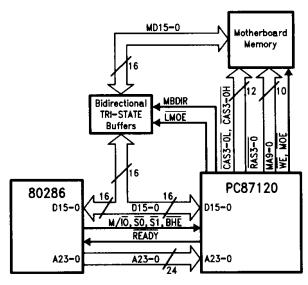

The PC87120, SuperAT, implements most of the medium scale/small scale integration circuits used in building an 80286 processor kernel in one chip. With the PC87120, a complete solution for 10–16 MHz 80286-based mother-board can be designed together with a CPU, memory devices and 16 ICs.

The PC87120 integrates all of the peripheral support required for compatibility in a PC/AT system, along with a programmable clock generator, a programmable bus controller and a programmable memory controller. In addition, the PC87120 incorporates a processor-coprocessor interface, a peripheral chip select, speaker circuitry, ROM BIOS access logic, and reset logic for the processor, coprocessor and the entire system.

The clock generator and bus controller can be programmed to run the processor and the expansion bus synchronously or asynchronously. This allows the designer to increase the system's performance while remaining compatible with the standard 8 MHz expansion bus.

The memory controller can be configured to support 1, 2 or 4 memory banks with zero or one programmed wait state. Conventional mode, two-way page interleaving mode or enhanced two-way page interleaving mode can be selected, allowing the designer to maximize system performance while using low-cost DRAMs.

## **Features**

- SuperAT chip for 10-16 MHz 80286-based PC/AT systems

- Intel® compatible peripherals:

- Two 8237 DMA controllers

- Two 8259 Interrupt controllers

- One 8254 Timer/Counter

- Provides 74LS612 memory mapper

- Software configurable memory organization allows the user to select conventional mode, page mode or twoway page interleaving mode

- Supports 512k to 8 MB motherboard DRAM

- Software configurable wait states

- Shadow RAM support for BIOS, video ROM and video RAM

- Hardware support for LIM EMS 3.2 and 4.0

- Programmable synchronous/asynchronous expansion bus operation

- 8-bit/16-bit BIOS ROM selectable switch

- Supports sleep, suspend, resume modes and slow refresh for DRAM for power savings

- Staggered refresh reduces power supply noise

- Fast GATEA20 and RC optimized for OS/2 operation

- Hardware and software selectable CPU high/low speed

- Low power M<sup>2</sup>CMOS<sup>TM</sup> technology

- 160-pin guad flat package

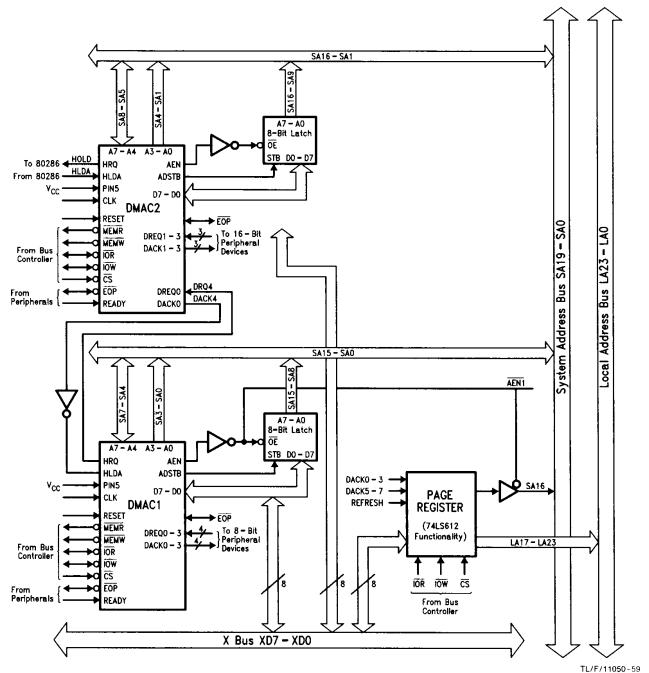

FIGURE 1. Block Diagram of a Typical PC/AT using the PC87120

TRI-STATE® and National® are registered trademarks of National Semiconductor Corporation. SuperAT™ and M²CMOS™ are trademarks of National Semiconductor Corporation. Intel® is a registered trademark of Intel Corporation.

AT™ is a trademark of International Business Machines.

## **Table of Contents**

# 1.0 GENERAL DESCRIPTION

## 2.0 DESCRIPTION

- 2.1 Pin Out Diagram of SuperAT

- 2.2 Alphabetical Pin Description

### 3.0 REGISTER DESCRIPTION

- 3.1 Configuration Registers

- 3.1.1 Configuration Register Access Enable

- 3.1.2 CPU/AT Bus Control Register

- 3.1.3 RAM/ROM Configuration Register #1

- 3.1.4 RAM/ROM Configuration Register #2

- 3.1.5 Shadow RAM Enable Register

- 3.1.6 ROM Area Enable/Shadow RAM Mode Register

- 3.1.7 DRAM Enable Register

- 3.1.8 Refresh Control Register

- 3.1.9 Sleep Mode/DMA Control Register

- 3.1.10 EMS Control Register

- 3.2 DMA Registers

- 3.3 Timer Registers

- 3.4 Initialization Controller Registers

- 3.4.1 Initialization Command Word 1 (ICW1)

- 3.4.2 Initialization Command Word 2 (ICW2)

- 3.4.3 Initialization Command Word 3 (ICW3)

- 3.4.4 Initialization Command Word 4 (ICW4)

- 3.4.5 Operation Command Word 1 (OCW1)

- 3.4.6 Operation Command Word 2 (OCW2)

- 3.4.7 Operation Command Word 3 (OCW3)

- 3.4.8 Interrupt Request Register (IRR)

- 3.4.9 In Service Register (ISR)

- 3.5 EMS Registers

- 3.6 Miscellaneous Registers

- 3.6.1 Port B

- 3.6.2 NMI Enable Flag

- 3.6.3 Programmable Option Select Register #94

- 3.6.4 Programmable Option Select Register #102

## **4.0 RESET AND SHUTDOWN LOGIC**

- 4.1 Power-On Reset

- 4.2 CPU Protected Mode to Real Mode Switch

- 4.3 Coprocessor Protected Mode to Real Mode Switch

- 4.4 CPU Shutdown Logic

## 5.0 CPU/AT BUS OPERATIONS

- 5.1 Clock Generation and Selection

- 5.2 CPU/AT Bus Interface

- 5.3 CPU/AT Bus Modes

- 5.3.1 Non-Turbo Mode

- 5.3.2 Turbo Bus Mode

- 5.3.3 Normal Mode

- 5.3.4 Asynchronous Mode

#### **6.0 MEMORY CONTROL**

- 6.1 Memory Data Bus Interface

- 6.2 Shadow RAM Support

- 6.3 Memory Remapping

- 6.4 Memory Access Modes

- 6.4.1 Conventional Mode

- 6.4.2 Page Interleaving Mode

- 6.4.2.1 Accesses to an Inactive Page and Bank

- 6.4.2.2 Accesses to an Active Page ("Page-Hit")

- 6.4.2.3 Accesses to an Inactive Page in an Active Bank ("Page-Miss")

- 6.4.3 Enhanced Page Interleaving Mode

- 6.4.3.1 Accesses to an Active Page ('Page-Hit'')

- 6.4.3.2 Accesses to an Inactive Page in an Active Bank ("Page-Miss")

- 6.5 EMS Memory Support

- 6.6 Memory Refresh

#### 7.0 PORT B AND NMI LOGIC

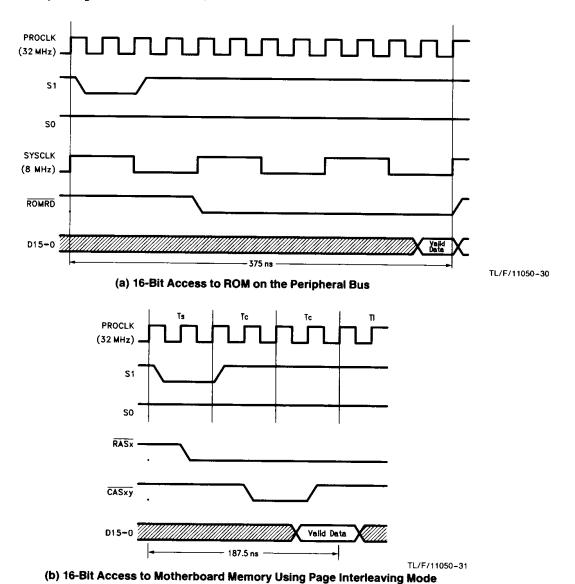

## 8.0 ROM/BIOS CONTROL CIRCUITRY

- 8.1 ROM on the Memory Bus

- 8.2 ROM on the Peripheral Bus

# 9.0 MATH CO-PROCESSOR (80287) INTERFACE 10.0 PERIPHERAL FUNCTIONS

- 10.1 DMA Operation

- 10.1.1 Program Cycle

- 10.1.2 Idle Cycle

- 10.1.3 Active Cycle

- 10.1.3.1 Single Transfer Mode

- 10.1.3.2 Block Transfer Mode

- 10.1.3.3 Demand Transfer Mode

- 10.1.3.4 Cascade Mode

- 10.1.4 Transfer Types

- 10.1.4.1 IO to Memory

- 10.1.4.2 Memory to IO

- 10.1.4.3 Memory to Memory

- 10.1.4.4 Verify

- 10.1.5 Autoinitialize

- 10.1.6 Priority

- 10.1.7 Compressed Timing

- 10.1.8 Address Generation

- 10.1.9 Register Description

- 10.1.9.1 Current Address Register

- 10.1.9.2 Current Word Register

- 10.1.9.3 Base Address Register

- 10.1.9.4 Base Word Count Register

- 10.1.9.5 Command Register

- 10.1.9.6 Mode Register

- 10.1.9.7 Request Register

## Table of Contents (Continued)

10.1.9.8 Mask Register

10.1.9.9 Status Register

10.1.9.10 Temporary Register

10.1.10 Software Commands

10.1.10.1 Clear First/Last Flip-Flop

10.1.10.2 Master Clear

10.1.10.3 Clear Mask Register

10.2 Timer Operation

10.2.1 Programming the Timer

10.2.2 Write Operations

10.2.3 Read Operations

10.2.3.1 Counter Latch Command

10.2.3.2 Read-Back Command

10.2.4 Mode Descriptions

10.2.4.1 Mode 0: Interrupt on Terminal Count

10.2.4.2 Mode 1: Hardware Retriggerable One-Shot

10.2.4.3 Mode 2: Rate Generator

10.2.4.4 Mode 3: Square Wave Mode

10.2.4.5 Mode 4: Software Triggered Strobe

10.2.4.6 Mode 5: Hardware Triggered Strobe

10.2.5 Gate

10.3 Programmable Interrupt Controller Operation

10.3.1 Programming the PIC

10.3.1.1 Initialization Programming

10.3.1.2 Normal Operation Programming

10.3.2 General Operation

10.3.3 Interrupt Sequence

10.3.4 End-of-Interrupt (EOI) Modes

10.3.4.1 Normal EOI Mode

10.3.4.2 Automatic EOI Mode

10.3.5 Priority Nesting

10.3.5.1 Normal Fully Nested Mode

10.3.5.2 Special Fully Nested Mode

10.3.5.3 Special Mask Mode

10.3.6 Priority

10.3.6.1 Fixed Priority

10.3.6.2 Rotating Priority

10.3.7 POLL Command

10.3.8 Reading Status

10.3.9 Edge and Level Triggered Modes

10.4 Peripheral Chip Select

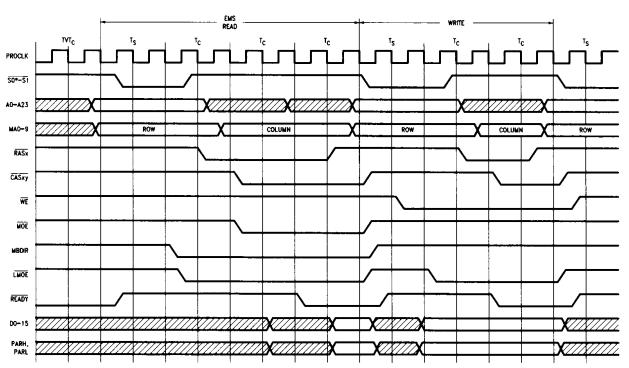

11.0 EMS

12.0 SLEEP, SUSPEND/RESUME MODE

13.0 DEVICE SPECIFICATIONS

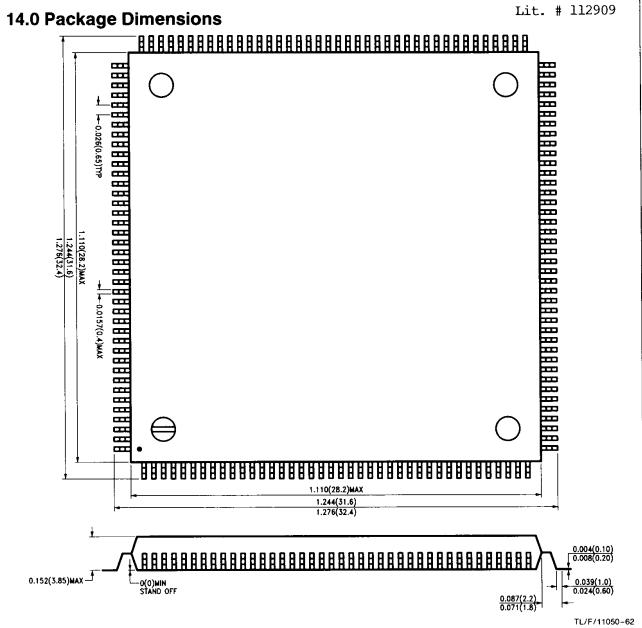

14.0 PACKAGE DIMENSIONS

# **List of Illustrations**

| System Design                                                         | 1 |

|-----------------------------------------------------------------------|---|

| PC87120 Top View                                                      | 1 |

| Remapped Motherboard Memory3-                                         | 1 |

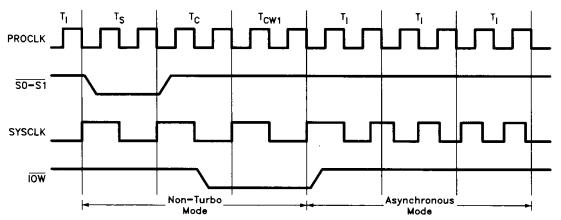

| Non-Turbo Mode to Asynchronous Software Switch                        | 1 |

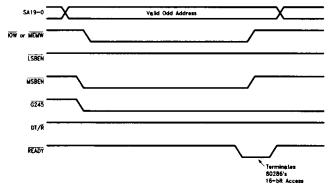

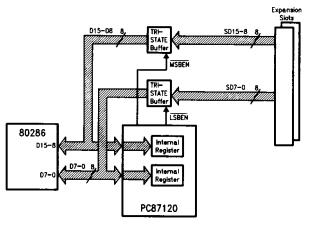

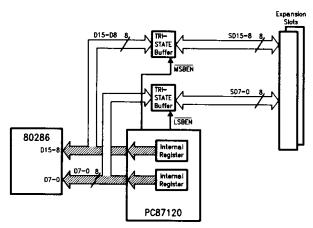

| CPU/AT Bus Interface                                                  | 2 |

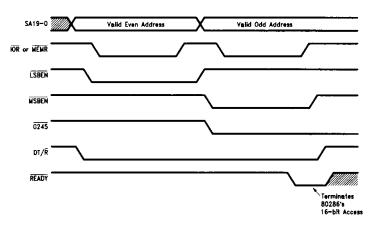

| 16-Bit Read Operation from an 8-Bit Peripheral5-3                     |   |

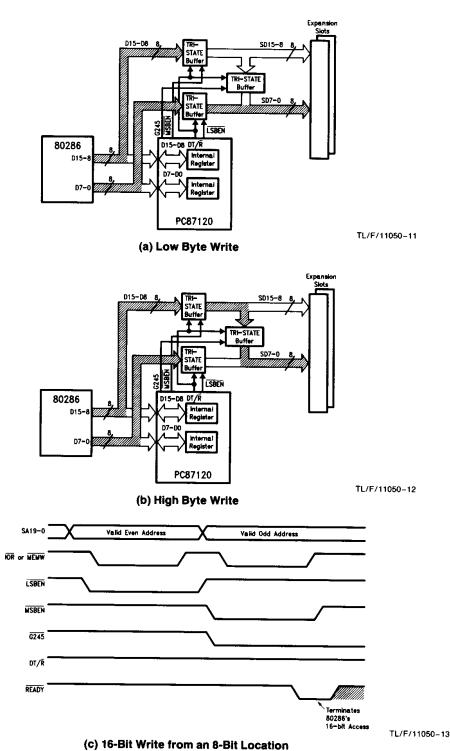

| 16-Bit Write Operation from an 8-Bit Peripheral                       | 4 |

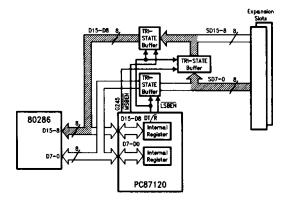

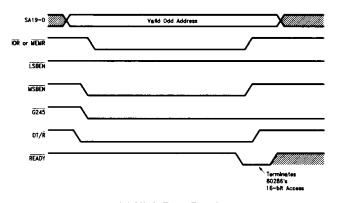

| High Byte Read/Write to and from Expansion Bus5-5                     | 5 |

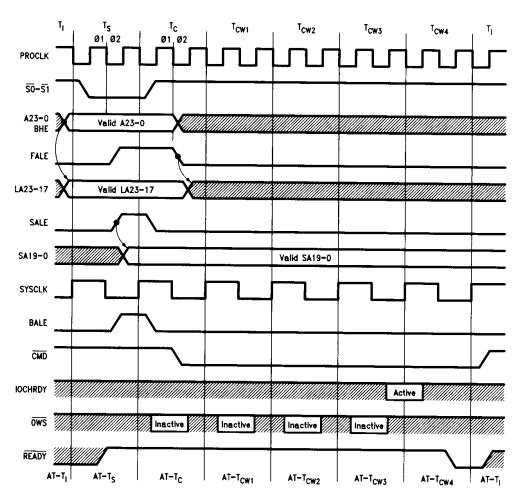

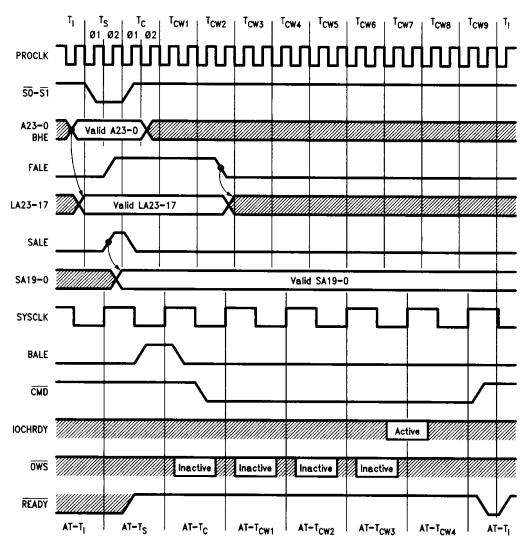

| 8-Bit Access Cycle in Non-Turbo Mode5-6                               | 3 |

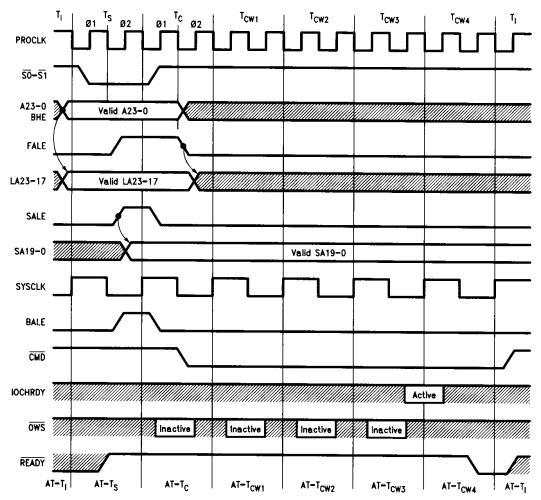

| Access to a 16-Bit Board in Non-Turbo Mode5-7                         | 7 |

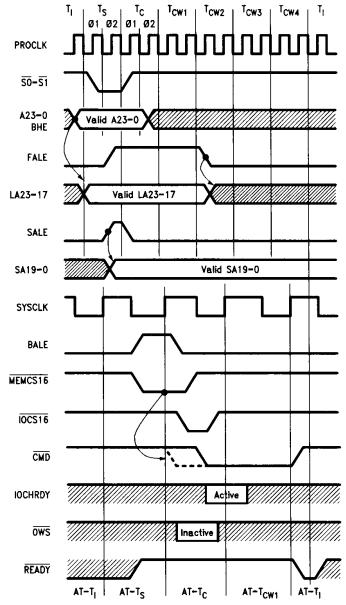

| 8-Bit Access Cycle in Turbo Bus Mode5-8                               | 3 |

| Accesses to a 16-Bit Board in Turbo Bus Mode5-§                       | Э |

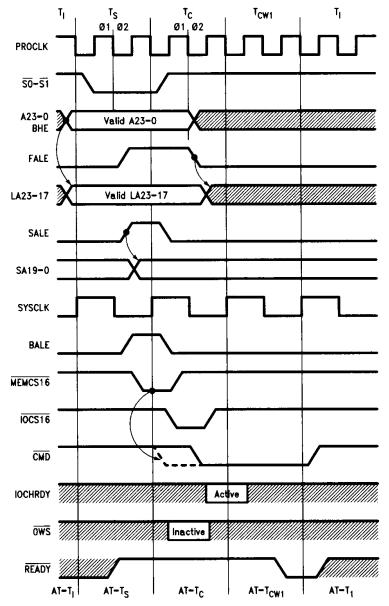

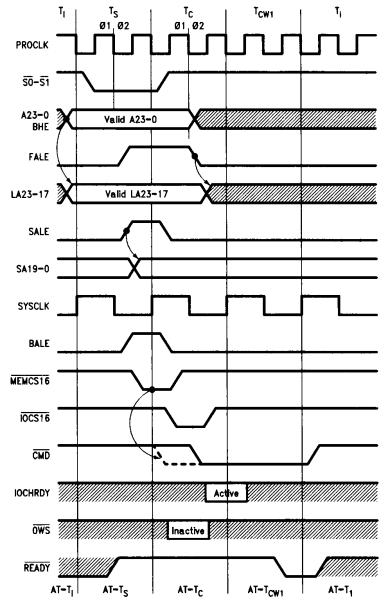

| 8-Bit Access Cycle in Normal Mode5-10                                 |   |

| Access to a 16-Bit Board in Normal Mode5-11                           | 1 |

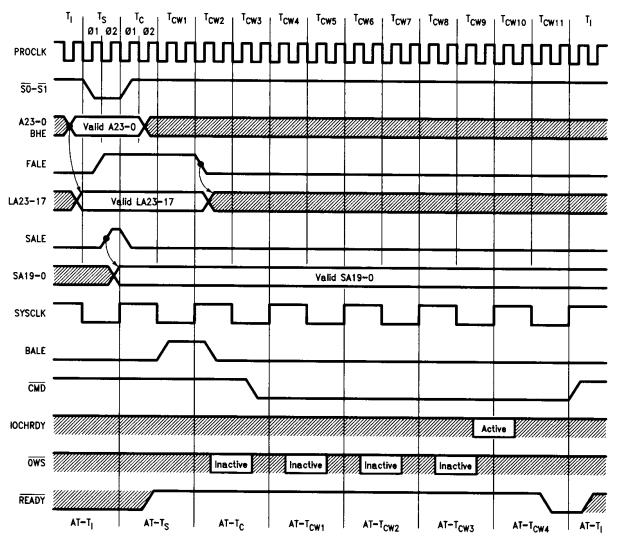

| 8-Bit Access Cycle in Asynchronous Mode5-12                           | 2 |

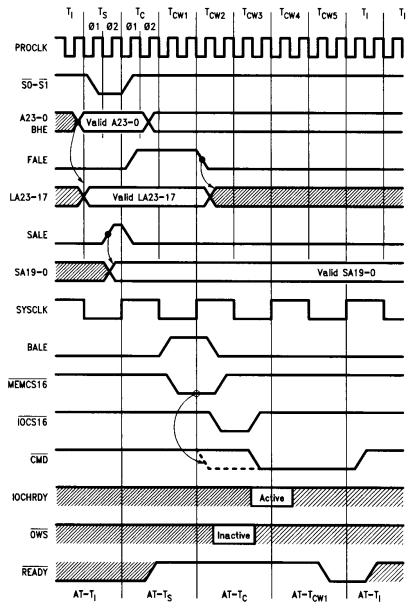

| Access to a 16-Bit Memory Board in Asynchronous Mode5-13              | 3 |

| 16-Bit Read Operation in Asynchronous Mode5-14                        | 4 |

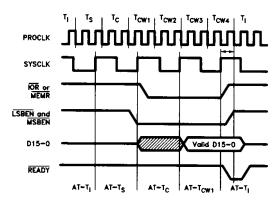

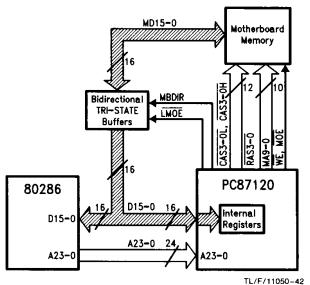

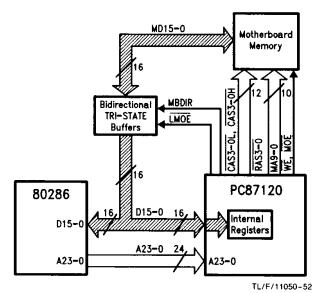

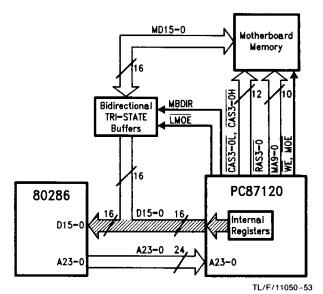

| Typical Memory Data Bus Interface6                                    | 1 |

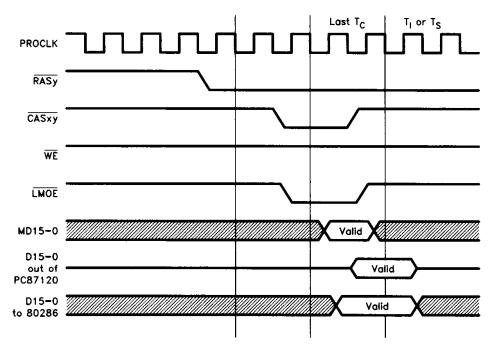

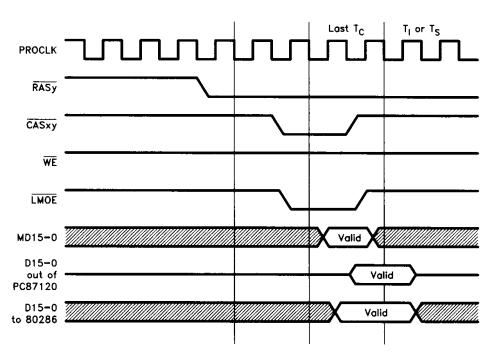

| Access Timing for BIOS6-2                                             | 2 |

| Remapped Motherboard Memory6-3                                        | 3 |

| Conventional Mode 1 Wait State6-2                                     | 4 |

| Conventional Mode 1 Wait State, Extended RAS6-5                       |   |

| Conventional Mode 0 Wait States6-6                                    | 3 |

| Page Interleaving Mode Memory Using 1 MB DRAMs6-7                     |   |

| Page Interleaving Mode Memory Using 256 kB DRAMs6-8                   |   |

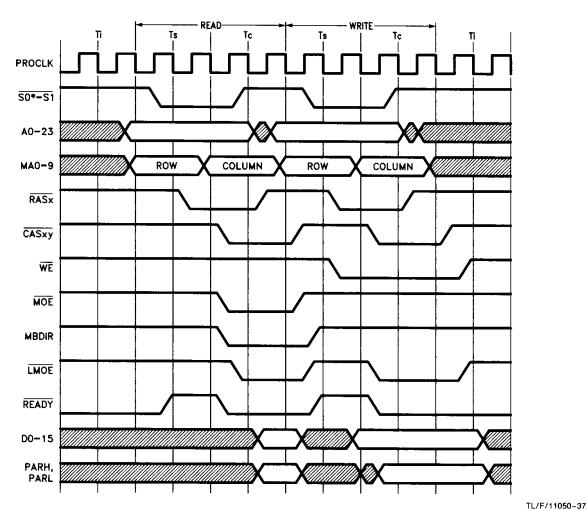

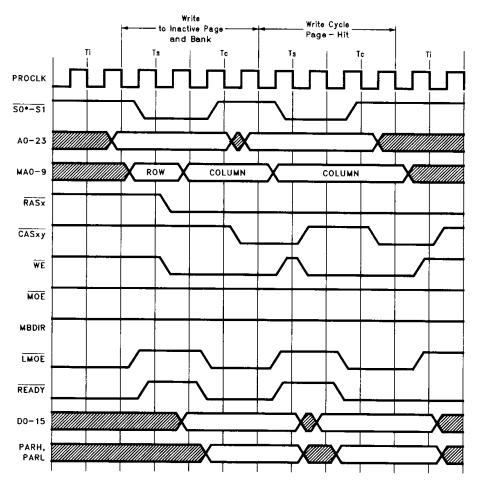

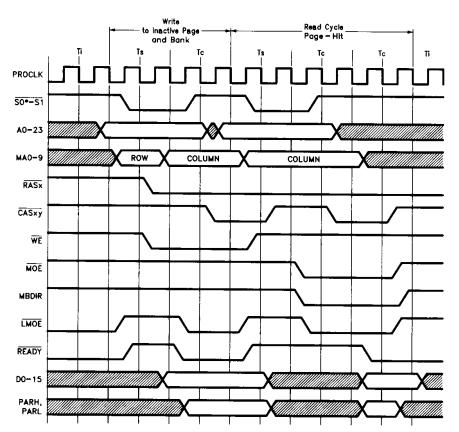

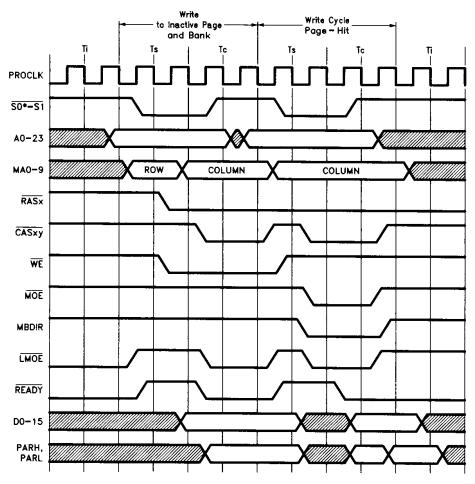

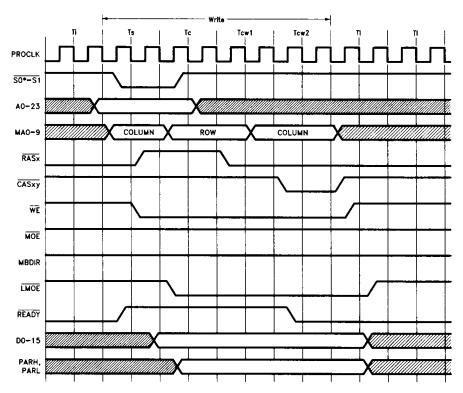

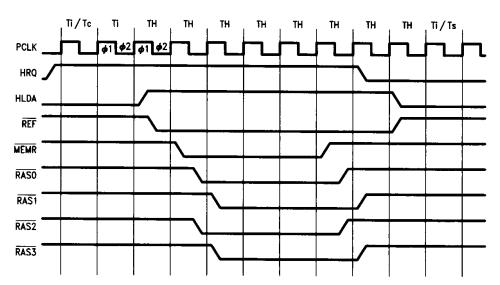

| Write to an Inactive Page and Bank in Page Interleaving Mode6-9       |   |

| Read Cycle to an Inactive Page and Bank in Page Interleaving Mode6-10 |   |

| 16-Bit Page Interleave Read6-11                                       |   |

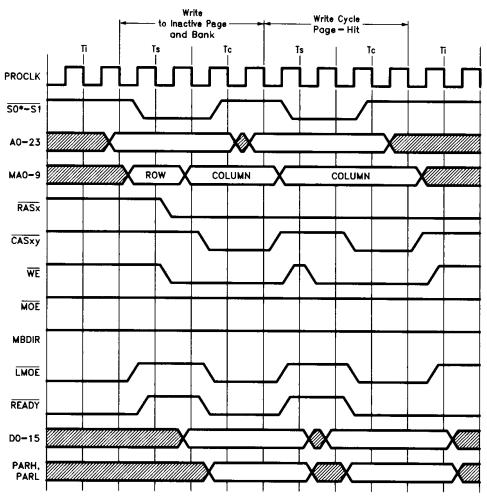

| Write Cycle Page-Hit in Page Interleaving Mode6-12                    | 2 |

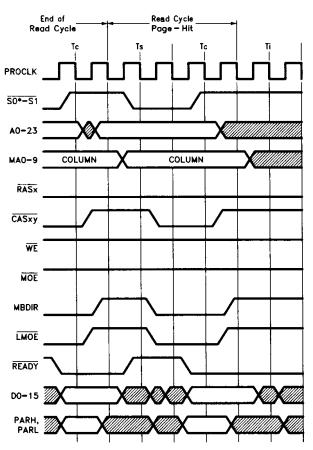

| Read Cycle Page Hit in Page Interleaving Mode6-13                     |   |

| Page Interleaving Read Cycle Page-Hit After Write Cycle               |   |

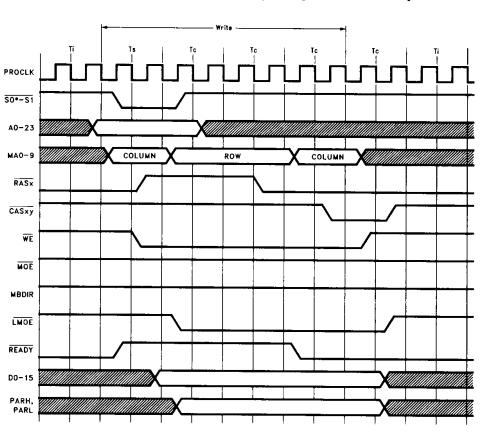

| Page Interleaving Mode Write Cycle Page-Miss6-15                      |   |

| Page Interleaving Mode Read Cycle Page-Miss6-16                       |   |

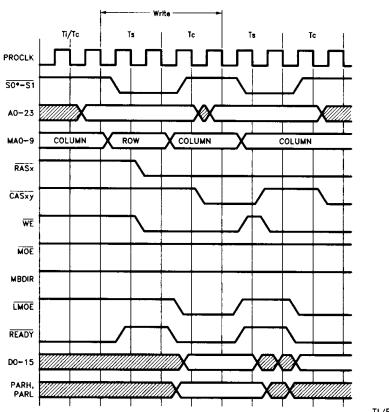

| Enhanced Page Interleave Mode Page-Hit Write Cycle6-17                |   |

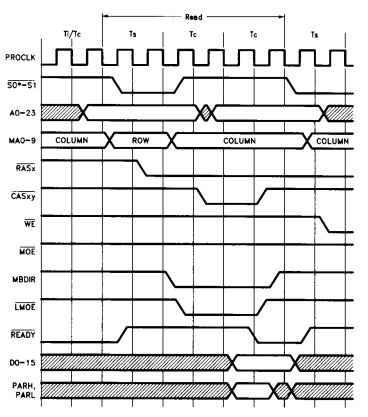

| Enhanced Page Interleaving Mode Page-Hit Read Cycle6-18               |   |

| 16-Bit Enhanced Page Interleave Read6-19                              | 9 |

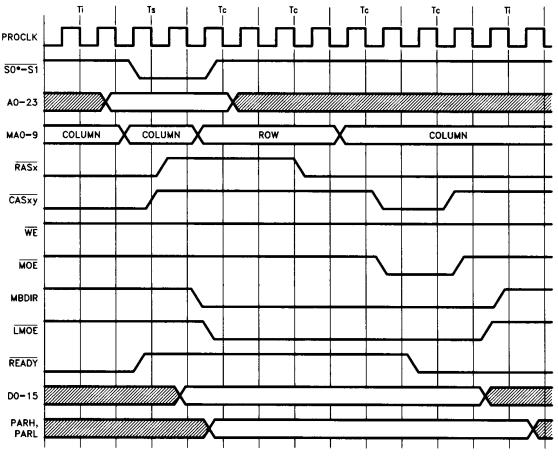

| Enhanced Page-Interleaving Mode Page-Miss Write Cycle6-20             |   |

| Enhanced Page-Interleaving Mode Page-Miss Read Cycle6-21              |   |

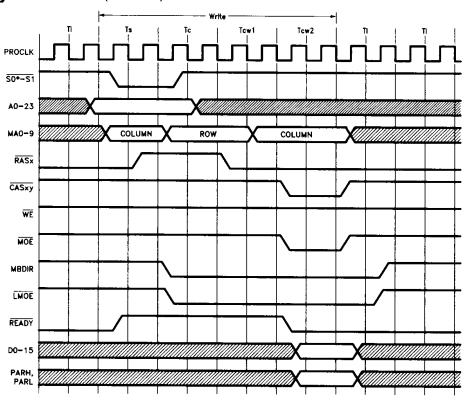

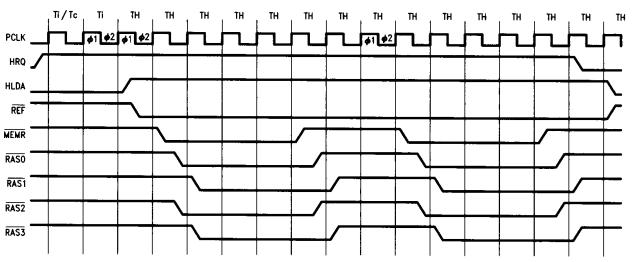

| Staggered Refresh6-22                                                 |   |

| Burst Mode Refresh                                                    |   |

| PC87120 DMA System                                                    | 1 |

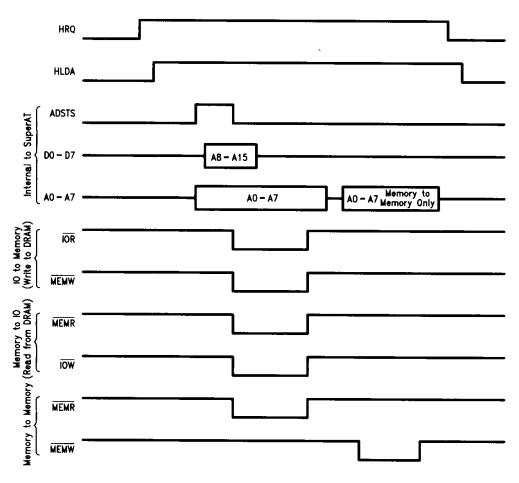

| DMA Transfer Types                                                    |   |

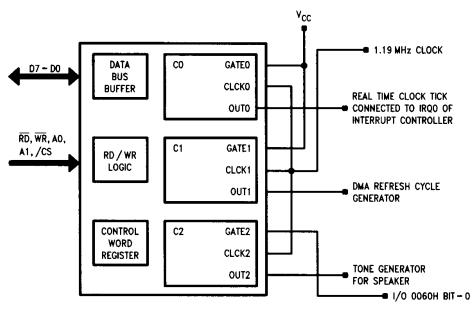

| PC87120 PIT Block Diagram                                             |   |

| Address Locations                                                     |   |

| Control Word (0043H0)                                                 |   |

| Counter Latch Command                                                 |   |

| Read Back Command                                                     |   |

| Status Byte                                                           |   |

| Package Dimensions                                                    |   |

| = 17.17.17.17.17.17.17.17.17.17.17.17.17.1                            | • |

# **List of Tables**

| Pin Description2-1                                                                                  |

|-----------------------------------------------------------------------------------------------------|

| Bus Mode Clocks5-1                                                                                  |

| Bus Mode Configuration Bits5-2                                                                      |

| Motherboard Memory Ranges6-1                                                                        |

| Remapped Memory Ranges6-2                                                                           |

| DRAM Access Requirements for Conventional Mode6-3                                                   |

| Programmable Wait States for Conventional Mode6-4                                                   |

| Penalty Wait States for Page Interleaving Mode6-5                                                   |

| Number of Rows Refreshed During Each Refresh Cycle                                                  |

| Refresh Rate6-7                                                                                     |

| PC87120 DMA System Pins                                                                             |

| DMA Clock and CPU Bus Mode Relationship10-2                                                         |

| PC87120 Channel Priorities when Both DMAC1 and DMAC2 are Programmed for Fixed Priority              |

| Example of Channel Priorities as Various Channels are Serviced when DMAC2 = Rotating, DMAC1 = Fixed |

| Page Register                                                                                       |

| Control Word Commands                                                                               |

| Mode Decode                                                                                         |

| Interrupt Functions                                                                                 |

#### 2.0 Description 2.1 PIN OUT DIAGRAM OF SuperAT SALE TI 120 GND SPEEDSEL 119 PROCLK 118 BUSY286 osc 🖂 OPTBUFFUL TT 117 CPUHLDA IRQ8 116 CPUHRO RTCAS C 115 RES CPU REFRESH \_\_\_\_ RES SYS 2 8 113 NMF 112 READY 111 BHE IOCHRDY 10 IOCHCK \_\_\_\_\_11 110 W/K V<sub>CC</sub> 12 109 51 IOCS16 -----13 108 50 107 A23 MEMCS 16 14 MASTER 15 106 A22 T/C 16 105 TT A21 104 TT A20 0WS 17 PC87120 FALE 18 103 A19 ATCLK 19 102 A18 101 A17 ĬŌR □□□□ 21 CLK2IN 22 160 pin PQFP 99 A15 GND CCC 23 98 A14 MENW 24 97 A13 (top view) MEMR 25 DACK7 CCC 26 95 A11 ĎÁCKÉ 27 94 A10 93 GND DACK5 \_\_\_\_\_28 DACK3 29 92 A9 DACK2 30 91 48 DACKI CITY 31 90 A7 89 A6 DACKO TTT 32 DRQ7 33 DRQ6 - 34 87 A3 DRQ5 \_\_\_\_\_ 35 DRQ3 - 36 85 42 DRQ2 37 84 111 A1 DRQ1 38 83 A0 82 SPINO DRQ0 - 39 LMEGCS LL 81 SPKR

FIGURE 2. PC87120 Top View

# 2.0 Description

# PIN DESCRIPTION

| PIN DESCRIPTION |                 |  |  |  |

|-----------------|-----------------|--|--|--|

| Pin #           | Description     |  |  |  |

| 1               | SALE            |  |  |  |

| 2               | SPEEDSEL        |  |  |  |

| 3               | osc             |  |  |  |

| 4               | OPTBUFFUL       |  |  |  |

| 5               | IRQ8            |  |  |  |

| 6               | RTCAS           |  |  |  |

| 7               | REFRESH         |  |  |  |

| 8               | RES SYS         |  |  |  |

| 9               | SYSCLK          |  |  |  |

| 10              | IOCHRDY         |  |  |  |

| 11              | IOCHCK          |  |  |  |

| 12              | V <sub>CC</sub> |  |  |  |

| 13              | IOCS16          |  |  |  |

| 14              | MEMCS16         |  |  |  |

| 15              | MASTER          |  |  |  |

| 16              | T/C             |  |  |  |

| 17              | ows             |  |  |  |

| 18              | FALE            |  |  |  |

| 19              | ATCLK           |  |  |  |

| 20              | iow             |  |  |  |

| 21              | ior .           |  |  |  |

| 22              | CLK2IN          |  |  |  |

| 23              | GND             |  |  |  |

| 24              | MEMW            |  |  |  |

| 25              | MEMR            |  |  |  |

| 26              | DACK7           |  |  |  |

| 27              | DACK6           |  |  |  |

| 28              | DACK5           |  |  |  |

| 29              | DACK3           |  |  |  |

| 30              | DACK2           |  |  |  |

| 31              | DACK1           |  |  |  |

| 32              | DACK0           |  |  |  |

| 33              | DRQ7            |  |  |  |

| 34              | DRQ6            |  |  |  |

| 35              | DRQ5            |  |  |  |

| 36              | DRQ3            |  |  |  |

| 37              | DRQ2            |  |  |  |

| 38              | DRQ1            |  |  |  |

| 39              | DRQ0            |  |  |  |

| 40              | LMEGCS          |  |  |  |

|                 |                 |  |  |  |

| Pin # | Description     |

|-------|-----------------|

| 41    | PW GOOD         |

| 42    | RESET287        |

| 43    | NPCS            |

| 44    | BUSY            |

| 45    | ERROR           |

| 46    | MA0             |

| 47    | MA1             |

| 48    | MA2             |

| 49    | MA3             |

| 50    | MA4             |

| 51    | V <sub>CC</sub> |

| 52    | GND             |

| 53    | MA5             |

| 54    | MA6             |

| 55    | MA7             |

| 56    | MA8             |

| 57    | MA9             |

| 58    | GND             |

| 59    | PARH            |

| 60    | PARL            |

| 61    | RAS0            |

| 62    | RAS1            |

| 63    | RAS2            |

| 64    | RAS3            |

| 65    | ROMRD           |

| 66    | CASOL           |

| 67    | CASOH           |

| 68    | GND             |

| 69    | CAS1L           |

| 70    | CAS1H           |

| 71    | CAS2L           |

| 72    | CAS2H           |

| 73    | CAS3L           |

| 74    | CAS3H           |

| 75    | GND             |

| 76    | Vcc             |

| 77    | WE              |

| 78    | MOE             |

| 79    | LMOE            |

| 80    | MBDIR           |

|       |                 |

| Pin # | Description |

|-------|-------------|

| 81    | SPKR        |

| 82    | SPIND       |

| 83    | A0          |

| 84    | A1          |

| 85    | A2          |

| 86    | А3          |

| 87    | A4          |

| 88    | <b>A</b> 5  |

| 89    | A6          |

| 90    | <b>A</b> 7  |

| 91    | A8          |

| 92    | A9          |

| 93    | GND         |

| 94    | A10         |

| 95    | A11         |

| 96    | A12         |

| 97    | A13         |

| 98    | A14         |

| 99    | A15         |

| 100   | A16         |

| 101   | A17         |

| 102   | A18         |

| 103   | A19         |

| 104   | A20         |

| 105   | A21         |

| 106   | A22         |

| 107   | A23         |

| 108   | So          |

| 109   | <u>S1</u>   |

| 110   | M/IO        |

| 111   | BHE         |

| 112   | READY       |

| 113   | NMI         |

| 114   | INTR        |

| 115   | RES CPU     |

| 116   | CPUHRQ      |

| 117   | CPUHLDA     |

| 118   | BUSY286     |

| 119   | PROCLK      |

| 120   | GND         |

|       |             |

| Pin # | Description     |

|-------|-----------------|

| 121   | <u>G245</u>     |

| 122   | DT/₹            |

| 123   | LSBEN           |

| 124   | MSBEN           |

| 125   | POE             |

| 126   | PP1CS           |

| 127   | IRQ15           |

| 128   | IRQ14           |

| 129   | GND             |

| 130   | IRQ12           |

| 131   | IRQ11           |

| 132   | IRQ10           |

| 133   | IRQ9            |

| 134   | IRQ7            |

| 135   | IRQ16           |

| 136   | V <sub>CC</sub> |

| 137   | IRQ5            |

| 138   | IRQ4            |

| 139   | IRQ3            |

| 140   | SA0             |

| 141   | GA20            |

| 142   | BALE            |

| 143   | D15             |

| 144   | D14             |

| 145   | D13             |

| 146   | D12             |

| 147   | D11             |

| 148   | D10             |

| 149   | D9              |

| 150   | D8              |

| 151   | D7              |

| 152   | D6              |

| 153   | D5              |

| 154   | GND             |

| 155   | D4              |

| 156   | D3              |

| 157   | D2              |

| 158   | D1              |

| 159   | D0              |

| 160   | GATEA20         |

## 2.2 ALPHABETICAL PIN DESCRIPTION

**TABLE 2-1. Pin Description**

| Symbol               | Pin<br>Number      | Туре | Description                                                                                                                                                                                                                                                                          |  |

|----------------------|--------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A0-A9<br>A10-A23     | 83-92<br>94-107    | 1/0  | Address Bus—These bidirectional address signals are inputs during CPU and BUS MASTER cycles; outputs during REFRESH and DMA cycles.                                                                                                                                                  |  |

| ATCLK                | 19                 | _    | AT Bus CLocK—This oscillator input is used for AT bus operation. It provides an independent clock from CPU clock and is only required when the AT bus state machine is not derived from CLK2IN.                                                                                      |  |

| BALE                 | 142                | 0    | Buffered Address Latch Enable—This active High signal latches valid addresses and memory decodes. It is forced High during DMA cycles.                                                                                                                                               |  |

| BHE                  | 111                | 1/0  | Bus High Enable—This active Low signal indicates transfer of data on the upper byte of the local data bus (D8-D15).                                                                                                                                                                  |  |

| BUSY                 | 44                 | _    | Processor Extension <b>BUSY</b> —This active Low signal asserted by the 80287 indicates that it is currently executing a command.                                                                                                                                                    |  |

| BUSY286              | 118                | 0    | <b>BUSY 286</b> —This active Low signal for the CPU indicates that the 80287 numeric processor is in operating mode.                                                                                                                                                                 |  |

| CAS0H<br>CAS3H       | 67, 70<br>72, 74   | 0    | Column Address Strobe (High Byte)—These active Low signals instruct the high byte of DRAM to latch the column address present on the MA0-MA9 pins.                                                                                                                                   |  |

| CASOL<br>CASOL       | 66, 69<br>71, 73   | 0    | Column Address Strobe (Low Byte)—These active Low signals instruct the low byte of DRAM to latch the column address present on the MA0~MA9 pins.                                                                                                                                     |  |

| CLK2IN               | 22                 | l    | CLocK2 INput—This oscillator input provides the fundamental timing for the system. The processor clock is always generated from this input signal and system clock may be derived from this signal.                                                                                  |  |

| CPUHLDA              | 117                | 1    | CPU HoLD Acknowledge—This active High signal from the CPU indicates that the CPU is relinquishing control of the system.                                                                                                                                                             |  |

| CPUHRQ               | 116                | 0    | CPU Hold ReQuest—Active High to CPU to gain control for DMA and Refresh operation.                                                                                                                                                                                                   |  |

| D15-0                | 143–153<br>155–159 | 1/0  | Data Bus—This bidirectional data bus provides a data path to and from the CPU.                                                                                                                                                                                                       |  |

| DACK 7-5<br>DACK 3-0 | 26-28<br>29-32     | 0    | DMA ACKnowledge—These active Low signals acknowledge DMA requests (DRQ7-5, DRQ3-0).                                                                                                                                                                                                  |  |

| DRQ7-5<br>DRQ3-0     | 33–35<br>36–39     | 1    | DMA ReQuest—These active High asynchronous signals request DMA services or control of the system. DRQ3-0 are for 8-bit DMA transfers, DRQ7-5 for 16-bi DMA transfers.                                                                                                                |  |

| DT/R                 | 122                | 0    | Data Transmit/Receive—When this signal is High, it indicates data flow from CPU to SD bus. When it is Low, it indicates data flow in the opposite direction. It also controls the direction of data swapping between high byte (SD8-15) and low byte (SD0-7) on the system data bus. |  |

| ERROR                | 45                 | I    | Processor Extension <b>ERROR</b> —This active Low signal asserted by the 80287, indicates that an unmasked error condition exists.                                                                                                                                                   |  |

| FALE                 | 18                 | 0    | Fast Address Latch Enable—This signal is an output to latch address A17-A23 to LA17-LA23.                                                                                                                                                                                            |  |

| G245                 | 121                | 0    | Gate 245—This active Low signal enables data transfer between high byte (SD8-15) and low byte (SD0-7) on the system data bus.                                                                                                                                                        |  |

| GA20                 | 141                | 1/0  | Gated Address 20—This signal is an output to generate LA20 as the address for the AT bus during CPU or DMA cycles. It is an input from LA20 during Master cycles.                                                                                                                    |  |

TABLE 2-1. Pin Description (Continued)

| Symbol                                  | Pin<br>Number                             | Туре | Description                                                                                                                                                                                                                                                    |

|-----------------------------------------|-------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GATEA20                                 | 160                                       | l    | GATE A20—This signal is an active Low input from the keyboard controller output port forcing A20 to be low during a CPU shutdown from protected mode.                                                                                                          |

| GND                                     | 23, 52, 58<br>68, 75, 93<br>120, 129, 154 | l    | Ground.                                                                                                                                                                                                                                                        |

| INTR                                    | 114                                       | 0    | INTerrupt Request—This active High signal requests the CPU to suspend its current program execution and service a pending external request. Interrupt requests are maskable.                                                                                   |

| IOCHCK                                  | 11                                        | -    | I/O CHannel CheCK—This active Low signal indicates an error condition from an I/O device. The error condition will interrupt the CPU when enabled through the NMI output.                                                                                      |

| IOCHRDY                                 | 10                                        | -    | I/O CHannel ReaDY—A Low on this input from an I/O or memory device lengthens the I/O or memory cycle by an integer number of clock cycles.                                                                                                                     |

| IOCS16                                  | 13                                        | 1/0  | I/O 16-bit Chip Select—This active Low signal indicates that the current data<br>transfer is a 16-bit IO cycle. This signal should be driven with an open collector of<br>TRI-STATE driver.                                                                    |

| ĪŌR                                     | 21                                        | 1/0  | I/O Read Command—This active Low signal instructs an I/O device to place the data onto the data bus.                                                                                                                                                           |

| ĪŌW                                     | 20                                        | 1/0  | I/O Write Command—This active Low signal instructs an I/O device to read the data on the data bus.                                                                                                                                                             |

| IRQ5-3<br>IRQ7-6<br>IRQ12-9<br>IRQ15-14 | 137-139<br>134-135<br>130-133<br>127-128  | 1    | Interrupt ReQuests—Edge triggered or level triggered input signals which request interrupt services. It should be held high until it's acknowledged.                                                                                                           |

| IRQ8                                    | 5                                         | I    | Interrupt ReQuest 8—Interrupt request from real time clock.                                                                                                                                                                                                    |

| LMEGCS                                  | 40                                        | 0    | Low MEG Chip Select—Active Low indicates Low Meg memory address space i accessed. This signal is forced Low during refresh cycles. Also, it is used to disable SMEMR and SMEMW signals on the AT bus if accesses are made beyond the 1 Meg Byte address space. |

| <u>LMOE</u>                             | 79                                        | 0    | Local Memory Output Enable—Active Low signal to enable data transfer between memory bus and local bus.                                                                                                                                                         |

| LSBEN                                   | 123                                       | 0    | Least Significant Byte ENable—This active Low signal enables low byte data transfer between local and system buses.                                                                                                                                            |

| MA0-MA9                                 | 46-50<br>53-57                            | 0    | Multiplexed Address—These are the multiplexed addresses for motherboard DRAM accesses. MA9 is for 1 MB DRAMs only.                                                                                                                                             |

| MASTER                                  | 15                                        | l    | MASTER—This active Low signal is used with DRQ and DACK signals to gain control of the system. Upon receiving DACK, an I/O processor can pull this signal low to gain control of the system buses.                                                             |

| MBDIR                                   | 80                                        | 0    | MD/D Bus DIRection—When High, data flows from D to MD buses; When Low, data flows from MD to D buses.                                                                                                                                                          |

| MEMCS16                                 | 14                                        | 1    | MEMory 16-bit Chip Select—This active Low signal indicates that the current data transfer is a 16-bit memory cycle. This signal should be driven with open collector or tri-state driver.                                                                      |

| MEMR                                    | 25                                        | 1/0  | MEMory Read Command—This active Low signal instructs a memory device to place the data onto the data bus.                                                                                                                                                      |

| MEMW                                    | 24                                        | 1/0  | MEMory Write Command—This active Low signal instructs a memory device to read the data on the data bus.                                                                                                                                                        |

TABLE 2-1. Pin Description (Continued)

| Symbol          | Pin<br>Number | Туре | Description                                                                                                                                                                                                                                                                        |

|-----------------|---------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M/ĪŌ            | 110           | 1    | Memory/IO—This signal from the CPU indicates a memory cycle when High and an IO cycle when low.                                                                                                                                                                                    |

| MOE             | 78            | 0    | Memory Output Enable—This active Low signal should be connected to the DRAM output enable pin to enable data output.                                                                                                                                                               |

| MSBEN           | 124           | 0    | Most Significant Byte ENable—This active Low signal enables high byte data transfer between local and system data buses.                                                                                                                                                           |

| NMI             | 113           | 0    | Non-Maskable Interrupt Request—This active High signal forces the CPU to execute the non-maskable interrupt routine under any condition.                                                                                                                                           |

| NPCS            | 43            | 0    | Numeric Processor Chip Select—This active Low signal drives the NPCS Pin of the 80287 and indicates that the CPU is performing an ESCAPE instruction.                                                                                                                              |

| OUTBUFFUL       | 4             | l    | OUTput BUFfer FULL—This signal from the keyboard controller generates an interrupt to the CPU when the keyboard buffer is full.                                                                                                                                                    |

| osc             | 3             | ı    | OSCillator Input—14.318 MHz clock input to generate 1.19 MHz clock for Timer 8254.                                                                                                                                                                                                 |

| PARH            | 59            | 1/0  | PARity High Byte—For the high byte of memory (D8-D15), this signal is used to generate the parity check during read cycles (input) and generates the parity bit for write cycles (output).                                                                                         |

| PARL            | 60            | 1/0  | PARity Low Byte—For the lower byte of memory (D0-D7), this signal is used to generate the parity check during read cycles (input) and generates the parity bit for write cycles (output).                                                                                          |

| POE             | 125           | 0    | Print POrt Enable—This active Low signal enables printer output port.                                                                                                                                                                                                              |

| PPICS           | 126           | 0    | PeriPheral Chip Select—This active Low signal selects I/O devices address from 60H to 7FH.                                                                                                                                                                                         |

| PROCLK          | 119           | 0    | PROcessor CLocK—This signal is an output to the clock input of the CPU.                                                                                                                                                                                                            |

| PW GOOD         | 41            | 1    | PoWer GOODA Low input to this pin will reset the system.                                                                                                                                                                                                                           |

| RAS0-3          | 61-64         | 0    | Row Address Strobe—These active Low signals instruct the DRAM to latch the row addresses present on the MA0-MA9 pins. Four RAS lines can support up to 4-bank memory configuration. A staggered refresh cycle will be performed to reduce power supply noise during RAS switching. |

| READY           | 112           | 0    | <b>READY</b> —This active Low signal to the CPU indicates that the current bus cycle has completed.                                                                                                                                                                                |

| REFRESH         | 7             | 1/0  | REFRESH—This active Low signal indicates a refresh cycle and can be driven by a microprocessor on the I/O channel during master cycles.                                                                                                                                            |

| RES CPU         | 115           | 0    | RESet CPU—This active High signal resets the CPU during power up, protected mode to real mode switch, and a shutdown cycle.                                                                                                                                                        |

| RES SYS         | 8             | 0    | RESet SYStem Driver—This active High signal resets or initializes system logic during power-up or during a low line voltage outage.                                                                                                                                                |

| RESET287        | 42            | 0    | RESET 80287—This active High signal resets the 80287 coprocessor.                                                                                                                                                                                                                  |

| ROMRD           | 65            | 0    | ROM Chip ReaD—This signal accesses data in the ROM and also supports shadow RAM. Once the ROM contents are copied into DRAM space after system initialization, ROMRD output is disabled and ROM addresses are mapped into DRAM physical address space.                             |

| RTCAS           | 6             | 0    | Real Time Clock Address Strobe—Active Low signal to latch RAM address into RTC for Read/Write operation.                                                                                                                                                                           |

| <u>50</u><br>51 | 108-109       | 1    | Bus Cycle Status—These input signals from the CPU define the state and type of the CPU cycle.                                                                                                                                                                                      |

## TABLE 2-1. Pin Description (Continued)

| Symbol          | Pin<br>Number   | Туре | Description                                                                                                                                                                                                        |  |

|-----------------|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SA0             | 140             | 1/0  | System Address—I/O slot address bit 0. Normally an output, this signal becomes an input during Master cycles.                                                                                                      |  |

| SALE            | 1               | 0    | System Address Latch Enable—Output to latch addresses from local address bus to system address bus to support system addresses.                                                                                    |  |

| SPEEDSEL        | 2               | I    | SPEED SELect—Hardware input switch, toggles to change CPU speed.                                                                                                                                                   |  |

| SPIND           | 82              | 0    | SPeed INDicator—When High, it indicates that the machine is running at high speed. When Low, it indicates that the machine is running at low speed.                                                                |  |

| SPKR            | 81              | 0    | SPeaKeR Output—Output drives the speaker input.                                                                                                                                                                    |  |

| SYSCLK          | 9               | 0    | SYStem CLocK—This signal is buffered to drive the system clock on the AT bu I/O channel. It may be programmed to be synchronous or asynchronous with the CPU clock (PROCLK).                                       |  |

| T/C             | 16              | 0    | Terminal Count—A pulse is active High when the terminal count for any DMA channel is reached.                                                                                                                      |  |

| V <sub>CC</sub> | 12, 51, 76, 136 | ı    | Power: +5V Supply.                                                                                                                                                                                                 |  |

| WE              | 77              | 0    | Write Enable—This output drives the DRAM to enable a write operation. It will tied to all motherboard DRAM.                                                                                                        |  |

| <u>ows</u>      | 17              | I    | Zero Wait States—This active Low signal from AT bus causes the CPU to complete the current bus cycle without inserting additional wait states. This signal should be driven by open collector or tri-state driver. |  |

# 3.0 Register Description

The PC87120 registers, each one byte wide, are divided into six groups as shown below. Several of the registers are divided into fields and individual bits which control entirely different functions.

| Group Name                     | Number of Registers |

|--------------------------------|---------------------|

| Configuration Registers        | 10                  |

| DMA Registers                  |                     |

| Timer Registers                |                     |

| Interrupt Controller Registers | 9                   |

| EMS Registers                  |                     |

| Miscellaneous Registers        | 4                   |

All of the registers are accessed through the IO port address space.

Following a system reset every register will be set to a default value. Some of the register bits are reserved and have a set value, which is hardwired. These hardwired reserved bits are tied low and will always be read as a 0, even if one attempts to write a 1 to these reserved bits. (These hardwired bits will be shown as **RESERVED:0**, indicating that it will always be read as a 0.) On the other hand, there are some reserved bits which do not control any functions, but are not hardwired. These reserved bits may be read as 0 or 1 and will be shown as **RESERVED**, without any value following.

#### 3.1 CONFIGURATION REGISTERS

The registers in this section are used to configure the PC87120's bus controller, clock generator and memory controller. These configuration registers are mapped into the IO address range FC80h-FC89h.

# 3.1.1 Configuration Register Access Enable (IO address FC87h)

(Default = Access Enable Flag is cleared)

In order to write or read from any of the configuration registers (located at IO addresses FC80h–FC86h and FC88h–FC89h), an access to this register (located at address FC87h) must immediately proceed it. When this register is read or written a configuration access enable flag is set in the PC87120. This flag will be cleared on the very next access to any location in the system including any access to the IO address range FC80h–FC89h. If the configuration access enable flag is not set and an access tries to read or write any of the PC87120's configuration registers, the access will be denied. In this way, accidental writes to any of the configuration registers will be ignored, preventing the configuration registers from accidental corruption.

## 3.1.2 CPU/AT Bus Control Register

(8-Bit, Read/Write-FC80)

(Default = 00110010)

### Bit 7-Reserved:0

## Bits 6-5-8-Bit AT Cycle Wait States

These two bits determine the number of programmed wait states which will be inserted into each 8-bit access to the AT expansion bus or the peripheral bus.

| Bit 6 | Bit 5 | Wait States       |

|-------|-------|-------------------|

| 0     | 0     | 5 Waits           |

| 0     | 1     | 4 Waits (default) |

| 1     | 0     | 3 Waits           |

| 1     | 1     | 2 Waits           |

### Bits 4-3—16-Bit AT Cycle Wait States

These two bits determine the number of programmed wait states which will be inserted into each 16-bit access to the AT expansion bus or the peripheral bus.

| Bit 4 | Bit 3 | Wait States      |

|-------|-------|------------------|

| 0     | 0     | 3 Waits          |

| 0     | 1     | 2 Waits          |

| 1     | 0     | 1 Wait (default) |

| 1     | 1     | 0 Waits          |

## Bits 2-0—Processor/System CLK Source Select

These three bits determine both the clocks' source(s) and their relative Frequencies. Glitch preventing logic is used to guarantee a smooth transition between various clock frequencies when new values are written to these bits.

| Bit 2 | Bit 1 | Bit 0 | PROCLK   | SYSCLK    |

|-------|-------|-------|----------|-----------|

| 0     | х     | Х     | CLK2IN/2 | CLK2IN/4  |

|       |       |       |          | (default) |

| 1     | 0     | 1     | CLK2IN   | CLK2IN/2  |

| 1     | 1     | 0     | CLK2IN   | CLK2IN/4  |

| 1     | 1     | 1     | CLK2IN   | ATCLK/2   |

## 3.1.3 RAM/ROM Configuration Register #1

(8-Bit, Read/Write—FC81)

(Default = 00000000)

### Bit 7—Page Interleave Mode Enable

This bit controls the access mode for motherboard memory.

- 0 = Enable conventional mode (Disable page interleaving mode, this is the default)

- 1 = Enable page interleaving mode

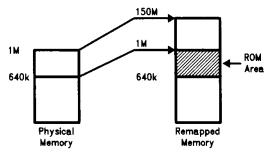

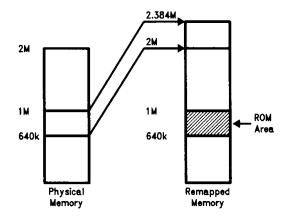

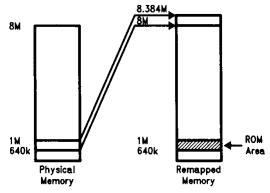

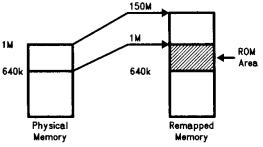

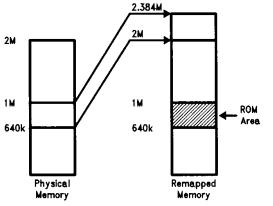

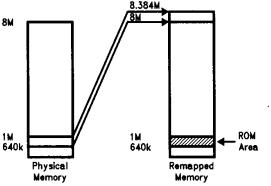

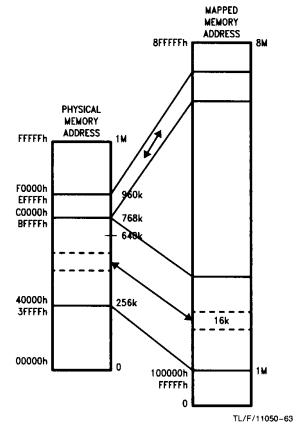

## Bit 6-640 kB to 1 MB RAM Relocation

This bit, when set to 1, remaps the memory which coincides with the ROM BIOS area (640 kB to 1 MB), to the top of the supported motherboard memory range. With 1 MB of DRAM, memory will reside from 0 to 640 kB and from 1 MB to 1.384 MB. The ROM BIOS will remain in the 640 kB to 1 MB range.

No remapping takes place when this bit equals 0. This bit must be set equal to 0 if less than 1 MB of DRAM is supported or if BIOS shadow RAM is being used.

- 0 = No remapping (mandatory for memory configurations 1 & 8)

- 1 = Relocate RAM area 640 kB-1 MB

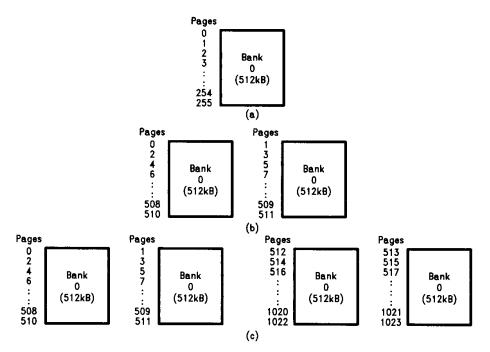

Figures 3-1a, 3-1b and 3-1c show how the motherboard memory between 640 kB and 1 MB range are remapped when 1, 2, and 8 MB of motherboard memory are configured.

(a) 1 MB of Motherboard Memory

TL/F/11050-3

TL/F/11050-4

(b) 2 MB of Motherboard Memory

FIGURE 3-1. Remapped Motherboard Memory

## Bits 5-3—DRAM Configuration

These three bits provide eight common configurations for the DRAM.

| Bit 5 | Bit 4 | Bit 3 | Configuration<br>Type | Memory<br>Configuration |

|-------|-------|-------|-----------------------|-------------------------|

| 0     | 0     | 0     | 1                     | 1-Bank 512 kB           |

| 0     | 0     | 1     | 2                     | 1-Bank 2 MB             |

| 0     | 1     | 0     | 3                     | 2-Bank 1 MB             |

| 0     | 1     | 1     | 4                     | 2-Bank 4 MB             |

| 1     | 0     | 0     | 5                     | 4-Bank 2 MB             |

| 1     | 0     | 1     | 6                     | 4-Bank 5 MB             |

| 1     | 1     | 0     | 7                     | 4-Bank 8 MB             |

| 1     | 1     | 1     | 8                     | 2-Bank 640 MB           |

| Configuration | DRAM Type |        |        |        |

|---------------|-----------|--------|--------|--------|

| Туре          | Bank 0    | Bank 1 | Bank 2 | Bank 3 |

| 1             | 256 kB    |        | _      | _      |

| 2             | 1 MB      | _      |        | _      |

| 3             | 256 kB    | 256 kB | _      | _      |

| 4             | 1 MB      | 1 MB   |        | _      |

| 5             | 256 kB    | 256 kB | 256 kB | 256 kB |

| 6             | 1 MB      | 1 MB   | 256 kB | 256 kB |

| 7             | 1 MB      | 1 MB   | 1 MB   | 1 MB   |

| 8             | 256 kB    | 64 kB  |        | _      |

### Bit 2—DRAM Wait States

One programmed wait state is added to every conventional mode motherboard memory access when this bit is set equal to zero. No programmed wait states are added when this bit is set equal to 1.

- 0 = 1 Programmed Wait State (default)

- 1 = No Programmed Wait States

## Bits 1-0—ROM Wait States

These two bits determine the number of wait states used to access the ROM BIOS. If shadow RAM is used for the BIOS, the number of programmed RAM wait states (determined by bit 2 of this register) will be used for every access to BIOS in the shadow RAM.

| Bit 1 | Bit 0 | Wait States |

|-------|-------|-------------|

| 0     | 0     | 3 Waits     |

| 0     | 1     | 2 Waits     |

| 1     | 0     | 1 Wait      |

| 1     | 1     | 0 Waits     |

## 3.1.4 RAM/ROM Configuration Register #2

(8-Bit, Read/Write—FC82)

(Default = 00000000)

The values of Bits 7–4 and Bit 0 of this register are determined by system reset strapping options. During a system reset certain outputs of the PC87120 become inputs. If these pins are pulled high by a 10 k $\Omega$  resistor during a system reset, then the corresponding bits in this register will be set equal to 1. If these pins are not pulled high during a system reset, then the corresponding bits will be set equal to 0.

The following illustrates how one of the bits in this register is set during a system reset:

If the  $\overline{DACK6}$  output is pulled high with a 10 k $\Omega$  resistor during the system reset, Bit 7 of this register will be set equal to 1. On the other hand, if  $\overline{DACK6}$  is not pulled high during a system reset, Bit 7 will be set to 0.

This shows an example of how Bits 7-4 and Bit 0 are configured during a system reset. This register is read only, so once these configuration bits are set they cannot be changed until the next system reset.

| Bit | Corresponding<br>Strapping Output |

|-----|-----------------------------------|

| 7   | DACK6                             |

| 6   | DACK5                             |

| 5   | DAČK3                             |

| 4   | DACK2                             |

| 0   | DACKO                             |

#### Bit 7—Mode Select for Interleave

Determines if Normal or Advanced two-way page interleaving is to be used for motherboard memory accesses. The state of this bit is ignored if convention mode is selected instead of two-way page interleaving mode (i.e., RAM/ROM Configuration Register #1, Bit 7 = 0).

The default value for this bit is 0, Normal two-way page interleaving mode. If the  $\overline{DACK6}$  output is pulled high by a 10 k $\Omega$  resistor during a system reset, this bit will be set equal to 1, advanced two-way page interleaving mode.

- 0 = Normal Two-Way Page Interleaving Mode (default)

- 1 = Advanced Two-Way Page Interleaving Mode

## Bit 6-8/16-Bit ROM BIOS Select

When set to 0, this bit indicates that 16-bit ROM BIOS will be used. 8-bit ROM BIOS selected when set to 1. The default for this bit is 0, 16-bit ROM BIOS.

If the  $\overline{DACK5}$  output is pulled high by a 10 k $\Omega$  resistor during a system reset, this bit will be set to 1, 8-bit ROM BIOS.

- 0 = 16-bit ROM BIOS (default)

- 1 = 8-bit ROM BIOS

## Bit 5—Page Mode Time Out Enable

When this bit is set to 0, it guarantees that no RAS signal will be held active low for more than 10.0  $\mu$ s, during page mode accesses. No time out is provided when this bit is set equal to 1.

This bit is ignored when the memory controller is configured to use conventional mode accesses (i.e., RAM/ROM Configuration Register #1, Bit 7 = 0). Conventional memory returns RAS to its inactive high state following every access.

The default for this bit is 0, Enable page mode time out. If the  $\overline{\text{DACK3}}$  output is pulled high by a 10 k $\Omega$  resistor during a system reset, this bit will be set to 1, disable page mode time out.

- 0 = Enable page mode time out (default)

- 1 = Disable page mode time out

# Bit 4—Extend RAS During Conventional Memory Access

When this bit is set equal to 1, the RAS and CAS strobes will rise at the same time at the end of every conventional memory access. Some DRAMs require RAS and CAS to rise at the same time.

On the other hand, when this bit is set to 0, RAS will rise a CLK2IN period before CAS. This will reduce the required latency between back to back memory cycles by a CLK2IN period.

This bit is ignored when the memory controller is configured to use two-way page interleaving mode (i.e., RAM/ROM Configuration Register #1, Bit 7 = 1). The default for this bit is 0, RAS rises a CLK2IN period before CAS.

If the  $\overline{DACK2}$  output is pulled high by a 10 k $\Omega$  resistor during a system reset, this bit will be set to 1, RAS and CAS rise at the same time.

- 0 = Off, RAS rises half a CLK2IN period before CAS

- 1 = On, RAS and CAS rise at the same time

#### Bit 3—Reserved:0

#### Bits 2-1—Bank Parity Check Error

These two bits are set when a parity error occurs and indicate which bank of memory the parity error occurred in.

If no parity error has occurred these two bits have no meaning.

| Bit 2 | Bit 1 | Bank No. |

|-------|-------|----------|

| 0     | 0     | Bank0    |

| 0     | 1     | Bank1    |

| 1     | 0     | Bank2    |

| 1     | 1     | Bank3    |

## Bit 0—ROM BIOS Location

When this bit equals 0, it indicates that the ROM BIOS's data pins are connected to the memory data bus. A 1 in this bit, means that the ROM BIOS's data pins are connected to the peripheral data bus (XD BUS).

The default for this bit is 0, ROM BIOS on the memory data bus.

If the  $\overline{\text{DACKO}}$  output is pulled high by a 10 k $\Omega$  resistor during a system reset, this bit will be set to 1, ROM BIOS on the peripheral data bus.

| Bit 0 | Location                           |  |

|-------|------------------------------------|--|

| 0     | Memory Data Bus (MD Bus) (default) |  |

| 1     | Peripheral Data Bus (XD Bus)       |  |

#### 3.1.5 Shadow RAM Enable Register

(8-Bit, Read/Write-FC83)

(Default = 00000000)

### Bits 7-6-ROM Type

These two bits determine the type and size of the ROM or EPROM chips supported. This information along with the 8/16-bit ROM BIOS Select bit determine the amount of ROM BIOS supported.

| Bit 7 | Bit 6 | Туре        |

|-------|-------|-------------|

| 0     | 0     | 16k (27128) |

| 0     | 1     | 32k (27256) |

| 1     | 1     | 64k (27256) |

### Bits 5-0—Shadow RAM Enable/Disable Bits

When using shadow RAM for BIOS, only the address range occupied by the BIOS should be enabled. If system BIOS uses shadow RAM, but video BIOS uses ROM, the shadow RAM address range for the system BIOS must be enabled, while the shadow RAM address range that coincides with the video BIOS must be disabled to prevent conflicts.

These six bits (Bits 5-0) are used to enable or disable 64 kB blocks of shadow RAM in the 640 kB to 1 MB BIOS address area. When a bit equals 0, it disables its 64 kB range of shadow RAM. When a bit equals 1, its 64 kB range of shadow RAM is enabled and the corresponding ROM should be disabled.

| Bit | Bit<br>Value | Function                                    |

|-----|--------------|---------------------------------------------|

| 5   | 0            | Disables Shadow RAM 0F0000 ~ 0FFFFF default |

|     | 1            | Enables Shadow RAM 0F0000 ~ 0FFFFF          |

| 4   | 0            | Disables Shadow RAM 0E0000 ~ 0EFFFF default |

|     | 1            | Enables Shadow RAM 0E0000 ~ 0EFFFF          |

| 3   | 0            | Disables Shadow RAM 0D0000 ~ 0DFFFF default |

|     | 1            | Enables Shadow RAM 0D0000 ~ 0DFFFF          |

| 2   | 0            | Disables Shadow RAM 0C0000 ~ 0CFFFF default |

|     | 1            | Enables Shadow RAM 0C0000 ~ 0CFFFF          |

| 1   | 0            | Disables Shadow RAM 0B0000 ~ 0BFFFF default |

|     | 1            | Enables Shadow RAM 0B0000 ~ 0BFFFF          |

| 0   | 0            | Disables Shadow RAM 0A0000 ~ 0AFFFF default |

|     | 1            | Enables Shadow RAM 0A0000 ~ 0AFFFF          |

# 3.1.6 ROM Area Enable/Shadow RAM Mode Register (8-Bit, Read/Write—FC84)

(Default = 00000010)

### Bits 7-6-Shadow RAM for Video ROM BIOS Area

These two bits determine access privileges to the shadow RAM for the video ROM BIOS area (located from 0C0000h to 0DFFFFh). When the video ROM BIOS is copied to shadow RAM, the shadow RAM must be configured in either the Write only option or READ/Write option. Otherwise, the copying is impossible.

After the BIOS has been copied to shadow RAM, the shadow RAM must be configured to the Read only option or Read/Write option. This will allow the system to read the video BIOS in shadow RAM. If the Read only option is selected the shadow RAM will act exactly like ROM and cannot be corrupted by accidental writes to this address range.

If the Read/Write option is selected, the video BIOS is susceptible to corruption by misdirected memory writes to this address range.

The states of these two bits are ignored if the shadow RAM for this address range is not enabled in the Shadow RAM Enable Register (i.e., Bits 3–2 set equal to 1 will enable the shadow RAM address range 0C0000h - 0DFFFFh).

| Bit 7 | Bit 6 | Function of Shadow RAM for Video BIOS (0C0000h - 0DFFFFh) |  |

|-------|-------|-----------------------------------------------------------|--|

| 0     | 0     | Disable (default)                                         |  |

| 0     | 1     | Read Only,                                                |  |

| 1     | 0     | Write Only                                                |  |

| 1     | 1     | Read/Write                                                |  |

#### Bits 5-4—Shadow RAM for Video RAM Area

These two bits determine access privileges to the shadow RAM for the video RAM area (located from 0A0000h to 0BFFFFh).

| Bit 5 | Bit 4 | Function of Shadow RAM for Video RAM (0A0000h - 0BFFFFh) |  |

|-------|-------|----------------------------------------------------------|--|

| 0     | 0     | Disable (default)                                        |  |

| 0     | 1     | Read Only,                                               |  |

| 1     | 0     | Write Only                                               |  |

| 1     | 1     | Read/Write                                               |  |

## Bits 3-2—Shadow RAM for System ROM BIOS Area

These two bits determine access privileges to the shadow RAM for the system ROM BIOS area (located from 0E0000h to 0FFFFFh). When the system ROM BIOS is copied to shadow RAM, the shadow RAM must be configured in either the Write only option or READ/Write option. Otherwise, the copying is impossible.

After the system BIOS has been copied to shadow RAM, the shadow RAM must be configured to the Read only option or Read/Write option. This will allow the system to read the system BIOS in shadow RAM. If the Read only option is selected the shadow RAM will act exactly like ROM and cannot be corrupted by accidental writes to this address range. If the Read/Write option is selected, the video BIOS is susceptible to corruption by misdirected memory writes to this address range.

The states of these two bits are ignored if the shadow RAM for this address range is not enabled in the Shadow RAM Enable Regiser (i.e., Bits 3–2 set equal to 1 will enable the shadow RAM address range 0E0000h - 0FFFFFh).

| Bit 3 | Bit 2 | Function of Shadow RAM for<br>System BIOS (0E0000h - 0FFFFFh) |

|-------|-------|---------------------------------------------------------------|

| 0     | 0     | Disable (default)                                             |

| 0     | 1     | Read Only,                                                    |

| 1     | 0     | Write Only                                                    |

| 1     | 1     | Read/Write                                                    |

## Bit 1—ROM BIOS Enable (0E0000h - 0EFFFFh)

This bit enables system ROM BIOS from 0E0000h to 0EFFFFh, when this bit is set to 0. When this bit equals 1, the system ROM BIOS for this memory range is disabled.

This BIOS range is only used if more than 64 kB of system BIOS is provided. If less than 64 kB of system BIOS is used only the 0F0000h to 0FFFFFh BIOS range is used and this bit is set equal to zero, disabling this 64 kB block of ROM BIOS. This bit should only be set to zero if more than 64 kB of system BIOS is provided and shadow RAM is not used.

- 0 = Enable ROM BIOS 0E0000h 0EFFFFh

- 1 = Disable ROM BIOS 0E0000h 0EFFFFh (default)

## Bit 0-ROM BIOS Enable (0F0000 - 0FFFFF)

This bit enables system ROM BIOS from 0F0000h to 0FFFFFh, when this bit equals 0. When this bit equals 1, the system ROM BIOS for this memory range is disabled. This system ROM BIOS should always be enabled unless the BIOS has been copied to shadow RAM and the shadow RAM copy is being used to improve system performance.

To prevent any conflicts, the system ROM BIOS and the corresponding shadow RAM system BIOS should never be enabled at the same time.

- 0 = Enable ROM BIOS 0F0000h 0EFFFFh (default)

- 1 = Disable ROM BIOS 0F0000h 0EFFFFh

#### 3.1.7 DRAM Enable Register

(8-Bit Read/Write-FC86)

(Default = 11110000)

### Bits 7-0—DRAM Enable Bits

All eight of these bits enable or disable 64 kB blocks of motherboard DRAM memory between 040000h and 0BFFFFh. These 64 kB blocks must be disabled when EMS expanded memory is mapped into these memory locations. This will prevent conflicts between the expanded memory and the coinciding DRAM memory normally at those physical addresses.

| Bit | Bit<br>Value | Function                              |

|-----|--------------|---------------------------------------|

| 7   | 0            | Enable RAM B0000h - BFFFFh            |

|     | 1            | Disable RAM B0000h - BFFFFh (default) |

| 6   | 0            | Enable RAM A0000h - AFFFFh            |

| L   | 1            | Disable RAM A0000h - AFFFFh (default) |

| 5   | 0            | Enable RAM 90000h - 9FFFFh            |

|     | 1            | Disable RAM 90000h - 9FFFFh (default) |

| 4   | 0            | Enable RAM 80000h - 8FFFFh            |

|     | 1            | Disable RAM 80000h - 8FFFFh (default) |

| 3   | 0            | Enable RAM 70000h - 7FFFFh (default)  |

|     | 1            | Disable RAM 70000h - 7FFFFh           |

| 2   | 0            | Enable RAM 60000h - 6FFFFh (default)  |

|     | 1            | Disable RAM 60000h - 6FFFFh           |

| 1   | 0            | Enable RAM 50000h - 5FFFFh (default)  |

|     | 1            | Disable RAM 50000h - 5FFFFh           |

| 0   | 0            | Enable RAM 40000h - 4FFFFh (default)  |

|     | 1            | Disable RAM 40000h - 4FFFFh           |

## 3.1.8 Refresh Control Register

(8-Bit, Read/Write—FC89)

(Default = XXXX0000)

#### Bits 7-4-Reserved

#### Bits 3-2-Burst Refresh

These two bits determine the number of refreshes performed for each refresh request. Multiple refreshes reduces latency of the average refresh cycle.

| Bit 3 | Bit 2 | Number of Refreshes per Cycle |

|-------|-------|-------------------------------|

| 0     | 0     | 1 (default)                   |

| 0     | 1     | 2                             |

| 1     | 0     | 3                             |

| 1     | 1     | 4                             |

### Bits 1-0-Period of Refresh Cycle

These two bits determine the refresh rate for the motherboard DRAM.

| Bit 1 | Bit 0 | Mode (Refresh Rate) |

|-------|-------|---------------------|

| 0     | 0     | 0 (4 ms) (default)  |

| 0     | 1     | 1 (8 ms)            |

| 1     | 0     | 2 (16 ms)           |

| 1     | 1     | 3 (32 ms)           |

## 3.1.9 Sleep Mode/DMA Control Register

(8-Bit Read/Write—FC85)

(Default = 00000000)

### Bit 7—DMA Clock Frequency

When this bit is set to 0, the DMA clock (DMACLK) runs at half the frequency of the system clock (SYSCLK). When set to 1, DMACLK runs at the same frequency as SYSCLK.

0 DMACLK = SYSCLK/2 (default)

1 DMACLK = SYSCLK

#### Bit 6---DMA Command Delays

Determines if a command delay is inserted into every DMA transfer. A command delay forces the command strobe(s) to stay inactive high for half a DMA clock (DMACLK) period at the beginning of each transfer. This will give the address an extra half SYSCLK period to setup before the command strobe(s) become active.

0 = One DMA clock cycle delay (default)

1 = No DMA clock cycle delay

### Bits 5-4-DMA Wait State

These two bits determine the number of wait states added to every DMA transfer.

| Bit 5 | Bit 4 | Wait State             |

|-------|-------|------------------------|

| 0     | 0     | 1 wait state (default) |

| 0     | 1     | 2 wait states          |

| 1     | 0     | 3 wait states          |

| 1     | 1     | 4 wait states          |

#### Bit 3-Gate A20 (GA20) Bit

When this bit is set to 0, GA20 will be the same value as the A20 input from the CPU. When this bit is set equal to 1, GA20 will be forced to 0. During real mode operation, GA20 must be forced to 0.

0 = Propagate CPU A20 to A20 line (default)

1 = Set A20 to 0

### Bit 2—Suspend/Resume Mode Enable

0 = Enable

1 = Disable

#### Bit 1-Clocks in Sleep Mode

When set to 1, this bit disables the clocks generated by the PC87120 during sleep mode. The processor clock (PROCLK) and the system clock (SYSCLK) will turn off, reducing power consumption. When set to 0, the clocks will continue to run even in sleep mode.

0 = Clocks are not shut off in sleep mode

1 = Clocks shut off when sleep mode is enabled

#### Bit 0—Sleep Mode Enable/Disable

When set to 1, this bit enables the PC87120 to enter sleep mode when it decodes a 80286 halt cycle. The PC87120 exits sleep mode whenever an interrupt occurs.

When this bit is set to 0, the PC87120 will lock the system and force a system reset when it decodes a 80286 halt cycle.

0 = Disable

1 = Enable

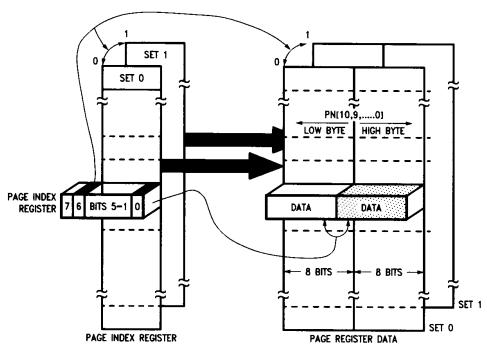

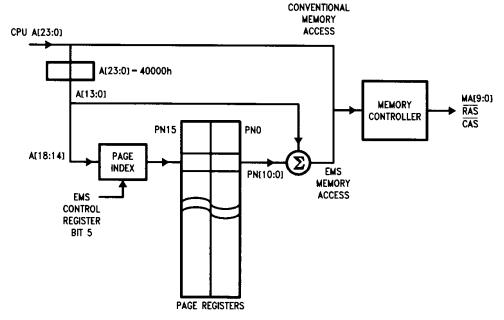

## 3.1.10 EMS Control Registers

(8-Bit Read/Write—FC88h)

(Default = XX000000)

#### Bits 7-6—Reserved

### Bit 5-EMS Set Select

This bit determines which EMS register set is in use. Toggling this bit allows one to switch from one set of EMS memory to the other set. This provides efficient support for task switching which requires different EMS memory ranges. Each set of EMS registers may be loaded at the beginning of each task. Then when tasks are switched, the appropriate EMS memory can be enabled by toggling this bit, instead of being forced to reload all of the EMS registers every time tasks are switched.

0 Set 0 in Use (default)

1 Set 1 in Use

## Bits 4-3-EMS I/O Port Address Select

These two bits provide a way to remap the IO ports through which the EMS registers may be programmed. The X in the following table corresponds to bits 7-4 of the IO address where the EMS registers are mapped.

For more information about the function of these bits refer to Section 3.5, EMS Registers.

| Bit 4 | Bit 3 | X           |

|-------|-------|-------------|

| 0     | 0     | 0 (default) |

| 0     | 1     | 1           |

| 1     | 0     | 2           |

| 1     | 1     | 3           |

## Bits 2-0-On-Board EMS Starting Address

These three bits determine the starting address for all motherboard EMS memory. All motherboard memory below 1 MB is considered real mode memory. All DRAM between 1 MB and the memory selected by these bits will be treated as extended memory. All memory above the indicated EMS starting address will be used as expanded memory.

| Bit 2 | Bit 1 | Bit 0 | Starting Address |

|-------|-------|-------|------------------|

| 0     | 0     | 0     | 1 MB (default)   |

| 0     | 0     | 1     | 2 MB             |

| 0     | 1     | 0     | 4 MB             |

| 0     | 1     | 1     | 6 MB             |

| 1     | 0     | 0     | 8 MB             |

#### **3.2 DMA REGISTERS**

The registers in this section are used to select the DMA transfer mode as well as the type of transfer for each DMA channel. Additionally, the DMA system registers contain the memory address corresponding to the DMA transfer. Since there are two DMA controllers (DMAC1 and DMAC2) in the PC87120's DMA system, there are two of every register listed in this section, except for the Page Register. The DMA system registers are mapped into the following IO address ranges: 0000-000Fh (DMAC1); even addresses 00C0-00CEh and 00D0-00DEh (DMAC2); and 0080-008Fh (Page Register). Note that all of the DMA system registers must be programmed; there are no default register values.

## 3.2.1 Command Register

(8-Bit, Write: 0008-DMAC1, 00D0-DMAC2)

### Bit 7—DMA Acknowledge Bit (DACK)

- 0 = DACK signals active low

- 1 = DACK signals active high

To maintain compatibility with the PC/AT this bit should be set to zero for DMAC2, making its DACK signals active low.

## Bit 6—DMA Request Bit (DRQ)

- 0 = DREQ signals active low

- 1 = DREQ signals active high

## Bit 5-Extended Write Bit (EW)

- 0 = Extended Write disabled

- 1 = Extended Write enabled

X if compressed timing is enabled, bit 3 = 1

## Bit 4—Rotating Priority Bit (RP)

- 0 = Fixed Priority

- 1 = Rotating Priority

## Bit 3—Compressed Timing Bit (CT)

- 0 = Normal Timing

- 1 = Compressed Timing

X if Memory-to-Memory Transfers are enabled, bit 0 = 1

#### Bit 2-DMA Controller Disable Bit (CD)

- 0 = DMA Controller Enabled

- 1 = DMA Controller Disabled

## Bit 1—Address Hold Bit (AH)

This bit determines whether or not the memory address in the DMA access for channel 0 is held constant. It is valid only during a memory-to-memory transfer.

- 0 = Address Hold Disabled on DMA Channel 0, memory address will increment or decrement as programmed

- 1 = Address Hold Enabled on DMA Channel 0, memory address is held constant.

X if Memory-to-Memory Transfers are disabled, bit 0 = 0

## Bit 0—Memory-to-Memory Transfer Bit (M-M)

- 0 = Memory-to-Memory Transfers Disabled

- 1 = Memory-to-Memory Transfers Enabled

## 3.2.2 Current Address Register

(16-Bit Read/Write)

| IO Address for Current<br>Address Register | DMA Channel<br>Assignments |

|--------------------------------------------|----------------------------|

| 00h                                        | Channel 0                  |

| 02h                                        | Channel 1                  |

| 04h                                        | Channel 2 DMAC1            |

| 06h                                        | Channel 3                  |

| C0h                                        | Channel 4)                 |

| C4h                                        | Channel 5 DMAC2            |

| C8h                                        | Channel 6                  |

| CCh                                        | Channel 7                  |

### Bits 15-0—Current DMA Memory Address Bits

These bits contain the 16 bits of the system memory address produced by the DMA controller and its corresponding 8-bit latch. Note that these bits are read or written in two 8-bit accesses where an internal flip-flop automatically switches between the high and low address bytes.

When programming the Current Address register for 8-bit data transfers (channels 0-3), the bits 15-0 correspond to the system address bits A15-A0. When programming the Current Address register for 16-bit data transfers (channels 5-7), the bits 15-0 correspond to the system address bits A16-A1. Therefore, the address programmed is the system memory address divided by two for 16-bit data transfers

## 3.2.3 Current Word Count Register

(16-Bit Read/Write)