- 5-V Core Logic With PCI Interface

- Supports PCI Clock Frequencies up to 33 MHz

- Accepts IRQSER Serial Interrupt Stream Input From TI™ PC Card Controllers

- Provides System Access to All 15 ISA-Style IRQs and 4 PCI-Style Interrupts

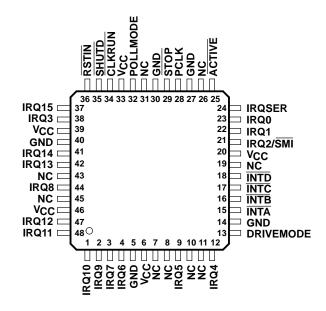

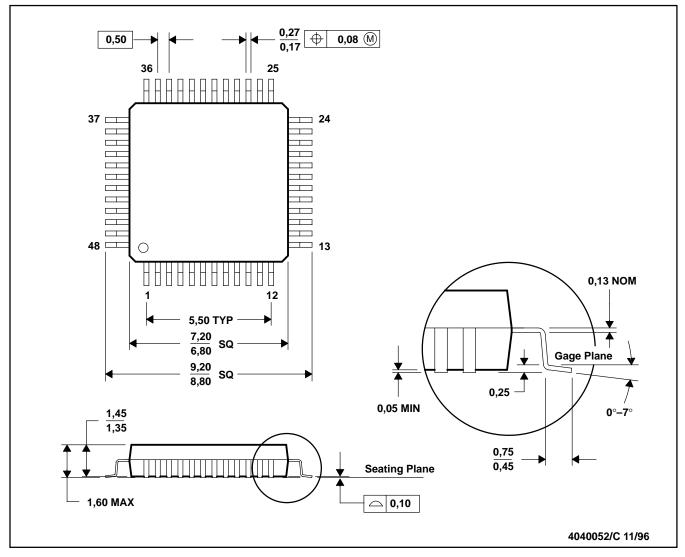

- Offered in 48-Pin TQFP Package

#### description

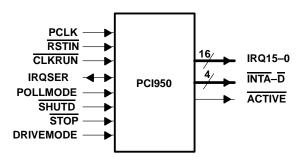

The PCI950 is an IRQSER interrupt descrializer that interfaces with existing and future TI PC Card controllers. The PCI950 accepts the IRQSER output of a TI PC Card controller and converts it to 16 ISA-style interrupts and 4 PCI-style interrupts. Interfacing the PC Card controller with the PCI950 permits system access of all available interrupts and features of the PC Card controller.

#### functional block diagram

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TI is a trademark of Texas Instruments Incorporated

TEXAS INSTRUMENTS

## **Terminal Functions**

| TERMINAL                  |                                                                     | 1/0  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------|---------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                      | NO.                                                                 | TYPE | Device active. When the PCI950 is busy, this output is low and when the PCI950 is idle, this output is                                                                                                                                                                                                                                                                                                                                                                                                        |

| ACTIVE                    | 25                                                                  | 0    | high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CLKRUN                    | 34                                                                  | I/O  | PCI clock run. CLKRUN is used by the central resource to request permission to stop the PCI clock or to slow the PCI clock rate. When the PCI950 is busy and CLKRUN is sampled high, then CLKRUN is driven low for two clock cycles. If CLKRUN is not used, it can be tied low. See Note 1.                                                                                                                                                                                                                   |

| DRIVEMODE                 | 13                                                                  | -    | Drive mode. When this input is high and the PCI950 samples a low on the IRQSER line during the sample phase of the IRQ data frame, then the PCI950 drives the IRQSER line high during the recovery phase. When this input is low and the PCI950 samples a low level on the IRQSER line during the sample phase of the IRQ data frame, then the PCI950 three-states the IRQSER line during the recovery phase.                                                                                                 |

| GND                       | 5, 14, 27,<br>30, 40                                                | 1    | Device ground terminals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| INTA, INTB,<br>INTC, INTD | 15, 16,<br>17, 18                                                   | 0    | PCI-style interrupts. These are four parallel PCI-style Interrupts, INTA-INTD. The PCI950 provides the PCI interrupts in an open-drain environment, which requires the system vendor to implement a pullup resistor on each implemented interrupt.                                                                                                                                                                                                                                                            |

| IRQ0, IRQ1,<br>IRQ3-15    | 23, 22,<br>38,12, 9,<br>4, 3, 44,<br>2, 1, 48,<br>47, 42,<br>41, 37 | 0    | ISA-style interrupts. These are 15 parallel ISA interrupts, IRQ0, 1, 3–15. The PCI950 provides the ISA interrupts in an open-drain environment, which requires the system vendor to implement a pullup resistor on each implemented interrupt.                                                                                                                                                                                                                                                                |

| IRQ2/SMI                  | 21                                                                  | 0    | System management interrupt. The PCI950 provides the SMI interrupt in an open-drain environment, which requires the system vendor to implement a pullup resistor on each implemented interrupt.                                                                                                                                                                                                                                                                                                               |

| IRQSER                    | 24                                                                  | I/O  | Serial interrupt stream from PC Card controller. This input is connected to the IRQSER output from the TI PC Card controller.                                                                                                                                                                                                                                                                                                                                                                                 |

| NC                        | 7, 8, 10,<br>11, 19,<br>26, 31,<br>43, 45                           | _    | No connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PCLK                      | 28                                                                  | I    | PCI-bus clock. The PCI-bus clock operates at frequencies ranging from 0–33 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| POLLMODE                  | 32                                                                  | -    | Poll mode. Selects between quiet mode and continuous mode. When this input is low, the PCI950 is in quiet mode. When this input is high, the PCI950 is in continuous mode. The POLLMODE signal is sampled during the rising edge of a start frame. After reset, the PCI950 generates the first cycle, and the stop-frame width in this cycle is set based on the POLLMODE input level. Any change in POLLMODE input causes the PCI950 to generate a start pulse.                                              |

| RSTIN                     | 36                                                                  | Ι    | Device reset. When RSTIN is asserted low, the internal counters are reset and all output buffers are put in a high-impedance state (three stated). After RSTIN is deasserted, the PCI950 defaults to continuous mode.                                                                                                                                                                                                                                                                                         |

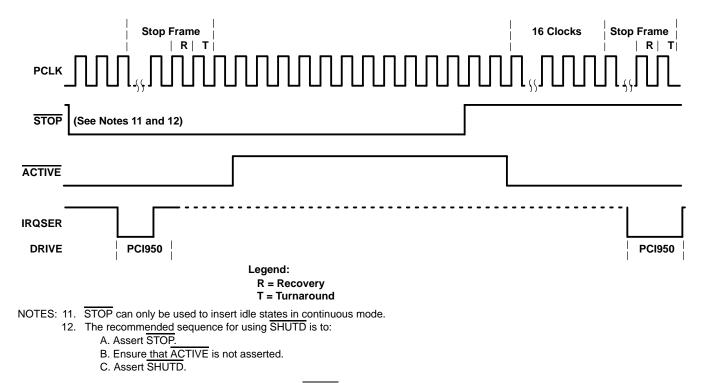

| SHUTD                     | 35                                                                  | -    | Shutdown. When SHUTD input is low, the internal clock is stopped and the outputs are placed in a high-impedance state (three stated). When SHUTD input is high, the device is in normal operation. During continuous mode of operation, the recommended use of SHUTD is to first assert STOP input, check that ACTIVE is high, and then assert SHUTD to stop the clock. During quiet mode of operation, the SHUTD input can be asserted after ACTIVE is sampled high.                                         |

| STOP                      | 29                                                                  | -    | Stop continuous mode. The default number of idle clocks between stop and start frame in continuous mode is one. But the STOP pin can be used to insert more than one idle state. If the PCI950 is in continuous mode and if during an IRQSER cycle the STOP input is driven low, then after completion of the IRQSER cycle any number of idle states can be inserted. The next start frame is initiated by PCI950 when STOP is driven high. If STOP is not to be used, then it must be tied high. See Note 1. |

| Vcc                       | 6, 20, 33,<br>39, 46                                                | _    | Device 5-V power-supply terminals                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

NOTE 1: Unused active-low inputs must be pulled up to V<sub>CC</sub> using a 43 kΩ resistor, and unused active-high inputs must be pulled down to GND using a 43 kΩ resistor.

#### functional description

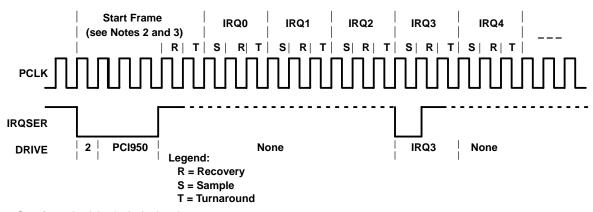

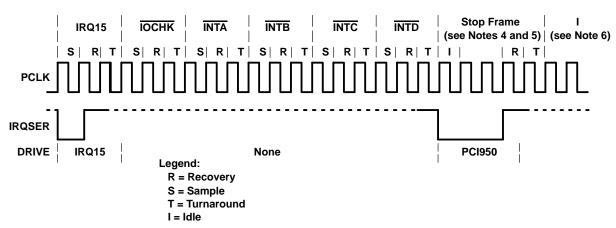

The PCI950 accepts the serialized IRQ stream from the PC Card controller for conversion to discrete ISA and PCI interrupts. The serialized IRQ protocol is defined in the document *Serialized IRQ Protocol for PCI Systems*, revision 6.0. This protocol uses a serial packet consisting of one start frame, several IRQ/data frames, and one stop frame.

Start frame: There are two modes of operation for the IRQSER start frame – quiet mode and continuous mode. During continuous mode the PCI950 initiates the start frame. A low level on the POLLMODE input pin selects the quiet mode and a high level selects continuous mode for the PCI950. The total low-pulse width on a start frame is eight clocks. After reset the PCI950 defaults to continuous mode.

IRQ/data frame: The PCI950 is designed to decode a fixed length of 21 IRQ/data frames that are sampled in the following sequence: IRQ0, IRQ1, SMI, IRQ3 through IRQ15, IOCHK, INTA, INTB, INTC, and INTD.

Stop frame: After the completion of a start frame and 21 IRQ data frames, the PCl950 generates a stop frame. The pulse width of the stop pulse is determined by the status of the POLLMODE input pin sampled during the start frame.

NOTES: 2. Start frame is eight clocks in duration.

3. Slave or host initiated: POLLMODE is level dependent.

Figure 1. IRQSER Start-Frame Timing

NOTES: 4. The PCI950 stop pulse is two or three clocks in duration.

- 5. There may be none, one, or more idle states during the stop frame.

- 6. When the PCI950 is in continuous mode, there are 17 idle states between the stop frame and the start frame.

Figure 2. IRQSER Stop-Frame Timing

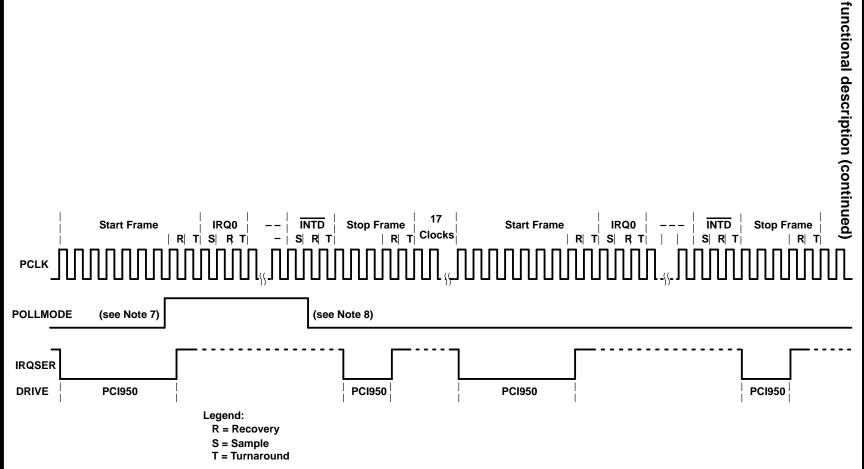

NOTES: 7. When the POLLMODE input level changes before the rising edge of the start frame, then the stop-frame width in the current IRQSER cycle reflects the change in mode.

8. Any change in the POLLMODE input level after the start frame is complete is reflected in the next IRQSER cycle.

Figure 3. POLLMODE Level Change During an IRQSER Cycle

#### functional description (continued)

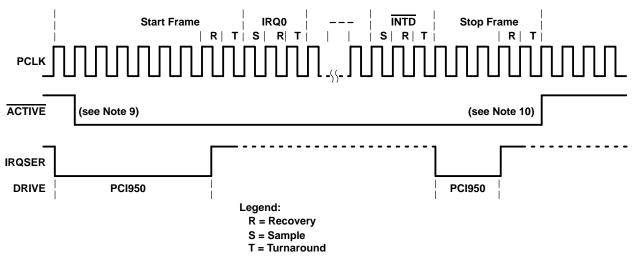

- NOTES: 9. ACTIVE goes low one clock cycle after the beginning of the PCI950 start pulse.

- 10. ACTIVE is set high two clock pulses after the PCI950 stop pulse.

Figure 4. ACTIVE Output Timing During Quiet Mode

Figure 5. Using STOP During Continuous Mode

#### **APPLICATION INFORMATION**

## system-level implementation

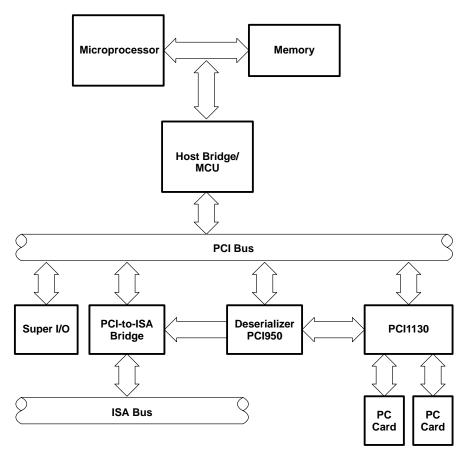

A typical PCI950 system implementation is shown in Figure 6. The PCI950 allows software access to interrupts that may not exist on the periphery of the PC Card controller, thus increasing the overall interrupt resources that can be utilized.

Figure 6. Typical System Installation

# absolute maximum ratings over operating temperature ranges (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub>                                          | 0.5 V to 6 V                              |

|--------------------------------------------------------------------------------|-------------------------------------------|

| Input voltage range, V <sub>I</sub>                                            | $\dots$ -0.5 V to V <sub>CC</sub> + 0.5 V |

| Output voltage range, V <sub>O</sub>                                           | 0.5 V to V <sub>CC</sub> + 0.5 V          |

| Input clamp current, $I_{IK}$ ( $V_I < 0$ or $V_I > V_{CC}$ ) (see Note 13)    | ±20 mA                                    |

| Output clamp current, $I_{OK}$ ( $V_O < 0$ or $V_O > V_{CC}$ ) (see Note 14) . | ±20 mA                                    |

| Storage temperature range, T <sub>stq</sub>                                    | –65°C to 150°C                            |

| Virtual junction temperature, T.J                                              |                                           |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# recommended operating conditions (see Note 15)

|                   |                                                                                    |            |      | NOM | MAX  | UNIT |

|-------------------|------------------------------------------------------------------------------------|------------|------|-----|------|------|

| VCC               | Supply voltage                                                                     | Commercial | 4.75 | 5   | 5.25 | ٧    |

| ∨ <sub>IH</sub> ‡ | High-level input voltage                                                           |            | 2    |     | VCC  | V    |

| V <sub>IL</sub> ‡ | Low-level input voltage                                                            |            | 0    |     | 0.8  | V    |

| VI                | Input voltage                                                                      |            | 0    |     | VCC  | V    |

| VO <sup>§</sup>   | Output voltage                                                                     |            | 0    |     | VCC  | V    |

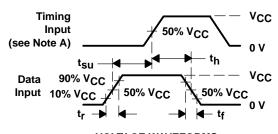

| t <sub>t</sub>    | Input transition time [rise time $(t_{f})$ and fall time $(t_{f})$ , see Figure 7] |            | 0    |     | 25   | ns   |

| TA                | Operating ambient temperature range                                                |            | 0    | 25  | 70   | °C   |

| TJ¶               | Virtual junction temperature                                                       |            | 0    | 25  | 115  | °C   |

<sup>‡</sup> Applies to external inputs and bidirectional buffers without hysteresis

NOTE 15: Unused pins (input or I/O) must be forced or tied high or low to prevent them from floating.

#### electrical characteristics over recommended operating conditions (unless otherwise noted)

|      | PARAMETER                                    | PINS             | TEST CONDITIONS          | MIN | MAX  | UNIT |

|------|----------------------------------------------|------------------|--------------------------|-----|------|------|

| Vон  | High-level output voltage                    | PCI#             | $I_{OH} = -2 \text{ mA}$ | 2.4 |      | V    |

|      |                                              | Standard         | I <sub>OH</sub> = -4 mA  | 2.1 |      |      |

|      | Low-level output voltage                     | PCI <sup>#</sup> | I <sub>OL</sub> = 6 mA   |     | 0.55 | V    |

| VOL  |                                              | Standard         | I <sub>OL</sub> = 4 mA   |     | 0.5  |      |

| lozL | 3-state output, high-impedance state current | Output pins      | V <sub>I</sub> = GND     |     | -10  | μΑ   |

| lozh | 3-state output, high-impedance state current | Output pins      | $V_I = V_{CC}$           |     | 10   | μΑ   |

|      | Low-level input current                      | Input pins       | V <sub>I</sub> = GND     |     | -1   |      |

| II∟  |                                              | I/O pins         | V <sub>I</sub> = GND     |     | -10  | μΑ   |

| I.u. | High-level input current                     | Input pins       | VI = VCC                 |     | 1    |      |

| lіН  |                                              | I/O pins         | VI = VCC                 |     | 10   | μΑ   |

<sup>#</sup>PCI pins are INTA, INTB, INTC, INTC, and SERIRQ.

NOTES: 13. Applies to external input and bidirectional buffers

<sup>14.</sup> Applies to external output and bidirectional buffers

<sup>§</sup> Applies to external output buffers

<sup>¶</sup> These junction temperatures reflect simulation conditions. The customer is responsible for verifying junction temperature.

For I/O pins, input leakage (I<sub>IL</sub> and I<sub>IH</sub>) includes I<sub>OZ</sub> leakage of the disabled output.

#### PARAMETER MEASUREMENT INFORMATION

#### LOAD CIRCUIT PARAMETERS

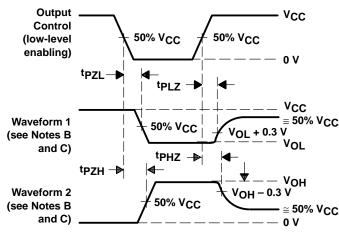

| TIMING<br>PARAMETER |                  | C <sub>LOAD</sub> †<br>(pF) | I <sub>OL</sub><br>(mA) | I <sub>OH</sub><br>(mA) | V <sub>LOAD</sub> (V) |  |

|---------------------|------------------|-----------------------------|-------------------------|-------------------------|-----------------------|--|

| •                   | tPZH             | 50                          | 8                       |                         | 0                     |  |

| <sup>t</sup> en     | t <sub>PZL</sub> | 50                          |                         | <b>–8</b>               | 3                     |  |

| <b>*</b>            | <sup>t</sup> PHZ | <b>50</b>                   | •                       |                         | 4.5                   |  |

| <sup>t</sup> dis    | tPLZ             | 50                          | 8                       | <b>–8</b>               | 1.5                   |  |

| <sup>t</sup> pd     |                  | 50                          | 8                       | -8                      | ‡                     |  |

<sup>†</sup>C<sub>LOAD</sub> includes the typical load-circuit distributed capacitance.

$$\ddagger \frac{\text{V}_{LOAD} - \text{V}_{OL}}{\text{I}_{OL}}$$

= 50  $\Omega$ , where  $\text{V}_{OL}$  = 0.6 V,  $\text{I}_{OL}$  = 8 mA

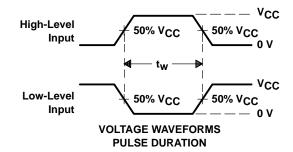

VOLTAGE WAVEFORMS **SETUP AND HOLD TIMES INPUT RISE AND FALL TIMES**

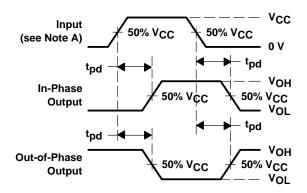

**VOLTAGE WAVEFORMS** PROPAGATION DELAY TIMES

**VOLTAGE WAVEFORMS ENABLE AND DISABLE TIMES, 3-STATE OUTPUTS**

- NOTES: A. Phase relationships between waveforms were chosen arbitrarily. All input pulses are supplied by pulse generators having the following characteristics: PRR = 1 MHz,  $Z_O = 50 \Omega$ ,  $t_{\Gamma} = 6 \text{ ns.}$

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. For tpl 7 and tpH7, VOI and VOH are measured values.

Figure 7. Load Circuit and Voltage Waveforms

## **MECHANICAL DATA**

# PT (S-PQFP-G48)

#### PLASTIC QUAD FLATPACK

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-026

# PCI950 IRQSER DESERIALIZER

SCPS015 - JULY 1997 - REVISED JANUARY 1998

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated