### **VDP Multiple Pixel Clock Generator**

#### **Features**

- Generates multiple clock outputs from 20MHz external reference clock

- Input frequency: 20MHz

- · Output frequencies:

- Selectable CLKOUT: 108MHz, 27MHz, 33.2MHz, 85MHz, 65MHz, 25MHz, 45MHz, and 40MHz

- REFOUT: 20MHz

- Operating Supply Voltage: 3.3V ± 0.3V

- Zero ppm frequency synthesis error on all clock outputs

- Commercial temperature: 0°C to +85°C

- 8-pin SOIC package

#### **Product Description**

The PCS1P2192A is a clock generator that generates multiple selectable pixel clock outputs for Video Display Panel applications from an external 20MHz reference clock. The PLL based clock generator is specifically designed to provide zero ppm frequency synthesis error on all clock outputs. Various pixel clock rates are selectable through frequency selection pins S[2:0] (Refer Frequency Selection Table) The device provides a reference clock output additionally. Operating Supply Voltage for this device is 3.3V± 0.3V. The device is available in an 8 pin SOIC package, in commercial temperature grade.

### **Applications**

PCS1P2192A is targeted towards Video Display Panel (VDP) applications like VGA, SVGA, XGA, WXGA, UXGA.

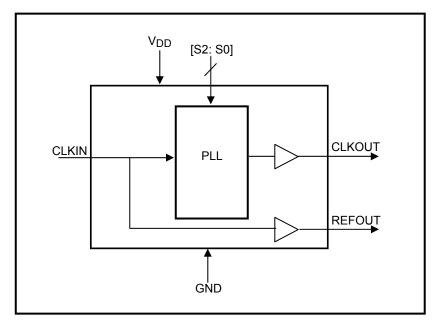

### **Block Diagram**

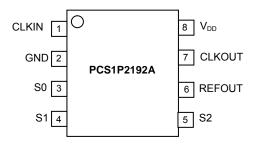

# **Pin Configuration**

# **Pin Description**

| Pin# | Pin Name | Туре | Description                                                                                                                                         |  |

|------|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1    | CLKIN    | 1    | 20MHz external reference clock input.                                                                                                               |  |

| 2    | GND      | Р    | Ground Connection.                                                                                                                                  |  |

| 3    | S0       | I    | Frequency select. Digital logic input used to select output frequency. Has an internal pull up resistor. ( <i>Refer Frequency Selection Table</i> ) |  |

| 4    | S1       | ı    | Frequency select. Digital logic input used to select output frequency. Has an internal pull up resistor. ( <i>Refer Frequency Selection Table</i> ) |  |

| 5    | S2       | I    | Frequency select. Digital logic input used to select output frequency. Has an interpull up resistor. (Refer Frequency Selection Table)              |  |

| 6    | REFOUT   | 0    | Reference clock output                                                                                                                              |  |

| 7    | CLKOUT   | 0    | Clock output                                                                                                                                        |  |

| 8    | $V_{DD}$ | Р    | Device Power Supply                                                                                                                                 |  |

# **Frequency Selection Table**

| S2             | <b>S</b> 1 | S0 | CLKOUT (MHz) |

|----------------|------------|----|--------------|

| 0              | 0          | 0  | 108          |

| 0              | 0          | 1  | 27           |

| 0              | 1          | 0  | 33.2         |

| 0              | 1          | 1  | 85           |

| 1              | 0          | 0  | 65           |

| 1              | 0          | 1  | 25           |

| 1              | 1          | 0  | 45           |

| ataSheet4U.con | າ 1        | 1  | 40           |

TA7TA7TA

# **Absolute Maximum Ratings**

| Symbol                                                                                                                                                                        | Parameter                                       | Rating       | Unit |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--------------|------|--|--|--|

| $V_{DD},V_{IN}$                                                                                                                                                               | Voltage on any input pin with respect to Ground | -0.5 to +4.6 | V    |  |  |  |

| T <sub>STG</sub>                                                                                                                                                              | Storage temperature                             | -65 to +125  | °C   |  |  |  |

| Ts                                                                                                                                                                            | Max. Soldering Temperature (10 sec)             | 260          | °C   |  |  |  |

| TJ                                                                                                                                                                            | Junction Temperature                            | 150          | °C   |  |  |  |

| T <sub>DV</sub> Static Discharge Voltage 2 KV (As per JEDEC STD22- A114-B)                                                                                                    |                                                 |              |      |  |  |  |

| Note: These are stress ratings only and are not implied for functional use. Exposure to absolute maximum ratings for prolonged periods of time may affect device reliability. |                                                 |              |      |  |  |  |

# **Recommended Operating Conditions**

| Parameter       | Description           | Min | Тур | Max | Unit |

|-----------------|-----------------------|-----|-----|-----|------|

| $V_{DD}$        | Operating Voltage     | 3.0 | 3.3 | 3.6 | V    |

| T <sub>A</sub>  | Operating Temperature | 0   |     | +85 | °C   |

| $C_L$           | Load Capacitance      |     |     | 15  | pF   |

| C <sub>IN</sub> | Input Capacitance     |     |     | 7   | pF   |

## **DC Electrical Characteristics**

| Symbol           | Parameter                                                | Min       | Тур | Max       | Unit |

|------------------|----------------------------------------------------------|-----------|-----|-----------|------|

| V <sub>IL</sub>  | Input low voltage (For CLKIN)                            | GND - 0.3 |     | 0.8       | V    |

| $V_{IH}$         | Input high voltage (For CLKIN)                           | 2.0       |     | VDD + 0.3 | V    |

| I <sub>IL</sub>  | Input low current                                        |           |     | 50        | μA   |

| I <sub>IH</sub>  | Input high current                                       |           |     | -50       | μA   |

| $V_{OL}$         | Output low voltage (VDD = 3.3V, I <sub>OL</sub> = 8mA)   |           |     | 0.4       | V    |

| V <sub>OH</sub>  | Output high voltage (VDD = 3.3V, I <sub>OH</sub> = -8mA) | 2.4       |     |           | V    |

| I <sub>DD</sub>  | Static supply current *                                  |           |     | 5         | mA   |

| I <sub>CC</sub>  | Dynamic supply current (3.3V and no load)                |           | 9   |           | mA   |

| $V_{DD}$         | Operating Voltage                                        | 3.0       | 3.3 | 3.6       | V    |

| t <sub>ON</sub>  | Power-up time (first locked cycle after power-up)        |           | 1   |           | mS   |

| Z <sub>OUT</sub> | Output impedance                                         |           | 40  |           | Ω    |

| * CLKIN pulle    | d low                                                    |           |     |           |      |

June 2009 Giving you the edge PCS1P2192A

# rev 1.0

## **AC Electrical Characteristics**

| Symbol                                  | Parameter                                     | Min | Тур                                     | Max | Unit |  |

|-----------------------------------------|-----------------------------------------------|-----|-----------------------------------------|-----|------|--|

| f <sub>IN</sub>                         | Input frequency                               |     | 20                                      |     | MHz  |  |

| f <sub>OUT</sub>                        | Output frequency                              |     | 108, 27,<br>33.2, 85, 65,<br>25, 45, 40 |     | MHz  |  |

| t <sub>LH</sub> *                       | Output rise time ( Measured from 20% to 80% ) | 1.2 |                                         | 2.5 | nS   |  |

| t <sub>HL</sub> *                       | Output fall time ( Measured from 80% to 20% ) | 0.8 |                                         | 1.6 | nS   |  |

| t <sub>JC</sub>                         | Period Jitter                                 |     | ±150                                    |     | pS   |  |

|                                         | Frequency Synthesis Error (All Outputs)       |     | 0                                       |     | ppm  |  |

| t <sub>D</sub>                          | Output duty cycle                             | 40  | 50                                      | 60  | %    |  |

| measured with a capacitive load of 15pF |                                               |     |                                         |     |      |  |

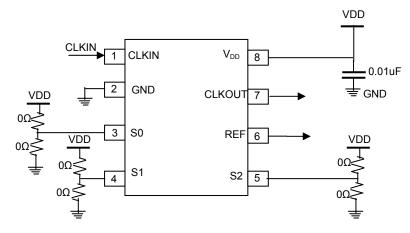

## **Typical Application Schematic**

Use either pull-up or pull-down  $0\Omega$  Resistor with [S2:S0] for selection of CLKOUT frequencies

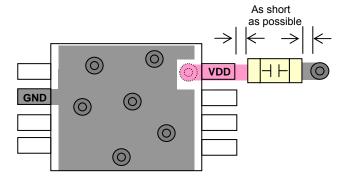

#### **PCB Layout Recommendation**

For optimum device performance, following guidelines are recommended.

- Dedicated VDD and GND planes.

- The device must be isolated from system power supply noise. A 0.01µF decoupling capacitor should be mounted on the component side of the board as close to the VDD pin as possible. No vias should be used between the decoupling capacitor and VDD pin. The PCB trace to VDD pin and the ground via should be kept as short as possible. All the VDD pins should have decoupling capacitors.

- In an optimum layout all components are on the same side of the board, minimizing vias through other signal layers.

A typical layout is shown in the figure

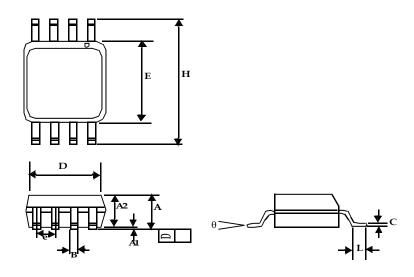

# **Package Information**

# 8-Pin SOIC Package

|        | Dimensions         |            |             |      |  |

|--------|--------------------|------------|-------------|------|--|

| Symbol | Inc                | hes        | Millimeters |      |  |

|        | Min                | Max        | Min         | Max  |  |

| A1     | 0.004              | 0.010      | 0.10        | 0.25 |  |

| Α      | 0.053              | 0.069      | 1.35        | 1.75 |  |

| A2     | 0.049              | 0.059      | 1.25        | 1.50 |  |

| В      | 0.012              | 0.020 0.31 |             | 0.51 |  |

| С      | 0.007              | 0.010      | 0.18        | 0.25 |  |

| D      | 0.193 BSC 4.90 BSC |            | BSC         |      |  |

| Е      | 0.154              | BSC        | 3.91 BSC    |      |  |

| е      | 0.050 BSC          |            | 1.27 BSC    |      |  |

| Н      | 0.236 BSC          |            | 6.00 BSC    |      |  |

| L      | 0.016              | 0.050      | 0.41        | 1.27 |  |

| θ      | 0°                 | 8°         | 0° 8°       |      |  |

June 2009 Giving you the edge PCS1P2192A

rev 1.0

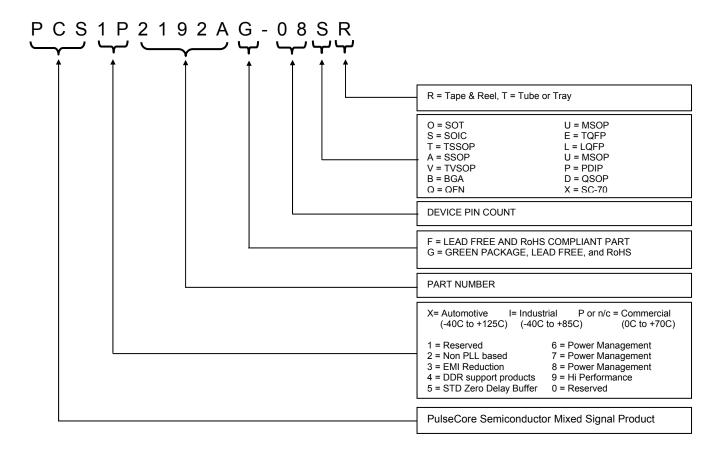

#### **Ordering Code**

| Part Number      | Marking      | Package Type                   | Temperature * |

|------------------|--------------|--------------------------------|---------------|

| PCS1P2192AG-08ST | PCS 1P2192AG | 8-Pin SOIC, TUBE, Green        | Commercial    |

| PCS1P2192AG-08SR | PCS 1P2192AG | 8-Pin SOIC, TAPE & REEL, Green | Commercial    |

<sup>\*</sup>VDP commercial temperature range (0°C to +85°C)

# **Device Ordering Information**

www.DataSheet4U.com

Licensed under U.S Patent Nos 5,488,627 and 5,631,921

June 2009 Giving you the edge PCS1P2192A

rev 1.0

PulseCore Semiconductor Corporation 2105 S. Bascom Ave Suite 210 Campbell, CA 95008 Tel: 408-879-9077

Fax: 408-879-9018 www.pulsecoresemi.com Copyright © PulseCore Semiconductor All Rights Reserved Part Number: PCS1P2192A Document Version: 1.0

Note: This product utilizes US Patent # 6,646,463 Impedance Emulator Patent issued to PulseCore Semiconductor, dated 11-11-2003

Many PulseCore Semiconductor products are protected by issued patents or by applications for patent

© Copyright 2006 PulseCore Semiconductor Corporation. All rights reserved. Our logo and name are trademarks or registered trademarks of PulseCore Semiconductor. All other brand and product names may be the trademarks of their respective companies. PulseCore reserves the right to make changes to this document and its products at any time without notice. PulseCore assumes no responsibility for any errors that may appear in this document. The data contained herein represents PulseCore's best data and/or estimates at the time of issuance. PulseCore reserves the right to change or correct this data at any time, without notice. If the product described herein is under development, significant changes to these specifications are possible. The information in this product data sheet is intended to be general descriptive information for potential customers and users, and is not intended to operate as, or provide, any guarantee or warrantee to any user or customer. PulseCore does not assume any responsibility or liability arising out of the application or use of any product described herein, and disclaims any express or implied warranties related to the sale and/or use of PulseCore products including liability or warranties related to fitness for a particular purpose, merchantability, or infringement of any intellectual property rights, except as express agreed to in PulseCore's Terms and Conditions of Sale (which are available from PulseCore). All sales of PulseCore products are made exclusively according to PulseCore's Terms and Conditions of Sale. The purchase of products from PulseCore does not convey a license under any patent rights, copyrights; mask works rights, trademarks, or any other intellectual property rights of PulseCore or third parties. PulseCore does not authorize its products for use as critical components in life-supporting systems where a malfunction or failure may reasonably be expected to result in significant injury to the user, and the inclusion of PulseCore products in such life-supporting systems implies that the manufacturer assumes all risk of such use and agrees to indemnify PulseCore against all claims arising from such use.

VDP Multiple Pixel Clock Generator