# **Multi-Output Clock Synthesizer**

#### **Features**

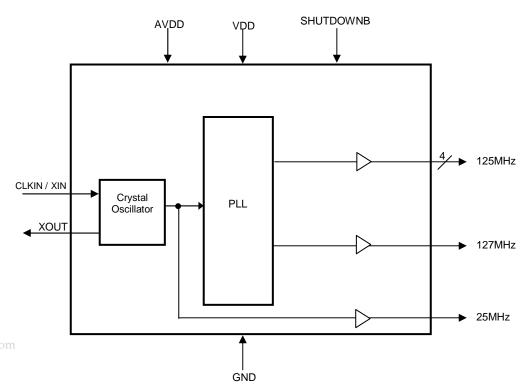

- Generates multiple clock outputs from an inexpensive 25MHz crystal or external reference clock

- Frequency outputs:

- o 25MHz Reference clock

- o 125MHz

- o 127MHz

- Zero ppm frequency synthesis error for all CLK outputs

- 3.3V ± 5%V Supply Voltage

- Low jitter design

- Packaged in 16-pin TSSOP

- Compatible with CY22393XC-MZ2

- Advanced CMOS process

## **Product Description**

The PCS1P2860A is a Precision multi-PLL based frequency synthesizer. Six Clock outputs are generated using an inexpensive 25MHz Crystal or external reference clock. The outputs consist of 25MHz Refout, 127MHz and four 125MHz clocks. SHUTDOWNB signal tri-states all the clocks when enabled. The device operates from a Supply Voltage of 3.3V ± 5%V. The device is available in a 16-pin TSSOP JEDEC package.

#### **Application**

PCS1P2860A is targeted for use in high-end multimedia, communications and consumer applications.

### **Block Diagram**

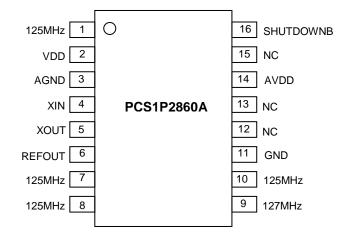

# Pin Diagram

#### **Pin Description**

| Pin# | Pin Name  | Pin Type | Pin Description                                                                                                    |  |  |  |

|------|-----------|----------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1    | 125MHz    | Output   | 125MHz Clock Output.                                                                                               |  |  |  |

| 2    | VDD       | Power    | Connect to +3.3V.                                                                                                  |  |  |  |

| 3    | AGND      | Power    | Connect to ground.                                                                                                 |  |  |  |

| 4    | XIN       | Input    | Crystal connection or external reference frequency input. It can be connected a 25MHz Fundamental mode crystal.    |  |  |  |

| 5    | XOUT      | Output   | Connection to crystal. If using an external reference clock, this pin must be left unconnected.                    |  |  |  |

| 6    | REFOUT    | Output   | 25MHz Reference Clock output.                                                                                      |  |  |  |

| 7    | 125MHz    | Output   | 125MHz Clock Output.                                                                                               |  |  |  |

| 8    | 125MHz    | Output   | 125MHz Clock Output.                                                                                               |  |  |  |

| 9    | 127MHz    | Output   | 127MHz Clock Output.                                                                                               |  |  |  |

| 10   | 125MHz    | Output   | 125MHz Clock Output.                                                                                               |  |  |  |

| 11   | GND       | Power    | Connect to ground.                                                                                                 |  |  |  |

| 12   | NC        |          | No connection.                                                                                                     |  |  |  |

| 13   | NC        |          | No connection.                                                                                                     |  |  |  |

| 14   | AVDD      | Power    | Connect to +3.3V.                                                                                                  |  |  |  |

| 15   | NC        |          | No connection.                                                                                                     |  |  |  |

| 16   | SHUTDOWNB | Input    | Output Enable bit. When this pin is made HIGH, all clocks are enabled. Tri-states all clocks when this pin is LOW. |  |  |  |

www.DataSheet4U.com

**Absolute Maximum Ratings**

| Symbol                                                                                                                                                                        | Parameter                                     | Rating          | Unit |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------|------|--|--|

| VDD                                                                                                                                                                           | Power Supply Voltage relative to Ground       | -0.5 to +4.6    | V    |  |  |

| V <sub>IN</sub>                                                                                                                                                               | Input Voltage relative to Ground (Input Pins) | -0.5 to VDD+0.3 | V    |  |  |

| T <sub>STG</sub>                                                                                                                                                              | Storage temperature                           | -65 to +150     | C    |  |  |

| Ts                                                                                                                                                                            | Max. Soldering Temperature (10 sec)           | 260             | C    |  |  |

| TJ                                                                                                                                                                            | Junction Temperature                          | 125             | C    |  |  |

| T <sub>DV</sub>                                                                                                                                                               | Static Discharge Voltage                      | 2               | KV   |  |  |

|                                                                                                                                                                               | (As per JEDEC STD22- A114-B)                  |                 |      |  |  |

| Note: These are stress ratings only and are not implied for functional use. Exposure to absolute maximum ratings for prolonged periods of time may affect device reliability. |                                               |                 |      |  |  |

**Operating Conditions**

| Parameter       | Description                                 | Min   | Тур | Max   | Unit |

|-----------------|---------------------------------------------|-------|-----|-------|------|

| VDD / AVDD      | Operating Voltage                           | 3.135 | 3.3 | 3.465 | V    |

| T <sub>A</sub>  | Operating Temperature (Ambient Temperature) | 0     |     | 70    | C    |

| $C_L$           | Load Capacitance                            |       |     | 15    | pF   |

| C <sub>IN</sub> | Input Capacitance                           |       | 5   |       | pF   |

## **DC Electrical Characteristics**

| Symbol Parameter |                          | Conditions                             | Min     | Тур | Max     | Units |

|------------------|--------------------------|----------------------------------------|---------|-----|---------|-------|

| VDD / AVDD       | Operating Voltage        |                                        | 3.135   | 3.3 | 3.465   | V     |

| VIH              | Input High Voltage       |                                        | 2.2     |     | VDD+0.3 | V     |

| VIL              | Input Low Voltage        |                                        | GND-0.3 |     | 1.0     | V     |

| lін              | Input HIGH current       | VIN = VDD                              |         |     | 30      | μA    |

| lı∟              | Input LOW current        | VIN = GND                              |         |     | 50      | μA    |

| Voн              | Output High Voltage      | VDD = 3.135, IOH = -12mA               | 2.4     |     |         | V     |

| Vol              | Output Low Voltage       | VDD = 3.135, IoL = 12mA                |         |     | 0.4     | V     |

| loz              | Output Leakage Current   | Three-state outputs                    |         |     | 10      | μA    |

| Icc              | Static Current           | CLKIN and SHUTDOWNB<br>Pins pulled low |         |     | 5.5     | mA    |

| IDD              | Dynamic Current          | No Load, All Clocks on                 |         | 35  |         | mA    |

| Zout             | Nominal output impedance |                                        |         | 30  |         | Ω     |

www.DataSheet4U.com

#### **AC Electrical Characteristics**

| Symbol                       | Parameter                                         |                 |     | Тур | Max | Unit |

|------------------------------|---------------------------------------------------|-----------------|-----|-----|-----|------|

| CLKIN / XIN                  | Input Frequency                                   | Input Frequency |     | 25  |     | MHz  |

|                              | Output Frequency Pin 6 Pin 1,7,8,10 Pin 9         | Pin 6           |     | 25  |     | MHz  |

| CLK OUT                      |                                                   | Pin 1,7,8,10    |     | 125 |     |      |

|                              |                                                   | Pin 9           |     | 127 |     |      |

| t <sub>LH</sub> <sup>1</sup> | Rising edge slew rate (Measured from 20% to 80%)  |                 | 1.1 | 1.7 |     | V/nS |

| t <sub>HL</sub> 1            | Falling edge slew rate (Measured from 80% to 20%) |                 | 1.3 | 2   |     | V/nS |

| T <sub>PJ</sub> <sup>1</sup> | Peak-to-peak Period Jitter @ VDD/2                |                 |     | 300 |     | pS   |

|                              | Synthesis Error (Output Frequency)                |                 |     | 0   |     | ppm  |

| t <sub>D</sub> <sup>1</sup>  | Output Duty Cycle @ VDD/2                         |                 | 45  | 50  | 55  | %    |

| tLOCK                        | PLL Lock Time from Pow                            | er-Up           |     |     | 3   | mS   |

NOTE: 1. CL= 15pF for outputs < 100MHz; CL = 10pF for outputs > 100MHz;

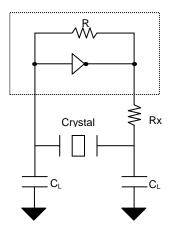

# **Typical Crystal Specifications**

| Fundamental AT cut parallel resonant crystal |                           |  |  |  |  |

|----------------------------------------------|---------------------------|--|--|--|--|

| Nominal frequency                            | 25MHz                     |  |  |  |  |

| Frequency tolerance                          | ± 50 ppm or better at 25℃ |  |  |  |  |

| Operating temperature range                  | -25℃ to +85℃              |  |  |  |  |

| Storage temperature                          | -40℃ to +85℃              |  |  |  |  |

| Load capacitance(C <sub>P</sub> )            | 18pF                      |  |  |  |  |

| Shunt capacitance                            | 7pF maximum               |  |  |  |  |

| ESR                                          | 25 Ω                      |  |  |  |  |

Note: Note: C<sub>L</sub> is Load Capacitance and Rx is used to prevent oscillations at overtone frequency of the Fundamental frequency.

# **Typical Crystal Interface Circuit**

$$\begin{split} C_L &= 2^*(C_P - C_S), \\ Where \ C_P &= Load \ capacitance \ of \ crystal \\ C_S &= Stray \ capacitance \ due \ to \ C_{IN,} \ PCB, \ Trace \ etc. \end{split}$$

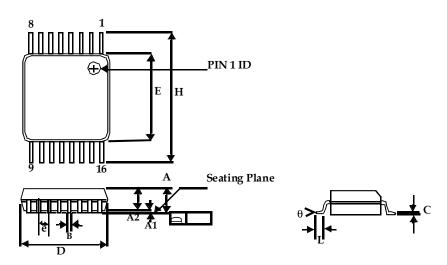

# **Package Information**

# 16-lead Thin Shrunk Small Outline Package (4.40-MM Body)

|        | Dimensions |       |             |      |  |

|--------|------------|-------|-------------|------|--|

| Symbol | Inch       | nes   | Millimeters |      |  |

|        | Min        | Max   | Min         | Max  |  |

| Α      |            | 0.043 |             | 1.20 |  |

| A1     | 0.002      | 0.006 | 0.05        | 0.15 |  |

| A2     | 0.031      | 0.041 | 0.80        | 1.05 |  |

| В      | 0.007      | 0.012 | 0.19        | 0.30 |  |

| С      | 0.004      | 0.008 | 0.09        | 0.20 |  |

| D      | 0.193      | 0.201 | 4.90        | 5.10 |  |

| E      | 0.169      | 0.177 | 4.30        | 4.50 |  |

| е      | 0.026 BSC  |       | 0.65 BSC    |      |  |

| Н      | 0.252 BSC  |       | 6.40 BSC    |      |  |

| L      | 0.020      | 0.030 | 0.50        | 0.75 |  |

| θ      | 0°         | 8°    | 0°          | 8°   |  |

www.DataSheet4U.com

**Ordering Information**

| Part Number      | Marking     | Package                          | Temperature |

|------------------|-------------|----------------------------------|-------------|

| PCS1P2860AG-16TR | 1P28<br>60A | 16-Pin TSSOP, TAPE & REEL, Green | 0℃ to +70℃  |

A "microdot" placed at the end of last row of marking or just below the last row toward the center of package indicates Pb-free.

Licensed under US patent #5,488,627 and #5,631,920.

Note: This product utilizes US Patent #6,646,463 Impedance Emulator Patent issued to PulseCore Semiconductor, dated 11-11-2003.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. U.S Patent Pending; Timing-Safe and Active Bead are trademarks of PulseCore Semiconductor, a wholly owned subsidiary of ON Semiconductor. This literature is subject to all applicable copyright laws

#### PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA **Phone:** 303-675-2175 or 800-344-3860 Toll Free LISA/Coada

USA/Canada

Fax: 303-675-2176 or 800-344-3867 Toll Free

USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center

Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your

local Sales Representative