# PCS3P7101A

## Low Power Peak EMI Reducing clock synthesizer

www.DataSheet4U.com

### Features

- Generates a 4x low EMI clock at the output

- Input frequency: 25 MHz

- Integrated loop filter components.

- Frequency deviation: ±0.25% (Typ) center spread

- Operates with a 3.3V Supply.

- Low power CMOS design.

- Available in 8-pin SOIC package.

- Pin compatible with ICS 341-22

### **Product Description**

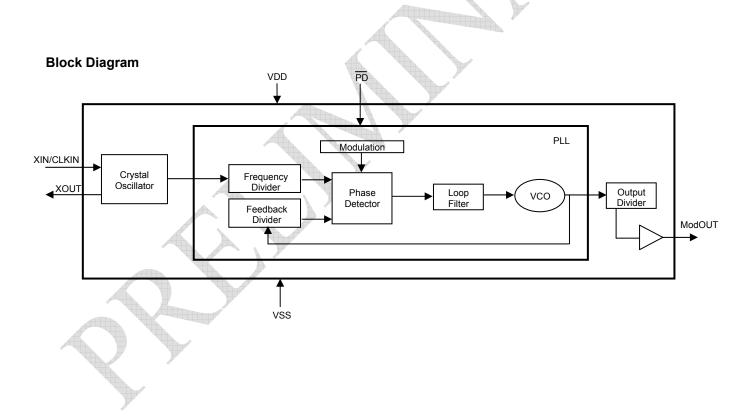

The PCS3P7101A is a low cost, single-output, clock synthesizer. The PCS3P7101A generates a 4x output clock from a 25 MHz standard fundamental mode, inexpensive crystal, or clock. It can replace multiple crystals and oscillators, saving valuable board space and cost. The device employs Spread Spectrum technique to reduce system electro-magnetic interference (EMI).

The device also has a power-down feature that tri-state the clock output and turns off the PLL when the  $\overline{\text{PD}}$  pin is taken low.

PulseCore Semiconductor Corporation 1715 S. Bascom Ave Suite 200, Campbell, CA 95008 • Tel: 408-879-9077 • Fax: 408 WWW.DataSheet4U.com www.pulsecoresemi.com

PCS3P7101A

## rev 0.1 Pin Configuration

CLKIN/XIN 1 VDD 2 VSS 3 NC 4 8 XOUT 7 PD 6 NC 5 ModOUT

#### **Pin Description**

| Fill Description |           |      |                                                                                                                                                                             |  |  |  |

|------------------|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin #            | Pin Name  | Туре | Description                                                                                                                                                                 |  |  |  |

| 1                | CLKIN/XIN | Ι    | Crystal connection or external reference frequency input. This pin has dual functions. It can be connected either to an external crystal or to an external reference clock. |  |  |  |

| 2                | VDD       | Р    | Power supply for the entire chip.                                                                                                                                           |  |  |  |

| 3                | VSS       | Р    | Ground connection                                                                                                                                                           |  |  |  |

| 4                | NC        | -    | No Connection                                                                                                                                                               |  |  |  |

| 5                | ModOUT    | 0    | Spread spectrum low EMI 4x clock output.                                                                                                                                    |  |  |  |

| 6                | NC        | -    | No Connection                                                                                                                                                               |  |  |  |

| 7                | PD        | Ι    | Powers down entire chip. Tri-states CLK outputs when low. Has an Internal pull-up resistor.                                                                                 |  |  |  |

| 8                | XOUT      | 0    | Crystal connection. If using an external reference, this pin must be left unconnected                                                                                       |  |  |  |

## **Absolute Maximum Ratings**

| Symbol                         | Parameter                                 | Rating       | Unit |

|--------------------------------|-------------------------------------------|--------------|------|

| $V_{\text{DD}}, V_{\text{IN}}$ | Voltage on any pin with respect to Ground | -0.5 to +4.6 | V    |

| T <sub>STG</sub>               | Storage temperature                       | -65 to +125  | °C   |

| T <sub>A</sub>                 | Operating temperature                     | 0 to +70     | °C   |

| Ts                             | Max. Soldering Temperature (10 sec)       | 260          | °C   |

| TJ                             | Junction Temperature                      | 150          | °C   |

| T <sub>DV</sub>                | Static Discharge Voltage                  | 2            | КV   |

| D.                             | (As per JEDEC STD 22- A114-B)             |              |      |

Recommended Operating Conditions<sup>1</sup>

|                                                | Min                                     | Тур | Max | Unit |    |

|------------------------------------------------|-----------------------------------------|-----|-----|------|----|

| Supply voltage, V <sub>DD</sub>                |                                         |     | 3.3 | 3.45 | V  |

| Low-level input voltage, VIL                   | V <sub>DD</sub> = 3.15V to3.45V         | -   | -   | 0.8  | V  |

| High-level input voltage, $V_{IH}$             | V <sub>DD</sub> = 3.15V to3.45V         | 2   | -   | -    | V  |

| High-level output current, I <sub>OH</sub>     | V <sub>DD</sub> = 3.15V to3.45V         | -   | -   | 12   | mA |

| Low-level output current, IOL                  | -                                       | -   | 12  | mA   |    |

| Operating free-air temperature, T <sub>A</sub> |                                         |     | -   | 70   | °C |

| Note:1 Unused inputs must be held hig          | h or low to prevent them from floating. |     |     |      |    |

# PCS3P7101A

## rev 0.1

#### **DC Electrical Characteristics**

| Symbol           | Param                       | eter       | Min  | Тур       | Maxww.I | aUnite 4 |

|------------------|-----------------------------|------------|------|-----------|---------|----------|

| V <sub>IL</sub>  | Input low voltage           | VSS - 0.3  | -    | 0.8       | V       |          |

| VIH              | Input high voltage          | 2.0        | -    | VDD + 0.5 | V       |          |

| IIL              | Input low current           | -          | -    | -35       | μA      |          |

| I <sub>IH</sub>  | Input high current          | -          | -    | 35        | μA      |          |

| V <sub>OL</sub>  | Output low voltage (VDD = 3 | -          | -    | 0.4       | V       |          |

| V <sub>OH</sub>  | Output high voltage (VDD =  | 2.4        | -    | -         | V       |          |

| I <sub>DD</sub>  | Static supply current*      |            | -    | 50        |         | uA       |

| I <sub>CC</sub>  | Dynamic supply current (3.3 | -          | TBD  | -         |         |          |

| VDD              | Operating voltage           |            | 3.15 | 3.3       | 3.45    | V        |

| Z <sub>OUT</sub> | Output impedance            |            | -    | 20        | -       | Ω        |

| CIN              | Input Capacitance           |            | -    | 4         | _       | pF       |

| Rpd              | Internal pull-up resistor   | PD         | -    | 250       | -       | ΚΩ       |

| Rpup             |                             | CLK output | -    | 525       | -       | kΩ       |

## AC Electrical Characteristics for 3.3V Supply

| Symbol Parameter  |                                                     | Min | Тур | Мах | Unit |

|-------------------|-----------------------------------------------------|-----|-----|-----|------|

| CLKIN/XIN         | Input frequency                                     | -   | 25  | -   | MHz  |

| ModOUT            | Output frequency                                    | -   | 100 | -   | MHz  |

| t <sub>LH</sub> * | Output rise time (measured from 0.8 to 2.0V)        | -   | 1   | -   | nS   |

| t <sub>HL</sub> * | Output fall time (measured at 2.0V to 0.8V)         | -   | 1   | -   | nS   |

| t <sub>PU</sub>   | Power-up time( PLL lock time from power-up)         | -   | 4   | 10  | mS   |

| t <sub>ON</sub>   | Power-up time (first locked cycle after power-up)** | -   | 4   | 7   | mS   |

|                   | Synthesis Error(Output Frequency)                   | -   | 0   | -   | ppm  |

| t <sub>JC</sub>   | Jitter (cycle to cycle)                             | -   | TBD | -   | pS   |

| t <sub>JP</sub>   | Period Jitter                                       | -   | TBD | -   | pS   |

| t <sub>D</sub>    | Output duty cycle                                   | 40  | 50  | 60  | %    |

| t <sub>ja</sub>   | Maximum Absolute Jitter                             | -   | TBD | -   | pS   |

$^{*t}_{LH}$  and  $t_{HL}$  are measured into a capacitive load of 15pF  $^{**}V_{DD}$  and XIN/CLKIN input are stable, PD pin is made high from low.

PCS3P7101A

rev 0.1

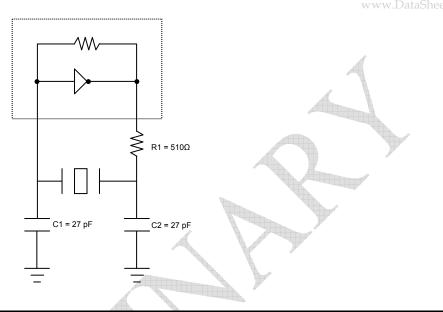

**Typical Crystal Oscillator Circuit**

## **Typical Crystal Specifications**

| Fundamental AT cut parallel resonant crystal |                            |  |  |  |

|----------------------------------------------|----------------------------|--|--|--|

| Nominal frequency                            | 25MHz                      |  |  |  |

| Frequency tolerance                          | ± 50 ppm or better at 25°C |  |  |  |

| Operating temperature range                  | -25°C to +85°C             |  |  |  |

| Storage temperature                          | -40°C to +85°C             |  |  |  |

| Load capacitance                             | 18pF                       |  |  |  |

| Shunt capacitance                            | 7pF maximum                |  |  |  |

| ESR                                          | 25Ω                        |  |  |  |

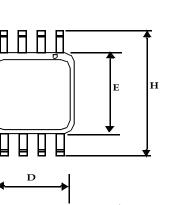

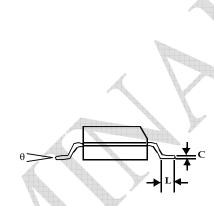

8-Pin SOIC Package

# September 2006

PCS3P7101A

rev 0.1

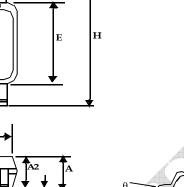

Package Information

|    |             | Dimensions |       |             |      |  |

|----|-------------|------------|-------|-------------|------|--|

|    | Symbol      | Incl       | hes   | Millimeters |      |  |

|    |             | Min        | Max   | Min         | Мах  |  |

| ß  | A1          | 0.004      | 0.010 | 0.10        | 0.25 |  |

| 6  | A           | 0.053      | 0.069 | 1.35        | 1.75 |  |

| -W | A2          | 0.049      | 0.059 | 1.25        | 1.50 |  |

|    | В           | 0.012      | 0.020 | 0.31        | 0.51 |  |

|    | С           | 0.007      | 0.010 | 0.18        | 0.25 |  |

|    | D           | 0.193      | BSC   | 4.90 BSC    |      |  |

|    | E           | 0.154      | BSC   | 3.91 BSC    |      |  |

|    | е           | 0.050      | BSC   | 1.27 BSC    |      |  |

|    | H 0.236 BSC |            |       | 6.00 BSC    |      |  |

|    | L           | 0.016      | 0.050 | 0.41        | 1.27 |  |

|    | θ           | 0°         | 8°    | 0°          | 8°   |  |

PCS3P7101A

rev 0.1

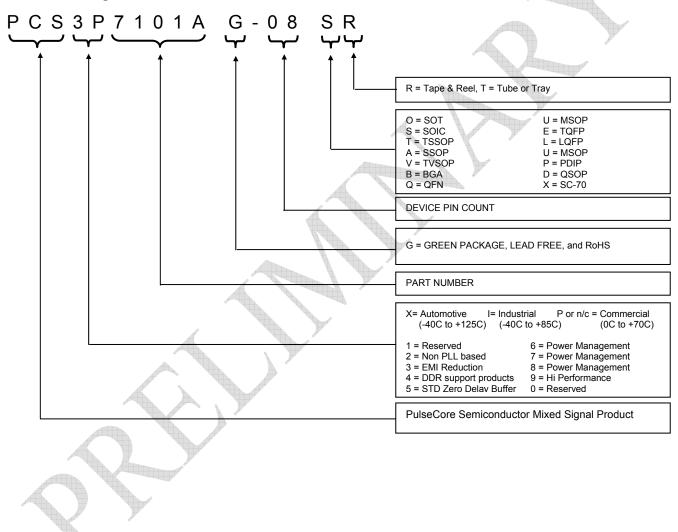

#### **Ordering Information**

www.DataSheet4U.com

| Part Number      | Marking  | Package Type                   | Temperature |

|------------------|----------|--------------------------------|-------------|

| PCS3P7101AG-08SR | 3P7101AG | 8-Pin SOIC, TAPE & REEL, Green | Commercial  |

| PCS3P7101AG-08ST | 3P7101AG | 8-Pin SOIC, TUBE, Green        | Commercial  |

#### **Device Ordering Information**

Licensed under US patent Nos 5,488,627 and 5,631,920.

Low Power Peak EMI Reducing clock synthesizer

www.DataSheet4U.com

# PCS3P7101A

rev 0.1

www.DataSheet4U.com

PulseCore Semiconductor Corporation 1715 S. Bascom Ave Suite 200 Campbell, CA 95008 Tel: 408-879-9077 Fax: 408-879-9018 www.pulsecoresemi.com Copyright © PulseCore Semiconductor All Rights Reserved Part Number: PCS3P7101A Document Version: v0.1

Note: This product utilizes US Patent # 6,646,463 Impedance Emulator Patent issued to PulseCore Semiconductor, dated 11-11-2003

© Copyright 2006 PulseCore Semiconductor Corporation. All rights reserved. Our logo and name are trademarks or registered trademarks of PulseCore Semiconductor. All other brand and product names may be the trademarks of their respective companies. PulseCore reserves the right to make changes to this document and its products at any time without notice. PulseCore assumes no responsibility for any errors that may appear in this document. The data contained herein represents PulseCore's best data and/or estimates at the time of issuance. PulseCore reserves the right to change or correct this data at any time, without notice. If the product described herein is under development, significant changes to these specifications are possible. The information in this product data sheet is intended to be general descriptive information for potential customers and users, and is not intended to operate as, or provide, any guarantee or warrantee to any user or customer. PulseCore does not assume any responsibility or liability arising out of the application or use of any product described herein, and disclaims any express or implied warranties related to the sale and/or use of PulseCore products including liability or warranties related to fitness for a particular purpose, merchantability, or infringement of any intellectual property rights, except as express agreed to in PulseCore's Terms and Conditions of Sale (which are available from PulseCore). All sales of PulseCore products are made exclusively according to PulseCore's Terms and Conditions of Sale. The purchase of products from PulseCore does not convey a license under any patent rights, copyrights; mask works rights, trademarks, or any other intellectual property rights of PulseCore or third parties. PulseCore does not authorize its products for use as critical components in life-supporting systems where a malfunction or failure may reasonably be expected to result in significant injury to the user, and the inclusion of PulseCore products in such life-supporting systems implies that the manufacturer assumes all risk of such use and agrees to indemnify PulseCore against all claims arising from such use.

#### Low Power Peak EMI Reducing clock synthesizer

www.DataSheet4U.com