## TETHYS™ II QUAD STS-192/STM-64 MUX/DEMUX

OCT 2009 REV. 1.0.0

## GENERAL DESCRIPTION

Tethys™ II PEB2756AE is optimized for SONET/SDH applications as a full-duplex Quad (SFI4.2) or Dual (SFI4.1) STS-192/STM-64 MUX/DEMUX with full framer functionality including pointer processing, and overhead termination; ideal for aggregation, ADM and DWDM applications. In the demultiplex ingress direction, Tethys™ II accepts four/two STS-192/STM-64 signals (SFI4.2/SFI-4.1 interfaces), locates the incoming SONET/SDH frame, optionally descrambles the data, monitors the TOH and POH, and provides STS-1 level pointer processing. In addition, Tethys supports TOH and POH overhead transparency.

In the multiplex direction, Tethys™ II PEB2756AE accepts sixteen STS-48/STM-16 signals in serial 2.5 Gbit/s format. Tethys™ II PEB2756AE further provides corresponding functionality in the DEMUX direction.

### **APPLICATIONS**

- ADM

- Metro Aggregation

- Digital Cross Connects

- Repeaters

- DWDM Equipment

- Test Equipment

# **FEATURES**

- Provides 4 SFI4.2 interfaces for STS-192/STM-64 links

- Provides 2 SFI4.1 interfaces for STS-192/STM-64 links

- Differential CML 2.5 G I/O interface to system/backplane

- TFI-5 Support

- Processes SONET/SDH up to 4 STS-192/STM-64 on the line side interface

- Processes SONET/SDH sixteen STS-48/STM-16 on the system/client side serial 2.5 Gbit/s interface

- Provides line timing of all line and system side interfaces

- Processes SONET/SDH flexible concatenation streams of STS-2c, 3c, 4c, ... to 192c

- Supports auto-detection of concatenation streams STS-3c/STM-1, STS-12c/STM-4, STS-48c/STM-16 and STS-192c/STM-64

- Supports STS-1 level pointer processing of STS-192/ STM-64 or STS-48/STM-16 streams

- Provides interfaces for dropping alarm and status information, and for forcing alarm conditions

- Supports system-side input deskew of up to ± 250 ns within a group of 4 x 2.5G GBps for each of four STS-192/STM-64

- Power dissipation of 23 W, depending on mode of operation

- Terminates and generates SONET section, line, and path layers

- Provides TOH and POH transparency

- Provides monitoring of POH bytes B3 and N1/Z5

- Provides B2 SF/SD capability for Poisson and bursty error distribution

- Provides full TOH/POH add/drop

- Provides STS-1 level POH add/drop

- Supports more than ± 746 UI programmable output skew on STS-192/STM-64 or STS-48/STM-16 out-put links to external cross-connects

- For diagnostic purposes, Tethys provides PRBS generator/checker and loop backs

- Provides B1, B2, H1 and H2 bit error generation for both receive and transmit direction diagnostics

- Provides 1 second performance monitors

- Provides B1, B2, H1 and H2 bit error generation for both receive and transmit direction diagnostics

- Provides 1 second performance monitors

- 0.13 micron process, 1.2 V core, 3.3 V I/O

- Motorola 32-bit synchronous microprocessor inter-face for configuration, control, and status monitoring

- Complies with GR-253, GR-1377, ITU-T G.707, and ANSI T1.105

- Provides a standard 5-signal IEEE 1149.1 JTAG test port for boundary scan board test purposes

### **SPECIFICATIONS**

• OIF TFI-5, OIF SFI-4.1, SFI4.2, GR-253-CORE

### ORDERING INFORMATION

| PART NUMBER | PACKAGE   | OPERATING TEMPERATURE RANGE |

|-------------|-----------|-----------------------------|

| PEB2756AE   | 1397 CBGA | -40°C to +85°C              |

REV. 1.0.0

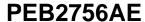

FIGURE 1. PEB2756AE BLOCK DIAGRAM

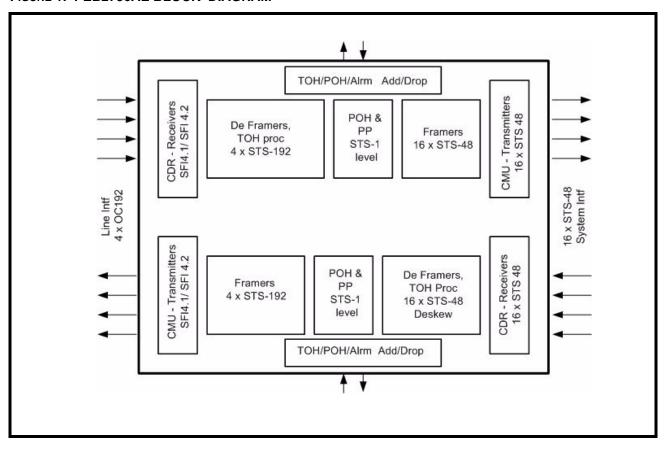

FIGURE 2. PEB2756AE IN DUAL 10G APPLICATION

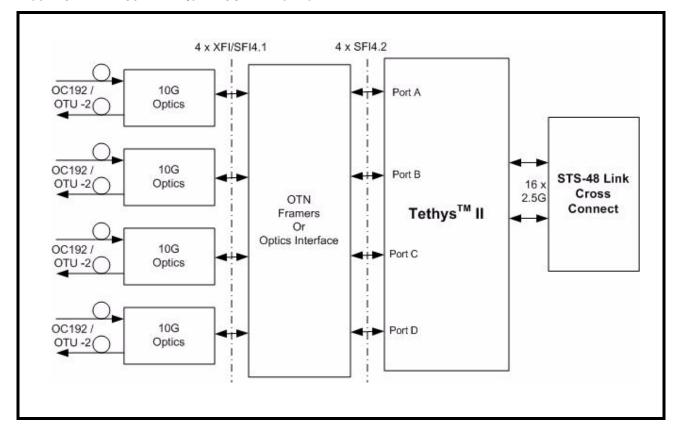

FIGURE 3. PEB2756AE IN QUAD 10G APPLICATION