Data Sheet, DS2, May 2001

TE3-CHATT Channelized T3 Termination with DS3 Framer, M13 Multiplexer, T4/ E1 Framers and 256 Channel HDLC/PPP controller PEB 3456 E Version 2.1

# Datacom

The second secon

Never stop thinking.

Edition 05.2001

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 5/21/01. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# TE3-CHATT Channelized T3 Termination with DS3 Framer, M13 Multiplexer, T1/ E1 Framers and 256 Channel HDLC/PPP controller PEB 3456 E Version 2.1

Datacom

Never stop thinking.

| Revision   | History: 05.2001 DS2                                                                                                                                                                                  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Previous \ |                                                                                                                                                                                                       |

| Major cha  | nges to document since last version                                                                                                                                                                   |

| Page       | Description                                                                                                                                                                                           |

| 27         | Pin Diagram Added                                                                                                                                                                                     |

| 162        | Corrected Part Number from 0076 to 0077.                                                                                                                                                              |

| 208        | Swap the bit positions of TBRTC and TBFTC In the CSPEC_BUFFER register as their bit postitions were not correct in the preliminary data sheet.                                                        |

| 209        | Swap the postions of TBRTC with TBFTC in Table 8-7, as their column positions were not correct in the preliminary data sheet                                                                          |

| 213        | Fixed typo in CSPEC_IMASK register, replaced ROFD with RFOD                                                                                                                                           |

| 243        | Fixed typo in IQMASK, replaced ROFD with RFOD                                                                                                                                                         |

| 256        | Added note to clarify configuration of FDL links 28 and 29.                                                                                                                                           |

| 263        | Added special programming note for reseting D3CLKCS register                                                                                                                                          |

| 268        | Added text to clarify function of TXBIT in D3TCOM                                                                                                                                                     |

| 268        | Reset value of D3TCOM Register was incorrectly documented.                                                                                                                                            |

| 268        | Note added to recommend seting register D3TCOM to 0070 after reset, for normal operation.                                                                                                             |

| 284        | Note added to explain that reset value of D3RSTAT will be different after some time.                                                                                                                  |

| 302        | Note added to explain that reset value of D2RSTAT will be different after some time                                                                                                                   |

| 389        | Update voltage min/max information for Table 9-1 Absolute Maximum Ratings                                                                                                                             |

| 391        | Update timing Information for Table 9-4 DC Characteristics (PCI<br>Interface Pins)                                                                                                                    |

| 392        | Update timing Information for Table 9-5 PCI Clock Characteristics                                                                                                                                     |

| 393        | Update timing Information for Table 9-6 PCI Interface Signal Characteristics                                                                                                                          |

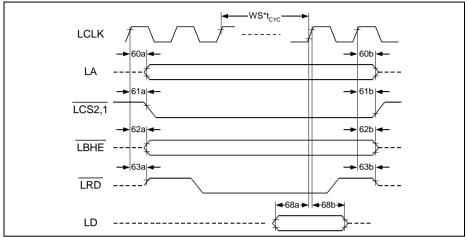

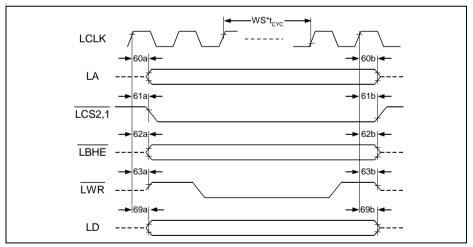

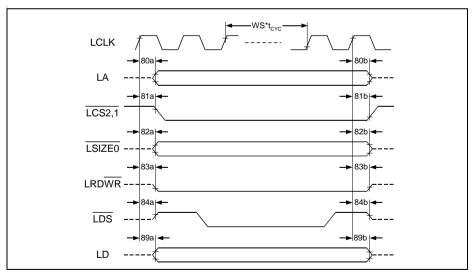

| 396        | Update timing Information for Table 9-8 Intel Bus Interface Timing                                                                                                                                    |

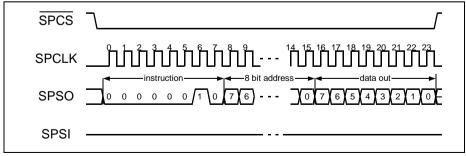

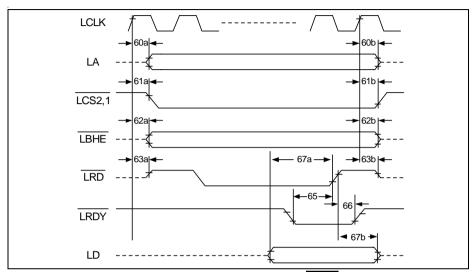

| 397        | Intel Bus Interface Timing Diagram modified. The setup and hold times for<br>"LD to LRDY" was not a valid timing parameter. Instead, the setup and hold<br>parameters for "LD to LRD" were specified. |

|      | History:05.2001DSVersion:Preliminary Data Sheet 11.1999nges to document since last version                               | 2    |

|------|--------------------------------------------------------------------------------------------------------------------------|------|

| Page | Description                                                                                                              |      |

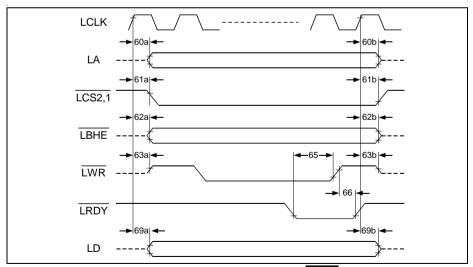

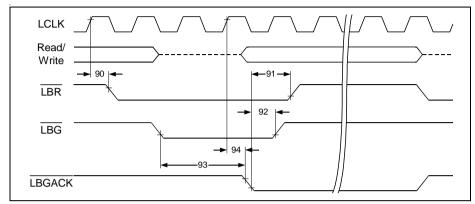

| 399  | Update timing Information for Table 9-9 Intel Bus Interface Timing (Master Mode)                                         |      |

| 399  | Timing parameter (setup time) 67a was changed from "LD to LDRY" to to LRD", because it was not a valid timing parameter. | "LD  |

| 399  | Timing parameter (hold time) 67b was changed from "LD to LDRY" to to LRD", because it was not a valid timing parameter.  | "LD  |

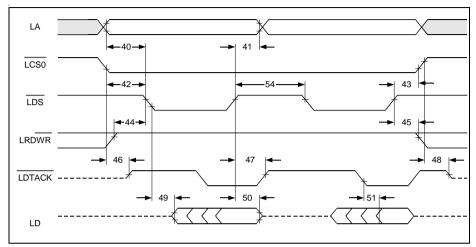

| 401  | Update timing Information for Table 9-10 Motorola Bus Interface Tir                                                      | ning |

| 404  | Update timing Information for Table 9-11 Motorola Bus Interface Tin<br>(Master Mode)                                     | ning |

| 407  | Update timing Information for Table 9-13 DS3 Transmit Cycle Timi                                                         | ng   |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

# Preface

The Channelized T3 Termination with DS3 Framer, M13 Multiplexer, T1/E1 Framers and 256 Channel HDLC/PPP controller is a Multichannel Protocol Controller for a wide area of telecommunication and data communication applications.

## **Organization of this Document**

This Data Sheet is divided into ten chapters and is organized as follows:

## Chapter 1 TE3-CHATT Overview

Gives a general description of the product and its family, lists the key features, and presents some typical applications

#### Chapter 2 Pin Description

Lists pin locations with associated signals, categorizes signals according to function, and describes signals.

#### Chapter 3 General Overview

This chapter provides short descriptions of all the internal functional blocks.

#### Chapter 4 Functional Description

Gives a detailed description of all functions

#### Chapter 5 Interface Description

This chapter provides functional diagrams of all interfaces.

## Chapter 6 Channel Programming / Reprogramming Concept

This chapter provides a detailed description of the channel programming concept.

- Chapter 7 Reset and Initialization procedure Gives examples of the initialzation procedure and operation.

- Chapter 8 Register Description

Gives a detailed description of all on-chip registers.

Chapter 9 Electrical Characteristics

Data Sheet

Gives a detailed description of all electrical DC and AC characteristics, and provides timing diagrams for all interfaces.

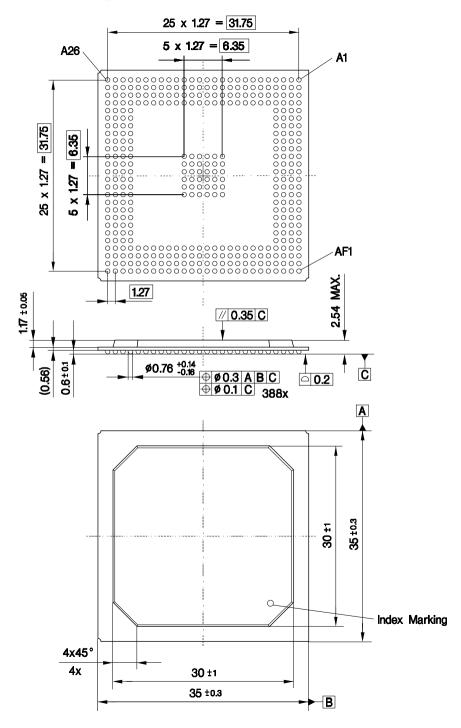

• Chapter 10 Package Outline.

Shows the mechanical values of the device package.

#### **Table of Contents**

#### Page

|                                                                                                                                           | Contents r                                                                                                                                                                                                                                                                                                                                                                                                                                                | aye                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>1.1<br>1.1.1<br>1.1.2<br>1.1.3<br>1.1.4<br>1.1.5<br>1.1.6<br>1.1.7<br>1.2<br>1.3                                                     | TE3-CHATT Overview         General Features         M12 Multiplexer and DS2 Framer         M23 Multiplexer and DS3 Framer         Frame Alignment T1 Features         Signaling Controller T1 Features         Frame Alignment E1 Features         Signaling Controller E1 Features         Bit Error Rate Tester         Logic Symbol         General System Integration                                                                                 | . 22<br>. 23<br>. 24<br>. 24<br>. 24<br>. 24<br>. 24<br>. 24<br>. 25                                                                                                   |

| <b>2</b><br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8                                                                          | Pin Description         Pin Diagram         Pin Definition and functions         PCI Bus Interface         SPI Interface         Local Microprocessor Interface         Serial Interface         Test Interface         Power Supply, Reserved Pins and No-connect Pins                                                                                                                                                                                   | . 27<br>. 28<br>. 29<br>. 35<br>. 36<br>. 39<br>. 44                                                                                                                   |

| <b>3</b><br>3.1<br>3.2<br>3.3<br>3.4                                                                                                      | General Overview<br>Functional Overview<br>Block Diagram<br>Internal Interface<br>Block Description                                                                                                                                                                                                                                                                                                                                                       | . 47<br>. 48<br>. 48                                                                                                                                                   |

| <b>4</b><br>4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.2<br>4.2.1<br>4.2.2<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.3.7 | Functional Description         Port Handler         Local Port Loop         Remote Line Loops         Test Breakout         Time slot Handler         Channelized Modes         Unchannelized Mode         Data Management Unit         Descriptor Concept         Receive Descriptor         Data Management Unit Receive         Transmit Descriptor         Data Management Unit Transmit         Byte Swapping         Transmission Bit/Byte Ordering | <ul> <li>53</li> <li>54</li> <li>54</li> <li>56</li> <li>56</li> <li>56</li> <li>58</li> <li>59</li> <li>60</li> <li>64</li> <li>66</li> <li>69</li> <li>71</li> </ul> |

| Table of | Contents                                                | Page |

|----------|---------------------------------------------------------|------|

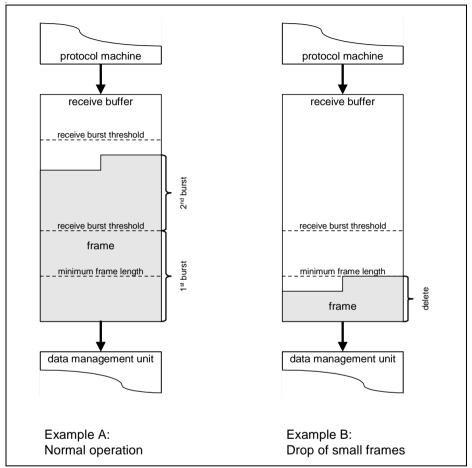

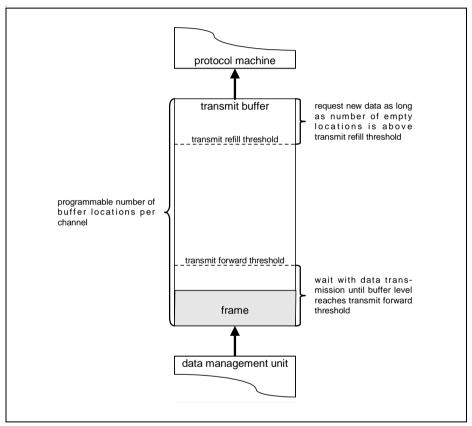

| 4.4      | Buffer Management                                       | 72   |

| 4.4.1    | Internal Receive Buffer                                 | 72   |

| 4.4.2    | Internal Transmit Buffer                                | 74   |

| 4.5      | Protocol Description                                    | 76   |

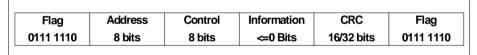

| 4.5.1    | HDLC Mode                                               | 76   |

| 4.5.2    | Bit Synchronous PPP with HDLC Framing Structure         | 77   |

| 4.5.3    | Octet Synchronous PPP                                   |      |

| 4.5.4    | Transparent Mode                                        | 78   |

| 4.6      | T1 Framer and FDL Function                              | 78   |

| 4.6.1    | 4-Frame Multiframe                                      | 79   |

| 4.6.2    | ESF Mode                                                | 80   |

| 4.6.2.1  | Multiframe Synchronization Procedure of the Receiver    | 81   |

| 4.6.2.2  | CRC-6 Generation / Check according to ITU-T G.706       | 81   |

| 4.6.2.3  | Remote Alarm (Yellow Alarm) Generation / Detection      | 82   |

| 4.6.2.4  | Facility Data Link                                      | 82   |

| 4.6.3    | SF Mode                                                 | 85   |

| 4.6.3.1  | Synchronization Procedure of the Receiver               | 85   |

| 4.6.3.2  | Remote Alarm (Yellow Alarm) Generation / Detection      |      |

| 4.6.4    | Common Features for SF and ESF                          |      |

| 4.6.4.1  | AIS (Blue Alarm) Generation/Detection                   | 87   |

| 4.6.4.2  | Loss of Signal (Red Alarm) Detection                    |      |

| 4.6.4.3  | In-Band Loop Generation and Detection                   | 88   |

| 4.6.4.4  | Pulse Density Detection                                 |      |

| 4.6.4.5  | Error Performance Monitoring                            |      |

| 4.6.4.6  | Pseudo-random Bit Sequence Generator and Monitor        |      |

| 4.7      | E1 Framing and Signaling                                |      |

| 4.7.1    | Doubleframe Format                                      |      |

| 4.7.1.1  | Synchronization Procedure of the Receiver               |      |

| 4.7.1.2  | A-bit Access                                            |      |

| 4.7.1.3  | Sa-bit Access                                           |      |

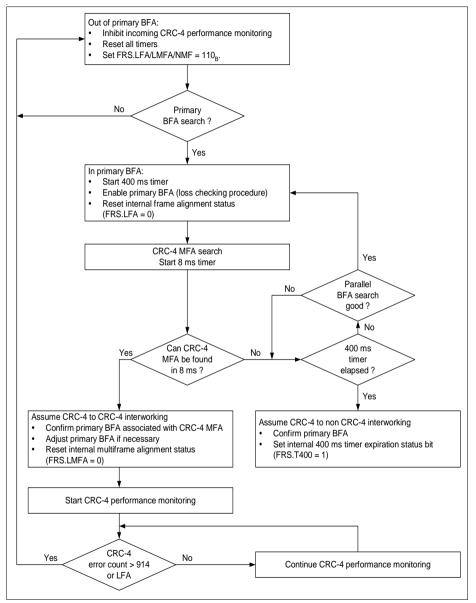

| 4.7.2    | CRC-4 Multiframe                                        |      |

| 4.7.2.1  | Synchronization Procedure of the Receiver               |      |

| 4.7.2.2  | CRC-4 Performance Monitoring                            |      |

| 4.7.2.3  | A-Bit Access                                            |      |

| 4.7.2.4  | Sa-bit Access                                           |      |

| 4.7.2.5  | E-Bit Access                                            |      |

| 4.7.3    | Common Features for E1 Doubleframe and CRC-4 Multiframe |      |

| 4.7.3.1  | Error Performance Monitoring and Alarm Handling         |      |

| 4.7.3.2  | Loss of Signal Detection                                |      |

| 4.7.3.3  | In-Band Loop Generation and Detection                   |      |

| 4.7.3.4  | Pseudo-random Bit Sequence Generator and Monitor        |      |

| 4.8      | Signaling Controller Protocol Modes                     | 101  |

| Tabl |    | of  | Contents |

|------|----|-----|----------|

| Tab  | e. | OI. | Contents |

|          |                                              | 3-  |

|----------|----------------------------------------------|-----|

| 4.8.1    | HDLC Mode                                    | 101 |

| 4.8.2    | Transparent Mode                             |     |

| 4.8.3    | BOM Mode                                     | 103 |

| 4.8.4    | Sa-bit Access                                |     |

| 4.8.5    | Signalling Controller FIFO Operations        |     |

| 4.9      | M12 Multiplexer/Demultiplexer and DS2 framer | 108 |

| 4.9.1    | M12 multiplex format                         | 108 |

| 4.9.1.1  | Synchronization Procedure                    | 109 |

| 4.9.1.2  | Multiplexer/Demultiplexer                    | 110 |

| 4.9.1.3  | Loopback Control                             | 110 |

| 4.9.1.4  | Alarm Indication Signal                      | 110 |

| 4.9.2    | ITU-T G.747 format                           | 111 |

| 4.9.2.1  | Synchronization Procedure                    | 111 |

| 4.9.2.2  | Multiplexer/Demultiplexer                    | 111 |

| 4.9.2.3  | Parity Bit                                   | 112 |

| 4.9.2.4  | Remote Alarm Indication                      | 112 |

| 4.9.2.5  | Alarm Indication Signal                      |     |

| 4.10     | M23 multiplexer and DS3 framer               |     |

| 4.10.1   | M23 multiplex format                         | 113 |

| 4.10.1.1 | Synchronization Procedure                    | 114 |

| 4.10.1.2 | Multiplexer/Demultiplexer                    |     |

| 4.10.1.3 | X-bit                                        |     |

| 4.10.1.4 | Alarm Indication Signal, Idle Signal         | 114 |

| 4.10.1.5 | Loss of Signal                               | 115 |

| 4.10.1.6 | Performance Monitor                          | 115 |

| 4.10.2   | C-bit parity format                          |     |

| 4.10.2.1 | Synchronization Procedure                    | 117 |

| 4.10.2.2 | Multiplexer/Demultiplexer                    |     |

| 4.10.2.3 | X-bit                                        |     |

| 4.10.2.4 | Far End Alarm and Control Channel            | 118 |

| 4.10.2.5 | Path Maintenance Data Link Channel           | 118 |

| 4.10.2.6 | Loopback Control                             | 118 |

| 4.10.2.7 | Alarm Indication Signal, Idle Signal         |     |

| 4.10.2.8 | Loss of Signal                               |     |

| 4.10.2.9 | Performance Monitor                          | 119 |

| 4.10.3   | Full Payload Rate Format                     | 120 |

| 4.11     | Test Unit                                    |     |

| 4.12     | Mailbox                                      | 121 |

| 4.13     | Interrupt Controller                         |     |

| 4.13.1   | Layer Two interrupts                         |     |

| 4.13.1.1 | General Interrupt Vector Structure           |     |

| 4.13.1.2 | System Interrupts                            |     |

|          | · ·                                          |     |

| 4.13.1.3<br>4.13.1.4<br>4.13.1.5<br>4.13.2<br>4.13.2.1<br>4.13.2.2<br>4.13.2.3<br>4.13.2.3<br>4.13.2.4<br>4.13.2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Port Interrupts<br>Channel Interrupts<br>Command Interrupts<br>Layer One Interrupts<br>General Interrupt Vector Structure<br>T1/E1 Framer Interrupts<br>Facility Data Link Interrupts<br>DS3, DS2 and Test Unit Interrupts<br>Mailbox Interrupts                                                                                                                           | 128<br>130<br>135<br>137<br>138<br>139<br>141<br>143<br>146                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| <b>5</b><br>5.1<br>5.1.1<br>5.2<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.3<br>5.3<br>5.3.1<br>5.3.1.1<br>5.3.1.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.1<br>5.3.1<br>5.3.1<br>5.3.2<br>5.3.2<br>5.3.1<br>5.3.2<br>5.3.2<br>5.3.1<br>5.3.2<br>5.3.1<br>5.3.2<br>5.3.1<br>5.3.2<br>5.3.1<br>5.3.2<br>5.3.1<br>5.3.2<br>5.3.1<br>5.3.2<br>5.3.1<br>5.3.2<br>5.3.1<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.2<br>5.3.5<br>5.3.5<br>5.3.5<br>5.5<br>5.5<br>5.5<br>5.5<br>5.5<br>5 | Interface Description<br>PCI Interface<br>PCI Read Transaction<br>PCI Write Transaction<br>SPI Interface (ROM Load Unit)<br>Accesses to a SPI EEPROM<br>SPI Read Sequence<br>SPI Write Sequence<br>Local Microprocessor Interface<br>Intel Mode<br>Slave Mode<br>Master Mode<br>Motorola Mode<br>Slave Mode<br>Master Mode<br>Master Mode<br>Master Mode<br>JTAG Interface | 147<br>147<br>148<br>149<br>150<br>150<br>151<br>152<br>153<br>153<br>153<br>156<br>156<br>156<br>158<br>161 |

| <b>6</b><br>6.1<br>6.2<br>6.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Channel Programming / Reprogramming Concept Channel Commands Transmit Channel Commands Receive Channel Commands                                                                                                                                                                                                                                                            | 163<br>164<br>164<br>166                                                                                     |

| <b>7</b><br>7.1<br>7.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Reset and Initialization procedure         Chip Initialization         Mode Initialization                                                                                                                                                                                                                                                                                 | 169<br>169<br>170                                                                                            |

| <b>8</b><br>8.1<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Transmit T1/E1 Framer Registers (Indirect Access)<br>Receive T1/E1 Framer Registers (Indirect Access)                                                                                                                                                                                                                                                                      | 171<br>171<br>173<br>173<br>175<br>180<br>181<br>182                                                         |

| 8.2     | Detailed Register Description                | 183 |

|---------|----------------------------------------------|-----|

| 8.2.1   | PCI Configuration Register                   | 183 |

| 8.2.2   | PCI Slave Register                           | 198 |

| 8.2.2.1 | Overhead Bit Timing                          | 215 |

| 8.2.2.2 | Stuff Bit Timing                             | 215 |

| 8.2.2.3 | T1/E1 Tributary Timing                       | 215 |

| 8.2.2.4 | Test Port Timing                             | 215 |

| 8.2.3   | Test Unit Registers                          |     |

| 8.2.3.1 | DS3, DS2 and Test Unit Interrupts            | 215 |

| 8.3     | M12 Multiplexer/Demultiplexer and DS2 framer |     |

| 8.3.1   | M12 multiplex format                         |     |

| 8.3.1.1 | Synchronization Procedure                    |     |

| 8.3.1.2 | Multiplexer/Demultiplexer                    | 215 |

| 8.3.1.3 | Loopback Control                             |     |

| 8.3.1.4 | Alarm Indication Signal                      |     |

| 8.3.2   | ITU-T G.747 format                           |     |

| 8.3.2.1 | Synchronization Procedure                    | 215 |

| 8.3.2.2 | Multiplexer/Demultiplexer                    | 215 |

| 8.3.2.3 | Parity Bit                                   |     |

| 8.3.2.4 | Remote Alarm Indication                      |     |

| 8.3.2.5 | Alarm Indication Signal                      |     |

| 8.4     | M23 multiplexer and DS3 framer               | 215 |

| 8.4.1   | M23 multiplex format                         |     |

| 8.4.1.1 | Synchronization Procedure                    |     |

| 8.4.1.2 | Multiplexer/Demultiplexer                    |     |

| 8.4.1.3 | X-bit                                        |     |

| 8.4.1.4 | Alarm Indication Signal, Idle Signal         |     |

| 8.4.1.5 | Loss of Signal                               | 215 |

| 8.4.1.6 | Performance Monitor                          |     |

| 8.4.2   | C-bit parity format                          | 215 |

| 8.4.2.1 | Synchronization Procedure                    |     |

| 8.4.2.2 | Multiplexer/Demultiplexer                    |     |

| 8.4.2.3 | X-bit                                        |     |

| 8.4.2.4 | Far End Alarm and Control Channel            | 215 |

| 8.4.2.5 | Path Maintenance Data Link Channel           |     |

| 8.4.2.6 | Loopback Control                             | 215 |

| 8.4.2.7 | Alarm Indication Signal, Idle Signal         |     |

| 8.4.2.8 | Loss of Signal                               |     |

| 8.4.2.9 | Performance Monitor                          |     |

| 8.4.3   | Full Payload Rate Format                     |     |

| 8.5     | Test Unit                                    | 215 |

| 8.5.1   | Local Port Loop                              |     |

| 8.5.2   | Remote Line Loops                            | 215 |

| 11                 | List of Abbreviations                                             | 421 |

|--------------------|-------------------------------------------------------------------|-----|

| 10                 | Package Outline                                                   | 420 |

| 5.4.0              | -                                                                 |     |

| 9.4.5<br>9.4.6     | JTAG Interface Timing                                             |     |

| 9.4.4.5<br>9.4.5   |                                                                   |     |

| 9.4.4.4<br>9.4.4.5 | T1/E1 Tributary Timing<br>Test Port Timing                        |     |

| 9.4.4.3<br>9.4.4.4 | Stuff Bit Timing                                                  |     |

| 9.4.4.2            | Overhead Bit Timing                                               |     |

| 9.4.4.1            | DS3 Serial Interface Timing                                       |     |

| 9.4.4              | tCYC is the clock period of the PCI clock.Serial Interface Timing |     |

| 9.4.3.4            | Motorola Bus Interface Timing (Master Mode)                       |     |

| 9.4.3.3            | Motorola Bus Interface Timing (Slave Mode)                        |     |

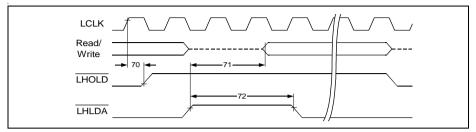

|                    | Intel Bus Interface Timing (Master Mode)                          |     |

| 9.4.3.1            |                                                                   |     |

| 9.4.3<br>9.4.3.1   | Intel Bus Interface Timing (Slave Mode)                           |     |

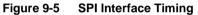

| 9.4.2<br>9.4.3     | Local Microprocessor Interface Timing                             |     |

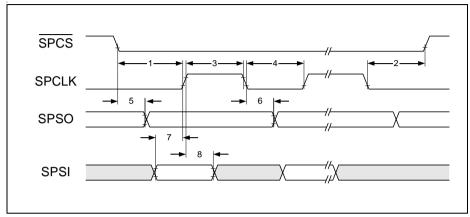

| 9.4.1              | SPI Interface Timing                                              |     |

| 9.4<br>9.4.1       | PCI Bus Interface Timing                                          |     |

| 9.3<br>9.4         | AC Characteristics                                                |     |

| 9.2                | DC Characteristics                                                |     |

| 9.2                | Absolute Maximum Ratings                                          |     |

| 9.1                | Important Electrical Requirements                                 |     |

| 9                  | Electrical Characteristics                                        | 389 |

| 8.9.6              | Facility Data Link Registers                                      |     |

| 8.9.5              | Receive Framer Registers                                          |     |

| 8.9.4              | Transmit Framer Register                                          |     |

| 8.9.3              | Test Unit Registers                                               |     |

| 8.9.2.2            | DS2 Control and Status Registers                                  |     |

| 8.9.2.1            | M13 Transmit Registers                                            | 263 |

| 8.9.2              | PCI and Local Bus Slave Register Set                              |     |

| 8.9.1.3            | M13 Transmit Registers                                            | 215 |

| 8.9.1.2            | DS2 Control and Status Registers                                  | 215 |

| 8.9.1.1            | DS3 Serial Interface Timing                                       | 215 |

| 8.9.1              | Serial Interface Timing                                           | 215 |

| 8.9                | General Features                                                  |     |

| 8.8.3              | M23 Multiplexer and DS3 Framer                                    | 215 |

| 8.8.2              | M12 Multiplexer and DS2 Framer                                    | 215 |

| 8.8.1              | Bit Error Rate Tester                                             | 215 |

| 8.8                | General System Integration                                        |     |

| 8.7                | Pin Diagram                                                       |     |

| 8.6                | Serial Interface                                                  |     |

| 8.5.3              | Test Breakout                                                     | 215 |

# List of Figures

| J.                                                                                                             |                                                                                                                                                                                                                                                                                                             |                                 |

|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

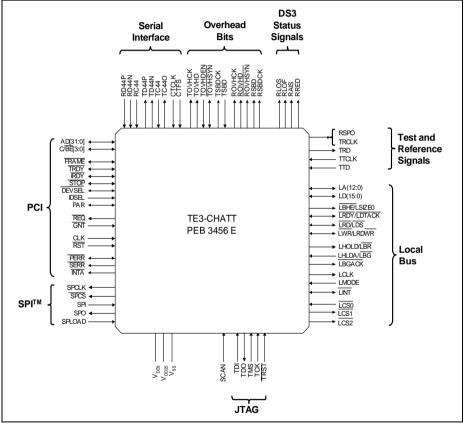

| Figure 1-1                                                                                                     | TE3-CHATT Logic Symbol 25                                                                                                                                                                                                                                                                                   |                                 |

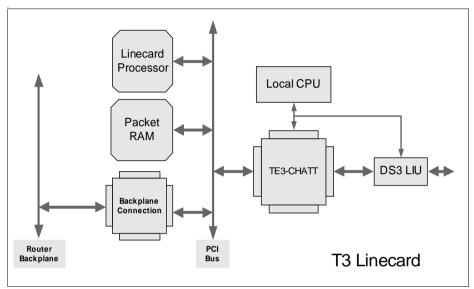

| Figure 1-2                                                                                                     | System Integration of the TE3-CHATT 26                                                                                                                                                                                                                                                                      |                                 |

| Figure 2-1                                                                                                     | TE3-CHATT Pin Configuration. 27                                                                                                                                                                                                                                                                             |                                 |

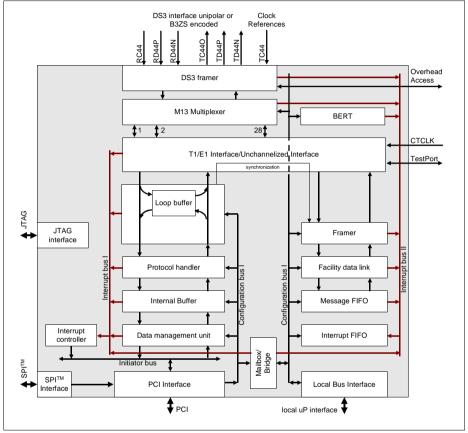

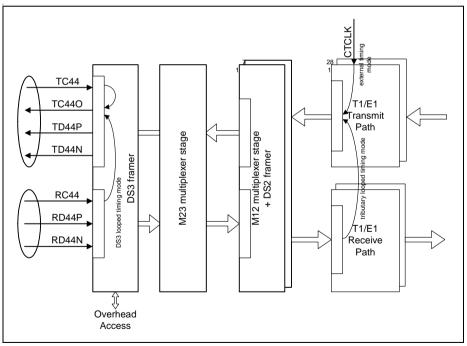

| Figure 3-1                                                                                                     | TE3-CHATT Block Diagram 48                                                                                                                                                                                                                                                                                  |                                 |

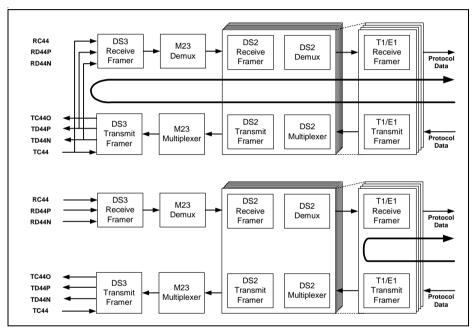

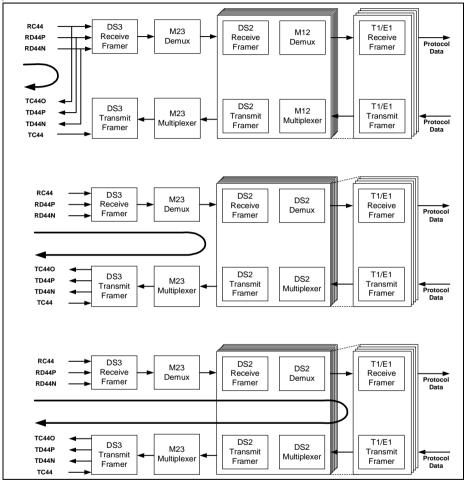

| Figure 4-1                                                                                                     | Port configuration in M13 mode                                                                                                                                                                                                                                                                              |                                 |

| Figure 4-2                                                                                                     | Local Port Loops in M13 mode                                                                                                                                                                                                                                                                                |                                 |

| Figure 4-3                                                                                                     | Remote Line Loops 55                                                                                                                                                                                                                                                                                        |                                 |

| Figure 4-4                                                                                                     | Test Breakout                                                                                                                                                                                                                                                                                               |                                 |

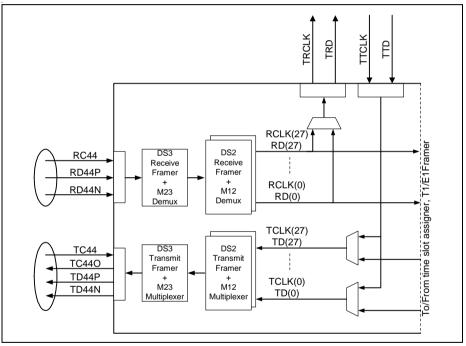

| Figure 4-5                                                                                                     | Time slot Assignment in Channelized Modes                                                                                                                                                                                                                                                                   |                                 |

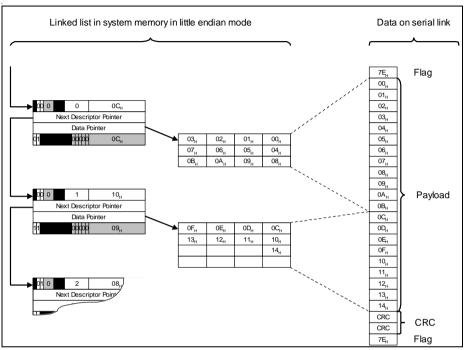

| Figure 4-6                                                                                                     | Descriptor Structure                                                                                                                                                                                                                                                                                        |                                 |

| Figure 4-7                                                                                                     | Receive Buffer Thresholds                                                                                                                                                                                                                                                                                   |                                 |

| Figure 4-8                                                                                                     | Transmit Buffer Thresholds                                                                                                                                                                                                                                                                                  |                                 |

| Figure 4-9                                                                                                     | HDLC Frame Format                                                                                                                                                                                                                                                                                           |                                 |

| Figure 4-10                                                                                                    | Bit Synchronous PPP with HDLC Framing Structure                                                                                                                                                                                                                                                             |                                 |

| Figure 4-11                                                                                                    | CRC-4 Multiframe Alignment Recovery Algorithms                                                                                                                                                                                                                                                              |                                 |

| Figure 4-12                                                                                                    | Interrupt Driven Reception Sequence Example 107                                                                                                                                                                                                                                                             |                                 |

| Figure 4-13                                                                                                    | Interrupt Driven Transmit Sequence Example 108                                                                                                                                                                                                                                                              |                                 |

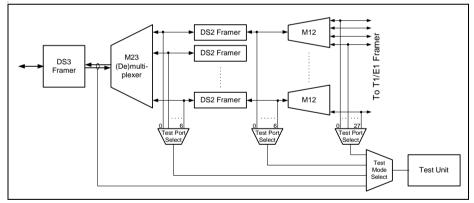

| Figure 4-14                                                                                                    | Test Unit Access Points 120                                                                                                                                                                                                                                                                                 |                                 |

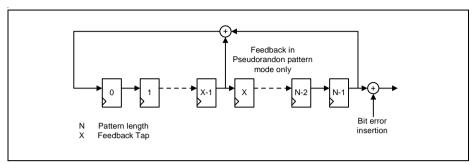

| Figure 4-15                                                                                                    | Pattern Generator 121                                                                                                                                                                                                                                                                                       |                                 |

| Figure 4-16                                                                                                    | Mailbox Structure                                                                                                                                                                                                                                                                                           |                                 |

| Figure 4-17                                                                                                    | Layer Two Interrupts (Channel, command, port and system interrupts                                                                                                                                                                                                                                          | •                               |

| 12                                                                                                             |                                                                                                                                                                                                                                                                                                             |                                 |

| Figure 4-18                                                                                                    | Interrupt Queue Structure in System Memory 125                                                                                                                                                                                                                                                              |                                 |

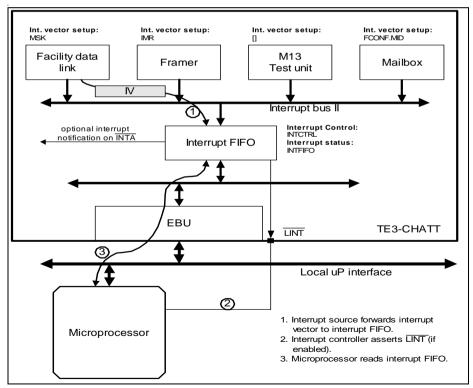

| Figure 4-19                                                                                                    | Framer, M13 and Facility Data Link and Mailbox Interrupt Notification                                                                                                                                                                                                                                       | •                               |

| 13                                                                                                             |                                                                                                                                                                                                                                                                                                             |                                 |

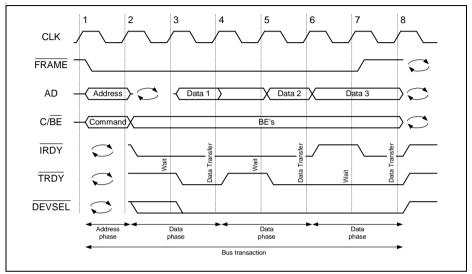

| Figure 5-1                                                                                                     | PCI Read Transaction                                                                                                                                                                                                                                                                                        |                                 |

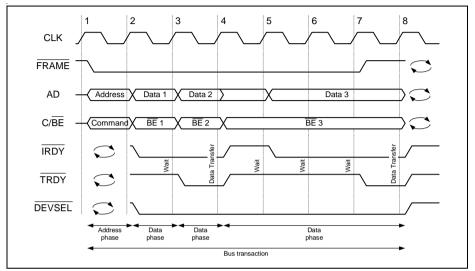

| Figure 5-2                                                                                                     | PCI Write Transaction                                                                                                                                                                                                                                                                                       | -                               |

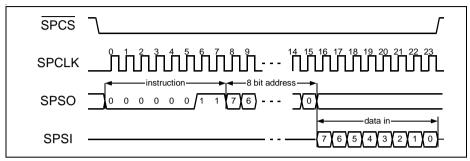

| Figure 5-3                                                                                                     | SPI Read Sequence 151                                                                                                                                                                                                                                                                                       |                                 |

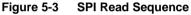

| Figure 5-4                                                                                                     | SPI Write Sequence. 151                                                                                                                                                                                                                                                                                     |                                 |

| Figure 5-5                                                                                                     | Intel Bus Mode 154                                                                                                                                                                                                                                                                                          |                                 |

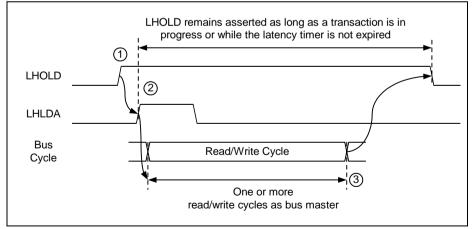

| Figure 5-6                                                                                                     | Intel Bus Arbitration                                                                                                                                                                                                                                                                                       | 1                               |

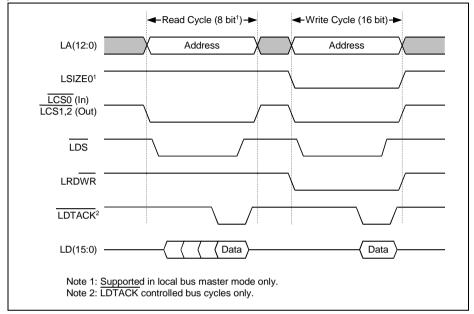

| Figure 5-7                                                                                                     |                                                                                                                                                                                                                                                                                                             |                                 |

|                                                                                                                | Motorola Bus Mode 157                                                                                                                                                                                                                                                                                       | 7                               |

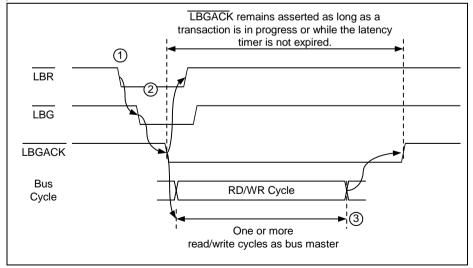

| Figure 5-8                                                                                                     | Motorola Bus Mode       157         Motorola Bus Arbitration       157                                                                                                                                                                                                                                      | 7<br>7                          |

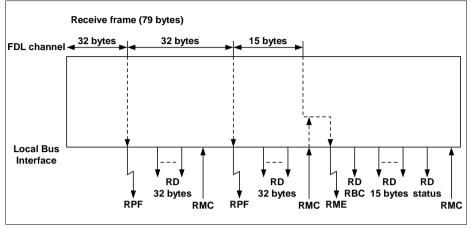

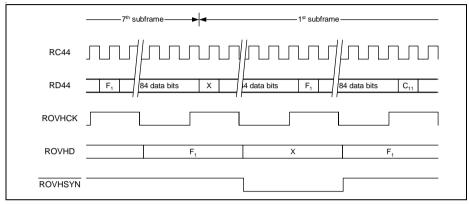

|                                                                                                                | Motorola Bus Mode       157         Motorola Bus Arbitration       157         Receive Overhead Access       158                                                                                                                                                                                            | 7<br>7                          |

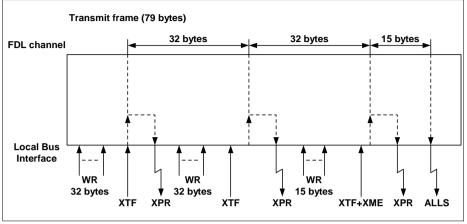

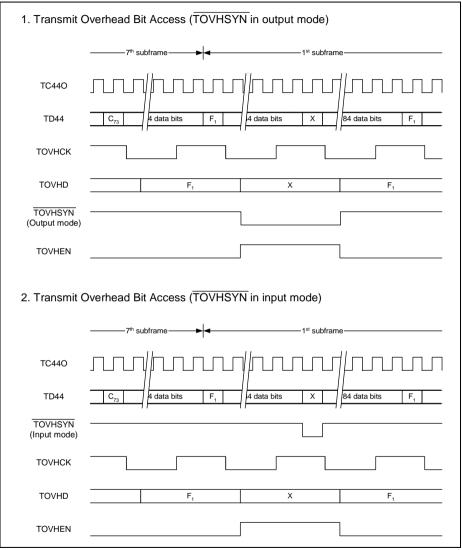

| Figure 5-8                                                                                                     | Motorola Bus Mode157Motorola Bus Arbitration157Receive Overhead Access158Transmit Overhead Access160                                                                                                                                                                                                        | 7<br>7<br>9<br>0                |

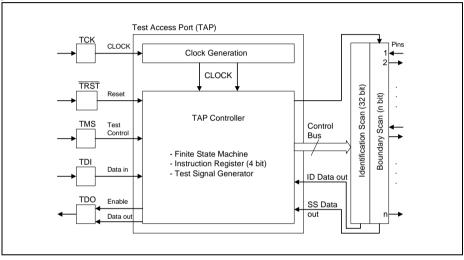

| Figure 5-8<br>Figure 5-9<br>Figure 5-10<br>Figure 5-11                                                         | Motorola Bus Mode       157         Motorola Bus Arbitration       157         Receive Overhead Access       158         Transmit Overhead Access       160         Block Diagram of Test Access Port and Boundary Scan Unit       161                                                                      | 7<br>7<br>9<br>0                |

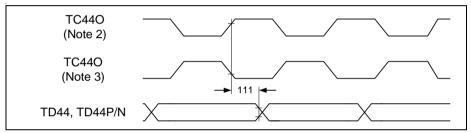

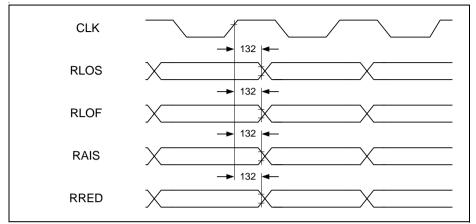

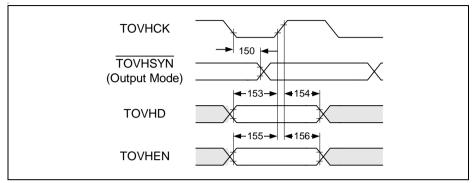

| Figure 5-8<br>Figure 5-9<br>Figure 5-10                                                                        | Motorola Bus Mode157Motorola Bus Arbitration157Receive Overhead Access159Transmit Overhead Access160Block Diagram of Test Access Port and Boundary Scan Unit161DS3 Transmit Overhead Timing215                                                                                                              | 7<br>7<br>9<br>1                |

| Figure 5-8<br>Figure 5-9<br>Figure 5-10<br>Figure 5-11<br>Figure 8-1<br>Figure 8-2                             | Motorola Bus Mode157Motorola Bus Arbitration157Receive Overhead Access159Transmit Overhead Access160Block Diagram of Test Access Port and Boundary Scan Unit161DS3 Transmit Overhead Timing215DS3 Transmit Overhead Synchronization Timing215                                                               | 7<br>7<br>9<br>0<br>1<br>5<br>5 |

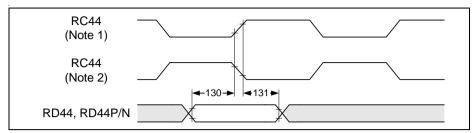

| Figure 5-8<br>Figure 5-9<br>Figure 5-10<br>Figure 5-11<br>Figure 8-1<br>Figure 8-2<br>Figure 8-3               | Motorola Bus Mode157Motorola Bus Arbitration157Receive Overhead Access158Transmit Overhead Access160Block Diagram of Test Access Port and Boundary Scan Unit161DS3 Transmit Overhead Timing215DS3 Transmit Overhead Synchronization Timing215DS3 Receive Overhead Timing215DS3 Receive Overhead Timing215   | 77901555                        |

| Figure 5-8<br>Figure 5-9<br>Figure 5-10<br>Figure 5-11<br>Figure 8-1<br>Figure 8-2<br>Figure 8-3<br>Figure 8-4 | Motorola Bus Mode157Motorola Bus Arbitration157Receive Overhead Access158Transmit Overhead Access160Block Diagram of Test Access Port and Boundary Scan Unit161DS3 Transmit Overhead Timing215DS3 Transmit Overhead Synchronization Timing215DS3 Receive Overhead Timing215DS3 Transmit Stuff Bit Timing215 | 779015555                       |

| Figure 5-8<br>Figure 5-9<br>Figure 5-10<br>Figure 5-11<br>Figure 8-1<br>Figure 8-2<br>Figure 8-3               | Motorola Bus Mode157Motorola Bus Arbitration157Receive Overhead Access158Transmit Overhead Access160Block Diagram of Test Access Port and Boundary Scan Unit161DS3 Transmit Overhead Timing215DS3 Transmit Overhead Synchronization Timing215DS3 Receive Overhead Timing215DS3 Receive Overhead Timing215   | 7790155555                      |

| List of Figure           | es P                                                                       | Page |

|--------------------------|----------------------------------------------------------------------------|------|

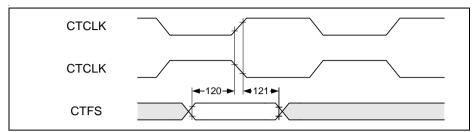

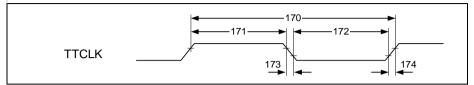

| Figure 8-7<br>Figure 8-8 | T1/E1 Tributary Synchronization Timing<br>T1/E1 Test Transmit Clock Timing |      |

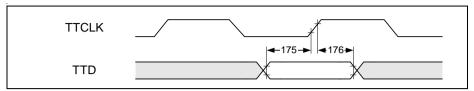

| Figure 8-9               | T1/E1 Test Transmit Data Timing                                            |      |

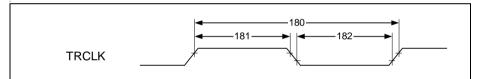

| Figure 8-10              | T1/E1 Test Receive Clock Timing                                            |      |

| Figure 8-11              | T1/E1 Test Receive Data Timing                                             |      |

| Figure 8-12              | Receive Overhead Access.                                                   |      |

| Figure 8-13              | Transmit Overhead Access                                                   |      |

| Figure 8-14              | Framer, M13 and Facility Data Link and Mailbox Interrupt Notification      |      |

| 21                       |                                                                            |      |

| Figure 8-15              | Test Unit Access Points                                                    | 215  |

| Figure 8-16              | Pattern Generator                                                          | 215  |

| Figure 8-17              | Port configuration in M13 mode                                             | 215  |

| Figure 8-18              | Local Port Loops in M13 mode                                               | 215  |

| Figure 8-19              | Remote Line Loops                                                          | 215  |

| Figure 8-20              | Test Breakout.                                                             | 215  |

| Figure 8-21              | TE3-CHATT Block Diagram                                                    | 215  |

| Figure 8-22              | TE3-CHATT Pin Configuration                                                | 215  |

| Figure 8-23              | System Integration of the TE3-CHATT                                        | 215  |

| Figure 8-24              | TE3-CHATT Logic Symbol.                                                    | 215  |

| Figure 8-25              | Clock Input Timing                                                         |      |

| Figure 8-26              | DS3 Transmit Cycle Timing                                                  |      |

| Figure 8-27              | DS3 Transmit Data Timing.                                                  |      |

| Figure 8-28              | DS3 Receive Cycle Timing                                                   |      |

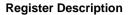

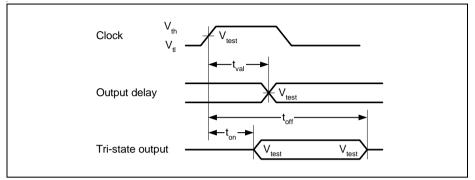

| Figure 9-1               | Input/Output Waveform for AC Tests                                         |      |

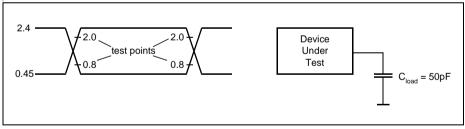

| Figure 9-2               | PCI Clock Cycle Timing                                                     |      |

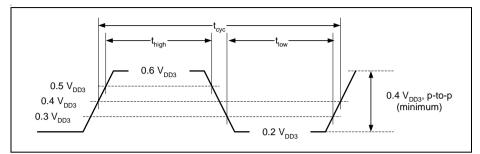

| Figure 9-3               | PCI Input Timing Measurement Conditions                                    |      |

| Figure 9-4               | PCI Output Timing Measurement Conditions                                   |      |

| Figure 9-5               | SPI Interface Timing                                                       |      |

| Figure 9-6               | Intel Read Cycle Timing (Slave Mode)                                       |      |

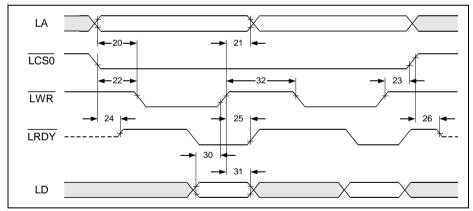

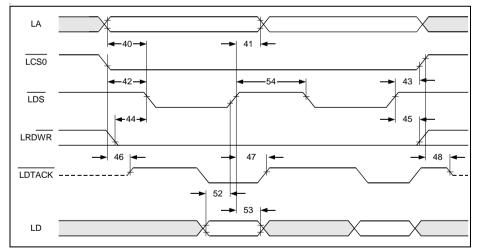

| Figure 9-7               | Intel Write Cycle Timing (Slave Mode).                                     |      |

| Figure 9-8               | Intel Read Cycle Timing (Master Mode, LRDY controlled)                     |      |

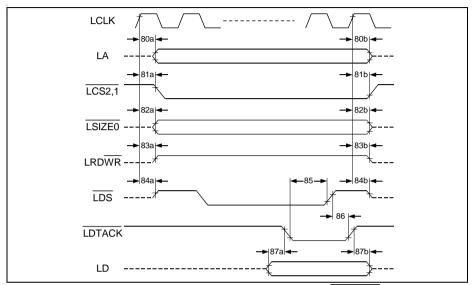

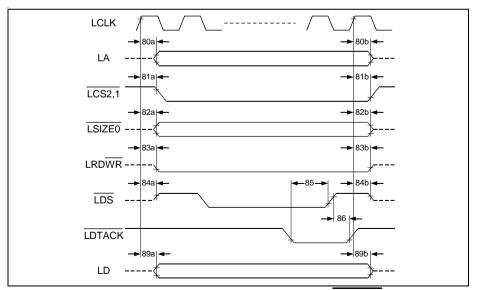

| Figure 9-9               |                                                                            |      |

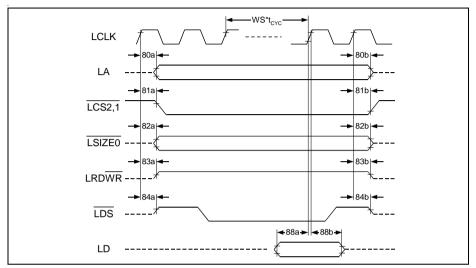

| Figure 9-10              | Intel Read Cycle Timing (Master Mode, Wait state controlled)               |      |

| Figure 9-11              | Intel Write Cycle Timing (Master Mode, Wait state controlled)              |      |

| Figure 9-12              | Intel Bus Arbitration Timing                                               |      |

| Figure 9-13              | Motorola Read Cycle Timing (Slave Mode)                                    |      |

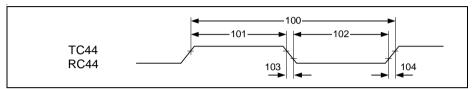

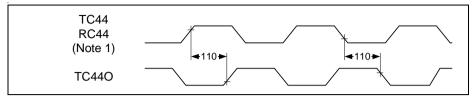

| Figure 9-14              | , ,                                                                        |      |

| Figure 9-15              | Motorola Read Cycle Timing (Master Mode, LDTACK controlled)                |      |

| Figure 9-16              | Motorola Write Cycle Timing (Master Mode, LDTACK controlled)               | 402  |

| Figure 9-17              | Motorola Read Cycle Timing (Master Mode, Wait state controlled).           |      |

| Figure 9-18              | Motorola Write Cycle Timing (Master Mode, Wait state controlled)           |      |

| Figure 9-19              | Motorola Bus Arbitration Timing                                            | 404  |

| Figure 9-20 | Clock Input Timing 406                           |

|-------------|--------------------------------------------------|

| Figure 9-21 | DS3 Transmit Cycle Timing 407                    |

| Figure 9-22 | DS3 Transmit Data Timing 407                     |

| Figure 9-23 | DS3 Receive Cycle Timing 408                     |

| Figure 9-24 | DS3 Transmit Overhead Timing 410                 |

| Figure 9-25 | DS3 Transmit Overhead Synchronization Timing 410 |

| Figure 9-26 | DS3 Receive Overhead Timing 411                  |

| Figure 9-27 | DS3 Transmit Stuff Bit Timing 412                |

| Figure 9-28 | DS3 Receive Stuff Bit Timing 412                 |

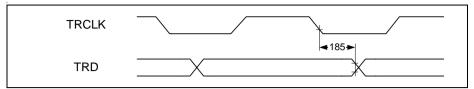

| Figure 9-29 | T1/E1 Tributary Clock Input Timing 413           |

| Figure 9-30 | T1/E1 Tributary Synchronization Timing 414       |

| Figure 9-31 | T1/E1 Test Transmit Clock Timing 415             |

| Figure 9-32 | T1/E1 Test Transmit Data Timing 416              |

| Figure 9-33 | T1/E1 Test Receive Clock Timing 416              |

| Figure 9-34 | T1/E1 Test Receive Data Timing 417               |

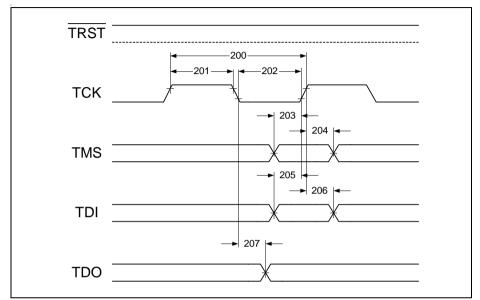

| Figure 9-35 | JTAG Interface Timing 418                        |

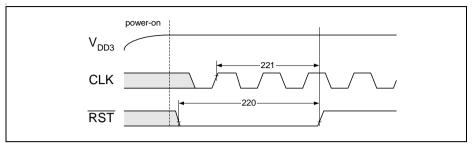

| Figure 9-36 | Reset Timing 419                                 |

## List of Tables

#### Page

| Table 4-1Receive Descriptor Structure61Table 4-2Transmit Descriptor Structure67Table 4-3Example for little/big Endian with BNO = 372Table 4-4Example for little big Endian with BNO = 772Table 4-54-Frame Multiframe Structure.79Table 4-6ESF Multiframe Structure.80Table 4-7SF Multiframe Structure.80Table 4-8Allocation of Bits 1 to 8 of Time slot 090Table 4-9CRC-4 Multiframe Structure.92Table 4-10Summary of Alarm Detection and Alarm Release98Table 4-11M12 multiplex format109Table 4-12ITU-T G.747 format111Table 4-13M23 multiplex format113Table 4-14C-bit parity format116Table 4-15Interrupt Vector Structure.125Table 5-1Correspondence between PCI memory space and chip select152Table 5-2C/BE to LA/LBHE mapping in Intel bus mode (8 bit port mode)155Table 5-3C/BE to LA/LBHE mapping in Intel bus mode (8 bit port mode)155Table 5-4C/BE to LA/LSIZE0 mapping in Motorola bus mode (8 bit port mode)158 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 4-3Example for little/big Endian with BNO = 372Table 4-4Example for little big Endian with BNO = 772Table 4-54-Frame Multiframe Structure.79Table 4-6ESF Multiframe Structure.80Table 4-7SF Multiframe Structure.80Table 4-8Allocation of Bits 1 to 8 of Time slot 090Table 4-9CRC-4 Multiframe Structure.92Table 4-10Summary of Alarm Detection and Alarm Release98Table 4-11M12 multiplex format109Table 4-12ITU-T G.747 format111Table 4-13M23 multiplex format113Table 4-14C-bit parity format116Table 4-15Interrupt Vector Structure.125Table 5-1Correspondence between PCI memory space and chip select152Table 5-2C/BE to LA/LBHE mapping in Intel bus mode (8 bit port mode)155Table 5-3C/BE to LA/LBHE mapping in Intel bus mode (16 bit port mode)155                                                                                                                                                           |

| Table 4-4Example for little big Endian with BNO = 772Table 4-54-Frame Multiframe Structure.79Table 4-6ESF Multiframe Structure.80Table 4-7SF Multiframe Structure.80Table 4-8Allocation of Bits 1 to 8 of Time slot 090Table 4-9CRC-4 Multiframe Structure.92Table 4-10Summary of Alarm Detection and Alarm Release98Table 4-11M12 multiplex format109Table 4-12ITU-T G.747 format111Table 4-13M23 multiplex format113Table 4-14C-bit parity format116Table 4-15Interrupt Vector Structure.125Table 5-1Correspondence between PCI memory space and chip select152Table 5-2C/BE to LA/LBHE mapping in Intel bus mode (8 bit port mode)155Table 5-3C/BE to LA/LBHE mapping in Intel bus mode (16 bit port mode)155                                                                                                                                                                                                                |

| Table 4-54-Frame Multiframe Structure.79Table 4-6ESF Multiframe Structure.80Table 4-7SF Multiframe Structure.80Table 4-7SF Multiframe Structure.85Table 4-8Allocation of Bits 1 to 8 of Time slot 090Table 4-9CRC-4 Multiframe Structure.92Table 4-10Summary of Alarm Detection and Alarm Release98Table 4-11M12 multiplex format109Table 4-12ITU-T G.747 format111Table 4-13M23 multiplex format113Table 4-14C-bit parity format116Table 4-15Interrupt Vector Structure.125Table 5-1Correspondence between PCI memory space and chip select152Table 5-2C/BE to LA/LBHE mapping in Intel bus mode (8 bit port mode)155Table 5-3C/BE to LA/LBHE mapping in Intel bus mode (16 bit port mode)155                                                                                                                                                                                                                                  |

| Table 4-6ESF Multiframe Structure80Table 4-7SF Multiframe Structure85Table 4-7SF Multiframe Structure90Table 4-8Allocation of Bits 1 to 8 of Time slot 090Table 4-9CRC-4 Multiframe Structure92Table 4-10Summary of Alarm Detection and Alarm Release98Table 4-11M12 multiplex format109Table 4-12ITU-T G.747 format111Table 4-13M23 multiplex format113Table 4-14C-bit parity format116Table 4-15Interrupt Vector Structure125Table 5-1Correspondence between PCI memory space and chip select152Table 5-2C/BE to LA/LBHE mapping in Intel bus mode (8 bit port mode)155Table 5-3C/BE to LA/LBHE mapping in Intel bus mode (16 bit port mode)155                                                                                                                                                                                                                                                                               |

| Table 4-7SF Multiframe Structure85Table 4-8Allocation of Bits 1 to 8 of Time slot 090Table 4-9CRC-4 Multiframe Structure92Table 4-10Summary of Alarm Detection and Alarm Release98Table 4-11M12 multiplex format109Table 4-12ITU-T G.747 format111Table 4-13M23 multiplex format113Table 4-14C-bit parity format116Table 4-15Interrupt Vector Structure125Table 5-1Correspondence between PCI memory space and chip select152Table 5-2C/BE to LA/LBHE mapping in Intel bus mode (8 bit port mode)155Table 5-3C/BE to LA/LBHE mapping in Intel bus mode (16 bit port mode)155                                                                                                                                                                                                                                                                                                                                                    |

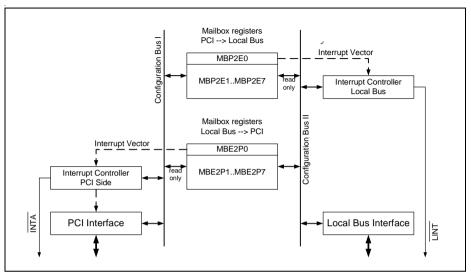

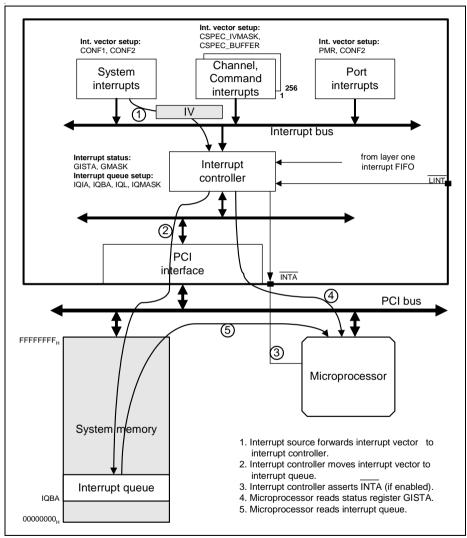

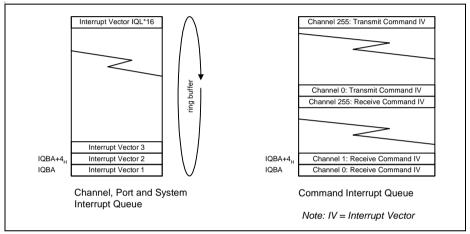

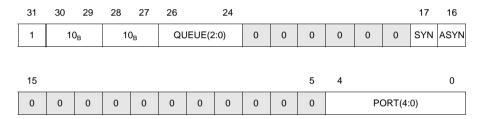

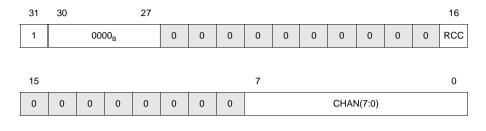

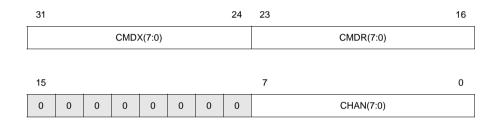

| Table 4-8Allocation of Bits 1 to 8 of Time slot 090Table 4-9CRC-4 Multiframe Structure.92Table 4-9Summary of Alarm Detection and Alarm Release98Table 4-10M12 multiplex format109Table 4-11M12 multiplex format109Table 4-12ITU-T G.747 format111Table 4-13M23 multiplex format113Table 4-14C-bit parity format116Table 4-15Interrupt Vector Structure.125Table 5-1Correspondence between PCI memory space and chip select152Table 5-2C/BE to LA/LBHE mapping in Intel bus mode (8 bit port mode)155Table 5-3C/BE to LA/LBHE mapping in Intel bus mode (16 bit port mode)155                                                                                                                                                                                                                                                                                                                                                    |