# Specification for Approval

| Customer | • |  |

|----------|---|--|

| Customer | • |  |

Model Type : <u>LCD Module</u>

Model Number : <u>PG12864ARS-ANN-G</u>

Edi : <u>0</u>

| Customer Sign | Sales Sign | Approved By | Prepared By         |

|---------------|------------|-------------|---------------------|

|               |            | rr          | - r · · · · · · - J |

|               |            |             |                     |

|               |            |             |                     |

|               |            |             |                     |

|               |            |             |                     |

# **CONTENTS**

## 1.SPECIFICATIONS

- 1.1 Features

- 1.2 Mechanical Specifications

- 1.3 Absolute Maximum Ratings

- 1.4 DC Electrical Characteristics

- 1.5 Optical Characteristics

# 2.MODULE STRUCTURE

- 2.1 Counter Drawing

- 2.2 Interface Pin Description

- 2.3 Timing Characteristics

- 2.4 Display Command

## 1. SPECIFICATIONS

### 1.1 Features

- Full dot-matrix structure with 128 dots \*64 dots

- 1/64 Duty, 1/9 bias

- STN LCD, positive

- Reflective LCD, gray

- 6 o'clock viewing angle

- 8 bits parallel data input

# 1.2 Mechanical Specifications

• Outline dimension : 93.0mm(L)\*70.0mm(W)\*9.7mm max.(H)

Viewing area : 72.0mm \*40.0mm

Active area : 66.52mm \*33.24mm

Dot size : 0.48mm \* 0.48mm

Dot pitch : 0.52mm \* 0.52mm

## 1.3 Absolute Maximum Ratings

| Item                     | Symbol  | Conditions | Min. | Max.    | Unit |

|--------------------------|---------|------------|------|---------|------|

| Power supply Voltage     | Vdd     | -          | 0    | 7.0     | V    |

| LCD drive Supply voltage | VDD-VEE | -          | 0    | 17      | V    |

| Input voltage            | VIN     | ı          | 0    | VDD+0.3 | V    |

| Operating temperature    | TOPR    | ı          | -20  | 70      | °C   |

| Storage temperature      | TSTG    | -          | -30  | 80      | °C   |

| Humidity*1               | HD      | -          | ı    | 90      | %RH  |

## 1.4 DC Electrical Characteristics

| Item                 | Symbol | Condition | Min.   | Тур. | Max.   | Unit |

|----------------------|--------|-----------|--------|------|--------|------|

| Logic Supply voltage | Vdd    | -         | 4.5    | 5    | 5.5    | V    |

| "H" input voltage    | VIH    | -         | 0.7Vdd | -    | Vdd    | V    |

| "L" input voltage    | VIL    | -         | 0      | -    | 0.3VDD | V    |

| Supply current       | IOP    | VDD=5V    | -      | -    | 13     | mA   |

| LCD driving voltage  | VLCD   | VDD-VO    | -      | 13.6 | -      | V    |

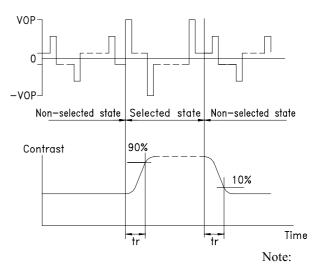

## 1.5 Optical Characteristics

1/64 duty, 1/9 bias, Vopr=13.6V, Ta=25°C

| Item                | Symbol | Conditions  | Min. | Тур.  | Max   | Reference   |

|---------------------|--------|-------------|------|-------|-------|-------------|

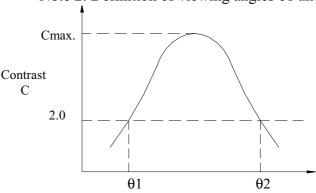

| Viewing angle θ     |        | C≥2.0,Ø=0°C | 30°  | -     | ı     | Notes 1 & 2 |

| Contrast            | C      | θ=5°, Ø=0°  | 2    | 3     | ı     | Note 3      |

| Response time(rise) | ton    | θ=5°, Ø=0°  | -    | 140ms | 200ms | Note 4      |

| Response time(fall) | toff   | θ=5°, Ø=0°  | -    | 300ms | 500ms | Note 4      |

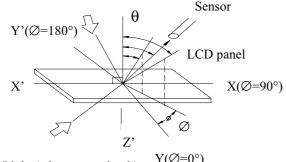

Note 1: Definition of angles  $\theta$  and  $\emptyset$

Light (when reflected)  $z (\theta=0^{\circ})$

Light (when transmitted )  $Y(\varnothing=0^{\circ})$   $(\theta=90^{\circ})$

Note 2: Definition of viewing angles  $\theta 1$  and  $\theta 2$

$\begin{array}{c} \text{viewing angle }\theta \ ( \mbox{$\varnothing$ fixed}) \\ \text{Note:} \quad \text{Optimum viewing angle with the} \\ \text{naked eye and viewing angle }\theta \ \text{at} \\ \text{Cmax. Above are not always the} \end{array}$

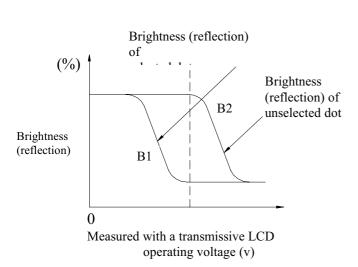

Note 3: Definition of contrast C

Brightness (reflection) of unselected dot (B2)

Brightness (reflection) of selected dot (B1)

panel which is displayed 1 cm<sup>2</sup>

Vopr : Operating voltgae fFRM : Frame frequency ton : Response time (rise) toff : Response time (fall)

POWERTIP TECHNOLOGY CORPORATION

# 2. MODULE STRUCTURE

# 2.1 Counter Drawing

\*See Appendix

# 2.2 Interface Pin Description

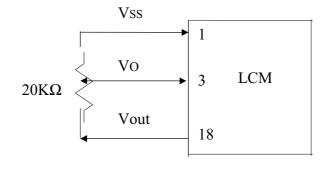

| Pin No. | Symbol      | Function                                                                                                                                                            |

|---------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Vss         | Signal ground (GND)                                                                                                                                                 |

| 2       | Vdd         | Power supply for logic (+5V)                                                                                                                                        |

| 3       | Vo          | Operating voltage for LCD (variable)                                                                                                                                |

| 4       | D/ I        | Register selection input High =Data register Low =Instruction register (for write) Busy flag address counter (for read)                                             |

| 5       | R/W         | R/W signal input is used to select the read/write mode High =Read mode, Low =Write mode                                                                             |

| 6       | E           | Start enable signal to read or write the data                                                                                                                       |

| 7-10    | DB0~<br>DB3 | Four low order bi-directional three-state data bus lines. Use for data transfer between the MPU and the LCD module. These four are not used during 4-bit operation. |

| 11-14   | DB4~<br>DB7 | For high order bi-directional three-state data bus lines. Used for data transfer between the MPU and the LCD module. DB7 can be used as a busy flag.                |

| 15      | CS1         | Chip enable for D2 (segment 1 to segment 64)                                                                                                                        |

| 16      | CS2         | Chip enable for D3 (segment 65 to segment 128)                                                                                                                      |

| 17      | RST         | Reset signal                                                                                                                                                        |

| 18      | Vout        | Negative voltage power supply                                                                                                                                       |

| 19      | NC          | Non-connection                                                                                                                                                      |

| 20      | NC          | Non-connection                                                                                                                                                      |

## Contrast Adjust

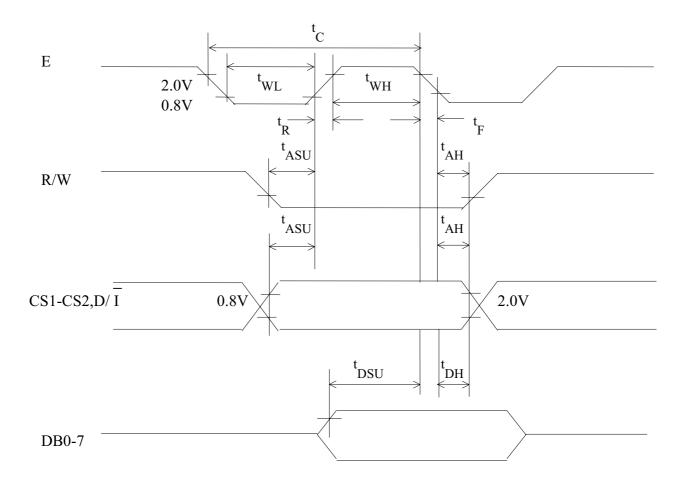

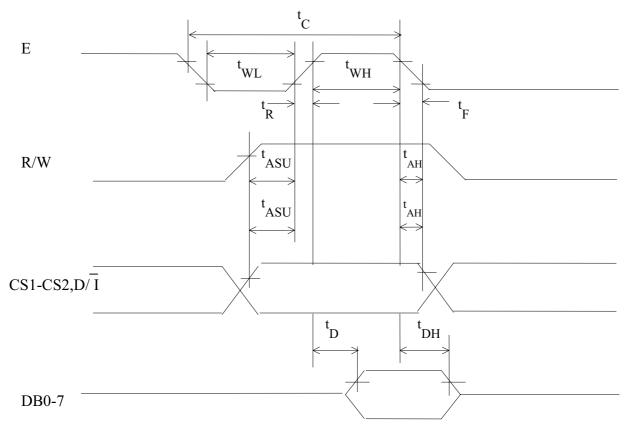

# 2.3 Timing Characteristics

MPU write timing

MPU read timing

| Characteristic         | Symbol | Min. | Тур | Max | Unit |

|------------------------|--------|------|-----|-----|------|

| E Cycle                | tC     | 1000 | -   | -   | ns   |

| E High Level Width     | tWH    | 450  | -   | -   | ns   |

| E Low Level Width      | tWL    | 450  | -   | -   | ns   |

| E Rise Time            | tR     | _    | -   | 25  | ns   |

| E Fall Time            | tF     | _    | -   | 25  | ns   |

| Address Set-Up time    | tASU   | 140  | -   | -   | ns   |

| Address Hold Time      | tAH    | 10   | -   | -   | ns   |

| Data Set-Up Time       | tsu    | 200  |     | -   | ns   |

| Data Delay Time        | tD     | _    | -   | 320 | ns   |

| Data Hold Time (Write) | tDHW   | 10   | -   | -   | ns   |

| Data Hold Time (Read)  | tDHR   | 20   | -   | -   | ns   |

## 2.4 Display command

|                    |    |     |      |      | Со   | de    |       |      |      |      | _             |                  |                       |

|--------------------|----|-----|------|------|------|-------|-------|------|------|------|---------------|------------------|-----------------------|

|                    | R/ | D/I | DB7  | DB   | DB5  | DB    | DB    | DB   | DB   | DB0  |               |                  |                       |

| Instructions       | W  |     |      | 6    |      | 4     | 3     | 2    | 1    |      | Functions     |                  |                       |

| Display on/off     | 0  | 0   | 0    | 0    | 1    | 1     | 1     | 1    | 1    | 1/0  | Controls dis  | splay on/off. R. | AM data and internal  |

|                    |    |     |      |      |      |       |       |      |      |      | status are no | ot affected.     |                       |

| Display start line | 0  | 0   | 1    | 1    | Disp | lay s | tart  | line | (0-6 | 63)  | Specifies th  | e RAM line di    | splayed at the top of |

|                    |    |     |      |      |      |       |       |      |      |      | the screen.   |                  |                       |

| Set Page (x        | 0  | 0   | 1    | 0    | 1    | 1     | 1     | Pa   | ge ( | 0-7) | Sets the pag  | ge (X address) o | of RAM at the page    |

| address)           |    |     |      |      |      |       |       |      |      |      | (X address)   | register.        |                       |

| Set Y address      | 0  | 0   | 0    | 1    | Y ad | dres  | s (0- | -63) |      |      | Sets the Y a  | ddress in the Y  | address in the        |

|                    |    |     |      |      |      |       |       |      |      |      | counter.      |                  |                       |

| Status read        | 1  | 0   | Busy | 0    | ON/  | Res   | et 0  | 0    | 0    | 0    | Reads the st  | atus.            |                       |

|                    |    |     |      |      | OFF  |       |       |      |      |      | Reads         | 1: Reset         |                       |

|                    |    |     |      |      |      |       |       |      |      |      |               | 0: Normal        |                       |

|                    |    |     |      |      |      |       |       |      |      |      | ON/OFF        | 1: Display of    | f                     |

|                    |    |     |      |      |      |       |       |      |      |      |               | 0: Display or    | 1                     |

|                    |    |     |      |      |      |       |       |      |      |      | Busy          | 1: Internal op   | peration              |

|                    |    |     |      |      |      |       |       |      |      |      |               | 0: Ready         |                       |

| Write display data | 0  | 1   | Writ | e da | ıta  |       |       |      |      |      | Writes data   | DB0 (LSB)        | Has access to the     |

|                    |    |     |      |      |      |       |       |      |      |      | to DB7 (MS    | SB) on the       | address of the        |

|                    |    |     |      |      |      |       |       |      |      |      | data bus into | o display        | display RAM           |

|                    |    |     |      |      |      |       |       |      |      |      | RAM.          |                  | specified in          |

| Read display data  | 1  | 1   | Read | da1  | ta   |       |       |      |      |      | Reads data    | DB0 (LSB)        | advance. After the    |

|                    |    |     |      |      |      |       |       |      |      |      | to DB7 (MS    | SB) from the     | access, Y address is  |

|                    |    |     |      |      |      |       |       |      |      |      | display RAI   | M to the data    | increased by 1.       |

|                    |    |     |      |      |      |       |       |      |      |      | bus.          |                  |                       |

|                    |    |     |      |      |      |       |       |      |      |      |               |                  |                       |

## **Detailed Explanation**

## Display On/Off

|      | R/W | D/I | DB7. |   |   |   |   |   |   | DB0 |

|------|-----|-----|------|---|---|---|---|---|---|-----|

| Code | 0   | 0   | 0    | 0 | 1 | 1 | 1 | 1 | 1 | D   |

|      |     |     | MSB  |   |   |   |   |   |   | LSB |

The display data appears when D is 1 and disappears when D is 0. Though the data is not on the screen with D=0, it remains in the display data RAM. Therefore, you can make it appear by changing D=0 into D=1.

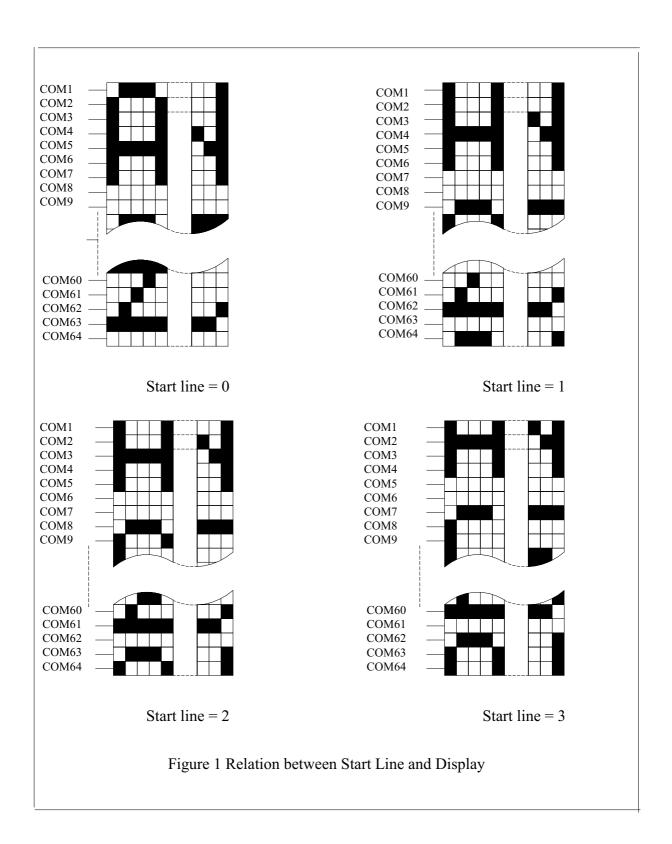

## - Display Start Line

|      | R/W | D/I | DB7. |   |   |   |   |   |   | DB0 |

|------|-----|-----|------|---|---|---|---|---|---|-----|

| Code | 0   | 0   | 1    | 1 | A | A | A | A | A | A   |

|      |     |     | MSB  |   |   |   |   |   |   | LSB |

Z address AAAAA (binary) of the display data RAM is set in the display start line register and displayed at the top of the screen. Figure 1 shows examples of display (1/64 duty cycle) when the start line=0-3. When the display duty cycle is 1/64 or more (ex. 1/32, 1/24 etc.), the data of total line number of LCD screen, from the line specified by display start line instruction, is displayed. See figure 1.

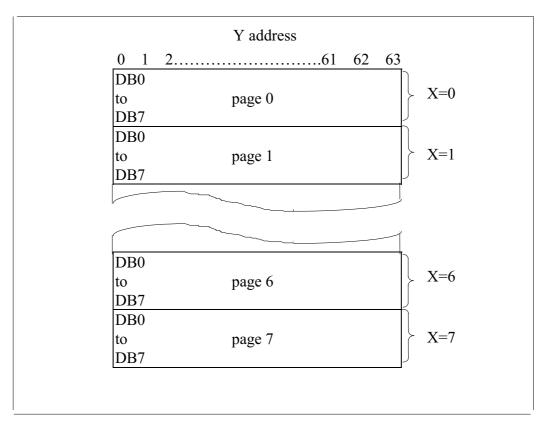

### Set page (X address)

|      | R/W | D/I | DB7. |   |   |   |   |   |   | DB0 |

|------|-----|-----|------|---|---|---|---|---|---|-----|

| Code | 0   | 0   | 1    | 0 | 1 | 1 | 1 | A | A | A   |

|      |     |     | MSB  |   |   |   |   |   |   | LSB |

X address AAA (binary) of the display data RAM is set in the X address register. After that, writing or reading to or from MPU is executed in this specified page until the next page is set. See figure 2.

### Set Y Address

|      | R/W | D/I | DB7. | ] | DB0 |   |   |   |   |     |

|------|-----|-----|------|---|-----|---|---|---|---|-----|

| Code | 0   | 0   | 0    | 1 | A   | A | A | A | A | A   |

|      |     |     | MSB  | , |     |   |   |   |   | LSB |

Y address AAAAA (binary) of the display data RAM is set in the Y address Counter. After that, address counter is increased by 1 every time the data is written or read to or from MPU.

#### **Status Read**

Y

|      | R/W | D/I | DB7  |   |        |       |   |   | DB0 |     |  |

|------|-----|-----|------|---|--------|-------|---|---|-----|-----|--|

| Code | 1   | 0   | Busy | 0 | ON/OFF | Reset | 0 | 0 | 0   | 0   |  |

|      |     |     | MSB  |   |        |       |   |   |     | LSB |  |

### • Busy

When busy is 1, the LSI is executing internal operations. No instructions are accepted while busy is 1, so you should make sure that busy is 0 before writing the next instruction.

### • ON/OFF

Shows the liquid crystal display conditions: on condition or off condition.

When on/off is 1, the display is in off condition.

When on/off is 0, the display is in on condition.

#### RESET

RESET=1 shows that the system is being initialized. In this condition, no instructions except status read can be accepted.

RESET=0 shows that initializing has finished and the system is in the usual operation condition.

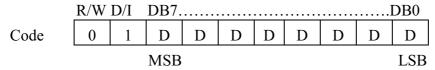

## Write Display Data

Write 8-bit data DDDDDDDD (binary) into the display data RAM. Then Y address is increased by 1 automatically.

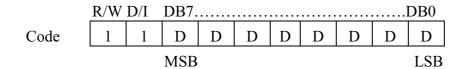

## **Read Display Data**

Reads out 8-bit data DDDDDDDD (binary) from the display data RAM. Then Y address is increased by 1 automatically.

One dummy read is necessary right after the address setting. For details, refer to the explanation of output register in "Function of Each Block".

Figure 2 Address Configuration of Display Data RAM