# **Product Standards**

PGA26E07BA

| Туре               | GaN-Tr                         |         |          |  |  |

|--------------------|--------------------------------|---------|----------|--|--|

| Application        | For power switching            |         |          |  |  |

| Structure          | N-channel enhancement mode FET |         |          |  |  |

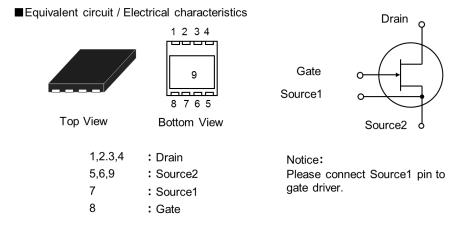

| Equivalent Circuit | Figure 1                       |         |          |  |  |

| Out Line           | DFN 8X8                        | Marking | PGA26E07 |  |  |

#### A. ABSOLUTE MAXIMUM RATINGS ( Tj = 25 °C , unless otherwise specified )

| No.  | Item                                                  | Quarteral | Values |      |      | 1.1  | Nata                                                   |

|------|-------------------------------------------------------|-----------|--------|------|------|------|--------------------------------------------------------|

| INO. | Item                                                  | Symbol    | Min.   | Тур. | Max. | Unit | Note                                                   |

| 1    | Drain-source voltage ( DC ) *1                        | VDSS      | -      | -    | 600  | V    |                                                        |

| 2    | Drain-source voltage ( pulse ) *2                     | VDSP      | -      | -    | 750  | V    |                                                        |

| 3    | Gate-source voltage ( DC ) *1                         | VGSS      | -10    | -    | -    | V    | *VGSS+ is given by IG ratings<br>*See application note |

| 4    | Gate current ( DC ) *1                                | IG        | -      | -    | 50   | mA   | *See application note                                  |

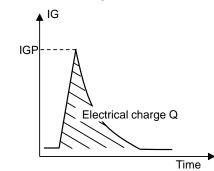

| 5    | Gate current ( pulse ) *3,4                           | IGP       | -      | -    | 1.5  | A    | *See application note                                  |

| 6    | Electric gate charge                                  | QGP       | -      | -    | 32   | nC   | *f=200kHz<br>*See application note                     |

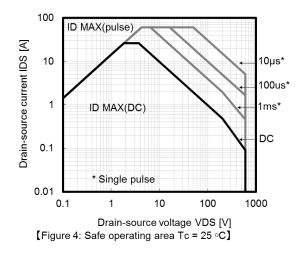

| 7    | Drain current(DC)<br>(Tc = 25 °C)*1                   | ID        | -      | -    | 26   | A    | Figure 4                                               |

| 8    | Drain reverse current ( DC )<br>( Tc = 25 °C ) *1     | IDR       | -      | -    | 26   | A    |                                                        |

| 9    | Drain current ( pulse )*5<br>( Tc = 25 °C )*1         | ID pulse  | -      | -    | 61   | A    | Figure 4                                               |

| 10   | Drain reverse current ( pulse )*5<br>( Tc = 25 °C )*1 | IDR pulse | -      | -    | 61   | А    |                                                        |

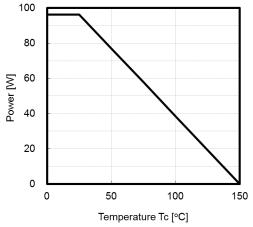

| 11   | Power dissipation ( $Tc = 25 ^{\circ}C$ )             | PD        | -      | -    | 96   | W    | Figure 2                                               |

| 12   | Junction temperature                                  | Tj        | -      | -    | 150  | °C   |                                                        |

| 13   | Storage temperature                                   | Tstg      | -55    | -    | 150  | °C   |                                                        |

| 14   | Drain-source voltage slope                            | dv/dt     | -      | -    | 200  | V/ns |                                                        |

[Special instructions]

\*1 : Please use this product to meet a condition of Tj within 150  $^{\circ}\text{C}.$

\*2 : Spike duty cycle D < 0.1, spike duration < 1us, total spike time < 1hour.

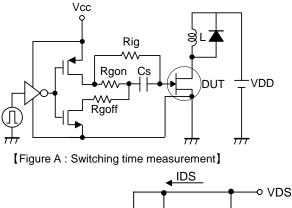

\*3 : IGP is defined as (Vcc - Vplateau) / Rgon, as shown in Figure A.

Vplateau is the voltage between Gate and Source1.

\*4 : Please use this product to meet both a maximum gate current and a maximum gate pulse charge of IGP(1.5A) and Q(32nC) respectively, as shown in Figure H.

\*5 : Pulse width limited by Tjmax.

Established: 2016-09-01 Revised: 2017-01-16

## PGA26E07BA

| No. | ltem                                               | Symbol  | Measurement Condition                | Min. | Тур. | Max. | Unit |

|-----|----------------------------------------------------|---------|--------------------------------------|------|------|------|------|

| 1   | Drain cut-off current                              | IDSS    | VDS=600 V, VGS=0 V, Tj=25 °C         | -    | -    | 100  | μA   |

|     |                                                    |         | VDS=600 V, VGS=0 V, Tj=150 °C        | -    | 100  | -    | μA   |

| 2   | Gate-source leakage current                        | IGSS    | VGS=-3 V<br>VDS=0 V                  | -1   | -    | -    | μA   |

| 3   | Gate forward voltage                               | VGSF    | IGS=26.1 mA<br>open drain            | 2.8  | 3.5  | 4.2  | V    |

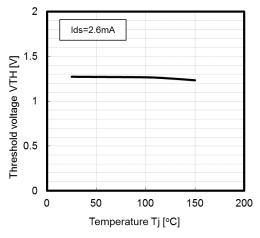

| 4   | Gate threshold voltage                             | VTH     | VDS=10 V<br>IDS=2.6 mA               | 0.9  | 1.2  | 1.6  | V    |

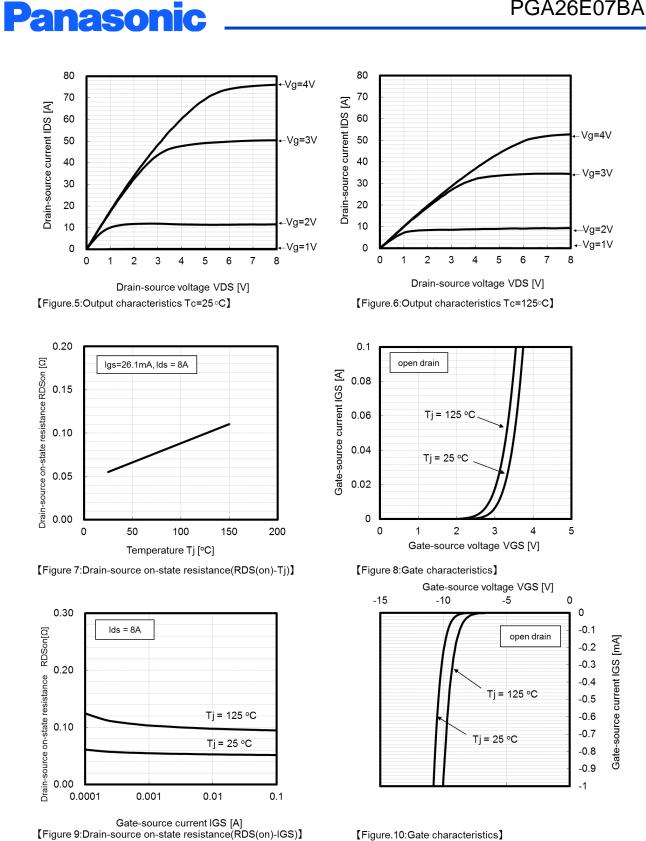

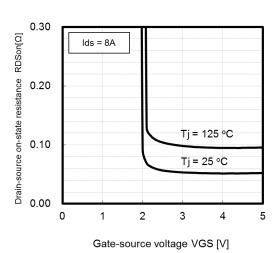

| 5   | Drain-source on-state resistance                   | RDS(on) | IGS=26.1 mA, IDS=8A, Tj=25 °C        | -    | 56   | 70   | mΩ   |

| Ŭ   |                                                    |         | IGS=26.1 mA, IDS=8 A, Tj=150 °C      | -    | 110  | -    | mΩ   |

| 6   | Gate resistance                                    | RG      | f=100MHz<br>open drain               | -    | 0.6  | -    | Ω    |

| 7   | Transfer conductance                               | gfs     | VDS=8 V<br>IDS=8 A                   | -    | 32   | -    | S    |

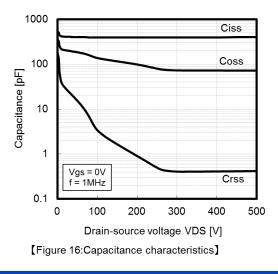

| 8   | Input capacitance                                  | Ciss    |                                      | -    | 405  | -    | pF   |

| 9   | Output capacitance                                 | Coss    | VDS=400 V<br>VGS=0 V<br>f=1 MHz      | -    | 71   | -    | pF   |

| 10  | Reverse transfer capacitance                       | Crss    |                                      | -    | 0.4  | -    | pF   |

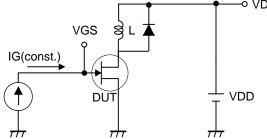

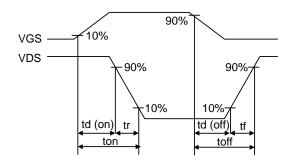

| 11  | Turn-on delay time                                 | td(on)  | VDD=400 V                            | -    | 3.7  | -    | ns   |

| 12  | Rise time                                          | tr      | IDS=8 A<br>(Figure A, Figure B)      | -    | 5.6  | -    | ns   |

| 13  | Turn-off delay time                                | td(off) | Vcc=12 V<br>Rgon=6.2 Ω, Rgoff=4.7 Ω, | -    | 5.5  | -    | ns   |

| 14  | Fall time                                          | tf      | Rig=680 Ω, Cs=1500 pF                | -    | 2.4  | -    | ns   |

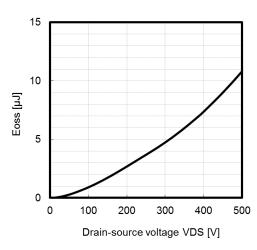

| 15  | Effective output capacitance<br>( energy related ) | Co(er)  |                                      | -    | 87   | -    | pF   |

| 16  | Effective output capacitance ( time related )      | Co(tr)  | VDS=0-480 V                          | -    | 106  | -    | pF   |

#### B. ELECTRICAL CHARACTERISTICS (Tj = 25 $^{\circ}$ C, unless otherwise specified)

## PGA26E07BA

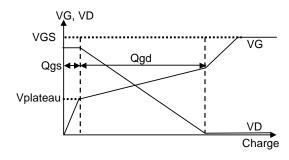

#### C. GATE CHARGE CHARACTERISTICS (Tj = 25 °C, unless otherwise specified)

| No. | Item                 | Symbol    | Measurement Condition                        | Min. | Тур. | Max. | Unit |

|-----|----------------------|-----------|----------------------------------------------|------|------|------|------|

| 1   | Gate charge          | Qg        |                                              | -    | 5.0  | -    | nC   |

| 2   | Gate-source charge   | Qgs       | VDD=400 V<br>IDS=8 A<br>(Figure C, Figure D) | -    | 0.9  | -    | nC   |

| 3   | Gate-drain charge    | Qgd       |                                              | -    | 2.6  | -    | nC   |

| 4   | Gate plateau voltage | V plateau | VDD=400 V<br>IDS=8 A                         | -    | 1.7  | -    | V    |

#### D. REVERSE CONDUCTING CHARACTERISTICS (Tj = 25 °C, unless otherwise specified )

| No. | Item                          | Symbol | Measurement Condition | Min. | Тур. | Max. | Unit |

|-----|-------------------------------|--------|-----------------------|------|------|------|------|

| 1   | Source-drain forward voltage  | VSD    | VGS=0 V<br>ISD=8 A    | -    | 2.1  | -    | V    |

| 2   | Reverse recovery charge       | Qrr    |                       | -    | 0    | -    | nC   |

| 3   | Reverse recovery time         | trr    | VDS=400 V             | -    | 0    | -    | ns   |

| 4   | Peak reverse recovery current | Irrm   | ISD=8 A               | -    | 0    | -    | А    |

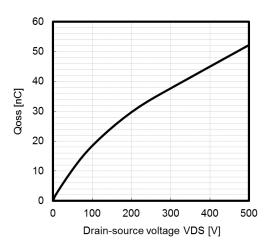

| 5   | Output charge                 | Qoss   |                       | -    | 45   | -    | nC   |

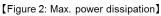

#### E. THERMAL RESISTANCE CHARACTERISTICS

| No. | Item                                             | Symbol   | Measurement Condition | Min. | Тур. | Max. | Unit |

|-----|--------------------------------------------------|----------|-----------------------|------|------|------|------|

| 1   | Thermal resistance<br>( junction to case )       | Rth(j-c) |                       | -    | -    | 1.3  | °C/W |

| 2   | Thermal resistance<br>( junction to ambient ) *1 | Rth(j-a) |                       | -    | -    | 46   | °C/W |

| 3   | Reflow soldering temperature                     | Tsold    | reflow MSL3           | -    | -    | 260  | °C   |

[Notes]

\*1 : Device mounted on four layers epoxy PCB (6.45  $\text{cm}^2$  copper area and 70  $\mu\text{m}$  thickness).

[Figure 1: Pin layout / Equivalent circuit]

nasonic

[Figure 3: Transient thermal impedance]

-

## PGA26E07BA

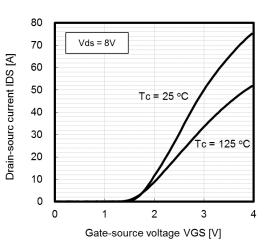

[Figure.10:Gate characteristics]

2

### PGA26E07BA

nasonic

[Figure.11:Drain-source on-state resistance(RDS(on)-VGS)]

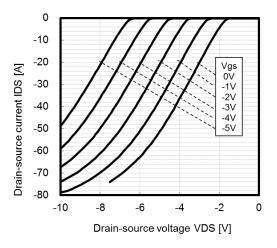

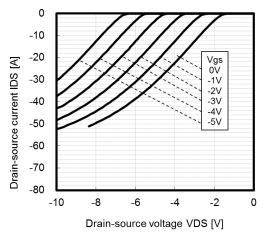

[Figure.13:Reverse channel characteristics (Tc=25°C)]

[Figure 15:Gate charge characteristics]

| Established: | 2016-09-01 |

|--------------|------------|

| Revised:     | 2017-01-16 |

[Figure 12:Transfer characteristics]

[Figure.14:Reverse channel characteristics (Tc=125°C)]

## PGA26E07BA

[Figure 17:Output capacitance stored energy]

[Figure.19:Threshold voltage (VTH-Tj)]

[Figure 18:Output charge]

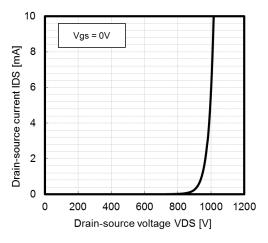

[Figure.20:Drain-Source leakage current (Tc=25°C)]

asonic

IDS

Clamp circuit 7/7

ISD ສີ L

- vds

L

VDD

VDD

$\pi$

8

[Figure C : Gate charge measurement]

VGS

DÙ

+

[Figure E : Reverse bias safe operating area

dv/dt measurement circuit]

$\pi$

Rig

[Figure B : Switching wave form]

[Figure D : Gate charge wave form]

[Figure F : Reverse bias safe operating area dv/dt wave form]

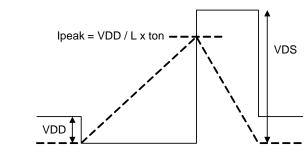

[Figure G : di/dt measurement circuit]

DU

Rig

Established: 2016-09-01 Revised: 2017-01-16

[Precautions for Use]

- The product has risks for break-down or burst or giving off smoke in following conditions. Avoid the following use. Fuse should be added at the input side or connect zener diode between Gate pin and GND, etc as a countermeasure to pass regulatory Safety Standard. Concrete countermeasure could be provided individually. However, customer should make the final judgment.

- (1) Reverse the Drain pin and gate pin connection to the power supply board.

- (2) Drain pin short to Source1 pin and Source2 pin.

- (3) Drain pin short to Gate pin.

- (4) Gate pin open.

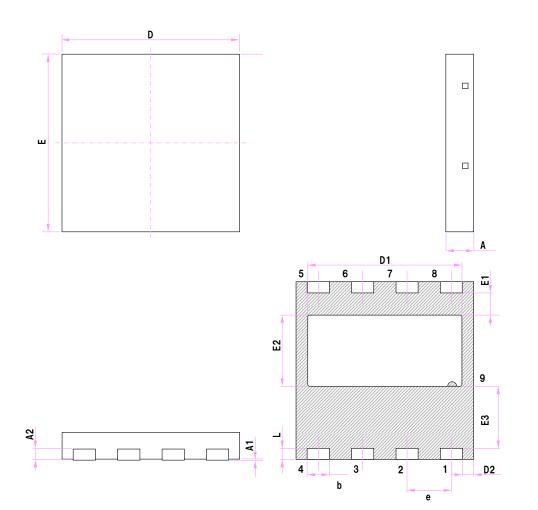

Outline

| SYMBOL  | DIMENSION   |      |      |  |  |  |

|---------|-------------|------|------|--|--|--|

| STNIDOL | MIN         | NOM  | MAX  |  |  |  |

| A       | 1.15        | 1.25 | 1.35 |  |  |  |

| A1      | 0.00        | 0.02 | 0.05 |  |  |  |

| A2      | 0.40        | 0.50 | 0.60 |  |  |  |

| b       | 0.90        | 1.00 | 1.10 |  |  |  |

| D       | 7.90        | 8.00 | 8.10 |  |  |  |

| D1      | 6.84        | 6.94 | 7.04 |  |  |  |

| D2      | 0.40        | 0.50 | 0.60 |  |  |  |

| E       | 7.90        | 8.00 | 8.10 |  |  |  |

| E1      | 0.90        | 1.00 | 1.10 |  |  |  |

| E2      | 3.10        | 3.20 | 3.30 |  |  |  |

| E3      | 2.70        | 2.80 | 2.90 |  |  |  |

| е       | 2.00 B.S.C. |      |      |  |  |  |

| L       | 0.40        | 0.50 | 0.60 |  |  |  |

Unit: mm

### Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed.

- (2) The technical information described in this book is intended only to show the main characteristics and application circuit examples of the products. No license is granted in and to any intellectual property right or other right owned by Panasonic Corporation or any other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any other company which may arise as a result of the use of technical information de-scribed in this book.

- (3) The products described in this book are intended to be used for general applications (such as office equipment, communications equipment, measuring instruments and household appliances), or for specific applications as expressly stated in this book.

Please consult with our sales staff in advance for information on the following applications, moreover please exchange documents separately on terms of use etc.: Special applications (such as for in-vehicle equipment, airplanes, aerospace, automotive equipment, traffic signaling equipment, combustion equipment, medical equipment and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

Unless exchanging documents on terms of use etc. in advance, it is to be understood that our company shall not be held responsible for any damage incurred as a result of or in connection with your using the products described in this book for any special application.

- (4) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most upto-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment. Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (6) Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. We do not guarantee quality for disassembled products or the product re-mounted after removing from the mounting board. When using products for which damp-proof packing is required, satisfy the conditions, such as shelf life and the elapsed time since first opening the packages.

- (7) When reselling products described in this book to other companies without our permission and receiving any claim of request from the resale destination, please understand that customers will bear the burden.

- (8) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of our company.