## PRESSURE SENSOR SIGNAL CONDITIONER

#### 1 DEVICE OVERVIEW

#### 1.1 FEATURES

- · Analog Features

- Analog Front-End for Resistive Bridge Sensors

- Self-Oscillating Demodulator for Capacitive Sensors

- On-Chip Temperature Sensor

- Programmable Gain

- 16-Bit, 1MHz Sigma-Delta Analog-to-Digital Converter for Signal Channel

- 10-Bit Sigma-Delta Analog-to-Digital Converter for Temperature Channel

- Two 12-Bit DAC Outputs

- Digital Features

- Microcontroller Core

- 10 MHz 8051 WARP Core

- 2 Clocks Per Instruction Cycle

- On–Chip Oscillator

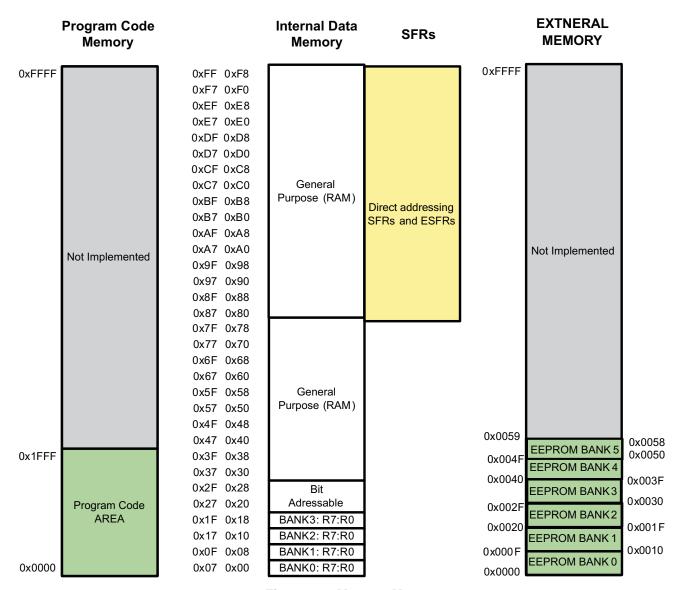

- Memory

- 8 KB of OTP Memory

- 89 Bytes of EEPROM

- 256 Bytes Data SRAM

- Peripheral Features

- Serial Peripheral Interface (SPI™)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

- One-Wire Interface

- Two Input Capture Ports

- Two Output Compare Ports

- Software Watchdog Timer

- Oscillator Watchdog

- Power Management Control

- Analog Low-Voltage Detect

- · General Features

- Power Supply: 4.5 V to 5.5 V Operational, –5.5 V to 16 V Abs Max

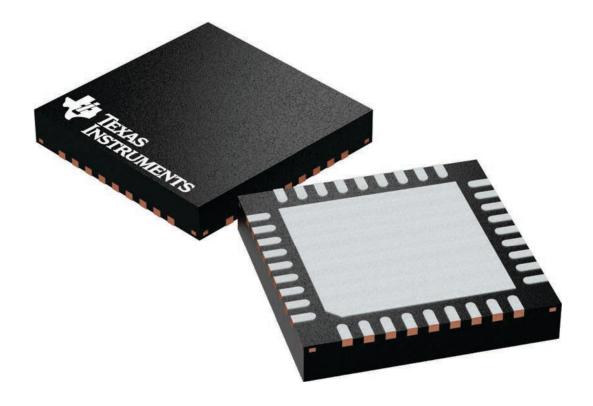

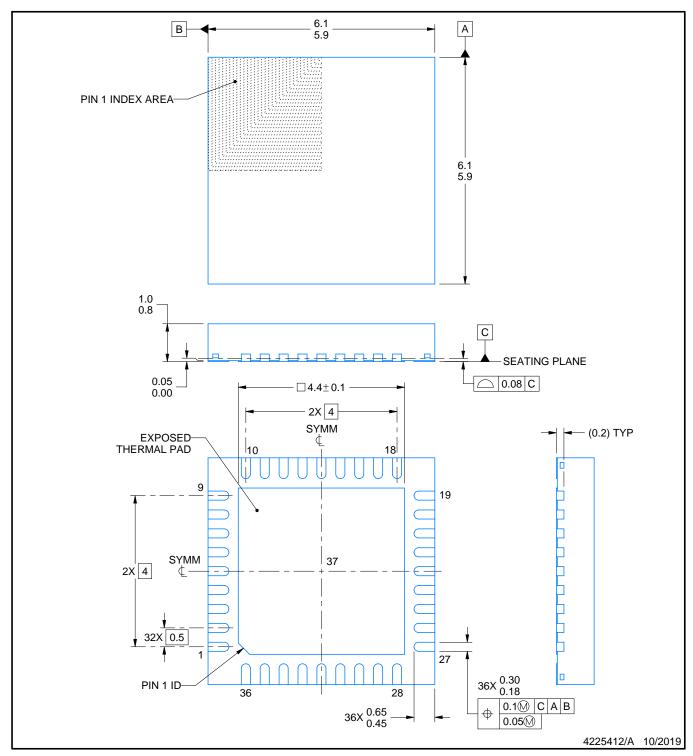

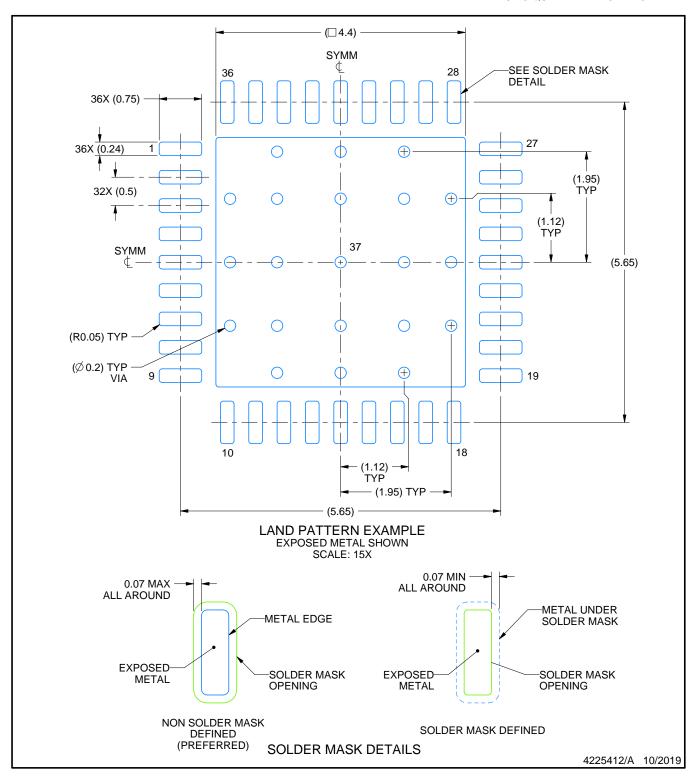

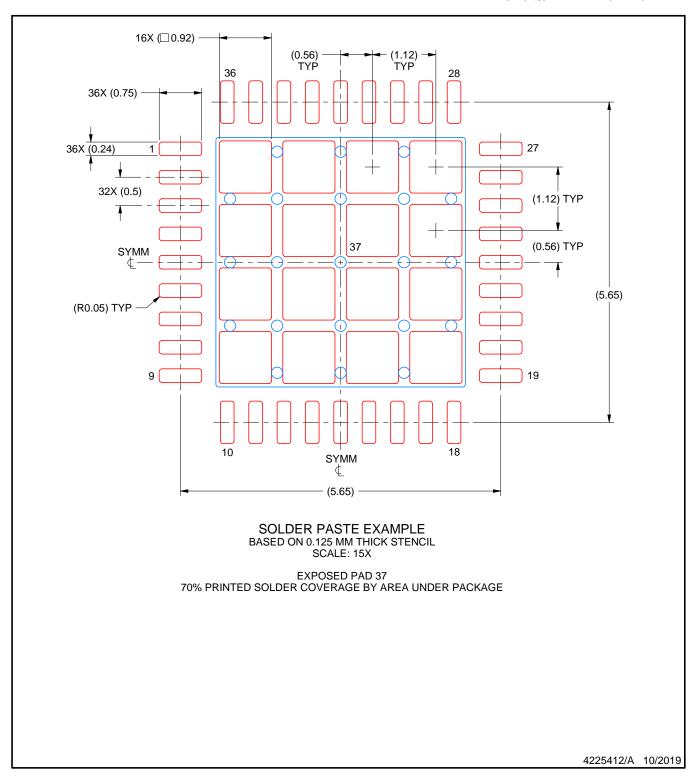

- PVQFN-36 package

### 1.2 APPLICATIONS

- Pressure Sensor Signal Conditioning

- Level Sensor Signal Conditioning

Humidity Sensor Signal Conditioning

### 1.3 SUPPORTS INDUSTRIAL SENSING APPLICATIONS

- Controlled Baseline

- · One Assembly and Test Site

- One Fabrication Site

- Extended Product Life Cycle

- Extended Product-Change Notification

- Product Traceability

#### **DEVICE OVERVIEW**

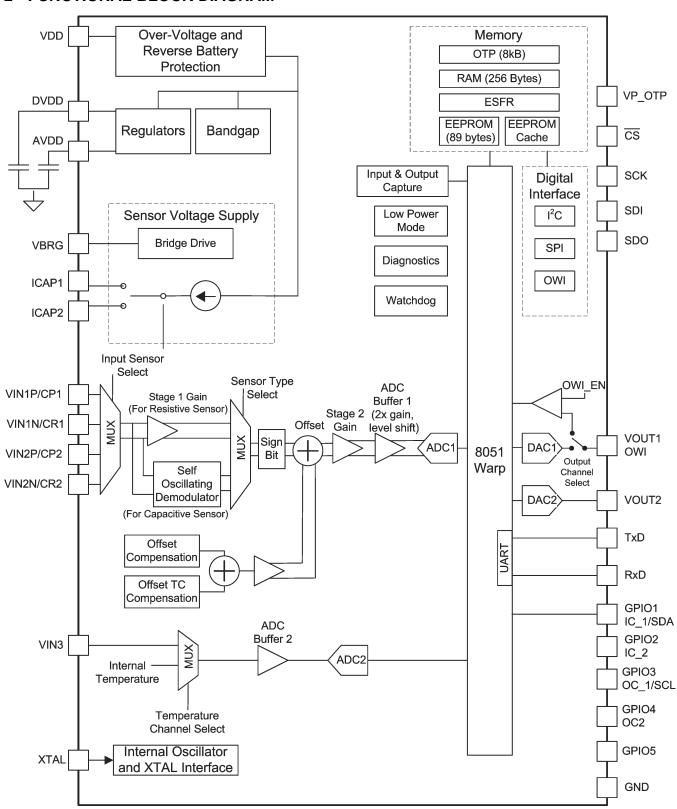

The PGA400-EP is an interface device for piezoresistive, strain gauge and capacitive sense elements. The device incorporates the analog front end that directly connects to the sense element and has voltage regulators and oscillator. The device also includes sigma-delta analog-to-digital converter, 8051 WARP core microprocessor and OTP memory. Sensor compensation algorithms can be implemented in software. The PGA400-EP also includes 2 DAC outputs.

### 1.1 ORDERING INFORMATION(1)

| T <sub>A</sub> | PACKAGE <sup>(2)</sup> | ORDERABLE PART NUMBER | TOP-SIDE MARKING | VID NUMBER     |

|----------------|------------------------|-----------------------|------------------|----------------|

| -40°C to 125°C | PVQFN (RHH)            | PGA400QRHHTEP         | PGA400QRHH-EP    | V62/13619-01XE |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at <a href="https://www.ti.com">www.ti.com</a>.

<sup>(2)</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

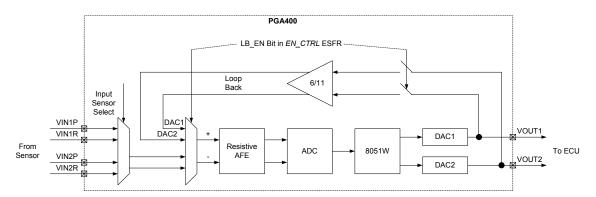

### 2 FUNCTIONAL BLOCK DIAGRAM

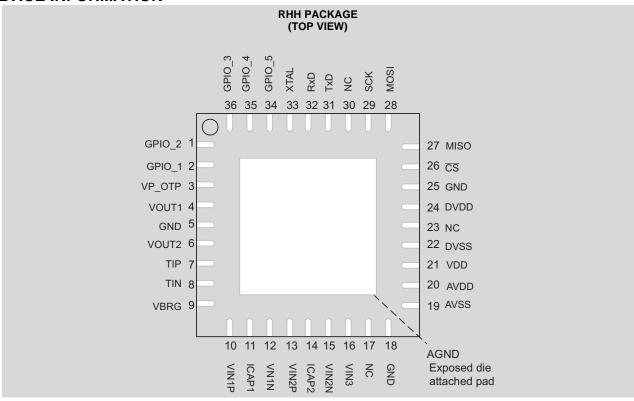

## 3 DEVICE INFORMATION

### **PIN DESCRIPTIONS**

| NAME   | NO.        | DESCRIPTION                                                             |

|--------|------------|-------------------------------------------------------------------------|

| GPIO_2 | 1          | General purpose IO 2 / input capture port 2                             |

| GPIO_1 | 2          | General purpose IO 1 / input capture port 1 / I2C Data                  |

| VT_OTP | 3          | One-time programmable memory programming voltage                        |

| VOUT1  | 4          | DAC1 output / One-wire interface                                        |

| GND    | 5, 18, 25  | Ground                                                                  |

| VOUT2  | 6          | DAC2 output                                                             |

| TIP    | 7          | Test pin reserved                                                       |

| TIN    | 8          | Test pin reserved                                                       |

| VBRG   | 9          | Resistive bridge supply voltage                                         |

| VIN1P  | 10         | Resistive sensor 1 positive input / capacitive sensor 1 positive input  |

| ICAP1  | 11         | Capacitive sensor drive current 1                                       |

| VIN1N  | 12         | Resistive sensor 1 negative input / capacitive sensor 1 reference input |

| VIN2P  | 13         | Resistive sensor 2 positive input / capacitive sensor 2 positive input  |

| ICAP2  | 14         | Capacitive sensor drive current 2                                       |

| VIN2N  | 15         | Resistive sensor 2 negative input / capacitive sensor 2 reference input |

| VIN3   | 16         | External temperature sensor input                                       |

| NC     | 17, 23, 30 | No connect                                                              |

| AVSS   | 19         | Ground                                                                  |

| AVDD   | 20         | Linear regulator output for internal analog circuit supply              |

| VDD    | 21         | Input power supply                                                      |

| DVSS   | 22         | Ground                                                                  |

| DVDD   | 24         | Linear regulator output for internal digital circuit supply             |

| CS     | 26         | Serial peripheral interface chip select                                 |

Submit Documentation Feedback Product Folder Links: PGA400-EP

# PIN DESCRIPTIONS (continued)

| NAME  | NO. | DESCRIPTION                                              |

|-------|-----|----------------------------------------------------------|

| MISO  | 27  | Serial peripheral interface slave data out               |

| MOSI  | 28  | Serial peripheral interface slave data in                |

| SCK   | 29  | Serial peripheral interface clock                        |

| TxD   | 31  | 8051 UART Tx (Port 3_1)                                  |

| RxD   | 32  | 8051 UART Rx (Port 3_0)                                  |

| XTAL  | 33  | XTAL External crystal input                              |

| GPIO5 | 34  | General purpose IO 5                                     |

| GPIO4 | 35  | General purpose IO 4 / output compare port 2             |

| GPIO3 | 36  | General purpose IO 3 / output compare port 1 / I2C Clock |

#### 4 ABSOLUTE MAXIMUM RATINGS

### 4.1 ABSOLUTE MAXIMUM RATINGS(1)

|                                                 | PARAMETER                                 | MIN  | MAX       | UNIT |

|-------------------------------------------------|-------------------------------------------|------|-----------|------|

| VDD,<br>Continuous                              | Power Supply Voltage                      | -5.5 | 16        | V    |

|                                                 | Voltage at VP_OTP                         | -0.3 | 8.0       | V    |

|                                                 | Voltage at sensor input and drive pins    | -0.3 | 3.6       | V    |

|                                                 | Voltage at any IO pin except at VOUT1/OWI | -0.3 | VDD + 0.3 | V    |

|                                                 | Voltage at VOUT1/OWI pin                  | -0.3 | 7.5       | V    |

| I <sub>DD</sub> , Short<br>on VOUT1<br>or VOUT2 | Supply Current                            | -45  | 45        | mA   |

| lout1, lout2                                    | Output Current                            | -30  | 30        | mA   |

| ESD                                             | Human Body Model (HBM)                    | ±2   |           | KV   |

| ESD                                             | Field Induced Charge Device Model (CDM)   | ±50  | 0         | V    |

| T <sub>jmax</sub>                               | Maximum Junction Temperature              |      | 150       | °C   |

| T <sub>stg</sub>                                | Storage Temperature                       | -40  | 150       | °C   |

<sup>(1)</sup> Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" are not implied. Exposure to Absolute-Maximum-Rated conditions for extended periods may affect device reliability.

#### 4.2 THERMAL INFORMATION

|                  |                                                             | PGA400-EP |       |

|------------------|-------------------------------------------------------------|-----------|-------|

|                  | THERMAL METRIC                                              | RHH       | UNITS |

|                  |                                                             | 36 PINS   |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance (1)                  | 30.6      |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance <sup>(2)</sup>    | 16.4      |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance (3)                    | 5.4       | 00044 |

| ΨЈТ              | Junction-to-top characterization parameter (4)              | 0.2       | °C/W  |

| ΨЈВ              | Junction-to-board characterization parameter <sup>(5)</sup> | 5.4       |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance (6)            | 0.7       |       |

<sup>(1)</sup> The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

(6) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

<sup>(2)</sup> The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

<sup>(3)</sup> The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

<sup>(4)</sup> The junction-to-top characterization parameter, ψ<sub>JT</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

<sup>(5)</sup> The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

## 4.3 RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER                             | TEST CONDITIONS                                                                   | MIN | TYP | MAX  | UNIT |

|-----------------|---------------------------------------|-----------------------------------------------------------------------------------|-----|-----|------|------|

| $V_{DD}$        | Power supply voltage                  |                                                                                   | 4.5 | 5   | 5.5  | V    |

| I <sub>DD</sub> | Power supply current - normal mode    | $V_{DD}$ = 5V, No load on VBRG, No load on DAC1 and DAC2                          |     |     | 13.6 | mA   |

|                 | Power supply current - low power mode | V <sub>DD</sub> = 5.5V, No load on VBRG, No load on DAC1 and DAC2, AFE turned OFF |     |     | 9.5  | mA   |

| VP_OTP          | OTP programming voltage               |                                                                                   | 7.0 | 7.4 | 7.8  | V    |

| I_VP_OTP        | OTP programming current               | During OTP Programming                                                            |     |     | 3    | mA   |

| tprog_OTP       | OTP programming timing per byte       |                                                                                   | 120 |     |      | μs   |

| T <sub>A</sub>  | Operating ambient temperature         |                                                                                   | -40 |     | 125  | °C   |

|                 | Programming temperature               | OTP or EEPROM                                                                     | -40 |     | 140  | °C   |

|                 | Micro start-up time                   | VDD ramp rate 1V/µs                                                               |     |     | 250  | μs   |

# **5 ELECTRICAL CHARACTERISTICS**

## 5.1 Overvoltage Protection

|                    | PARAMETER                         | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------|-----------------------------------|-----------------|-----|-----|-----|------|

| OV                 | Overvoltage protection threshold  |                 | 5.5 | 6.1 | 7.0 | V    |

| OV <sub>hyst</sub> | Overvoltage protection hysteresis |                 |     | 410 |     | mV   |

## 5.2 Regulators

|            | PARAMETER        | TEST CONDITIONS            | MIN | TYP | MAX | UNIT |

|------------|------------------|----------------------------|-----|-----|-----|------|

| $V_{AVDD}$ | AVDD voltage     | C <sub>AVDD</sub> = 100 nF |     | 3.3 |     | V    |

| I_AVDD     | AVDD current     | V <sub>AVDD</sub> = 3.3 V  |     |     | 5   | mA   |

| V          | DV/DD violations | No EEPROM Programming      |     | 3.3 |     | V    |

| $V_{DVDD}$ | DVDD voltage     | EEPROM Programming         |     | 3.6 |     | V    |

# 5.3 Internal Oscillator and External Crystal Interface

| PARAMETER                        | TEST CONDITIONS               | MIN       | TYP | MAX       | UNIT |  |  |  |

|----------------------------------|-------------------------------|-----------|-----|-----------|------|--|--|--|

| INTERNAL OSCILLATOR              |                               |           |     |           |      |  |  |  |

| Internal Oscillator frequency    | T <sub>amb</sub> = 25 °C      | 38.4      | 40  | 41.6      | MHz  |  |  |  |

| Internal Oscillator frequency    | Accross operating temperature | 36.3      |     | 43.7      | MHz  |  |  |  |

| EXTERNAL 40-MHZ CRYSTAL          |                               | ·         |     | ·         |      |  |  |  |

| Low-level input voltage on XTAL  |                               | -0.3      |     | 0.1× VDD  | V    |  |  |  |

| High-level input voltage on XTAL |                               | 0.7 × VDD |     | VDD + 0.3 | V    |  |  |  |

# 5.4 Sensor Supply

|                                   | PARAMETER                                                  | TEST CONDITIONS                                                            | MIN   | TYP   | MAX   | UNIT |

|-----------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------|-------|-------|-------|------|

| VBRG SUF                          | PPLY FOR RESISTIVE BRIDGE SENSO                            | DRS                                                                        | ı     |       |       |      |

| $V_{BRG}$                         | Supply Voltage                                             | $0.44 \text{ k}\Omega \leq R_{BRG} \leq 20 \text{ k}\Omega$                | 3.2   | 3.33  | 3.4   | V    |

| R <sub>BRG</sub>                  | Resistive Bridge Resistance                                |                                                                            | 0.44  |       | 20    | ΚΩ   |

| $C_{BRG}$                         | Capacitive Load                                            | $R_{BRG} = 20 \text{ k}\Omega$                                             |       |       | 500   | pF   |

|                                   | Line regulation                                            | $V_{DD} = 4.5V, 5.5V, R_{BRG} = 0.44 \text{ k}\Omega$                      | -40   |       | 40    | mV   |

|                                   | Load regulation                                            | $V_{DD} = 5.0 \text{ V}, 10  \mu\text{A} \leq I_{LOAD} \leq 10 \text{ mA}$ | -40   |       | 40    | mV   |

| CAPx SUI                          | PPLY FOR CAPACITIVE SENSORS                                |                                                                            |       |       |       |      |

|                                   |                                                            | CI[2:0] = 000, ICAP_V = 100 mV                                             | -5.3  |       | -4.3  |      |

|                                   |                                                            | CI[2:0] = 001, ICAP_V = 100 mV                                             | -8    |       | -6.6  |      |

|                                   |                                                            | CI[2:0] = 010, ICAP_V = 100 mV                                             | -10.8 |       | -8.8  |      |

|                                   |                                                            | CI[2:0] = 011, ICAP_V = 100 mV                                             | -13.5 |       | -11.1 |      |

|                                   |                                                            | CI[2:0] = 100, ICAP_V = 100 mV                                             | -16.2 |       | -13.3 |      |

|                                   |                                                            | CI[2:0] = 101, ICAP_V = 100 mV                                             | -18.9 |       | -15.5 |      |

|                                   | Supply Current Amplitude on ICAP,<br>T <sub>A</sub> = 25°C | CI[2:0] = 110, ICAP_V = 100 mV                                             | -21.6 |       | -17.8 | μА   |

|                                   |                                                            | CI[2:0] = 111, ICAP_V = 100 mV                                             | -24.4 |       | -20.1 |      |

| CAP_A                             |                                                            | CI[2:0] = 000, ICAP_V = 3.2 V                                              | 4.5   |       | 5.6   |      |

|                                   |                                                            | CI[2:0] = 001, ICAP_V = 3.2 V                                              | 6.9   |       | 8.5   |      |

|                                   |                                                            | CI[2:0] = 010, ICAP_V = 3.2 V                                              | 9.2   |       | 11.3  |      |

|                                   |                                                            | CI[2:0] = 011, ICAP_V = 3.2 V                                              | 11.5  |       | 14.1  |      |

|                                   |                                                            | CI[2:0] = 100, ICAP_V = 3.2 V                                              | 13.6  |       | 16.7  |      |

|                                   |                                                            | CI[2:0] = 101, ICAP_V = 3.2 V                                              | 15.8  |       | 19.2  |      |

|                                   |                                                            | CI[2:0] = 110, ICAP_V = 3.2 V                                              | 18.1  |       | 22.1  |      |

|                                   |                                                            | CI[2:0] = 111, ICAP_V = 3.2 V                                              | 20.4  |       | 24.8  |      |

|                                   | Variation over temperature                                 |                                                                            | -5.0  |       | +5.0  | %    |

|                                   |                                                            | CV[1:0] = 00                                                               | 70    | 90    | 110   |      |

| CPx_V,                            | Capacitive Sensor Drive - Voltage at                       | CV[1:0] = 01                                                               | 255   | 300   | 345   | >/   |

| CRx_V                             | CPx and CRx pins                                           | CV[1:0] = 10                                                               | 425   | 500   | 575   | mV   |

|                                   |                                                            | CV[1:0] = 11                                                               | 595   | 700   | 805   |      |

| SELF OSC                          | ILLATING CURRENT MODE DEMODU                               | ILATOR FOR CAPACITIVE SENSORS                                              |       |       |       |      |

|                                   |                                                            | $CR[1:0] = 00, R_{REF} = 78 \text{ k}\Omega$                               | -1.07 | -1.01 | -0.94 |      |

| D / D                             | Cain in Transieron de la compute de                        | $CR[1:0] = 01, R_{REF} = 78 \text{ k}\Omega$                               | -2.13 | -1.97 | -1.82 | 1/// |

| R <sub>F</sub> / R <sub>REF</sub> | Gain in Transimpedance amplifier                           | $CR[1:0] = 10, R_{REF} = 78 \text{ k}\Omega$                               | -4.24 | -3.93 | -3.63 | V/V  |

|                                   |                                                            | $CR[1:0] = 11, R_{REF} = 78 \text{ k}\Omega$                               | -8.45 | -7.85 | -7.26 |      |

| Cf                                | Feedback Capacitor in<br>Transimpedance amplifier          |                                                                            | 14    | 16    | 18    | pF   |

# 5.5 Temperature Sensor

| PARAMETER                   | TEST CONDITIONS | MIN         | TYP | MAX | UNIT   |

|-----------------------------|-----------------|-------------|-----|-----|--------|

| Temperature Range           |                 | <b>–</b> 55 |     | 125 | °C     |

| Temperature ADC Resolution  |                 |             | 10  |     | bits   |

| Temperature ADC Update Rate |                 |             | 8   |     | ms     |

| Gain (1)                    |                 | 2.7         | 2.8 | 2.9 | LSB/°C |

| Offset (1)                  |                 | -105        |     | -66 | LSB    |

| Total Error                 |                 | -4          |     | 4   | °C     |

(1) The Temperature ADC Value is given by the equation: ADC Code =  $Gain^*Temperature$  (in  $^{\circ}C$ ) + Offset

# 5.6 Analog Front Ends

| PARAMETER                                 | TEST CONDITIONS   | MIN | TYP  | MAX | UNIT  |  |  |

|-------------------------------------------|-------------------|-----|------|-----|-------|--|--|

| STAGE 1 GAIN FOR RESISTIVE BRIDGE SENSORS |                   |     |      |     |       |  |  |

|                                           | Sx_G1[2:0] = 000  |     | 3.0  |     |       |  |  |

|                                           | Sx_G1[2:0] = 001  |     | 4.4  |     |       |  |  |

|                                           | Sx_G1[2:0] = 010  |     | 6.8  |     |       |  |  |

| Coin Stone                                | Sx_G1[2:0] = 011  |     | 10.2 |     | \//\/ |  |  |

| Gain Steps                                | Sx_G1[2:0] = 100  |     | 14.6 |     | V/V   |  |  |

|                                           | Sx_G1[2:0] = 101  |     | 25.5 |     |       |  |  |

|                                           | Sx_G1[2:0] = 110  |     | 34.0 |     |       |  |  |

|                                           | Sx_G1[2:0] = 111  |     | 51.0 |     |       |  |  |

| Bandwidth                                 | -3 dB, Gain = 111 |     | 7    |     | KHz   |  |  |

# 5.7 Stage 2 Gain

| PARAMETER  | TEST CONDITIONS             | MIN   | TYP   | MAX   | UNIT    |  |

|------------|-----------------------------|-------|-------|-------|---------|--|

|            | Sx_G2[4:0] = 00000          | 0.97  | 1.01  | 1.05  |         |  |

|            | Sx_G2[4:0] = 00001          | 1.06  | 1.11  | 1.16  |         |  |

|            | Sx_G2[4:0] = 00010          | 1.18  | 1.23  | 1.28  |         |  |

|            | Sx_G2[4:0] = 00011          | 1.31  | 1.37  | 1.42  |         |  |

|            | Sx_G2[4:0] = 00100          | 1.45  | 1.52  | 1.58  |         |  |

|            | Sx_G2[4:0] = 00101          | 1.61  | 1.68  | 1.76  |         |  |

|            | Sx_G2[4:0] = 00110          | 1.79  | 1.87  | 1.94  |         |  |

|            | Sx_G2[4:0] = 00111          | 1.98  | 2.07  | 2.16  |         |  |

|            | Sx_G2[4:0] = 01000          | 2.20  | 2.29  | 2.39  |         |  |

|            | Sx_G2[4:0] = 01001          | 2.44  | 2.55  | 2.65  |         |  |

|            | Sx_G2[4:0] = 01010          | 2.71  | 2.83  | 2.94  |         |  |

|            | Sx_G2[4:0] = 01011          | 3.00  | 3.13  | 3.26  |         |  |

|            | Sx_G2[4:0] = 01100          | 3.34  | 3.48  | 3.62  |         |  |

|            | Sx_G2[4:0] = 01101          | 3.74  | 3.90  | 4.06  |         |  |

|            | Sx_G2[4:0] = 01110          | 4.12  | 4.30  | 4.48  |         |  |

| Onin Olama | Sx_G2[4:0] = 01111          | 4.61  | 4.81  | 5.01  | \ / \ / |  |

| Gain Steps | Sx_G2[4:0] = 10000          | 5.09  | 5.31  | 5.54  | V/V     |  |

|            | Sx_G2[4:0] = 10001          | 5.67  | 5.92  | 6.16  |         |  |

|            | Sx_G2[4:0] = 10010          | 6.26  | 6.52  | 6.79  |         |  |

|            | Sx_G2[4:0] = 10011          | 6.93  | 7.23  | 7.53  |         |  |

|            | Sx_G2[4:0] = 10100          | 7.70  | 8.04  | 8.37  |         |  |

|            | Sx_G2[4:0] = 10101          | 8.57  | 8.95  | 9.32  |         |  |

|            | Sx_G2[4:0] = 10110          | 9.54  | 9.96  | 10.37 |         |  |

|            | Sx_G2[4:0] = 10111          | 10.62 | 11.06 | 11.51 |         |  |

|            | Sx_G2[4:0] = 11000          | 11.76 | 12.27 | 12.79 |         |  |

|            | Sx_G2[4:0] = 11001          | 13.02 | 13.58 | 14.15 |         |  |

|            | Sx_G2[4:0] = 11010          | 14.48 | 15.10 | 15.72 |         |  |

|            | Sx_G2[4:0] = 11011          | 16.03 | 16.71 | 17.40 |         |  |

|            | Sx_G2[4:0] = 11100          | 17.72 | 18.53 | 19.34 |         |  |

|            | Sx_G2[4:0] = 11101          | 19.61 | 20.49 | 21.37 |         |  |

|            | Sx_G2[4:0] = 11110          | 21.72 | 22.70 | 23.68 |         |  |

|            | Sx_G2[4:0] = 11111          | 23.85 | 25.06 | 26.28 | -       |  |

| Bandwidth  | -3 dB, Gain Setting = 11111 | 120   |       |       | KHz     |  |

## 5.8 Offset and Offset TC Compensation

| PARAMETER                         | TEST CONDITIONS                                         | MIN  | TYP  | MAX  | UNIT         |

|-----------------------------------|---------------------------------------------------------|------|------|------|--------------|

| Offset Compensation Low           | Offset Setting = 0x000, Stage 1<br>Gain Setting = 0b000 | -385 | -324 | -279 | mV           |

| Offset Compensation High          | Offset Setting = 0x3FF, Stage 1<br>Gain Setting = 0b000 | 279  | 324  | 385  | mV           |

| Offset Compensation Resolution    | Stage 1 Gain Setting = 0b000                            | 0.59 |      | 0.72 | mV/step      |

| Offset TC Compensation Low        | Offset TC Setting = 0x00, Stage 1<br>Gain Value = 0b000 |      | -371 |      | μV/°C        |

| Offset TC Compensation H igh      | Offset TC Setting= 0x3F, Stage 1<br>Gain Value = 0b000  |      | 361  |      | μV/°C        |

| Offset TC Compensation Resolution | Stage 1 Gain Value = 0b000                              |      | 11.6 |      | μV/V/°C/step |

| Reference Temperature             |                                                         |      | 22   |      | °C           |

# 5.9 Analog to Digital Converter

| PARAMETER                          | TEST CONDITIONS          | MIN   | TYP   | MAX   | UNIT     |

|------------------------------------|--------------------------|-------|-------|-------|----------|

| ADC BUFFER FOR 16-BIT AD CONVERTER | 1                        |       |       |       |          |

| Gain                               |                          | 1.9   | 2     | 2.1   | V/V      |

| DC Level Shift                     | ADC_BUF bit = 1          | -1.74 | -1.65 | -1.55 | V        |

| DC Offset                          |                          | -15   |       | 15    | mV       |

| ADC BUFFER FOR 10-BIT AD CONVERTER | 2                        |       |       |       | •        |

| VIN3 Input Voltage Range           |                          | 0.425 |       | 1.7   | V        |

| Gain                               |                          | 1.09  | 1.15  | 1.21  | V/V      |

| DC Offset                          |                          | -15   |       | 15    | mV       |

| VIN3 VOLTAGE VERSUS ADC CODE       |                          |       |       |       |          |

| Gain <sup>(1)</sup>                |                          | 740   | 760   | 780   | LSB/V    |

| Offset <sup>(1)</sup>              |                          | -850  | -820  | -790  | LSB      |

| Gain Temperature Coefficient       | T <sub>amb</sub> = 25 °C |       | 0.02  |       | LSB/V/°C |

| Offset Temperature Coefficient     | T <sub>amb</sub> = 25 °C |       | -0.02 |       | LSB/°C   |

| Integral Nonlinearity              |                          | -1    |       | 1     | LSB      |

<sup>(1)</sup> ADC Code = Gain\*VIN3+Offset

## 5.10 One Wire Interface

|                       | PARAMETER                         | TEST CONDITIONS | MIN       | TYP | MAX       | UNIT               |

|-----------------------|-----------------------------------|-----------------|-----------|-----|-----------|--------------------|

|                       | Communication Baud Rate           |                 | 2400      |     | 115000    | Bits Per<br>Second |

| OWI_EN                | OWI Enable                        |                 | 6.5       |     | 7.0       | V                  |

| OWI_EN <sub>hys</sub> | OWI Enable Hysteresis             |                 |           | 50  |           | mV                 |

|                       | Internal Pullup                   |                 |           | 10  |           | ΚΩ                 |

|                       | Activation Signal Pulse Low time  |                 | 12        |     |           | ms                 |

|                       | Activation Signal Pulse High time |                 | 12        |     |           | ms                 |

| OWI_VIH               | OWI Transceiver Rx Threshold      |                 | 0.7 × VDD |     | VDD + 0.3 | V                  |

| OWI_VIL               | OWI Transceiver Rx Threshold      |                 | -0.3      |     | 0.3 × VDD | V                  |

| OWI_VOH               | OWI Transceiver Tx Threshold      | VDD = 5 V       | 4.0       |     |           |                    |

| OWI_VOL               | OWI Transceiver Tx Threshold      | VDD = 5 V       |           |     | 0.8       | V                  |

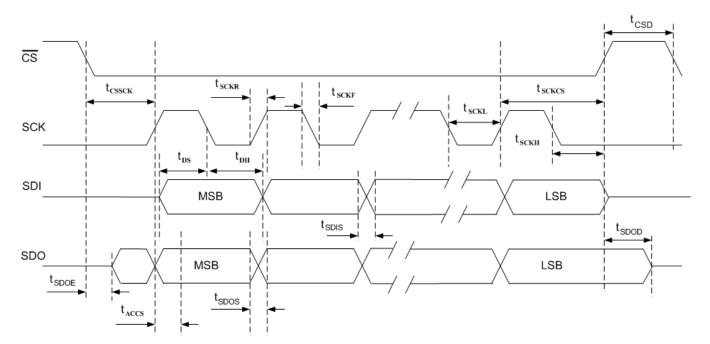

# 5.11 Serial Peripheral Interface (SPI) Interface

over operating free-air temperature range (unless otherwise noted)

|          | PARAMETER                | TEST CONDITIONS | MIN       | TYP | MAX       | UNIT |

|----------|--------------------------|-----------------|-----------|-----|-----------|------|

| $V_{IH}$ | High-level input voltage |                 | 0.7 × VDD |     | VDD + 0.3 | V    |

**ELECTRICAL CHARACTERISTICS**

# Serial Peripheral Interface (SPI) Interface (continued)

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                              | TEST CONDITIONS | MIN  | TYP | MAX       | UNIT |

|---------------------|----------------------------------------|-----------------|------|-----|-----------|------|

| V <sub>IL</sub>     | Low-level input voltage                |                 | -0.3 |     | 0.3 × VDD | V    |

| V <sub>OH</sub>     | High-level output voltage              |                 | 4.0  |     |           | V    |

| $V_{OL}$            | Low-level output voltage               |                 |      |     | 0.8       | V    |

| f <sub>SCK</sub>    | SPI Frequency                          |                 |      |     | 4         | MHz  |

| tcssck              | CS Low to First SCK Rising Edge        |                 | 25   |     |           | ns   |

| t <sub>SCKCS</sub>  | Last SCK Rising Edge to CS Rising Edge |                 | 125  |     |           | ns   |

| t <sub>CSD</sub>    | CS Disable Time                        |                 | 500  |     |           | ns   |

| t <sub>DS</sub>     | SDI Setup Time                         |                 | 25   |     |           | ns   |

| t <sub>DH</sub>     | SDI Hold Time                          |                 | 25   |     |           | ns   |

| t <sub>SDIS</sub>   | SDI Fall/Rise Time                     |                 |      |     | 7         | ns   |

| t <sub>SCKR</sub>   | SCK Rise Time                          |                 |      |     | 7         | ns   |

| t <sub>SCKF</sub>   | SCK Fall Time                          |                 |      |     | 7         | ns   |

| t <sub>SCKH</sub>   | SCK High Time                          |                 | 125  |     |           | ns   |

| t <sub>SCKL</sub>   | SCK Low Time                           |                 | 125  |     |           | ns   |

| t <sub>SDOE</sub>   | SDO Enable Time                        |                 | 15   |     |           | ns   |

| t <sub>ACCS</sub>   | SCK Rising Edge to SDO Data Valid      |                 | 15   |     |           | ns   |

| t <sub>SDOD</sub>   | SDO Disable Time                       |                 |      |     | 15        | ns   |

| t <sub>SDOS</sub>   | SDO Rise/Fall Time                     |                 | 3    |     | 11        | ns   |

| C <sub>L(SDO)</sub> | Capacitive Load for Data Output (SDO)  |                 |      | 10  |           | pF   |

Figure 5-1. SPI Timing

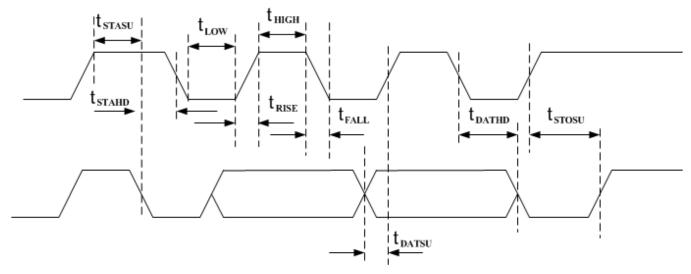

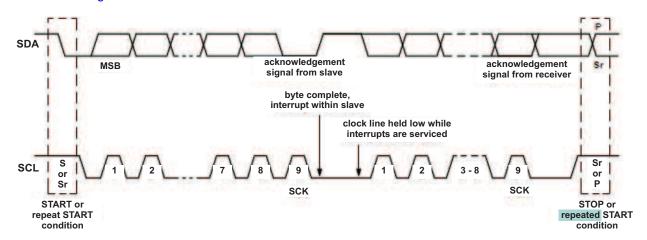

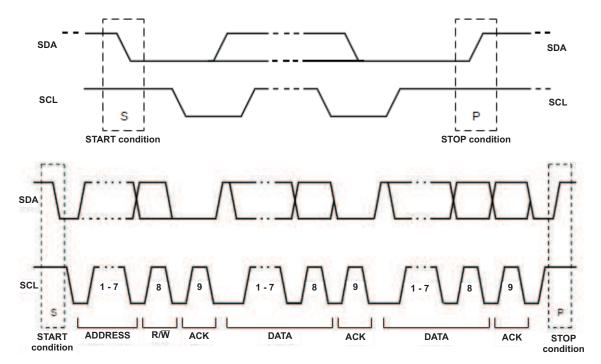

## 5.12 I2C Interface

|          | PARAMETER                | TEST CONDITIONS | MIN       | TYP MAX   | UNIT |

|----------|--------------------------|-----------------|-----------|-----------|------|

| $V_{IH}$ | High-level input voltage |                 | 0.7 × VDD | VDD + 0.3 | V    |

| $V_{IL}$ | Low-level input voltage  |                 | -0.3      | 0.3 × VDD | V    |

11

# **I2C Interface (continued)**

|                    | PARAMETER                   | TEST CONDITIONS | MIN  | TYP | MAX | UNIT |

|--------------------|-----------------------------|-----------------|------|-----|-----|------|

| V <sub>OH</sub>    | High-level output voltage   |                 | 4.0  |     |     | V    |

| V <sub>OL</sub>    | Low-level output voltage    |                 |      |     | 0.8 | V    |

| f <sub>SCL</sub>   | SCL clock frequency         |                 |      |     | 400 | KHz  |

| t <sub>STASU</sub> | START condition set-up time |                 | 500  |     |     | ns   |

| t <sub>STAHD</sub> | START condition hold time   |                 | 500  |     |     | ns   |

| $t_{LOW}$          | SCL low time                |                 | 1.25 |     |     | μs   |

| t <sub>HIGH</sub>  | SCL high time               |                 | 1.25 |     |     | μs   |

| t <sub>RISE</sub>  | SCL and SDA rise time       |                 |      |     | 7   | ns   |

| t <sub>FALL</sub>  | SCL and SDA fall time       |                 |      |     | 7   | ns   |

| t <sub>DATSU</sub> | Data setup time             |                 | 500  |     |     | ns   |

| t <sub>DATHD</sub> | Data hold time              |                 | 500  |     |     | ns   |

| t <sub>STOSU</sub> | STOP condition set-up time  |                 | 500  |     |     | ns   |

Figure 5-2. I<sup>2</sup>C Timing

# 5.13 Non-Volatile Memory

| PARAMETER                        | TEST CONDITIONS                   | MIN | TYP | MAX  | UNIT   |

|----------------------------------|-----------------------------------|-----|-----|------|--------|

| OTP                              |                                   |     | 8   |      | KB     |

| OTP Number of Erase/Write Cycles | Erase using UV light              |     |     | 10   | Cycles |

| EEPROM                           | Programmable using SPI or OWI     |     | 89  |      | Bytes  |

| EEFROIVI                         | Number of bytes writeable by 8051 |     | 16  |      | Bytes  |

| EEPROM Erase/Write Cycles        |                                   |     |     | 1000 | Cycles |

## 5.14 GPIO

|                 | PARAMETER                 | TEST CONDITIONS                                                                 | MIN       | TYP MAX   | UNIT |

|-----------------|---------------------------|---------------------------------------------------------------------------------|-----------|-----------|------|

| $V_{IH}$        | High-level input voltage  | $R_{LOAD} \ge 10 \text{ k}\Omega \text{ to } V_{DD} \text{ or to } 0 \text{ V}$ | 0.7 × VDD | VDD + 0.3 | V    |

| $V_{IL}$        | Low-level input voltage   | $R_{LOAD} \ge 10 \text{ k}\Omega \text{ to } V_{DD} \text{ or to } 0 \text{ V}$ | -0.3      | 0.3 × VDD | V    |

| $V_{OH}$        | High-level output voltage | I <sub>OH</sub> = 1 mA                                                          | 4.0       |           | V    |

| $V_{OL}$        | Low-level output voltage  | $I_{OL} = -1 \text{ mA}$                                                        |           | 0.8       | V    |

| I <sub>OH</sub> | High-level output current | V <sub>OH</sub> = 4.5 V                                                         |           | 1         | mA   |

| I <sub>OL</sub> | Low-level output current  | V <sub>OL</sub> = 0.5 V                                                         |           | 1         | mA   |

| $R_{PU}$        | Pull-up resistance        |                                                                                 |           | 160       | kΩ   |

# 5.15 DAC1 and DAC2 Output

| PARAMETER                    | TEST CONDITIONS                                                                                                   | MIN  | TYP MA | X  | UNIT |

|------------------------------|-------------------------------------------------------------------------------------------------------------------|------|--------|----|------|

| Settling time                | DAC Code 000h to FFFh step.Output is 90% of Full Scale. $R_{LOAD} = 5 \text{ k}\Omega, C_{LOAD} = 500 \text{ pF}$ |      |        | 7  | μs   |

| Zero scale error             | DAC code = 000h, $I_{DAC}$ = 1.5 mA                                                                               |      |        | 16 | mV   |

| Full scale voltage           | Output when DAC code is FFFh, I <sub>DAC</sub> = - 1.5 mA                                                         | 4.85 | 4.9    | 95 | V    |

| Output current amplitude     | DAC Code = 0FFFh , DAC Code = 0000h                                                                               |      | 1      | .5 | mA   |

| Short circuit source current | VDD = 5V, DAC code = 000h                                                                                         | -34  | ='     | 10 | mA   |

| Short circuit sink current   | VDD = 5V, DAC code = FFFh                                                                                         | 10   | ;      | 34 | mA   |

| INL (best-fit line)          |                                                                                                                   | -3.5 | 3      | .5 | LSB  |

# **5.16 Input Capture and Output Compare**

|                 | PARAMETER                           | TEST CONDITIONS                                                                 | MIN       | TYP | MAX      | UNIT    |

|-----------------|-------------------------------------|---------------------------------------------------------------------------------|-----------|-----|----------|---------|

| INPUT (         | CAPTURE PORTS                       |                                                                                 | -         |     |          |         |

| V <sub>IH</sub> | High-level input voltage            | $R_{LOAD} \ge 10 \text{ k}\Omega \text{ to } V_{DD} \text{ or to } 0 \text{ V}$ | 0.7 × VDD | V   | DD + 0.3 | V       |

| V <sub>IL</sub> | Low-level input voltage             | $R_{LOAD} \ge 10 \text{ k}\Omega \text{ to } V_{DD} \text{ or to } 0 \text{ V}$ | -0.3      | 0   | .3 × VDD | V       |

|                 |                                     | 10_20_MHZ bit = 1                                                               |           | 10  |          | N.41.1- |

|                 | Input capture timer clock frequency | 10_20_MHZ bit = 0                                                               |           | 20  |          | MHz     |

|                 | Input capture timer bits            |                                                                                 |           | 16  |          | Bits    |

| OUTPU           | T COMPARE PORTS                     |                                                                                 |           |     |          |         |

| V <sub>OH</sub> | High-level output voltage           | I <sub>OH</sub> = 1 mA                                                          | VDD - 1.0 |     |          | V       |

| V <sub>OL</sub> | Low-level output voltage            | I <sub>OL</sub> = -1 mA                                                         |           |     | 0.8      | V       |

|                 | Output assessed the second          | 10_20_MHZ bit = 1                                                               |           | 10  |          | N.41.1- |

|                 | Output compare timer frequency      | 10_20_MHZ bit = 0                                                               |           | 20  |          | MHz     |

|                 | Output compare timer bits           |                                                                                 |           | 16  |          | Bits    |

| I <sub>OH</sub> | High-level output current           |                                                                                 |           |     | 1        | mA      |

| I <sub>OL</sub> | Low-level output current            |                                                                                 |           |     | 1        | mA      |

#### 5.17 Diagnostics

|                       | PARAMETER                                                        | TEST CONDITIONS | MIN   | TYP   | MAX   | UNIT |

|-----------------------|------------------------------------------------------------------|-----------------|-------|-------|-------|------|

|                       | 8051 Software watchdog                                           |                 |       | 500   |       | ms   |

|                       | Main clock normal operation range                                |                 | 35    | 40    | 45    | MHz  |

| VBRG_OV               | Sensor supply over voltage threshold                             |                 | 3.55  | 3.65  | 3.75  | V    |

| VBRG_UV               | Sensor supply under voltage threshold                            |                 | 2.9   | 3.0   | 3.11  | V    |

|                       | AVDD OV threshold                                                |                 | 3.7   |       | 3.95  | V    |

|                       | AVDD UV threshold                                                |                 | 2.72  |       | 3.1   | V    |

| Sensor <sub>OV</sub>  | Output overvoltage threshold for gain stage 1 and 2              |                 | 2.3   | 2.5   | 2.6   | V    |

| Sensor <sub>UV</sub>  | Output undervoltage threshold for gain stage 1 and 2             |                 | 0.7   | .85   | 1.0   | V    |

| f_cap <sub>High</sub> | Capacitive sensor interface clock high frequency fault threshold |                 | 1.5   |       | 2.5   | MHz  |

| f_cap <sub>Low</sub>  | Capacitive sensor interface clock low frequency fault threshold  |                 | 30    |       | 50    | kHz  |

|                       | EEPROM CHG PUMP overvoltage threshold                            |                 |       | 14.65 |       | V    |

|                       | EEPROM CHG PUMP undervoltage threshold                           |                 |       | 11.45 |       | V    |

|                       | DAC loop back voltage gain                                       |                 | 0.537 | 0.545 | 0.557 | V/V  |

|                       | Open wire leakage current 1 - open VDD with pull-up on VOUT1     |                 |       |       | 2     | μΑ   |

|                       | Open wire leakage current 2 - open GND with pull-down on VOUT1   |                 |       |       | 20    | μΑ   |

#### 6 FUNCTIONAL DESCRIPTIONS

In this section, individual blocks in the Section 2 are described in more detail.

### 6.1 Overvoltage / Reverse Voltage Protection Block

The PGA400-EP includes an Overvoltage and Reverse Voltage Protection block. This block protects the device from overvoltage and reverse-battery conditions on the external power supply. In this block, a control circuit monitors the input supply line for reverse-battery and overvoltage fault conditions protects the device if these voltage conditions occur on the external power supply.

## 6.2 Linear Regulators and Bandgap + Current Blocks

The PGA400-EP contains two precision low-drift bandgap supply voltage references for other blocks of the device. One bandgap provides the reference voltage for internal linear regulators that supply AVDD and DVDD. The other bandgap reference provides the voltage reference for the all the other internal circuitry, including sensor supply regulators, sensor offset compensation, etc.

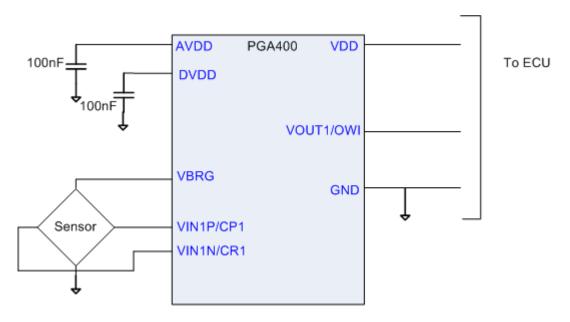

The PGA400-EP has two main linear regulators: AVDD Regulator and DVDD Regulator. The AVDD regulator provides the 3.3 V voltage source for internal analog circuitry while the DVDD regulator provides the 3.3 V regulated voltage for the digital circuitry. The user needs to connect bypass capacitors of 100nF on both the AVDD and DVDD pins of the device.

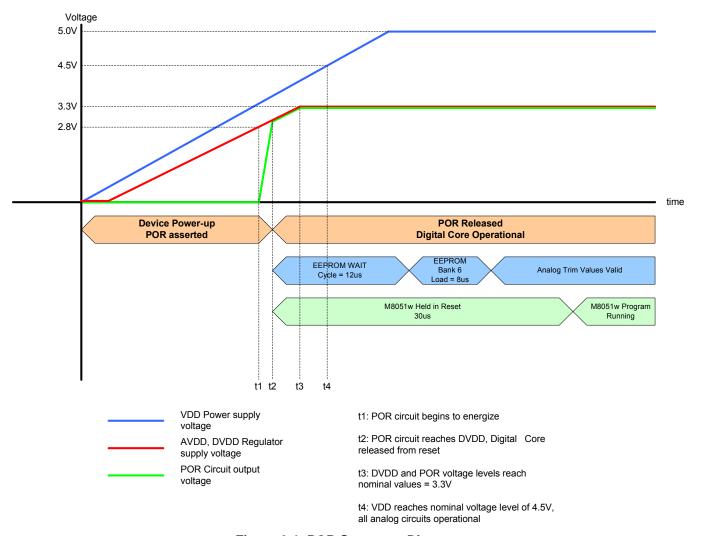

Figure 6-1 shows the Power-On Reset sequence for AVDD and DVDD with respect to the voltage applied to the VDD pin.

Figure 6-1. POR Sequence Diagram

#### 6.3 Internal OSC/XTAL I/F Block

The device includes an internal 40 MHz oscillator, which by default provides the internal clocks required. The device can also be configured to use an external 40-MHz crystal as a time base via the XTAL\_EN bit in the Sensor Control Register (SENCTRL). When the XTAL\_EN bit is set high, the internal 40-MHz oscillator is disabled and control of the main system clock is driven by the external clock source connected to the XTAL pin.

#### NOTE

Do not use the XTAL pin as an output for sourcing a clock signal to other devices.

## 6.4 Sensor Voltage Supply Block

The Sensor Voltage Supply block of the PGA400-EP supplies both the VBRG output for resistive bridge sensors and the ICAP supply for capacitive sensors.

## 6.4.1 VBRG Supply for Resistive Bridges

The VBRG pin on the PGA400-EP is a 3.3-V nominal output supply from a linear regulator with a precise internal temperature independent band-gap reference.

## 6.4.2 ICAP Supply for Capacitive Sensors

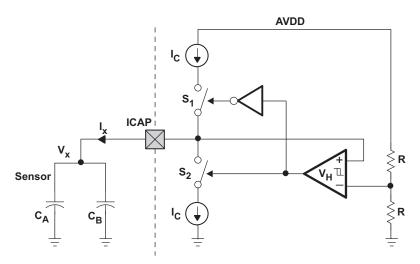

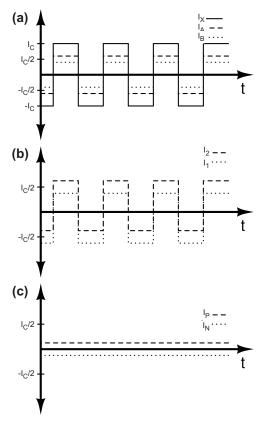

A functional schematic of the capacitive sensor drive circuit is shown in Figure 6-2. The common node of the sensor capacitances is tied to the ICAP pin and the current and voltage at this point are referred to as  $I_X$  and  $V_X$  respectively. For the sake of understanding the operation of the drive circuit by itself, the other terminals of the sensor may be treated as if they were tied to ground, because the sensor signal measurement circuit regulates the voltage at these nodes. This circuit is essentially a relaxation oscillator where the capacitance of the sensor, the charging current  $I_C$ , and the comparator hysteresis  $V_H$  determine the frequency of oscillation.

Figure 6-2. Capacitive Sensor Drive Circuit

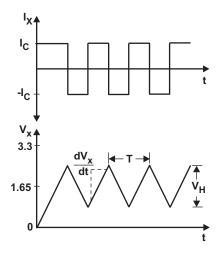

To illustrate the circuit operation, the sensor voltage  $V_X$  is initially set to 0 V. In this state, the positive terminal of the hysteretic comparator is lower than its negative reference terminal, producing a logical zero at the output. This results is switch S2 is open and switch S1 is closed, allowing the upper current source to charge the sensor capacitance. Figure 6-3 shows the resulting waveform. Equation 1 calculates the linear ramp up slope of the voltage,  $V_X$ :

$$\frac{dV_x}{dt} = \frac{1_C}{C_A + C_B} \tag{1}$$

After  $V_X$  is charged up to the high threshold of the comparator, the circuit inverts the states of switches  $S_1$  and  $S_2$ . By closing  $S_2$  and opening  $S_1$  the lower current source begins to discharge the sensor capacitances, making  $V_X$  ramp down with an equal but opposite rate as before. Once  $V_X$  reaches the low threshold of the comparator, the circuit again inverts the states of the switches and returns to the positive charging state. This process of charging and discharging repeats with a period characterized as shown in Equation 2.

$$T = \frac{2 \cdot V_H}{I_C} \cdot (C_A + C_B) \tag{2}$$

Both the comparator hysteresis voltage  $V_H$  and capacitor charging current  $I_C$  are configurable to allow control of the oscillation period for a particular sensor. Bits CV[1..0] in the Capacitive Sensor Settings Register (CAPSEN) can be used to set  $V_H$ .  $V_H$  can be set between 100 mV and 700 mV with four possible steps. Bits CI[2..0] in the Capacitive Sensor Settings Register (CAPSEN) can be used to set  $I_C$ , with possible values between 5  $\mu A$  and 22  $\mu A$  with eight possible steps.

#### NOTE

For capacitive sensors, one common set of configurations registers are implemented. If different settings are needed for the two capacitive sensors, then the software must dynamically update the register values.

Figure 6-3. Capacitive Sensor Drive Waveforms

### 6.5 Internal Temperature Block and External Temperature Sensing

The device has the ability to perform temperature compensation via an internal or external temperature sensor. The user can select the source of the sensor with the TEMP\_SEN bit in the Sensor Control Register (SENCTRL). When the TEMP\_SEN bit is set to "0" the internal temperature sensor is used, and when the TEMP\_SEN bit is set to "1" the external temperature sensor is used.

## 6.5.1 Internal Temperature Sensor

The device contains an internal temperature sensor which is converted by an ADC and made available to the 8051 microprocessor so that appropriate temperature compensation algorithms can be implemented in software. The nominal relationship between the device temperature and the ADC Code is shown in Equation 3.

(3)

#### 6.5.2 External Temperature Sensor

The device accepts a temperature from an external temperature sensor via the VIN3 pin. The input temperature needs to be in the form of a voltage.

#### **NOTE**

The Offset TC block has been configured to operate with the internal temperature sensor transfer function. If an external temperature sensor is used and the user needs to use Offset TC compensation, then the temperature-to-voltage transfer function of the external temperature sensor has to match the transfer function of the internal temperature sensor.

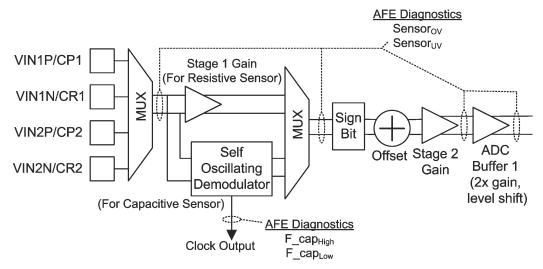

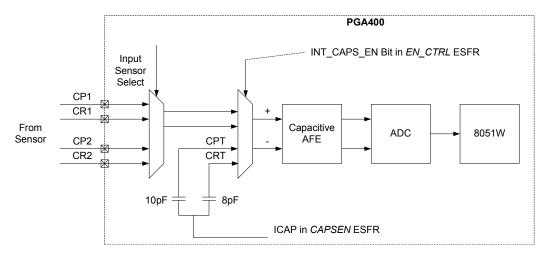

## 6.6 Using the Analog Front End

The PGA400 can be used to interface with Resistive Bridge Sensors as well as Capacitive Sensors. To enable multiple sensors of either type a series of muxes are used. These muxes are controlled by the Sensor Control Register (SENCTRL) and Capacitve Sensor Setting Register (CAPSEN).

The SEN\_TYP bit of the Capacitive Sensor Settings Register (CAPSEN) configures the device to be used with either resisitive or capacitive sensor types. When this bit is set to '0', the device is configured for capacitive sensors and when the bit is set to "1" the device is configured for resistive bridge sensors. When either front-end is selected, the other option is disabled and placed in a low quiescent current state.

The Analog Front End (AFE) can also be configured to measure two sensors sequentially. This is controlled via the SEN\_CHNL bit in the Sensor Control Register (SENCTRL). When this bit is set to '0', the analog MUX at the input of the AFE is switched to pass the signals present at VIN1P and VIN1N pins. For capacitive sensors, the capacitive sensor drive current is also applied to the ICAP1 pin. When this bit is set to '1', the VIN2P, VIN2N and ICAP2 pins become active. The SEN\_CHNL bit also controls which External Special Function Registers (ESFRs) are applied to the Stage 1 Gain, Stage 2 Gain, Offset TC and the Sign bits.

In addition the sensor supply regulator can be independently enabled or disabled via the VBRG\_EN bit in the Sensor Control Register (SENCTRL). This allows the VBRG 3.3 V output to be used with external temperature sensors while the AFE is configured in capacitive sensor mode. For more information on programming the PGA400-EP please refer to the

## 6.7 Stage 1 Gain Block

When the device is configured to interface with resistive sensors, the first gain block that the signal passes through in the AFE is the Stage 1 Gain block. This gain block is designed with precision, low drift, low flicker noise amplifiers.

The gain of this stage is adjustable to accommodate sensors with a wide-range of signal spans and can be set from 3V/V to 51V/V in 8 possible steps. The Stage 1 Gain has two independent registers, Sensor 1 Gain Register (SEN1GAIN) and Sensor 2 Gain Register (SEN2GAIN), so that two different resistive sensors can be connected with different gain settings. For Stage 1 Gain settings use either the S1\_G1 bits or the S2\_G2 bits in the registers mentioned above. The gain setting that is used depends on the SEN\_CHNL bit in Sensor Control Register (SENCTRL).

Table 6-1 outlines the ranges of of resistive bridge sensor characteristics that are compatible.

| PARAMETER                                                    | CONDITION                      | MIN  | TYP MAX | UNIT    |

|--------------------------------------------------------------|--------------------------------|------|---------|---------|

| Resistive bridge resistance                                  | -40°C ≤ T <sub>A</sub> ≤ 150°C | 2    | 20      | ΚΩ      |

| Resistive bridge resistance TC                               |                                | -350 | 4800    | PPM/°C  |

| Resistive bridge offset (compensated in Analog Front End)    | T <sub>A</sub> = 25°C          | -33  | 33      | mV/V    |

| Resistive bridge offset TC (compensated in Analog Front End) |                                | -40  | 40      | μV/V/°C |

| Resistive bridge span                                        | T <sub>A</sub> = 25°C          | 1.4  | 75      | mV/V    |

Table 6-1. Target Resistive Bridge Sensors

#### 6.8 Self Oscillating Demodulator Block

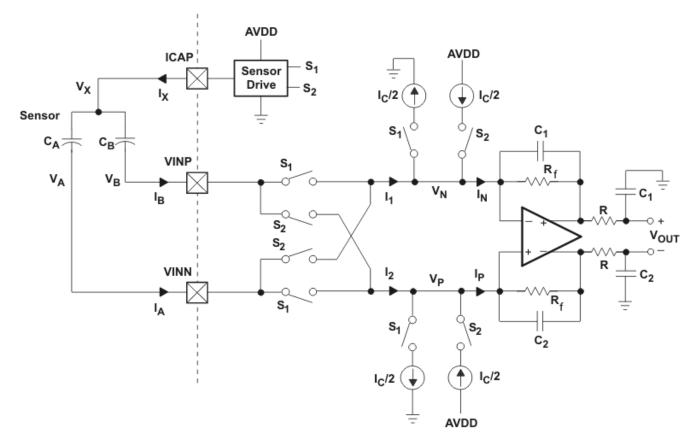

Figure 6-4 shows an essential schematic of the capacitive sensor signal measurement circuit. The Sensor Voltage Supply block discussed in is depicted only as a functional block called Sensor Drive that provides the sensor drive current via the ICAPx pin and the clock signals  $S_1$  and  $S_2$  that are used by the synchronous demodulator in the measurement circuit. As with the ICAP supply circuitry the demodulator block circuitry toggles between two states during normal operation. In one state the  $S_1$  switches are closed while the  $S_2$  switches are open and in the other state the  $S_1$  switches are open while the  $S_2$  switches are closed.

Figure 6-4. Capacitive Sensor Signal Measurement Circuit

To illustrate the operation of the circuit, assume that it has been given sufficient time to settle and is now operating in its normal steady-state mode of operation. During the positive charging phase,  $I_X$  is positive and the  $S_1$  switches are closed. In this state, the amplifier seeks to regulate its input terminals to the same potential, creating a virtual ground at the VINP and VINN pins. This allows  $I_X$  to be expressed in Equation 4 as:

$$I_X = (C_A + C_B) \cdot \frac{dV_X}{dt} \tag{4}$$

In a similar manner, Equation 5 describes the currents through  $C_{\text{A}}$  and  $C_{\text{B}}$  and the difference between these currents.

$$I_A = C_A \cdot \frac{dV_X}{dt} \tag{5}$$

$$I_B = C_B \cdot \frac{dV_X}{dt} \tag{6}$$

$$\Delta I = (I_A - I_B) = (C_A - C_B) \bullet \frac{dV_X}{dt} = I_X \bullet \left(\frac{C_A - C_B}{C_A + C_B}\right)$$

(7)

The drive current is split between the capacitors in proportion to their relative difference. Measuring  $\Delta I$  provides a means to infer the value of the difference in capacitance ( $C_A - C_B$ ) or the value of one of the capacitors if the other is known. Also, driving the sensor with a current source and measuring the resulting difference in current has the benefit of being fully differential and thus less susceptible to common-mode disturbances and non-idealities. Note that the expressions for  $I_A$  and  $I_B$  may are rewritten in terms of common-mode and differential-mode components in Equation 8 and Equation 9.

$$I_A = \frac{I_X}{2} + \frac{\Delta I}{2} \tag{8}$$

$$I_B = \frac{I_X}{2} - \frac{\Delta I}{2} \tag{9}$$

The capacitive sensor signal measurement circuit extracts and amplifies  $\Delta I$ . Figure 6-5 illustrates the current waveforms at different points in the circuit of Figure 6-4. The currents into and out of the sensor are shown on axis (a). Initially, the circuit is in the discharge phase where  $I_X$  is negative and  $S_2$  switches are closed. After some time, the state switches to the charge phase where the  $S_1$  switches are closed. This process of changing the state of the circuit continues periodically with a frequency set by the sensor drive circuit.

During each half cycle the  $I_X$  current is split into the individual capacitor currents  $I_A$  and  $I_B$ . As shown in Figure 6-5(b), while the  $S_1$  switches are closed  $I_2 = I_A$  and  $I_1 = I_B$ , but when the  $S_2$  switches are closed the currents are inverted such that  $I_2 = I_B$  and  $I_1 = I_A$ . Because the sign of  $I_X$  is also changing, the difference between  $I_2$  and  $I_1$  remains constant and equal to  $\Delta I$  (ignoring the glitches that occur at phase transitions).

While the  $S_1$  switches are closed, half the sensor drive current ( $I_C/2$ ) is subtracted from  $I_2$  and  $I_1$  and while the  $S_2$  switches are closed, half the sensor drive current is added to them. This removes the cycle-to-cycle offset in Figure 6-5(b), delivering the DC currents  $I_P$  and  $I_N$  to the trans-impedance amplifier, as shown in Figure 6-5(c) where  $I_P - I_N = \Delta I$ . For low frequency signals, the output voltage of the amplifier is shown in Equation 10.

$$V_{out} = R_{\int} \bullet \Delta I = R_{\int} \bullet I_{C} \bullet \left( \frac{C_A - C_B}{C_A + C_B} \right)$$

$$\tag{10}$$

For a given sensor, the drive current  $I_C$  should be adjusted to keep  $V_{OUT}$  < 1.65 V over the expected operating conditions of the sensor to avoid saturating the ADC input.

#### **NOTE**

for some types of wide span sensors, it may be necessary to reduce the gain set by the value of  $R_{\rm f}$  in the transimpedance amplifier. The drive current  $I_{\rm C}$  and feedback resistance  $R_{\rm f}$  can be adjusted via Capacitive Sensor Settings Register (CAPSEN).

Figure 6-5. Current Waveforms in the Sensor Signal Measurement Circuit

This process of changing the state of the circuit continues periodically with a frequency set by the sensor drive circuit described in Equation 11.

$$f = \frac{I_C}{2 \cdot V_H \cdot (C_A + C_B)} \tag{11}$$

BEcause the op-amp must settle at each switching cycle, there is an upper bound imposed on the sensor drive frequency. Using a minimum half-cycle time of seven times the op-amp settling time and a minimum op-amp GBW of 7 MHz, shows the following upper bound on the switching frequency:

$$f_{\text{MAX}} \leq 800 \text{ kHz}$$

In reality, there are glitches and residual up-converted noise in the  $I_P$  and  $I_N$  signals. For this reason, the trans-impedance amplifier has a low-pass characteristic, with one pole set by the feedback elements  $R_f$  and  $C_f$ , and a second pole at the output set by R and the same capacitance  $C_f$ . For most sensor types, R is equal to  $R_f$ . In this case, the frequency dependent trans-impedance may be expressed as shown in Equation 12.

$$Z(s) = \frac{R_f}{1 + s \cdot R_f \cdot C_f)^2} \Omega$$

(12)

Where with nominal values of  $R_f = 625 \text{ k}\Omega$  and  $C_f = 16 \text{ pF}$ , the corner frequency of the filter is 15.9 kHz. If the minimum permissible ripple suppression is chosen to be 40 dB at the switching frequency, and the corner frequency is rounded up to 20 kHz, illustrates the lower bound on the switching frequency:

$f_{\min} \ge 200 \text{ kHz}$

For a given sensor, the drive circuit comparator hysteresis value  $V_H$  and the drive current  $I_C$  should be chosen so that the switching frequency remains within the range of 200 to 800 kHz as the sensor capacitance varies within its expected range.

Table 6-2 outlines the ranges of compatible capacitive bridge sensor characteristics.

CONDITION UNIT **PARAMETER** MIN MAX Capacitive sensor initial capacitance 310 10 pF (Cp+Cr) Capacitive sensor offset (Cp,0-Cr,0)/(Cp,0+Cr,0)-0.160.16 (compensated in Analog Front End) Capacitive sensor span (Cp,100 - Cr,100)/(Cp,100 + Cr,100)0.04 1.00 %Cv,0/ 0.8 Capacitive sensor offset TC °C

**Table 6-2. Target Capacitive Sensors**

## 6.8.1 Configuring the Capacitive Sensor Interface for a Particular Sensor

A general procedure for choosing what values to use for the capacitive sensor drive current ( $I_C$ ), drive voltage comparator hysteresis ( $V_H$ ) and trans-impedance ( $R_f$ ) is the following:

- Find the values of I<sub>C</sub> that maintain V<sub>OUT</sub> below 1.65 V for the maximum sensor span plus offset

- Using the largest allowed value for  $I_C$  and the minimum and maximum total sensor capacitance  $(C_A+C_B)$ , find a value for  $V_H$  that maintains the switching frequency within the range of 200 kHz to 800 kHz

- If the frequency constraints cannot be met, reduce the value of I<sub>C</sub> and iterate to find an optimal solution

This procedure can be applied to configure the capacitive sensor interface with total capacitances ranging from 10 pF to 300 pF and span plus offset ratios  $(C_A-C_B)/(C_A+C_B)$  up to 0.36.

The Stage 1 gain has two independent registers for the two sensors that can be potentially connected. The Stage 1 gain setting used depends on the SEN CHNL bit in the Sensor Control Register.

## 6.9 Sign Bit Block

The device has a sign bit block that is used for span sign compensation. This block is used to change the polarity of the first stage output, and it is implemented through the use of four switches. The switches are set through the use of the S1\_INV bit for sensor 1 and the S2\_INV bit for sensor 2 in the Sensor Control Register (SENCTRL). There are two independent sign bit settings to accommodate configuring the polarity for two independent sensors. The sensor sign bit used is based on the SEN\_CHNL bit in the Sensor Control Register.

### 6.10 Offset and Offset TC Compensation Blocks

The offset compensation circuit can be configured to null out the sensor offset and first order offset temperature coefficient. The offset compensation block is located between the Sign Bit block and the Stage 2 Gain block as shown in the Section 2.

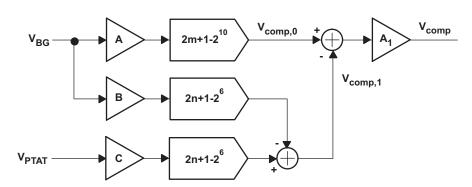

The offset compensation,  $V_{\text{COMP}}$ , is a value that is subtracted from the output of the sign bit block. This offset provides a means to null the sensor offset prior to Stage 2 Gain. The offset compensation circuit block provides ten bits of zero-order compensation and six bits of first-order TC compensation.

A more detailed block diagram of the offset compensation subsystem is shown in Figure 6-6. As shown  $V_{comp}$  is derived from two references,  $V_{BG}$  and  $V_{PTAT}$ . Where  $V_{BG}$  is a precise temperature independent band-gap reference voltage, and  $V_{PTAT}$  is a proportional-to-absolute-temperature voltage. In PGA400-EP, the gains in the offset compensation circuitry (A, B, C) have been designed assuming the following characteristics about the reference signals:

$$V_{BG} = 1.23 \text{ V}$$

(13)

$$V_{PTAT}(T) = k_{PTAT} \bullet (T + 273) + \xi_{PTAT}$$

(14)

where

$$k_{PTAT} = 3.7 \text{ mV/}^{\circ}\text{C}$$

and  $\xi_{PTAT} = -47 \text{ mV}$  (15)

#### **NOTE**

If an external temperature sensor is used, the signal applied to the VIN3 pin must have the same temperature dependency as the above mentioned  $V_{\text{PTAT}}$  signal or else the offset TC compensation does not work as intended.

Figure 6-6. Block Diagram of Offset Compensation Circuit

The zero-order portion of  $V_{COMP}$  is produced by scaling  $V_{BG}$  by the gain A to generate the reference for a 10-bit DAC. The DAC scales this reference by  $2m+1-2^{10}$ , where m is decimal equivalent of the DAC's digital input and ranges from 0 to 1023. The zero-order portion of the compensation voltage is expressed as a function of m as shown in Equation 16.

$$V_{COMP,0}(m) = V_{BG} \bullet A \bullet (2 \bullet m + 1 - 2^{10}) V$$

(16)

The first order portion of  $V_{COMP}$  is constructed from the difference between scaled versions of  $V_{PTAT}$  and  $V_{BG}$ . The reason for this is that the temperature compensation signal should pivot about a particular reference temperature, which ideally would be the same temperature at which the zero-order portion of the sensor offset is calibrated out. Because  $V_{PTAT}$  pivots about 0 K, a temperature independent offset must be introduced to shift the pivot temperature up to a practical value like 22°C. The first-order portion of the compensation voltage is expressed in Equation 17.

$$Vcomp, 1 (n,T) = (C \bullet [k_{PTAT} \bullet (T + 273) + \xi_{PTAT}] - B \bullet V_{BG}) \bullet (2 \bullet n + 1 - 2^6) V$$

(17)

Where the reference temperature about which this function pivots may be expressed in terms of the other variables as shown in Equation 18.

$$T_R = \frac{1}{k_{PTAT}} \cdot \left( \frac{V_{BG} \cdot B}{C} - \varepsilon_{PTAT} \right) - 273 \,^{\circ}C$$

(18)

The gains B and C are set to produce a reference temperature of approximately 22°C.

When Equation 17 and Equation 18 are combined and consolidate the values of the constants, the final output voltage of the offset compensation circuit is expressed as a function of m, n, T, and  $A_1$  in the following way:

$$V_{comp}(m, n, T, A1) = A_1 \cdot \frac{1277}{3} \cdot \left[ 250 \cdot (2 \cdot m + 1 - 2^{10}) + 4.921 \cdot (T - 22)g(2 \cdot n + 1 - 2^{6}) \right] nV$$

(19)

For resistive sensors, the gain used for the offset compensation calculation is always the same as the first stage gain in the AFE and is controlled by the same registers. For capacitive sensors,  $A_1$  is an independent variable that may be set to meet a specific sensor or noise requirements.

## NOTE

The above voltage V<sub>comp</sub> is subtracted (differentially) from the output of the first stage.

The Offset and Offset TC has two independent registers, Sensor 1 Offset Register (SEN1OFF1 and SEN1OFF2) and Sensor 2 Offset Register (SEN2OFF1 and SEN2OFF2), to accommodate for two independent sensors that can be potentially connected. The sensor offset value used is based on the SEN\_CHNL bit in the Sensor Control Register (SENCTRL).

## 6.11 Stage 2 Gain Block

The Stage 2 Gain block is contructed with a low flicker noise, low offset amplifier. Both resistive bridge sensors and capacitive sensors share this gain stage. The gain setting for this stage ranges from 1 V/V to 25 V/V in 32 possible steps.

The Stage 2 Gain block has two independent registers, Sensor 1 Gain Register (SEN1GAIN) and Sensor 2 Gain Register (SEN2GAIN). This accommodates two different sensors that can be connected with different gain settings. The Stage 2 gain is determined by the SEN\_CHNL bit in Sensor Control Register.

#### 6.12 ADC Buffer Blocks

The device has two buffer blocks, one for the pressure signal path and one for the temperature signal path.

## 6.12.1 Analog to digital Converter Buffer 1

The ADC Buffer 1 is a differential amplifier with 2X gain that is used to condition the pressure signal before reaching the Analog to Digital Converter (ADC).

In addition to gain this block can be configured to provide a level shift using the ADC\_BUF bit in Sensor Control Register (SENCTRL). When this bit is set to '0', no offset is introduced to the signal, and the output of the ADC buffer is simply two times the output of Gain Stage 2. When this bit is set to '1', a -1.65 V offset is introduced such that the output of the ADC buffer is equal to two times the output of Gain Stage 2 minus 1.65 V. The Level Shift feature of the ADC Buffer shifts the output of the Stage 2 Gain so that the full dynamic range of the sigma-delta modulator can be used.

#### 6.12.2 Analog to digital Converter Buffer 2

The ADC Buffer 2 is a unity gain differential amplifier. This buffer block conditions the temperature signal before reaching the ADC.

#### 6.13 Sigma Delta Modulator Blocks

There are two independent Sigma Delta Modulator ADCs, one for the pressure signal and another for the temperature signal.

### 6.13.1 Sigma Delta Modulator for AD Converter 1

The Sigma Delta Modulator 1 block is a 1-bit 1MHz sigma-delta modulator for the pressure sensor signal. To further condition the signal this stage is followed by two stages of digital decimation filters.

## 6.13.2 Sigma Delta Modulator for AD Converter 2

The Sigma Delta Modulator 2 block is a 1-bit 128kHz sigma-delta modulator for the temperature signal. The input signal to the sigma-delta modulator can come from either the internal or external temperature. The output of this ADC is followed by a single decimation filter.

FUNCTIONAL DESCRIPTIONS

#### 6.14 Decimation Filter Blocks

The device contains three Signal Decimation Filters. Two back to back decimation filters for the pressure sensor signal path and one decimation filter for the termperature path.

#### 6.14.1 ADC1 Decimation Filter Blocks

The sensor signal path contains two decimation filters in series with each other. The first decimation filter has a fixed decimation ratio and a second decimation filter that has a variable decimation ratio.

The 1st Stage Decimator Filter has a fixed decimation ratio of 32. Based on the 1MHz sampling frequency of the sigma-delta modulator, the output rate of the 1st stage decimator is fixed at 32 µs per sample.

The 2nd Stage Decimator has a variable decimation ratio. This filter further decimates the output of the first stage decimator. The decimation ratios of the second stage can be configured for a decimation ratio of 2, 4, or 8 using the OSR[1..0] bits in the Decimator and Low Power Control Register (DECCTRL).

The output of the second decimation filter in the sensors signal path is a 16 bit **signed** value. Some example second stage decimation output codes for given differential voltages at the input of the sigma delta modulator are shown in Table 6-3:

Table 6-3. Input Voltage to Output Counts for the Signal Channel ADC

| SIGMA DELTA MODULATOR<br>DIFFERENTIAL INPUT VOLTAGE | NOISE-FREE OUTPUT |  |  |

|-----------------------------------------------------|-------------------|--|--|

| -3.3V                                               | -32768            |  |  |

| -1.65V                                              | -16384            |  |  |

| 0                                                   | 0                 |  |  |

| 1.65V                                               | 16383             |  |  |

| 3.3V                                                | 32767             |  |  |

#### 6.14.2 Decimation Filters for AD Converter 2

The temperature path contains one fixed ratio decimation filter block after the sigma delta modulator. The filter is 10-bit with fixed decimation ratio of 1024. Based on the 128-kHz sampling frequency, the output rate of the fixed ratio decimation filter is fixed at 8 ms per sample.

The output of the temperature channel decimation filter is a 10 bit **signed** value. The equation to calculate the relationship between the input voltage at VIN3 and the output of the decimator block is shown below.

ADC Code =  $760^{\circ}$  VIN3 -820, VIN3 is voltage at the input of the buffer in volts. (20)

Table 6-4 summarizes the relationship between the internal temperature sensor and the decimator output.

Table 6-4. Input Voltage to Output Counts for the Temperature Channel ADC

| INTERNAL TEMPERATURE | NOISE-FREE OUTPUT OF<br>TEMPERATURE CHANNEL<br>DECIMATOR |

|----------------------|----------------------------------------------------------|

| -40°C                | -196                                                     |

| -20°C                | -140                                                     |

| 0°C                  | -83                                                      |

| 20°C                 | -27                                                      |

| 40°C                 | 28                                                       |

| 150°C                | 338                                                      |

## 6.14.3 Accessing the ADC Values for the 8051

the ADC Decimator Output Register (ADCMSB and ADCLSB) makes available the output of all three decimators that are available to the microprocessor.

The microprocessor specifies which decimator is loaded by writing a "1" to the appropriate bit in the Load ADC Decimator Shadow Register (LD DEC).

If more than 1 bit in the LD\_DEC register is set to 1 simultaneously, then only one decimator output is loaded into ADCMSB and ADCLSB register. The priority used to determine which decimator output gets loaded is as follows:

- Decimator 1 Output

- Decimator 2 Output

- Temperature Decimator

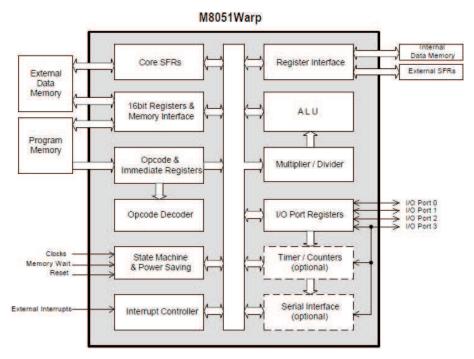

## 6.15 8051 WARP Microprocessor Block

The 8051 WARP microprocessor is an exceptionally high-performance version of this popular 8-bit microcontroller, requiring only 2 clocks per machine cycle rather than the 12 clocks per cycle of the industry standard device while it maintains functional compatibility with the standard device

Figure 6-7. 8051W Core. The 8051W core includes two 16-bit timers and serial interface.

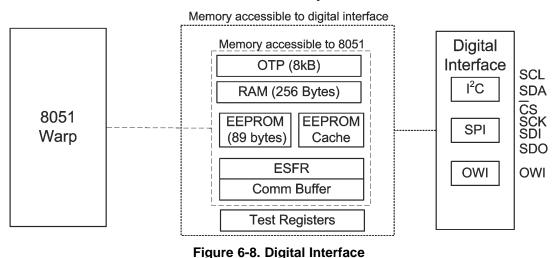

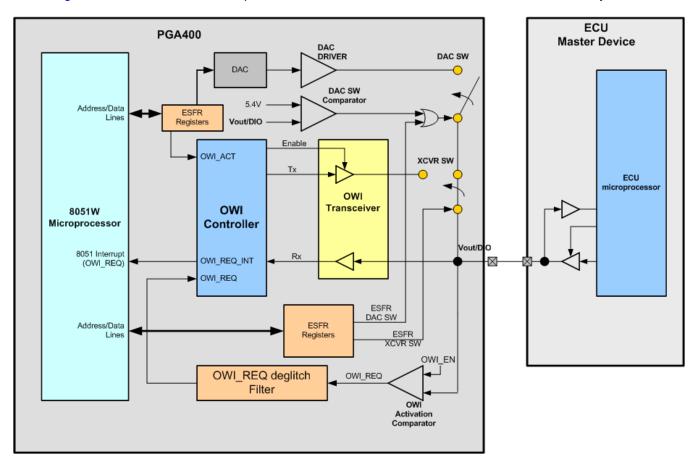

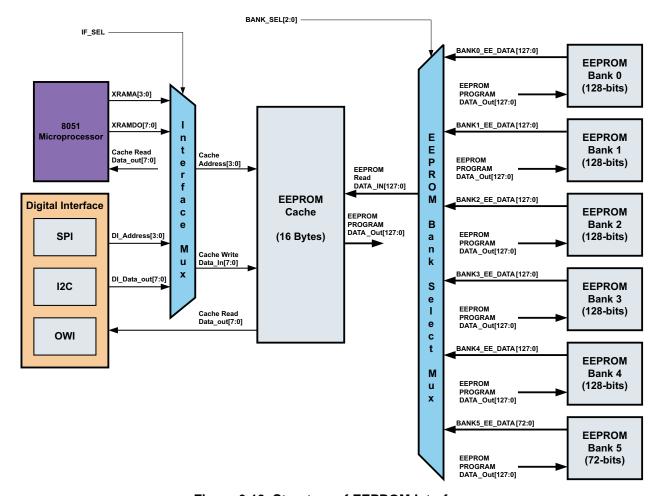

## 6.16 Digital Interface

The digital interfaces are used to access (read as well as write) the internal memory spaces described in Section 6.20. Each interface uses different pin(s) for communication. The device has three separate modes of communication:

- 1. One-Wire Interface (OWI)

- 2. Serial Peripheral Interface (SPI)

- 3. Inter-Integrated Circuit (I<sup>2</sup>C)

Each communication mode has its own protocol of communication, but all three access the same memory elements within the device. For all three communication modes the PGA400-EP device operates as a slave device.

Figure 6-8 shows the interface between the 8051W, the Memory block and the Digital Interface. In the PGA400-EP, only the Digital Interface OR the 8051W can access can access the internal memory spaces. It is not possible for both 8051W and the Digital Interface to access the memory spaces simultaneously. Therefore there is an access selection bit called IF\_SEL in the Micro/Interface Control Register (MICRO\_IF\_SEL\_T) that allows either the 8051W microprocessor or the digital interfaces to have access to the OTP, EEPROM, ESFR and RAM memory spaces.

Figure 6-8 also shows that a special memory space called the Test Registers are only accessible only via the Digital interface. Since the Micro/Interface Control Register is in the Test Register memory block which is only accessible via the digital interface, only the digital interfaces can change the memory access selection.