# 10 Gbit/s Physical Layer Device for POS, ATM and Ethernet

### GENERAL DESCRIPTION

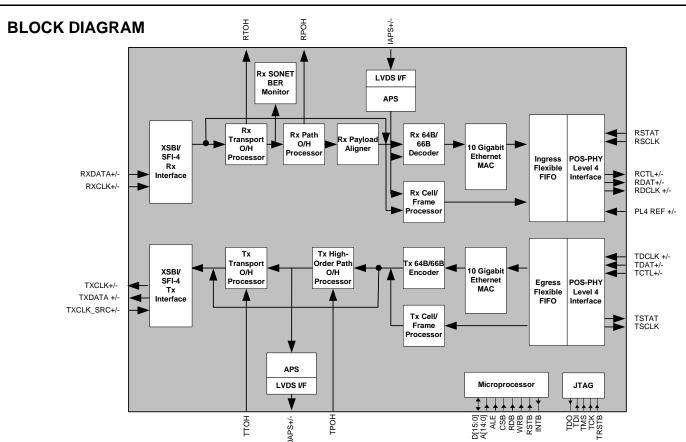

The S/UNI-9953 is a single chip ATM, POS and 10 Gigabit Ethernet User-Network Interface operating at 9953.28 Mbit/s and 10.3 Gbit/s. The S/UNI 9953 is intended for use in OC-192c and high-density OC-48c POS/ATM applications as well as 10 Gigabit Ethernet WAN and LAN PHY port cards.

## **FEATURES**

- Provides WAN Interface Sub-layer (WIS), Physical Coding Sub-layer (PCS), and Media Access Controller (MAC) functionality for OC-192c rate 10 Gigabit Ethernet WAN PHY datastream.

- Provides PCS and MAC layer functionality for 10.3 Gbit/s 10 Gigabit Ethernet LAN PHY datastream.

- Supports framing, scrambling/ descrambling and pointer processing for the following:

- STS-192c (STM-64-64c).

- 4 x STS-48c (4 x STM-16-16c).

- STS-192 (STM-64) channelized down to STS-48c (STM-16c).

- Supports alarm signal insertion/detection, B1/2/3 processing and insertion/termination of SONET Section/Line/Path overhead bytes (or SDH equivalents).

- Provides ATM and POS payload processing for:

- STS-192c (STM-64-64c)

- 4 x STS-48c (4 x STM-16-16c).

- STS-192 (STM-64) channelized down to STS-48c (STM-16c).

### **INTERFACES**

- Provides SATURN® POS-PHY™ Level 4 16-bit LVDS System-side Interface (clocked at 700 MHz nominal).

- Directly connects to optics via 16 bit by 622 MHz OIF SFI-4 (OIF99.102) or 16 bit by 622/645 MHz IEEE P802.3ae XSBI line-side interfaces.

### POS/ATM

- Implements the ATM Forum User Network Interface Specification and the ATM physical layer for Broadband ISDN according to CCITT Rec. I.432.

- Implements the Point-to-Point Protocol (PPP) over SONET/SDH specification according to RFC 2615(1619)/1662 of the PPP Working Group of the Internet Engineering Task Force (IETF).

### 10 GIGABIT ETHERNET

- Implements 10 Gigabit Ethernet WAN and LAN PHY according the IEEE P802.3ae standard currently under development.

- Provides standard IEEE P802.3ae 10 Gigabit Ethernet Media Access Controller (10GMAC) for frame verification.

- Implements IEEE P802.3ae 64B/66B Physical Coding Sub-layer (PCS).

#### 10 GIGABIT ETHERNET MAC

Verifies frame integrity (FCS and length checks).

# 10 Gbit/s Physical Layer Device for POS, ATM and Ethernet

- Provides egress Ethernet frame encapsulation (pads to min. size, add preamble, IFG and CRC generation).

- · Supports VLAN tagged frames.

- Provides eight exact-match address filters to filter frames based on SA, DA or VID.

- Provides 64-bin hash based algorithm to filter multicast addresses.

- · Minimum frame size of 64 bytes.

- Provides statistics counters to support RMON/SNMP.

- Supports jumbo frames up to 9.6 Kbytes.

- Programmable inter-packet gap (IPG).

- Implements in-band PAUSE flowcontrol and provides support for out-ofband flow control.

- Upper layer device can flow-control using dedicated pins or host signaling to cause generation of a PAUSE frame.

### **GENERAL**

- Provides internal FIFOs (16 KB ingress, 20 KB egress) to accommodate system latencies.

- Provides line-side and system-side loopbacks for system level diagnostic capability.

- Provides support for automatic protection switching (APS) via two 16bit LVDS 777.76 MHz ports.

- Provides a generic 16-bit microprocessor bus interface for configuration, control, and status monitoring.

- Standard 5 signal P1149.1 JTAG test port.

- Low power 1.8 V CMOS core logic with 3.3 V CMOS/TTL compatible digital inputs and digital outputs.

- Industrial temperature range (-40 °C to +85 °C).

- 1152 pin FCBGA package.

### **DEVICE INTERWORKING**

- Other PMC-Sierra devices that implement the POS-PHY Level 4 interface include:

- S/UNI 1x10GE.

- · S/UNI 10xGE.

- · S/UNI 9953-POS.

#### POS-PHY LEVEL 4 INTERFACE

- Designed to transmit cells, packets or frames between physical and data-link layer devices.

- Supports mixed traffic protocols on a channel by channel basis.

- Requires less pins and draws less power than other 10 Gigabit interface options.

- Compliant with the following standards:

- Optical Internetworking Forum -System Physical Interface Level 4 Phase II (SPI-4 Phase II).

- ATM Forum Frame Based ATM Interface Level 4 (ATMF0161.00).

- SATURN® POS-PHY<sup>™</sup> Level 4, Issue 6, March 2001.

### **APPLICATIONS**

- Edge and Core Routers.

- Multi-Service (Multi-Protocol) Switches.

- Internet POP and Transport POP L2 Ethernet Switches.

- SONET/SDH add/drop multiplexers and optical cross-connects.

- WAN and Edge ATM switches.

- · Up-link cards.

- SONET/SDH ATM/POS and 10 Gigabit Ethernet test equipment.

- Emerging DPT, IPT, and GFP applications.

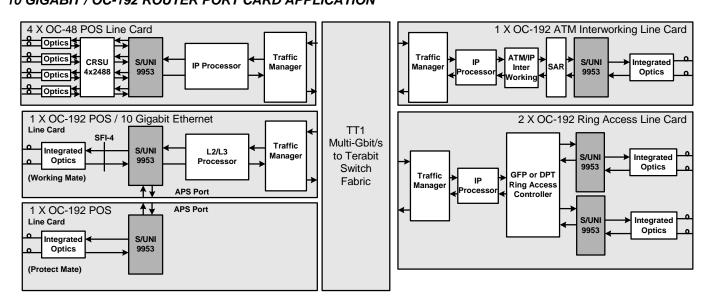

# TYPICAL APPLICATION 10 GIGABIT / OC-192 ROUTER PORT CARD APPLICATION

Head Office: PMC-Sierra, Inc. #105 - 8555 Baxter Place Burnaby, B.C. V5A 4V7 Canada Tel: 604.415.6000

Fax: 604.415.6200

To order documentation, send email to: document@pmc-sierra.com or contact the head office, Attn: Document Coordinator

All product documentation is available on our web site at: http://www.pmc-sierra.com

For corporate information, send email to: info@pmc-sierra.com

PMC-2000181 (A2)

© Copyright PMC-Sierra,

Inc. 2001. All rights reserved.

SATURN and S/UNI are

registered trademarks and

POS-PHY and PMC-Sierra

are trademarks of PMCSierra, Inc.