# **Quad Power Sequencing Controller**

### Features

- Power supply sequencer with four outputs

- Power-up and power-down sequencing

- Six programmable delays

- Maximum 90V supply voltage

- Input voltage window comparator

- Low power supply current (500µA typical)

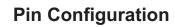

- 16-Lead SOIC Package

## Applications

- Reduction of transient current demand and protection of sensitive loads

- Telecom and networking systems

- High voltage MEMS and display driver supplies

## **General Description**

Many systems require that their power supplies are enabled and disabled sequentially in order to reduce transient current demand on the power bus, or to avoid damage to components having multiple supply voltages such as microprocessors, ASICs, MEMS drivers, etc.

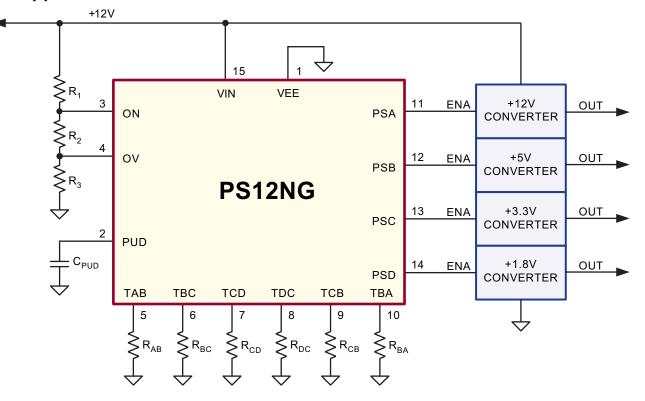

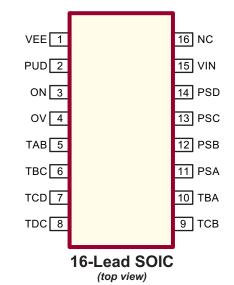

The PS12 incorporates a power-up delay timer, a window voltage comparator, 4 open drain enable outputs, and 6 enable delay timers. The enable delays are individually programmable for both the power-up (ABCD) and the power-down (DCBA) sequence.

Power-up and power-down are controlled by a window comparator formed by the ON and OV voltage comparators.  $V_{IN}$  voltage within the window initiates power-up;  $V_{IN}$  voltage outside of the window maintains or initiates power-down. The power-up sequence may be interrupted while in progress. The power-down sequence, once initiated, cannot be interrupted until it is brought to completion.

### **Typical Application Circuit**

## **Ordering Information**

|        | Dovice                                           | Package Option |  |  |  |  |  |  |

|--------|--------------------------------------------------|----------------|--|--|--|--|--|--|

| Device | Device                                           | 16-Lead SOIC   |  |  |  |  |  |  |

|        | PS12                                             | PS12NG-G       |  |  |  |  |  |  |

|        | -G indicates package is RoHS compliant ('Green') |                |  |  |  |  |  |  |

## **Absolute Maximum Ratings**

| Parameter                                      | Value       |

|------------------------------------------------|-------------|

| VIN <sup>1</sup>                               | -0.3V+100V  |

| PSAPSD <sup>1</sup>                            | -0.3V+100V  |

| ON, OV <sup>1</sup>                            | -0.3V+8V    |

| ESD (all pins except VIN, PSAPSD) <sup>2</sup> | ±2kV        |

| Operating ambient temperature                  | -40°C+85°C  |

| Operating junction temperature                 | -40°C+125°C |

| Storage temperature                            | -65°C+150°C |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

Notes:

1. Referenced to VEE 2. HBM, 1.5kΩ, 100pF

### **Thermal Resistance**

| Package                | <b>H</b> <sub>ja</sub> |

|------------------------|------------------------|

| 16-Lead SOIC           | 65K/W to 120K/W        |

| (PCB Layout dependent) |                        |

## **Block Diagram**

## **Pin Configuration**

| Top Marking           |                                                                         |

|-----------------------|-------------------------------------------------------------------------|

| PS12NG<br>YWW LLLLLLL | Y = Last Digit of Year Sealed<br>WW = Week Sealed<br>L = Lot Number     |

| Bottom Marking        | C = Country of Origin                                                   |

| AAA 222222222         | A = Assembler ID*<br>= "Green" Packaging<br>*May be part of top marking |

|                       |                                                                         |

### **Electrical Characteristics**

$(T_{J} = 25^{\circ}\text{C unless otherwise specified. Voltages referenced to VEE, V_{VIN} = +4.5V...+90V. Values marked with * apply over the full temperature range.)$

| Symbol             | Parameter                                 | Min     | Тур  | Max  | Units |   | Conditions                                  |  |

|--------------------|-------------------------------------------|---------|------|------|-------|---|---------------------------------------------|--|

| Supply (V          | N)                                        |         |      |      |       |   |                                             |  |

| V <sub>VIN</sub>   | Supply voltage                            | 4.5     | -    | 90   | V     | * |                                             |  |

| 1                  | Supply surrent                            | -       | 500  | 625  |       | - | V <sub>IN</sub> = 36V, R <sub>T</sub> = 2MΩ |  |

| I <sub>VIN</sub>   | Supply current                            | -       | 400  | -    | μA    | - | $V_{IN} = 12V, R_T = 2M\Omega$              |  |

| nput Volta         | age Monitor (ON)                          |         |      |      |       |   |                                             |  |

| V                  | Power-up threshold                        | 1.16    | 1.22 | 1.28 | V     | * | V <sub>on</sub> Rising                      |  |

| V                  | Power-down threshold                      | 1.06    | 1.12 | 1.18 | V     | * | V <sub>on</sub> Falling                     |  |

| V <sub>HY</sub>    | Power-up/Power-down hysteresis            | -       | 100  | -    | mV    | - |                                             |  |

| I <sub>ON</sub>    | Input Current                             | -       | ±1   | -    | nA    | - |                                             |  |

| nput Volta         | age Monitor (OV)                          |         |      |      |       |   |                                             |  |

| $V_{OVPD}$         | Power-down threshold                      | 1.16    | 1.22 | 1.28 | V     | * | V <sub>ov</sub> Rising                      |  |

| V                  | Power-up threshold                        | 1.06    | 1.12 | 1.18 | V     | * | V <sub>ov</sub> Falling                     |  |

| V <sub>HY</sub>    | Power-up/power-down hysteresis            | -       | 100  | -    | mV    | - |                                             |  |

| I <sub>ov</sub>    | Input current                             | -       | ±1   | -    | nA    | - |                                             |  |

| Power Su           | oply Enable Outputs (PSA, PSB, PSC, PSD)  |         |      |      |       |   |                                             |  |

| I <sub>LKG</sub>   | High state leakage current                | -       | -    | 10   | μA    | * | V <sub>PS</sub> = 90V PS = HiZ              |  |

| V <sub>SAT</sub>   | Low state output voltage                  | -       | -    | 100  | mV    | - | I <sub>PS</sub> = 1mA PS = Low              |  |

| Power-up           | Delay (PUD)                               |         |      |      |       |   |                                             |  |

| I <sub>PUD</sub>   | Output current                            | -8.4    | -12  | -16  | μA    | - |                                             |  |

| V <sub>PUD</sub>   | Threshold voltage                         | 1.15    | 1.20 | 1.25 | V     | - |                                             |  |

| $R_{\text{DISCH}}$ | Discharge FET ON resistance               | -       | 500  | -    | Ω     | - | I <sub>DISCH</sub> = 1mA                    |  |

|                    | oply Enable Timing (TAB, TBC, TCD, TDC, T | CB, TBA | A)   |      |       |   |                                             |  |

| R <sub>T</sub>     | Timing resistance range                   | 50      | -    | 2000 | kΩ    | - |                                             |  |

|                    |                                           | 160     | 200  | 240  | ms    |   | R <sub>τ</sub> = 2MΩ                        |  |

| $T_{PSPS(MAX)}$    | Maximum PS-to-PS delay                    | 100     | 200  | 240  | 1115  | - | $R_{T} = 210122$                            |  |

## **Pin Description**

| Pin # | Function | Description                                                                                                                                                                                  |

|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | VIN      | Power supply pins.                                                                                                                                                                           |

|       |          | VIN positive with respect to VEE.                                                                                                                                                            |

| 1     | VEE      | The outputs PSA thru PSD are pulled to a logic low state upon application of power.                                                                                                          |

| 2     | PUD      | Hookup pin for the power-up-delay (PUD) timing capacitor.                                                                                                                                    |

| 2     |          | Pin pulls capacitor to ground upon application of power. (See timing diagram)                                                                                                                |

| 3     | ON       | Input pin of the ON comparator. Rising transition initiates power-up sequence.                                                                                                               |

| 4     | OV       | Input pin of the OV comparator. Rising transition initiates the power-down sequence.                                                                                                         |

| 5     | TAB      |                                                                                                                                                                                              |

| 6     | TBC      | Hookup pins for timing resistors.                                                                                                                                                            |

| 7     | TCD      | On power-up, the resistor at TAB determines the delay between the rising transitions of PSA and RSB; similarly, TBC relates to (RSB (RSC)) and TCD to (RSC) (RSD)                            |

| 8     | TDC      | PSB; similarly, TBC relates to ( PSB / PSC ), and TCD to ( PSC / PSD ).                                                                                                                      |

| 9     | ТСВ      | On power-down, the resistor at TDC determines the delay between the falling transitions of PSD and PSC; similarly, TCB relates to ( PSC / PSB ), and TBA to ( PSB / PSA ).                   |

| 10    | TBA      |                                                                                                                                                                                              |

| 11    | PSA      | Power supply enable output pins.                                                                                                                                                             |

| 12    | PSB      | These four pins control loads, such as DC/DC converter modules, load switches, ICs, etc. Configured with open drain output stages.                                                           |

| 13    | PSC      | On power-up, right after expiration of the PUD delay, the sequencer asserts PSA, and subsequently asserts PSB, PSC and PSD observing the delays, programmed by the (TAB, TBC, and TCD) pins. |

| 14    | PSD      | On power-down, the sequencer deasserts PSD, and subsequently deasserts PSC, PSB, and PSA observing the delays, programmed by the (TAB, TBC, and TCD) pins.                                   |

| 16    | NC       | No connect                                                                                                                                                                                   |

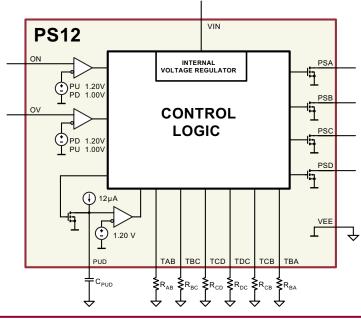

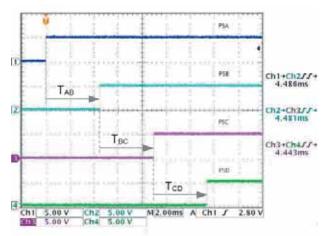

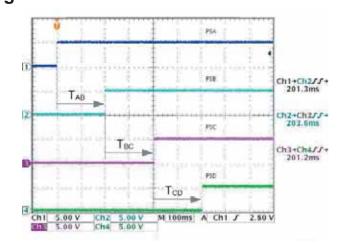

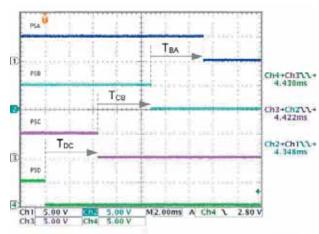

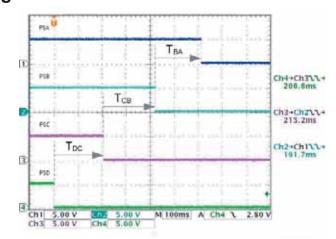

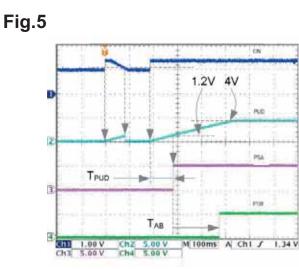

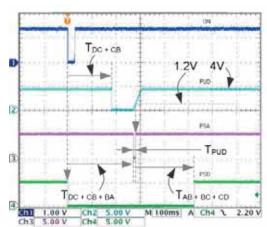

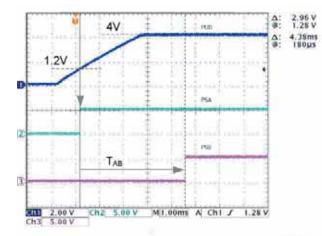

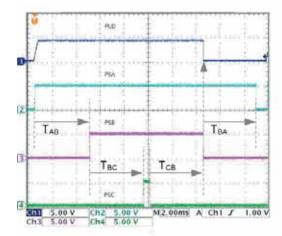

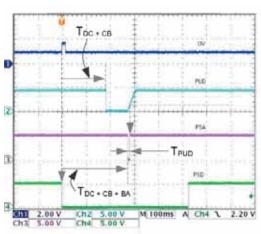

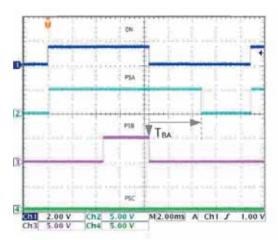

## Oscillograms

| Figure     | Function              | Description                                                                                                   |  |  |  |  |  |  |

|------------|-----------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1, 2, 3, 4 | PS (A, B, C, D)       | Power-up and power-down delays. Delay times around 5ms and 200ms.                                             |  |  |  |  |  |  |

| 5, 6       | ON, PUD, PS (A, B, D) | ON pin detail. Fig.6. shows a power-down / power-up sequence.                                                 |  |  |  |  |  |  |

| 7, 8       | PUD, PS (A, B)        | PUD pin detail; PSA is asserted when voltage at PUD pin about 1.2V.<br>PUD pin resets when PSB is deasserted. |  |  |  |  |  |  |

| 9          | OV, PUD, PS (A, B)    | OV pin detail. Overvoltage returns to voltage window.                                                         |  |  |  |  |  |  |

| 10         | ON, PS (A, B, C)      | Partial power-up sequence. Power-down triggered by loss of valid ON.                                          |  |  |  |  |  |  |

The figures of typical waveforms are organized in the following way:

Fig.1

Fig.2

Fig.3

Fig.4

Fig.7

Fig.8

Fig.10

## **Functional Description**

The PS12 provides power-up and power-down sequencing for devices such as power supply modules, load switches, ICs, etc. The four outputs PSA thru PSD are configured with open drain drivers, which are typically used to power supply modules. Some systems may require level-shifting or isolating drivers.

Upon application of power, the power-up delay timer is reset and the enable outputs PSA thru PSD are de-asserted.

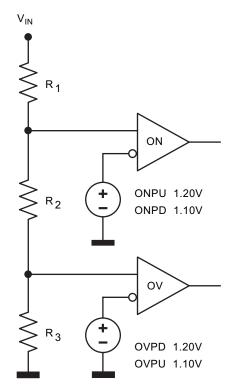

#### Window Comparator

The state of the four PS outputs and the associated powerup and power-down sequencing is controlled by a window comparator formed by the ON and OV voltage comparators.

These comparators define a voltage window having thresholds programmed by an external resistive divider. The ON comparator defines the lower threshold of the window, while the OV comparator defines the upper threshold of the window. Both comparator thresholds feature 200mV hysteresis.

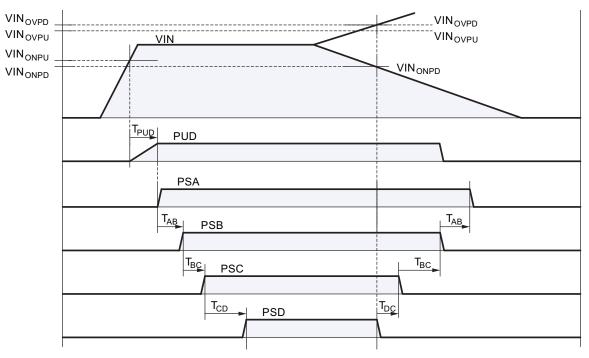

#### **Power-up and Power-down Sequence**

Power supply voltage moving into the window causes the start of a power-up sequence. The sequence consists of the power-up delay, programmed by  $C_{PUD}$ , and the subsequent assertion of the PS outputs in the sequence ABCD using the enable to enable delays ( $T_{AB}$ ,  $T_{BC}$ ,  $T_{CD}$ ), as programmed by the resistors ( $R_{AB}$ ,  $R_{BC}$ ,  $R_{CD}$ ).

Power supply voltage moving outside the window causes the start of a power-down sequence. The sequence consists of the de-assertion of the most recently asserted PS output, typically PSD, and subsequent de-assertion of other asserted PS outputs in the sequence DCBA using the enable delays ( $T_{DC}$ ,  $T_{CB}$ ,  $T_{BA}$ ), as programmed by the resistors ( $R_{DC}$ ,  $R_{CB}$ ,  $R_{BA}$ ).

The power-up sequence may be terminated prematurely by a power-down sequence. On the other hand, the power-down sequence is latching in nature; once power-down is initiated, the sequence is brought to completion regardless of changes in the state of the window comparator. After the power-down sequence is completed, a new power-up sequence may start, depending on the state of the window comparator at that time.

### Enable Outputs at Low $V_{IN}$

The internal circuits of the PS12 can be expected to provide well-defined outputs at a power supply voltage of about 3.3V and above.

At lower power supply voltages, the existence of poorly defined output levels should typically not be an issue if the PS12 and the controlled loads share the same supply, since the loads may not be adequately biased as well.

Some caution is warranted when the controlled loads are independently powered and the power supply voltage to the PS12 is inadequate or ill-defined.

#### **Delay Time Considerations**

The PS12 is characterized for enable to enable delay times between 5ms and 200ms, which should cover most applications. Initial characterization of this device shows excellent linearity between delay time and programming resistance for a delay time in the range of 2.5ms to 5 seconds.

Shorting of a programming pin is not advised, and may reduce long term reliability, as internal circuits are not dimensioned for sourcing the resultant pin current.

### Power-up Delay (PUD)

The power-up delay is set by the time required to charge the  $C_{PUD}$  capacitor to 1.2V. The PUD pin sources a current of 12µA, resulting in a delay time of 100ms per µF. Charging continues past the power-up delay until a voltage of about 4V is reached.

An internal voltage comparator at the PUD pin inhibits the power-up sequence, should the  $C_{PUD}$  capacitor not be discharged before initiating the power-up delay.

Discharge of the  $C_{PUD}$  capacitor occurs during the powerdown sequence. The discharge transistor is turned on at the end of the sequence when PSA is the last remaining asserted output.

#### **Programming ON and UV**

Start the design by programming the power-up voltage. The power-down voltage  $VIN_{ONPD}$  is fixed at 83.3% of the power-up voltage. Next, program the overvoltage power down voltage  $V_{OVPD}$  by selecting the multiplying factor  $R_2 / R_3$ , knowing  $VIN_{ONPLI}$ .

A numerical example:

$V_{IN}$  = 12V and  $[R_1, R_2, R_3]$  = [107k $\Omega$ , 4.99k $\Omega$ , 9.09k $\Omega$ ], results in the following:

(1)

$$R_{DIV} = 121.1 k\Omega$$

(2)  $I_{DIV} = 99.1 \mu A$ ,

(3) [VIN<sub>ONPU</sub>, VIN<sub>ONPD</sub>, VIN<sub>OVPD</sub>, VIN<sub>OVPU</sub>] = [10.32V, 8.60V, 15.98V, 13.32V].

Note the following:

$$\frac{\text{VIN}_{\text{OVPD}}}{\text{VIN}_{\text{ONPU}}} = \frac{\frac{\text{V}_{\text{OVPD}}}{\text{R}_3}}{\frac{\text{V}_{\text{ONPU}}}{\text{R}_2 + \text{R}_3}} = \frac{1.20}{1.20} \left(\frac{\text{R}_2 + \text{R}_3}{\text{R}_3}\right) = 1 + \frac{\text{R}_2}{\text{R}_3}$$

#### Programming the Power-up Delay

The power-up delay  $(T_{PUD})$  is set by the time required to charge the  $C_{PUD}$  capacitor to the threshold voltage  $V_{PUD}$ :

$$V_{PUD} = 1.20V$$

$$I_{PUD} = 12\mu A$$

$$T_{PUD} = \frac{C_{PUD} \bullet V_{PUD}}{I_{PUD}}$$

A numerical example:

A 100nF capacitor results in a T<sub>PUD</sub> of 12ms.

### Programming the PS to PS Delay

The PS to PS delays are set by the six timing resistors. Delay time and resistance are related as follows:

$$T_{PSPS} = K_T \cdot R_T$$

$$K_T = 100 \frac{ns}{O}$$

A numerical example:

A resistance of  $100k\Omega$  results in a delay time of 10ms.

The ON and OV inputs draw negligible current, allowing the use of a high impedance divider. A divider current between  $10\mu$ A and  $100\mu$ A is more than adequate.

$$R_{DIV} = R_1 + R_2 + R_3$$

$$I_{DIV} = \frac{V_{IN}}{R_{DIV}}$$

$V_{IN}$  thresholds can be determined from the following:

| ON<br>Power-up:   | V <sub>ONPU</sub> = 1.20V | $\frac{VIN_{ONPU}}{R_{DIV}} = \frac{V_{ONPU}}{R_2 + R_3}$                                                         |

|-------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------|

| ON<br>Power-down: | V <sub>ONPD</sub> = 1.00V | $\frac{\text{VIN}_{\text{ONPD}}}{\text{R}_{\text{DIV}}} = \frac{\text{V}_{\text{ONPD}}}{\text{R}_2 + \text{R}_3}$ |

| OV<br>Power-down: | V <sub>OVPD</sub> = 1.20V | $\frac{\text{VIN}_{\text{OVPD}}}{\text{R}_{\text{DIV}}} = \frac{\text{V}_{\text{OVPD}}}{\text{R}_{3}}$            |

| OV<br>Power-up:   | V <sub>OVPU</sub> = 1.00V | $\frac{\text{VIN}_{\text{OVPU}}}{\text{R}_{\text{DIV}}} = \frac{\text{V}_{\text{OVPU}}}{\text{R}_{3}}$            |

## **Timing Diagram**

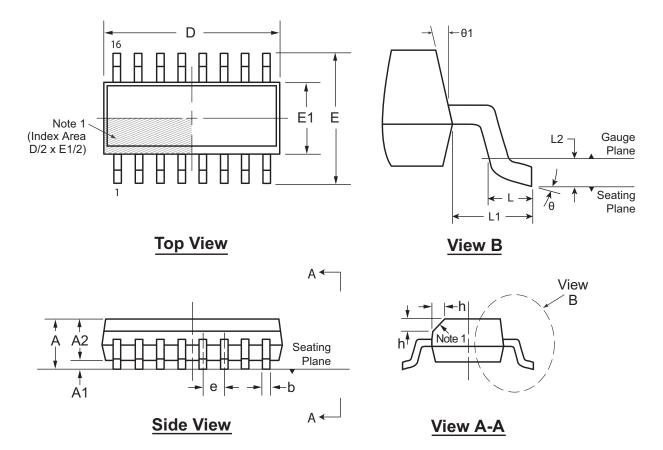

## 16-Lead SOIC (Narrow Body) Package Outline (NG) 9.90x3.90mm body, 1.75mm height (max), 1.27mm pitch

#### Note 1:

This chamfer feature is optional. If it is not present, then a Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier may be either a mold, or an embedded metal or marked feature.

| Symb              | ol  | A    | A1   | A2   | b    | D     | E    | E1   | е           | h       | L    | L1          | L2          | θ              | θ1              |

|-------------------|-----|------|------|------|------|-------|------|------|-------------|---------|------|-------------|-------------|----------------|-----------------|

| <b>D</b>          | MIN | 1.35 | 0.10 | 1.25 | 0.31 | 9.80  | 5.80 | 3.80 | 1.27<br>BSC | 0.25 0. | 0.40 | 1.04<br>REF | 0.25<br>BSC | 0 <sup>0</sup> | 5°              |

| Dimension<br>(mm) | NOM | -    | -    | -    | -    | 9.90  | 6.00 | 3.90 |             | -       | -    |             |             | -              | -               |

|                   | MAX | 1.75 | 0.25 | 1.65 | 0.51 | 10.00 | 6.20 | 4.00 | 000         | 0.50    | 1.27 |             | 000         | 8 <sup>0</sup> | 15 <sup>0</sup> |

JEDEC Registration MS-012, Variation AC, Issue E, Sept. 2005. Drawings not to scale.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <u>http://www.supertex.com/packaging.html</u>.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell its products for use in such applications, unless it receives an adequate "product liability indemnification insurance agreement". **Supertex** does not assume responsibility for use of devices described and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions or inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications, refer to the **Supertex** website: http://www.supertex.com.

©2007 Supertex inc. All rights reserved. Unauthorized use or reproduction is prohibited.